(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4046959号

(P4046959)

(45) 発行日 平成20年2月13日(2008.2.13)

(24) 登録日 平成19年11月30日(2007.11.30)

|              |           |              |   |

|--------------|-----------|--------------|---|

| (51) Int.Cl. | F 1       |              |   |

| HO 1 J 31/12 | (2006.01) | HO 1 J 31/12 | C |

| HO 1 J 29/28 | (2006.01) | HO 1 J 29/28 |   |

| HO 1 J 29/92 | (2006.01) | HO 1 J 29/92 | Z |

請求項の数 20 (全 34 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2001-250571 (P2001-250571)  |

| (22) 出願日     | 平成13年8月21日 (2001.8.21)        |

| (65) 公開番号    | 特開2002-150979 (P2002-150979A) |

| (43) 公開日     | 平成14年5月24日 (2002.5.24)        |

| 審査請求日        | 平成17年11月8日 (2005.11.8)        |

| (31) 優先権主張番号 | 特願2000-267594 (P2000-267594)  |

| (32) 優先日     | 平成12年9月4日 (2000.9.4)          |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100085006<br>弁理士 世良 和信                     |

| (74) 代理人  | 100100549<br>弁理士 川口 嘉之                     |

| (74) 代理人  | 100106622<br>弁理士 和久田 純一                    |

| (72) 発明者  | 小島 伸介<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

| (72) 発明者  | 大西 智也<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

最終頁に続く

(54) 【発明の名称】電子線発生装置及び画像形成装置

## (57) 【特許請求の範囲】

## 【請求項 1】

電子線発生装置であって、

電子放出素子を有する電子源基板と、

該電子源基板と対向して配置される対向基板と、を有しており、

該対向基板には、前記電子放出素子が放出する電子を加速する電位が与えられるアノード電位規定領域と、該アノード電位規定領域の周囲に該アノード電位規定領域と所定の間隔を空けて配置され所定の電位が与えられる導電性部材と、前記アノード電位規定領域及び前記導電性部材に接する抵抗膜と、前記アノード電位規定領域と前記導電性部材との間の沿面距離を増大させる沿面距離増大構造と、が設けられていることを特徴とする電子線発生装置。

## 【請求項 2】

前記沿面距離増大構造は、前記アノード電位規定領域と前記導電性部材との間に位置し前記電子源基板に向かって凸である凸部である請求項1に記載の電子線発生装置。

## 【請求項 3】

前記沿面距離増大構造は、前記アノード電位規定領域と前記導電性部材との間に位置し前記電子源基板に向かって凹である凹部である請求項1に記載の電子線発生装置。

## 【請求項 4】

前記沿面距離増大構造は、前記アノード電位規定領域と前記導電性部材との間に位置する凹凸部である請求項1に記載の電子線発生装置。

10

20

**【請求項 5】**

前記凸部の高さが  $1 \mu m$  以上である請求項 2 に記載の電子線発生装置。

**【請求項 6】**

前記沿面距離増大構造が前記アノード電位規定領域の少なくとも周囲 3 辺を取り囲むように配置される請求項 1 乃至 5 のいずれかに記載の電子線発生装置。

**【請求項 7】**

前記電子源基板と前記対向基板との間にそれらの間隔を維持するスペーサを有しており、該スペーサの少なくとも一部もしくはスペーサを固定するための部材の少なくとも一方が前記アノード電位規定領域の領域外に存在し、

前記沿面距離増大構造は、前記スペーサの少なくとも一部もしくはスペーサを固定するための部材が形成されている場所以外の場所に形成される請求項 1 乃至 6 のいずれかに記載の電子線発生装置。 10

**【請求項 8】**

前記抵抗膜のシート抵抗範囲が  $1 \times 10^7$  / 以上、  $1 \times 10^{14}$  / 以下である請求項 1 乃至 7 のいずれかに記載の電子線発生装置。

**【請求項 9】**

電子線発生装置であって、

電子放出素子を有する電子源基板と、

該電子源基板と対向して配置される対向基板と、を有しており、

該対向基板の前記電子源基板に向いた同一平面上に、前記電子放出素子が放出する電子を加速する電位が与えられるアノード電位規定領域と、該アノード電位規定領域の周囲に該アノード電位規定領域と所定の間隔を空けて配置され所定の電位が与えられる導電性部材とを有しており、更に該同一平面上の前記アノード電位規定領域と前記導電性部材との間に、前記導電性部材から放出された電子によって発生する二次電子の多重散乱を抑制するための多重散乱抑制構造が配置されており、 20

前記多重散乱抑制構造は、前記アノード電位規定領域と前記導電性部材との間に位置し前記電子源基板に向かって凸である凸部であることを特徴とする電子線発生装置。

**【請求項 10】**

電子線発生装置であって、

電子放出素子を有する電子源基板と、

該電子源基板と対向して配置される対向基板と、を有しており、

該対向基板の前記電子源基板に向いた同一平面上に、前記電子放出素子が放出する電子を加速する電位が与えられるアノード電位規定領域と、該アノード電位規定領域の周囲に該アノード電位規定領域と所定の間隔を空けて配置され所定の電位が与えられる導電性部材とを有しており、更に該同一平面上の前記アノード電位規定領域と前記導電性部材との間に、前記導電性部材から放出された電子によって発生する二次電子の多重散乱を抑制するための多重散乱抑制構造が配置されており、 30

前記多重散乱抑制構造は、前記アノード電位規定領域と前記導電性部材との間に位置する凹凸部であることを特徴とする電子線発生装置。

**【請求項 11】**

前記凸部の高さが  $1 \mu m$  以上である請求項 9 に記載の電子線発生装置。

**【請求項 12】**

前記多重散乱抑制構造が前記アノード電位規定領域の少なくとも周囲 3 辺を取り囲むように配置される請求項 9 乃至 11 のいずれかに記載の電子線発生装置。

**【請求項 13】**

前記電子源基板と前記対向基板との間にそれらの間隔を維持するスペーサを有しており、該スペーサの少なくとも一部もしくはスペーサを固定するための部材の少なくとも一方が前記アノード電位規定領域の領域外に存在し、

前記多重散乱抑制構造は、前記スペーサの少なくとも一部もしくはスペーサを固定するための部材が形成されている場所以外の場所に形成される請求項 9 乃至 12 のいずれかに 50

記載の電子線発生装置。

【請求項 1 4】

前記導電性部材は、前記アノード電位規定領域を完全に取り囲むように配置される請求項 1 乃至 1 3 のいずれかに記載の電子線発生装置。

【請求項 1 5】

前記電子放出素子は、冷陰極素子である請求項 1 乃至 1 4 のいずれかに記載の電子線発生装置。

【請求項 1 6】

前記アノード電位規定領域と、前記電子放出素子を有する電子源基板側の電極との間の印加電圧が 3 kV 以上である請求項 1 乃至 1 5 のいずれかに記載の電子線発生装置。 10

【請求項 1 7】

前記導電性部材には、前記アノード電位よりも低い電位が与えられる請求項 1 乃至 1 6 のいずれかに記載の電子線発生装置。

【請求項 1 8】

前記導電性部材には、カソード電位が与えられる請求項 1 乃至 1 7 のいずれかに記載の電子線発生装置。

【請求項 1 9】

前記導電性部材には、グランド電位が与えられる請求項 1 乃至 1 7 のいずれかに記載の電子線発生装置。

【請求項 2 0】

上記請求項 1 乃至 1 9 のいずれかに記載の電子線発生装置に前記電子放出素子が放出する電子によって発光する蛍光体を設けたことを特徴とする画像形成装置。 20

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

本発明は電子線発生装置及びこの電子線発生装置を用いた表示装置等の画像形成装置に関するものである。

【0 0 0 2】

【従来の技術】

従来から、電子放出素子として熱陰極素子と冷陰極素子の 2 種類が知られている。このうち冷陰極素子では、例えば表面伝導型放出素子や、電界放出型素子（以下 F E 型と記す）や、金属 / 絶縁層 / 金属型放出素子（以下 M I M 型と記す）、などが知られている。 30

【0 0 0 3】

表面伝導型放出素子としては、例えば M . I . E l i n s o n , R a d i o E n g . E l e c t r o n P h y s . , 1 0 , 1 2 9 0 , ( 1 9 6 5 ) や、後述する他の例が知られている。

【0 0 0 4】

表面伝導型放出素子は、基板上に形成された小面積の薄膜に、膜面に平行に電流を流すことにより電子放出が生ずる現象を利用するものである。この表面伝導型放出素子としては、前記エリンソン等による  $SnO_2$  薄膜を用いたものの他に、Au 薄膜によるもの [ G . D i t t m e r : " T h i n S o l i d F i l m s " , 9 , 3 1 7 ( 1 9 7 2 ) ] や、  $In_2O_3 / SnO_2$  薄膜によるもの [ M . H a r t w e l l a n d C . G . F o n s t a d : " I E E E T r a n s . E D C o n f . " , 5 1 9 ( 1 9 7 5 ) ] や、カーボン薄膜によるもの [ 荒木久他 : 真空、第 26 卷、第 1 号、22 ( 1 9 8 3 ) ] 等が報告されている。 40

【0 0 0 5】

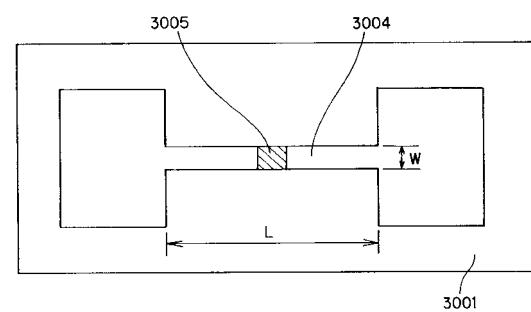

これらの表面伝導型放出素子の素子構成の典型的な例として、図 1 8 に前述の M . H a r t w e l l らによる素子の平面図を示す。

【0 0 0 6】

同図において、3 0 0 1 は基板で、3 0 0 4 はスパッタで形成された金属酸化物よりなる 50

導電性薄膜である。

**【0007】**

導電性薄膜3004は図示のようにH字形の平面形状に形成されている。この導電性薄膜3004に、後述の通電フォーミングと呼ばれる通電処理を施すことにより、電子放出部3005が形成される。図中の間隔Lは、0.5~1[mm]、幅Wは、0.1[mm]に設定されている。

**【0008】**

尚、図示の便宜から、電子放出部3005は導電性薄膜3004の中央に矩形の形状で示したが、これは模式的なものであり、実際の電子放出部の位置や形状を忠実に表現しているわけではない。

10

**【0009】**

M. Hartwellらによる素子をはじめとして上述の表面伝導型放出素子においては、電子放出を行う前に導電性薄膜3004に通電フォーミングと呼ばれる通電処理を施すことにより電子放出部3005を形成するのが一般的であった。

**【0010】**

即ち、通電フォーミングとは、導電性薄膜3004の両端に一定の直流電圧、もしくは、例えば1V/分程度の非常にゆっくりとしたレートで昇圧する直流電圧を印加して通電し、導電性薄膜3004を局所的に破壊もしくは変形もしくは変質せしめ、電気的に高抵抗な状態の電子放出部3005を形成することである。

20

**【0011】**

尚、局所的に破壊もしくは変形もしくは変質した導電性薄膜3004の一部には亀裂が発生する。

**【0012】**

この通電フォーミング後に導電性薄膜3004に適宜の電圧を印加した場合には、亀裂付近において電子放出が行われる。

**【0013】**

FE型の例としては、例えばW.P.Dyke&W.W.Dolan, "Field emission", Advance in Electron Physics, 8, 89(1956)や、或は、C.A.Spinndt, "Physical properties of thin-film field emission cathodes with molybdenum cones", J. Appl. Phys., 47, 5248(1976)などが知られている。

30

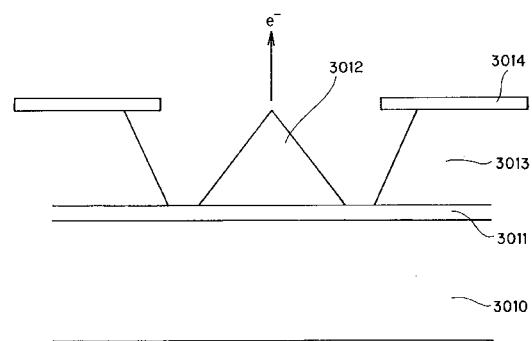

**【0014】**

このFE型の素子構成の典型的な例として、図19に前述のC.A.Spinndtらによる素子の断面図を示す。

**【0015】**

同図において、3010は基板で、3011は導電材料よりなるエミッタ配線、3012はエミッタコーン、3013は絶縁層、3014はゲート電極である。

**【0016】**

本素子は、エミッタコーン3012とゲート電極3014の間に適宜の電圧を印加することにより、エミッタコーン3012の先端部より電界放出を起こさせるものである。

40

**【0017】**

また、FE型の他の素子構成として、図19のような積層構造ではなく、基板上に基板平面とほぼ平行にエミッタとゲート電極を配置した例もある。

**【0018】**

また、MIM型の例としては、例えば、C.A.Mead, "Operation of tunnel-emission Devices", J. Appl. Phys., 32, 646(1961)などが知られている。

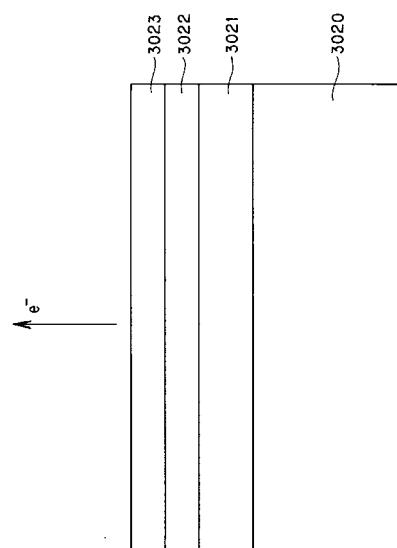

**【0019】**

MIM型の素子構成の典型的な例を図20に示す。同図は断面図であり、図において、3

50

020は基板で、3021は金属よりなる下電極、3022は厚さ100オングストローム程度の薄い絶縁層、3023は厚さ80～300オングストローム程度の金属よりなる上電極である。MIM型においては、上電極3023と下電極3021の間に適宜の電圧を印加することにより、上電極3023の表面より電子放出を起こさせるものである。

#### 【0020】

上述の冷陰極素子は、熱陰極素子と比較して低温で電子放出を得ることができるため、加熱用ヒータを必要としない。

#### 【0021】

従って、熱陰極素子よりも構造が単純であり、微細な素子を作成可能である。また、基板上に多数の素子を高い密度で配置しても、基板の熱溶融などの問題が発生しにくい。また、熱陰極素子がヒータの加熱により動作するため応答速度が遅いのとは異なり、冷陰極素子の場合には応答速度が速いという利点もある。

10

#### 【0022】

このため、冷陰極素子を応用するための研究が盛んに行われてきている。例えば、表面伝導型放出素子は、冷陰極素子の中でも特に構造が単純で製造も容易であることから、大面積にわたり多数の素子を形成できる利点がある。

#### 【0023】

そこで、例えば本願出願人による特開昭64-31332号公報において開示されるように、多数の素子を配列して駆動するための方法が研究されている。

#### 【0024】

20

また、表面伝導型放出素子の応用については、例えば画像形成装置、画像記録装置などの画像形成装置や、荷電ビーム源等が研究されている。

#### 【0025】

特に、画像形成装置への応用としては、例えば本願出願人による米国特許5,066,883号や特開平2-257551号公報や特開平4-28137号公報において開示されているように、表面伝導型放出素子と電子との衝突により発光する蛍光体とを組み合わせて用いた画像形成装置が研究されている。

#### 【0026】

表面伝導型放出素子と蛍光体とを組み合わせて用いた画像形成装置は、従来の他の方式の画像形成装置よりも優れた特性が期待されている。

30

#### 【0027】

例えば、近年普及してきた液晶表示装置と比較しても自発光型であるためバックライトを必要としない点や、視野角が広い点が優れているといえる。

#### 【0028】

また、FE型を多数個ならべて駆動する方法は、例えば本願出願人による米国特許4,904,895号に開示されている。

#### 【0029】

また、FE型を画像形成装置に応用した例として、例えば、R.Mayerらにより報告された平板型の表示装置が知られている[R.Mayer：“Recent Development on Microtips Display at LETI”, Tech.Digest of 4th Int.Vacuum Microelectronics Conf., Nagahama, pp.6～9(1991)]。

40

#### 【0030】

また、MIM型を多数個並べて画像形成装置に応用した例は、例えば本願出願人による特開平3-55738号公報に開示されている。

#### 【0031】

上記のような電子放出素子を用いた画像形成装置のうちで、奥行きの薄い平面型表示装置は省スペースかつ軽量であることから、ブラウン管型の表示装置に置き換わるものとして注目されている。

#### 【0032】

50

このような電子放出素子をマトリクス状に配設した電子源基板を気密容器内に収容した平面型の表示パネル部が提案されており、この気密容器の内部は10マイナス4乗[Pa]程度、もしくはそれ以上の真空に保持されている。

#### 【0033】

また、特開平5-6748号には、平板型陰極線管の軽量化を計るために収納容器の一部を金属とし、該金属部にアース電位を与える構成が開示されている。さらに、スクリーンガラスの内面に沿面放電を防止するために凹凸を形成して沿面距離を長くした構成や、二次電子放出防止膜を形成する構成が開示されている。

#### 【0034】

【発明が解決しようとする課題】10

図21は、表示パネルを、画像表示面の水平方向から見た模式図である。

#### 【0035】

上述のように、この気密容器の内部は10マイナス4乗[Pa]程度、もしくはそれ以上の真空に保持されなければならないため、真空度保持用の手段が必要となる。

#### 【0036】

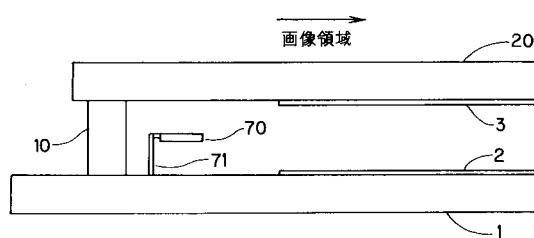

そこで従来は、図21に示すようにBa蒸発型のゲッター部材70をゲッター支持体71と共に画像領域外に配置し、真空容器を封じ切った後に高周波加熱等でBaを飛散させ、ゲッター膜を形成することで真空度を保持していた。

#### 【0037】

図中、1は電子源基板を兼ねるリアプレート、2は電子源領域、10は支持枠、20はフェースプレート、3は蛍光膜とメタルバックと呼ばれる金属膜（例えばAl）からなる画像形成部材である。20

#### 【0038】

一方、電子源から放出された電子を加速するために、電子源領域2と画像形成部材3との間には数百Vから数kV以上程度の高電圧(Va)が印加される。

#### 【0039】

画像形成装置の輝度は、このVa電圧に大きく依存し、更なる高輝度化を目的として、Va電圧を高くしていく必要があった。

#### 【0040】

ところが、高Va化するに従い、画像領域外である前述のゲッター部材70やゲッター支持体71の周辺の電界も上昇し、ゲッター部材70やゲッター支持体71のエッジ部、あるいはゲッター支持体71とリアプレート1との界面など、形状的に電界集中しやすい部位の放電が問題となってきた。30

#### 【0041】

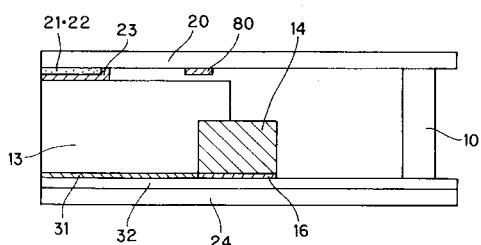

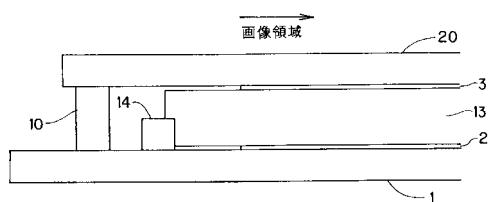

また大気圧支持を目的として、図22のように比較的薄いガラス板からなる構造支持体（スペーサ13）を、画像領域外に配設されたスペーサ固定部材14とともに、前述のリアプレート1とフェースプレート20との間に設ける場合がある。図22は、従来の電子線発生装置のスペーサ支持部の模式図である。

#### 【0042】

このスペーサ表面は高電界中にさらされるため、従来この沿面での放電が問題となっていた。40

#### 【0043】

この問題点を解決するために、スペーサに微小電流が流れるようにして帯電を除去する提案がなされている（特開昭57-118355号公報、特開昭61-124031号公報）。そこでは絶縁性のスペーサの表面に高抵抗薄膜を形成することによりスペーサ表面に微小電流が流れるようにして、表面での帯電を減らし、沿面耐圧の向上を図っている。

#### 【0044】

しかしながら、我々が検討した結果、この帯電防止膜を付与する方法をスペーサ固定部材にまで拡大しても、高圧印加条件によっては、スペーサ固定部材での放電は完全になくすまでには至らなかった。

**【0045】**

これは、板状のスペーサに対して、スペーサ固定部材の形状の複雑さに起因する電位分布の乱れ、形状効果（エッジ、突起）、スペーサとスペーサ固定部材接続部などにおける電界集中が原因と考えられる。

**【0046】**

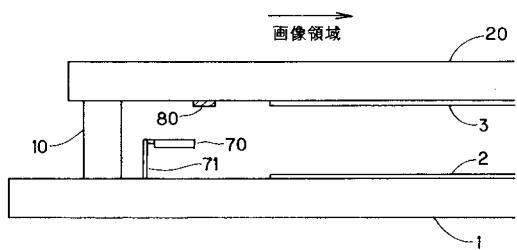

そこで、図23のように、画像領域外に構造物を有する場合、フェースプレート20に垂直な方向より見た正射影において、一部が構造物より画像領域12に近い場所になるようにフェースプレート20の内面上に低抵抗導体80を形成し、それをGND電位に規定する構造とすることにより、構造物での放電を防止した。図23は、従来の電子線発生装置のゲッター部分の模式図である。

10

**【0047】**

しかし、画像形成装置の小型化を目的として、カソード電位に規定された導電性部材と画像領域との距離を小さくしていくと、その間での沿面放電が問題となる場合もあった。

**【0048】**

さらには、画像領域の外側の辺において、前述のようなゲッター支持体、スペーサ支持体などの構造物が画像領域外に存在しない辺であっても、支持枠10と画像領域との距離を小さくしていった場合、支持枠10の内面部分の沿面放電が問題となることがあった。

**【0049】**

以上のような放電は、画像表示中に突発的に起こり、画像を乱すだけでなく、放電個所近傍の電子源を著しく劣化させ、その後の表示が正常にできなくなるという問題があった。

20

**【0050】**

本発明は望ましくない放電を抑制し、良好な表示画像を得る為の電子線発生装置及び画像形成装置を提供するものである。

**【0051】****【課題を解決するための手段】**

本願に係る電子線発生装置の発明の一つは以下のように構成される。電子線発生装置であって、電子放出素子を有する電子源基板と、該電子源基板と対向して配置される対向基板と、を有しており、該対向基板には、前記電子放出素子が放出する電子を加速する電位が与えられるアノード電位規定領域と、該アノード電位規定領域の周囲に該アノード電位規定領域と所定の間隔を空けて配置され所定の電位が与えられる導電性部材と、前記アノード電位規定領域及び前記導電性部材に接する抵抗膜と、前記アノード電位規定領域と前記導電性部材との間の沿面距離を増大させる沿面距離増大構造と、が設けられていることを特徴とする電子線発生装置。前記沿面距離増大構造は、前記アノード電位規定領域と前記導電性部材との間に位置し前記電子源基板に向かって凸である凸部であると好適である。前記沿面距離増大構造は、前記アノード電位規定領域と前記導電性部材との間に位置し前記電子源基板に向かって凹である凹部であってもよい。前記沿面距離増大構造は、前記アノード電位規定領域と前記導電性部材との間に位置する凹凸部であってもよい。

30

**【0052】**

ここで、前記凸部の高さが1μm以上であると特に好適である。

**【0053】**

また、前記沿面距離増大構造が前記アノード電位規定領域の少なくとも周囲3辺を取り囲むように配置される構成が特に好適である。

40

**【0054】**

また、前記電子源基板と前記対向基板との間にそれらの間隔を維持するスペーサを有しており、該スペーサの少なくとも一部もしくはスペーサを固定するための部材の少なくとも一方が前記アノード電位規定領域の領域外に存在し、前記沿面距離増大構造は、前記スペーサの少なくとも一部もしくはスペーサを固定するための部材が形成されている場所以外の場所に形成される構成が好適である。

**【0055】**

また以上述べた各発明において、前記抵抗膜はアノード電位規定領域と導電性部材の間

50

で微小電流を流すものであると良く、特にそのシート抵抗範囲が $1 \times 10^{-7}$  / 以上、 $1 \times 10^{-4}$  / 以下であると好適である。

**【0056】**

また本願に係る電子線発生装置の発明の一つは以下のように構成される。電子線発生装置であって、電子放出素子を有する電子源基板と、該電子源基板と対向して配置される対向基板と、を有しており、該対向基板の前記電子源基板に向いた同一平面上に、前記電子放出素子が放出する電子を加速する電位が与えられるアノード電位規定領域と、該アノード電位規定領域の周囲に該アノード電位規定領域と所定の間隔を空けて配置され所定の電位が与えられる導電性部材とを有しており、更に該同一平面上の前記アノード電位規定領域と前記導電性部材との間に、前記導電性部材から放出された電子によって発生する二次電子の多重散乱を抑制するための多重散乱抑制構造が配置されており、前記多重散乱抑制構造は、前記アノード電位規定領域と前記導電性部材との間に位置し前記電子源基板に向かって凸である凸部であることを特徴とする電子線発生装置。

10

**【0057】**

また本願に係る電子線発生装置の発明の一つは以下のように構成される。電子線発生装置であって、電子放出素子を有する電子源基板と、該電子源基板と対向して配置される対向基板と、を有しており、該対向基板の前記電子源基板に向いた同一平面上に、前記電子放出素子が放出する電子を加速する電位が与えられるアノード電位規定領域と、該アノード電位規定領域の周囲に該アノード電位規定領域と所定の間隔を空けて配置され所定の電位が与えられる導電性部材とを有しており、更に該同一平面上の前記アノード電位規定領域と前記導電性部材との間に、前記導電性部材から放出された電子によって発生する二次電子の多重散乱を抑制するための多重散乱抑制構造が配置されており、前記多重散乱抑制構造は、前記アノード電位規定領域と前記導電性部材との間に位置する凹凸部であることを特徴とする電子線発生装置。

20

**【0058】**

前記凸部の高さが $1 \mu m$ 以上であることが好適である。

**【0059】**

前記多重散乱抑制構造が前記アノード電位規定領域の少なくとも周囲3辺を取り囲むように配置されることが好適である。

30

**【0060】**

前記電子源基板と前記対向基板との間にそれらの間隔を維持するスペーサを有しており、該スペーサの少なくとも一部もしくはスペーサを固定するための部材の少なくとも一方が前記アノード電位規定領域の領域外に存在し、前記多重散乱抑制構造は、前記スペーサの少なくとも一部もしくはスペーサを固定するための部材が形成されている場所以外の場所に形成されることが好適である。

**【0062】**

以上述べた各発明において、前記導電性部材は、前記アノード電位規定領域を完全に取り囲むように配置される構成が特に好適である。

**【0064】**

また以上述べた各発明において、前記電子放出素子は、冷陰極素子である構成、前記電子放出素子は、電極間に電子放出部を含む導電性膜を有する電子放出素子である構成、前記電子放出素子は、表面伝導型電子放出素子である構成が特に好適である。

40

**【0065】**

また以上述べた各発明は、前記アノード電位規定領域と、前記電子放出素子を有するリアプレート側の電極との間の印加電圧が $3 kV$ 以上である構成において特に有効な発明である。

**【0066】**

また以上述べた各発明において、前記導電性部材には、前記アノード電位よりも低い電位が与えられるとよい。また以上述べた各発明は、前記導電性部材に与えられる電位がカソード電位になるような構成において特に好適に適用できる。また、以上述べた各発明にお

50

いて、前記導電性部材には、グランド電位を与える構成を好適に採用できる。

【0067】

また本願は、以上述べた各発明の構成の電子線発生装置に前記電子放出素子が放出する電子によって発光する蛍光体を設けたことを特徴とする画像形成装置の発明を含んでいる。

【0068】

【発明の実施の形態】

以下に図面を参照して、この発明の好適な実施の形態を例示的に詳しく説明する。ただし、この実施の形態に記載されている構成部品の寸法、材質、形状、その相対配置などは、特に特定的な記載がない限りは、この発明の範囲をそれらのみに限定する趣旨のものではない。

10

【0069】

また、以下の図面において、前述の従来技術の説明で用いた図面に記載された部材、及び既述の図面に記載された部材と同様の部材には同じ番号を付す。

【0070】

(電子線発生装置の実施形態)

本発明に係る電子線発生装置の一実施形態を適用した、画像形成装置の表示パネルの構成と製造方法について、具体的な例を示して説明する。

【0071】

まず、パネル全体の構成を説明し、次に、各実施形態で本発明の特徴部分について詳細に説明する。

20

【0072】

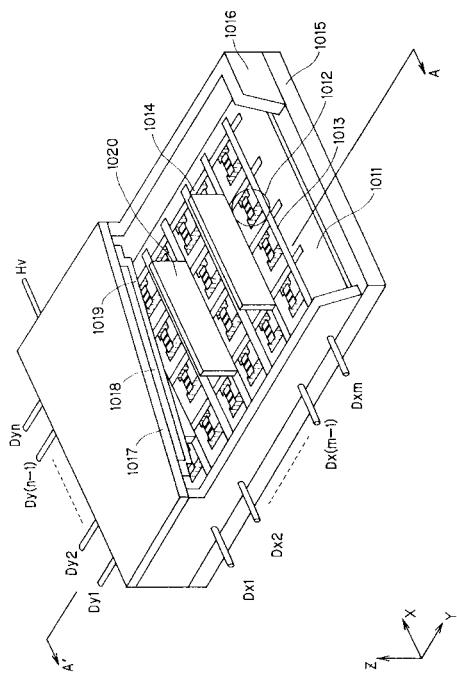

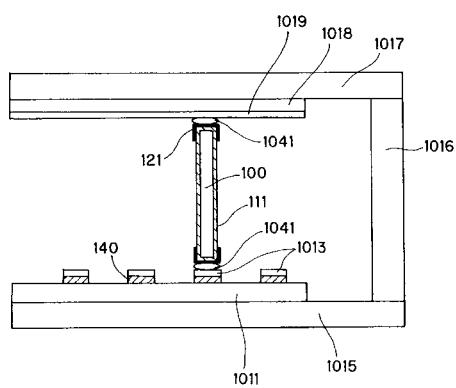

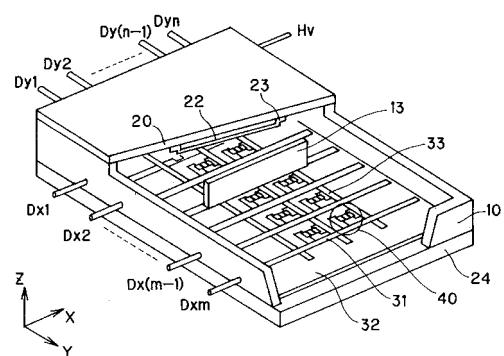

図1は、実施形態に用いた表示パネルの斜視図であり、内部構造を示すためにパネルの一部を切り欠いて示している。図1は、本発明に係る電子線発生装置の一実施形態の斜視断面図である。

【0073】

図中、1015はリアプレート、1016は側壁、1017はフェースプレートであり、1015～1017により表示パネルの内部を真空に維持するための気密容器を形成している。なお、図1ではアノード電位規定領域を囲む導電性部材や、多重散乱抑制のための凸構造等は省略している。

【0074】

30

電子源基板であるリアプレート1015および、対向基板であるフェースプレート1017は、いずれも絶縁性基板であり、青板ガラスや、表面にSiO<sub>2</sub>被膜を形成した青板ガラス、Naの含有量を少なくしたガラス、石英ガラス、あるいはセラミックスなど、条件に応じて各種材料を用いる。

【0075】

気密容器を組み立てるにあたっては、各部材の接合部に十分な強度と気密性を保持させるため封着する必要があるが、たとえばフリットガラスを接合部に塗布し、大気中あるいは窒素雰囲気中で、摂氏400～500度で10分以上焼成することにより封着を達成した。気密容器内部を真空に排気する方法については後述する。

【0076】

40

また、上記気密容器の内部は10のマイナス4乗[Pa]程度、もしくはそれ以上の真空に保持されるので、大気圧や不意の衝撃などによる気密容器の破壊を防止する目的で、耐大気圧構造体として、スペーサ1020が設けられている。

【0077】

次に、本発明の画像形成装置に用いることができる電子放出素子基板について説明する。

【0078】

本発明の画像形成装置に用いられる電子源基板は複数の冷陰極素子を基板上に配列することにより形成される。

【0079】

冷陰極素子の配列の方式には、冷陰極素子を並列に配置し、個々の素子の両端を配線で接

50

続するはしご型配置（以下、はしご型配置電子源基板と称する）や、冷陰極素子の一対の素子電極のそれぞれX方向配線、Y方向配線を接続した単純マトリクス配置（以下、マトリクス型配置電子源基板と称する）が挙げられる。

**【0080】**

なお、はしご型配置電子源基板を有する画像形成装置には、電子放出素子からの電子の飛翔を制御する電極である制御電極（グリッド電極）を必要とする。

**【0081】**

リアプレート1015には、基板1011が固定されているが、該基板上には冷陰極素子1012がN×M個形成されている（N、Mは2以上の正の整数であり、目的とする表示画素数に応じて適宜設定される。 10

**【0082】**

たとえば、高品位テレビジョンの表示を目的とした表示装置においては、N=3000、M=1000以上の数を設定することが望ましい。）。

**【0083】**

N×M個の冷陰極素子は、M本の行方向配線1013とN本の列方向配線1014により単純マトリクス配線されている。前記、1011～1014によって構成される部分をマルチ電子ビ-ム源と呼ぶ。

**【0084】**

本発明の画像形成装置に用いるマルチ電子ビ-ム源は、冷陰極素子を単純マトリクス配線もしくは、はしご型配置した電子源であれば、冷陰極素子の材料や形状あるいは製法に制限はない。 20

**【0085】**

したがって、たとえば表面伝導型放出素子やFE型、あるいはMIM型などの冷陰極素子を用いることができる。

**【0086】**

次に、冷陰極素子として表面伝導型放出素子（後述）を基板上に配列して単純マトリクス配線したマルチ電子ビ-ム源の構造について述べる。

**【0087】**

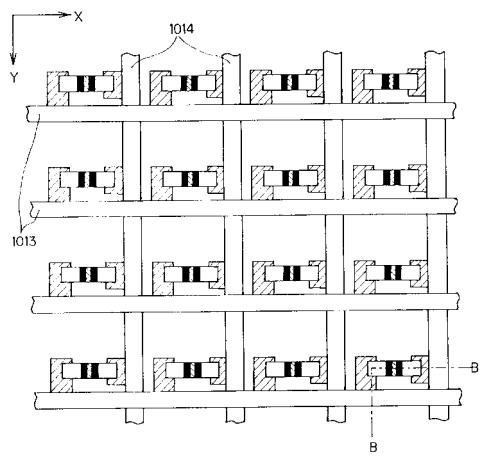

図2に示すのは、図1の表示パネルに用いたマルチ電子ビ-ム源の平面図である。

**【0088】**

基板1011上には、後述の図6で示すものと同様な表面伝導型放出素子が配列され、これらの素子は行方向配線1013と列方向配線1014により単純マトリクス状に配線されている。 30

**【0089】**

行方向配線1013と列方向配線1014の交差する部分には、電極間に絶縁層（不図示）が形成されており、電気的な絶縁が保たれている。

**【0090】**

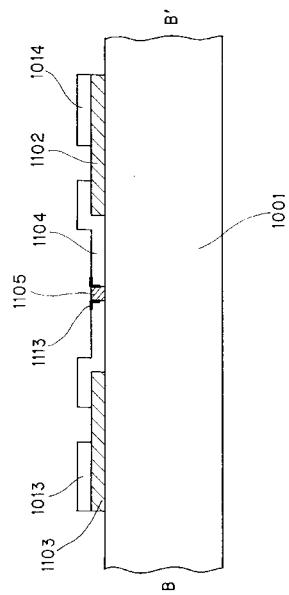

図2のB-B'に沿った断面を、図3に示す。なお、このような構造のマルチ電子源は、あらかじめ基板上に行方向配線1013、列方向配線1014、電極間絶縁層（不図示）、および表面伝導型放出素子の素子電極と導電性薄膜を形成した後、行方向配線1013および列方向配線1014を介して各素子に給電して通電フォーミング処理（後述）と通電活性化処理（後述）を行うことにより製造した。 40

**【0091】**

本実施形態においては、気密容器のリアプレート1015にマルチ電子ビ-ム源の基板1011を固定する構成としたが、マルチ電子ビ-ム源の基板1011が十分な強度を有するものである場合には、気密容器のリアプレートとしてマルチ電子ビ-ム源の基板1011自体を用いてよい。

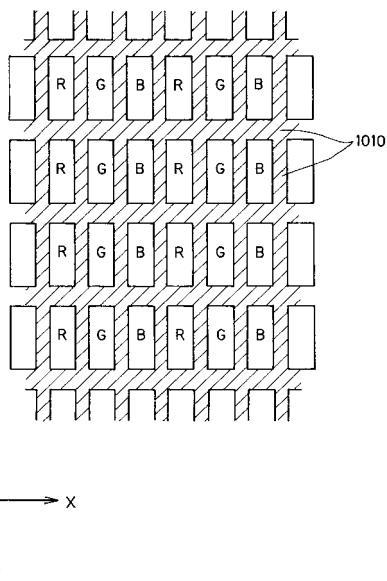

**【0092】**

また、フェースプレート1017の下面には、蛍光膜1018が形成されている。本実施形態はカラ-表示装置であるため、蛍光膜1018の部分にはCRTの分野で用いられる 50

赤、緑、青、の3原色の蛍光体が塗り分けられている。

【0093】

図4に示すように各色の蛍光体の間には黒色の導電体1010が設けてある。図4は、図1に示される電子線発生装置に用いられる表示パネルのフェースプレートの蛍光体配列を例示した平面図である。

【0094】

黒色の導電体1010を設ける目的は、電子ビームの照射位置に多少のずれがあつても表示色にずれが生じないようにする事や、外光の反射を防止して表示コントラストの低下を防ぐ事、電子ビームによる蛍光膜のチャージアップを防止する事などである。

【0095】

黒色の導電体1010には、黒鉛を主成分として用いたが、上記の目的に適するものであればこれ以外の材料を用いても良い。

【0096】

また、蛍光膜1018のリアプレート側の面には、CRTの分野では公知のメタルバック1019を設けてある。

【0097】

メタルバック1019を設けた目的は、蛍光膜1018が発する光の一部を鏡面反射して光利用率を向上させる事や、負イオンの衝突から蛍光膜1018を保護する事や、電子ビーム加速電圧を印加するための電極として作用させる事や、蛍光膜1018を励起した電子の導電路として作用させる事などである。

【0098】

メタルバック1019は、蛍光膜1018をフェースプレート1017上に形成した後、蛍光膜表面を平滑化処理し、その上にA1を真空蒸着する方法により形成した。このメタルバックにアノード電位が供給される。メタルバックが形成された領域がアノード電位規定領域となる。

【0099】

図5は図1のA-A'の断面模式図であり、各部の番号は図1に対応している。ここでもアノード電位規定領域を囲む導電性部材や凸部などは省略している。

【0100】

スペーサ1020は絶縁性部材100の表面に帯電防止を目的とした高抵抗膜111を成膜し、かつフェースプレート1017の内側（メタルバック1019等）及び基板1011の表面（行方向配線1013または列方向配線1014）に面したスペーサの当接面及び接する側面部に低抵抗膜121を成膜した部材からなるもので、上記目的を達成するのに必要な数だけ、かつ必要な間隔をおいて配置され、フェースプレートの内側および基板1011の表面に固定される。

【0101】

また、高抵抗膜は、絶縁性部材100の表面のうち、少なくとも気密容器内の真空中に露出している面に成膜されており、スペーサ1020上の低抵抗膜121を介して、フェースプレート1017の内側（メタルバック1019等）及び基板1011の表面（行方向配線1013または列方向配線1014）に電気的に接続される。

【0102】

ここで説明される態様においては、スペーサ1020の形状は薄板状とし、行方向配線1013に平行に配置され、行方向配線1013に電気的に接続されている。

【0103】

スペーサ1020としては、基板1011上の行方向配線1013および列方向配線1014とフェースプレート1017内面のメタルバック1019との間に印加される高電圧に耐えるだけの絶縁性を有し、かつスペーサ1020の表面への帯電を防止する程度の導電性を有する必要がある。

【0104】

スペーサ1020の絶縁性部材100としては、例えば石英ガラス、Na等の不純物含有

10

20

30

40

50

量を減少したガラス、ソーダライムガラス、アルミナ等のセラミックス部材等が挙げられる。

**【0105】**

なお、絶縁性部材100はその熱膨張率が気密容器および基板1011を成す部材と近いものが好ましい。

**【0106】**

スペーサ1020を構成する高抵抗膜111には、高電位側のフェースプレート1017(メタルバック1019等)に印加される加速電圧Vaを帯電防止膜である高抵抗膜111の抵抗値Rsで除した電流が流される。

**【0107】**

そこで、スペーサの抵抗値Rsは帯電防止および消費電力からその望ましい範囲に設定される。

**【0108】**

帯電防止の観点から表面抵抗R/は10の14乗以下であることが好ましい。

**【0109】**

十分な帯電防止効果を得るためにには10の11乗以下がさらに好ましい。表面抵抗の下限はスペーサ形状とスペーサ間に印加される電圧により左右されるが、10の7乗以上であることが好ましい。

**【0110】**

絶縁材料上に形成された帯電防止膜の厚みtは10nm~1μmの範囲が望ましい。

10

**【0111】**

材料の表面エネルギーおよび基板との密着性や基板温度によっても異なるが、一般的に10nm以下の薄膜は島状に形成され、抵抗が不安定で再現性に乏しい。

**【0112】**

スペーサは上述したようにその上に形成した帯電防止膜を電流が流れることにより、あるいはディスプレイ全体が動作中に発熱することによりその温度が上昇する。

**【0113】**

帯電防止膜の抵抗温度係数が大きな負の値であると温度が上昇した時に抵抗値が減少し、スペーサに流れる電流が増加し、さらに温度上昇をもたらす。

**【0114】**

20

そして電流は電源の限界を越えるまで増加しつづける。このような電流の暴走が発生する抵抗温度係数の値は経験的に負の値で絶対値が1%/以下である。

**【0115】**

すなわち、帯電防止膜の抵抗温度係数は負でありかつ-1%/より大であることが望ましい。

**【0116】**

帯電防止特性を有する高抵抗膜111の材料としては、例えば金属酸化物を用いることが出来る。

**【0117】**

金属酸化物の中でも、クロム、ニッケル、銅の酸化物が好ましい材料である。

40

**【0118】**

その理由はこれらの酸化物は二次電子放出効率が比較的小さく、冷陰極素子1012から放出された電子がスペーサ1020に当たった場合においても帯電しにくいためと考えられる。

**【0119】**

金属酸化物以外にも炭素は二次電子放出効率が小さく好ましい材料である。特に、非晶質カーボンは高抵抗であるため、スペーサ抵抗を所望の値に制御しやすい。

**【0120】**

帯電防止特性を有する高抵抗膜111の他の材料として、アルミと遷移金属合金の窒化物は遷移金属の組成を調整することにより、良伝導体から絶縁体まで広い範囲に抵抗値を制

50

御できるので好適な材料である。

**【0121】**

さらには後述する表示装置の作製工程において抵抗値の変化が少なく安定な材料である。

**【0122】**

かつ、その抵抗温度係数が - 1 % / より大であり、実用的に使いやすい材料である。

**【0123】**

遷移金属元素としては Ti, Cr, Ta、W 等があげられる。窒化膜はスパッタ、窒素ガス雰囲気中での反応性スパッタ、電子ビーム蒸着、イオンプレーティング、イオンアシスト蒸着法等の薄膜形成手段により絶縁性部材上に形成される。金属酸化膜も同様の薄膜形成法で作製することができるが、この場合窒素ガスに代えて酸素ガスを使用する。その他 10 CVD 法、アルコキシド塗布法でも金属酸化膜を形成できる。

**【0124】**

カーボン膜は蒸着法、スパッタ法、CVD 法、プラズマ CVD 法で作製され、特に非晶質カーボンを作製する場合には、成膜中の雰囲気に水素が含まれるようにするか、成膜ガスに炭化水素ガスを使用する。

**【0125】**

その他の高抵抗膜 111 の材料としては、炭素、珪素、ゲルマニウムを有した、窒化物、酸化物、炭化物、ホウ化物なども用いることが出来る。

**【0126】**

スペーサ 1020 を構成する低抵抗膜 121 は、高抵抗膜 111 を高電位側のフェースプレート 1017 (メタルバック 1019 等) 及び低電位側の基板 1011 (配線 1013、1014 等) と電気的に接続する為に設けられたものであり、以下では、スペーサ電極 121 という名称も用いる。スペーサ電極 121 は以下に列挙する複数の機能を有することが出来る。 20

**【0127】**

高抵抗膜 111 をフェースプレート 1017 及び基板 1011 と電気的に接続する。

**【0128】**

既に記載したように、高抵抗膜 111 はスペーサ 1020 表面での帯電を防止する目的で設けられたものであるが、高抵抗膜 111 をフェースプレート 1017 (メタルバック 1019 等) 及び基板 1011 (配線 1013、1014 等) と直接或いは当接材 1041 30 を介して接続した場合、接続部界面に大きな接触抵抗が発生し、スペーサ表面に発生した電荷を速やかに除去できなくなる可能性がある。

**【0129】**

これを避ける為に、フェースプレート 1017、基板 1011 及び当接材 1041 と接触するスペーサ 1020 の当接面或いは側面部に低抵抗のスペーサ電極 121 を設けた。

**【0130】**

高抵抗膜 111 の電位分布を均一化する。冷陰極素子 1012 より放出された電子は、フェースプレート 1017 と基板 1011 の間に形成された電位分布に従って電子軌道を成す。スペーサ 1020 の近傍で電子軌道に乱れが生じないようにする為には、高抵抗膜 111 の電位分布を全域にわたって制御する必要がある。 40

**【0131】**

高抵抗膜 111 をフェースプレート 1017 (メタルバック 1019 等) 及び基板 1011 (配線 1013、1014 等) と直接或いは当接材 1041 を介して接続した場合、接続部界面の接触抵抗の為に、接続状態のむらが発生し、高抵抗膜 111 の電位分布が所望の値からずれてしまう可能性がある。

**【0132】**

これを避ける為に、スペーサ 1020 がフェースプレート 1017 及び基板 1011 と当接するスペーサ端部 (当接面 3 或いは側面部 5) の全長域に低抵抗のスペーサ電極 121 を設け、このスペーサ電極 121 に所望の電位を印加することによって、高抵抗膜 111 全体の電位を制御可能とした。 50

## 【0133】

放出電子の軌道を制御する。冷陰極素子1012より放出された電子は、フェースプレート1017と基板1011の間に形成された電位分布に従って電子軌道を成す。

## 【0134】

スペーサ近傍の冷陰極素子から放出された電子に関しては、スペーサを設置することに伴う制約（配線、素子位置の変更等）が生じる場合がある。

## 【0135】

このような場合、歪みやむらの無い画像を形成する為には、放出された電子の軌道を制御してフェースプレート1017上の所望の位置に電子を照射する必要がある。

## 【0136】

フェースプレート1017及び基板1011と当接する面の側面部に低抵抗のスペーサ電極121を設けることにより、スペーサ1020近傍の電位分布に所望の特性を持たせ、放出された電子の軌道を制御することが出来る。

## 【0137】

低抵抗膜121は、高抵抗膜111に比べ十分に低いシート抵抗値（少なくとも一桁以上）を有する材料を選択すればよく、Ni, Cr, Au, Mo, W, Pt, Ti, Al, Cu, Pd等の金属、あるいは合金、及びPd, Ag, Au, RuO<sub>2</sub>, Pd-Ag等の金属や金属酸化物とガラス等から構成される印刷導体、あるいはIn<sub>2</sub>O<sub>3</sub>-SnO<sub>2</sub>等の透明導体及びポリシリコン等の半導体材料等より適宜選択される。

## 【0138】

また、Dx1～DxmおよびDy1～DynおよびHvは、当該表示パネルと不図示の気回路とを電気的に接続するために設けた気密構造の電気接続用端子である。

## 【0139】

Dx1～Dxmはマルチ電子ビーム源の行方向配線1013と、Dy1～Dynはマルチ電子ビーム源の列方向配線1014と、Hvはフェースプレートのメタルバック1019と電気的に接続している。

## 【0140】

また、気密容器内部を真空中に排氣するには、気密容器を組み立てた後、不図示の排氣管と真空ポンプとを接続し、気密容器内を10マイナス5乗[Pa]程度の真空中度まで排氣する。

## 【0141】

その後、排氣管を封止するが、気密容器内の真空中度を維持するために、封止の直前あるいは封止後に気密容器内の所定の位置にゲッター膜（不図示）を形成する。

## 【0142】

ゲッター膜とは、たとえばBaを主成分とするゲッター材料をヒーターもしくは高周波加熱により加熱し蒸着して形成した膜であり、該ゲッター膜の吸着作用により気密容器内は1×10マイナス5乗[Pa]ないしは1×10マイナス7乗[Pa]、もしくはそれ以上の真空中度に維持される。

## 【0143】

以上説明した表示パネルを用いた画像形成装置は、容器外端子Dx1ないしDxm、Dy1ないしDynを通じて各冷陰極素子1012に電圧を印加すると、各冷陰極素子1012から電子が放出される。

## 【0144】

それと同時にメタルバック1019に容器外端子Hvを通じて3[kV]を超える高電位を印加する。冷陰極素子に印加される電位はいずれもグランド電位近傍なので、電子放出素子とメタルバックの間には3[kV]以上の電圧が印加され、上記放出された電子を加速し、フェースプレート1017の内面に衝突させる。

## 【0145】

これにより、蛍光膜1018をなす各色の蛍光体が励起されて発光し、画像が表示される。

10

20

30

40

50

**【 0 1 4 6 】**

通常、冷陰極素子である本発明の表面伝導型放出素子への 1 0 1 2 への印加電圧は 1 2 ~ 1 6 [ V ] 程度、メタルバック 1 0 1 9 と冷陰極素子 1 0 1 2 との距離 d は 0 . 1 [ mm ] から 8 [ mm ] 程度、メタルバック 1 0 1 9 と冷陰極素子 1 0 1 2 間の電圧は 3 [ kV ] から 1 0 [ kV ] 程度である。

**【 0 1 4 7 】**

以上、本発明の実施形態の表示パネルの基本構成と製法、および画像形成装置の概要を説明した。

**【 0 1 4 8 】**

次に、前記実施形態の表示パネルに用いたマルチ電子ビ - ム源の製造方法について説明する。 10

**【 0 1 4 9 】**

本発明の画像形成装置に用いるマルチ電子ビ - ム源は、冷陰極素子を単純マトリクス配線した電子源であれば、冷陰極素子の材料や形状あるいは製法に制限はない。

**【 0 1 5 0 】**

したがって、たとえば表面伝導型放出素子や F E 型、あるいは M I M 型などの冷陰極素子を用いることができる。

**【 0 1 5 1 】**

ただし、表示画面が大きくてしかも安価な表示装置が求められる状況のもとでは、これらの冷陰極素子の中でも、表面伝導型放出素子が特に好ましい。 20

**【 0 1 5 2 】**

表面伝導型放出素子は、比較的製造方法が単純なため、大面積化や製造コストの低減が容易である。

**【 0 1 5 3 】**

また、発明者らは、表面伝導型放出素子の中でも、電子放出部もしくはその周辺部を微粒子膜から形成したものがとりわけ電子放出特性に優れ、しかも製造が容易に行えることを見いだしている。

**【 0 1 5 4 】**

したがって、高輝度で大画面の画像形成装置のマルチ電子ビ - ム源に用いるには、最も好適であると言える。 30

**【 0 1 5 5 】**

そこで、上記実施形態の表示パネルにおいては、電子放出部もしくはその周辺部を微粒子膜から形成した表面伝導型放出素子を用いた。そこで、まず好適な表面伝導型放出素子について基本的な構成と製法および特性を説明し、その後で多数の素子を単純マトリクス配線したマルチ電子ビ - ム源の構造について述べる。

**【 0 1 5 6 】****( 表面伝導型放出素子の好適な素子構成と製法 )**

電子放出部もしくはその周辺部を微粒子膜から形成する表面伝導型放出素子の代表的な構成には、平面型と垂直型の 2 種類があげられる。ここでは実際、作製に用いた平面型の説明を行なう。 40

**【 0 1 5 7 】****( 平面型の表面伝導型放出素子 )**

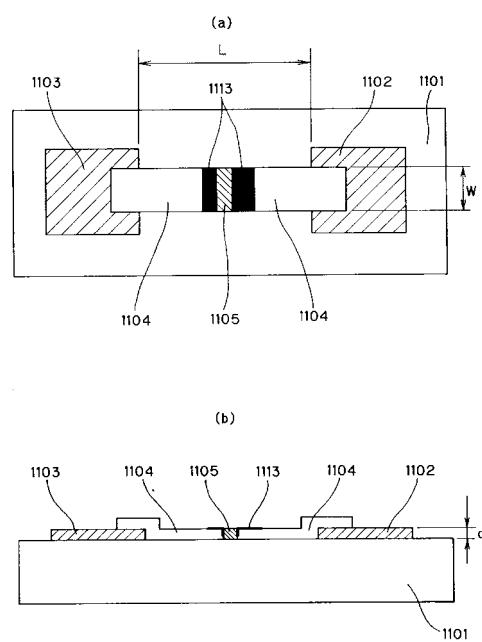

平面型の表面伝導型放出素子の素子構成と製法について説明する。図 6 に示すのは、図 1 に示される電子線発生装置に用いられる、平面型の表面伝導型放出素子の構成を説明するための平面図 ( a ) および断面図 ( b ) である。

**【 0 1 5 8 】**

図中、 1 1 0 1 は基板、 1 1 0 2 と 1 1 0 3 は素子電極、 1 1 0 4 は導電性薄膜、 1 1 0 5 は通電フォーミング処理により形成した電子放出部、 1 1 1 3 は通電活性化処理により形成した薄膜である。

**【 0 1 5 9 】**

基板 1101 としては、たとえば、石英ガラスや青板ガラスをはじめとする各種ガラス基板や、アルミナをはじめとする各種セラミクス基板、あるいは上述の各種基板上にたとえば  $\text{SiO}_2$  を材料とする絶縁層を積層した基板、などを用いることができる。

#### 【0160】

また、基板 1101 上に基板面と平行に対向して設けられた素子電極 1102 と 1103 は、導電性を有する材料によって形成されている。

#### 【0161】

たとえば、Ni, Cr, Au, Mo, W, Pt, Ti, Cu, Pd, Ag 等をはじめとする金属、あるいはこれらの金属の合金、あるいは  $\text{In}_2\text{O}_3$  -  $\text{SnO}_2$  をはじめとする金属酸化物、ポリシリコンなどの半導体、などの中から適宜材料を選択して用いればよい。 10

#### 【0162】

電極を形成するには、たとえば真空蒸着などの製膜技術とフォトリソグラフィー、エッチングなどのパターニング技術を組み合わせて用いれば容易に形成できるが、それ以外の方法（たとえば印刷技術）を用いて形成してもさしつかえない。

#### 【0163】

素子電極 1102 と 1103 の形状は、当該電子放出素子の応用目的に合わせて適宜設計される。

#### 【0164】

一般的には、電極間隔 L は通常は数百 μm の範囲から適当な数値を選んで設計されるが、なかでも表示装置に応用するために好ましいのは数 μm より数十 μm の範囲である。 20

#### 【0165】

また、素子電極の厚さ d については、通常は数百 μm の範囲から適当な数値が選ばれる。

#### 【0166】

また、導電性薄膜 1104 の部分には、微粒子膜を用いる。ここで述べた微粒子膜とは、構成要素として多数の微粒子を含んだ膜（島状の集合体も含む）のことをさす。

#### 【0167】

微粒子膜を微視的に調べれば、通常は、個々の微粒子が離間して配置された構造か、あるいは微粒子が互いに隣接した構造か、あるいは微粒子が互いに重なり合った構造が観測される。 30

#### 【0168】

微粒子膜に用いた微粒子の粒径は、数 μm の範囲に含まれるものであるが、なかでも好ましいのは 10 μm から 200 μm の範囲のものである。

#### 【0169】

また、微粒子膜の膜厚は、以下に述べるような諸条件を考慮して適宜設定される。すなわち、素子電極 1102 あるいは 1103 と電気的に良好に接続するのに必要な条件、後述する通電フォーミングを良好に行うのに必要な条件、微粒子膜自身の電気抵抗を後述する適宜の値にするために必要な条件、などである。具体的には、数 μm から数千 μm の範囲のなかで設定するが、なかでも好ましいのは 10 μm から 500 μm の間である。 40

#### 【0170】

また、微粒子膜を形成するのに用いられる材料としては、たとえば、Pd, Pt, Ru, Ag, Au, Ti, In, Cu, Cr, Fe, Zn, Sn, Ta, W, Pb, などをはじめとする金属や、PdO, SnO<sub>2</sub>, In<sub>2</sub>O<sub>3</sub>, PbO, Sb<sub>2</sub>O<sub>3</sub>, などをはじめとする酸化物や、HfB<sub>2</sub>, ZrB<sub>2</sub>, LaB<sub>6</sub>, CeB<sub>6</sub>, YB<sub>4</sub>, GdB<sub>4</sub>, などをはじめとする硼化物や、TiC, ZrC, HfC, TaC, SiC, WC, などをはじめとする炭化物や、TiN, ZrN, HfN, などをはじめとする窒化物や、Si, Ge, などをはじめとする半導体や、カーボン、などがあげられ、これらの中から適宜選択される。

#### 【0171】

以上述べたように、導電性薄膜 1104 を微粒子膜で形成したが、そのシート抵抗値につ 50

いては、10の3乗から10の7乗 [ / sq ] の範囲に含まれるよう設定した。

**【0172】**

なお、導電性薄膜1104と素子電極1102および1103とは、電気的に良好に接続されるのが望ましいため、互いの一部が重なりあうような構造をとっている。

**【0173】**

その重なり方は、図6の例においては、下から、基板、素子電極、導電性薄膜の順序で積層したが、場合によっては下から基板、導電性薄膜、素子電極、の順序で積層してもさしつかえない。

**【0174】**

また、電子放出部1105は、導電性薄膜1104の一部に形成された亀裂状の部分であり、電気的には周囲の導電性薄膜よりも高抵抗な性質を有している。亀裂は、導電性薄膜1104に対して、後述する通電フォーミングの処理を行うことにより形成する。10

**【0175】**

亀裂内には、数から数百の粒径の微粒子を配置する場合がある。なお、実際の電子放出部の位置や形状を精密かつ正確に図示するのは困難なため、図6においては模式的に示した。

**【0176】**

また、薄膜1113は、炭素もしくは炭素化合物よりなる薄膜で、電子放出部1105およびその近傍を被覆している。薄膜1113は、通電フォーミング処理後に、後述する通電活性化の処理を行うことにより形成する。20

**【0177】**

薄膜1113は、単結晶グラファイト、多結晶グラファイト、非晶質カーボン、のいずれかか、もしくはその混合物であり、膜厚は500 [ ] 以下とするが、300 [ ] 以下とするのがさらに好ましい。

**【0178】**

なお、実際の薄膜1113の位置や形状を精密に図示するのは困難なため、図6においては模式的に示した。また、平面図(a)においては、薄膜1113の一部を除去した素子を図示した。

**【0179】**

以上、好ましい素子の基本構成を述べたが、実施形態においては以下のようないました。30

**【0180】**

すなわち、基板1101には青板ガラスを用い、素子電極1102と1103にはNi薄膜を用いた。素子電極の厚さdは1000 [ ]、電極間隔Lは2 [ μm ]とした。微粒子膜の主要材料としてPdもしくはPdOを用い、微粒子膜の厚さは約100 [ ]、幅Wは100 [ μm ]とした。

**【0181】**

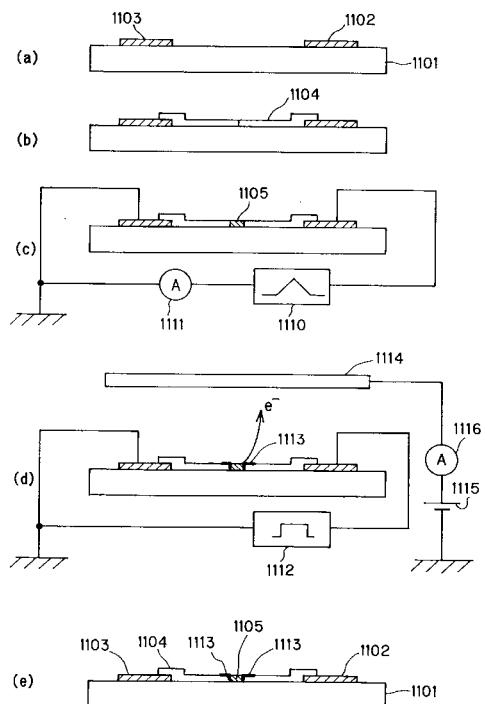

次に、好適な平面型の表面伝導型放出素子の製造方法について説明する。図7の(a)~(e)は、図1に示される電子線発生装置に用いられる表面伝導型放出素子の製造工程を説明するための断面図で、各部材の表記は前記図6と同一である。40

**【0182】**

1) まず、図7(a)に示すように、基板1101上に素子電極1102および1103を形成する。

**【0183】**

形成するにあたっては、あらかじめ基板1101を洗剤、純水、有機溶剤を用いて十分に洗浄後、素子電極の材料を堆積させる(堆積する方法としては、たとえば、蒸着法やスパッタ法などの真空成膜技術を用ればよい。)。

**【0184】**

その後、堆積した電極材料を、フォトリソグラフィー・エッチング技術を用いてパターニングし、(a)に示した一対の素子電極(1102と1103)を形成する。50

## 【0185】

2) 次に、同図(b)に示すように、導電性薄膜1104を形成する。形成するにあたっては、まず前記(a)の基板に有機金属溶液を塗布して乾燥し、加熱焼成処理して微粒子膜を成膜した後、フォトリソグラフィー・エッチングにより所定の形状にパターニングする。

## 【0186】

ここで、有機金属溶液とは、導電性薄膜に用いる微粒子の材料を主要元素とする有機金属化合物の溶液である(具体的には、本実施形態では主要元素としてPdを用いた。また、実施形態では塗布方法として、ディップィング法を用いたが、それ以外のたとえばスピナーフラッシュ法やスプレー法を用いてもよい。)。

10

## 【0187】

また、微粒子膜で作られる導電性薄膜の成膜方法としては、本実施形態で用いた有機金属溶液の塗布による方法以外の、たとえば真空蒸着法やスパッタ法、あるいは化学的気相堆積法などを用いる場合もある。

## 【0188】

3) 次に、同図(c)に示すように、フォーミング用電源1110から素子電極1102と1103の間に適宜の電圧を印加し、通電フォーミング処理を行って、電子放出部1105を形成する。

## 【0189】

通電フォーミング処理とは、微粒子膜で作られた導電性薄膜1104に通電を行って、その一部を適宜に破壊、変形、もしくは変質せしめ、電子放出を行うのに好適な構造に変化させる処理のことである。

20

## 【0190】

微粒子膜で作られた導電性薄膜のうち電子放出を行うのに好適な構造に変化した部分(すなわち電子放出部1105)においては、薄膜に適当な亀裂が形成されている。

## 【0191】

なお、電子放出部1105が形成される前と比較すると、形成された後は素子電極1102と1103の間で計測される電気抵抗は大幅に増加する。

## 【0192】

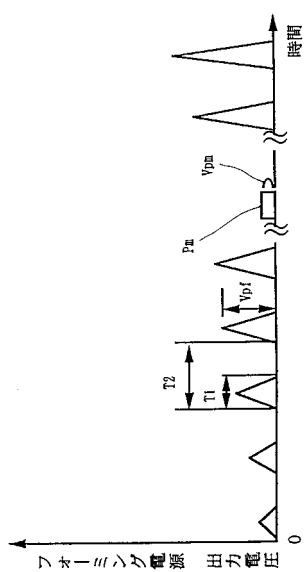

通電方法をより詳しく説明するために、図8に、図1に示される電子線発生装置に適用されるフォーミング用電源1110から印加する適宜の電圧波形の一例を示す。

30

## 【0193】

微粒子膜で作られた導電性薄膜をフォーミングする場合には、パルス状の電圧が好ましく、本実施形態の場合には同図に示したようにパルス幅T1の三角波パルスをパルス間隔T2で連続的に印加した。その際には、三角波パルスの波高値Vpfを、順次昇圧した。

## 【0194】

また、電子放出部1105の形成状況をモニターするためのモニターパルスPmを適宜の間隔で三角波パルスの間に挿入し、その際に流れる電流を電流計1111で計測した。

## 【0195】

実施形態においては、たとえば10のマイナス3乗[Pa]程度の真空雰囲気下において、たとえばパルス幅T1を1[msec]、パルス間隔T2を10[msec]とし、波高値Vpfを1パルスごとに0.1[V]ずつ昇圧した。

40

## 【0196】

そして、三角波を5パルス印加するたびに1回の割りで、モニターパルスPmを挿入した。

## 【0197】

フォーミング処理に悪影響を及ぼすことがないように、モニターパルスの電圧Vpmは0.1[V]に設定した。

## 【0198】

そして、素子電極1102と1103の間の電気抵抗が $1 \times 10$ の6乗[ ]になった段

50

階、すなわちモニターパルス印加時に電流計 1111 で計測される電流が  $1 \times 10$  のマイナス 7 乗 [ A ] 以下になった段階で、フォーミング処理にかかる通電を終了した。

#### 【 0199 】

なお、上記の方法は、本実施形態の表面伝導型放出素子に関する好ましい方法であり、たとえば微粒子膜の材料や膜厚、あるいは素子電極間隔  $L$  など表面伝導型放出素子の設計を変更した場合には、それに応じて通電の条件を適宜変更するのが望ましい。

#### 【 0200 】

4) 次に、図 7 の ( d ) に示すように、活性化用電源 1112 から素子電極 1102 と 1103 の間に適宜の電圧を印加し、通電活性化処理を行って、電子放出特性の改善を行う。

10

#### 【 0201 】

通電活性化処理とは、前記通電フォーミング処理により形成された電子放出部 1105 に適宜の条件で通電を行って、その近傍に炭素もしくは炭素化合物を堆積せしめる処理のことである(図においては、炭素もしくは炭素化合物よりなる堆積物を部材 1113 として模式的に示した。)。

#### 【 0202 】

なお、通電活性化処理を行うことにより、行う前と比較して、同じ印加電圧における放出電流を典型的には 100 倍以上に増加させることができる。

#### 【 0203 】

具体的には、10 のマイナス 4 乗ないし 10 のマイナス 3 乗 [ Pa ] の範囲内の真空雰囲気中で、電圧パルスを定期的に印加することにより、真空雰囲気中に存在する有機化合物を起源とする炭素もしくは炭素化合物を堆積させる。

20

#### 【 0204 】

堆積物 1113 は、単結晶グラファイト、多結晶グラファイト、非晶質カーボン、のいずれか、もしくはその混合物であり、膜厚は 500 [ ] 以下、より好ましくは 300 [ ] 以下である。

#### 【 0205 】

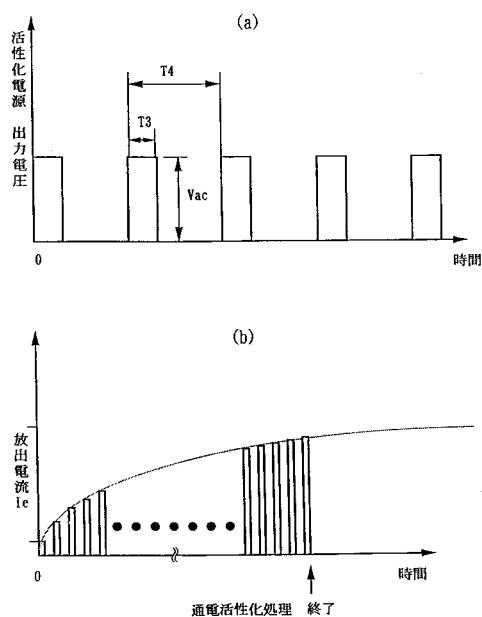

通電方法をより詳しく説明するために、図 9 の ( a ) に、図 1 に示される電子線発生装置に適用される活性化用電源 1112 から印加する適宜の電圧波形の一例を示す。

#### 【 0206 】

30

本実施形態においては、一定電圧の矩形波を定期的に印加して通電活性化処理を行ったが、具体的には、矩形波の電圧  $V_{ac}$  は 14 [ V ] , パルス幅  $T_3$  は 1 [ msec ] , パルス間隔  $T_4$  は 10 [ msec ] とした。

#### 【 0207 】

なお、上述の通電条件は、本実施形態の表面伝導型放出素子に関する好ましい条件であり、表面伝導型放出素子の設計を変更した場合には、それに応じて条件を適宜変更するのが望ましい。

#### 【 0208 】

図 7 の ( d ) に示す 1114 は該表面伝導型放出素子から放出される放出電流  $I_e$  を捕捉するためのアノード電極で、直流高電圧電源 1115 および電流計 1116 が接続されている(なお、基板 1101 を、表示パネルの中に組み込んでから活性化処理を行う場合には、表示パネルの蛍光面をアノード電極 1114 として用いる。)。

40

#### 【 0209 】

活性化用電源 1112 から電圧を印加する間、電流計 1116 で放出電流  $I_e$  を計測して通電活性化処理の進行状況をモニターし、活性化用電源 1112 の動作を制御する。

#### 【 0210 】

電流計 1116 で計測された放出電流  $I_e$  の一例を図 9 ( b ) に示すが、活性化電源 1112 からパルス電圧を印加しはじめると、時間の経過とともに放出電流  $I_e$  は増加するが、やがて飽和してほとんど増加しなくなる。

#### 【 0211 】

50

このように、放出電流  $I_e$  がほぼ飽和した時点で活性化用電源 1112 からの電圧印加を停止し、通電活性化処理を終了する。

【0212】

なお、上述の通電条件は、本実施形態の表面伝導型放出素子に関する好ましい条件であり、表面伝導型放出素子の設計を変更した場合には、それに応じて条件を適宜変更するのが望ましい。

【0213】

以上のようにして、図7(e)に示す平面型の表面伝導型放出素子を製造した。

【0214】

【実施例】

10

以下、本発明の具体的な実施例について図面を用いて説明する。

【0215】

(実施例1)

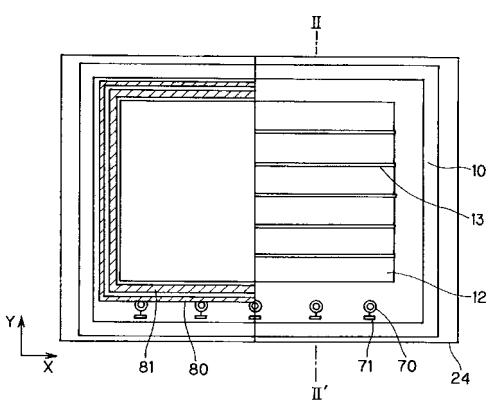

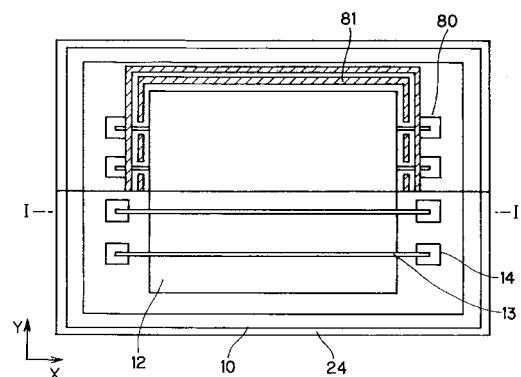

本発明の実施例1について説明する。図10は、本発明に係る電子線発生装置の実施例1を示すパネルの模式的平面図で、フェースプレート上方から見た場合の構成を示す。

【0216】

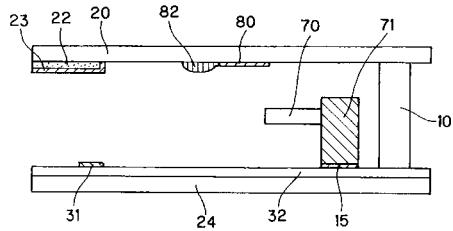

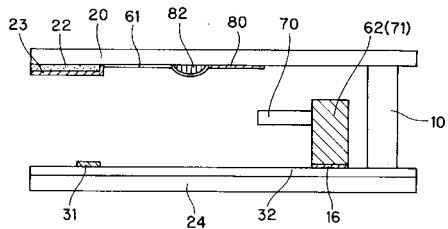

図10は、便宜上フェースプレートの右半面を取り除いた図となっている。図11は図10中符号II-II'のゲッター支持体近傍断面図である。図12は、実施例1の電子線発生装置の一部を破断した斜視図である。

【0217】

20

図10、図11、図12においてリアプレート24にはマトリクス状に複数配列された表面伝導型電子放出素子40が設けられた基板32が固定されている。

【0218】

表面伝導型電子放出素子40は行方向配線31と列方向配線33により結線されている。

【0219】

フェースプレート20とリアプレート24は支持枠10を用いて気密接合され、気密容器を形成している。

【0220】

フェースプレート20にはブラックマトリクス(不図示)、蛍光体22、メタルバック23、およびメタルバック23の電位を規定するための電極(不図示)等が設けられる。

30

【0221】

メタルバック23が設けられた領域であるアノード電位規定領域とアノード電位規定領域を対向するリアプレート24側に正射影した領域との間の領域を画像領域12とする。

【0222】

フェースプレート20とリアプレート24の間には大気圧支持部材としてスペーサ13が行方向配線31上に挿入されている。スペーサ13には表面に各種成膜がされていてよい。

【0223】

本実施例では、スペーサ13に帯電防止を目的とした高抵抗膜を成膜し、かつメタルバック23及び行方向配線31に面したスペーサの当接面及び接する側面部に電気的接続を良好にするための低抵抗膜を成膜してある。

40

【0224】

図10、図12に示されるように、スペーサ13は画像領域12の内に配置されており、接着剤により行方向配線31上に固定されている。固定する場所はブラックマトリクス上であってもよい。

【0225】

図10、図11において、画像領域12の外側の一部には、ゲッター部材70とそれを支持するためのゲッター支持体71が形成されている。

【0226】

ゲッター支持体71は接着剤15により、リアプレート24に固定されている。

50

**【 0 2 2 7 】**

なお、ゲッター支持体 7 1 はフェースプレート 2 0 に固定してもよい。フェースプレート 2 0 内面のメタルバック形成領域であるアノード電位規定領域の外側には、ゲッター部材 7 0 およびゲッター支持体 7 1 の放電を抑制するために、アノード電位規定領域の周りを取り囲むように、本発明の構成要素たる導電性部材としての低抵抗導体 8 0 が形成されている。

**【 0 2 2 8 】**

低抵抗導体 8 0 の一部は、フェースプレート 2 0 に垂直な方向より見た正射影において、ゲッター部材 7 0 およびゲッター支持体 7 1 よりアノード電位規定領域に近い場所に位置する。

10

**【 0 2 2 9 】**

低抵抗導体 8 0 は接続端子（不図示）により GND 接続されている。また、GND 接続配線をフェースプレート 2 0 側に取り出すような構成であってもよい。

**【 0 2 3 0 】**

そして、画像領域 1 2 と、低抵抗導体 8 0 の間（図 1 0 の 8 1 が示す領域）には、真空容器の内側に対して凸形状となる構造体 8 2（以下、凸型構造体 8 2 と記す）が形成されている。

**【 0 2 3 1 】**

以下、本実施例の特徴部分である凸型構造体 8 2、およびそれに深く関係する部分について説明する。

20

**【 0 2 3 2 】**

本実施例では図 1 1 に示すように、アノードとなるメタルバック 2 3 と、カソードとなる低抵抗導体 8 0 の間には、カソードに接続するように凸型構造体 8 2 が形成されている。なお、メタルバックよりカソードに近い場所にアノード電位となる部材が存在する構造の場合、そのアノード電位となる部材と低抵抗導体の間に凸型構造体を設ける。

**【 0 2 3 3 】**

ここで、凸型構造体 8 2 を設けることによる、メタルバック 2 3 と低抵抗導体 8 0 間の放電抑制の要因を説明する。

**【 0 2 3 4 】**

一つ目に、沿面距離を長くすることにより、沿面耐圧が上がるということがあげられる。

30

ここで、沿面距離とは、表面に沿って測った距離のことである。

**【 0 2 3 5 】**

これによって、画像形成装置を小型化するために、メタルバック 2 3 と低抵抗導体 8 0 の間の実質的な距離を短くすることができる。

**【 0 2 3 6 】**

二つ目には、低抵抗導体 8 0 からの電界放出電子の再入射時の入射エネルギーを抑制することによる、二次電子放出確率の抑制ということがあげられる。

40

**【 0 2 3 7 】**

画像形成装置の表示輝度を高くするために、電子加速電圧 V<sub>a</sub> の高電圧化が必要となると、低抵抗導体 8 0 からの電界放出電子による放電が問題となってくる。

**【 0 2 3 8 】**

そこで、電界放出電子が電界により加速され、エネルギーが増加し、再入射時の二次電子放出係数が大きく増大する前に凸型構造体 8 2 に放出電子を衝突させることで、再放出時の二次電子の放出数を減少させ、多重散乱二次電子の発生を防いだ。

**【 0 2 3 9 】**

凸型構造体 8 2 の位置は、放出電子のエネルギーが低い低抵抗導体 8 0 近傍にあることが望ましい。

**【 0 2 4 0 】**

さらに、凸型構造体 8 2 の高さは、放出電子が凸型構造体 8 2 に衝突せずに飛び越す確率が低くなるために、放出二次電子の再放出最大高さ（FP からの距離）と同程度か、もし

50

くは高い凸部の高さを有することが望ましい。なお、凸型構造体 8 2 の高さは構成によって適切な値は異なる。

#### 【 0 2 4 1 】

本実施例では、低抵抗導体 8 0 の高さを 0 . 1  $\mu\text{m}$ 、凸型構造体 8 2 の高さを 1  $\mu\text{m}$ とした。この凸型構造体 8 2 の高さ 1  $\mu\text{m}$ 以上が好ましい。特に本実施例ではアノード電位規定領域を構成するメタルバックとそれを囲む導電性部材とが同一平面上に形成されており、凸構造が無いと導電性部材からメタルバックが見通せる構造となっている。この構造においては凸部を同一平面上に設けることによって好ましくない放電を好適に抑制することができる。

#### 【 0 2 4 2 】

低抵抗導体 8 0 は Pt と Ti を用いて、スパッタ法により形成した。凸型構造体 8 2 はポリベンゾイミダゾール (PBI) を、スプレー法により塗布し、300 の熱処理を行い形成した。

#### 【 0 2 4 3 】

低抵抗導体 8 0 は、抵抗が十分に低い材料を選択すればよく、Ni, Cr, Au, Mo, W, Pt, Ti, Al, Cu, Pd 等の金属、あるいはこれらの合金等より適宜選択される。

#### 【 0 2 4 4 】

低抵抗導体 8 0 を形成する方法としては、スパッタ、電子ビーム蒸着、イオンプレーティング、イオンアシスト蒸着法等を用いることが出来る。

#### 【 0 2 4 5 】

凸型構造体 8 2 の材質としては、PBI 以外にも様々な材料を用いる事ができるが、高い絶縁性を有するものの、かつ、表示パネルを作製する際の熱工程でその熱に耐え得るだけの耐熱性を有することが必要である。

#### 【 0 2 4 6 】

##### ( 実施例 2 )

また、前述の実施例 1 の変形例である実施例 2 として、図 13 に示すように、メタルバック 2 3 と低抵抗導体 8 0 の間に高抵抗膜 6 1 を形成しても良い。図 13 は、本発明に係る電子線発生装置の実施例 2 における、図 10 中の符号 II - II' のゲッター支持体近傍断面図である。

#### 【 0 2 4 7 】

低抵抗導体 8 0 から放出された電子、あるいは放出電子の作用でイオン化したイオンにより引き起こされる帯電を、高抵抗膜 6 1 で微小電流が流れることにより防止することができる。

#### 【 0 2 4 8 】

以上の説明より、実施例 1 及び実施例 2 では、メタルバック 2 3 と低抵抗導体 8 0 のギャップにおいて、図 11 のような構成にすることにより、沿面距離を長くとること、および、低抵抗導体 8 0 からの放出電子を抑制することで、放電を押さえると考えられる。

#### 【 0 2 4 9 】

メタルバック 2 3 と低抵抗導体 8 0 のギャップを 2 mm として電子加速電圧を印加したところ、14 kV の放電耐圧を確認した。

#### 【 0 2 5 0 】

以上のようにして製造された電子線発生装置を用いた画像形成装置は、輝度の高く、かつ放電の無い、表示品位の良好な画像を表示することができた。

#### 【 0 2 5 1 】

##### ( 実施例 3 )

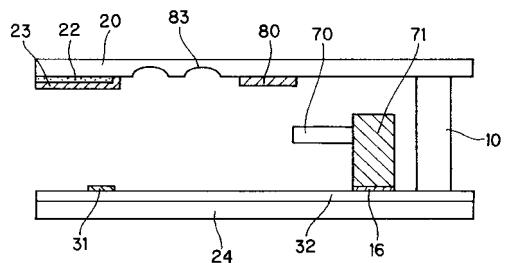

次に、本発明に係る電子線発生装置の実施例 3 について説明する。図 14 は、本発明に係る電子線発生装置の実施例 3 における、実施例 1 の図 10 中符号 II - II' のゲッター支持体近傍断面図である。ここでは実施例 1 と異なる部分のみを記述する。

#### 【 0 2 5 2 】

10

20

30

40

50

本実施例では、図14に示すように、アノードとなるメタルバック23と、カソードとなる低抵抗導体80の間（図10の81が示す領域）は、真空容器の内側に対して凹形状となるような構造83（以下、凹型構造83と記す）となっている。

【0253】

凹型構造83を設けることにより、実施例1と同様に沿面距離を長くすることで、沿面耐圧を上げることができる。

【0254】

本実施例では、フェースプレート20を深さ20μm切削することによって凹型構造83を形成した。凹型構造83の形成法としては、他にエッチングなどを用いてもよい。

10

【0255】

以上の説明より、メタルバック23と低抵抗導体80のギャップにおいて、図14のような構成にすることにより、沿面距離を長くすることで、放電を押さえると考えられる。

【0256】

メタルバック23と低抵抗導体80のギャップを2mmとして電子加速電圧を印加したところ、14kVの放電耐圧を確認した。

【0257】

以上のようにして製造された電子線発生装置を用いた画像形成装置は、輝度の高く、かつ放電の無い表示品位の良好な画像を表示することができた。

【0258】

またこの実施例においてもメタルバックと低抵抗導体の間を電気的に接続する抵抗膜を設けると特に好適である。

20

【0259】

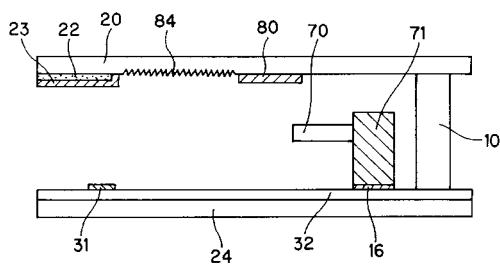

（実施例4）

図15は、本発明に係る電子線発生装置の実施例4における、図10中符号II-II'のゲッター支持体近傍断面図である。ここでは実施例1と異なる部分のみを記述する。

【0260】

本実施例では、図15に示すように、アノードとなるメタルバック23とカソードとなる低抵抗導体80の間（図10の81が示す領域）は、凹形状と凸形状とが少なくとも1以上連なる、凹凸形状となるような構造84（以下、凹凸型構造84と記す）となっている。凹部と凸部からなる凹凸が複数連なるようにすると好適である。

30

【0261】

ここで、凹凸型構造84を設けることによる、メタルバック23と低抵抗導体80間の放電抑制の要因を説明する。

【0262】

一つ目は、実施例1、2と同様に沿面距離を長くすることで、沿面耐圧が上がるということがあげられる。

【0263】

二つ目は、低抵抗導体80からの電界放出電子のフェースプレート表面への入射角依存性を緩和することによる、二次電子放出の抑制ということがあげられる。

【0264】

40

まず、低抵抗導体80（陰極）の接点付近の電界集中点から電界放出された電子のフェースプレート表面への入射が考えられる。この経路の入射角は分布をもち、通常、加速電圧として沿面方向に数～数十kV/cm程度の高電界が印加されているため高入射角となる電子がある。

【0265】

したがって、高入射角の入射電子により固体内部に形成した正電荷により実効的な電荷注入が行われる。ここで電子が斜め入射すると、二次電子の生成部位が表面に近い浅いところに分布が移動するため、再結合により消失されずに真空中に放出される割合が増加し、正の帯電が拡大し、フェースプレートの正帯電の大きな原因となっている。

【0266】

50

そこで、表面と見なす界面の法線の方向に分布を持たせると、局所的に定義された入射角はマクロに定義された角度に対して分布をもつことになり、二次電子放出係数の入射角依存性が緩和する。入射角の依存性は90度入射近傍で急激に増大する特性を示す為、入射角を分散させ緩和する効果は大きい。

【0267】

したがって、フェースプレートの表面に凹凸の構造を持たせることにより、上記多重散乱を防ぐことが出来るので、フェースプレート上の陽極陰極間での放電を抑止することが出来る。

【0268】

本実施例では、フェースプレート20にサンドブラスト処理を施し、表面の平均粗さが、

10

100オングストロームとなるような凹凸型構造84を形成した。凹凸型構造84の形成法としては、他にサンドペーパーによる処理を行ってもよい。

【0269】

以上の説明より、メタルバック23と低抵抗導体80のギャップにおいて、図15のような構成にすることにより、沿面距離を長くとること、および、二次電子放出を抑制することで、放電を押さえると考えられる。

【0270】

メタルバック23と低抵抗導体80のギャップを2mmとして電子加速電圧を印加したところ、14kVの放電耐圧を確認した。

【0271】

以上のようにして製造された電子線発生装置を用いた画像形成装置は、輝度の高く、かつ放電の無い表示品位の良好な画像を表示することができた。

【0272】

この実施例においてもメタルバックと低抵抗導体の間を抵抗膜によって電気的に接続し、抵抗膜に微小な電流が流れるようにして帯電を除去するようにした構成が好適である。

【0273】

(実施例5)

次に、本発明に係る電子線発生装置の実施例5について説明する。図16は実施例5を示すパネルの模式的平面図で、フェースプレート上方から見た場合の構成を示す。図17は、図16中符号I-I'のスペーサ固定部材近傍断面図である。

30

【0274】

図16は、便宜上フェースプレートの下半面を取り除いた図となっている。ここでは実施例1と異なる部分のみを記述する。

【0275】

図16、図17に示されるように、スペーサ13は画像領域12の外側まで両端部が延在して、支持枠10内の所定の位置にスペーサ固定部材14により固定されている。

【0276】

スペーサ固定部材14はスペーサを垂直に自立させるための溝が形成されており、スペーサ13の両端部に固定され、接着剤15によりリアプレート24もしくは、ブラックマトリクス21及び蛍光体22が形成されたフェースプレート20に固定される。

40

【0277】

本実施例では、図16に示されるように、画像領域外周のスペーサ13の配置される場所のみにおいて、実施例1に示したような凸型構造体を形成しない構成とした。

【0278】

これにより、凸型構造体とスペーサ13との干渉を防ぎつつ、干渉しない場所では実施例1と同じ構成とし、メタルバック23と低抵抗導体80のギャップでの放電を押さえた。

【0279】

メタルバック23と低抵抗導体80のギャップを2mmとして電子加速電圧を印加したところ、14kVの放電耐圧を確認した。

【0280】

10

20

30

40

50

以上のようにして製造された電子線発生装置を用いた画像形成装置は、輝度の高く、かつ放電の無い表示品位の良好な画像を表示することができた。この実施例においても、メタルバックと低抵抗導体の間を電気的に接続する抵抗膜を設ける構成とすると好適である。

#### 【0281】

以上述べた各実施例の構成よれば、フェースプレートに形成されたメタルバック（アノード）と、画像領域外に形成される導電性部材（カソード）との間に、多重散乱抑制手段を有することにより、二次電子放出の抑制をはかり、放電を抑制することができる。また、抵抗膜をアノード電位規定領域と導電性部材とのそれぞれに接触させて設けることにより、特に好適に放電を抑制することができる。放電を抑制することにより、高輝度で表示品位の良好な画像の表示が可能な電子線発生装置及び画像形成装置を提供することができる。

10

#### 【0282】

##### 【発明の効果】

以上実施例を挙げて説明してきたように、本願発明によれば望ましくない放電を抑制した電子線発生装置及び画像形成装置が実現できる。

##### 【図面の簡単な説明】

【図1】本発明に係る電子線発生装置の一実施形態の斜視断面図である。

【図2】図1の表示パネルに用いたマルチ電子ビーム源の平面図である。

【図3】図2に示されるB-B'の断面図である。

【図4】図1に示される電子線発生装置に用いられる表示パネルのフェースプレートの蛍光体配列を例示した平面図である。

20

【図5】図1に示される電子線発生装置のA-A'断面図である。

【図6】図1に示される電子線発生装置に用いられる平面型の表面伝導型放出素子の平面図(a)、断面図(b)である。

【図7】図1に示される電子線発生装置に用いられる平面型の表面伝導型放出素子の製造工程を示す断面図である。

【図8】図1に示される電子線発生装置に適用される通電フォーミング処理の際の印加電圧波形である。

【図9】図1に示される電子線発生装置に適用される通電活性化処理の際の印加電圧波形(a)、放出電流Ieの変化(b)である。

30

【図10】本発明に係る電子線発生装置の実施例1に用いられるパネルの模式的平面図である。

【図11】図10中の符号II-II'のゲッター支持体近傍断面図である。

【図12】図10に示される電子線発生装置に用いられるパネルの一部を切り欠いて示した斜視図である。

【図13】本発明に係る電子線発生装置の実施例2における、図10中の符号II-II'のゲッター支持体近傍断面図である。

【図14】本発明に係る電子線発生装置の実施例3における、図10中の符号II-II'のゲッター支持体近傍断面図である。

【図15】本発明に係る電子線発生装置の実施例4における、図10中の符号II-II'のゲッター支持体近傍断面図である。

40

【図16】本発明に係る電子線発生装置の実施例5における、パネルの一部を切り欠いて示した模式的平面図である。

【図17】図16中の符号I-I'のスペーサ固定部材近傍断面図である。

【図18】従来の表面伝導型放出素子の一例を示した模式的平面図である。

【図19】従来のFE型素子の一例を示した模式的断面図である。

【図20】従来のMIM型素子の一例を示した模式的断面図である。

【図21】従来の電子線発生装置のゲッター部分の模式図である。

【図22】従来の電子線発生装置のスペーサ支持部の模式図である。

【図23】従来の電子線発生装置のゲッター部分の模式図である。

50

## 【符号の説明】

|                   |             |    |

|-------------------|-------------|----|

| 1                 | リアプレート      |    |

| 2                 | 電子源領域       |    |

| 3                 | 画像形成部材      |    |

| 5                 | 側面部         |    |

| 1 0               | 支持枠         |    |

| 1 2               | 画像領域        |    |

| 1 3               | スペーサ        |    |

| 1 4               | スペーサ固定部材    |    |

| 1 5               | 接着剤         | 10 |

| 2 0               | フェースプレート    |    |

| 2 1               | ブラックマトリクス   |    |

| 2 2               | 蛍光体         |    |

| 2 3               | メタルバック      |    |

| 2 4               | リアプレート      |    |

| 3 1               | 行方向配線       |    |

| 3 2               | 基板          |    |

| 3 3               | 列方向配線       |    |

| 4 0               | 表面伝導型電子放出素子 |    |

| 6 1               | 高抵抗膜        | 20 |

| 7 0               | ゲッター部材      |    |

| 7 1               | ゲッター支持体     |    |

| 8 0               | 低抵抗導体       |    |

| 8 2               | 凸型構造体       |    |

| 8 3               | 凹型構造        |    |

| 8 4               | 凹凸型構造       |    |

| 1 0 0             | 絶縁性部材       |    |

| 1 1 1             | 高抵抗膜        |    |

| 1 2 1             | スペーサ電極      |    |

| 1 2 1             | 低抵抗膜        | 30 |

| 1 0 1 0           | 導電体         |    |

| 1 0 1 1           | 基板          |    |

| 1 0 1 2           | 冷陰極素子       |    |

| 1 0 1 3           | 行方向配線       |    |

| 1 0 1 4           | 列方向配線       |    |

| 1 0 1 5           | リアプレート      |    |

| 1 0 1 6           | 側壁          |    |

| 1 0 1 7           | フェースプレート    |    |

| 1 0 1 8           | 蛍光膜         |    |

| 1 0 1 9           | メタルバック      | 40 |

| 1 0 2 0           | スペーサ        |    |

| 1 0 4 1           | 当接材         |    |

| 1 1 0 1           | 基板          |    |

| 1 1 0 2 , 1 1 0 3 | 素子電極        |    |

| 1 1 0 4           | 導電性薄膜       |    |

| 1 1 0 5           | 電子放出部       |    |

| 1 1 1 0           | フォーミング用電源   |    |

| 1 1 1 1           | 電流計         |    |

| 1 1 1 2           | 活性化用電源      |    |

| 1 1 1 3           | 薄膜          | 50 |

1 1 1 4 アノード電極

1 1 1 5 直流高電圧電源

1 1 1 6 電流計

3 0 0 4 導電性薄膜

3 0 0 5 電子放出部

3 0 1 2 エミッタコーン

3 0 1 4 ゲート電極

3 0 2 0 基板

3 0 2 1 下電極

3 0 2 2 絶縁層

3 0 2 3 上電極

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図 2 3】

---

フロントページの続き

審査官 山口 剛

(56)参考文献 特開平10-321167(JP,A)

特開平05-074379(JP,A)

特開平10-097835(JP,A)

特開平05-006748(JP,A)

特開平09-027264(JP,A)

特開平11-317181(JP,A)

国際公開第00/052727(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H01J 31/12

H01J 29/18-29/32

H01J 29/86-29/92