(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) Int. Cl.

H01L 21/20 (2006.01)

(11) 공개번호 10-2007-0047307

(43) 공개일자 2007년05월04일

|             |                   |             |                |

|-------------|-------------------|-------------|----------------|

| (21) 출원번호   | 10-2007-7003816   |             |                |

| (22) 출원일자   | 2007년02월16일       |             |                |

| 심사청구일자      | 없음                |             |                |

| 번역문 제출일자    | 2007년02월16일       |             |                |

| (86) 국제출원번호 | PCT/US2005/029113 | (87) 국제공개번호 | WO 2006/023492 |

| 국제출원일자      | 2005년08월08일       | 국제공개일자      | 2006년03월02일    |

(30) 우선권주장 10/919,952 2004년08월17일 미국(US)

(71) 출원인

프리스케일 세미컨덕터, 인크.

미합중국 텍사스 (우편번호 78735) 오스틴 월리암 캐논 드라이브 웨스트 6501

(72) 발명자

사다카, 마리암 지.

미국 텍사스 78738, 오스틴, 나파 드라이브 3119

토마스, 손 지.

미국 애리조나 85296, 킥버트, 이. 모르간 스트리트 1160

화이트, 테드 알.

미국 텍사스 78731, 오스틴, 로렐우드 드라이브 6508

리우, 천-리

미국 애리조나 85212, 메사, 에스. 킴 2534

바, 알렉산더 엘.

프랑스 에프-38920 크롤, 임파쎄 드 라 폐라드 51

구엔, 비치-엔

미국 텍사스 78733, 오스틴, 에스. 로렐우드 드라이브 110

테안, 분-위

미국 텍사스 78750, 오스틴, 록클레븐 코브 10201

(74) 대리인

이범래

전체 청구항 수 : 총 28 항

(54) 그레이드된 반도체층

(57) 요약

반도체 디바이스를 형성하기 위한 공정. 상기 공정은 스트레이인된 실리콘층(305)을 형성하기 위한 템플레이트층(207)을 형성하는 단계를 포함한다. 하나의 예에서, 그레이드된 실리콘층(107)이 형성되고, 게르마늄이 더 아랫부분의 더 높은 농도로 및 상부의 더 낮은 농도로 존재한다. 응축공정에서, 상기 층의 상부의 게르마늄은 상기 실리콘게르마늄층의 나머지 부분으로 확산된다. 실리콘게르마늄층이 더 아랫부분에서의 더 높은 게르마늄 농도를 가지기 때문에, 응축 후의 게르마늄 축적은 상기 실리콘게르마늄층의 나머지 부분의 더 윗부분에서 감소할 것이다.

**대표도**

도 3

**특허청구의 범위****청구항 1.**

반도체 구조를 형성하는 방법에 있어서,

절연체상 반도체(SOI) 구조를 갖는 웨이퍼를 제공하는 단계로서, 상기 웨이퍼는 절연체 위에 제 1 반도체층을 포함하고, 상기 제 1 반도체층은 적어도 두 개의 성분들로 이루어지고, 상기 제 1 반도체층은 상기 제 1 반도체층의 제 2 부분들 위에 놓이는 제 1 부분을 포함하고, 상기 제 1 부분은 상기 적어도 두 개의 성분들 중의 제 1 성분의 제 1 농도를 포함하고, 상기 제 2 부분은 적어도 두 개의 성분들 중의 제 1 성분의 제 2 농도를 포함하며, 상기 제 1 농도는 제 2 농도보다 작은, 상기 웨이퍼 제공 단계;

상기 제 1 반도체층의 일부를 소모하고 상기 제 1 반도체층의 나머지 부분 위에 상기 적어도 두 개의 성분들 중의 제 2 성분을 포함하는 물질을 형성하기 위해 제 1 반도체층상에 응축공정을 수행하는 단계;

상기 물질을 제거하는 단계; 및

유전체를 제거한 후에 상기 나머지 부분 위에 제 2 성분을 포함하는 제 2 반도체층을 형성하는 단계를 포함하는, 반도체 구조를 형성하는 방법.

**청구항 2.**

제 1 항에 있어서, 상기 제 2 반도체층을 형성하는 단계는 상기 제 1 반도체층의 나머지 부분들을 템플레이트층으로 이용하는 단계를 포함하는, 반도체 구조를 형성하는 방법.

**청구항 3.**

제 1 항에 있어서, 상기 제 1 반도체층은 제 1 성분 함유 기체 및 제 2 성분 함유 기체를 제 1 비율로 상기 웨이퍼 위에 흐르게 하고, 이어서 상기 제 1 성분 함유 기체 및 상기 제 2 성분 함유 기체를 제 2 비율로 상기 웨이퍼 위에 흐르게 함으로써 형성되고, 상기 제 1 비율은 상기 제 2 비율보다 큰, 반도체 구조를 형성하는 방법.

**청구항 4.**

제 1 항에 있어서, 상기 제 1 반도체층은 화학기상증착층(CVD layer)인, 반도체 구조를 형성하는 방법.

**청구항 5.**

제 1 항에 있어서, 상기 제 2 반도체층이 에피택설성장층(epitaxially grown layer)인, 반도체 구조를 형성하는 방법.

**청구항 6.**

제 1 항에 있어서, 상기 제 1 성분은 게르마늄이고 상기 제 2 성분은 실리콘인, 반도체 구조를 형성하는 방법.

### 청구항 7.

제 6 항에 있어서, 상기 게르마늄은 상기 응축공정 후에 상기 제 1 반도체층의 나머지의 부분 내에 응축되는, 반도체 구조를 형성하는 방법.

### 청구항 8.

제 1 항에 있어서, 상기 제 1 반도체층의 나머지 부분은 상기 응축공정을 수행하기 전의 제 1 반도체층보다 더 느슨한 (relaxed) 것으로 특징되는, 반도체 구조를 형성하는 방법.

### 청구항 9.

제 1 항에 있어서, 상기 제 1 반도체층의 제 1 및 제 2 부분들은 제 1 성분의 상기 제 1 반도체층의 백그레이드된(back graded) 일부의 부분인, 반도체 구조를 형성하는 방법.

### 청구항 10.

제 1 항에 있어서, 채널 영역을 포함하는 트랜지스터를 형성하는 단계를 더 포함하고, 상기 채널영역의 적어도 일부는 상기 제 2 반도체층에 위치하는, 반도체 구조를 형성하는 방법.

### 청구항 11.

제 1 항에 있어서, 상기 나머지 부분의 농도 기울기(concentration gradient)는 제 1 성분의 실질적으로 일정한 분포를 포함하는, 반도체 구조를 형성하는 방법.

### 청구항 12.

제 1 항에 있어서, 상기 응축공정은 제 1 성분의 산화물보다 제 2 성분의 산화물을 더 우선적으로 생산하는, 반도체 구조를 형성하는 방법.

### 청구항 13.

제 1 항에 있어서, 상기 제 1 반도체층은 제 1 부분과 제 2 부분 사이에 위치하는 제 3 부분을 포함하고, 상기 제 3 부분은 제 1 성분의 제 3 농도를 포함하며, 상기 제 3 농도는 상기 제 2 농도보다 적고 상기 제 1 농도보다 큼, 반도체 구조를 형성하는 방법.

### 청구항 14.

반도체 구조를 형성하는 방법에 있어서,

제 1 반도체층을 포함하는 웨이퍼를 공급하는 단계로서, 상기 제 1 반도체층은 실리콘 및 게르마늄을 포함하고, 상기 제 1 반도체층은 제 1 게르마늄 농도를 갖는 제 1 부분 및 제 2 게르마늄 농도를 갖는 제 2 부분을 포함하고, 상기 제 1 부분은 제 2 부분 위에 놓이고, 상기 제 1 농도는 상기 제 2 농도보다 더 적은, 상기 웨이퍼 공급 단계;

상기 제 1 반도체층의 일부를 소모하고 상기 제 1 반도체층의 나머지 부분 위에 놓이는 실리콘을 포함하는 물질들을 형성하도록 상기 제 1 반도체층위에 응축공정을 수행하는 단계;

상기 실리콘을 포함하는 물질을 제거하는 단계; 및

상기 실리콘을 포함하는 물질을 제거하는 단계 후에 상기 나머지 부분 위에 실리콘을 포함하는 제 2 반도체층을 형성하는 단계를 포함하는, 반도체 구조를 형성하는 방법.

### 청구항 15.

제 14 항에 있어서, 상기 응축공정은 산화공정을 포함하고, 상기 실리콘을 포함하는 물질은 실리콘 산화물을 포함하는, 반도체 구조를 형성하는 방법.

### 청구항 16.

제 14 항에 있어서, 상기 제 2 반도체층을 형성하는 단계는 상기 제 1 반도체층의 나머지 부분들을 템플레이트층으로 이용하는 단계를 더 포함하는, 반도체 구조를 형성하는 방법.

### 청구항 17.

제 14 항에 있어서, 상기 제 1 반도체층은 실리콘 함유 기체 및 게르마늄 함유 기체를 제 1 비율로 상기 웨이퍼 위에 흐르게 하고, 이어서 실리콘 함유 기체 및 게르마늄 함유 기체를 상기 제 1 비율보다 더 큰 제 2 비율로 상기 웨이퍼 위에 흐르게 함으로써 형성되는, 반도체 구조를 형성하는 방법.

### 청구항 18.

제 17 항에 있어서, 상기 제 1 반도체층의 나머지 부분은 응축공정을 수행하기 이전의 제 1 반도체층보다 더 느슨한 것으로 특징되는, 반도체 구조를 형성하는 방법.

### 청구항 19.

제 14 항에 있어서, 상기 제 1 반도체층의 제 1 및 제 2 부분은 제 1 반도체층의 게르마늄의 백그레이드된(back graded) 일부의 부분인, 반도체 구조를 형성하는 방법.

### 청구항 20.

제 14 항에 있어서, 상기 나머지 부분의 게르마늄 농도 기울기는 게르마늄의 실질적으로 일정한 분포를 포함하는, 반도체 구조를 형성하는 방법.

### 청구항 21.

제 14 항에 있어서, 채널 영역을 포함하는 트랜지스터를 형성하는 단계를 더 포함하고, 상기 채널영역의 적어도 일부는 상기 제 2 반도체층에 위치하는, 반도체 구조를 형성하는 방법.

### 청구항 22.

제 14 항에 있어서, 상기 제 2 반도체층은 스트레인된 실리콘(strained silicon)으로 특징되는, 반도체 구조를 형성하는 방법.

### 청구항 23.

제 14 항에 있어서, 상기 제 1 반도체층의 제 1 부분은 응축공정을 수행하는 동안 소모되는, 반도체 구조를 형성하는 방법.

### 청구항 24.

제 14 항에 있어서, 상기 웨이퍼는 절연체상 반도체(SOI) 구조를 갖고, 상기 제 1 반도체층은 절연체 위에 위치하는, 반도체 구조를 형성하는 방법.

### 청구항 25.

제 14 항에 있어서, 상기 제 1 반도체층에 응축 단계를 수행하는 단계는 상기 제 1 반도체층의 선택 영역 상에 응축공정을 수행하는 단계를 더 포함하는, 반도체 구조를 형성하는 방법.

### 청구항 26.

반도체 디바이스를 형성하는 방법에 있어서,

절연체상 반도체(SOI) 구조를 갖는 웨이퍼를 제공하는 단계로서, 상기 웨이퍼는 절연체 위에 제 1 반도체층을 포함하고, 상기 제 1 반도체층은 게르마늄 및 실리콘을 포함하고, 상기 제 1 반도체층은 제 1 반도체층의 제 2 부분 위에 놓이는 제 1 반도체층의 제 1 부분을 포함하고, 상기 제 1 부분은 제 1 게르마늄 농도를 포함하고 제 2 부분은 제 2 게르마늄 농도를 포함하고, 상기 제 1 농도는 상기 제 2 농도보다 작은, 상기 웨이퍼 제공단계;

상기 제 1 반도체층의 일부를 소모하고 상기 제 1 반도체층의 나머지 부분 위에 산화물을 형성하기 위해서 제 1 반도체층 위에 산화공정을 수행하는 단계;

상기 산화물을 제거하는 단계;

상기 산화물을 제거한 후에 나머지 부분을 템플레이트층으로 이용하여 상기 나머지 부분 위에 실리콘을 포함하는 제 2 반도체층을 형성하는 단계; 및

채널영역을 포함하는 트랜지스터를 형성하는 단계로서, 채널영역 적어도 일부는 상기 제 2 반도체층에 위치하는, 상기 트랜지스터를 형성하는 단계를 포함하는, 반도체 디바이스를 형성하는 방법.

### 청구항 27.

제 26 항에 있어서, 상기 나머지 부분의 게르마늄 농도 기울기는 실질적으로 일정한 분포를 포함하는, 반도체 디바이스를 형성하는 방법.

## 청구항 28.

제 26 항에 있어서, 상기 제 1 반도체층의 나머지 부분은 산화공정을 수행하기 전의 제 1 반도체층보다 더 느슨한 것으로 특징되는, 반도체 디바이스를 형성하는 방법.

### 명세서

#### 기술분야

본 발명은 일반적으로 반도체 디바이스 및 특히 스트레인된(strained) 채널영역을 가진 반도체 디바이스를 형성하는 것과 관련된다.

#### 배경기술

전자 및 정공 운동도(electron and hole motilities)는 채널영역에 대한, 특히 절연체상 반도체(SOI) 구조를 갖는 웨이퍼들로 만들어진 디바이스들에 대한, 스트레인된(예를 들면 쌍축 인장 스트레인(bi-axial tensile strain) 실리콘의 이용으로 향상될 수 있다. 스트레인된 실리콘층은 템플레이트층(예를 들면 실리콘 게르마늄)위에 실리콘층을 침착시킴으로써 형성될 수 있다. 일부 공정들에서, 응축공정이 상기 실리콘게르마늄템플레이트위에 수행되어 실리콘의 침착에 앞서 상기 층을 느슨하게 한다(relax). 응축공정의 그러한 하나의 예는 실리콘게르마늄템플레이트층의 산화를 포함한다. 그러한 공정으로,  $\text{SiO}_2$ 의 층이 템플레이트층의 상부에 성장되고, 템플레이트층 소모된 부분의 게르마늄이 실리콘게르마늄층의 나머지 부분 아래로 확산되어 나머지 부분을 풍부하게 한다. 이어서 산화물이 스트레인된 실리콘의 침착에 앞서 에칭된다.

그러한 방법에 따른 일어날 수 있는 하나의 문제는 게르마늄이 실리콘게르마늄층의 나머지 부분으로 적절히 확산되지 않을 수 있다는 것이다. 따라서, 실리콘게르마늄층의 더 아랫부분의 게르마늄 농도와 대조적으로 나머지 층의 상부에서 상대적으로 높은 게르마늄 농도가 있을 수 있다. 템플레이트층에서의 게르마늄 농도에 있어 이러한 차이들은 전위(dislocations)의 영역에서 형성되는 기능장에 반도체 디바이스로 이르게 할 수 있는 전위를 유발할 수 있다.

#### 발명의 상세한 설명

반도체 디바이스들의 제조에 있어서 진보된 공정이 요구된다.

본 발명은 첨부된 도면을 참조함으로써 당업자가 잘 이해할 수 있고, 그것의 다수의 대상들, 특징들, 및 이점들이 명백해질 것이다.

#### 실시예

다음은 본 발명을 실행하기 위한 발명의 실시예이다. 여기에 기술된 사항은 본 발명을 예시하는 것으로 의도된 것이며, 한정하는 것으로 해석되어서는 안된다.

템플레이트층 물질의 층에 그레이드된(graded) 게르마늄 농도를 제공하는 것은 응축공정이 상기 층에서 수행된 후 더욱 일정한 게르마늄 그레이드(grade)를 제공한다는 것이 발견되었다.

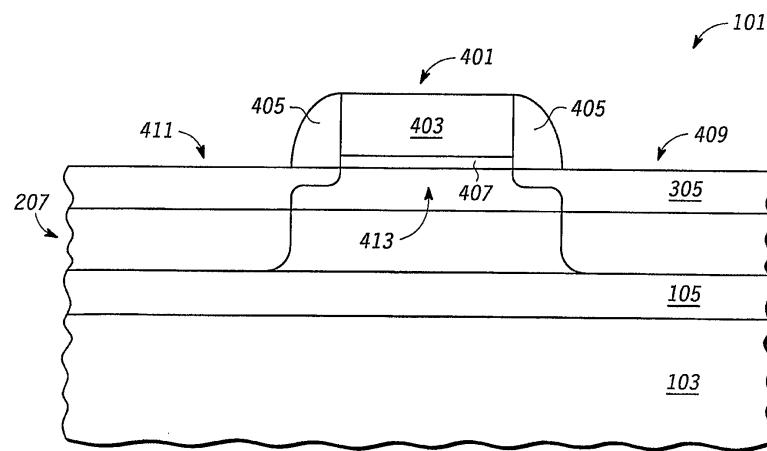

도 1은 반도체 디바이스의 제조 단계 동안의 웨이퍼(101)의 부분적인 단면도이다. 소개되는 실시예에서 웨이퍼(101)는 기판(103)위에 위치한 절연층(105)(예를 들면, 산화물)을 가진 반도체 기판(103)을 포함한다. 실리콘층(106)(예를 들면, 100 Å)은 절연층(105)위에 위치한다. 한 실시예에서, 층(106), 층(105), 및 기판(103)은 SIMOX공정 또는 하나의 실리콘 웨이퍼를 다른 웨이퍼의 산화층에 본딩함으로써 형성된다. 한 실시예에서 웨이퍼(101)는 절연체상 반도체(SOI) 구조를 갖는다. 또 다른 실시예들에서는, 웨이퍼(101)는 SOI 구조들의 다른 타입들(예를 들면, 사파이어 또는 석영 위의 실리콘)을 가질 것이다.

소개되는 실시예에서, 실리콘게르마늄층(silicon germanium layer)(107)은 실리콘층(106)위에 형성된다. 소개되는 실시예에서, 층(107)의 게르마늄 농도는 층(107)의 아랫부분의 높은 농도부터 층(107)의 상부에서의 더 낮은 농도까지 그레이드된다(graded).

하나의 실시예에서, 층(107)은 화학기상증착(chemical vapor deposition : CVD)에 의해 에피택셜 성장된다(epitaxially grown). 그러한 공정의 하나의 예에서, 게르마늄 함유 기체(예를 들면, 게르만(germane) 또는 게르마늄 테트라클로라이드(germanium tetrachloride)) 및 실리콘 함유 기체(예를 들면, 실란(silane) 또는 디클로로 실란(di-chloro silane)가 게르마늄 기체 대 실리콘 함유 기체의 제 1 비율로 층(106)위에 흐른다(flow). 층(107)의 더 윗부분들이 형성됨에 따라, 게르마늄 함유 기체 대 실리콘 함유 기체의 비율이 감소되어 이 부분들의 게르마늄 농도를 감소시킨다.

하나의 예에서, 게르마늄 농도는 층(107)의 하부에서 50%이고, 층(107)의 상부에서는 10%로 점차 감소한다. 그러나, 다른 실시예들들은 다른 게르마늄 그레이드 프로파일들을 가질 것이다. 다른 실시예들에서, 층(107)의 하부의 게르마늄 농도는 100% 게르마늄부터 10% 게르마늄까지의 범위가 될 것이다. 층(107)의 상부에서 게르마늄 농도는 0-20%의 범위를 가질 것이다. 그러나 다른 실시예들에서 층(107)은 상부 및 하부에서 서로 다른 게르마늄 농도를 가질 것이다.

하나의 실시예에서, 층(107)은 하부의 30%부터 상부의 10%까지의 게르마늄 그레이드와 함께 700Å의 두께를 가진다. 다른 실시예들에서, 층(107)은 다른 두께일 수 있다. 일부 실시예에서는 층(107)의 두께는 CVD 공정 동안 게르마늄 농도를 그레이드시킬 수 있는 능력뿐만 아니라, 층(107)의 하부의 게르마늄 농도 및 층(107)의 상부의 게르마늄 농도에 의존한다.

소개되는 실시예에서, 더 윗부분들이 더 아랫부분보다 더 낮은 게르마늄 농도를 갖는다는 점에서, 층(107)의 게르마늄 농도가 백그레이드된(back graded) 것으로 특징된다. 그러나, 일부 실시예들에서는, 층(107)은 게르마늄 농도가 백그레이드되지는 않는 부분을 포함할 수 있다. 예를 들면, 하나의 실시예에서 층(107)은 절연층(105) 위에 형성될 것이다, 상기에서 초기에 게르마늄 농도는 0(zero)이지만 빠르게 증가한다(예를 들면, 30%). 그리고 나서 그 위의 부분의 게르마늄 농도는 상부의 더 낮은 농도(예를 들면, 10%)까지 백그레이드될 것이다.

일부 실시예들에서, CVD 공정에서 게르마늄 함유 기체 대 실리콘 함유 기체의 비율은 선형적으로 또는 단계적 방식(step wise fashion)으로 적용될 수 있다. 일부 실시예들에서, 단계적 공정(step wise process)의 단계들의 수는 희망하는 게르마늄 농도 그레이드에 달려있다.

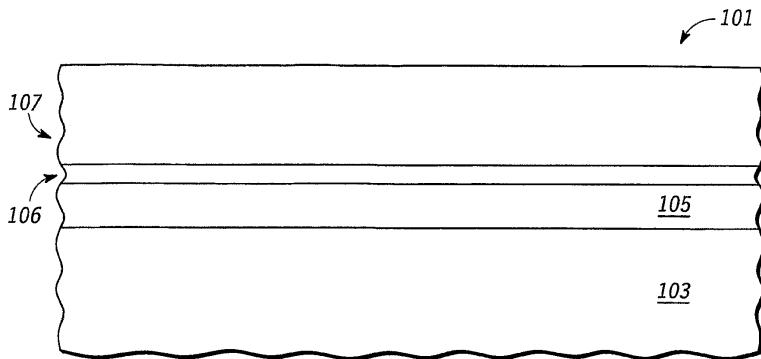

도 2는 웨이퍼(101) 위에 응축공정이 진행된 후의 웨이퍼(101)의 부분적인 단면도를 보여준다. 소개되는 실시예의 응축공정 동안, 층(107)의 상부(도 1)은 실리콘 산화물 층(209)이 실리콘게르마늄층(207)의 나머지 부분 위에 성장하게 하기 위해서 소모된다(consumed). 또한 응축공정 동안, 게르마늄이 층(107)에서 층(106)으로 확산된다(층(106)이 층(107)의 나머지 부분과 효과적으로 병합된다). 따라서 도 2에서, 층(207)은 층(106) 및 층(107)의 나머지 부분들을 포함한다. 다른 실시예들에서, 응축공정들의 다른 타입들이 이용될 수 있어서 층의 나머지 부분에서의 게르마늄 농도를 증가시킬 수 있다.

응축공정 동안, 게르마늄은 소모되는 층(107)의 상부에서 나머지 부분(층(207))으로 확산된다. 층(107)이 그레이드되기 때문에, 응축공정 후의 층(207)에서의 게르마늄 농도는 비교적 일정하다. 이전의 일부 기술 공정들과 비교하면, 층(207)의 상부에서 만들어진 게르마늄의 상대적인 부족이 있다. 하나의 실시예에서, 층(207)에서의 게르마늄 농도는 층(207)의 두께에 걸쳐서 약 35% ±2% 이다. 그러나, 결과적인 층(207)의 게르마늄 농도는 다른 실시예들에서 다른 값들이 될 수 있고 및/또는 다른 기울기들(gradients)이 될 수 있다.

하나의 실시예에서, 응축공정이 6% HCl 기체(예를 들면, 6% 농도)를 가지고 1050°C에서 30분 동안 수행된다. 그러나, 다른 응축공정들이 다른 온도(1200°C까지 및 그 이상)에서의, 다른 시간 동안, 및/또는 다른 기체들을 가지고, 수행된다. 하나의 실시예에서, 층(207)은 40nm의 두께를 갖는다.

다른 농도의 실리콘 게르마늄을 이용하는 또 다른 이점은 더 낮은 온도(예를 들면, 일부 예들의 1200°C 공정과 대조적으로 1050°C)에서 및/또는 더 짧은 응축 시간 동안의 응축공정을 고려한다는 점이다. 하나의 실시예에서, 층(107)의 하부에서 더 높은 게르마늄 농도를 갖는 것은 확산을 위한 제 2 추진력을 제공한다, 여기에서 더 윗부분에서의 낮은 게르마늄 농도 때문에 게르마늄 원소들이 층(107)의 위쪽으로 확산된다. 이와 같은 확산을 위한 제 2 추진력은 그외에 응축으로 인해 소모되는 층(107)의 상부의 게르마늄으로부터 게르마늄의 확산 추진력에 더해진다. 더 낮은 온도에서 응축공정을 수행하는 하나의 이점은 층(207)에서 일어날 수 있는 용해(melting)를 방지하는 것일 것이다. 일부 실시예들과 함께, 더 높은 게르마늄 농도는 실리콘 게르마늄의 용해점을 낮춘다. 따라서 더 낮은 온도들에서 응축공정들을 수행하는 것이 유리할 수 있다.

일부 실시예들에서, 실리콘캡층(silicon cap layer)(도시되지 않음)은 층(107)의 응축 전에 실리콘게르마늄층(107)위에 형성될 수 있다.

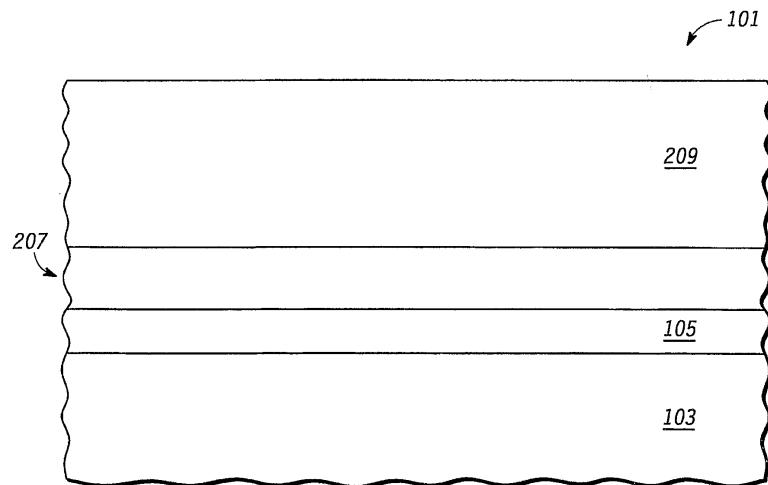

도 3은 산화물 층(209)가 제거된 후(예를 들면, HF 습식 애칭에 의해) 및 스트레인된 실리콘층(305)이 실리콘게르마늄층(207)위에 에피택셜로 침착된 후의 웨이퍼(101)의 부분적인 단면도이다. 층(207)은 침착층(deposit layer)(305)에 대한 템플레이트층으로 기능한다. 상기에서 층(305)의 격자는 층(207)의 격자와 동일한 격자상수(lattice constant)를 갖는다. 하나의 실시예에서, 층(305)은 200Å의 두께를 갖는다. 그러나 다른 실시예들에서, 다른 두께를 가질 것이다.

하나의 실시예에서, 층(207)은 응축공정 후에 느슨해진다(relaxed). 따라서, 실리콘층(305)의 격자는 층(207)의 격자상수를 매치하기 위한 인장 스트레인(tensile strain)을 갖는다. 다른 실시예들에서, 층(207)은 다른 스트레인 특성(부분적으로 느슨해진)을 갖는다. 층(207)의 스트레인 특성은 층(107)의 스트레인 농도보다 더 느슨해진다.

일부 실시예들에서, 다른 공정들이 층(305)에 수행될 수 있다. 이는 "템플레이트층 형성(Template Layer Formation)"이라 명명된 응용예들을 설명하는 공정들을 포함한다. 이는 공동의 양수인을 갖고 있고, 문서 번호 SC12851ZP P01을 갖고 있고, 동시에 출원되고, 전체가 완전히 참조로써 통합되었다. 다른 공정들의 예들은 염소 함유 기체로 포스트 베이킹(post bake)하는 것을 포함한다.

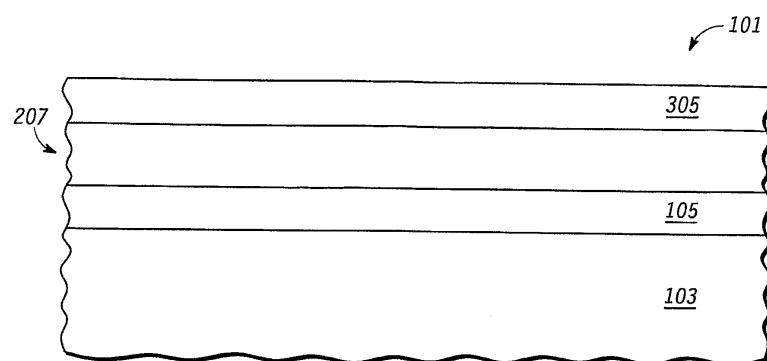

도 4는 트랜지스터(401)가 형성된 후의 웨이퍼(101)의 부분적인 단면도를 도시한다. 트랜지스터(401)은 게이트 산화물(gate oxide)(407)위에 형성된 게이트(403)를 포함한다. 게이트 산화물(407)은 스트레인된 실리콘층(305)위에 형성된다. 또한 트랜지스터(307)는 층(305)위에 형성된 스페이서(spacer)(405)를 포함한다. 소개되는 실시예에서, 트랜지스터(401)는 예를 들면 선택 영역들에서 층(305 및 207)으로 불순물들을 주입함으로써 형성되는 소스/드레인 영역들(411 및 409)을 포함한다. 트랜지스터(401)는 스트레인된 실리콘층(305)에서 형성된(실시예에서 도시됨) 채널영역(413)을 포함한다.

다른 실시예들에서, 템플레이트층 물질은 실리콘 게르마늄 탄소, 실리콘 주석, 게르마늄 탄소, 탄소와 같은 다른 성분들을 포함한다. 웨이퍼(101)는 다른 트랜지스터들을(도시되지 않음) 포함할 것이다. 일부 실시예들에서, 층(107)이 선택적으로 웨이퍼(101)의 일부 영역들에서 형성될 수 있다. 다른 실시예들에서, 층(107)이 웨이퍼(101)의 전체 위에 형성된다. 또한 일부 실시예들에서, 응축공정이 선택적으로 층(107)의 전체 위에 수행될 수 있다. 다른 실시예들에서, 응축공정이 웨이퍼의 선택영역에 수행될 수 있고, 다른 영역들은 마스크된다. 예를 들면, 층(305)이 N-채널영역 및 P-채널영역에서 서로 다른 스트레인 특성들을 갖는 것이 바람직할 수 있다.

하나의 실시예에서, 반도체 구조를 형성하는 방법은 절연체상 반도체(SOI) 구조를 갖는 웨이퍼를 제공하는 단계를 포함한다. 웨이퍼는 절연체 위에 제 1 반도체층을 포함한다. 제 1 반도체층은 적어도 두 개의 성분들로 이루어진다. 제 1 반도체층은 제 1 반도체층의 제 2 부분 위에 놓이는 제 1 부분을 포함한다. 제 1 부분은 적어도 두 개의 성분들 중의 제 1 성분의 제 1 농도를 포함하고 및 제 2 부분은 적어도 두 개의 성분들 중의 제 1 성분의 제 2 농도를 포함한다. 제 1 농도는 제 2 농도보다 작다. 상기 방법은 제 1 반도체층의 부분을 소모하기 위해 및 상기 제 1 반도체층의 나머지 부분 위에 적어도 두 개의 성분들 중의 제 2 성분을 포함하는 물질을 형성하기 위해 제 1 반도체층위에 응축공정을 수행하는 단계를 더 포함한다. 또한 상기 방법은 상기 물질을 제거하고, 상기 물질을 제거한 후에 나머지 부분 위에 제 2 성분을 포함하는 제 2 반도체층을 형성하는 단계를 포함한다.

또 다른 실시예에서, 반도체 구조를 형성하는 방법은 웨이퍼를 제공하는 단계를 포함한다. 웨이퍼는 제 1 반도체층을 포함한다. 제 1 반도체층은 실리콘 및 게르마늄을 포함한다. 제 1 반도체층은 제 1 게르마늄 농도를 갖는 제 1 부분 및 제 2 게르마늄 농도를 갖는 제 2 부분을 포함한다. 제 1 부분은 제 2 부분들 위에 놓여진다. 제 1 농도는 제 2 농도보다 작다. 또한 상기 방법은 제 1 반도체층의 부분을 소모하기 위해 및 상기 제 1 반도체층의 나머지 부분 위에 실리콘을 포함하는 물질을 형성하기 위해 제 1 반도체층위에 응축공정을 수행하는 단계를 포함한다. 마찬가지로 상기 방법은 실리콘을 포함하는 물질을 제거하고, 실리콘을 포함하는 물질을 제거한 후에 나머지 부분 위에 실리콘을 포함하는 제 2 반도체층을 형성하는 단계를 포함한다.

또 다른 실시예에서, 반도체 디바이스를 형성하는 방법은 절연체상 반도체(SOI) 구조를 갖는 웨이퍼를 제공하는 단계를 포함한다. 웨이퍼는 절연체 위의 제 1 반도체층을 포함한다. 제 1 반도체층은 게르마늄 및 실리콘을 포함한다. 제 1 반도체층은 제 1 반도체층의 제 2 부분 위에 놓이는 제 1 부분을 포함한다. 제 1 부분은 제 1 게르마늄 농도를 포함하고 및 제 2 부분은 제 2 게르마늄 농도를 포함한다. 제 1 농도는 제 2 농도보다 작다. 또한 상기 방법은 제 1 반도체층의 부분을 소모하기 위해 및 상기 제 1 반도체층의 나머지 부분 위에 산화물을 형성하기 위해 제 1 반도체층에 산화공정(oxidation

process)을 수행하는 단계를 포함한다. 마찬가지로 상기 방법은 산화물을 제거하고, 산화물을 제거한 후에 나머지 부분을 템플레이트층으로 이용하는 나머지 부분 위에 실리콘을 포함하는 제2 반도체층을 형성하는 단계를 포함한다. 또한 상기 방법은 채널영역을 포함하는 트랜지스터를 형성하는 단계를 포함한다. 적어도 채널영역 부분은 제2 반도체층에 위치한다.

본 발명의 특별한 실시예들이 소개되고 기술되었더라도, 당업자들은 여기에 기재된 내용에 기초하여, 본 발명 및 본 발명의 더 넓은 양상을 벗어나지 않고도 다른 그레이드들과 변경들이 가능할 수 있다는 것을 인식할 것이다. 따라서 여기에 덧붙여진 청구항들은 본 발명의 사상 내에 그러한 모든 그레이드들과 변경들을 포함하고, 본 발명의 의도 및 사상 내에 존재한다.

### 산업상 이용 가능성

본 발명은 반도체 구조를 형성하는 방법에 있어서 진보된 공정을 제공할 수 있고, 또한 스트레인된 채널영역을 가진 반도체 디바이스를 제공할 수 있다.

### 도면의 간단한 설명

도 1은 본 발명에 따른 반도체 디바이스의 제조 단계 동안의 웨이퍼의 한 실시예의 부분적인 단면도이다.

도 2는 본 발명에 따른 반도체 디바이스의 다른 제조 단계 동안의 웨이퍼의 실시예의 부분적인 단면도이다.

도 3은 본 발명에 따른 반도체 디바이스의 다른 제조 단계 동안의 웨이퍼의 실시예의 부분적인 단면도이다.

도 4는 본 발명에 따른 반도체 디바이스의 다른 제조 단계 동안의 웨이퍼의 실시예의 부분적인 단면도이다.

다른 도면들에서의 같은 참조번호의 이용은 다른 주의가 없다면 동일한 항목들을 나타낸다. 상기 도면들이 반드시 스케일에 맞게 그려진 것은 아니다.

### 도면

도면1

도면2

도면3

도면4