(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5709709号

(P5709709)

(45) 発行日 平成27年4月30日(2015.4.30)

(24) 登録日 平成27年3月13日(2015.3.13)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 27/146 | (2006.01) |

| HO 1 L 27/144 | (2006.01) |

| HO 1 L 31/08  | (2006.01) |

| HO 4 N 5/32   | (2006.01) |

| HO 1 L        | 27/14     |

| HO 1 L        | 27/14     |

| HO 1 L        | 31/00     |

| HO 4 N        | 5/32      |

請求項の数 11 (全 20 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2011-209461 (P2011-209461) |

| (22) 出願日     | 平成23年9月26日 (2011.9.26)       |

| (65) 公開番号    | 特開2013-12697 (P2013-12697A)  |

| (43) 公開日     | 平成25年1月17日 (2013.1.17)       |

| 審査請求日        | 平成26年9月12日 (2014.9.12)       |

| (31) 優先権主張番号 | 特願2011-122015 (P2011-122015) |

| (32) 優先日     | 平成23年5月31日 (2011.5.31)       |

| (33) 優先権主張国  | 日本国 (JP)                     |

早期審査対象出願

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (74) 代理人  | 100124442<br>弁理士 黒岩 創吾                     |

| (72) 発明者  | 藤吉 健太郎<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内   |

| (72) 発明者  | 望月 千織<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内    |

最終頁に続く

(54) 【発明の名称】 検出装置の製造方法、その検出装置及び検出システム

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素を基板の上に有し、前記画素が、前記基板の上に配置されたスイッチ素子と、前記スイッチ素子の上に配置され前記画素毎に分離され前記スイッチ素子と接合された電極の上に設けられた不純物半導体層と前記不純物半導体層の上に設けられた半導体層を含む変換素子と、を有し、前記不純物半導体層の不純物濃度は前記半導体層の不純物濃度よりも高く、前記スイッチ素子を覆うように前記基板と複数の前記電極との間に設けられた有機材料からなる層間絶縁層を有する検出装置の製造方法であって、

前記層間絶縁層に接する複数の前記電極と、複数の前記電極のうち隣接する2つの電極の間ににおいて前記層間絶縁層を覆うように配置された無機材料からなる絶縁部材と、を形成する第1の工程と、

前記第1の工程の後に、前記絶縁部材と複数の前記電極とを覆う、前記不純物半導体層となる不純物半導体膜を成膜する第2の工程と、

を有する検出装置の製造方法。

## 【請求項 2】

前記第1の工程は、前記層間絶縁層を覆うように無機材料からなる絶縁膜を成膜し、前記絶縁膜の一部を除去して、前記絶縁部材を形成する工程と、前記層間絶縁層及び前記絶縁部材を覆うように透明導電性酸化物膜を成膜し、前記透明導電性酸化物膜の一部を除去して、前記電極を形成する工程と、を有する請求項1に記載の検出装置の製造方法。

10

20

**【請求項 3】**

前記第1の工程は、前記層間絶縁層を覆うように透明導電性酸化物膜を成膜し、前記透明導電性酸化物膜の一部を除去して、前記電極を形成する工程と、前記層間絶縁層及び前記電極を覆うように無機材料からなる絶縁膜を成膜し、前記絶縁膜の一部を除去して、前記絶縁部材を形成する工程と、を有する請求項1に記載の検出装置の製造方法。

**【請求項 4】**

前記第2の工程の後に、前記絶縁部材の上において前記不純物半導体膜の一部を除去して、不純物半導体層を形成する第3の工程を更に有する請求項1から3のいずれか1項に記載の検出装置の製造方法。

**【請求項 5】**

前記第3の工程の後に、前記不純物半導体膜を覆うように半導体膜を成膜する第4の工程を更に有する請求項4に記載の検出装置の製造方法。

**【請求項 6】**

前記第2の工程の後に、前記不純物半導体層を覆うように半導体膜を成膜する第5の工程を更に有する請求項1から3のいずれか1項に記載の検出装置の製造方法。

**【請求項 7】**

前記第5の工程の後に、前記絶縁部材の上で前記不純物半導体膜と前記半導体膜とを除去して、前記不純物半導体膜から前記不純物半導体層を、前記半導体膜から前記変換素子の半導体層を、それぞれ形成する第6の工程を更に有する請求項6に記載の検出装置の製造方法。

**【請求項 8】**

前記第4の工程は、前記半導体膜を成膜する前に前記半導体膜よりも水素濃度の高い半導体膜を成膜する工程を更に有する請求項5に記載の検出装置の製造方法。

**【請求項 9】**

前記第4の工程の後に、前記半導体膜を覆うように前記不純物半導体膜とは異なる導電型の不純物半導体膜を成膜する工程と、前記異なる導電型の不純物半導体膜を覆うように前記電極とは異なる前記変換素子の他の電極となる導電膜を成膜する工程と、前記導電膜と接合する電極配線の正射影が前記絶縁部材と重なるように前記電極配線を形成する工程と、を更に有する請求項5に記載の製造方法。

**【請求項 10】**

複数の画素を基板の上に有し、前記画素が、前記基板の上に配置されたスイッチ素子と、前記スイッチ素子の上に配置され前記画素毎に分離され前記スイッチ素子と接合された電極の上に設けられた不純物半導体層と前記不純物半導体層の上に設けられた半導体層を含む変換素子と、を有し、前記不純物半導体層の不純物濃度は前記半導体層の不純物濃度よりも高く、複数の前記スイッチ素子を覆うように複数の前記スイッチ素子と複数の前記電極との間に設けられた有機材料からなる層間絶縁層を有する検出装置であって、前記層間絶縁層に接して前記層間絶縁層の上に配置された複数の前記電極のうち隣接する2つの電極の間において前記層間絶縁層を覆うように前記層間絶縁層の上に配置された無機材料からなる絶縁部材を有し、

前記不純物半導体層の端部が、前記絶縁部材の上に重なるように配置されていることを特徴とする検出装置。

**【請求項 11】**

請求項10に記載の検出装置と、

前記検出装置からの信号を処理する信号処理手段と、

前記信号処理手段からの信号を記録するための記録手段と、

前記信号処理手段からの信号を表示するための表示手段と、

前記信号処理手段からの信号を伝送するための伝送処理手段と、

を具備する検出システム。

**【発明の詳細な説明】****【技術分野】**

10

20

30

40

50

**【0001】**

本発明は、医療用画像診断装置、非破壊検査装置、放射線を用いた分析装置などに応用される検出装置の製造方法、その検出装置、及び、検出システムに関するものである。

**【背景技術】****【0002】**

近年、薄膜半導体製造技術は、TFT（薄膜トランジスタ）等のスイッチ素子と、フォトダイオード等の放射線又は光を電荷に変換する変換素子と、を組み合わせた画素のアレイ（画素アレイ）を有する検出装置にも利用されている。

特許文献1に示す従来の検出装置は、基板の上に配置された透明導電性酸化物からなる画素毎に分離された電極上に設けられた変換素子を有する。また、基板と電極との間に配置された有機材料からなる層間絶縁層に設けられたコンタクトホールを介して電極と接続されたスイッチ素子、を有する。変換素子は、層間絶縁層の上でその不純物半導体層や半導体層が除去されており、画素毎に分離されている。

10

**【先行技術文献】****【特許文献】****【0003】**

【特許文献1】特開2007-035773号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

20

しかしながら、特許文献1の構成を製造しようとすると、変換素子の不純物半導体層となる不純物半導体膜を成膜する際に、層間絶縁層が露出している工程が存在する。このような場合、製造方法によっては、不純物半導体膜の成膜時において、層間絶縁層が露出されることとなる。そのため、層間絶縁層の有機材料が、成膜時のプロセスによって一部飛散し、不純物半導体層へ混入してしまう。それにより、変換素子の不純物半導体層が有機汚染されてしまい、不純物半導体層の欠陥や不純物半導体層と半導体層との間の欠陥が増加し、変換素子での暗電流の増加を招くという問題がある。

**【0005】**

そこで、層間絶縁層の露出を防止する為に、層間絶縁層を覆うように無機材料からなる絶縁層を配置することが考えられる。しかしながら、この場合、透明導電性酸化物からなる変換素子の電極が絶縁層上に配置されることとなる。この透明導電性酸化物は、非晶質状態で成膜されてから多結晶化することによって形成される。透明導電性酸化物は、多結晶化の際に内部応力が変化する。無機材料からなる絶縁層は有機材料からなる層間絶縁層に比べて硬度が高く、結合エネルギーが大きいため、透明導電性酸化物の多結晶化の際の内部応力に追従することができず、絶縁層から変換素子の電極が剥離するといった問題が生じ得る。

30

**【0006】**

本発明は、このような問題を解決しようとするものであり、変換素子の不純物半導体層への有機材料の混入を低減し、且つ、変換素子の電極の剥離を低減し得る検出装置を提供することを目的とする。

40

**【課題を解決するための手段】****【0007】**

本発明の検出装置の製造方法は、複数の画素を基板の上に有し、前記画素が、前記基板の上に配置されたスイッチ素子と、前記スイッチ素子の上に配置され前記画素毎に分離され前記スイッチ素子と接合された電極の上に設けられた不純物半導体層と前記不純物半導体層の上に設けられた半導体層を含む変換素子と、を有し、前記不純物半導体層の不純物濃度は前記半導体層の不純物濃度よりも高く、前記スイッチ素子を覆うように前記基板と複数の前記電極との間に設けられた有機材料からなる層間絶縁層を有する検出装置の製造方法であって、前記層間絶縁層に接する複数の前記電極と、複数の前記電極のうち隣接する2つの電極の間に於いて前記層間絶縁層を覆うように配置された無機材料からなる絶縁

50

部材と、を前記層間絶縁層の上に形成する第1の工程と、前記第1の工程の後に、前記絶縁層と複数の前記電極とを覆う、前記不純物半導体層となる不純物半導体膜を成膜する第2の工程と、を有する。

#### 【0008】

また、本発明の検出装置は、複数の画素を基板の上に有し、前記画素が、前記基板の上に配置されたスイッチ素子と、前記スイッチ素子の上に配置され前記画素毎に分離され前記スイッチ素子と接合された電極の上に設けられた不純物半導体層と前記不純物半導体層の上に設けられた半導体層を含む変換素子と、を有し、前記不純物半導体層の不純物濃度は前記半導体層の不純物濃度よりも高く、前記スイッチ素子を覆うように前記基板と複数の前記電極との間に設けられた有機材料からなる層間絶縁層を有する検出装置であって、

10

前記層間絶縁層に接して前記層間絶縁層の上に配置された複数の前記電極のうち隣接する2つの電極の間ににおいて前記層間絶縁層を覆うように前記層間絶縁層の上に配置された無機材料からなる絶縁部材を有し、前記不純物半導体層の端部が、前記絶縁部材の上に重なるように配置されたものである。

#### 【発明の効果】

#### 【0009】

本発明により、変換素子の不純物半導体層への有機材料の混入を低減し、且つ、変換素子の電極の剥離を低減し得る検出装置を提供することが可能となる。

#### 【図面の簡単な説明】

#### 【0010】

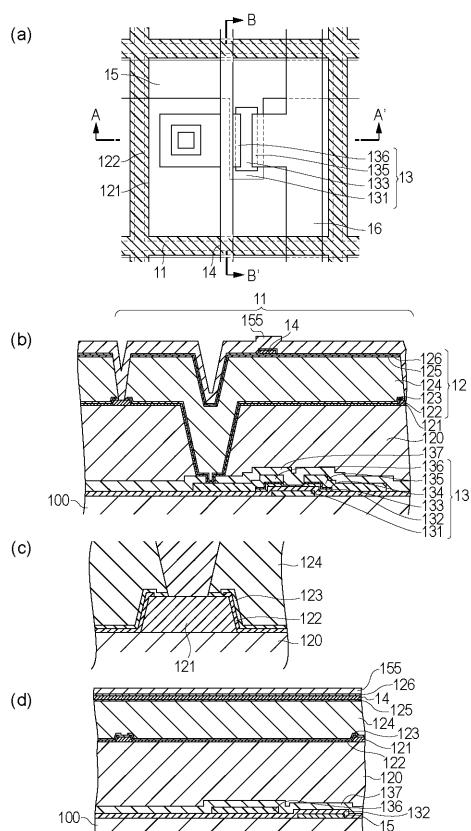

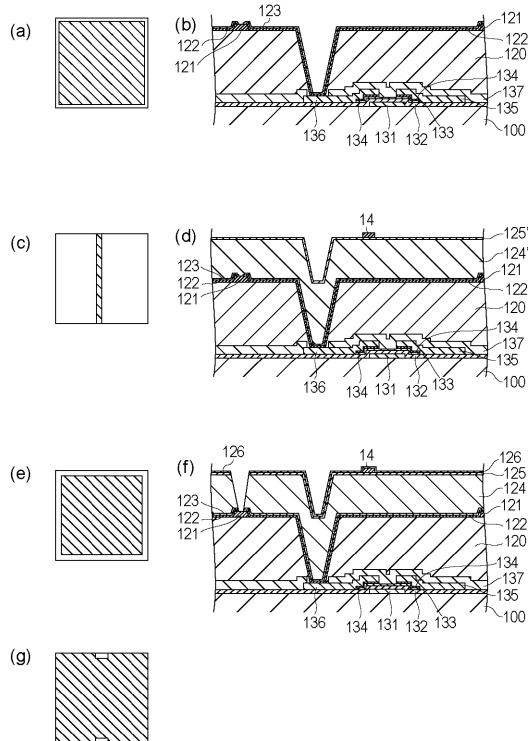

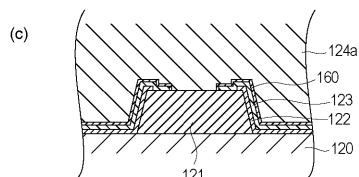

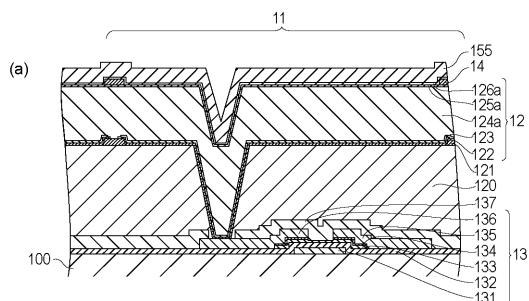

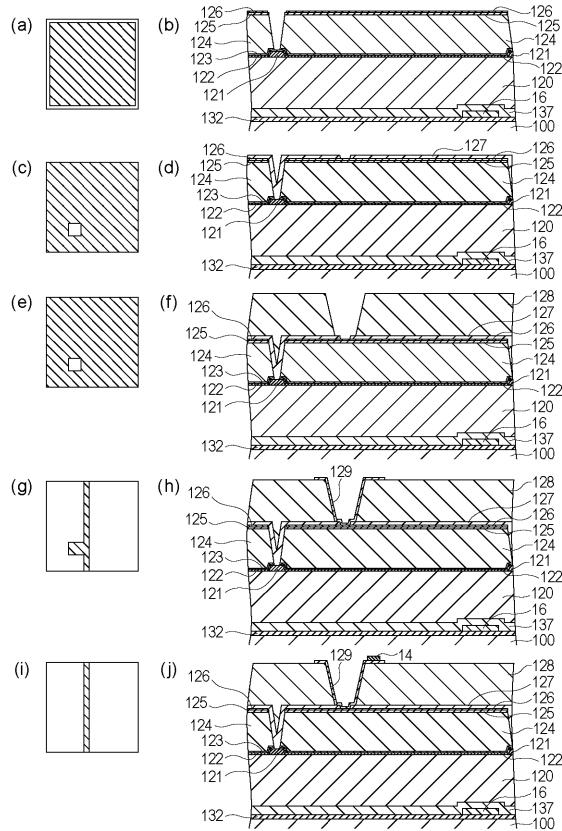

【図1】本発明の第1の実施形態に係る検出装置の1画素あたりの平面図、断面図、及び、画素間の拡大図である。

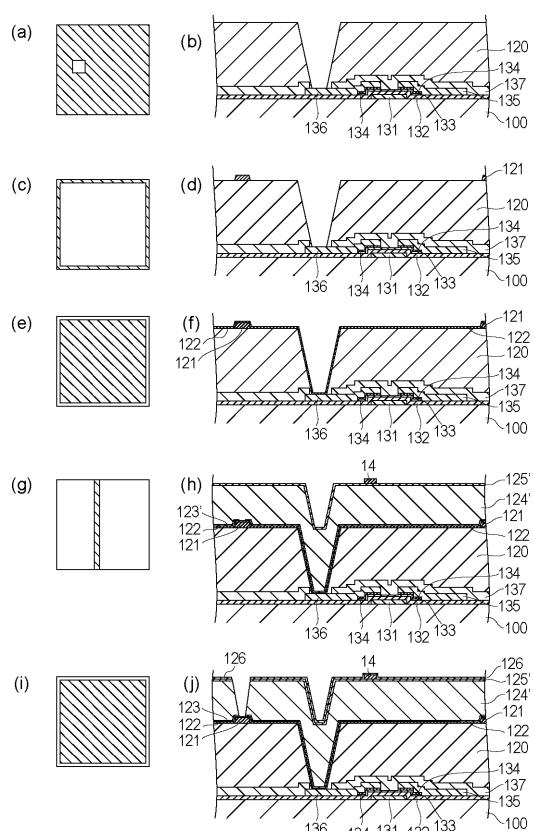

【図2】本発明の第1の実施形態に係る検出装置の製造方法を説明するためのマスクパターン及び断面図である。

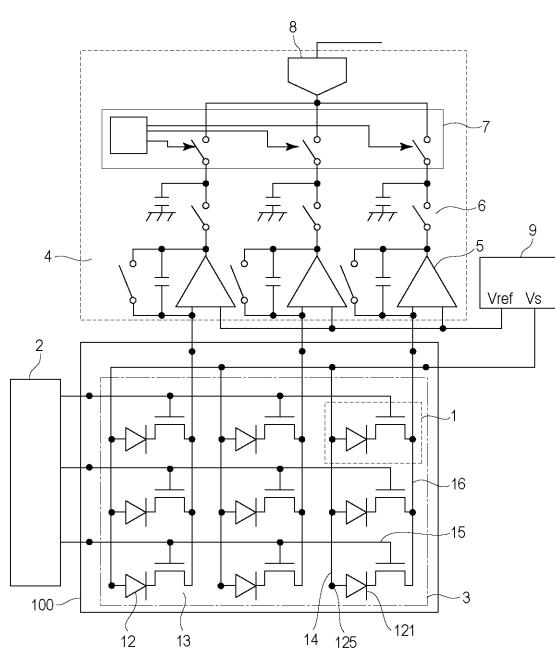

#### 【図3】本発明の検出装置の等価回路図である。

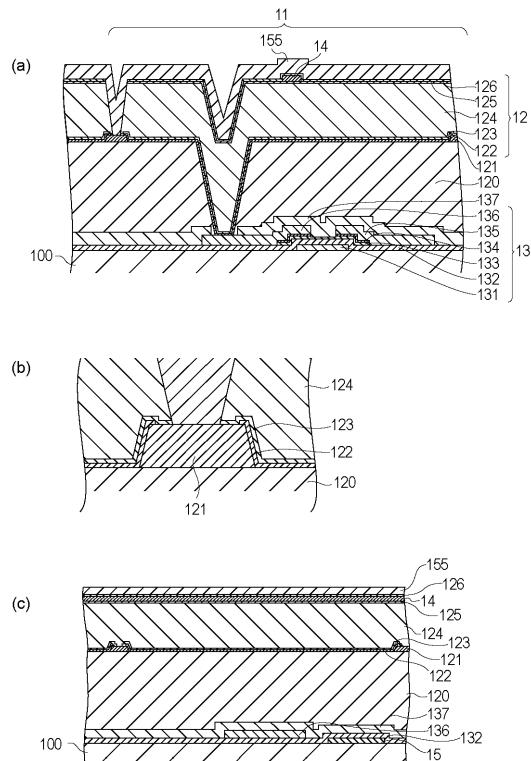

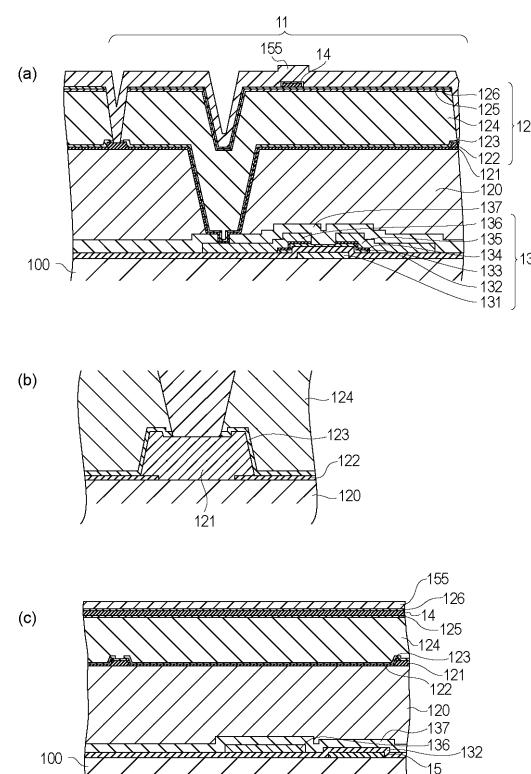

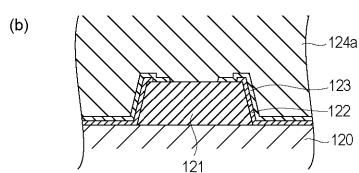

【図4】本発明の第2の実施形態に係る検出装置の1画素あたりの断面図、及び、画素間の拡大図である。

【図5】本発明の第2の実施形態に係る検出装置の製造方法を説明するためのマスクパターン及び断面図である。

30

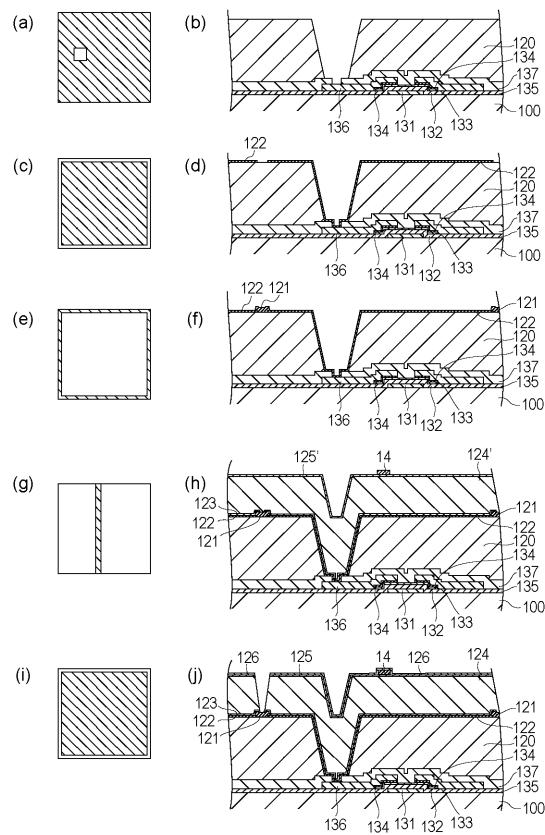

【図6】本発明の第3の実施形態に係る検出装置の1画素あたりの断面図及び画素間の拡大図である。

【図7】本発明の第3の実施形態に係る検出装置の製造方法を説明するためのマスクパターン及び断面図である。

【図8】本発明の第4の実施形態に係る検出装置の1画素あたりの断面図、及び、画素間の拡大図である。

【図9】本発明の第5の実施形態に係る検出装置の1画素あたりの断面図及び画素間の拡大図である。

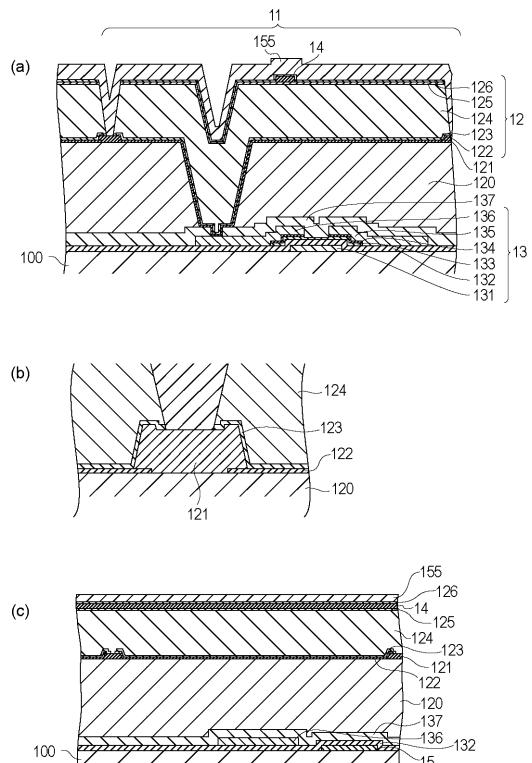

【図10】本発明の第5の実施形態に係る検出装置の製造方法を説明するためのマスクパターン及び断面図である。

40

【図11】本発明の第6の実施形態に係る検出装置の1画素あたりの断面図及び画素間の拡大図である。

【図12】本発明の第7の実施形態に係る検出装置の1画素あたりの平面図、及び、断面図である。

【図13】本発明の第7の実施形態に係る検出装置の製造方法を説明するためのマスクパターン及び断面図である。

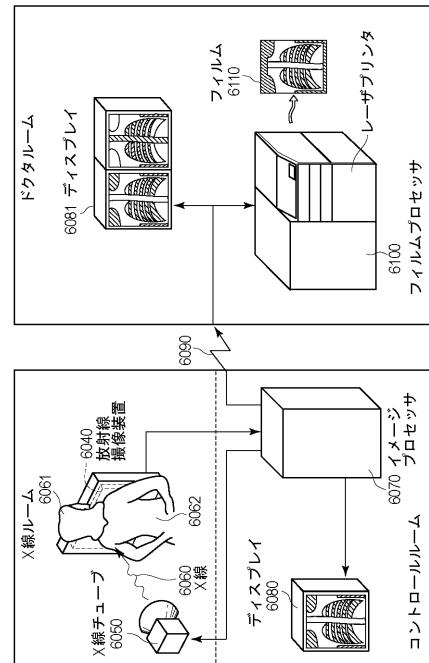

#### 【図14】本発明の検出装置を用いた放射線検出システムの概念図である。

#### 【発明を実施するための形態】

#### 【0011】

以下、本発明の実施形態について、添付の図面を参照して具体的に説明する。なお、本

50

願明細書において放射線は、放射線崩壊によって放出される粒子（光子を含む）の作るビームである 線、 線、 線などの他に、同程度以上のエネルギーを有するビーム、例えばX線や粒子線、宇宙線なども、含まれるものとする。

### 【0012】

#### （第1の実施形態）

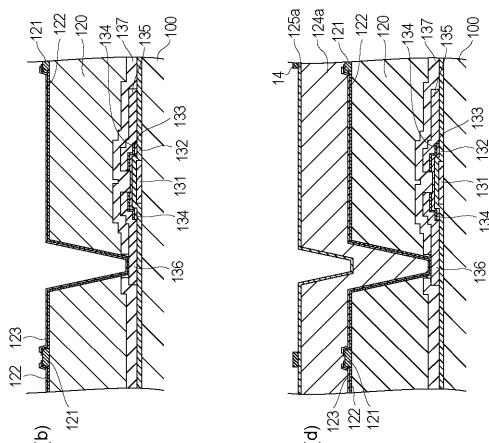

先ず、図1(a)～(d)を用いて本発明の第1の実施形態に係る検出装置の一画素の構成について説明する。図1(a)は1画素あたりの平面図である。なお、図1では、簡便化の為、変換素子については第1電極のみを示している。図1(b)は図1(a)のA-A'での断面図であり、図1(c)は画素端部(画素間)の拡大図であり、図1(d)は図1(a)のB-B'での断面図である。

10

### 【0013】

本発明の検出装置における1つの画素11は、放射線又は光を電荷に変換する変換素子12と、変換素子12の電荷に応じた電気信号を出力するスイッチ素子であるTFT(薄膜トランジスタ)13とを含む。変換素子12は、PIN型のフォトダイオードを用いている。変換素子12は、ガラス基板等の絶縁性の基板100の上に設けられたTFT13の上に層間絶縁層120を挟んで積層されて配置されている。

### 【0014】

TFT13は、基板100の上に、基板側から順に、制御電極131と、絶縁層132と、半導体層133と、半導体層133よりも不純物濃度の高い不純物半導体層134と、第1主電極135と、第2主電極136と、を含む。不純物半導体層134はその一部領域で第1主電極135及び第2主電極136と接しており、その一部領域と接する半導体層133の領域の間の領域が、TFTのチャネル領域となる。制御電極131は制御配線15と電気的に接合されており、第1主電極135は信号配線16と電気的に接合されており、第2主電極136は変換素子12の第1電極122と電気的に接合されている。なお、本実施形態では第1主電極135と第2主電極136と信号配線16とは、同じ導電層で一体的に構成されており、第1主電極135が信号配線16の一部をなしている。保護層137はTFT13、制御配線15、及び信号配線16を覆うように設けられている。本実施形態では、スイッチ素子として非晶質シリコンを主材料とした半導体層133及び不純物半導体層134を用いた逆スタガ型のTFTを用いたが、本発明はそれに限定されるものではない。例えば、多結晶シリコンを主材料としたスタガ型のTFTを用いたり、有機TFT、酸化物TFT等を用いたりすることができる。

20

### 【0015】

層間絶縁層120は、複数のTFT13を覆うように、基板100と後述する複数の第1電極122との間に配置されており、コンタクトホールを有している。変換素子12の第1電極122とTFT13の第2主電極136とが、層間絶縁層120に設けられたコンタクトホールにおいて、電気的に接合される。

30

### 【0016】

変換素子12は、層間絶縁層120の上に、層間絶縁層側から順に、第1電極122と、第1導電型の不純物半導体層123と、半導体層124と、第2導電型の不純物半導体層125と、第2電極126と、を含む。ここで、第1導電型の不純物半導体層123は、第1導電型の極性を示し、半導体層124及び第2導電型の不純物半導体層125よりも第1導電型の不純物の濃度が高いものである。また、第2導電型の不純物半導体層125は、第2導電型の極性を示し、第1導電型の不純物半導体層123及び半導体層124よりも第2導電型の不純物の濃度が高いものである。第1導電型と第2導電型とは互いに異なる極性の導電型であり、例えば第1導電型がn型であれば第2導電型はp型である。変換素子12の第2電極126には電極配線14が電気的に接合される。変換素子12の第1電極122は層間絶縁層120に設けられたコンタクトホールにおいて、TFT13の第2主電極136と電気的に接合される。なお、本実施形態では、非晶質シリコンを主材料とした第1導電型の不純物半導体層123、半導体層124、第2導電型の不純物半導体層125を用いたフォトダイオードを用いたが、本発明はこれに限定されるものでは

40

50

ない。例えば非晶質セレンを主材料とした第1導電型の不純物半導体層123、半導体層124、第2導電型の不純物半導体層125を用いた、放射線を直接電荷に変換する素子も用いることができる。

#### 【0017】

層間絶縁層120の上の複数の第1電極122の間には、無機材料からなる絶縁層121が層間絶縁層120に接して配置されている。そして、第1電極122と絶縁部材121とが、層間絶縁層120を覆うように層間絶縁層120の上に配置されている。そのため、不純物半導体層123となる不純物半導体膜を成膜する際に、層間絶縁層120が表面に露出されることが無く、不純物半導体層123への有機材料の混入が低減できる。また、本実施形態では、不純物半導体層123、半導体層124、及び不純物半導体層125が、絶縁部材121の上で画素ごとに分離されている。その分離のためのドライエッチング工程の際、絶縁部材121がエッチングストッパー層として働く為、層間絶縁層120がドライエッチングのスピーシーズに晒されることなく、有機材料による各層への汚染を防止することが可能となる。10

#### 【0018】

第1電極122には、ITO等の透明導電性酸化物が用いられる。透明導電性酸化物は、非晶質状態では、多結晶状態と比べて、著しくエッティングの速度高く、また、パターン制御性が高いといった特徴がある。その為、透明導電性酸化物の形成方法としては、まず、非晶質状態で成膜された透明導電性酸化物をエッティングした後、アニール工程により多結晶化させる方法が一般的である。このアニール工程において、透明導電性酸化物の内部応力が変化するため、膜密着性の観点で、透明導電性酸化物と接する下地の膜種が非常に重要となる。例えば、表面硬度が高く、結合エネルギーの高い無機材料からなる絶縁層上に、透明導電性酸化物を配置した場合、無機材料からなる絶縁層がITOの内部応力の変化による変形に追従できず、第1電極122が剥離する場合がある。一方、表面硬度が低く、結合エネルギーの弱い、有機材料からなる層間絶縁層120上に透明導電性酸化物を配置した場合、層間絶縁層120は無機材料からなる絶縁層よりも透明導電性酸化物の内部応力の変化による変形に追従できる。また、透明導電性酸化物の多結晶化の際のエネルギーにより、有機材料の結合が、多結晶化した透明導電性酸化物と再接合しなおすことでの、応力の変化に対応でき、第1電極122の剥離を低減できる。本実施形態では、第1電極122は70~180μmの幅を有して設けられており、その大部分が層間絶縁層120に接して配置されている為、第1電極122の剥離を低減できる。なお、本実施形態では、第1電極122は、その端約5μm程度が絶縁部材121の上に配置されている。この場合、第1電極122と絶縁部材121との間の密着力は低いが、第1電極122と層間絶縁層120とが接している幅に比べて非常に小さいため、第1電極122の剥離の問題は発生しない。2030

#### 【0019】

そして、変換素子12を覆うように、パッシベーション層155が設けられている。

#### 【0020】

次に、図2を用いて、本発明の第1の実施形態における検出装置の製造方法について説明する。特に層間絶縁層120にコンタクトホールを形成する工程からは、マスクパターンとプロセス中の断面図を用いて詳しく説明する。なお、図2の(a), (c), (e), (g), (i)は、それぞれ各工程で使用されるフォトマスクのマスクパターンの平面模式図である。また、図2の(b), (d), (f), (h), (j)は、それぞれ図1(a)のA-A'に対応する位置の各工程における断面模式図である。40

#### 【0021】

まず、絶縁性の基板100の上に、複数のTFT13が設けられており、複数のTFT13を覆うように保護層137が設けられている。保護層137には、第2主電極136上のフォトダイオードと電気的に接続する部分において、エッティングにより、コンタクトホールが設けられている。そして、図2(b)に示す工程では、TFT13及び保護層137を覆うように、スピナー等の塗布装置を用いて、感光性を有する有機材料であるアク50

リル樹脂を層間絶縁膜として成膜する。感光性を有する有機材料としては、他にもポリイミド樹脂等が使用可能である。そして、図2(a)に示すマスクを用いて、露光、現像処理によりコンタクトホールを有する層間絶縁層120を形成する。

#### 【0022】

次に、図2(d)に示す工程では、層間絶縁層120を覆うように、窒化シリコン膜や酸化シリコン等の一般的な無機材料からなる絶縁膜をプラズマCVD法により成膜する。そして、図2(c)に示すマスクを用いて絶縁膜をエッチングして、画素間に絶縁部材121を形成する。

#### 【0023】

次に、図2(f)に示す工程では、層間絶縁層120及び絶縁部材121を覆うように、スパッタリング法によりITOからなる非晶質な透明導電性酸化物膜を成膜する。そして、図2(e)に示すマスクを用いて透明導電性酸化物膜をウエットエッチングし、アニール処理により多結晶化して、変換素子の第1電極122を形成する。この際、層間絶縁層120は、複数の絶縁部材121と複数の第1電極122によって、表面が覆われることとなる。また、この多結晶化によって、第1電極122の内部応力が増加するが、第1電極122の大部分が層間絶縁層120に接して形成される為、密着性が保たれ、第1電極122の剥離の問題は生じない。なお、ここでは透明導電性酸化物として、ITOを用いたが、その他、ZnO、SnO<sub>2</sub>、ATO、AZOや、CdIn<sub>2</sub>O<sub>4</sub>、MgIn<sub>2</sub>O<sub>4</sub>、ZnGa<sub>2</sub>O<sub>4</sub>、InGaZnO<sub>4</sub>も好適に用いられる。また、CuAlO<sub>2</sub>等のCuを含むデラフォサイト型などの非晶質状態をとり得る透明導電性酸化物も好適に用いられる。

#### 【0024】

次に、図2(h)に示す工程では、絶縁層121及び第1電極122を覆うように、第1導電型の不純物半導体膜123'をしてリン等の5価の元素を不純物として混入した非晶質シリコン膜をプラズマCVD法により成膜する。次いで、非晶質シリコン膜からなる半導体膜124'、と、第2導電型の不純物半導体膜125'をしてボロン等の3価の元素を不純物として混入した非晶質シリコン膜と、をプラズマCVD法によりこの順に成膜する。不純物半導体膜123'の成膜に際して、層間絶縁層120が絶縁部材121と第1主電極122によって覆われていない場合、層間絶縁層120がプラズマに晒されてしまう。有機材料からなる層間絶縁層120がこのプラズマに晒されると、有機材料が飛散して不純物半導体膜123'に混入する場合がある。そこで、本実施形態では、層間絶縁層120を絶縁部材121と第1主電極122とで覆い、第1導電型の不純物半導体層123となる不純物半導体膜123'の成膜時に層間絶縁層120の表面が露出しない構造としている。それにより、有機材料が飛散して第1導電型の不純物半導体膜へ混入することを防止することができる。次に、不純物半導体膜125'を覆うように、スパッタリング法により電極配線14となるAl等の導電膜を成膜する。そして、図2(g)に示すマスクを用いて導電膜をウエットエッチングして、電極配線14を形成する。

#### 【0025】

次に、図2(j)に示す工程では、不純物半導体膜125'及び電極配線14を覆うように、スパッタリング法により透明導電性酸化物膜を成膜する。次に、図2(i)に示すマスクを用いて透明導電性酸化物膜をウエットエッチングして、変換素子12の第2電極126を形成する。そして、同じ図2(i)に示すマスクを用いて不純物半導体膜125'と半導体膜124'、と不純物半導体膜123'とをドライエッティングにより一部を除去することにより、1画素ごとに変換素子12を素子分離する。素子分離された変換素子12には、不純物半導体層125'、半導体層124'、不純物半導体層123'が形成される。このドライエッティングによる画素分離は、絶縁部材121の上で行われる。その為、絶縁部材121がエッティングストッパー層として機能し、ドライエッティングのスピーシーズに層間絶縁層120が晒されることなく、有機材料による各層への汚染を防止することが可能となる。また、第1電極122は不純物半導体層123によって覆われた形状となる。そのため、第1電極122と半導体層124と直接接合するショットキー接合を持たない

10

20

30

40

50

構成となる。なお、本実施形態では、第2電極126の材料として透明導電性酸化物を用いたが、本発明はそれに限定されるものではなく、導電膜であればよい。例えば、変換素子として放射線を直接電荷に変換する素子を用いる場合には、A1等の放射線を透過しやすい導電膜を用いることができる。

#### 【0026】

そして、変換素子12及び絶縁部材121を覆うように、パッシベーション層155を形成し、図1(b)に示す構成が得られる。このパッシベーション層155の形成時においても、層間絶縁層120が露出しない構造となっているので、有機材料による各層への汚染することを防止することができる。

#### 【0027】

なお、本実施形態では、図2(j)に示す工程で、ドライエッチングにより、1画素ごとに変換素子12の素子分離を行っているが、電極配線14がエッチングのマスクとなってしまう。そのため、図1(d)で示すように、電極配線14の正射影が位置する不純物半導体膜125'、と半導体膜124'、と不純物半導体膜123'は除去されずに残存する。したがって、電極配線14の正射影が位置する領域の不純物半導体層123が隣接する画素の第1電極122間でつながった構造となる。このような構造でも不純物半導体層123の抵抗が絶縁体とみなせるほど十分高い場合には、不純物半導体層123は電気的に1画素ごとに分離されることとなり、問題なく動作させることが可能である。十分高い不純物半導体層123を得るためにには、膜厚やドープ量を適正化する必要がある。

#### 【0028】

次に、図3を用いて本発明の第1の実施形態に係る検出装置の概略的等価回路を説明する。なお、図3では説明の簡便化のため3行3列の等価回路図を用いたが、本発明はそれに限定されるものではなく、検出装置はn行m列(n, mはいずれも2以上の自然数)の画素アレイを有する。本実施形態における検出装置は、基板100の表面上に、行方向及び列方向に配列された複数の画素1を含む変換部3が設けられている。各画素1は、放射線又は光を電荷に変換する変換素子12と、変換素子12の電荷に応じた電気信号を出力するTFT13と、を含む。変換素子の第2電極126側の表面に、放射線を可視光に波長変換するシンチレータ(不図示)が配置されてもよい。電極配線14は、列方向に配列された複数の変換素子12の第2電極126に共通に接続される。制御配線15は、行方向に配列された複数のTFT13の制御電極131に共通に接続され、駆動回路2に電気的に接続される。駆動回路2が列方向に複数配列された制御配線15に駆動パルスを順次に又は同時に供給することにより、行単位で画素からの電気信号が、行方向に配列された複数の信号配線16に並列に出力される。信号配線16は、列方向に配列された複数のTFT13の第1主電極135に共通に接続され、読出回路4に電気的に接続される。読出回路4は、信号配線16毎に、信号配線16からの電気信号を積分して増幅する積分增幅器5と、積分增幅器5で増幅して出力された電気信号をサンプルホールドするサンプルホールド回路6を備える。読出回路4は更に、複数のサンプルホールド回路6から並列に出力される電気信号を直列の電気信号に変換するマルチプレクサ7と、出力された電気信号をデジタルデータに変換するA/D変換器8を含む。積分增幅器5の非反転入力端子には電源回路9から基準電位Vrefが供給される。電源回路9は更に、行方向に配列された複数の電極配線14に電気的に接続されており、変換素子12の第2電極126にバイアス電位Vsを供給する。

#### 【0029】

以下に、本実施形態の検出装置の動作について説明する。変換素子12の第1電極122にはTFT13を介して基準電位Vrefを与え、第2電極125には、放射線又は可視光によって発生した電子正孔対分離に必要なバイアス電位Vsを与える。この状態で、被検体を透過した放射線又はそれに応じた可視光が変換素子12に入射し、電荷に変換され変換素子12に蓄積される。この電荷に応じた電気信号は、駆動回路2から制御配線15に印加される駆動パルスによりTFT13が導通状態となることで、信号配線16に出力され、読出回路4によりデジタルデータとして外部に読み出される。

10

20

30

40

50

**【0030】**

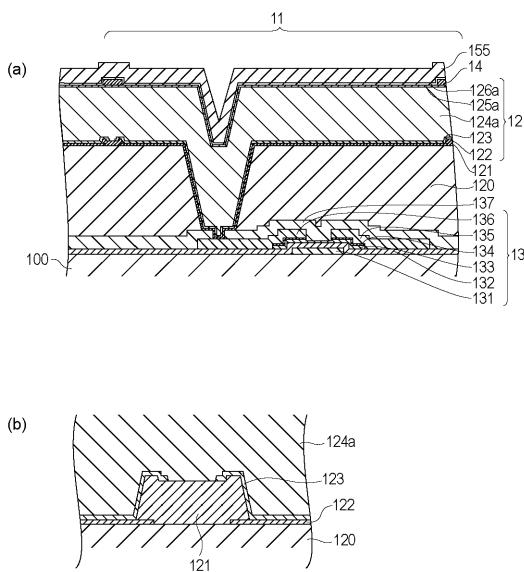

(第2の実施形態)

次に、図4(a)～(c)を用いて本発明の第1の実施形態に係る検出装置の一画素の構成について説明する。図4(a)は図1(a)のA-A'での断面図であり、図4(b)は画素端部(画素間)の拡大図であり、図4(c)は図1(a)のB-B'での断面図である。また、第1の実施形態で説明したものと同じものは同じ番号を付与し、詳細な説明は割愛する。

**【0031】**

第1の実施形態では、図1(d)のように、電極配線14の正射影が位置する領域の不純物半導体層123が隣接する画素の第1電極122間でつながった構造となっていた。一方、本実施形態では、不純物半導体膜123'を成膜後に、不純物半導体層123の形成を行っている。このため、図4(c)のように、画素間で不純物半導体層123が分離された画素を得ることができる。

10

**【0032】**

次に、図5を用いて、本発明の第2の実施形態における検出装置の製造方法を説明する。なお、図5の(a),(c),(e)は、それぞれ各工程で使用されるフォトマスクのマスクパターンの平面模式図である。また、図5の(b),(d),(f)は、それぞれ図1(a)のA-A'に対応する位置の各工程における断面模式図である。なお、第1の実施形態で説明したものと同じ工程については、詳細な説明は割愛する。特に、第1電極122を形成する工程までは、図2(a)～(f)を用いて説明したものと同様であるため、それ以降の工程について説明する。

20

**【0033】**

まず、図5(b)に示す工程では、絶縁層121及び第1電極122を覆うように、第1導電型の不純物半導体膜123'をしてリン等の5価の元素を不純物として混入した非晶質シリコン膜をプラズマCVD法により成膜する。不純物半導体膜123'の成膜に際して、層間絶縁層120が絶縁層121と第1主電極122によって覆われていない場合、層間絶縁層120がプラズマに晒されてしまう。有機材料からなる層間絶縁膜120がこのプラズマに晒されると、有機材料が飛散して不純物半導体膜123'に混入する場合がある。そこで、本実施形態では、層間絶縁層120を絶縁層121と第1主電極122とで覆い、第1導電型の不純物半導体層123となる不純物半導体膜123'の成膜時に層間絶縁層120の表面が露出しない構造としている。それにより、有機材料が飛散して第1導電型の不純物半導体膜へ混入することを防止することができる。そして、図5(a)に示すマスクを用いて不純物半導体膜をドライエッチングして、不純物半導体層123を形成する。このドライエッチングによる画素分離は、絶縁層121の上で行われる。その為、絶縁層121がエッチングストッパー層として機能し、ドライエッチングのスピーザーズに層間絶縁層120が晒されることなく、有機材料による不純物半導体層123への汚染を防止することが可能となる。また、第1電極122は不純物半導体層123によって覆われた形状とする。

30

**【0034】**

次に、図5(d)に示す工程では、絶縁層121及び、不純物半導体層123を覆うように、非晶質シリコン膜からなる半導体膜124'、と、第2導電型の不純物半導体膜125'をしてボロン等の3価の元素を不純物として混入した非晶質シリコン膜と、をプラズマCVD法によりこの順に成膜する。次に、不純物半導体膜125'を覆うように、スパッタリング法により電極配線14となるA1等の導電膜を成膜する。そして、図5(c)に示すマスクを用いて導電膜をウエットエッチングして、電極配線14を形成する。

40

**【0035】**

次に、図5(f)に示す工程では、不純物半導体膜125'及び共通電極配線14を覆うように、スパッタリング法により透明導電性酸化物膜を成膜する。次に、図5(e)に示すマスクを用いて透明導電性酸化物膜をウエットエッチングして、変換素子12の第2電極126を形成する。そして、同じ図5(e)に示すマスクを用いて不純物半導体膜1

50

25' と半導体膜 124' とをドライエッティングにより除去することにより、1画素ごとに変換素子 12 を素子分離する。素子分離された変換素子 12 には、不純物半導体層 125、半導体層 124、不純物半導体層 123 が形成される。このドライエッティングによる画素分離は、絶縁層 121 の上で行われる。その為、絶縁層 121 がエッティングストップ一層として機能し、ドライエッティングのスピーシーズに層間絶縁層 120 が晒されることなく、有機材料による各層への汚染を防止することが可能となる。また、第 1 電極 122 は不純物半導体層 123 によって覆われた形状となっているため、第 1 電極 122 と半導体層 124 と直接接合するショットキー接合を持たない構成となる。なお、本実施形態では、第 2 電極 126 の材料として透明導電性酸化物を用いたが、本発明はそれに限定されるものではなく、導電膜であればよい。例えば、変換素子として放射線を直接電荷に変換する素子を用いる場合には、A1 等の放射線を透過しやすい導電膜を用いることができる。

10

#### 【0036】

そして、変換素子 12 及び絶縁層 121 を覆うように、パッシベーション層 155 を形成し、図 4 (a)、及び図 4 (c) に示す構成が得られる。このパッシベーション層 155 の形成時においても、層間絶縁層 120 が露出しない構造となっているので、有機材料による各層への汚染することを防止することができる。

#### 【0037】

また、本実施形態では、図 5 (b) に示す工程で、図 5 (a) に示すマスクを用いて、個別化された不純物半導体層 123 の形成を行ったが、図 5 (a) の代わりに図 5 (g) に示すマスクを用いて、不純物半導体膜 123' の除去を行ってもよい。図 5 (g) に示す部分の不純物半導体膜 123' をあらかじめ除去して、図 5 (f) に示す工程で、図 5 (e) に示すマスクを用いて、不純物半導体膜 125' と、半導体膜 124' と、不純物半導体膜 123' とをドライエッティングにより除去する。このことにより、不純物半導体層 123 が 1 画素ごとに分離された変換素子 12 を得ることができる。また、図 5 (g) のようなマスク用いることで、図 5 (f) に示す工程でのドライエッティングのみでほぼ第 1 の不純物半導体層 123 の面積が決まる。そのため、不純物半導体膜 123' のドライエッティング工程と半導体膜 124' のドライエッティング工程との重ね合わせを考慮する必要のある図 5 (a) のマスクを使用するよりも、不純物半導体膜 123' の面積を大きくすることができる。

20

30

#### 【0038】

##### (第 3 の実施形態)

次に、図 6 (a) ~ 図 6 (c) を用いて本発明の第 3 の実施形態に係る検出装置の一画素の構成について説明する。図 6 (a) は図 1 (a) の A - A' での断面図であり、図 6 (b) は画素端部(画素間)の拡大図であり、図 6 (c) は図 1 (a) の B - B' での断面図である。また、先の実施形態で説明したものと同じものは同じ番号を付与し、詳細な説明は割愛する。

#### 【0039】

第 1 の実施形態では、第 1 電極 122 の端が絶縁部材 121 の上に配置されているのにに対し、本実施形態では、第 1 電極 122 の端が層間絶縁層 120 と絶縁部材 121 との間に配置されている。この構成により、透明導電性酸化物からなる第 1 電極 122 の全体が層間絶縁層 120 の上部のみに配置されることとなり、実施形態 1 に比べて層間絶縁層 120 と第 1 電極 122 の密着性をより高くできる。

40

#### 【0040】

次に、図 7 を用いて、本発明の第 3 の実施形態における検出装置の製造方法を説明する。特に層間絶縁層コンタクトホール形成からの工程については、マスクパターンとプロセス中の断面図を用いて詳細に説明する。なお、図 7 の (a), (c), (e), (g), (i) は、それぞれ各工程で使用されるフォトマスクのマスクパターンの平面模式図である。また、図 7 の (b), (d), (f), (h), (j) は、それぞれ図 1 (a) の A - A' に対応する位置の各工程における断面模式図である。なお、先の実施形態で説明し

50

たものと同じ工程については、詳細な説明は割愛する。

#### 【0041】

まず、図7(b)に示す工程では、TFT13及び保護層137を覆うように、感光性を有する有機材料であるアクリル樹脂を層間絶縁膜として成膜する。そして、図7(a)に示すマスクを用いて、コンタクトホールを有する層間絶縁層120を形成する。

#### 【0042】

次に、図7(d)に示す工程では、層間絶縁層120を覆うように、スパッタリング法によりITOからなる非晶質透明導電性酸化物膜を成膜する。そして、図7(c)に示すマスクを用いて、透明導電性酸化物膜をウエットエッチングし、アニール処理により多結晶化して、変換素子の第1電極122を形成する。この多結晶化によって、第1電極122の内部応力が増加するが、第1電極122の全体が層間絶縁層120に接して形成される為、密着性が保たれ、第1電極122の剥離の問題は生じない。

10

#### 【0043】

次に、図7(f)に示す工程では、層間絶縁層120及び第1電極122を覆うように、窒化シリコン膜等の無機材料からなる絶縁膜をプラズマCVD法により成膜する。そして、図7(e)に示すマスクを用いて絶縁膜をエッチングして、画素間に絶縁部材121を形成する。この際、層間絶縁層120は、絶縁部材121と第1電極122によって、表面が覆われることとなる。

#### 【0044】

次に、図7(h)に示す工程では、絶縁部材121及び第1電極122を覆うように、第1導電型の不純物半導体膜123'をしてリン等の5価の元素を不純物として混入した非晶質シリコン膜をプラズマCVD法により成膜する。次いで、非晶質シリコン膜からなる半導体膜124'、第2導電型の不純物半導体膜125'をしてボロン等の3価の元素を不純物として混入した非晶質シリコン膜と、をプラズマCVD法によりこの順に成膜する。本実施形態では、層間絶縁層120を絶縁部材121と第1主電極122とで覆い、第1導電型の不純物半導体層123となる不純物半導体膜123'の成膜時に層間絶縁層120の表面が露出しない構造としている。それにより、有機材料が飛散して第1導電型の不純物半導体膜へ混入することを防止することができる。次に、不純物半導体膜125'を覆うように、スパッタリング法により電極配線14となるA1等の導電膜を成膜する。そして、図7(g)に示すマスクを用いて導電膜をウエットエッチングして、電極配線14を形成する。

20

30

#### 【0045】

次に、図7(j)に示す工程では、不純物半導体膜125'及び電極配線14を覆うように、スパッタリング法により透明導電性酸化物膜を成膜する。次に、図7(i)に示すマスクを用いて透明導電性酸化物をウエットエッチングにより除去して、第2電極126を形成する。そして、同じ図7(i)に示すマスクを用いて、不純物半導体膜125'と半導体膜124'、不純物半導体膜123'とドライエッティングにより一部を除去することにより、1画素ごとに変換素子12を素子分離する。素子分離された変換素子12には、不純物半導体層125、半導体層124、不純物半導体層123が形成される。このドライエッティングによる画素分離は、絶縁部材121の上で行われる。その為、絶縁部材121がエッティングストッパー層として機能し、ドライエッティングのスピーシーズに層間絶縁層120が晒されることなく、有機材料による各層への汚染を防止することができる。

40

#### 【0046】

そして、変換素子12及び絶縁部材121を覆うように、パッシベーション層155を形成し、図6(a)に示す構成が得られる。このパッシベーション層155の形成時においても、層間絶縁層120が露出しない構造となっているので、有機材料による各層への汚染することを防止することができる。

#### 【0047】

なお、本実施形態においても、電極配線14の正射影が位置する領域の不純物半導体層

50

123が隣接する画素の第1電極122間でつながった構造となる。このような構造でも、不純物半導体層123の抵抗が絶縁体とみなせるほど高い場合には、不純物半導体層123は電気的に1画素ごとに分離されることとなり、問題なく動作させることができる。

#### 【0048】

##### (第4の実施形態)

次に、本発明の第4の実施形態に係る検出装置の一画素の構成について説明する。図8(a)は図1(a)のA-A'での断面図であり、図8(b)は画素端部(画素間)の拡大図であり、図8(c)は図1(a)のB-B'での断面図である。なお、第3の実施形態で説明したものと同じものは同じ番号を付与し、詳細な説明は割愛する。

10

#### 【0049】

第3の実施形態では、図6(c)のように、電極配線14の正射影が位置する領域の不純物半導体層123が隣接する画素の第1電極122間でつながった構造となっていた。一方、本実施形態では、第2の実施形態と同様に、不純物半導体膜123'を成膜後に、不純物半導体層123の形成を行っている。そのため、図8(c)のように、画素間で不純物半導体層123が分離された画素を得ることができる。

#### 【0050】

なお、本実施形態の製造方法は、絶縁部材121を形成するまでの工程は、第3の実施形態で説明した図7(b), (d), (f)に示す工程と同様であり、不純物半導体層123を形成する工程からは、第2の実施形態で説明した工程と同様である。そのため、本実施形態における製造方法の詳細な説明は割愛する。

20

#### 【0051】

##### (第5の実施形態)

次に、図9(a)～(c)を用いて本発明の第3の実施形態に係る検出装置の一画素の構成について説明する。図9(a)は図1(a)のA-A'での断面図であり、図9(b)は画素端部(画素間)の拡大図である。また、図9(c)は画素端部(画素間)の他の例を示す拡大図である。なお、先の実施形態で説明したものと同じものは同じ番号を付与し、詳細な説明は割愛する。

#### 【0052】

第1の実施形態では、半導体層124、不純物半導体層125、及び第2電極126が画素毎に分離されている。それに対し、本実施形態では、図9(a)のように、半導体層124a、不純物半導体層125a、及び第2電極126aが画素毎に分離されていない。一方、第1電極122及び不純物半導体層123は画素毎に分離されているため、変換素子12は第1電極122毎に個別化されることとなる。そのため、本実施形態の構成では、第1の実施形態の構成に比べて開口率を大きくすることが可能となる。ここで、第1電極122毎に個別化を更に確実なものとするために、図9(c)に示すように、半導体層124aよりも水素濃度の高い半導体層160を、絶縁部材121と不純物半導体層123とを覆うように5nm程度の非常に薄い厚さで設けることが好ましい。この半導体層160は、半導体層124aや不純物半導体層123に比べて比抵抗が高いため、隣接する画素間でのリークを低減することが可能となる。そして、半導体層160の膜厚を、トンネル効果が可能な厚さとすることで、不純物半導体層123と半導体層124aとの間では電荷の移動が可能となり、変換素子12はフォトダイオードとして機能できる。また、第2電極126aが画素毎に分離されていないため、開口率を低下させる電極配線14は設けなくてもよい。ただし、第2電極126aだけでは抵抗が高い場合には、電極配線14を設ける方がより好ましい。その場合、半導体層124aや第2電極126aを画素毎に分離していないため、電極配線14の正射影が絶縁部材121と重なる位置に配置することができ、開口率を低下させることなく電極配線14を設けることができる。

30

40

#### 【0053】

次に、図10を用いて、本発明の第5の実施形態における検出装置の製造方法を説明する。なお、図10の(a), (c)は、それぞれ各工程で使用されるフォトマスクのマス

50

クパターンの平面模式図である。また、図10の(b), (d)は、それぞれ図1(a)のA-A'に対応する位置の各工程における断面模式図である。なお、第1の実施形態で説明したものと同じ工程については、詳細な説明は割愛する。特に、第1電極122を形成する工程までは、図2(a)~(f)を用いて説明したものと同様であるため、それ以降の工程について説明する。

#### 【0054】

まず、図10(b)に示す工程では、絶縁部材121及び第1電極122を覆うように、第1導電型の不純物半導体膜123'をしてリン等の5価の元素を不純物として混入した非晶質シリコン膜をプラズマCVD法により成膜する。本実施形態では、層間絶縁層120を絶縁部材121と第1主電極122とで覆い、第1導電型の不純物半導体層123となる不純物半導体膜123'の成膜時に層間絶縁層120の表面が露出しない構造としている。それにより、有機材料が飛散して第1導電型の不純物半導体膜へ混入することを防止することができる。そして、図10(a)に示すマスクを用いて、不純物半導体膜123'をドライエッチングにより一部を除去することにより、不純物半導体層123を形成する。このドライエッチングによる画素分離は、絶縁部材121の上で行われる。その為、絶縁部材121がエッチングストッパー層として機能し、ドライエッチングのスピーキーズに層間絶縁層120が晒されることなく、有機材料による不純物半導体層123への汚染を防止することが可能となる。

#### 【0055】

次に、図10(d)に示す工程では、絶縁部材121及び不純物半導体層123を覆うように、半導体層124aとなる非晶質シリコン膜をプラズマCVD法により成膜する。次いで、第2導電型の不純物半導体層125aとなるボロン等の3価の元素を不純物として混入した非晶質シリコン膜をプラズマCVD法により成膜する。ここで、図9(c)に示す半導体層160を設ける場合には、非晶質シリコン膜の成膜に際して、最初に水素濃度の高くして非晶質シリコン膜を5nm程度の厚さで成膜し、次いで水素濃度を下げて非晶質シリコン膜を成膜するとよい。次に、不純物半導体層125を覆うように、スパッタリング法により電極配線14となるA1等の導電膜を成膜する。そして、図10(c)に示すマスクを用いて導電膜をウエットエッチングして、電極配線14を形成する。

#### 【0056】

次に、不純物半導体膜125'及び電極配線14を覆うように、スパッタリング法により透明導電性酸化物からなる第2電極126aを成膜する。そして、第2電極126aを覆うように、パッシベーション層155を形成し、図9(a)に示す構成が得られる。

#### 【0057】

##### (第6の実施形態)

次に、図11(a)及び図11(b)を用いて本発明の第4の実施形態に係る検出装置の一画素の構成について説明する。図11(a)は図1(a)のA-A'の断面図であり、図11(b)は画素端部(画素間)の拡大図である。なお、先の実施形態で説明したものと同じものは同じ番号を付与し、詳細な説明は割愛する。

#### 【0058】

第3の実施形態では、半導体層124、不純物半導体層125、及び第2電極126が画素毎に分離されている。それに対し、本実施形態では、図11(a)のように、半導体層124a、不純物半導体層125a、及び第2電極126aが画素毎に分離されていない。一方、第1電極122及び不純物半導体層123は画素毎に分離されているため、変換素子12は第1電極122毎に個別化されることとなる。そのため、本実施形態の構成では、第2の実施形態の構成に比べて開口率を大きくすることが可能となる。また、第2電極126aが画素毎に分離されていないため、開口率を低下させる電極配線14は設けなくてもよい。ただし、第2電極126aだけでは抵抗が高い場合には、電極配線14を設ける方がより好ましい。その場合、半導体層124aや第2電極126aを画素毎に分離していないため、電極配線14の正射影が絶縁部材121と重なる位置に配置することができ、開口率を低下させることなく電極配線14を設けることができる。

10

20

30

40

50

**【0059】**

なお、本実施形態の製造方法は、絶縁層121を形成するまでの工程は、第3の実施形態で説明した図7(b), (d), (f)に示す工程と同様であり、不純物半導体層123を形成する工程からは、第5の実施形態で説明した工程と同様である。そのため、本実施形態における製造方法の詳細な説明は割愛する。

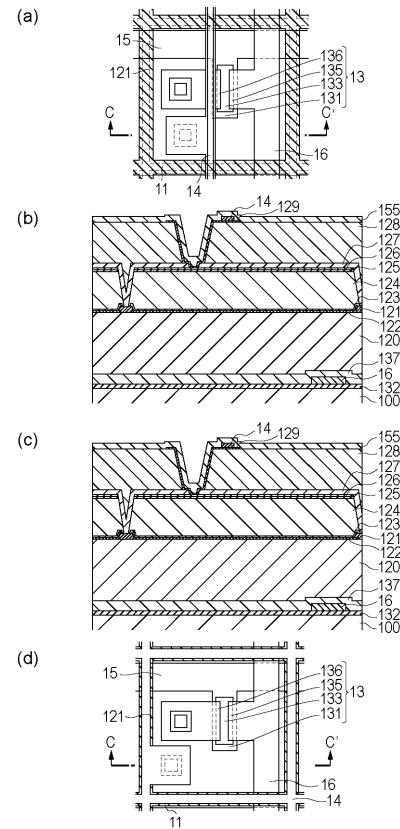

**【0060】****(第7の実施形態)**

次に、図12(a)及び図12(b)を用いて本発明の第7の実施形態に係る検出装置の1画素の構成について説明する。図12(a)は一画素あたりの平面図であり、図12(b)は図12(a)のC-C'での断面図である。なお、先の実施形態で説明したものと同じものは、同じ番号を付与し、詳細な説明は割愛する。

10

**【0061】**

先の実施形態では、変換素子12の第2電極126上に電極配線14が直接接続されている。それに対し、本実施形態では、図12(b)のように、第2電極126上の絶縁層127及び、層間絶縁層128のコンタクトホールを介して電極配線14が電気的に接続されている。このような構造とすることで、まず変換素子12を形成した後に、電極配線14を形成することが可能となる。第2の実施形態や第4の実施形態では、変換素子12を形成する際に、第1導電型の不純物半導体層123を形成した後、半導体層124と第2の不純物半導体膜125を形成するという2工程で、変換素子の個別化を行っている。それに対し、本実施形態では、不純物半導体膜123'、半導体膜124'、不純物半導体膜125'を連続して成膜し、連続してドライエッチングして、変換素子を個別化することが可能となる。不純物半導体膜123'、半導体膜124'、不純物半導体膜125'を連続して成膜することで、不純物半導体層123と半導体層124の間及び半導体層124と不純物半導体層125の間の界面の結晶状態が良好な変換素子を得ることができる。

20

**【0062】**

次に、図13を用いて、本発明の第7の実施形態における検出装置の製造方法を説明する。なお、図13(a), (c), (e), (g), (i)は、各工程で使用されるフォトマスクのマスクパターンの平面模式図である。また図13(b), (d), (f), (h), (j)はそれぞれ図12(a)のC-C'に対応する位置の各工程における断面模式図である。なお、先の実施形態で説明したものと同じ工程については、詳細な説明は割愛する。特に、第1電極122を形成する工程までは、図2(a)~(f)を用いて説明したものと同様であるため、それ以降の工程について説明する。

30

**【0063】**

まず図13(b)に示す工程では、絶縁層121及び第1電極122を覆うように、第1導電型の不純物半導体膜123'をしてリン等の5価の元素を不純物として混入した非晶質シリコン膜をプラズマCVD法により成膜する。次いで、非晶質シリコン膜からなる半導体膜124'、第2導電型の不純物半導体膜125'をしてボロン等の3価の元素を不純物として混入した非晶質シリコン膜と、をプラズマCVD法によりこの順に成膜する。本実施形態では、層間絶縁層120を絶縁層121と第1主電極122とで覆い、第1導電型の不純物半導体層123となる不純物半導体膜123'の成膜時に層間絶縁層120の表面が露出しない構造としている。それにより、有機材料が飛散して第1導電型の不純物半導体膜へ混入することを防止することができる。次に、不純物半導体膜125'を覆うように、スパッタリング法により透明導電性酸化物を成膜する。次に、図13(a)に示すマスクを用いて透明導電性酸化物をウエットエッチして、第2の電極126を形成する。そして、同じ図13(a)に示すマスクを用いて、不純物半導体膜125'、半導体膜124'、不純物半導体膜123'をドライエッチングにより除去することにより、1画素ごとに変換素子12を素子分離する。素子分離された変換素子12には、不純物半導体層125、半導体層124、不純物半導体層123が形成される。

40

**【0064】**

50

次に、図13(d)に示す工程では、変換素子12及び、絶縁層121を覆うように、窒化シリコン膜等の無機材料からなる絶縁膜をプラズマCVD法により成膜する。この絶縁膜の成膜時においても、層間絶縁層120が露出しない構造となっているので、有機材料による各層への汚染することを防止することができる。そして、図13(c)に示すマスクを用いて、絶縁膜をドライエッチングして、絶縁層127を形成する。

#### 【0065】

次に、図13(f)に示す工程では、電極126及び、絶縁層127を覆うように、感光性を有する有機材料であるアクリル樹脂を層間絶縁層として成膜する。そして、図13(e)に示すマスクを用いてコンタクトホールを有する層間絶縁層128を形成する。

#### 【0066】

次に、図13(h)に示す工程では、スパッタリング法により透明導電性酸化物を成膜する。次に、図13(g)に示すマスクを用いて透明導電性酸化物をウエットエッチして、導電層129を形成する。

#### 【0067】

次に、図13(j)に示す工程では、スパッタリング法により電極配線14となるA1等の導電膜を成膜する。そして、図13(i)に示すマスクを用いて導電膜をウエットエッチングして、電極配線14を形成する。この工程により、電極配線14と変換素子12の第2電極126が導電層129によって、電気的に接続される。この際、導電層129を透明導電性酸化物によって形成することにより、開口率の低下を抑制ことができる。

#### 【0068】

そして、電極配線14、導電層129、及び、層間絶縁層128を覆うように、パッジベーション層155を形成し、図12(b)に示す構成が得られる。

#### 【0069】

また、本実施形態では、画素間の構造が第2の実施形態と同様の例を示したが、当然、第4の実施形態と同様の構造でも問題ない。この場合、図12(a)-C-C'での断面図は、図12(c)のような構造となる。

#### 【0070】

また、図12(d)のように、電極配線14を画素間に配置することも可能である。この場合、A1等で形成される電極配線14が画素間に配置されるため、開口率の低下させることなく電極配線14設けることができる。また、この電極配線14がグリッドの機能も果たすため、MTFを増加させることができる。また、バイアス電位Vsを画面内の上下方向のみからではなく左右からも供給することができるため、バイアス電位供給遅延による画像ムラ等の発生を防止することができる。

#### 【0071】

##### (応用実施形態)

次に、図14を用いて、本発明の検出装置を用いた放射線検出システムを説明する。

#### 【0072】

放射線源であるX線チューブ6050で発生したX線6060は、患者あるいは被験者6061の胸部6062を透過し、放射線検出装置6040に含まれる変換部3の各変換素子12に入射する。この入射したX線には患者6061の体内部の情報が含まれている。X線の入射に対応して変換部3で放射線を電荷に変換して、電気的情報を得る。この情報はデジタルデータに変換され信号処理手段となるイメージプロセッサ6070により画像処理され制御室の表示手段となるディスプレイ6080で観察できる。

#### 【0073】

また、この情報は電話回線6090等の伝送処理手段により遠隔地へ転送でき、別の場所のドクタールームなど表示手段となるディスプレイ6081に表示もしくは光ディスク等の記録手段に保存することができ、遠隔地の医師が診断することも可能である。また記録手段となるフィルムプロセッサ6100により記録媒体となるフィルム6110に記録することもできる。

#### 【符号の説明】

10

20

30

40

50

## 【0074】

- 1 1 画素

- 1 2 変換素子

- 1 3 スイッチ素子

- 1 4 電極配線

- 1 5 制御配線

- 1 6 信号配線

- 1 0 0 基板

- 1 2 0 層間絶縁層

- 1 2 1 絶縁部材

- 1 2 2 第1電極

- 1 2 3 第1導電型の不純物半導体層

- 1 2 4 半導体層

- 1 2 5 第2導電型の不純物半導体層

- 1 2 6 第2電極

- 1 5 5 保護層

10

## 【図1】

## 【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【 図 1 2 】

【図13】

【 図 1 4 】

---

フロントページの続き

(72)発明者 渡辺 実

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 大藤 将人

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 横山 啓吾

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 川鍋 潤

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 和山 弘

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 安田 雅彦

(56)参考文献 特開2008-244445(JP,A)

特開2004-265934(JP,A)

特開2009-267326(JP,A)

特開2012-074625(JP,A)

米国特許出願公開第2010/0320556(US,A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 27/14 - 148

H 01 L 31/08

H 04 N 5/32

G 01 T 1/20