## (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

HO1L 23/12 (2006.01) HO1L 21/02 (2006.01) **H01L 21/3105** (2006.01) **H01L 21/56** (2006.01) **H01L 21/762** (2006.01)

(52) CPC특허분류

**H01L 23/12** (2013.01) H01L 21/02527 (2013.01)

(21) 출원번호 10-2018-0005704

(22) 출원일자 2018년01월16일

> 심사청구일자 없음

(30) 우선권주장

1020170124569 2017년09월26일 대한민국(KR)

(11) 공개번호

(43) 공개일자 2019년04월03일

(71) 출원인

한국전자통신연구원

대전광역시 유성구 가정로 218 (가정동)

10-2019-0035453

(72) 발명자

이형석

대전광역시 서구 둔산1동 목련아파트304동 1306

김진식

대전광역시 유성구 엑스포로 448 205동 1505호

배성범

대전시 유성구 지족로 343 반석마을 205동 901호

(74) 대리인

특허법인 고려

전체 청구항 수 : 총 20 항

## (54) 발명의 명칭 **반도체 장치 및 이의 제조 방법**

## (57) 요 약

본 발명은 반도체 장치 및 이의 제조 방법을 제공한다. 이 반도체 장치는, 제 1 영역과 제 2 영역을 포함하는 방 열판; 상기 방열판의 상기 제 1 영역에 배치되는 제 1 소자; 및 상기 방열판의 상기 제 2 영역에 배치되는 제 2 소자를 포함하되, 상기 제 1 소자는 제 1 기판을 포함하고, 상기 제 2 소자는 제 2 기판을 포함하고, 상기 제 1 기판은 상기 제 2 기판과 서로 다른 물질을 포함하고, 상기 제 1 기판은 상기 방열판과 접하며, 상기 제 2 소자 는 상기 방열판에 플립 칩 본딩 방식으로 본딩된다.

## 대 표 도 - 도1

200

## (52) CPC특허분류

HO1L 21/31051 (2013.01) HO1L 21/563 (2013.01) HO1L 21/7624 (2013.01)

## 이 발명을 지원한 국가연구개발사업

과제고유번호 2015-0-00044 부처명 미래창조과학부

연구관리전문기관 정보통신기술진흥센터(IITP)

연구사업명 ETRI연구개발지원사업

연구과제명 고효율 GaN 기반 기지국/단말기용 핵심부품 및 모듈 개발

기 여 율 1/1

주관기관한국전자통신연구원연구기간2017.03.01 ~ 2018.02.28

## 명 세 서

## 청구범위

#### 청구항 1

제 1 영역과 제 2 영역을 포함하는 방열판;

상기 방열판의 상기 제 1 영역에 배치되는 제 1 소자; 및

상기 방열판의 상기 제 2 영역에 배치되는 제 2 소자를 포함하되,

상기 제 1 소자는 제 1 기판을 포함하고.

상기 제 2 소자는 제 2 기판을 포함하고,

상기 제 1 기판은 상기 제 2 기판과 서로 다른 물질을 포함하고,

상기 제 1 기판은 상기 방열판과 접하며,

상기 제 2 소자는 상기 방열판에 플립 칩 본딩 방식으로 본딩되는 반도체 장치.

#### 청구항 2

제 1 항에 있어서.

상기 제 1 기판은 실리콘을 포함하고, 상기 제 2 기판은 질화갈륨을 포함하는 반도체 장치.

#### 청구항 3

제 2 항에 있어서,

상기 제 1 소자는 실리콘 전계 효과 트랜지스터이고,

상기 제 2 소자는 질화갈륨 전계효과 트랜지스터인 반도체 장치.

#### 청구항 4

제 1 항에 있어서,

상기 제 1 소자는 상기 제 1 기판 상에 배치되는 제 1 소오스 전극, 제 1 드레인 전극 및 이들 사이의 제 1 게 이트 전극을 더 포함하고,

상기 제 2 소자는 상기 제 2 기판 상에 배치되는 제 2 소오스 전극, 제 2 드레인 전극 및 이들 사이의 제 2 게이트 전극을 더 포함하고,

상기 제 2 기판과 상기 방열판 사이에 상기 제 2 소오스 전극, 상기 제 2 드레인 전극 및 상기 제 2 게이트 전극이 배치되는 반도체 장치.

#### 청구항 5

제 4 항에 있어서,

상기 제 1 소오스 전극과 접하며 상기 제 2 영역의 상기 방열판 표면으로 연장되는 제 1 배선; 및

상기 제 1 드레인 전극과 접하며 상기 제 2 영역의 상기 방열판 표면으로 연장되는 제 2 배선을 더 포함하되.

상기 제 2 소오스 전극, 상기 제 2 드레인 전극 및 상기 제 2 게이트 전극 중 어느 하나는 상기 제 1 배선과 연결되고.

상기 제 2 소오스 전극, 상기 제 2 드레인 전극 및 상기 제 2 게이트 전극 중 다른 하나는 상기 제 2 배선과 연결되는 반도체 장치.

## 청구항 6

제 5 항에 있어서,

상기 제 1 배선과 상기 제 2 배선은 상기 제 1 기판의 측면을 덮는 반도체 장치.

#### 청구항 7

제 1 항에 있어서,

상기 제 1 기판은 상기 제 2 영역의 상기 방열판의 표면을 노출시키는 반도체 장치.

#### 청구항 8

제 1 항에 있어서,

상기 방열판은 다이아몬드를 포함하는 반도체 장치.

## 청구항 9

제 1 항에 있어서,

상기 방열판은 상기 제 2 영역을 사이에 두고 상기 제 1 영역과 이격된 제 3 영역을 더 포함하고,

상기 반도체 장치는 상기 제 3 영역에 배치되는 제 3 소자를 더 포함하며,

상기 제 3 소자는 제 3 기판을 포함하고,

상기 제 1 기판과 상기 제 3 기판은 동일한 물질을 포함하는 반도체 장치.

## 청구항 10

제 9 항에 있어서,

상기 제 2 소자는 질화갈륨 전계효과 트랜지스터이고,

상기 제 1 소자와 상기 제 3 소자는 상기 제 2 소자에 전기적으로 연결되며,

상기 제 1 소자와 상기 제 3 소자는 각각 캐패시터, 인덕터 및 저항 중 선택되는 하나인 반도체 장치.

## 청구항 11

희생 기판 상에 분리막과 제 1 기판막을 차례로 적층하는 단계;

상기 제 1 기판막 상에 제 1 영역과 제 2 영역을 포함하는 방열판을 형성하는 단계;

상기 희생기판과 상기 분리막을 제거하는 단계;

상기 제 1 기판막을 패터닝하여 상기 제 2 영역의 상기 방열판을 노출시키되 상기 제 1 영역에서 상기 방열판과 접하는 제 1 기판을 형성하는 단계;

상기 제 1 기판에 제 1 소자를 형성하는 단계;

상기 제 2 영역에서 상기 방열판 상에 배치되는 복수개의 도전 패드들과 상기 도전패드들 중 적어도 하나와 상기 제 1 소자를 연결하는 제 1 배선을 형성하는 단계; 및

상기 제 2 영역에서 상기 도전 패드들 상에 제 2 소자를 형성하는 단계를 포함하는 반도체 장치의 제조 방법.

## 청구항 12

제 11 항에 있어서,

상기 제 1 기판막은 실리콘막이고, 상기 분리막은 실리콘산화막이고,

상기 희생 기판 상에 상기 분리막과 상기 제 1 기판막을 차례로 적층하는 단계는 소이(SOI, Silicon on insulator) 기판을 준비함으로써 진행되는 반도체 장치의 제조 방법.

#### 청구항 13

제 11 항에 있어서,

상기 방열판을 형성하는 단계는 다이아몬드를 증착하는 단계를 포함하는 반도체 장치의 제조 방법.

#### 청구항 14

제 11 항에 있어서,

상기 방열판을 형성하는 단계 전에, 상기 제 1 기판막의 두께를 줄이는 단계를 더 포함하는 반도체 장치의 제조 방법.

## 청구항 15

제 11 항에 있어서,

상기 제 2 영역에서 상기 도전 패드들 상에 제 2 소자를 형성하는 단계는 플립 칩 본딩 방식으로 진행되는 반도 체 장치의 제조 방법.

#### 청구항 16

제 15 항에 있어서,

상기 제 2 소자는 제 2 기판, 상기 제 2 기판 상에 배치되며 서로 이격된 제 2 전극들을 포함하며,

상기 제 2 영역에서 상기 도전 패드들에 제 2 소자를 연결하는 단계는 솔더막을 개재하여 상기 도전 패드들과 상기 제 2 전극들을 연결하는 반도체 장치의 제조 방법.

#### 청구항 17

제 11 항에 있어서,

상기 방열판은 상기 제 2 영역을 사이에 두고 상기 제 1 영역과 이격되는 제 3 영역을 더 포함하되.

상기 제 1 기판막을 패터닝하는 단계는 상기 제 3 영역에서 상기 방열판과 접하는 제 2 기판을 형성하는 단계를 더 포함하는 반도체 장치의 제조 방법.

### 청구항 18

제 17 항에 있어서.

상기 제 2 소자를 연결하는 단계 전에,

상기 제 2 기판 상에 제 3 소자를 형성하는 단계; 및

상기 도전 패드들의 일부와 상기 제 3 소자를 연결시키는 제 2 배선을 형성하는 단계를 더 포함하는 반도체 장치의 제조 방법.

## 청구항 19

제 18 항에 있어서,

상기 제 2 소자는 질화갈륨 전계효과 트랜지스터이고,

상기 제 1 소자와 상기 제 3 소자는 각각 캐패시터, 인덕터 및 저항 중 선택되는 하나인 반도체 장치의 제조 방법.

## 청구항 20

제 11 항에 있어서,

상기 제 1 소자는 실리콘 전계 효과 트랜지스터이고,

상기 제 2 소자는 질화갈륨 전계효과 트랜지스터인 반도체 장치의 제조 방법.

## 발명의 설명

### 기술분야

[0001] 본 발명은 반도체 장치 및 이의 제조 방법에 관한 것이다.

## 배경기술

[0002] 질화물 반도체 중에서 특히 질화갈륨 반도체는 와이드 밴드갭 반도체로서 실리콘에 비해 높은 전계 강도(약 3.0 ×10 <sup>6</sup> V/cm)와 높은 전자 이동도 (1500 cm <sup>2</sup>/Vs at 300K)을 가지고 있기 때문에 차세대 RF 및 전력용 반도체물질로서 주목을 받고 있다. 질화물 반도체는 전력용 반도체로서 다른 반도체 소자와 함께 연결되어 노멀리 오프 (normally-off) 소자로 사용되기도 하며, 수동(passive)/능동(active) 소자와의 구성을 통해 무선 통신용 단말기 송수신부의 핵심부품으로 사용되기도 한다.

## 발명의 내용

## 해결하려는 과제

- [0003] 본 발명이 해결하고자 하는 과제는 신뢰성이 향상되며 고집적화된 반도체 장치를 제공하는데 있다.

- [0004] 본 발명이 해결하고자 하는 다른 과제는 제조비용을 줄이며 수율을 높일 수 있는 반도체 장치의 제조 방법을 제공하는데 있다.

## 과제의 해결 수단

- [0005] 상기 과제를 달성하기 위한 본 발명에 따른 반도체 장치는, 제 1 영역과 제 2 영역을 포함하는 방열판; 상기 방열판의 상기 제 1 영역에 배치되는 제 1 소자; 및 상기 방열판의 상기 제 2 영역에 배치되는 제 2 소자를 포함하되, 상기 제 1 소자는 제 1 기판을 포함하고, 상기 제 2 소자는 제 2 기판을 포함하고, 상기 제 1 기판은 상기 제 2 기판과 서로 다른 물질을 포함하고, 상기 제 1 기판은 상기 방열판과 접하며, 상기 제 2 소자는 상기 방열판에 플립 칩 본딩 방식으로 본딩된다.

- [0006] 상기 제 1 기판은 실리콘을 포함하고, 상기 제 2 기판은 질화갈륨을 포함할 수 있다.

- [0007] 일 예에 있어서, 상기 제 1 소자는 실리콘 전계 효과 트랜지스터이고, 상기 제 2 소자는 질화갈륨 전계효과 트랜지스터일 수 있다.

- [0008] 상기 제 1 소자는 상기 제 1 기판 상에 배치되는 제 1 소오스 전극, 제 1 드레인 전극 및 이들 사이의 제 1 게이트 전극을 더 포함하고, 상기 제 2 소자는 상기 제 2 기판 상에 배치되는 제 2 소오스 전극, 제 2 드레인 전극 및 이들 사이의 제 2 게이트 전극을 더 포함하고, 상기 제 2 기판과 상기 방열판 사이에 상기 제 2 소오스 전극, 상기 제 2 드레인 전극 및 상기 제 2 게이트 전극이 배치될 수 있다.

- [0009] 상기 반도체 장치는 상기 제 1 소오스 전극과 접하며 상기 제 2 영역의 상기 방열판 표면으로 연장되는 제 1 배선; 및 상기 제 1 드레인 전극과 접하며 상기 제 2 영역의 상기 방열판 표면으로 연장되는 제 2 배선을 더 포함하되, 상기 제 2 소오스 전극, 상기 제 2 드레인 전극 및 상기 제 2 게이트 전극 중 어느 하나는 상기 제 1 배선과 연결되고, 상기 제 2 소오스 전극, 상기 제 2 드레인 전극 및 상기 제 2 게이트 전극 중 다른 하나는 상기 제 2 배선과 연결될 수 있다.

- [0010] 상기 제 1 배선과 상기 제 2 배선은 상기 제 1 기판의 측면을 덮을 수 있다.

- [0011] 상기 제 1 기판은 상기 제 2 영역의 상기 방열판의 표면을 노출시킬 수 있다.

- [0012] 상기 방열판은 다이아몬드로 이루어질 수 있다.

- [0013] 상기 방열판은 상기 제 2 영역을 사이에 두고 상기 제 1 영역과 이격된 제 3 영역을 더 포함하고, 상기 반도체 장치는 상기 제 3 영역에 배치되는 제 3 소자를 더 포함하며, 상기 제 3 소자는 제 3 기판을 포함하고, 상기 제 1 기판과 상기 제 3 기판은 동일한 물질을 포함할 수 있다. 이때, 상기 제 2 소자는 질화갈륨 전계효과 트랜지스터이고, 상기 제 1 소자와 상기 제 3 소자는 상기 제 2 소자에 전기적으로 연결되며, 상기 제 1 소자와 상기 제 3 소자는 각각 캐패시터, 인덕터 및 저항 중 선택되는 하나일 수 있다.

- [0014] 상기 다른 과제를 달성하기 위한 본 발명에 따른 반도체 장치의 제조 방법은, 분리막과 제 1 기판막이 차례로 적충된 희생 기판을 준비하는 단계; 상기 제 1 기판막 상에 제 1 영역과 제 2 영역을 포함하는 방열판을 형성하는 단계; 상기 제 1 기판막과 상기 방열판을 상기 분리막으로부터 분리하는 단계; 상기 제 1 기판막을 패터닝하여 상기 제 2 영역의 상기 방열판을 노출시키되 상기 제 1 영역에서 상기 방열판과 접하는 제 1 기판을 형성하는 단계; 상기 제 1 기판에 제 1 소자를 형성하는 단계; 상기 제 2 영역에서 상기 방열판 상에 배치되는 복수개의 도전 패드들과 상기 도전패드들 중 적어도 하나와 상기 제 1 소자를 연결하는 제 1 배선을 형성하는 단계; 및 상기 제 2 영역에서 상기 도전 패드들에 제 2 소자를 연결하는 단계를 포함한다.

- [0015] 상기 제 1 기판막은 실리콘막이고, 상기 분리막은 실리콘산화막이고, 상기 분리막과 상기 제 1 기판막이 차례로 적충된 희생 기판은 소이(SOI, Silicon on insulator) 기판일 수 있다.

- [0016] 상기 방열판을 형성하는 단계는 다이아몬드를 중착하는 단계를 포함할 수 있다.

- [0017] 상기 방법은 상기 방열판을 형성하는 단계 전에, 상기 제 1 기판막의 두께를 줄이는 단계를 더 포함할 수 있다.

- [0018] 상기 제 2 영역에서 상기 도전 패드들에 제 2 소자를 연결하는 단계는 플립 칩 본딩 방식으로 진행될 수 있다.

- [0019] 상기 제 2 소자는 제 2 기판, 상기 제 2 기판 상에 배치되며 서로 이격된 제 2 전국들을 포함하며, 상기 제 2 영역에서 상기 도전 패드들에 제 2 소자를 연결하는 단계는 솔더막을 개재하여 상기 도전 패드들과 상기 제 2 전국들을 연결할 수 있다.

- [0020] 상기 방열판은 상기 제 2 영역을 사이에 두고 상기 제 1 영역과 이격되는 제 3 영역을 더 포함하되, 상기 제 1 기판막을 패터닝하는 단계는 상기 제 3 영역에서 상기 방열판과 접하는 제 2 기판을 형성하는 단계를 더 포함할 수 있다.

- [0021] 상기 방법은 상기 제 2 소자를 연결하는 단계 전에, 상기 제 2 기판 상에 제 3 소자를 형성하는 단계; 및 상기 도전 패드들의 일부와 상기 제 3 소자를 연결시키는 제 2 배선을 형성하는 단계를 더 포함할 수 있다.

#### 발명의 효과

- [0022] 본 발명의 실시예들에 따른 반도체 장치에서는 방열효과를 극대화시켜 소자의 순방향 전류 특성을 향상시키고 고온 신뢰성을 향상시킬 수 있다. 또한 본 발명에 따른 반도체 장치에서는 방열판의 수평 크기를 줄이고 반도체 장치의 수직 두께를 줄일 수 있어 고집적화에 유리하다.

- [0023] 본 발명의 실시예들에 따른 반도체 장치의 제조 방법에서는 제조비용을 줄이며 수율을 높일 수 있다.

#### 도면의 간단한 설명

[0024] 도 1은 본 발명의 실시예들에 따른 반도체 장치의 단면도이다.

도 2는 본 발명의 실시예들에 따른 반도체 장치의 사시도이다.

도 3 내지 도 6은 도 1의 반도체 장치를 제조하는 과정을 순차적으로 나타내는 단면도들이다.

도 7은 본 발명의 실시예들에 따른 반도체 장치의 사시도이다.

## 발명을 실시하기 위한 구체적인 내용

- [0025] 이상의 본 발명의 목적들, 다른 목적들, 특징들 및 이점들은 첨부된 도면과 관련된 이하의 바람직한 실시예들을 통해서 쉽게 이해될 것이다. 그러나 본 발명은 여기서 설명되는 실시예들에 한정되지 않고 다른 형태로 구체화될 수도 있다. 오히려, 여기서 소개되는 실시예들은 개시된 내용이 철저하고 완전해질 수 있도록 그리고 당업자에게 본 발명의 사상이 충분히 전달될 수 있도록 하기 위해 제공되는 것이다.

- [0026] 본 명세서에서, 어떤 구성 요소가 다른 구성 요소 상에 있다고 언급되는 경우에 그것은 다른 구성요소 상에 직접 형성될 수 있거나 또는 그들 사이에 제 3의 구성요소가 개재될 수도 있다는 것을 의미한다. 또한, 도면들에 있어서, 구성요소들의 두께는 기술적 내용의 효과적인 설명을 위해 과장된 것이다.

- [0027] 본 명세서에서 기술하는 실시예들은 본 발명의 이상적인 예시도인 단면도 및/또는 평면도들을 참고하여 설명될 것이다. 도면들에 있어서, 막 및 영역들의 두께는 기술적 내용의 효과적인 설명을 위해 과장된 것이다. 따라서, 제조 기술 및/또는 허용 오차 등에 의해 예시도의 형태가 변형될 수 있다. 따라서, 본 발명의 실시예들은 도시된 특정 형태로 제한되는 것이 아니라 제조 공정에 따라 생성되는 형태의 변화도 포함하는 것이다. 예를

들면, 직각으로 도시된 식각 영역은 라운드지거나 소정 곡률을 가지는 형태일 수 있다. 따라서, 도면에서 예시된 영역들은 속성을 가지며, 도면에서 예시된 영역들의 모양은 소자의 영역의 특정 형태를 예시하기 위한 것이며 발명의 범주를 제한하기 위한 것이 아니다. 본 명세서의 다양한 실시예들에서 제1, 제2 등의 용어가 다양한 구성요소들을 기술하기 위해서 사용되었지만, 이들 구성요소들이 이 같은 용어들에 의해서 한정되어서는 안 된다. 이들 용어들은 단지 어느 구성요소를 다른 구성요소와 구별시키기 위해서 사용되었을 뿐이다. 여기에 설명되고 예시되는 실시예들은 그것의 상보적인 실시예들도 포함한다.

- [0028] 본 명세서에서 사용된 용어는 실시예들을 설명하기 위한 것이며 본 발명을 제한하고자 하는 것은 아니다. 본 명세서에서, 단수형은 문구에서 특별히 언급하지 않는 한 복수형도 포함한다. 명세서에서 사용되는 '포함한다 (comprise)' 및/또는 '포함하는(comprising)'은 언급된 구성요소는 하나 이상의 다른 구성요소의 존재 또는 추가를 배제하지 않는다.

- [0029] 이하, 도면들을 참조하여, 본 발명의 실시예들에 대해 상세히 설명하기로 한다.

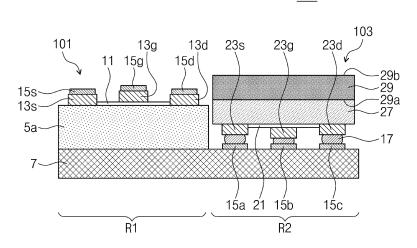

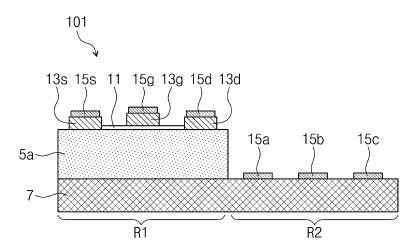

- [0030] 도 1은 본 발명의 실시예들에 따른 반도체 장치의 단면도이다.

- [0031] 도 1을 참조하면, 본 예에 따른 반도체 장치(200)는 방열판(7)을 포함할 수 있다. 상기 방열판(7)은 예를 들면 다이아몬드로 이루어질 수 있다. 다이아몬드의 열전도도는 약 2200W/mK로, 물질 중에 가장 우수한(높은) 열전도 도를 가져, 이를 방열판(7)으로 사용하는 경우 매우 뛰어난 열 방출 효과를 기대할 수 있다. 상기 방열판(7)은 바람직하게는 50μm~1cm의 두께를, 보다 바람직하게는 100μm~5mm의 두께를 가질 수 있다. 상기 방열판(7)은 제 1 영역(R1)과 제 2 영역(R2)을 포함할 수 있다. 상기 제 1 영역(R1)에서 상기 방열판(7) 상에는 제 1 소자(101)가 배치될 수 있다. 상기 제 2 영역(R2)에서 상기 방열판(7) 상에는 제 2 소자(103)가 배치될 수 있다.

- [0032] 상기 제 1 소자(101)는 예를 들면 실리콘 전계효과 트랜지스터일 수 있다. 상기 제 1 소자(101)는 제 1 기판 (5a)을 포함할 수 있다. 상기 제 1 기판(5a)은 상기 방열판(7)과 접할 수 있다. 상기 제 1 기판(5a)은 상기 제 2 영역(R2)의 상기 방열판(7)의 표면을 노출시킬 수 있다. 상기 제 1 영역(R1)에서 상기 제 1 기판(5a)의 상부면과 상기 제 2 영역(R2)에서 상기 방열판(7)의 표면은 서로 단차질 수 있다. 상기 제 1 기판(5a)은 예를 들면실리콘 단결정으로 형성될 수 있다. 도시하지는 않았지만, 상기 제 1 기판(5a)에는 불순물 주입 영역들이 배치될 수 있다. 상기 불순물 주입 영역들의 일부는 N형의 불순물로 도핑될 수 있다. 상기 불순물 주입 영역들의 다른 일부는 P형의 불순물로 도핑될 수 있다. 상기 불순물 주입 영역들은 웰(well) 영역이거나 소오스/드레인 영역을 구성할 수 있다.

- [0033] 상기 제 1 소자(101)는 상기 제 1 기판(5a) 상에 배치되며 서로 이격된 제 1 전극들(13s, 13d, 13g)을 더 포함할 수 있다. 상기 제 1 전극들(13s, 13d, 13g)은 제 1 소오스 전극(13s), 제 1 드레인 전극(13d) 및 제 1 게이트 전극(13g)을 포함할 수 있다. 상기 제 1 전극들(13s, 13d, 13g)은 불순물이 도핑된 폴리실리콘, 티타늄, 알루미늄, 금, 구리, 텅스텐, 니켈 및 백금 중 적어도 하나의 물질을 포함할 수 있다. 상기 제 1 게이트 전극(13g)과 상기 제 1 기판(5a) 사이에는 제 1 게이트 절연막(11)이 개재될 수 있다. 상기 제 1 게이트 절연막(11)은 예를 들면 실리콘산화막, 실리콘질화막, 실리콘산화질화막 및 금속 산화막 중 적어도 하나의 물질로 형성될 수 있다. 상기 제 1 소오스 전극(13s)과 상기 제 1 드레인 전극(13d)은 상기 제 1 기판(5a)과 접할 수 있다.

- [0034] 상기 제 2 소자(103)는 예를 들면 질화갈륨 전계효과 트랜지스터일 수 있다. 상기 제 2 소자(103)는 제 2 기판(27, 29)을 포함할 수 있다. 상기 제 2 기판(27, 29)는 제 1 서브 기판막(29)과 제 2 서브 기판막(27)을 포함할 수 있다. 상기 제 1 서브 기판막(29)은 서로 대향되는 제 1 면(29a)과 제 2 면(29b)을 포함할 수 있다. 상기 제 2 서브 기판막(27)은 상기 제 1 서브 기판막(29)의 상기 제 1 면(29a) 상에 배치될 수 있다. 상기 제 1 면(29a)은 상기 제 2 면(29b)보다 상기 방열판(7)에 인접할 수 있다. 상기 제 1 서브 기판막(29)은 예를 들면 실리콘, 탄화실리콘(SiC) 또는 알루미늄 산화막(또는 사파이어)을 포함할 수 있다. 상기 제 2 서브 기판막(27)은 예를 들면 차례로 적충된 질화갈륨막(GaN)과 알루미늄갈륨질화막(AlGaN)을 포함할 수 있다. 즉, 상기 질화갈륨막은 상기 제 1 면(29a)에 접할 수 있고 상기 알루미늄갈륨질화막은 상기 제 1 면(29a)과 이격될 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 에피택시얼 공정으로 형성될 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 네피택시얼 공정으로 형성될 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 에파택시얼 공정으로 형성된 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 에파택시얼 공정으로 형성된 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 에파택시얼 공정으로 형성된 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 에파택시얼 공정으로 형성된 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 에파택시얼 공정으로 형성된 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 에파택시얼 공정으로 형성된 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 에파택시얼 공정으로 형성된 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 에파택시얼 공정으로 형성된 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 에파택시얼 공정으로 형성된 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 에파택시얼 공정으로 형성된 수 있다. 상기 질화갈륨막과 상기 알루미늄갈륨질화막은 상기 제 2 소자(103) 구동시 전하의 전송속도를 향상시키는 역할을 할 수 있다.

- [0035] 상기 제 2 소자(103)는 상기 제 2 서브 기판막(27) 상에 배치되며 서로 이격된 제 2 전극들(23s, 23d, 23g)을 포함할 수 있다. 상기 제 2 전극들(23s, 23d, 23g)은 제 2 소오스 전극(23s), 제 2 드레인 전극(23d) 및 이들

사이의 제 2 게이트 전극(23g)을 포함할 수 있다. 상기 제 2 전극들(23s, 23d, 23g)은 불순물이 도핑된 폴리실 리콘, 티타늄, 알루미늄, 금, 구리, 텅스텐, 니켈 및 백금 중 적어도 하나의 물질을 포함할 수 있다. 상기 제 2 게이트 전극(23g)과 상기 제 2 서브 기판막(27) 사이에는 제 2 게이트 절연막(21)이 개재될 수 있다. 상기 제 2 게이트 절연막(21)은 예를 들면 실리콘산화막, 실리콘질화막, 실리콘산화질화막 및 금속 산화막 중 적어도 하나의 물질로 형성될 수 있다. 상기 제 2 소오스 전극(23s)과 상기 제 2 드레인 전극(23d)은 상기 제 2 서브 기판막(27)과 접할 수 있다. 상기 제 2 전극들(23s, 23d, 23g)은 상기 제 2 서브 기판막(27)과 상기 방열판(7) 사이에 배치될 수 있다.

- [0036] 상기 제 1 전극들(13s, 13d, 13g) 상에는 각각 제 1 도전 패드들(15s, 15d, 15g)이 배치될 수 있다. 상기 제 1 도전 패드들(15s, 15d, 15g)은 제 1 소오스 도전 패드(15s), 제 1 드레인 도전 패드(15d) 및 제 1 게이트 도전 패드(15g)를 포함할 수 있다. 상기 제 1 소오스 도전 패드(15s)는 상기 제 1 소오스 전극(13s)와 접할 수 있다. 상기 제 1 드레인 도전 패드(15d)는 상기 제 1 드레인 조전 패드(15g)는 상기 제 1 게이트 도전 패드(15g)는 상기 제 1 게이트 전극(13g)와 접할 수 있다.

- [0037] 상기 제 2 영역(R2)에서 상기 방열판(7) 상에는 제 2 도전 패드들(15a, 15b, 15c)가 배치될 수 있다. 상기 제 2 도전 패드들(15a, 15b, 15c)는 제 2 a 도전 패드(15a), 제 2 b 도전 패드(15b) 및 제 2 c 도전 패드(15c)을 포함할 수 있다. 상기 제 1 도전 패드들(15s, 15d, 15g)과 상기 제 2 도전 패드들(15a, 15b, 15c)은 예를 들면 동일한 도전형 물질로 형성될 수 있다. 상기 제 1 도전 패드들(15s, 15d, 15g)과 상기 제 2 도전 패드들(15a, 15b, 15c)은 불순물이 도핑된 폴리실리콘, 티타늄, 알루미늄, 금, 구리, 텅스텐, 니켈 및 백금 중 적어도 하나의 물질을 포함할 수 있다. 상기 제 1 도전 패드들(15s, 15d, 15g)의 일부는 상기 제 2 도전 패드들(15a, 15b, 15c)의 일부와 전기적으로 연결될 수 있다.

- [0038] 상기 제 2 소자(103)는 상기 제 2 영역(R2)에서 상기 방열판(7)에 플립 칩 본딩 방식으로 본딩될 수 있다. 구체 적으로 상기 제 2 소자(103)는 상기 제 2 도전 패드들(15a, 15b, 15c) 상에 솔더막(17)을 개재하여 본딩될 수 있다. 상기 솔더막(17)은 주석과 납 중 적어도 하나를 포함할 수 있다. 또는 상기 제 2 소자(103)는 상기 제 2 도전 패드들(15a, 15b, 15c) 상에 금, 구리, 주석 및 납 중 선택되는 적어도 하나의 금속을 포함하는 범프를 개 재하여 본딩될 수 있다. 상기 제 2 a 도전 패드(15a)는 상기 제 2 소오스 전극(23s)와 전기적으로 연결될 수 있다. 상기 제 2 b 도전 패드(15b)는 상기 제 2 게이트 전극(23g)와 전기적으로 연결될 수 있다. 상기 제 2 c 도전 패드(15c)는 상기 제 2 드레인 전극(23d)와 전기적으로 연결될 수 있다.

- [0039] 도시하지는 않았지만, 상기 반도체 장치(200)는 상기 제 1 소자(101)와 상기 제 2 소자(103)를 덮는 층간절연막이, 패시베이션막 및/또는 몰드막 중 적어도 하나를 더 포함할 수 있다.

- [0040] 도 1의 반도체 장치(200)에서는 질화갈륨 전계효과 트랜지스터일 수 있는 제 2 소자(103)가 다이아몬드일 수 있는 방열판(7)에 플립 칩 본딩 방식으로 직접 연결될 수 있으므로 상기 제 2 소자(103)에서 발생할 수 있는 열을 신속히 외부로 방출시킬 수 있다. 이로써 상기 제 2 소자(103) 내에서 열저항의 감소로 인해 제 2 소자(103)의 순방향 전류 특성을 향상시킬 수 있고, 고온 신뢰성을 향상시킬 수 있다.

- [0041] 도 1의 반도체 장치(200)에서는 실리콘 전계효과 트랜지스터일 수 있는 제 1 소자(101)과 에서는 질화갈륨 전계효과 트랜지스터일 수 있는 제 2 소자(103)가 플립칩 본딩을 통해 연결되므로 배선 연결 길이가 단축될 수 있어 신호 전달 속도를 향상시킬 수 있다. 또한 와이어 본딩 연결에 비하여 방열판(7)의 수평 크기를 줄일 수 있다.

- [0042] 또한 도 1의 반도체 장치(200)에서는 제 1 기판(5a)가 제 2 영역(R2)에서 상기 방열판(7)의 표면을 노출시키며 상기 제 1 기판(5a)과 상기 방열판(7)의 노출된 표면이 단차진 구조를 이루기에 상기 방열판(7)의 노출된 표면 에 상기 제 2 소자(103)가 실장될 수 있어 상기 반도체 장치(200)의 전체 두께가 상대적으로 감소할 수 있다. 이로써 고집적화됨과 동시에 신뢰성이 향상된 반도체 장치(200)를 구현할 수 있다.

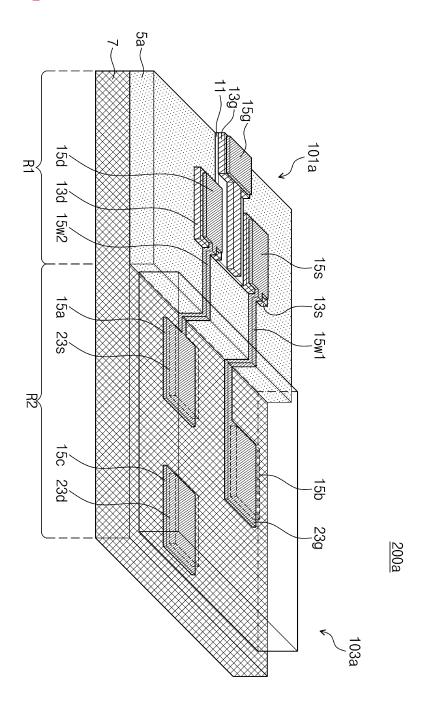

- [0043] 도 2는 본 발명의 실시예들에 따른 반도체 장치의 사시도이다.

- [0044] 도 2를 참조하면, 본 예에 따른 반도체 장치(200a)는 도 1의 구조에서 제 1 소오스 도전 패드(15s)와 제 2 b 도 전 패드(15b)를 연결하는 제 1 배선(15w1)을 더 포함할 수 있다. 상기 반도체 장치(200a)는 제 1 드레인 도전 패드(15d)와 제 2 a 도전 패드(15a)를 연결하는 제 2 배선(15w2)을 더 포함할 수 있다. 즉, 제 1 소자(101a)의 제 1 소오스 전극(13s)는 제 2 소자(103a)의 제 2 게이트 전극(23g)과 전기적으로 연결될 수 있다. 그리고 제 1 소자(101a)의 제 1 드레인 전극(13d)는 제 2 소자(103a)의 제 2 소오스 전극(23s)과 전기적으로 연결될 수 있다. 상기 제 1 및 제 2 배선들(15w1, 15w2)은 상기 제 1 기판(5a)의 측벽을 덮을 수 있다. 도시하지는 않았지만, 상기 제 1 및 제 2 배선들(15w1, 15w2)과 상기 제 1 기판(5a) 사이에는 절연막이 개재될 수 있다. 그 외의

구조는 도 1을 참조하여 설명한 바와 동일/유사할 수 있다. 상기 반도체 장치(200a)는 예를 들면, 실리콘 전계 효과 트랜지스터와 캐스코드 연결을 이용한 노멀리 온(Normally-on) 질화물 반도체 소자일 수 있다.

- [0045] 도 3 내지 도 7은 도 1의 반도체 장치를 제조하는 과정을 순차적으로 나타내는 단면도들이다.

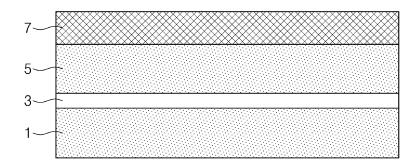

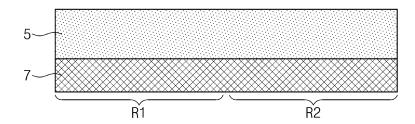

- [0046] 도 3을 참조하면, 희생 기판(1) 상에 분리막(3)과 제 1 기판막(5)을 차례로 적충한다. 상기 분리막(3)은 실리콘 산화막일 수 있다. 상기 희생 기판(1)은 예를 들면 실리콘 단결정일 수 있다. 상기 희생 기판(1) 상에 상기 분리막(3)과 상기 제 1 기판막(5)을 차례로 적충하는 과정은 SOI(silicon on insulator) 기판을 준비함으로써 진행될 수 있다. 또는 희생 기판(1) 상에 분리막(3)과 상기 제 1 기판막(5)을 증착 공정으로 차례로 적충할 수 있다. 상기 제 1 기판막(5)이 원하는 두께를 가지도록 상기 제 1 기판막(5)의 일부를 제거하는 과정이 진행될 수 있다. 이를 위해 상기 제 1 기판막(5)에 대하여 CMP(Chemical Mechanical Polishing) 공정을 진행하거나 전면에치백 공정을 진행할 수 있다. 상기 제 1 기판막(5)의 상기 원하는 두께는 바람직하게는 0.5㎞~3㎞이 수 있다.

- [0047] 계속해서 상기 제 1 기판막(5) 상에 방열판(7)을 형성한다. 상기 방열판(7)은 바람직하게는 다이아몬드를 증착함으로써 형성될 수 있다. 상기 다이아몬드를 증착하는 과정은 예를 들면 열적 CVD(Thermal Chemical Vapor Deposition) 또는 마이크로웨이브 CVD 방식으로 진행될 수 있다. 상기 다이아몬드를 증착하는 과정에서 증착 온도는 바람직하게는 500℃ 이상이며 보다 바람직하게는 700~1000℃이다. 상기 방열판(7)은 바람직하게는 50μm~1cm의 두께를, 보다 바람직하게는 100μm~5mm의 두께를 가질 수 있다.

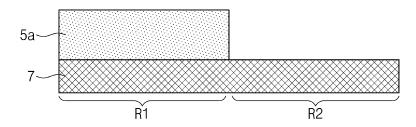

- [0048] 도 4를 참조하면, 상기 희생 기판(1)과 상기 분리막(3)을 제거할 수 있다. 상기 희생 기판(1)과 상기 분리막(3)을 제거하는 과정은 습식/건식 식각 공정 또는 기계적 래핑(lapping) 공정에 의해 진행될 수 있다. 이에 의해 상기 제 1 기판막(5)의 표면을 노출시킬 수 있다. 그리고 제 1 기판막(5) 상에 방열판(7)이 적충된 구조를 뒤집을 수 있다. 이에 의해 상기 제 1 기판막(5)이 상기 방열판(7) 상에 배치되는 구조가 될 수 있다. 상기 방열판(7)은 제 1 영역(R1)과 제 2 영역(R2)을 가질 수 있다.

- [0049] 도 5를 참조하면, 도시하지는 않았지만, 상기 제 1 기판막(5) 상에 상기 제 1 영역(R1)을 덮되 상기 제 2 영역 (R2)을 노출시키는 마스크 패턴을 형성할 수 있다. 상기 마스크 패턴은 예를 들면 포토레지스트 패턴일 수 있다. 상기 마스크 패턴을 식각 마스크로 이용하여 상기 제 1 기판막(5)을 식각하여 상기 제 1 영역(R1)의 상기 방열판(7)을 덮되 상기 제 2 영역(R2)의 상기 방열판(7)을 노출시키는 제 1 기판(5a)을 형성할 수 있다. 도시하지는 않았지만, 이온주입공정을 진행하여 상기 제 1 기판(5a) 내에 불순물 주입 영역들을 형성할 수 있다.

- [0050] 도 6을 참조하면, 상기 제 1 기판(5a) 상에 제 1 게이트 절연막(11)을 형성할 수 있다. 상기 제 1 게이트 절연막(11)은 증착 및 식각 공정을 통해 형성될 수 있다. 상기 제 1 게이트 절연막(11)은 상기 제 1 기판(5a)의 일부를 덮도록 형성될 수 있다. 상기 제 1 기판(5a) 상에 제 1 전극들(13s, 13g, 13d)을 형성할 수 있다. 상기 제 1 전극들(13s, 13g, 13d)은 예를 들면 도전막을 증착하고 식각하여 형성될 수 있다. 또는 상기 제 1 전극들(13s, 13g, 13d)은 도전성 페이스트를 스크린 프린팅 또는 잉크젯 프린팅의 방법으로 공급하여 형성될 수 있다. 상기 제 1 전극들(13s, 13g, 13d)은 제 1 소오스 전극(13s), 제 1 게이트 전극(13g) 및 제 1 드레인 전극(13d)을 포함할 수 있다. 상기 제 1 게이트 전극(13g)은 상기 제 1 게이트 절연막(11) 상에 형성될 수 있다. 상기제 1 전극들(13s, 13g, 13d)은 불순물이 도핑된 폴리실리콘, 티타늄, 알루미늄, 금, 구리, 텅스텐, 니켈 및 백금 중 적어도 하나의 물질로 형성될 수 있다. 상기 제 1 게이트 절연막(11)은 예를 들면 실리콘산화막, 실리콘 질화막, 실리콘산화질화막 및 금속 산화막 중 적어도 하나의 물질로 형성될 수 있다.

- [0051] 도 6 및 도 2를 참조하면, 상기 제 1 전극들(13s, 13g, 13d) 상에 각각 제 1 도전 패드들(15s, 15g, 15d)을 형성할 수 있다. 그리고 상기 제 2 영역(R2)에서 상기 방열판(7) 상에 제 2 도전 패드들(15a, 15b, 15c)을 형성할 수 있다. 이때 상기 제 1 배선(15w1)과 제 2 배선(15w2)도 형성될 수 있다. 상기 제 1 도전 패드들(15s, 15g, 15d), 상기 제 2 도전 패드들(15a, 15b, 15c) 및 상기 제 1 및 제 2 배선들(15w1, 15w2)은 동시에 형성될 수 있다. 상기 제 1 도전 패드들(15s, 15g, 15d), 상기 제 2 도전 패드들(15s, 15g, 15d), 상기 제 2 도전 패드들(15s, 15g, 15d), 상기 제 2 도전 패드들(15a, 15b, 15c) 및 상기 제 1 및 제 2 배선들(15w1, 15w2)은 도전막을 중착하고 식각함으로써 형성될 수 있다. 또는 상기 제 1 도전 패드들(15s, 15g, 15d), 상기 제 2 도전 패드들(15a, 15b, 15c) 및 상기 제 1 및 제 2 배선들(15w1, 15w2)은 도전성 페이스트를 스크린 프린팅 또는 잉크젯 프린팅의 방법으로 공급하여 형성될 수 있다. 상기 제 1 도전 패드들(15s, 15g, 15d), 상기 제 2 도전 패드들(15a, 15b, 15c) 및 상기 제 1 및 제 2 배선들(15w1, 15w2)은 불순물이 도핑된 폴리실리콘, 티타늄, 알루미늄, 금, 구리, 텅스텐, 니켈 및 백금 중 적어도 하나의 물질을 포함할 수 있다.

- [0052] 도 1을 참조하여, 제 2 소자(103)을 준비한다. 상기 제 2 소자(103)는 예를 들면 질화갈륨 전계효과 트랜지스터 일 수 있다. 상기 제 2 소자(103)는 위에서 설명한 바와 동일할 수 있다. 상기 제 2 소자(103)를 상기 제 2 도

전 패드들(15a, 15b, 15c)에 플립 칩 본딩 방식으로 실장할 수 있다. 즉, 제 1 서브 기판막(29)의 제 1 면(29 a)이 아래를 향하도록 상기 제 2 소자(103)를 상기 방열판(7)의 상기 제 2 영역(R2)에 위치시키고, 제 2 전극들 (23s, 23g, 23d)과 상기 제 2 도전 패드들(15a, 15b, 15c) 사이에 솔더막(17)을 개재한 상태에서 열을 가하는 리플로우 공정을 진행하여 상기 제 2 소자(103)를 본딩시킬 수 있다.

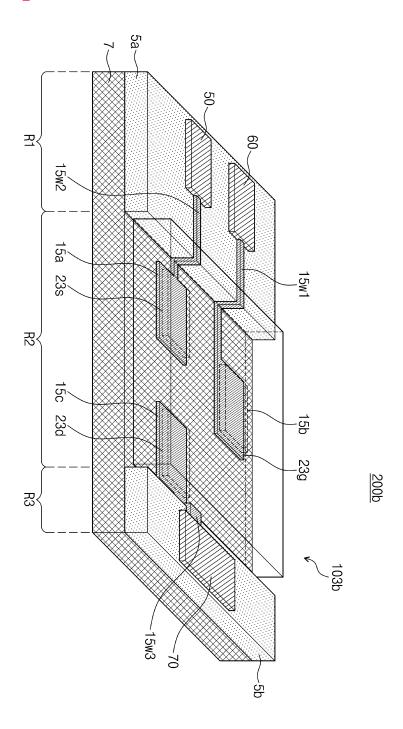

- [0053] 도 7은 본 발명의 실시예들에 따른 반도체 장치의 사시도이다.

- [0054] 도 7을 참조하면, 본 예에 따른 반도체 장치(200b)에서는 방열판(7)이 제 3 영역(R3)을 더 포함할 수 있다. 즉, 상기 방열판(7)은 서로 나란히 배열된 제 1 영역(R1), 제 2 영역(R2) 및 상기 제 3 영역(R3)을 포함할 수 있다. 상기 방열판(7)의 상기 제 1 영역(R1)에는 제 1 기판(5a)이 배치될 수 있다. 상기 방열판(7)의 상기 제 3 영역(R3)에는 제 3 기판(5b)이 배치될 수 있다. 상기 제 1 기판(5a)과 상기 제 3 기판(5b)은 동일한 물질로, 예를 들면 실리콘 단결정으로 이루어질 수 있다. 상기 방열판(7)의 상기 제 2 영역(R2)에는 도 1을 참조하여 설명한 제 2 소자(103b)가 플립칩 본딩 방식으로 실장될 수 있다.

- [0055] 상기 제 1 기판(5a)과 상기 제 3 기판(5b) 상에는 수동 소자가 배치될 수 있다. 구체적으로 상기 제 1 기판(5a) 상에는 서로 이격된 제 1 서브 소자(50)와 제 2 서브 소자(60)가 배치될 수 있다. 상기 제 1 서브 소자(50)는 예를 들면 캐패시터일 수 있다. 상기 제 1 서브 소자(50)는 예를 들면 두 개의 전극들과 이들 사이에 개재된 유전막을 포함할 수 있다. 상기 제 2 서브 소자(60)는 예를 들면 인덕터일 수 있다. 상기 제 2 서브 소자(60)는 코일 형태의 구조물을 포함할 수 있다. 상기 제 3 기판(5b) 상에는 제 3 소자(70)가 배치될 수 있다. 상기 제 3 소자(70)는 예를 들면 저항일 수 있다. 상기 제 2 서브 소자(60)는 상기 제 2 소자(103b)의 제 2 게이트 전극(23g)에 제 1 배선(15w1)에 의해 전기적으로 연결될 수 있다. 상기 제 1 서브 소자(50)는 상기 제 2 소자(103b)의 제 2 소자(103b)의 제 2 보이(103b)의 제 2 보이(15w2)에 의해 전기적으로 연결될 수 있다. 상기 제 3 소자(70)는 상기 제 2 소자(103b)의 제 2 드레인 전극(23d)에 제 3 배선(15w3)에 의해 전기적으로 연결될 수 있다. 상기 반도체 장치(200b)는 RF 소자일 수 있으며, MMIC(Monolithic Microwave Integrated Circuit)일 수 있다. 그 외의 구조는 위에서 설명한 바와 동일/유사할 수 있다.

- [0056] 상기 반도체 장치(200b)에서 상기 제 1 기판(5a)과 상기 제 3 기판(5b)은 도 4 및 도 5의 과정에서, 제 1 기판 막(5)을 식각하여 동시에 형성될 수 있다. 그 외의 제조 과정은 도6 및 도 1을 참조하여 설명한 과정과 유사할 수 있다.

- [0057] 본 발명에 따른 반도체 장치의 제조 방법에서는 MMIC 등에서 필요한 수동 소자의 공정을 상대적으로 비싼 질화물 반도체 대신 상대적으로 저렴한 실리콘 층 위에서 수행하기 때문에 단위 면적당 제조 비용을 줄일 수 있고소자의 수율을 높일 수 있다.

#### 도면

## 도면1

200 103 101 13d 23s 23d 13g 23g 11 15g 15d 29b 29 15s-29a 13s 27 5a-17 15a 21 15b 15c Ř2 Ŕ1

# 도면2

# 도면3

## 도면4

# 도면5

# 도면6

# 도면7