(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-138118

(P2011-138118A)

(43) 公開日 平成23年7月14日(2011.7.14)

(51) Int.Cl.

**G02F 1/1368 (2006.01)**

**H01L 29/786 (2006.01)**

**H01L 21/336 (2006.01)**

**G02F 1/133 (2006.01)**

F 1

G02F 1/1368

H01L 29/78 618B

H01L 29/78 618Z

G02F 1/133 550

テーマコード(参考)

2H092

2H193

5F110

審査請求 未請求 請求項の数 8 O L (全 21 頁)

(21) 出願番号 特願2010-268889 (P2010-268889)

(22) 出願日 平成22年12月2日 (2010.12.2)

(31) 優先権主張番号 特願2009-276374 (P2009-276374)

(32) 優先日 平成21年12月4日 (2009.12.4)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 肇平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム(参考) 2H092 GA12 GA13 GA17 JA25 JA26

JA28 JA31 JA32 JA34 JA37

JA41 JB05 JB22 JB31 KA08

KA12 KA18 MA05 MA08 MA13

MA17 NA05 NA22 PA06 QA07

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】表示装置において、画素への信号の書き込み時間を短縮すること、また、高い電圧を印加する場合でも、信号の書き込みを高速に行うことを目的とする。

【解決手段】トランジスタと、前記トランジスタのソース又はドレインに電気的に接続された液晶素子とが設けられた画素を有し、前記トランジスタは、半導体材料として真性又は実質的に真性な酸化物半導体が用いられており、且つオフ電流が  $1 \times 10^{-17} \text{ A} / \mu\text{m}$  以下であり、前記画素には、容量素子が設けられていない。容量素子を設けなくてもよいため、信号の書き込み時間を短縮することができる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

トランジスタと、前記トランジスタのソース又はドレインに電気的に接続された液晶素子とが設けられた画素を有し、

前記トランジスタは、半導体材料として酸化物半導体が用いられており、

前記画素には、容量素子が設けられていないことを特徴とする表示装置。

**【請求項 2】**

トランジスタと、前記トランジスタのソース又はドレインに電気的に接続された液晶素子とが設けられた画素を有し、

前記トランジスタは、半導体材料として真性又は実質的に真性な酸化物半導体が用いられており、

前記画素には、容量素子が設けられていないことを特徴とする表示装置。

**【請求項 3】**

トランジスタと、前記トランジスタのソース又はドレインに電気的に接続された液晶素子とが設けられた画素を有し、

前記トランジスタは、半導体材料として真性又は実質的に真性な酸化物半導体が用いられており、且つオフ電流が  $1 \times 10^{-17} \text{ A} / \mu\text{m}$  以下であり、

前記画素には、容量素子が設けられていないことを特徴とする表示装置。

**【請求項 4】**

請求項 1 乃至請求項 3 のいずれか一において、

前記液晶素子には、ビデオ信号が入力される前に前記ビデオ信号の電圧以上の電圧が入力されることを特徴とする表示装置。

**【請求項 5】**

トランジスタと、

前記トランジスタのソース又はドレインに電気的に接続された第 1 の電極、前記第 1 の電極の上方に形成された液晶層、及び前記第 1 の電極の下方に絶縁膜を介して形成された第 2 の電極とが設けられた画素を有し、

前記第 1 の電極と第 2 の電極とは重なっておらず、且つ第 1 の電極の端部と第 2 の電極の端部とが一致してあり、

前記トランジスタは、半導体材料として酸化物半導体が用いられており、

前記画素には、容量素子が設けられていないことを特徴とする表示装置。

**【請求項 6】**

トランジスタと、

前記トランジスタのソース又はドレインに電気的に接続された第 1 の電極、前記第 1 の電極の上方に形成された液晶層、及び前記第 1 の電極の下方に絶縁膜を介して形成された第 2 の電極とが設けられた画素を有し、

前記第 1 の電極と第 2 の電極とは重なっておらず、且つ第 1 の電極の端部と第 2 の電極の端部とが一致してあり、

前記トランジスタは、半導体材料として真性又は実質的に真性な酸化物半導体が用いられており、

前記画素には、容量素子が設けられていないことを特徴とする表示装置。

**【請求項 7】**

トランジスタと、

前記トランジスタのソース又はドレインに電気的に接続された第 1 の電極、前記第 1 の電極の上方に形成された液晶層、及び前記第 1 の電極の下方に絶縁膜を介して形成された第 2 の電極とが設けられた画素を有し、

前記第 1 の電極と第 2 の電極とは重なっておらず、且つ第 1 の電極の端部と第 2 の電極の端部とが一致してあり、

前記トランジスタは、半導体材料として真性又は実質的に真性な酸化物半導体が用いられており、且つオフ電流が  $1 \times 10^{-17} \text{ A} / \mu\text{m}$  以下であり、

10

20

30

40

50

前記画素には、容量素子が設けられていないことを特徴とする表示装置。

【請求項 8】

請求項 4 乃至請求項 7 のいずれか一において、

前記第 1 の電極には、ビデオ信号が入力される前に前記ビデオ信号以上の電圧が入力されることを特徴とする表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

技術分野は、半導体装置及びその作製方法に関する。また当該半導体装置を用いて作製された表示装置及びその駆動方法に関する。

10

【背景技術】

【0002】

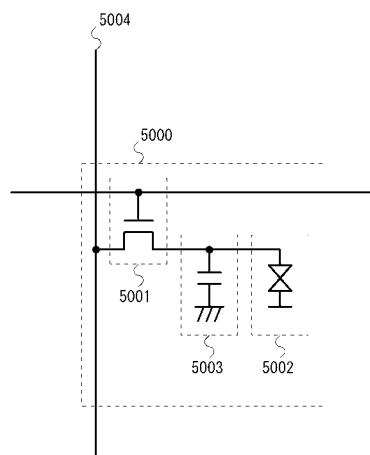

液晶表示装置では、画素にスイッチ素子が設けられたアクティブマトリックス型のものが多く採用されている。図 13 に示すように、画素 5000 は、スイッチ素子として機能するトランジスタ 5001、トランジスタ 5001 を介して配線 5004 からビデオ信号が入力される液晶素子 5002、及び液晶素子 5002 に書き込まれたビデオ信号を保持する容量素子 5003 により構成されている。容量素子 5003 を設けることで、スイッチ素子がオフの時もビデオ信号を保持することができる。

【0003】

そして、トランジスタの半導体材料としては、汎用性に優れたシリコンが用いられている。しかし近年では、汎用性と共に性能の向上が求められており、酸化物半導体を用いた電界効果型トランジスタ (FET とも呼ぶ) に関する技術が注目されている (特許文献 1)。

20

【0004】

また、液晶の応答速度を高めるため、ビデオ信号を書き込む前に液晶に高い電圧を瞬間に印加する技術、所謂オーバードライブ駆動が行われている (特許文献 2)。

【先行技術文献】

【特許文献】

【0005】

【特許文献 1】特開 2006-165532 号公報

30

【特許文献 2】特開昭 64-010299 号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

従来の液晶表示装置では、液晶素子の液晶容量  $C_{LC}$  と容量素子の保持容量  $C_S$  (一般的に 100 fF 以上 300 fF 以下) との合成容量 ( $C_{LC} + C_S$ ) を充電する必要があるため、充電に必要な時定数  $= R (C_{LC} + C_S)$  を考慮すると、保持容量  $C_S$  の充電時間の分だけ信号を書き込むための時間が長くなるという問題が生じていた。R はトランジスタのオン抵抗である。

【0007】

特に、特許文献 2 のようなオーバードライブ駆動を行う場合には、瞬間に高い電圧を印加する必要がある。しかし、容量素子への充電時間が影響を及ぼし、所望の電圧に達するまでの時間が長くなっていた。

40

【0008】

これらの問題は、保持容量  $C_S$  が大きくなることで顕著になる。しかしながら、容量素子を配置しない構成とした場合、特許文献 1 のような半導体材料では、トランジスタのオフ電流が高いため、信号を保持することが困難であった。そのため、従来の液晶表示装置においては、容量素子は不可欠であった。

【0009】

上記問題に鑑み、表示装置において、容量素子への充電時間を短縮し、信号の書き込み

50

を高速に行うことの目的の一とする。

【0010】

また、オーバードライブ駆動等の高い電圧を印加する場合でも、信号の書き込みを高速に行える表示装置を提供することの目的の一とする。

【課題を解決するための手段】

【0011】

本発明の一態様は、トランジスタと、トランジスタのソース又はドレインに電気的に接続された液晶素子とが設けられた画素を有し、トランジスタは、半導体材料として酸化物半導体が用いられており、画素の容量素子の容量を削減する表示装置、好ましくは、容量素子が設けられていない表示装置、さらに好ましくは、意図的に設けないだけではなく、意図しないのに生じている容量（寄生容量）をも積極的に削減する表示装置である。寄生容量は 50 fF 以下、より好ましくは 10 fF 以下であるとよい。

10

【0012】

また、本発明の他の一態様は、トランジスタと、トランジスタのソース又はドレインに電気的に接続された第1の電極、第1の電極の上方に形成された液晶層、及び第1の電極の下方に絶縁膜を介して形成された第2の電極とが設けられた画素を有し、第1の電極と第2の電極とは重なっておらず、且つ第1の電極の端部と第2の電極の端部とが一致しており、トランジスタは、半導体材料として酸化物半導体が用いられており、画素には、容量素子が設けられていない表示装置である。

20

【0013】

また、上記トランジスタに用いる酸化物半導体は真性（i型ともいう）又は実質的に真性であり、トランジスタのオフ電流が  $1 \times 10^{-17} \text{ A} / \mu\text{m}$  以下である。

【0014】

また、液晶素子にビデオ信号を入力する前にビデオ信号の電圧以上の電圧を入力するオーバードライブ駆動を採用する。

【発明の効果】

【0015】

容量素子を充電するための時間を短縮できるため、画素への信号の書き込みを高速に行うことができる。

30

【0016】

また、容量素子への充電時間を短縮することで、高い電圧でも短時間で印加することができるため、オーバードライブ駆動を効果的に行うことができる。

【図面の簡単な説明】

【0017】

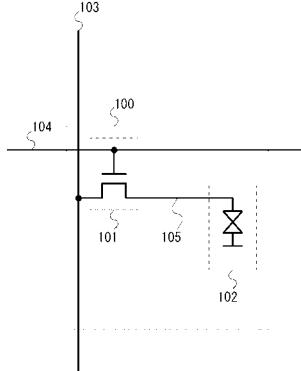

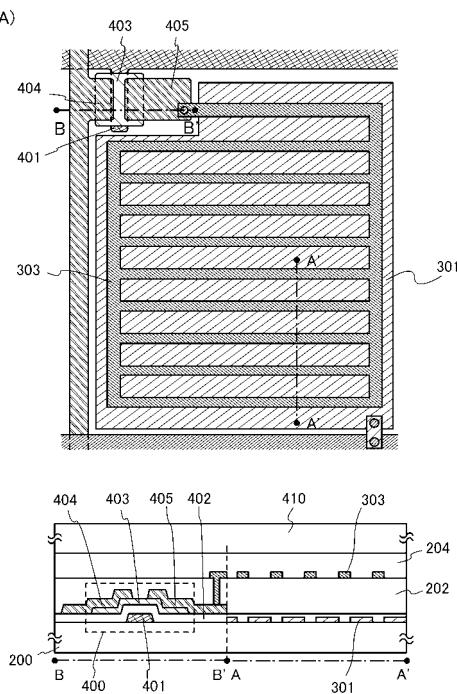

【図1】表示装置の画素を示す図。

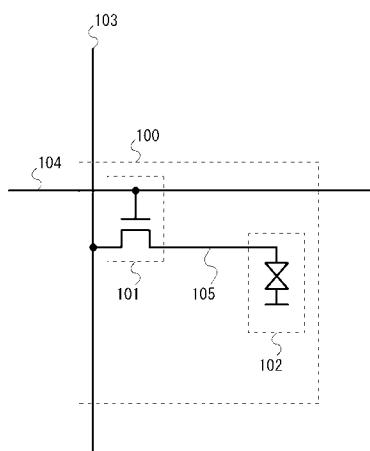

【図2】表示装置の電極構造を示す図。

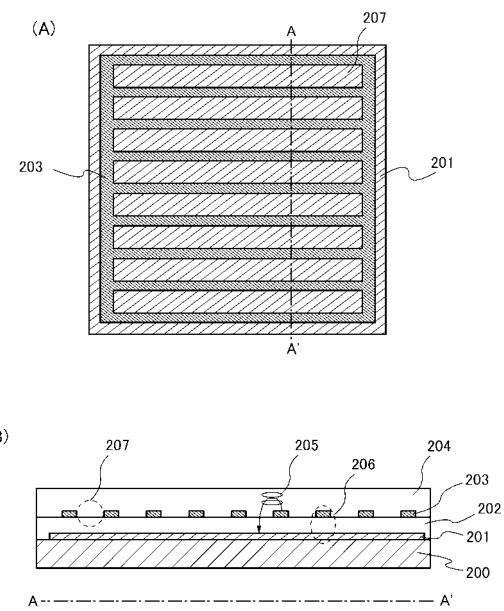

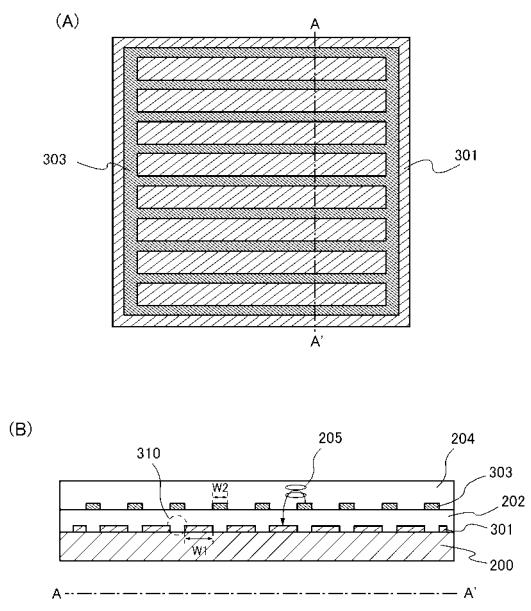

【図3】表示装置の電極構造を示す図。

【図4】表示装置の画素を示す図。

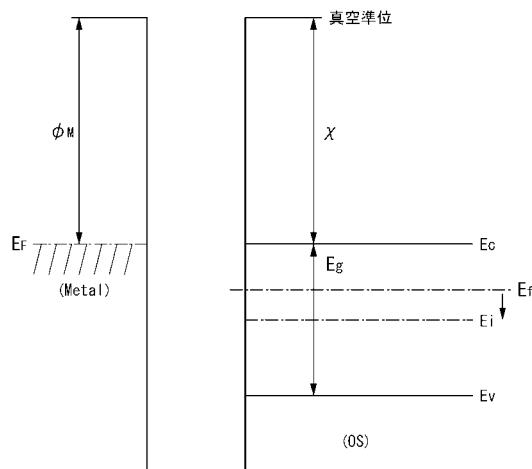

【図5】エネルギーーバンド図。

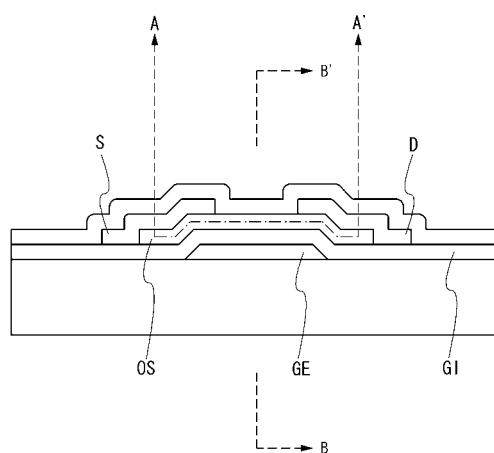

【図6】酸化物半導体を用いたトランジスタを示す図。

40

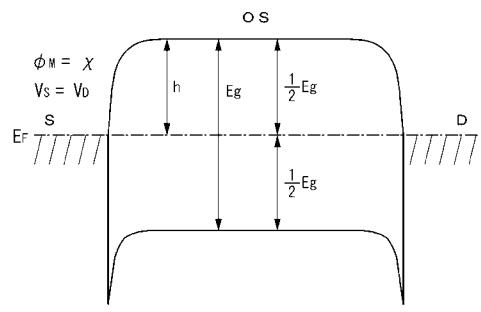

【図7】エネルギーーバンドを示す図。

【図8】エネルギーーバンドを示す図。

【図9】半導体装置の作製方法を示す図。

【図10】電子機器の一例を示す図。

【図11】オーバードライブ駆動を説明する図。

【図12】トランジスタの電気特性を示す図。

【図13】表示装置の画素を示す図。

【発明を実施するための形態】

【0018】

本発明の実施の形態の一例について、図面を用いて以下に説明する。但し、本発明は以

50

下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0019】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、理解を容易にするため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

【0020】

なお、本明細書等における「第1」、「第2」などの序数は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

10

【0021】

(実施の形態1)

液晶表示装置の画素の一例を、図1を用いて説明する。画素100を構成する素子は、スイッチ素子として機能するトランジスタ101、及び液晶素子102である。

【0022】

トランジスタ101は、ゲートが配線103(ゲート信号線)に電気的に接続され、ソース又はドレインの一方が配線104(ソース信号線)に電気的に接続され、他方が液晶素子102に電気的に接続されている。

【0023】

本実施の形態では、トランジスタ101の半導体材料として真性又は実質的に真性の酸化物半導体を用い、トランジスタ101のオフ電流が、チャネル幅 $1\text{ }\mu\text{m}$ 当たり $1\times 10^{-17}\text{ A}$ 以下( $1\times 10^{-17}\text{ A}/\mu\text{m}$ 以下ともいう)であることを特徴としている。

20

【0024】

トランジスタ101のオフ電流が $1\times 10^{-17}\text{ A}/\mu\text{m}$ 以下であることは、トランジスタ101がオフの間のリーク電流が実質的にゼロであることを意味している。すなわち、トランジスタ101がオフになっても、ノード105の電位が変動しないため、画素に書き込まれた信号は保持される。

【0025】

したがって、図1に示すように、画素100には容量素子を設けなくてもよい。つまり、容量配線を設けなくてよい。図1に示す画素を図13に示す従来例と比較した場合、容量素子の保持容量 $C_s$ を充電する時間が不要なため、画素への信号の書き込みを高速に行うことができる。

30

【0026】

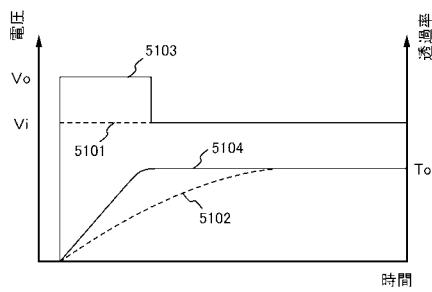

このような容量素子を必須としない画素構成は、オーバードライブ駆動を効果的に行うことができる。オーバードライブ駆動について図11を用いて説明する。

【0027】

図11は、印加電圧に対する液晶の透過率の時間変化を表したものである。オーバードライブ駆動を行わない場合、破線5101で示すビデオ信号の電圧 $V_i$ に対して透過率は破線5102のように時間変化して所望の透過率 $T_0$ に達する。

40

【0028】

これに対し、オーバードライブ駆動を行う場合は、実線5103のように電圧 $V_i$ よりも高いオーバードライブ電圧 $V_0$ を印加することで、実線5104のように所望の透過率 $T_0$ に到達するまでの時間を短縮することができる。このように、信号を書き込む前に印加電圧を瞬間的に高く(または低く)することで液晶の応答速度を高めることができる。

【0029】

しかし、オーバードライブ電圧 $V_0$ のように瞬間的に高い電圧を印加する場合には、容量素子への充電時間の影響がより顕著になり、所望の電圧に達するまでの時間が長くなってしまう。そこで、容量素子を必須としない画素構成を採用することで、容量素子への充電時間が短縮され、高い電圧でも短時間で印加することが可能となるため、オーバードライブ駆動を効果的に行うことができる。

50

## 【0030】

また、この画素構成は、液晶表示装置において倍速駆動を採用した場合にも有効である。倍速駆動では、表示するコマ数が増えるため、より速く画素に信号を入力する必要がある。そこで容量素子を必須としない画素構成とすることで、充電時間を短縮でき、倍速駆動を効果的に行うことができる。

## 【0031】

上記の構成及び効果は、真性又は実質的に真性な酸化物半導体を用いてトランジスタ101を形成し、オフ電流を $1 \times 10^{-17} \text{ A} / \mu\text{m}$ 以下とすることで得られるものである。

## 【0032】

これに対し従来の酸化物半導体はn型化しており、オフ電流は小さくても $1 \times 10^{-9} \text{ A} / \mu\text{m}$ 程度であった。そのため画素の容量素子は必須であり、信号の書き込み時間が長くなっていた。

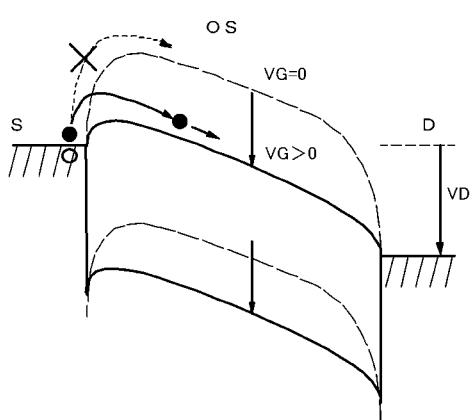

## 【0033】

ここで、本実施の形態の酸化物半導体を用いたトランジスタの電導機構を、図5～図8を用いて説明する。なお、以下の説明では、理解を容易にするため理想的な状況を仮定しており、そのすべてが現実の様子を反映しているとは限らない。また、以下の説明はあくまでも一考察に過ぎず、発明の有効性に影響を与えるものではないことを付記する。

## 【0034】

図5は、真空準位と金属(Metal)の仕事関数( $\phi_M$ )、酸化物半導体(OS)の電子親和力( $\phi$ )の関係を示す。金属のフェルミ準位を $E_F$ とし、酸化物半導体のフェルミ準位を $E_f$ 、伝導帯下端のエネルギーを $E_c$ 、価電子帯上端のエネルギーを $E_v$ 、真性フェルミ準位を $E_i$ とし、酸化物半導体のエネルギーバンドギャップを $E_g$ とする。なお、酸化物半導体のエネルギー bandwidth ギャップ( $E_g$ )は $3.0 \sim 3.5 \text{ eV}$ である。

20

## 【0035】

図5において、従来のようなn型化した酸化物半導体の場合、フェルミ準位( $E_f$ )は、バンドギャップ( $E_g$ )の中央に位置する真性フェルミ準位( $E_i$ )から離れて、伝導帯( $E_c$ )寄りに位置する。

## 【0036】

ここで、キャリア密度を低減し真性半導体に近づけることで、酸化物半導体のフェルミ準位( $E_f$ )は真性フェルミ準位( $E_i$ )に近づく。本実施の形態の真性又は実質的に真性な酸化物半導体とは、フェルミ準位( $E_f$ )が真性フェルミ準位( $E_i$ )に近接又は一致するまで、キャリア密度が低減されている状態を指す。

30

## 【0037】

本実施の形態における真性又は実質的に真性な酸化物半導体は、以下の技術思想に基づいて得られるものである。

## 【0038】

まず、酸化物半導体をn型化する要因の一つとして、酸化物半導体中に水素を含むことが挙げられる。酸化物半導体において水素の一部はドナーとなり、伝導帯の下 $0.1 \sim 0.2 \text{ eV}$ に浅い準位を形成して、キャリア濃度を増加させる。

40

## 【0039】

また、n型化の要因の一つとして、酸化物半導体の主成分である酸素が欠損(酸素欠損)していることが挙げられる。酸素欠損は、酸化物半導体に深いドナー準位を形成し、キャリア濃度を増加させる。

## 【0040】

半導体において、状態密度(DOS: density of states)等の物性研究は多くなされているが、これらの研究は、欠陥の準位そのものを十分に減らすという思想を含まない。本実施の形態では、DOS増大の原因たり得る水や水素を酸化物半導体中より除去することで、高純度化し、真性化した酸化物半導体を作製する。これは、DOSそのものを十分に減らすという思想に立脚するものである。そして、これによって極め

50

て優れた工業製品の製造を可能とするものである。

【0041】

すなわち本実施の形態では、n型化の要因の一つである水素等の不純物を酸化物半導体から極力除去すること、かつ、酸素欠損を除去することによって、酸化物半導体を高純度化することを特徴している。そして、高純度化することで、真性又は実質的に真性の酸化物半導体を得るものである。これにより、図5において、フェルミ準位( $E_f$ )は真性フェルミ準位( $E_i$ )と同程度とすることができます。

【0042】

具体的には、酸化物半導体の水素濃度を $5 \times 10^{19} / \text{cm}^3$ 以下、望ましくは $5 \times 10^{18} / \text{cm}^3$ 以下、より望ましくは $5 \times 10^{17} / \text{cm}^3$ 以下まで低減する。そして、従来と比べて十分に小さいキャリア濃度の値(例えば、 $1 \times 10^{12} / \text{cm}^3$ 未満、望ましくは $1.45 \times 10^{10} / \text{cm}^3$ 以下)とすることが好ましい。

【0043】

図6は、真性又は実質的に真性な酸化物半導体を用いて作製したトランジスタの一例であり、逆スタガー型のボトムゲート構造の薄膜トランジスタを示している。ゲート電極(GE)上にゲート絶縁膜(GI)を介して酸化物半導体層(OS)が設けられ、その上にソース電極(S)およびドレイン電極(D)が設けられている。

【0044】

ここで、酸化物半導体とソース電極及びドレイン電極との間にショットキー型の障壁が形成されないことが好ましい。本実施の形態では、酸化物半導体の電子親和力( )と、ソース電極及びドレイン電極となる金属の仕事関数( $M$ )とをほぼ等しくする。例えば、酸化物半導体のバンドギャップ( $E_g$ )が $3.15 \text{ eV}$ である場合、電子親和力( )は $4.3 \text{ eV}$ であると言われており、仕事関数( $M$ )が $4.3 \text{ eV}$ 程度であるチタン(Ti)を酸化物半導体に接触させた構造を有するソース電極及びドレイン電極を形成すればよい。

【0045】

図7に、図6のA-A'断面におけるエネルギー-band図(模式図)を示す。図7(A)はソース電極(S)とドレイン電極(D)の間の電位差をゼロ(等電位、 $V_D = 0 \text{ V}$ )とした場合を示しており、図7(B)はソース電極に対しドレイン電極及びゲート電極の電位を高くした場合( $V_D > 0 \text{ V}$ )を示している。図7(B)において、破線はゲート電極に電圧を印加しない場合( $V_G = 0 \text{ V}$ )、実線はゲート電極に正の電圧( $V_G > 0 \text{ V}$ )を印加した場合を示す。ゲート電極に電圧を印加しない場合は高いポテンシャル障壁のために電極から酸化物半導体側へキャリア(電子)が注入されず、電流を流さないオフ状態を示す。一方、ゲート電極に正の電圧を印加するとポテンシャル障壁が低下し、電流を流すオン状態を示す。

【0046】

図7(B)において黒丸( )は電子を示す。ゲート電極およびドレイン電極(D)に正の電位が与えられると、実線のように、電子はバリア( $h$ )をこえて酸化物半導体(OS)に注入され、ドレイン電極(D)に向かって流れる。バリア( $h$ )の高さは、ゲート電圧とドレイン電圧に依存して変化するが、正のドレイン電圧が印加される場合には、電圧印加のない図7(A)のバリアの高さ、すなわちバンドギャップ( $E_g$ )の $1/2$ 、より低くなる。

【0047】

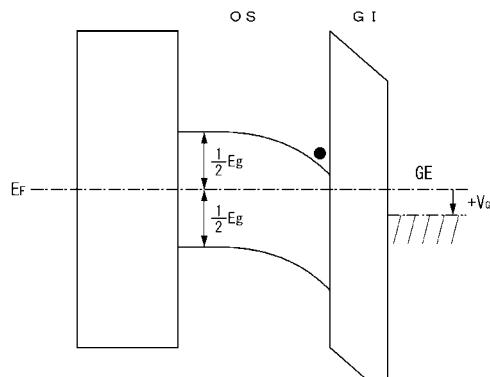

このとき電子は、図8(A)で示すように、ゲート絶縁膜(GI)と酸化物半導体層(OS)との界面付近(酸化物半導体のエネルギー的に安定な最低部)を移動する。

【0048】

また、図8(B)に示すように、ゲート電極(GE)に負の電位が与えられると、少数キャリアであるホールは実質的にゼロであるため、オフ電流は限りなくゼロに近い値となる。

【0049】

10

20

30

40

50

このように、真性又は実質的に真性な酸化物半導体を用いてトランジスタを形成することで、オフ電流を実質的にゼロとすることが可能となる。また、トランジスタの温度特性が良好であり、代表的には、-25から150までの温度範囲において、トランジスタの電流電圧特性において、オン電流、オフ電流、電界効果移動度、S値、及びしきい値電圧の変動がほとんどなく、温度による電流電圧特性の劣化がほとんどない。

#### 【0050】

なお、真性又は実質的に真性な酸化物半導体は、ゲート絶縁膜との界面特性が顕在化する。そのため、ゲート絶縁膜と酸化物半導体との界面を良好にすることが好ましい。具体的には、例えば、VHF帯～マイクロ波帯の電源周波数で生成される高密度プラズマを用いたCVD法で作製される絶縁膜や、スパッタリング法で作製される絶縁膜などを用いることが好ましい。

10

#### 【0051】

なお、酸化物半導体のバンドギャップ( $E_g$ )は、シリコンのバンドギャップと比べると大きいため、アバランシェ降伏が起こりにくい。このため、酸化物半導体を用いたトランジスタはドレイン耐圧が高くなり、高電界が印加されてもオン電流の指数関数的急上昇が生じにくい。

20

#### 【0052】

本実施の形態に係るトランジスタを用いた液晶表示装置は、図1に示すように、画素100に容量素子を設けなくてもよい。したがって、図1に示す画素を図13に示す従来例と比較した場合、容量素子の保持容量 $C_s$ を充電する時間が不要なため、画素100への信号の書き込みを高速に行うことができる。

20

#### 【0053】

なお、容量素子を設ける構成とすることもできる。ただ容量素子を設ける場合にも、トランジスタ101のリーク電流が十分小さいため、保持容量 $C_s$ を小さくすることができ、充電時間を短縮することができる。

#### 【0054】

本実施の形態では、逆スタガー型のボトムゲート構造の薄膜トランジスタの例を示したが、トップゲート構造でもよく、順スタガー型としてもよい。また、チャネルエッチ構造又はチャネルストップ構造を適宜採用することができる。

30

#### 【0055】

なお、液晶素子としては、ネマチック液晶、コレステリック液晶、スマートチック液晶、ディスコチック液晶、サーモトロピック液晶、リオトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶(PDLC)、強誘電液晶、反強誘電液晶、主鎖型液晶、側鎖型高分子液晶、プラズマアドレス液晶(PALC)、バナナ型液晶などを用いることができる。

#### 【0056】

また、液晶表示装置の表示方式は、TNモード、STNモード、IPSモード、FFSモード、MVAモード、PVAモード、ASVモード、ASMモード、OCBモード、ECBモード、FLCモード、AFLCモード、PDLCモード、ゲストホストモード、ブルー相(Blue Phase)モードなどを用いることができる。ただし、これに限定されず、液晶素子及びその駆動方式として様々なものを用いることができる。

40

#### 【0057】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

#### 【0058】

##### (実施の形態2)

本実施の形態では、液晶表示装置の表示方式において、FFSモードを用いた場合について説明する。

#### 【0059】

まず、図2に従来のFFSモードの画素の電極構造の一例を示す。図2は、図13の画素回路における液晶素子5002の部分を示しており、図2(A)は上面図、図2(B)

50

は断面図である。

【0060】

図2では、基板200上に電極201を有し、電極201を覆うように絶縁膜202を有し、絶縁膜202上に電極203を有し、電極203上に液晶層204を有する。電極201又は電極203の一方が画素電極であり、他方が共通電極である。電極203はスリット207(開口部)を有している。電極201はプレート状(一面を覆う形状)の電極である。絶縁膜202は単層でも積層でもよい。

【0061】

FFSモードにより液晶層204に横電界が印加されることで、液晶205は横方向に配向されるため、液晶表示装置の視野角を広くすることができる。

10

【0062】

従来、図2に示すように、電極201をプレート状とし、電極201と電極203とが重なった部分に容量素子206(保持容量C<sub>s</sub>)が形成される構造となっていた。この場合、実施の形態1で説明したように、保持容量C<sub>s</sub>の充電時間の分だけ、書き込み時間が長くなってしまう。

【0063】

そのため、本実施の形態におけるFFSモードは、図3のような電極構造を有することを特徴とする。図3は、図1の画素回路における液晶素子102の部分を示しており、図3(A)は上面図、図3(B)は断面図である。

20

【0064】

図2と異なる点は、図3(B)に示すように、電極301と電極303とが重なっていない、あるいは重なっても、その面積が従来のものより格段に小さい点である。図3(B)に示した構造の場合、電極301と電極303との間に容量素子が形成されず、また、電極301と電極303との間の寄生容量も大きく減少する。また、電極301と電極303との端部を一致させることで、電極301と電極303とにより生じる横電界が印加されやすくなる。

30

【0065】

すなわち、電極301と電極303とが重ならず、且つ電極301の端部と電極303の端部とが一致する構成とすることで、FFSモードによる横方向への配向の効果と、保持容量C<sub>s</sub>低減による書き込み時間短縮の効果が相乗的に得ることができる。電極301を形成する際にスリット310(開口部)を設ける様にエッチングを施し、当該スリット310上に電極303を形成すればよい。この構成は、作製工程の微差により、電極301が電極303の下部にわずかに回り込んだ場合や両電極の端部にわずかに間隔が生じた場合も含むものとする。

30

【0066】

なお、図3(B)において、電極301の幅W1を電極303の幅W2より広くすることで、液晶層204に印加される横方向の電界が印加されやすくなるため、特に有効である。

【0067】

また、図3(B)では電極303の間隔(スリット310の幅)は電極301の幅W1と等しく書かれているが、W1を電極303の間隔より狭くして、いわゆるオフセット状態とすることもできる。

40

【0068】

図3の電極構造は、本発明の一態様に係る酸化物半導体をトランジスタに用いた場合に特に有効である。真性又は実質的に真性な酸化物半導体を用い、トランジスタのオフ電流を $1 \times 10^{-17} \text{ A} / \mu\text{m}$ 以下とすることで、画素に容量素子を設けなくてもよくなるため、信号の書き込み時間を短縮することができる。

【0069】

なお、容量素子を設ける構成とすることもできる。ただ容量素子を設ける場合にも、トランジスタのリーク電流が十分小さいため、保持容量C<sub>s</sub>を小さくすることができ、充電

50

時間を短縮することができる。その場合、図3において、電極301と電極303の一部を重なすることで、面積の小さい容量素子を形成すればよい。表示領域を狭くする必要がないため有効である。

【0070】

図3の電極構造を用いて、図1の画素を形成したものを図4に示す。図4(A)は上面図、図4(B)は断面図である。A-A'部は図1におけるトランジスタ101を示し、B-B'部は図1における液晶素子102を示しており図3の電極構造を採用している。

【0071】

A-A'部には、基板200と基板410と間にゲート電極401、ゲート絶縁膜402、酸化物半導体層403、電極404、及び電極405が設けられ、トランジスタ400が形成されている。電極404と電極405とは、一方がソース電極であり他方がドレイン電極である。酸化物半導体層403は、本発明の一態様に係る真性又は実質的に真性な酸化物半導体を用いることができる。

10

【0072】

そして電極405が、電極303と電気的に接続されている。図4は一例であり、電極405が、電極301と電気的に接続されてもよい。また、ゲート電極401と電極301とを同層に設ける構成、電極404と電極405と電極301とを同層に設ける構成、又は電極404と電極405と電極303とを同層に設ける構成とすることで、工程数を削減してもよい。

20

【0073】

電極301と電極303としては、モリブデン(Mo)、チタン(Ti)、クロム(Cr)、タンタル(Ta)、タングステン(W)、アルミニウム(Al)、銅(Cu)、ネオジム(Nd)、スカンジウム(Sc)等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

30

【0074】

また、導電性の金属酸化物である酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )、酸化インジウム酸化スズ合金( $In_2O_3-SnO_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛合金( $In_2O_3-ZnO$ )等の各種金属酸化物材料を用いることができる。また、これらにシリコン若しくは酸化シリコンを含ませてもよい。これらは透光性を有する材料である。

30

【0075】

そして、電極301と電極303との少なくとも一方を、上記の透光性を有する材料で形成しておくことが好ましい。

【0076】

なお、図4では、逆スタガー型のボトムゲート構造の薄膜トランジスタを示したが、トップゲート構造でもよく、順スタガー型としてもよい。また、チャネルエッチ構造又はチャネルトップ構造を適宜採用することができる。

40

【0077】

また、図示していないが配向膜、カラーフィルタ、遮光膜、スペーサ、封止材等を適宜設けることができる。

【0078】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0079】

(実施の形態3)

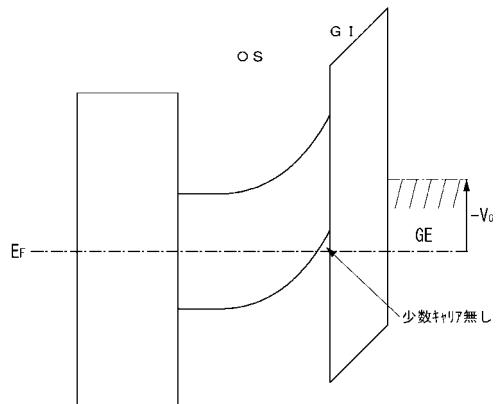

本実施の形態では、半導体装置の作製方法の一例について、図9を用いて説明する。

【0080】

まず、絶縁表面を有する基板1000上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極1001を形成する。形成されたゲート電極1001の端部がテーパであると、上に積層するゲート絶縁膜の被覆性が向上するため好ましい。

50

【0081】

絶縁表面を有する基板 1000 に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。たとえば、各種ガラス基板を用いることができる。

#### 【0082】

ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が 730 以上のもとのを用いると良い。また、ガラス基板には、例えば、アルミニノシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。酸化ホウ素 ( $B_2O_3$ ) と比較して酸化バリウム ( $BaO$ ) を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$  より  $BaO$  を多く含むガラス基板を用いることが好ましい。

10

#### 【0083】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いても良い。他にも、結晶化ガラス基板などを用いることができる。また、プラスチック基板等も適宜用いることができる。

#### 【0084】

下地膜となる絶縁膜を基板 1000 とゲート電極 1001 との間に設けてもよい。下地膜は、基板 1000 からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

20

#### 【0085】

また、ゲート電極 1001 は、モリブデン ( $Mo$ )、チタン ( $Ti$ )、クロム ( $Cr$ )、タンタル ( $Ta$ )、タングステン ( $W$ )、アルミニウム ( $Al$ )、銅 ( $Cu$ )、ネオジム ( $Nd$ )、スカンジウム ( $Sc$ ) 等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

#### 【0086】

次いで、ゲート電極 1001 上にゲート絶縁膜 1002 を形成する。

#### 【0087】

ゲート絶縁膜 1002 は、プラズマ CVD 法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。スパッタリング法により酸化シリコン層を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

30

#### 【0088】

ここで、ゲート絶縁膜 1002 上に形成される真性又は実質的に真性な酸化物半導体（高純度化された酸化物半導体）は、界面準位、界面電荷に対して極めて敏感である。そのため、界面を形成するゲート絶縁膜 1002 は、高品質化が要求される。

#### 【0089】

例えば、 $\mu$  波（例えば、周波数 2.45 GHz）を用いた高密度プラズマ CVD は、緻密で絶縁耐圧の高い高品質な絶縁膜を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁膜とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

40

#### 【0090】

もちろん、ゲート絶縁膜 1002 として良質な絶縁膜を形成できるものであれば、スパッタリング法やプラズマ CVD 法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁膜の膜質、酸化物半導体との界面特性が改質される絶縁膜であっても良い。いずれにしても、ゲート絶縁膜としての膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

#### 【0091】

50

ゲート絶縁膜1002は、ゲート電極1001側から窒化物絶縁膜と、酸化物絶縁膜との積層構造とすることもできる。例えば、第1のゲート絶縁膜としてスパッタリング法により膜厚50nm以上200nm以下の窒化シリコン膜( $\text{SiN}_y$  ( $y > 0$ ))を形成し、第1のゲート絶縁膜上に第2のゲート絶縁膜として膜厚5nm以上300nm以下の酸化シリコン膜( $\text{SiO}_x$  ( $x > 0$ ))を積層して、膜厚100nmのゲート絶縁膜とする。ゲート絶縁膜の膜厚は、トランジスタに要求される特性によって適宜設定すればよく350nm乃至400nm程度でもよい。

#### 【0092】

次いで、ゲート絶縁膜1002上に、膜厚2nm以上200nm以下の酸化物半導体膜1003を形成する(図9(A)参照。)。

10

#### 【0093】

酸化物半導体膜1003は、 $\text{In-Sn-Ga-Zn-O}$ 、 $\text{In-Ga-Zn-O}$ 、 $\text{In-Sn-Zn-O}$ 、 $\text{In-Al-Zn-O}$ 、 $\text{Sn-Ga-Zn-O}$ 、 $\text{Al-Ga-Zn-O}$ 、 $\text{Sn-Al-Zn-O}$ 、 $\text{In-Zn-O}$ 、 $\text{Sn-Zn-O}$ 、 $\text{Al-Zn-O}$ 、 $\text{Zn-Mg-O}$ 、 $\text{Sn-Mg-O}$ 、 $\text{In-Mg-O}$ 、 $\text{In-O}$ 、 $\text{Sn-O}$ 、 $\text{Zn-O}$ などを用いて形成することができる。

#### 【0094】

また、 $\text{In-A-B-O}$ で表現される酸化物半導体材料を用いても良い。ここで、Aは、ガリウム(Ga)やアルミニウム(Al)などの13族元素、シリコン(Si)やゲルマニウム(Ge)に代表される14族元素などから選択される—または複数種類の元素を表す。また、Bは、亜鉛(Zn)に代表される12族元素から選択される—又は複数種類の元素を表す。なお、In、A、Bの含有量は任意であり、Aの含有量がゼロの場合を含む。一方、InおよびBの含有量はゼロではない。すなわち、上述の表記には、 $\text{In-Ga-Zn-O}$ や $\text{In-Zn-O}$ などが含まれる。

20

#### 【0095】

中でも、 $\text{In-Ga-Zn-O}$ 系の酸化物半導体材料は、無電界時の抵抗が十分に高くオフ電流を十分に小さくすることが可能であり、また、電界効果移動度も高いため、半導体装置に用いる半導体材料としては好適である。

#### 【0096】

$\text{In-Ga-Zn-O}$ 系の酸化物半導体材料の代表例としては、 $\text{InGaO}_3$  ( $\text{ZnO}$ )<sub>m</sub> ( $m > 0$ )で表記されるものがある。また、Gaに代えてMを用い、 $\text{InMO}_3$  ( $\text{ZnO}$ )<sub>m</sub> ( $m > 0$ )のように表記される酸化物半導体材料がある。ここで、Mは、ガリウム(Ga)、アルミニウム(Al)、鉄(Fe)、ニッケル(Ni)、マンガン(Mn)、コバルト(Co)などから選ばれた一の金属元素または複数の金属元素を示す。例えば、Mとしては、Ga、GaおよびAl、GaおよびFe、GaおよびNi、GaおよびMn、GaおよびCoなどを適用することができる。なお、上述の組成はあくまでも一例に過ぎないことを付記する。

30

#### 【0097】

本実施の形態では、酸化物半導体膜1003を、 $\text{In-Ga-Zn-O}$ 系の金属酸化物をターゲットとして用い、スパッタ法により形成する。

40

#### 【0098】

酸化物半導体膜1003をスパッタリング法で作製するためのターゲットとしては、例えば、In、Ga、およびZnを含むターゲットの組成比を、 $\text{In:Ga:Zn} = 1:x:y$ とする。ここで、xは0以上2以下、yは1以上5以下である。例えば、 $\text{In:Ga:Zn} = 1:1:1$  [atom比] ( $x = 1$ 、 $y = 1$ ) (すなわち、 $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO} = 1:1:2$  [mole数比]) の組成比を有するターゲットなどを用いても良い。また、ターゲットとして $\text{In:Ga:Zn} = 1:1:0.5$  [atom比] の組成比を有する金属酸化物、または $\text{In:Ga:Zn} = 1:1:2$  [atom比]、 $\text{In:Ga:Zn} = 1:0:1$  [atom比] ( $x = 0$ 、 $y = 1$ ) の組成比を有する金属酸化物を用いることもできる。

50

## 【0099】

減圧状態に保持された処理室内に基板 1000 を保持し、基板 1000 を室温又は 400 未満の温度に加熱する。そして、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、金属酸化物をターゲットとして酸化物半導体膜 1003 を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した処理室は、例えば、水素原子、水 (H<sub>2</sub>O) など水素原子を含む化合物 (より好ましくは炭素原子を含む化合物も) 等が排気されるため、当該処理室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。また、クライオポンプにより処理室内に残留する水分を除去しながらスパッタ成膜を行うことで、酸化物半導体膜 1003 を成膜する際の基板温度は室温から 400 未満とすることができる。

10

## 【0100】

次いで、酸化物半導体膜を第 2 のフォトリソグラフィ工程により島状の酸化物半導体層 1004 に加工する (図 9 (B) 参照。)。

## 【0101】

次いで、ゲート絶縁膜 1002、及び酸化物半導体層 1004 上に、導電膜を形成する。導電膜をスパッタリング法や真空蒸着法で形成すればよい。導電膜としては、アルミニウム (Al)、クロム (Cr)、銅 (Cu)、タンタル (Ta)、チタン (Ti)、モリブデン (Mo)、タンクステン (W) から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、Si、Ti、Ta、W、Mo、Cr、Nd、Sc、Y など Al 膜に生ずるヒロックやウィスカーの発生を防止する元素が添加されている Al 材料を用いることで耐熱性を向上させることができる。

20

## 【0102】

また、導電膜は、単層構造でも、2 層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する 2 層構造、Ti 膜と、その Ti 膜上に重ねてアルミニウム膜を積層し、さらにその上に Ti 膜を成膜する 3 層構造などが挙げられる。例えば、Al、Cu などの金属層の上面もしくは下面の一方または双方に Cr、Ta、Ti、Mo、W などの高融点金属層を積層させた構成としても良い。

30

## 【0103】

また、導電膜として、導電性の金属酸化物である酸化インジウム (In<sub>2</sub>O<sub>3</sub>)、酸化スズ (SnO<sub>2</sub>)、酸化亜鉛 (ZnO)、酸化インジウム酸化スズ合金 (In<sub>2</sub>O<sub>3</sub>–SnO<sub>2</sub>、ITO と略記する)、酸化インジウム酸化亜鉛合金 (In<sub>2</sub>O<sub>3</sub>–ZnO) または前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

## 【0104】

本実施の形態では、導電膜としてチタン (Ti) を用いた。

40

## 【0105】

第 3 のフォトリソグラフィ工程により、ソース電極 1005、ドレイン電極 1006 を形成した (図 9 (C) 参照。)。

## 【0106】

なお、導電膜のエッティングの際に、酸化物半導体層 1004 は除去されないようにそれぞれの材料及びエッティング条件を適宜調節する。

## 【0107】

なお、第 3 のフォトリソグラフィ工程では、酸化物半導体層 1004 は一部のみがエッティングされ、溝部 (凹部) を有する酸化物半導体層となることもある。

## 【0108】

50

次に、酸化物半導体層 1004 の一部に接し保護絶縁膜となる酸化物絶縁膜 1007 を形成する(図9( D )参照。)。

【0109】

本実施の形態では、酸化物半導体層 1004 がソース電極 1005、ドレイン電極 1006 と重ならない領域において、酸化物半導体層 1004 と酸化物絶縁膜 1007 とが接するように形成する。

【0110】

本実施の形態では、酸化物絶縁膜 1007 として、島状の酸化物半導体層 1004、ソース電極 1005、ドレイン電極 1006 まで形成された基板 1000 を室温又は 100 未満の温度に加熱し、水素及び水分が除去された高純度酸素を含むスパッタガスを導入しシリコン半導体のターゲットを用いて、欠陥を含む酸化シリコン層を成膜する。

【0111】

なお、処理室内の残留水分を除去しつつ酸化物絶縁膜 1007 を成膜することが好ましい。酸化物半導体層 1004 及び酸化物絶縁膜 1007 に水素、水酸基又は水分が含まれないようにするためである。

【0112】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した処理室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該処理室で成膜した酸化物絶縁膜 1007 に含まれる不純物の濃度を低減できる。

【0113】

なお、酸化物絶縁膜 1007 として、酸化シリコン層に代えて、酸化窒化シリコン層、酸化アルミニウム層、または酸化窒化アルミニウム層などを用いることもできる。

【0114】

さらに、酸化物絶縁膜 1007 と酸化物半導体層 1004 とを接した状態で 100 乃至 400 で加熱処理を行ってもよい。本実施の形態における酸化物絶縁膜 1007 は欠陥を多く含むため、この加熱処理によって酸化物半導体層 1004 中に含まれる水素、水分、水酸基又は水素化物などの不純物を酸化物絶縁膜 1007 に拡散させ、酸化物半導体層 1004 中に含まれる該不純物をより低減させることができる。また、ここでの加熱処理により、酸化物絶縁膜 1007 に含まれる酸素が酸化物半導体層 1004 に供給される。

【0115】

以上の工程により、酸化物半導体層 1004 を有するトランジスタ 1008 を作製することができる(図9( E )参照。)。

【0116】

酸化物半導体層 1004 は、水素等の不純物が十分に除去され、酸素が供給されることにより高純度化されている。具体的には、酸化物半導体層 1004 の水素濃度は  $5 \times 10^{-19} / \text{cm}^3$  以下、望ましくは  $5 \times 10^{-18} / \text{cm}^3$  以下、より望ましくは  $5 \times 10^{-17} / \text{cm}^3$  以下であり、従来と比べて十分に小さいキャリア濃度の値(例えば、 $1 \times 10^{-12} / \text{cm}^3$  未満、望ましくは、 $1.45 \times 10^{-10} / \text{cm}^3$  以下)をとる。このように、真性または実質的に真性な酸化物半導体を用いることで、オフ電流が  $1 \times 10^{-17} \text{ A} / \mu\text{m}$  以下のトランジスタ 1008 を得ることができる。上記の水素濃度は、例えば、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectroscopy)等で測定することができる。また、キャリア濃度は、酸化物半導体を用いて MOS キャパシタを作製し、例えば、CV 測定の結果(CV 特性)等を評価することによって求めることができる。

【0117】

また、酸化物絶縁膜 1007 上に保護絶縁膜 1009 を設けてもよい。本実施の形態で

10

20

30

40

50

は、保護絶縁膜 1009 を酸化物絶縁膜 1007 上に形成する。保護絶縁膜 1009 としては、窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、又は窒化酸化アルミニウム膜などを用いる。

【0118】

本実施の形態の方法で作製したトランジスタ 1008 を実施の形態 1、2 の液晶表示装置に用いることができる。画素に容量素子を配置しなくてもよい。画素に容量素子を配置しない場合、容量素子の保持容量  $C_s$  を充電する時間が不要になり、全体の充電時間を短縮することができる。

【0119】

また、上記の工程は、エレクトロルミネセンス表示装置、電子インクを用いた表示装置などのバックプレーン（トランジスタが形成された基板）の製造に用いることができる。上記の工程は、400 以下の温度で行われるため、厚さが 1mm 以下で、一辺が 1m を超えるガラス基板を用いる製造工程にも適用することができる。また、400 以下の処理温度で全ての工程を行うことができるので、表示装置を製造するために多大なエネルギーを消費しないで済む。

【0120】

なお、本実施の形態では、逆スタガー型のボトムゲート構造の薄膜トランジスタを示したが、トップゲート構造でもよく、順スタガー型としてもよい。また、チャネルエッチ構造又はチャネルトップ構造を適宜採用することができる。

【0121】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0122】

（実施の形態 4）

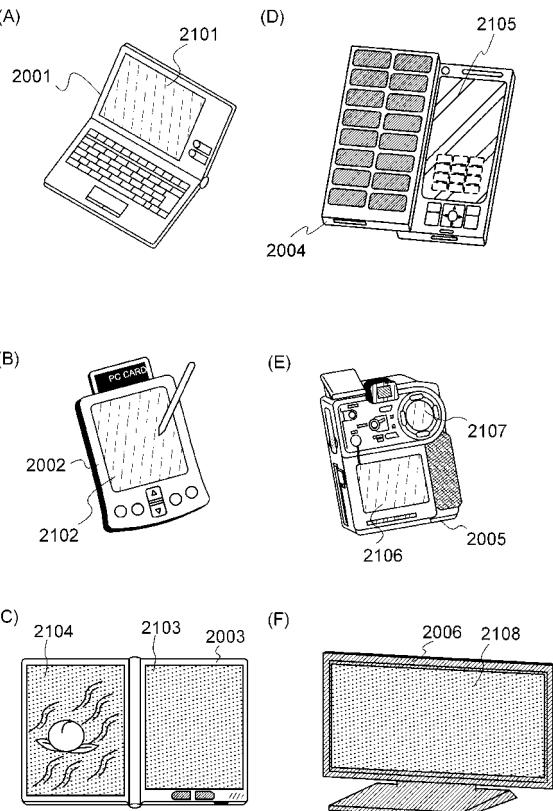

本実施の形態では、先の実施の形態で得られる表示装置を搭載した電子機器の一例を図 10 に示す。

【0123】

図 10 (A) は、ノート型のパーソナルコンピュータである。本体 2001 に表示部 2101 を有する。

【0124】

図 10 (B) は、携帯情報端末 (PDA) である。本体 2002 に表示部 2102 を有する。

【0125】

図 10 (C) には、電子ペーパーの一例として、電子書籍を示す。本体 2003 に表示部 2103 及び表示部 2104 を有する。

【0126】

図 10 (D) は、携帯電話機である。本体 2004 に表示部 2105 を有する。

【0127】

図 10 (E) は、デジタルカメラである。本体 2005 に表示部 2106 及び表示部 2107 を有する。

【0128】

図 10 (F) は、テレビジョン装置である。本体 2006 に表示部 2108 を有する。

【0129】

図 10 (A) ~ (F) の電子機器において、表示部 2101 ~ 2108 に先の実施の形態に係る表示装置を設けることで、画素に容量素子を配置しない又は容量値を極力小さくすることができ、信号の書き込みを高速に行うことができる。また、オーバードライブ駆動又は倍速駆動等を効果的に行うことができ、電子機器の性能を大幅に向上させることができる。

【0130】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【実施例 1】

10

20

30

40

50

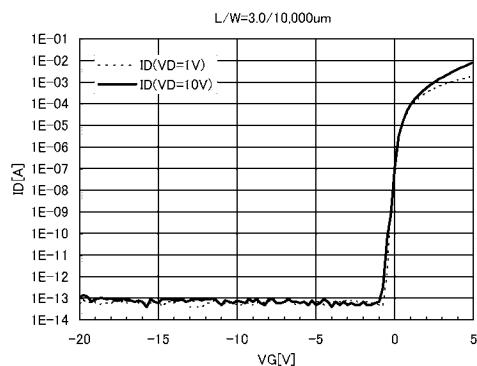

## 【0131】

実施の形態3の方法により得られた真性又は実質的に真性な酸化物半導体膜を用いたトランジスタの初期特性について、 $V_G$  -  $I_D$  特性を図12に示す。

## 【0132】

図12は、トランジスタのチャネル幅 $W$ を $1 \times 10^4 \mu\text{m}$ 、チャネル長 $L$ を $3 \mu\text{m}$ 、基板温度を室温としたサンプルの測定結果を示しており、オフ電流において測定器（パラメータ・アナライザ、Agilent 4156C；Agilent社製）測定限界である $1 \times 10^{-13} \text{ A}$ 以下、サブスレッショルドスイング値（S値）において $0.1 \text{ V}/\text{dec}$ であった。なお、オフ電流は、チャネル幅 $1 \mu\text{m}$ 当たりに換算すると、 $1 \times 10^{-7} \text{ A}/\mu\text{m}$ である。また、サンプルでは、チャネル幅 $W = 50 \mu\text{m}$ 、チャネル長 $L = 3 \mu\text{m}$ のトランジスタを200個並列に接続して、チャネル幅 $W = 1 \times 10^4 \mu\text{m}$ 、チャネル長 $L = 3 \mu\text{m}$ のトランジスタを作製した。

10

## 【0133】

本実施例は、上記実施の形態と適宜組み合わせて実施することができる。

## 【符号の説明】

## 【0134】

|      |         |    |

|------|---------|----|

| 100  | 画素      | 20 |

| 101  | トランジスタ  |    |

| 102  | 液晶素子    |    |

| 103  | 配線      |    |

| 104  | 配線      |    |

| 105  | ノード     |    |

| 200  | 基板      |    |

| 201  | 電極      |    |

| 202  | 絶縁膜     |    |

| 203  | 電極      |    |

| 204  | 液晶層     |    |

| 205  | 液晶      |    |

| 206  | 容量素子    |    |

| 207  | スリット    | 30 |

| 301  | 電極      |    |

| 303  | 電極      |    |

| 310  | スリット    |    |

| 400  | トランジスタ  |    |

| 401  | ゲート電極   |    |

| 402  | ゲート絶縁膜  |    |

| 403  | 酸化物半導体層 |    |

| 404  | 電極      |    |

| 405  | 電極      |    |

| 410  | 基板      | 40 |

| 1000 | 基板      |    |

| 1001 | ゲート電極   |    |

| 1002 | ゲート絶縁膜  |    |

| 1003 | 酸化物半導体膜 |    |

| 1004 | 酸化物半導体層 |    |

| 1005 | ソース電極   |    |

| 1006 | ドレイン電極  |    |

| 1007 | 酸化物絶縁膜  |    |

| 1008 | トランジスタ  |    |

| 1009 | 保護絶縁膜   | 50 |

5 0 0 0 画素

5 0 0 1 トランジスタ

5 0 0 2 液晶素子

5 0 0 3 容量素子

5 0 0 4 配線

5 1 0 1 破線

5 1 0 2 破線

5 1 0 3 実線

5 1 0 4 実線

2 0 0 1 ~ 2 0 0 6 本体

2 1 0 1 ~ 2 1 0 8 表示部

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

(A) A-A' 断面エレキ-バンド図

(B) 電圧印加時のエレキ-バンド図

【図8】

(A) B-B' 断面エレキ-バンド図 (+V\_G)

(B) B-B' 断面エレキ-バンド図 (-V\_G)

【図9】

【図10】

【 図 1 1 】

【 図 1 3 】

【図 1 2】

---

フロントページの続き

F ターム(参考) 2H193 ZA04 ZE01 ZE04 ZP02 ZP03 ZQ16 ZR12

5F110 AA06 BB01 CC05 CC07 DD01 DD02 DD03 DD04 DD07 DD13

DD14 DD15 DD17 EE02 EE03 EE04 EE06 EE14 FF01 FF02

FF03 FF04 FF09 FF28 FF30 GG01 GG06 GG22 GG24 GG33

GG34 GG35 GG43 HK02 HK03 HK04 HK06 HK07 HK21 HK22

HK32 HK33 HL02 HL03 HL04 HL06 HL07 NN02 NN22 NN23

NN34 NN40