(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5119283号

(P5119283)

(45) 発行日 平成25年1月16日(2013.1.16)

(24) 登録日 平成24年10月26日(2012.10.26)

(51) Int.Cl.

F 1

|        |        |           |        |             |

|--------|--------|-----------|--------|-------------|

| G 11 B | 7/007  | (2006.01) | G 11 B | 7/007       |

| G 11 B | 20/12  | (2006.01) | G 11 B | 20/12       |

| G 11 B | 20/10  | (2006.01) | G 11 B | 20/10 301   |

| G 11 B | 7/0045 | (2006.01) | G 11 B | 20/10 341 C |

| G 11 B | 7/005  | (2006.01) | G 11 B | 7/0045 D    |

請求項の数 6 (全 13 頁) 最終頁に続く

(21) 出願番号

特願2010-48577(P2010-48577)

(22) 出願日

平成22年3月5日(2010.3.5)

(65) 公開番号

特開2011-187095(P2011-187095A)

(43) 公開日

平成23年9月22日(2011.9.22)

審査請求日

平成24年8月3日(2012.8.3)

早期審査対象出願

(73) 特許権者 50918944

日立コンシーマエレクトロニクス株式会社

東京都千代田区大手町二丁目2番1号

(74) 代理人 100100310

弁理士 井上 学

(74) 代理人 100098660

弁理士 戸田 裕二

(72) 発明者 池田 政和

神奈川県横浜市戸塚区吉田町292番地

株式会社日立製作所 コンシーマエレクトロニクス研究所内

最終頁に続く

(54) 【発明の名称】記録媒体、再生及び記録方法、再生及び記録装置

## (57) 【特許請求の範囲】

## 【請求項 1】

データを記録する複数のクラスタを記録する領域を有する記録層を複数層備えた記録媒体において、

記録するクラスタに付加され、かつ、クラスタの識別とクラスタ内の位置を示す第1のアドレスが記録される領域と、

前記クラスタに同期してデータを記録するトラックにウォブリング重畳されて記録されていて、クラスタの識別とクラスタ内の位置を含む情報を示す第2のアドレスと、を有し、

前記第1のアドレスは、実データに付加されて記録されるアドレスであって、

前記第2のアドレスは、記録媒体における物理的な記録位置を示すアドレスであり、前記複数の記録層の番号を示す層番号アドレスと、前記複数のクラスタのデータ位置を示すクラスタ番号アドレスと、前記クラスタの物理的な位置を特定するクラスタ内カウント値と、により構成され、

前記第2のアドレスの下位2ビットの規則性の切り替え有無を示し、かつ、前記クラスタ番号アドレスの拡張ビットとして使用され、かつ、記録媒体に記録されない仮想ビットが、該第2のアドレスに仮想的に埋め込まれており、

前記下位2ビットの規則性は、インクリメントの繰り返しであるか否かであることを特徴とする記録媒体。

## 【請求項 2】

10

20

前記請求項 1 に記載した記録媒体にデータを記録する記録方法であって、記録された前記第 2 のアドレスを前記記録媒体から読み込み、

前記第 2 のアドレスに仮想的に埋め込まれた前記仮想ビットを復元し、

前記復元された仮想ビットに基づき、前記第 2 のアドレスを検出し、

前記検出した第 2 のアドレスにより、前記記録媒体にデータを記録することを特徴とする記録方法。

**【請求項 3】**

前記請求項 1 に記載した記録媒体にデータを記録する記録装置であって、記録された前記第 2 のアドレスを前記記録媒体から読み込むピックアップと、

前記第 2 のアドレスに仮想的に埋め込まれた前記仮想ビットを復元し、前記復元された仮想ビットに基づき、前記第 2 のアドレスを検出するアドレス再生回路と、

前記検出した第 2 のアドレスにより、前記記録媒体にデータを記録するデータ記録回路と、

を有することを特徴とする記録装置。

**【請求項 4】**

前記請求項 1 に記載した記録媒体からデータを再生する再生方法であって、記録された前記第 2 のアドレスを前記記録媒体から読み込み、

前記第 2 のアドレスに仮想的に埋め込まれた前記仮想ビットを復元し、

前記復元された仮想ビットに基づき、前記第 2 のアドレスを検出し、

前記検出した第 2 のアドレスにより、前記記録媒体からデータを再生することを特徴とする再生方法。

**【請求項 5】**

前記請求項 1 に記載した記録媒体からデータを再生する再生装置であって、記録された前記第 2 のアドレスを前記記録媒体から読み込むピックアップと、

前記第 2 のアドレスに仮想的に埋め込まれた前記仮想ビットを復元し、前記復元された仮想ビットに基づき、前記第 2 のアドレスを検出するアドレス再生回路と、

前記検出した第 2 のアドレスにより、前記記録媒体からデータを再生するデータ再生回路と、

を有することを特徴とする再生装置。

**【請求項 6】**

データを記録する複数のクラスタを記録する領域を有する記録層を複数層備えた記録媒体におけるアドレスの記録方法であって、

記録するクラスタに付加され、かつ、クラスタの識別とクラスタ内の位置を示す第 1 のアドレスを記録する領域を設け、

前記クラスタに同期してデータを記録するトラックにウォブリング重畠してクラスタの識別とクラスタ内の位置を含む情報を示す第 2 のアドレスを記録し、

前記第 1 のアドレスは、実データに付加して記録されるアドレスであって、

前記第 2 のアドレスは、記録媒体における物理的な記録位置を示すアドレスであり、前記複数の記録層の番号を示す層番号アドレスと、前記複数のクラスタのデータ位置を示すクラスタ番号アドレスと、前記クラスタの物理的な位置を特定するクラスタ内カウント値と、により構成され、

前記第 2 のアドレスの下位 2 ビットの規則性の切り替え有無を示し、かつ、前記クラスタ番号アドレスの拡張ビットとして使用され、かつ、記録媒体に記録されない仮想ビットが、該第 2 のアドレスに仮想的に埋め込まれており、

前記下位 2 ビットの規則性は、インクリメントの繰り返しであるか否かであることを特徴とするアドレスの記録方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、アドレスが記録されている記録媒体、例えば光ディスク、光ディスクの再生

10

20

30

40

50

及び記録方法、記録媒体よりデータの記録再生を行う再生装置、記録装置に関する。

【背景技術】

【0002】

特許文献1の図6において、Blu-ray Discのアドレス情報の相関を示しており、段落[0010]の記載「アドレスユニット番号(AUN)は、図6で示したように、物理的セクタ番号と連携し、かつ物理的ADIP(Address In Pre-groove)アドレスと連携するので、記録位置を探索するための参照情報として有用に使われる。」が示されている。図によれば、セクタ単位のデータに1アドレス割り付けられている物理的セクタ番号(Physical Sector Number, PSN)とウォブルに埋め込まれる物理的ADIPアドレス(Physical ADIP Address, PAA)との関係において、 $32^*PSN = 3^*PAA$ という関係であるが、PSNのビット31からビット27の5ビットはPAAに対応するビットを割り付けられていない。10

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008-41243号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1のようなビット割り付けにおいて、PSNが従来の27ビットで表現されるデータ量より多くなってしまう場合、ウォブルに埋め込むべきPAAのビット数が足りなくなってしまう。また、PAAのビット数を拡張する場合には、ウォブルアドレス構造の大幅な改造が必要となってしまう。20

【0005】

本発明の目的は、大幅なウォブル構造改造を実施しないでウォブルアドレスの拡張が可能な記録媒体、アドレス生成及び検出方法、再生及び記録装置を提供することである。

【課題を解決するための手段】

【0006】

上記問題を解決するために、ウォブルアドレスの一部あるいは全てに埋め込んだ情報の有無や規則の差異により表されて、ディスクに記録しない仮想ビットを生成する。

【発明の効果】

【0007】

本発明により、従来のウォブルアドレス構造のビット構成のままアドレス拡張が可能となる。

【図面の簡単な説明】

【0008】

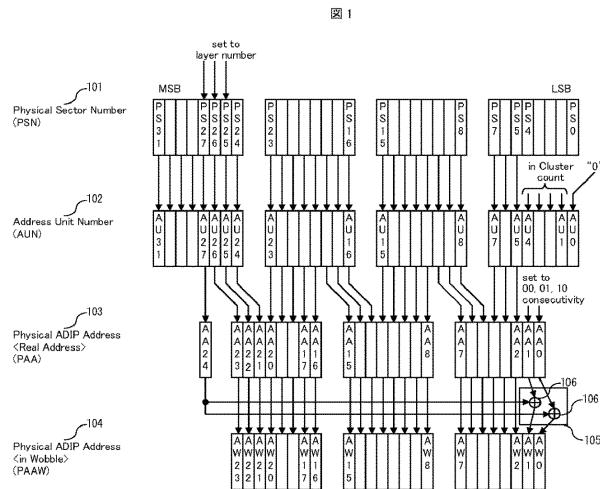

【図1】本発明の第1の実施例である多層光ディスクのアドレスの相関図である。

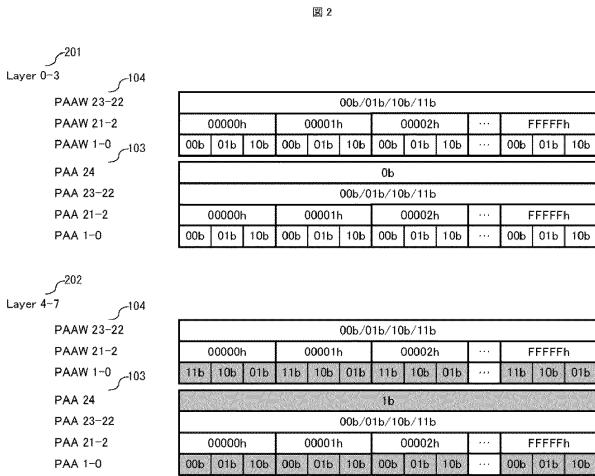

【図2】本発明の第1の実施例におけるアドレス検出のタイミング図である。

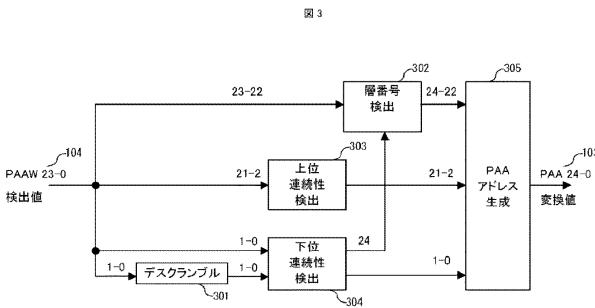

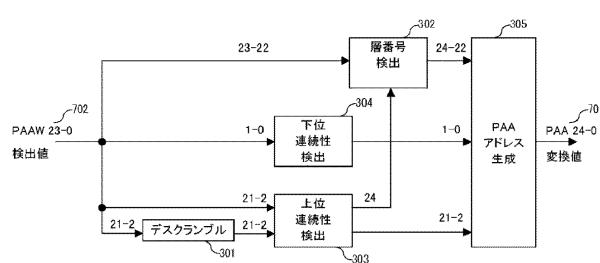

【図3】本発明の第1の実施例におけるアドレス検出の検出回路図である。

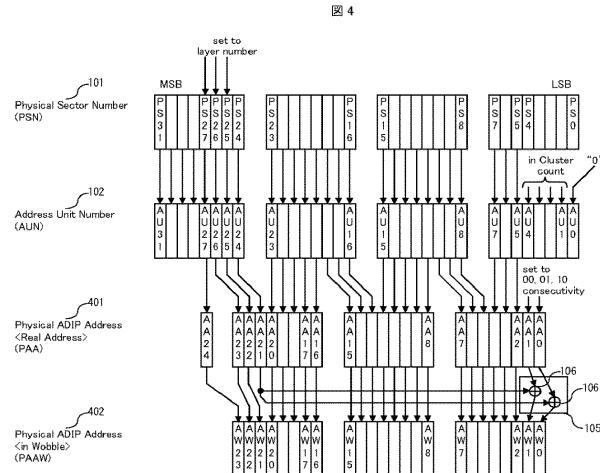

【図4】本発明の第2の実施例である多層光ディスクのアドレスの相関図である。

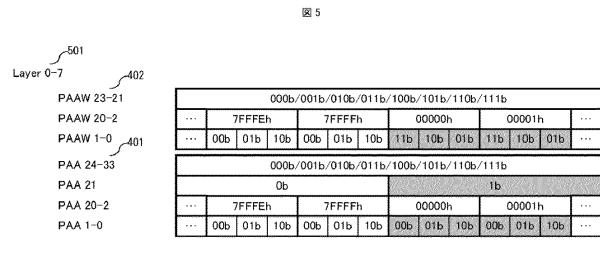

【図5】本発明の第2の実施例におけるアドレス検出のタイミング図である。40

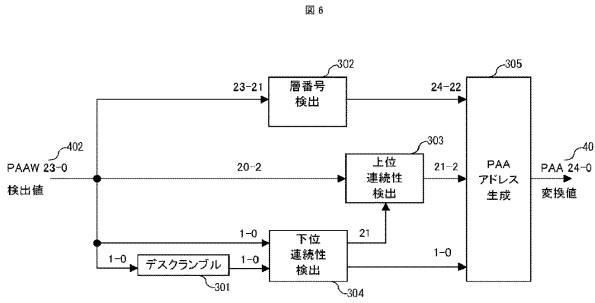

【図6】本発明の第2の実施例におけるアドレス検出の検出回路図である。

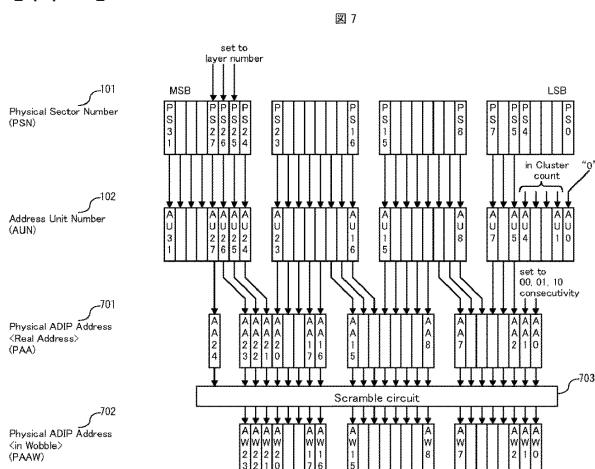

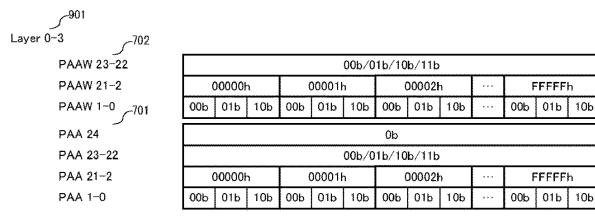

【図7】本発明の第3の実施例である多層光ディスクのアドレスの相関図である。

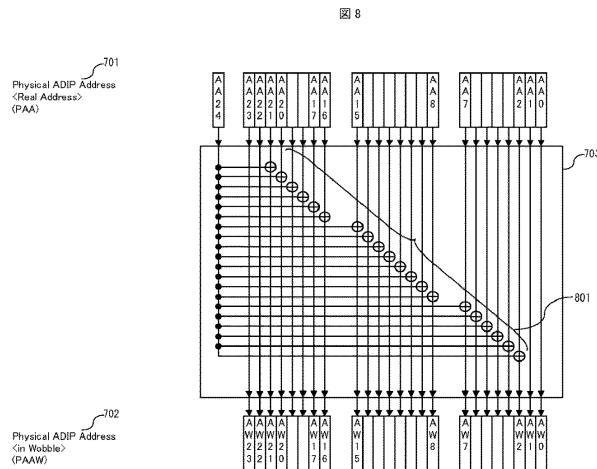

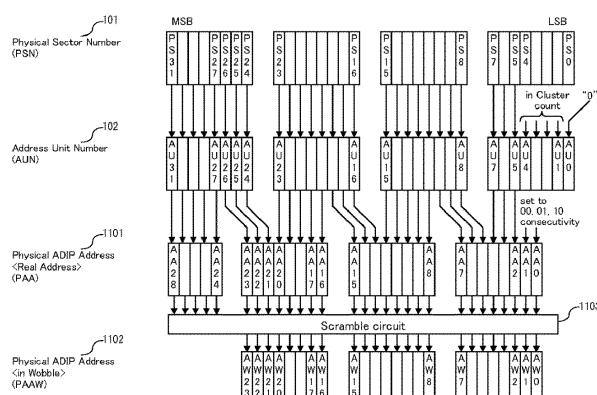

【図8】本発明の第3の実施例であるスクランブル回路の一例である。

【図9】本発明の第3の実施例におけるアドレス検出のタイミング図である。

【図10】本発明の第3の実施例におけるアドレス検出の検出回路図である。

【図11】本発明の第4の実施例である光ディスクのアドレスの相関図である。

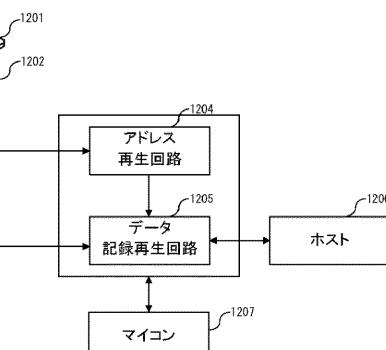

【図12】本発明の第1の実施例である光ディスク記録再生装置である。

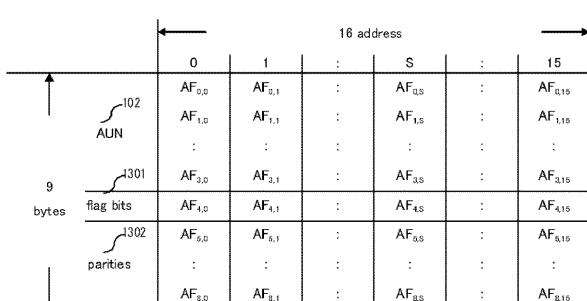

【図13】多層光ディスクのアドレスフィールド構造図である。

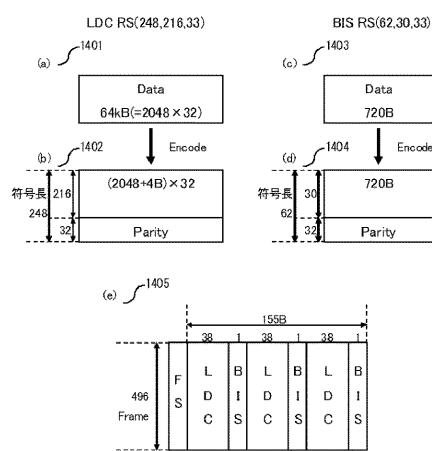

【図14】多層光ディスクのデータ構造、ECC構造、フレーム構造図である。

【発明を実施するための形態】

10

20

30

40

50

## 【0009】

以下、図面を参照して本発明の実施例について説明する。

## 【0010】

図1は本発明の第1の実施例である多層光ディスクのアドレスの相関図である。101はセクタの物理的なセクタ番号であるPhysical Sector Number(以降、PSN)、102はクラスタ単位のデータに埋め込まれるアドレスであるAddress Unit Number(以降、AUN)、103はウォブルによる物理的なADIPアドレスであるPhysical ADIP Addressの実際のアドレス(以降、PAA)、104はPhysical ADIP Addressのウォブルに実際に埋め込むアドレス(以降、PAAW)、105はスクランブル回路、106は排他的論理和(Ex-OR)を示す。ここで、スクランブルとは、演算処理の一つで、アドレスの各ビットの値の変換や規則性の変換を目的とする処理のことをいうものとする。PAA 103の上位3bitを層番号に割り付け、従来のPAA 24ビットから1bitのアドレス拡張した場合の例を示す。また、アドレス拡張の仮想ビットであるPAA ビット24のビット情報は、PAAの下位2ビットに関連付けてウォブルに埋め込むものとする。従来のPAA 24ビット構成において、3ビットの層番号、19ビットのクラスタ番号、2ビットのクラスタ内カウント値として割り付けた場合、8層までの層番号と各層あたり32ギガバイト( $64\text{キロバイト} \times 2^{19}$ )のデータ容量のデータに対してアドレスを割り当てることが出来る。しかし、各層あたり32ギガバイトを越える高密度な光ディスクの場合に、クラスタ番号を20ビットに拡張することで各層あたり64ギガバイト( $64\text{キロバイト} \times 2^{20}$ )のデータ容量のデータに対してアドレスを割り付けることが出来るが、層番号のビットが2ビットに減ってしまうため5層以上のアドレス生成ができなくなってしまう。そこで、層番号として1ビット拡張し、従来と同等の3ビットにより8層までのアドレスを生成する。

10

## 【0011】

以下、図1に示されるアドレスの生成方法について説明する。PSN 28ビット(残り4ビットは未使用)のアドレス範囲において、ウォブル上のアドレス範囲としてPAA 25ビットを割り当てる。ただし、ウォブルを用いてディスクに埋め込まれるアドレスのビット数は24ビットしかないため、最上位のPAA ビット24は、仮想アドレスビットとして他のビットへ情報を埋め込む。本実施例の場合は、PAA ビット24をスクランブル回路105のスクランブル処理ON/OFFを決める制御ビットとして入力し、下位2ビットのPAA ビット1-0に対してスクランブル処理を施してウォブルへ埋め込む。情報を埋め込む演算処理であるスクランブル回路の一例として、排他的論理和106を用いる方法を用いることで、PAA ビット24が”0”の場合には、PAA ビット1-0は従来と同じ0,1,2,0,1,2,...とカウントし、PAA ビット24が”1”的場合には、排他的論理和演算後の値となるため3,2,1,3,2,1,...とカウントすることになる。即ち、仮想ビットPAA ビット24に従って、PAA ビット1-0のカウントの規則性を変えている。そこで、スクランブル回路105からの出力であるPAAW ビット1-0をウォブルに実際に埋め込むことで、仮想ビットPAA ビット24をウォブルに埋め込まないで済むようになる。効果として、従来のウォブルアドレスのビット数のまま、アドレス拡張が可能となる。

20

## 【0012】

次に、ウォブルに埋め込まれたアドレスPAAWの検出方法について、図2のタイミング図及び図3の検出回路図の一例を用いて説明する。ウォブルアドレスの検出方法として、誤検出や未検出を考慮して、アドレスを連続的に検出することで保護してアドレスの生成を行う。そこで、PAAW ビット1-0の下位アドレスの連続性をチェックして、仮想ビットであるPAA ビット24の復元を行う。図3における下位連続性検出回路304には、ウォブルから検出されたアドレスPAAW ビット1-0と、デスクランブル回路301によりデスクランブルされたアドレスビット1-0が入力される。デスクランブル回路301において、アドレス生成時には排他的論理和106によりスクランブルされているので、”1”とPAAW ビット1-0との排他的論理和の結果をデスクランブル演算後として出力を行う。仮想ビットPAA ビット24は層番号の3ビット目に割り当てられていることから、層番号0~3の場合(201)と層番号4~7の場合(202)に応じて検出結果が異なることになる。層番号0~3の場合(201)、下位連続

30

性検出回路304にはPAAW ビット1-0は0,1,2,0,1,2,...として入力されるため、PAA ビット24は”0”、PAA ビット1-0はPAAW ビット1-0そのままを出力する。一方、層番号4~7の場合(202)、下位連続性検出回路304にはPAAW ビット1-0は3,2,1,3,2,1,...として入力される。ここで、アドレスの検出値”3”的検出や連続性のデクリメントを検出することで、アドレス生成時のスクランブル処理有りを検出し、PAA ビット24は”1”として出力する。また、下位のPAA ビット1-0に関しては、PAAW ビット1-0のデスクランブル処理後の値である0,1,2,0,1,2,...を出力することとする。これにより、下位連続性検出回路304の出力としてクラスタ内カウント値(PAA ビット1-0)の検出、更に生成されたPAA ビット24とウォブルから検出されたPAAW ビット23-22から層番号検出回路302において、層番号アドレス(PAA ビット24-22)の生成、層番号の検出を行う。また、ウォブルから検出されたPAAW ビット21-2から上位アドレス検出回路303において、クラスタ番号アドレス(PAA ビット21-2)の生成、クラスタ番号の検出を行う。よって、それぞれの検出回路302,303,304より得られたアドレスをPAAアドレス生成回路305に入力されて、PAA ビット24-0のアドレスへと変換が出来る。10

#### 【0013】

以上のように、仮想ビットを他のビットに情報として埋め込んでアドレスを生成し、検出時にアドレスを復元することで、ウォブルのアドレス構造を変えず、ウォブルに埋め込むアドレスのビット数を増やすことなく物理的位置を示すアドレスのビット数を拡張することが出来る。Blu-ray Discにおける物理的ADIPアドレスにおいて、2ビットの層番号と20ビットのクラスタ番号のアドレス割り付けとして、仮想ビットで層番号のアドレスを拡張すれば、8層までの層番号と64ギガバイトまでのディスクに適用できる。同様に、従来の3ビットの層番号と19ビットのクラスタ番号のアドレス割り付けで層番号のアドレスを拡張する場合に用いれば、16層までの層番号と各層あたり32ギガバイトまでのディスクにも適用できる。なお、本実施例のように層番号0~3の場合にスクランブル処理OFFとして仮想ビットを制御しているため、結果としてPAA ビット23-0とPAAW ビット23-0と同じ値になることから、従来の光ディスクとの互換も維持することが可能となる。20

#### 【0014】

また、図12に、本実施例で説明したアドレス生成により作成された光ディスクからデータを再生、データを記録する記録再生装置の一例を示す。1201に光ディスク、1202にピックアップ、1203にスピンドルモータ、1204にアドレス再生回路、1205にデータ記録再生回路、1206に外部ホスト、1207にシステム全体を統括するマイコンを示す。図1に示すアドレス生成方法を用いて作成された光ディスク1201から、ピックアップ1202を介して読み取られたウォブル信号は、アドレス再生回路1204に入力されてアドレス情報の検出を行う。これにより図3で説明したようなアドレス検出回路を用いて構成することで、データを記録再生する位置の検出が可能となり、ピックアップ1202及びデータ記録再生回路1205を介して得られるデータのホスト1206へのデータの入出力、データの記録再生が可能となる。30

#### 【0015】

図4は本発明の第2の実施例である多層光ディスクのアドレスの相関図である。図1との違いは、仮想ビットの割り付けがPAA ビット24ではなくビット21とする点である。401はPhysical ADIP Addressの実際のアドレス(以降、PAA)、402はPhysical ADIP Addressのウォブル埋め込みアドレス(以降、PAAW)として図1と同様だが、ビット割り付けだけが異なり、その他は同一とする。アドレスの生成方法として、第1の実施例と同様に、PAA ビット21をスクランブル回路105のスクランブル処理ON/OFFを決める制御ビットとして入力し、下位2ビットのPAA ビット1-0に対してスクランブル処理を施してウォブルへ埋め込む。即ち、仮想ビットPAA ビット21に従って、PAA ビット1-0のカウントの規則性を変えている。効果として、従来のウォブルアドレスのビット数のまま、アドレス拡張が可能となる。40

#### 【0016】

ウォブルに埋め込まれたアドレスPAAWの検出方法について、図5のタイミング図及び図6の検出回路図の一例を用いて説明する。本実施例の場合は、仮想ビットPAA ビット21は層50

番号アドレスではなくて、クラスタ番号アドレスに割り付けられているため、各層でアドレス生成の切り替えが発生する。また、情報を埋め込む演算処理であるスクランブル方法としても下位2ビットのPAA ビット1-0に排他的論理和106でかけられているため、先ほどと同様に下位連続性検出回路304においてスクランブル処理有無の検出を行って、仮想ビットPAA ビット21の生成、PAA 1-0の検出を行う。これにより、下位連続性検出回路304の出力としてクラスタ内カウント値（PAA ビット1-0）の検出、更に下位連続性検出回路304で検出されたPAA ビット21とウォブルから検出されたPAAW ビット20-2を用いて上位アドレス検出回路303において、クラスタ番号アドレス（PAA ビット21-2）の生成やクラスタ番号の検出、ウォブルから検出されたPAAW ビット23-22を用いて層番号アドレス（PAA ビット24-22）の検出を行う。よって、それぞれの検出回路302,303,304より得られたアドレスをPAAアドレス生成回路305に入力されて、PAA ビット24-0のアドレスへと変換が出来る。

。

#### 【 0 0 1 7 】

以上のように、仮想ビットを他のビットに情報として埋め込んでアドレスを生成し、検出時にアドレスを復元することで、ウォブルのアドレス構造を変えず、ウォブルに埋め込むアドレスのビット数を増やすことなく物理的位置を示すアドレスのビット数を拡張することが出来る。第1の実施例と異なり、仮想ビットを層番号でなく、各層のクラスタ番号アドレスに割り当てても同様に生成、検出が可能である。また、図12と同様に、本実施例で説明したアドレス生成により作成された光ディスクからデータを再生する再生装置や光ディスクにデータを記録する記録装置においても、図6で説明したアドレス検出回路を用いることで、データを記録再生する位置の検出が可能となる。

。

#### 【 0 0 1 8 】

図7は本発明の第3の実施例である多層光ディスクのアドレスの相關図である。図1との違いは、スクランブルの方法として下位2ビットのPAA ビット1-0だけでなく、ビット全体のPAA 23-0に施す点である。701はPhysical ADIP Addressの実際のアドレス（以降、PAA）、702はPhysical ADIP Addressのウォブル埋め込みアドレス（以降、PAAW）、703はスクランブル回路として図1と同様だが、ビット割り付けだけが異なり、その他は同一とする。アドレスの生成方法として、情報を埋め込む演算処理であるスクランブル回路703の一例を図8に示す。図8の場合、クラスタ番号アドレスに対応するPAA ビット21-2の各ビットに対して、PAA ビット24との排他的論理和106を用い、他のビットはそのまま入出力するものとする。このため、PAA ビット24が”0”的場合には、PAA ビット21-2は従来と同じ0,1,2,3,4,5,...,FFFFFhとインクリメントし、PAA ビット24が”1”的場合には、スクランブル処理後の値となるためFFFFFh,FFFEh,FFFDh,...,0とデクリメントすることになる。即ち、仮想ビットPAA ビット24に従って、PAA ビット21-2のカウントの規則性を変えている。効果として、従来のウォブルアドレスのビット数のまま、アドレス拡張が可能となる。

。

#### 【 0 0 1 9 】

ウォブルに埋め込まれたアドレスPAAWの検出方法について、図9のタイミング図及び図10の検出回路図の一例を用いて説明する。本実施例の場合は、仮想ビットであるPAA ビット24はPAAW ビット21-2の上位アドレスの連続性をチェックして、復元を行う。また、スクランブル方法としても上位20ビットのPAA ビット21-2に排他的論理和106でかけられているため、上位連続性検出回路303においてスクランブルの有無（この例では、インクリメントとデクリメントの連続性の違い）の検出を行って、仮想ビットPAA ビット24の生成、PAA 21-2の検出を行う。層番号0~3の場合（901）、上位連続性検出回路303にはPAAW ビット21-2は0,1,2,3,4,5,...,FFFFFhとして入力されるため、PAA ビット24は”0”、PAA ビット21-2はPAAW ビット21-2そのままを出力する。一方、層番号4~7の場合（902）、上位連続性検出回路303にはPAAW ビット21-2はFFFFFh,FFFEh,FFFDh,...,0として入力されるため、デクリメントを検出して、PAA ビット24は”1”として出力し、デスクランブル処理後（この例では、”1”とPAAW ビット21-2の排他的論理和）の値である0,1,2,3,4,5,...,FFFFFhを出力する。これにより、上位連続性検出回路303の出力としてクラスタ番号ア

。

10

20

30

40

50

ドレス (PAA ビット21-2) の生成、クラスタ番号の検出が出来る。更に生成されたPAA ビット24とウォブルから検出されたPAAW ビット23-22から層番号検出回路302において、層番号アドレス (PAA ビット24-22) の生成、層番号の検出を行う。また、ウォブルから検出されたPAAW ビット1-0から下位アドレス検出回路304において、クラスタ内カウント値 (PAA ビット1-0) の検出を行う。よって、それぞれの検出回路302,303,304より得られたアドレスをPAAアドレス生成回路305に入力されて、PAA ビット24-0のアドレスへと変換が出来る。

#### 【 0 0 2 0 】

以上のように、仮想ビットを他のビットに情報として埋め込んでアドレスを生成し、検出時にアドレスを復元することで、ウォブルのアドレス構造を変えず、ウォブルに埋め込むアドレスのビット数を増やすことなく物理的位置を示すアドレスのビット数を拡張することが出来る。第1の実施例と異なり、仮想ビットの情報を埋め込む位置として、アドレスの一部だけでなく、全体に埋め込んでも同様に生成、検出が可能である。また、図12と同様に、本実施例で説明したアドレス生成により作成された光ディスクからデータを再生する再生装置や光ディスクにデータを記録する記録装置においても、図10で説明したアドレス検出回路を用いることで、データを記録再生する位置の検出が可能となる。

#### 【 0 0 2 1 】

図11は本発明の第4の実施例である光ディスクのアドレスの相関図である。図7との違いは、PSN ビット31-27に対応してPAA ビット28-24の5ビットを仮想ビットとして用い、PAA 103の構成としてPAA ビット28-2をクラスタ番号、PAA ビット1-0をクラスタ内カウント値として割り付けている点である。1101はPhysical ADIP Addressの実際のアドレス（以降、PAA）、1102はPhysical ADIP Addressのウォブル埋め込みアドレス（以降、PAAW）、1103はスクランブル回路として図7と同様だが、ビット割り付けだけが異なり、その他は同一とする。スクランブル回路1103のスクランブル規則として複数の種類の形として情報を埋め込み、各々のスクランブル規則（本実施例の場合は、5ビットの仮想ビット追加なので $2^5=32$ 通り）を検出して切り替えることで、複数ビットの仮想ビットの生成、検出が同様に可能となる。即ち、仮想ビットPAA ビット28-24に従って、PAA ビット23-0のカウントの規則性を変えている。効果として、従来のウォブルアドレスのビット数のまま、アドレス拡張が可能となる。

#### 【 0 0 2 2 】

以上のように、仮想ビットを他のビットに情報として埋め込んでアドレスを生成し、検出時にアドレスを復元することで、ウォブルのアドレス構造を変えず、ウォブルに埋め込むアドレスのビット数を増やすことなく物理的位置を示すアドレスのビット数を拡張することが出来る。第1～3の実施例と異なり、仮想ビットとして1ビットだけの拡張だけでなく、複数ビットの場合にも同様に生成、検出が可能である。また、第1～3の実施例では、層番号とクラスタ番号で構成されるアドレスに対して、本実施例ではクラスタ番号でのみ構成されるアドレスを用いて説明したが、同様に生成、検出が可能である。また、図12と同様に、本実施例で説明したアドレス生成により作成された光ディスクからデータを再生する再生装置や光ディスクにデータを記録する記録装置においても、同様にデータを記録再生する位置の検出が可能となる。

#### 【 0 0 2 3 】

図13及び図14は、本発明の第5の実施例に用いられるAUN構造、データ構造、ECC構造、フレーム構造を示す図である。記録再生単位であるクラスタには、メインデータ（1セクタ2048バイト × 32セクタ）に対するLDC ( Long Distance Code ) と、BIS ( Burst Indicator Subcode ) が含まれる。図14 ( a ) に示すメインデータ64キロバイトに対して、図14 ( b ) のようにECCエンコードされる。メインデータ1セクタである2048バイトに4バイトのEDC ( Error Detection Code ) を付加し、32セクタに対してLDC符号化される。また、メインデータのBurst Indicatorとして用いることに適した数値関係として、BISは図14 ( c ) に示す720Bのデータに対して図14 ( d ) のようにECCエンコードされる。更に、図14 ( b ) に示す248 × 304バイトのデータを所定のインターリーブ処理により152 × 496バイトのLDCデ

10

20

30

40

50

ータに並び替え、図14(d)に示す $62 \times 24$ バイトのデータを所定のインターリープ処理により $3 \times 496$ バイトのBISデータに並び替えを行なう。そこで、図14(e)で示すように $38 \times 3$ バイト(152バイト)のLDCデータと、 $1 \times 3$ バイト(3バイト)のBISデータに同期信号(Frame SYNC、FS)を付加して1フレームを構成し、全496フレームのデータによりクラスタを構成する。ここで、1クラスタ単位に付加されるアドレスとしてのAUNは、図13で示すAddress Field(以下、AF)構造を有し、BISのデータ構造720バイトに含まれる。4バイトのAUN(AF0-AF3)102と各種情報を格納する1バイトのflag bits(AF4)1301に対して4バイトの誤り訂正用のパリティ(AF5-AF8)1302が付加されて、16アドレスによりAF構造を構成する。よって、クラスタ構造32セクタ(32個のPSN)に対して、16個のAUNが割り当てられている。

10

#### 【0024】

図1の多層光ディスクのアドレス相関図を用いて、セクタ単位に割り付けられた2種類のアドレスのアドレス生成方法について説明する。例えば、8層までの層番号と各層あたり64ギガバイトのデータ容量のデータに対してアドレスを割り当てる場合を考える。1セクタに割り当てられているPSN 101で8層までの層番号と64ギガバイトのデータ容量を割り当てるには、全28ビット必要となるが、PSNとして元々32ビット準備されているため、27ビットで表現されるデータ量よりも多くなった場合からアドレスビット拡張をする必要がなく、層番号を示すアドレスビットの割り付けをシフトすることで容易に対応が出来る。また、32セクタのPSN 101で構成されるクラスタ構造に対して16個のアドレスが割り当たっているAUN 102の場合も、同様に28ビット必要になる。図13から分かるように、AUN 102は元々4バイト(32ビット)のアドレスビットを用いてAF構造を構成していることから、アドレスビットを拡張する必要はない。そのため、AUN 102のアドレスは従来のアドレス構造から変更はないので、従来のアドレス構造と切り替えの必要はない。また、AUNを用いて構成されているBIS 1404は元々30バイトに対して32バイトのパリティ付加しているため、LDC 1402のユーザーデータに対してのパリティ付加よりも強力なECCが付与されているので、信頼性を高く維持できる。一方、ウォブルに埋め込まれるPAA(PAAW 104)は従来の24ビットの構造では8層までの層番号と各層あたり64ギガバイトのデータ容量のデータに対してアドレスを割り当てることが困難で、アドレス拡張が必要となる。そこで、図1で示すように、ウォブルに埋め込まないことでディスク上に記録しない仮想ビットを他のビットに情報として埋め込んでアドレスを生成し、検出時にアドレスを復元することで、ウォブルのアドレス構造を変えず、更にデータの周期性を維持できて、ウォブルに埋め込むアドレスのビット数を増やすことなく物理的位置を示すアドレスを拡張することが出来る。

20

#### 【0025】

以上のように、データ容量の高密度化などによりアドレスの拡張が必要になる時、PAAのようにアドレスのビット数が少なく拡張が困難な場合にはディスク上に記録しない拡張ビット(仮想ビット)を用いて他のビットに情報として埋め込むことでアドレス構造や周期性を大幅に変更しないでアドレス拡張が可能となる。また、AUNのようにアドレスのビット数が十分で、更には、アドレスフラグなどクラスタ周期で更新可能なビットの拡張が可能であるため、周期性を変えずにビット割り付けを追加することが出来、アドレス拡張や規則性の変換を行なわないことで、PSNとの親和性や従来のアドレスとの互換や信頼性を最大限に維持することが出来る。

30

#### 【0026】

これまでの実施例において、情報の埋め込み方法としてスクランブルを用いて、スクランブル回路として一例(図1の105、図4の105、図7や図8の703)を用いて説明したが、本回路に限定されるものではなく、スクランブルの有無やスクランブル規則性の違いなどによるビット操作を用いて情報の埋め込み、情報の検出が可能であるような回路や方法であれば、同様に適用は可能である。ただし、アドレスのビット操作や値を変換する処理としてスクランブルと説明してきたが、スクランブルは演算処理の一つを意味するものとし、アドレスの各ビットの変換や規則性の変換を行う処理であれば、スクランブルに限定され

40

50

るものではない。

#### 【0027】

また、仮想ビットのビット数、仮想ビットのビットを配置する位置、スクランブル情報などの情報を埋め込むビット位置、アドレスのビット構成に関しても、本実施例に限定されるものではない。ただし、仮想ビット 자체を配置する位置としては検出安定性を考慮すればアドレスとして変化する頻度が少ないほうがよく、スクランブル情報などの情報を埋め込むビット位置は検出時間を考慮すればアドレスとして変化する頻度が多いほうがよい。

#### 【0028】

また、本実施例では記録される媒体として光ディスク、アドレスとしてウォブルに埋め込まれたアドレスを用いて説明したが、本実施例に限定されるものではなく、生成されるアドレスに対して読み込まれるアドレスのビット数が少なくなるようにビットを削減する考えが適用できれば、同様に適用は可能となる。更に、仮想ビットをウォブルに埋め込まないアドレスとして説明したが、読み込まれるアドレスの領域とは異なる領域に格納しておいて、アドレス検出時に用いても良い。

#### 【符号の説明】

#### 【0029】

101...Physical Sector Number (PSN)、102...Address Unit Number (AUN)、103...Physical ADIP Address (PAA)、104...Physical ADIP Address (PAAW)、105...スクランブル回路、106...排他的論理和、301...デスクランブル回路、302...層番号検出回路、303...上位連続性検出回路、304...下位連続性検出回路、305...PAAアドレス生成回路、401...Physical ADIP Address (PAA)、402...Physical ADIP Address (PAAW)、701...Physical ADIP Address (PAA)、702...Physical ADIP Address (PAAW)、703...スクランブル回路、801...排他的論理和、1101...Physical ADIP Address (PAA)、1102...Physical ADIP Address (PAAW)、1103...スクランブル回路、1201...光ディスク、1202...ピックアップ、1203...スピンドルモータ、1204...アドレス再生回路、1205...データ記録再生回路、1206...ホスト、1207...マイコン、1301...flag bits、1302...parities

10

20

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図 8】

【図 9】

図 9

【図 10】

図 10

【図 11】

図 11

【図 12】

図 12

【図 13】

図 13

## 【図 1 4】

図 14

---

フロントページの続き

(51)Int.Cl.

F I

G 1 1 B 7/005

Z

(72)発明者 西村 孝一郎

神奈川県横浜市戸塚区吉田町 292 番地 株式会社日立製作所 コンシューマエレクトロニクス研究所内

(72)発明者 永井 裕

神奈川県横浜市戸塚区吉田町 292 番地 株式会社日立製作所 コンシューマエレクトロニクス研究所内

審査官 ゆずりは 広行

(56)参考文献 特開2010-186507 (JP, A)

特開2001-167562 (JP, A)

特開2001-243722 (JP, A)

特開2002-319246 (JP, A)

特開2003-123333 (JP, A)

特開2006-269077 (JP, A)

特表2008-523534 (JP, A)

国際公開第2008/060104 (WO, A1)

特開2010-198665 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 1 1 B 7 / 0 0 - 7 / 0 1 3

G 1 1 B 2 0 / 1 0

G 1 1 B 2 0 / 1 2