(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-128575

(P2012-128575A)

(43) 公開日 平成24年7月5日(2012.7.5)

|                      |                 |             |

|----------------------|-----------------|-------------|

| (51) Int.Cl.         | F 1             | テーマコード (参考) |

| GO6F 12/02 (2006.01) | GO6F 12/02 590B | 5B060       |

| GO6F 13/28 (2006.01) | GO6F 13/28 310M | 5B061       |

審査請求 未請求 請求項の数 8 O L (全 16 頁)

|           |                              |          |                                                         |

|-----------|------------------------------|----------|---------------------------------------------------------|

| (21) 出願番号 | 特願2010-278299 (P2010-278299) | (71) 出願人 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号              |

| (22) 出願日  | 平成22年12月14日 (2010.12.14)     | (74) 代理人 | 100125254<br>弁理士 別役 重尚                                  |

|           |                              | (72) 発明者 | 鈴木 総一郎<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内               |

|           |                              |          | F ターム (参考) 5B060 AB09 AB19 AC13 GA09<br>5B061 BA03 DD03 |

(54) 【発明の名称】データ転送装置、その制御方法、および制御プログラム

## (57) 【要約】

【課題】D R A Mなどのメモリに複数種類のデータを転送して格納する際、プリチャージの回数を抑えてデータを効率よく転送する。

【解決手段】データ転送制御装置310は、互いに異なる複数種類のデータをD R A M 320に転送する。D R A Mには複数のページが規定されており、データ転送制御装置は複数種類のデータについて所定のデータ量を1つの単位として、当該1つの単位毎に前記複数種類のデータをページの1つに転送する。この際、C P U 205は複数種類のデータについて所定のデータ量を設定する。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

互いに異なる複数種類のデータをメモリに転送するデータ転送装置において、前記メモリには複数の転送領域が規定されており、前記複数種類のデータについて所定のデータ量を1つの単位として、当該1つの単位毎に前記複数種類のデータを前記転送領域に転送するメモリアクセス手段と、前記複数種類のデータについて前記所定のデータ量を設定する設定手段とを有することを特徴とするデータ転送装置。

## 【請求項 2】

前記メモリアクセス手段は、前記転送領域の1つに転送された前記複数種類のデータのデータ量が前記所定のデータ量となると、前記転送領域の1つに続く転送領域に前記複数種類のデータを転送することを特徴とする請求項1記載のデータ転送装置。

10

## 【請求項 3】

前記メモリアクセス手段は、前記複数種類のデータを1回のバースト転送によって前記転送領域の1つに転送し、1回のバースト転送毎に別の前記転送領域に前記複数種類のデータを転送することを特徴とする請求項1記載のデータ転送装置。

## 【請求項 4】

前記設定手段は、前記所定のデータ量を前記複数種類のデータの出現頻度比率に応じて設定することを特徴とする請求項1～3いずれか1項記載のデータ転送装置。

20

## 【請求項 5】

前記複数種類のデータは、撮影の結果得られた画像データを複数の周波数帯域で分割した画像データであることを特徴する請求項1～4いずれか1項記載のデータ転送装置。

## 【請求項 6】

前記メモリアクセス手段は、前記複数種類のデータのうち最もデータ量の少ないデータを除いた一部の種類のデータについて、当該データの出現頻度比率に応じたデータ量を前記転送領域の1つに転送し、さらに前記最もデータ量の少ないデータを含んだ残りの種類のデータを前記転送領域の1つに転送することを特徴とする請求項1～3いずれか1項記載のデータ転送装置。

## 【請求項 7】

互いに異なる複数種類のデータを、複数の転送領域が規定されたメモリに転送するデータ転送装置を制御するための制御方法において、

30

前記複数種類のデータについて所定のデータ量を1つの単位として、当該1つの単位毎に前記複数種類のデータを前記転送領域に転送するメモリアクセスステップと、

前記複数種類のデータについて前記所定のデータ量を設定する設定ステップとを有することを特徴とする制御方法。

## 【請求項 8】

互いに異なる複数種類のデータを、複数の転送領域が規定されたメモリに転送するデータ転送装置を制御するための制御プログラムにおいて、

前記データ転送装置に備えられたコンピュータに、

前記複数種類のデータについて所定のデータ量を1つの単位として、当該1つの単位毎に前記複数種類のデータを前記転送領域に転送するメモリアクセスステップと、

40

前記複数種類のデータについて前記所定のデータ量を設定する設定ステップとを実行させることを特徴とする制御プログラム。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、複数種類の画像データをDRAMなどのメモリに転送するデータ転送装置、その制御方法、および制御プログラムに関する。

## 【背景技術】

## 【0002】

50

デジタルカメラなどの撮像装置で用いられる画像処理装置において、一般に画像データ格納用メモリとしてDRAMが用いられている。近年、撮像装置における画像の高画質化に伴って、DRAMに格納される画像データの量（データ量）が増加している。

【0003】

ところで、画像データを複数の周波数帯域に分割して複数種類の画像データ（分割画像データともいう）をDRAMに格納し、当該分割画像データの各々に対して適切な画像処理を施すことが行われている。そして、周波数帯域毎に処理された分割画像データを周波数合成して、合成後の画像データについてノイズを低減するようにしている。

【0004】

上述のような処理を行うと、不可避的にDRAMに格納される画像データのデータ量が増加するため、DRAMに画像データを効率よく転送することが重要となる。

【0005】

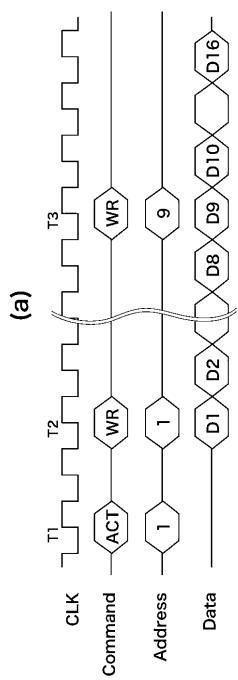

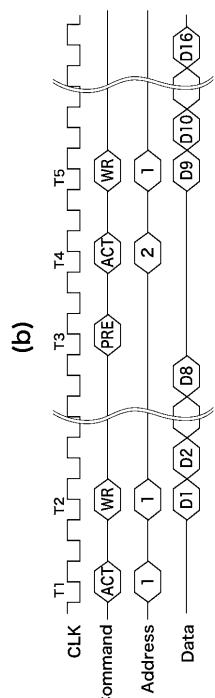

図8は、SDRAM（Synchronous DRAM）に対するデータの書き込みタイミングを説明するためのタイミングチャートである。そして、図8(a)は、同一のロウ（行）アドレス（同一のページ）に対して2回データの書き込みアクセスを行う場合のタイミングを示す図であり、図8(b)は、同一のバンクにおける2つの異なるロウアドレス（ページ）にデータを書き込む場合のタイミングを示す図である。なお、図8においては、BL（バースト長：1回のアドレス指定により連続的アクセス可能なワード数）を「8」としている。

【0006】

図8(a)に示すように、時刻T1において、ACTコマンド(Command)によりロウアドレス(Address)を指定する(ロウアドレス=1)。そして、時刻T2において、WRコマンドによりカラム(列)アドレス(Column Address)を指定して、8ワード分のデータ(Data:D1~D8)の書き込みが行われる。

【0007】

時刻T3において、WRコマンドによりカラムアドレス(Column Address)を指定して、次の8ワード分のデータ(Data:D9~D16)の書き込みが完了する。

【0008】

図8(b)に示すように、時刻T1において、ACTコマンドによりロウアドレスを指定する(ロウアドレス=1)。そして、時刻T2において、WRコマンドによりカラムアドレス(Column Address)を指定して、8ワード分のデータ(Data:D1~D8)の書き込みが行われる。

【0009】

DRAMでは、同一バンクにおいて異なるロウアドレス(異なるページ)にデータを書き込む場合には、DRAMに対するプリチャージコマンド(ページクローズ)、およびACTコマンド(ページオープン)が必要となる。

【0010】

図8(b)に示す例では、時刻T3においてプリチャージが行われ、時刻T4においてACTコマンドによりロウアドレスが指定されている(ロウアドレス=2)。その後、時刻T5においてWRコマンドによりカラムアドレス(Column Address)が指定されて、8ワード分のデータ(Data:D9~D16)の書き込みが行われている。

【0011】

このように、同一バンクの異なるページに対するデータの書き込む回数(ページ切換え回数)が多くなると、その分プリチャージおよびACTコマンドが必要となる。その結果、DRAMに対するアクセス効率が低下してしまうという問題がある。

【0012】

従来、上述のような問題に対して、ページ切換え回数をできる限り少なくして、プリチャージ回数を減らし、DRAMに対して効率良くアクセスするためのデータ転送手法が提案されている。

【0013】

10

20

30

40

50

例えば、画像の一部を示す矩形領域データに対してDRAMにおける1ページうちの連続アドレスを割り付け、これによって、DRAMに対して矩形領域データを書き込む際のプリチャージ回数を少なくすることが行われている（例えば、特許文献1参照）。

#### 【0014】

また、特許文献1においては、2つの矩形領域にまたがったデータを書き込む際に発生するプリチャージを抑えるため、隣接する矩形領域データが相互にDRAMの異なるバンクに格納されるようにアドレスを割り当てている。

#### 【先行技術文献】

#### 【特許文献】

#### 【0015】

【特許文献1】特開2000-330864号公報

10

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0016】

しかしながら、特許文献1に記載のデータ転送においては、1種類のデータ（特許文献1においては、1つの矩形領域データ）をDRAMに書き込む際、別種類の複数のデータを同時にDRAMに書き込む（つまり、アクセスする）場合には、複数種類のデータを全て異なるバンクに格納する必要がある。

#### 【0017】

前述のように、1つ（1枚）の画像データから複数の周波数帯域分割画像データを生成するように、十数種類のデータが同時にDRAMに対してアクセスする可能性がある場合には、特許文献1に記載のデータ転送手法では、十数個のバンクを有するDRAMを用いる必要がある。このため、DRAMに要するコストが増大してしまう。

20

#### 【0018】

さらに、1枚の画像データから得られた複数種類のデータを全て別のバンクに格納するとなると、画像データの管理が極めて複雑になってしまうという問題もある。

#### 【0019】

また、多くのバンクにまたがって1つ（1枚）の画像データが格納されると、他の画像データをDRAMに格納する際のアクセス制約が増大する。

#### 【0020】

30

複数種類の画像データが同時にDRAMに書き込まれる（つまり、アクセスする）場合には、DRAMのコストおよびデータ管理を考慮すると、同一のバンクに複数種類の画像データを格納することが望ましい。

#### 【0021】

従って、本発明の目的は、メモリであるDRAMの同一バンクに複数種類のデータを同時に書き込む（アクセスする）際ににおいて、プリチャージの回数を抑えて、データを効率よく転送することのできるデータ転送装置、その制御方法、および制御プログラムを提供することにある。

#### 【課題を解決するための手段】

#### 【0022】

40

上記の目的を達成するために、本発明によるデータ転送装置は、互いに異なる複数種類のデータをメモリに転送するデータ転送装置において、前記メモリには複数の転送領域が規定されており、前記複数種類のデータについて所定のデータ量を1つの単位として、当該1つの単位毎に前記複数種類のデータを前記転送領域に転送するメモリアクセス手段と、前記複数種類のデータについて前記所定のデータ量を設定する設定手段とを有することを特徴とする。

#### 【0023】

本発明による制御方法は、互いに異なる複数種類のデータを、複数の転送領域が規定されたメモリに転送するデータ転送装置を制御するための制御方法において、前記複数種類のデータについて所定のデータ量を1つの単位として、当該1つの単位毎に前記複数種類

50

のデータを前記転送領域に転送するメモリアクセスステップと、前記複数種類のデータについて前記所定のデータ量を設定する設定ステップとを有することを特徴とする。

【0024】

本発明による制御プログラムは、互いに異なる複数種類のデータを、複数の転送領域が規定されたメモリに転送するデータ転送装置を制御するための制御プログラムにおいて、前記データ転送装置に備えられたコンピュータに、前記複数種類のデータについて所定のデータ量を1つの単位として、当該1つの単位毎に前記複数種類のデータを前記転送領域に転送するメモリアクセスステップと、前記複数種類のデータについて前記所定のデータ量を設定する設定ステップとを実行させることを特徴とする。

【発明の効果】

【0025】

本発明によれば、DRAMなどのメモリに複数種類のデータを転送して格納する際、プリチャージの回数を抑えて、データを効率よく転送することができるという効果がある。

【図面の簡単な説明】

【0026】

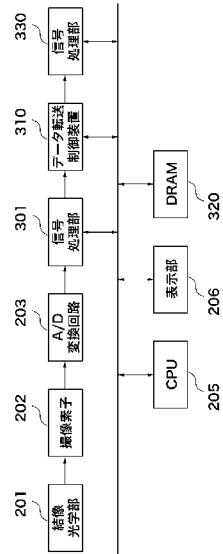

【図1】本発明の第1の実施形態によるデータ転送装置が用いられた画像処理装置である撮像装置の一例を示すブロック図である。

【図2】図1に示すデータ転送制御装置を詳細に説明するためのブロック図である。

【図3】図2に示すデータ転送制御装置におけるDRAMへの画像データの格納およびその際のプリチャージ発生回数の一例について説明するための図であり、(a)はDRAMに画像データを格納する手法を説明するための図、(b)はその際に生じるプリチャージの発生回数を説明するための図である。

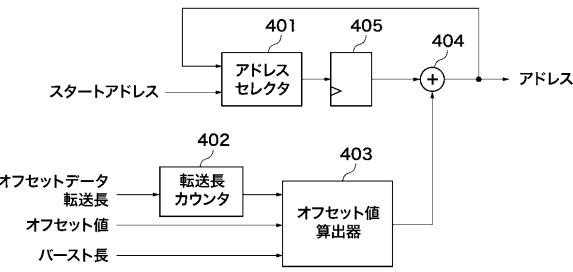

【図4】図2に示すWRD MACの各々についてそのデータ格納アドレス算出機能を説明するためのブロック図である。

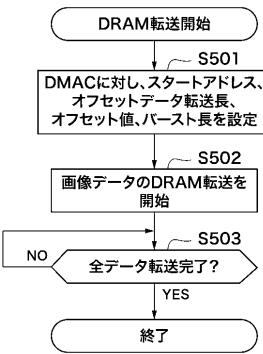

【図5】図2に示すデータ転送制御装置における画像データのDRAM転送を説明するためのフローチャートである。

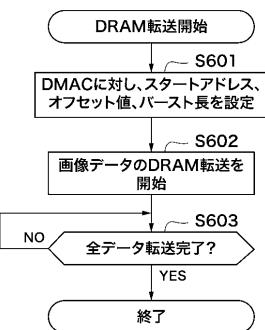

【図6】図2に示すデータ転送制御装置においてオフセットデータ転送長設定機能が備えられていない場合のDRAM転送を説明するためのフローチャートである。

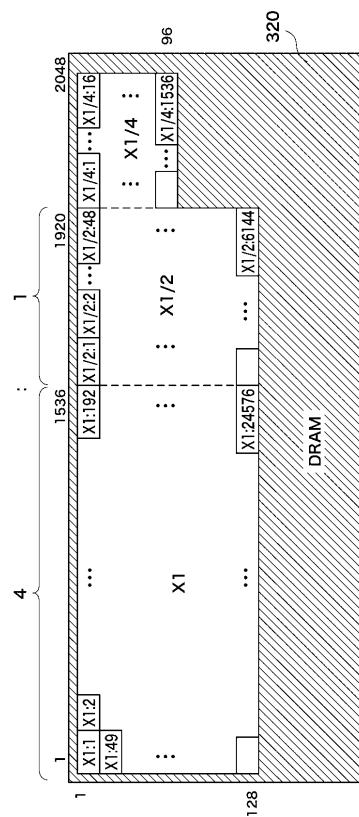

【図7】図2に示すデータ転送制御装置におけるDRAMへの画像データの格納の他の例について説明するための図である。

【図8】SDRAM (Synchronous DRAM)に対するデータの書き込みタイミングを説明するためのタイミングチャートであり、(a)は同一のロウ(行)アドレス(同一のページ)に対して2回データの書き込みアクセスを行う場合のタイミングを示す図、(b)は同一のバンクにおける2つの異なるロウアドレス(ページ)にデータを書き込む場合のタイミングを示す図である。

【図9】従来技術におけるDRAMへの画像データの格納およびその際のプリチャージ発生回数について説明するための図であり、(a)はDRAMに画像データを格納する手法を説明するための図、(b)はその際に生じるプリチャージの発生回数を説明するための図である。

【発明を実施するための形態】

【0027】

以下、本発明の実施の形態によるデータ転送装置の一例について、図面を参照して説明する。なお、以下の説明では、画像データを転送する場合について説明するが、画像データ以外のデータについても同様にして適用することができる。

【0028】

(第1の実施形態)

図1は本発明の第1の実施形態によるデータ転送制御装置が用いられた画像処理装置である撮像装置の一例を示すブロック図である。

【0029】

図1を参照して、図示の撮像装置は、結像光学部201を有しており、この結像光学部

10

20

30

40

50

201はレンズおよび絞りなどを備えている。そして、撮影の際、結像光学部201はフォーカス調節および露出調節を行って撮像素子（例えば、CCD）202に光学像を結像する。撮像素子202は光学像を電気信号（アナログ画像信号）に変換する。このアナログ画像信号はA/A変換器203によってデジタル画像信号（画像データ）に変換される。

【0030】

撮像装置は、第1および第2の画像処理部301および330、データ転送制御装置310、CPU205、表示部（例えば、液晶モニタ）206、およびDRAM（メモリ）320を有している。そして、これらはバスによって相互に接続されている。なお、CPU205は撮像装置全体の制御を司る。なお、DRAM320には複数のページ（転送領域）が規定されている。10

【0031】

画像データ（つまり、撮影の結果得られた画像データ）は第1の信号処理部301に与えられ、ここでノイズ低減などの各種画像処理が施される。その後、画像データはデータ転送制御装置310に送られて、データ転送制御装置310はDRAM（メモリ）320に対して画像データおよび各種制御データの書き込み／読み出しを行う。

【0032】

データ転送制御装置310から第2の信号処理部330に対して画像データが送られ、画像データは再び第2の信号処理部330においてノイズ低減などの各種画像処理が施される。そして、第2の信号処理部330において生成された画像データは、例えば、CPU205の制御下で画像として表示部20に表示される。20

【0033】

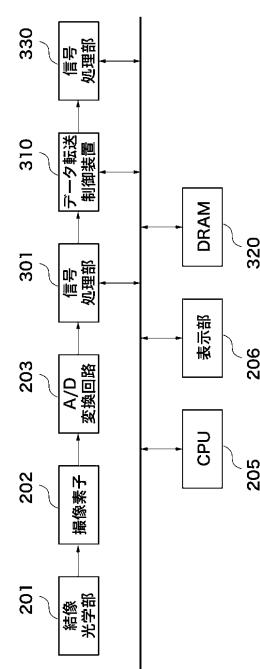

図2は、図1に示すデータ転送制御装置310を詳細に説明するためのブロック図である。

【0034】

図2を参照して、いま、第1の信号処理部301は、 $1024 \times 768$ 画素で、1画素 = 8bitの画像データを水平方向および垂直方向において1/2ダウンサンプリングする。これによって、第1の信号処理部301は、 $1024 \times 768$ 画素、 $512 \times 384$ 画素、および $256 \times 192$ 画素（1画素 = 8bit）の画像データを出力する。つまり、第1の信号処理部301は、撮影の結果得られた画像データを複数の周波数帯域に分割して複数種類の画像データとする。30

【0035】

以下の説明では、第1の信号処理部301が出力する $1024 \times 768$ 画素の画像データをX1、 $512 \times 384$ 画素の画像データをX1/2、そして、 $256 \times 192$ 画素の画像データをX1/4で表すことにする。

【0036】

ここで、画像データX1は入力画像データと同一の画像データであり、画像データX1/2は画像データX1を水平方向および垂直方向において1/2ダウンサンプリングした画像データである。また、画像データX1/4は画像データX1/2を水平方向および垂直方向において1/2ダウンサンプリングした画像データである。40

【0037】

図示のように、データ転送制御装置310は、第1～第3の書き込みダイレクトメモリアクセス制御部（WRDMAC：Write Direct Memory Access Controller）401～403、メモリアクセス部420、および第1～第3の読み出しダイレクトメモリアクセス制御部（RDDMAC：Read Direct Memory Access Controller）411～413を備えている。

【0038】

データ転送制御装置310は、画像データX1、X1/2、およびX1/4をDRAM（メモリ）320に格納する。ここで、画像データX1、X1/2、およびX1/4の各々は、1バイト（1Byte = 8bit）毎にデータ転送装置310に入力される。50

## 【0039】

データ転送制御装置310において、画像データX1、X1/2、およびX1/4の1ByteデータはそれぞれWRDMAC401～403に入力される。図示の例では、DRAM320は、2048カラムアドレス、4096ロウアドレス、そして、1ワード=32bitの容量を有しており、8バースト転送が可能である。

## 【0040】

DRAM320に対して8バースト転送を行うため、WRDMAC401～403は、それぞれ画像データX1、X1/2、およびX1/4を32Byte(=32bit×8バースト)単位(1つの単位毎)でメモリアクセス部420に出力する。メモリアクセス部420は、画像データ画像データX1、X1/2、およびX1/4について32Byteデータ、ロウアドレス、およびカラムアドレスをDRAM320に出力する。これによって、メモリアクセス部420は画像データX1、X1/2、およびX1/4をDRAM320に転送して格納する(書き込む)。

10

## 【0041】

データ転送制御装置310は、DRAM320に格納された画像データX1、X1/2、およびX1/4を読み出して、第2の信号処理部330に出力する。具体的には、メモリアクセス部420は、DRAM320から8バースト転送で画像データX1、X1/2、およびX1/4を読み出して、当該画像データX1、X1/2、およびX1/4をRDDMAC411～413に出力する。

20

## 【0042】

そして、RDDMAC411～413は、それぞれ画像データX1、X1/2、およびX1/4を1Byte(バイト)単位で出力する。第2の信号処理部330は、画像データX1、X1/2、およびX1/4をアップサンプリングして合成し、1024×768画素(1画素=8ビット)の画像データを出力する。

## 【0043】

ここで、従来技術におけるDRAMへの画像データの格納およびその際のプリチャージ発生回数について説明する。

## 【0044】

図9は、従来技術におけるDRAMへの画像データの格納およびその際のプリチャージ発生回数について説明するための図である。そして、図9(a)はDRAMに画像データを格納する手法を説明するための図であり、図9(b)はその際に生じるプリチャージの発生回数を説明するための図である。

30

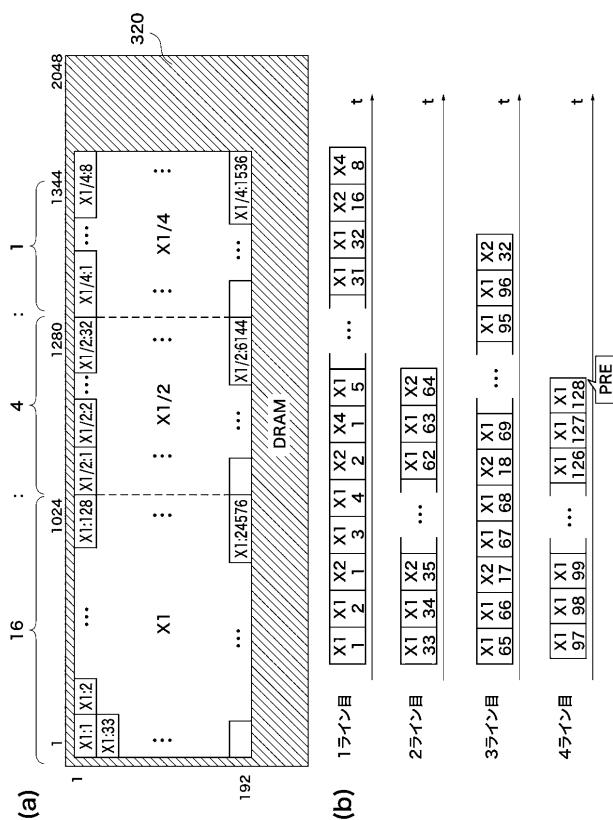

## 【0045】

図9(a)において、いま、8バースト転送分の32Byteを1ブロックとすると、画像データX1は32(=1024/32)×768ブロック、画像データX1/2は16(=512/32)×384ブロック、画像データX1/4は8(=256/32)×192ブロックとなる。

## 【0046】

つまり、画像データX1の総ブロック数は24576(=32×768)ブロック、画像データX1/2の総ブロック数は6144(=16×384)ブロック、画像データX1/4の総ブロック数は1536(=8×192)ブロックとなる。そして、画像データX1、X1/2、およびX1/4の各々は1ブロック単位(1つの単位)でDRAM320に格納される。

40

## 【0047】

図9(a)に示す画像データのDRAM格納手法は、1ページに1種類の画像データを格納する手法であり、ロウアドレス1～96で指定される領域に画像データX1が格納され、ロウアドレス101～124で指定される領域に画像データX1/2が格納される。また、ロウアドレス131～136で指定される領域に画像データX1/4が格納される。

## 【0048】

50

図9(b)では、メモリアクセス部420がWRDMAC401～403から受信する画像データX1、X1/2、およびX1/4の受信順番が示されている。第1の信号処理部301に入力画像データの始めの水平1ライン目1024画素(=32ブロック)が入力されると、第1の信号処理部301は、画像データX1について32ブロック、画像データX1/2について16ブロック、そして、画像データX1/4について8ブロック分の水平1ラインデータを生成する。

【0049】

ここで、画像データX1/2は画像データX1を水平方向に1/2間引いた画像データであるから、画像データX1が2ブロック出力される期間中に、画像データX1/2については1ブロック出力される。また、画像データX1/4は画像X1/2を水平方向に1/2間引いた画像データであるから、画像データX1/2が2ブロック出力される期間中に、画像データX1/4については1ブロック出力される。

10

【0050】

第1の信号処理部301に入力画像データの水平2ライン目が入力されると、画像データX1について水平1ラインデータが生成される。一方、画像データX1/2は画像データX1を垂直方向に1/2間引いた画像データであるから、画像データX1/2については水平1ラインデータが生成されない。同様に、画像データX1/4は画像データX1/2を垂直方向に1/2間引いた画像データであるから、画像データX1/4については水平1ラインデータが生成されない。

20

【0051】

第1の信号処理部301に入力画像データの水平3ライン目が入力されると、画像データX1およびX1/2については水平1ラインデータが生成される。一方、画像データX1/4は画像データX1/2を垂直方向に1/2間引いた画像データであるから、画像データX1/4については水平1ラインデータが生成されない。

30

【0052】

第1の信号処理部301に入力画像データの水平4ライン目が入力されると、画像データX1については水平1ラインデータが生成される。一方、画像データX1/2およびX1/4はそれぞれ画像データX1およびX1/2を垂直方向に1/2間引いた画像データであるから、画像データX1/2およびX1/4については水平1ラインデータが生成されない。

【0053】

このように、水平4ラインまでにおいて、画像データX1、X1/2、およびX1/4の出力頻度比率(出現頻度比率ともいう)は、X1:X1/2:X1/4=16:4:1となる。そして、水平5ライン目以降についても水平1～4ラインと同一の頻度で画像データX1、X1/2、およびX1/4が出力される。

【0054】

このため、水平5ライン目以降の画像データX1、X1/2、およびX1/4の出力頻度も、水平4ライン単位でX1:X1/2:X1/4=16:4:1となる。

【0055】

ここで、3種類の画像データX1、X1/2、およびX1/4を、図9(a)に示すようにしてDRAM320に格納すると、異なる種類の画像データを格納する際に必ずページ切換えが発生する。このため、プリチャージ処理を行う必要がある。

40

【0056】

図9(b)に示すように、水平4ライン分(1ライン目～4ライン目)が入力された際に生成される画像データX1、X1/2、およびX1/4をDRAM320に格納すると、プリチャージ処理は合計72回発生することになる。したがって、 $1024 \times 768$ 画素の入力画像データに対しては、プリチャージ処理を13824回(=72×768/4)行う必要がある。

【0057】

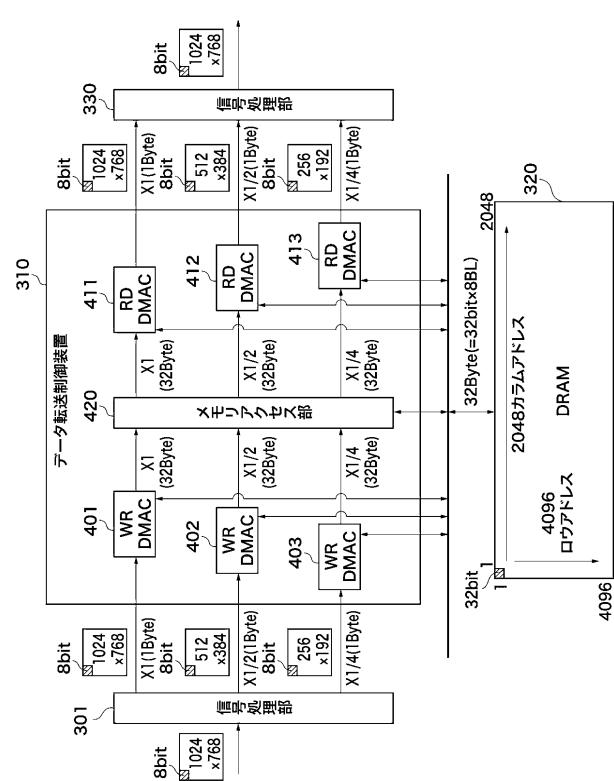

図3は、図2に示すデータ転送制御装置310におけるDRAM320への画像データ

50

の格納およびその際のプリチャージ発生回数について説明するための図である。そして、図3(a)はDRAMに画像データを格納する手法を説明するための図であり、図3(b)はその際に生じるプリチャージの発生回数を説明するための図である。

【0058】

図3(a)において、ここでは、1ページ(1つの転送領域)に複数の画像データX1、X1/2、およびX1/4を格納するものとする。そして、1ページに格納する画像データX1、X1/2、およびX1/4の比率は出力頻度比率と同一の16:4:1とする。

【0059】

画像データX1、X1/2、およびX1/4の出力頻度比率(出現頻度比率)は、入力画像データの水平4ライン単位において16:4:1となる。このため、水平4ライン分のデータ量を1ページ(1つの転送領域)に格納している。

【0060】

そして、次の水平4ライン分の画像データが入力された際に生成される画像データX1、X1/2、およびX1/4は次ページ(次の転送領域、つまり、1つの転送領域に続く転送領域)に格納される。以降、水平4ライン分の画像データが入力された際に生成される画像データX1、X1/2、およびX1/4を1つの単位とし、画像データの全てがDRAM320に格納されるまで、ページ毎に画像データX1、X1/2、およびX1/4が格納される。

【0061】

図3(b)には、メモリアクセス部420(図2)がWRDMAC401～403から受信する画像データX1、X1/2、およびX1/4の受信順番が示されている。図3(b)に示すデータ受信順番は図9(b)に示す順番と同一である。

【0062】

図3(a)で説明したようにして、この画像データX1、X1/2、およびX1/4をDRAM320に格納すると、入力画像データの水平4ライン分が入力された際に生成される画像データX1、X1/2、およびX1/4がDRAM320に格納する間ではページ切換えが発生しない。このため、プリチャージ処理を行う必要はない。

【0063】

そして、入力画像データの水平5ライン目が入力された際に生成される画像データX1、X1/2、およびX1/4をDRAM320に格納する際に、プリチャージ処理を1回行えばよい。したがって、 $1024 \times 768$ 画素の入力画像データに対しては、192回( $= 768 / 4$ )のプリチャージ処理を行うだけよいことになる。

【0064】

このように、図3(a)に示すように、画像データの格納を行えば、プリチャージ処理の回数を少なくすることができる。その結果、画像データを効率よくDRAM320に転送することができる。また、画像データを読み出す際ににおいても、DRAM320に対して、書込みと同様のアクセスを行えば、画像データを効率よくDRAM320から読み出すことができる。

【0065】

図4は、図2に示すWRDMAC401～403の各々についてそのデータ格納アドレス算出機能を説明するためのブロック図である。

【0066】

図1、図2、および図4を参照すると、WRDMAC401～403の各々は、アドレスセレクタ401、転送長カウンタ402、オフセット値算出器403、加算器404、およびフリップフロップ405を有している。

【0067】

WRDMAC401～403の各々は、画像データを転送すると格納アドレス値をジャンプさせるオフセット機能を備えている。CPU205は、WRDMAC401～403に対して、スタートアドレス、オフセットデータ転送長、オフセット値、およびバースト

10

20

30

40

50

長を設定する。ここで、オフセットデータ転送長が所定のデータ量である。

【0068】

アドレスセレクタ401は、データ格納開始の際、CPU205に設定されたスタートアドレスをアドレス値として選択する。図示の例において、画像データX1、X1/2、およびX1/4の「スタートロウアドレス、スタートカラムアドレス」は、それぞれ画像データX1が「1、1」、画像データX1/2が「1、1025」、画像データX1/4が「1、1281」となる。

【0069】

転送長カウンタ402は、転送データ長をカウントして、CPU205に設定されたオフセットデータ転送長の画像データを転送する毎に、オフセット値算出器403にオフセットタイミング信号を出力する。図示の例では、CPU205は、入力画像データの水平4ライン分が入力された際に生成される画像データX1、X1/2、およびX1/4のデータ量をオフセット転送長として設定する。

10

【0070】

具体的には、画像データX1に係るオフセット転送長が4096Byte(1024×4ライン)となる。また、画像データX1/2に係るオフセット転送長が1024Byte(512×2ライン)となり、画像データX1/4に係るオフセット転送長が256Byte(256×1ライン)となる。

【0071】

転送長カウンタ402からオフセットタイミング信号を受信すると、オフセット値算出器403は、CPU205に設定されたオフセット値を出力し、それ以外のタイミングではCPU205に設定されたバースト長を出力する。図示の例では、CPU205は、ロウアドレスについては現在のロウアドレス値に「1」を加算した値、カラムアドレスについてはスタートカラムアドレスとなるようにオフセット値を設定する。これによって、オフセットタイミングにおいてアドレスは次ページへとジャンプする。さらに、図示の例では、CPU205は、「8」をバースト長として設定する。

20

【0072】

加算器404は、オフセット値算出器403から出力された値を現在のアドレス値に加算して、次の画像データを格納するアドレス値を生成する。アドレスセレクタ401は、8バースト長の画像データが転送される毎に、加算器404が出力する値を現在のアドレス値として選択する。そして、この現在のアドレス値はフリップフロップ404で保持される。

30

【0073】

図5は、図2に示すデータ転送制御装置310における画像データX1、X1/2、およびX1/4のDRAM転送を説明するためのフローチャートである。

【0074】

図1、図2、図4、および図5を参照して、CPU205は、WRDMAC401～403に対して、スタートアドレス、オフセットデータ転送長、オフセット値、およびバースト長を設定する(ステップS501)。CPU205は、データ転送制御装置310に対してDRAM320への画像データ転送開始を指示する(ステップS502)。そして、CPU205は全画像データのDRAM転送が終了したか否かを監視する(ステップS503)。

40

【0075】

全画像データのDRAM転送が終了しないと(ステップS503において、NO)、CPU205は待機する。一方、全画像データのDRAM転送が終了すると(ステップS503において、YES)、つまり、データ転送制御装置310から転送完了を報知されると、CPU205はDRAM転送制御を終了する。

【0076】

このように、第1の実施形態では、DRAM320の同一バンクに対して複数種類のデータを同時に書き込み又は読み出す(アクセスともいう)場合においても、プリチャージ

50

の回数を抑えることができる。この結果、画像データを効率よくDRAMに転送することができる。

【0077】

なお、第1の実施形態においては、画像データの書き込みを行った後、画像データの読み出しを行う場合について説明したが、画像データの書き込みおよび読み出しを並列して行うようにしてもよい。

【0078】

また、第1の実施形態においては、3種類の画像データX1、X1/2、およびX1/4をDRAM320に格納するようにしたが、複数種類の画像データ又はデータであれば、同様にして適用することができる。そして、上述の例では、3種類の画像データX1、X1/2、およびX1/4の出力頻度を16:4:1としたが、出力頻度比率はこの例に限定されず、他の出力頻度比率であってもよい。

【0079】

加えて、上述の例では、入力画像画像データの画素数を $1024 \times 768$ （1画素=8bit）、DRAM320の容量を $2048 \times 4096$ （1ワード=32bit）としたが、これに限定されず、他の画素数およびDRAM容量であってもよい。さらに、上述の例では、画像データをバースト長でDRAM320に書き込むようにしたが、バースト長以外のバースト長においてDRAM320にアクセスするようにしてもよい。

【0080】

また、第1の実施形態では、データ転送制御装置にオフセットデータ転送長を設定し、所定の量の画像データを転送すると、アドレス値をジャンプさせるようにしたが、必ずしもデータ転送制御装置がオフセットデータ転送長を設定する機能を有していないともよい。

【0081】

例えば、1ページに格納する画像データを1回のバースト転送によってDRAM320に転送可能であれば、1回のバースト転送毎に次ページに画像データを格納していくようにしてもよい。ここでは、バースト長が所定のデータ量を表すことになる。

【0082】

図6は図2に示すデータ転送制御装置においてオフセットデータ転送長設定機能が備えられていない場合のDRAM転送を説明するためのフローチャートである。

【0083】

図1、図2、および図6を参照して、まず、CPU205は、WRDMAC401~403に対して、スタートアドレス、オフセット値、およびバースト長を設定する（ステップS601）。図示の例では、バースト長として、入力画像データの水平4ライン分が入力された際に生成される画像データのデータ量（所定のデータ量）が設定される。

【0084】

また、オフセット値については、ロウアドレスとして現在のロウアドレス値に「1」を加算した値が設定され、カラムアドレスとしてスタートカラムアドレスが設定される。

【0085】

続いて、CPU205は、データ転送制御装置310にDRAM320に対する画像データの転送開始を指示する（ステップS602）。そして、CPU205は全画像データのDRAM転送が終了したか否かを監視する（ステップS603）。データ転送制御装置310は、DRAM転送の際、1ページに格納する画像データを1回のバースト転送によってDRAM320に転送する。つまり、データ転送制御装置310は、水平ライン分の画像データを1ページに格納すると、続く水平ライン分の画像データを次のページに格納する。

【0086】

全画像データのDRAM転送が終了しないと（ステップS603において、NO）、CPU205は待機する。一方、全画像データのDRAM転送が終了すると（ステップS603において、YES）、つまり、データ転送制御装置310から転送完了を報知される

10

20

30

40

50

と、CPU205はDRAM転送制御を終了する。

【0087】

(第2の実施形態)

続いて、本発明の第2の実施形態によるデータ転送制御装置について説明する。なお、第2の実施形態において、撮像装置の構成およびデータ転送制御装置の構成は第1の実施形態と同様であり、さらに、DRAM転送制御についても第1の実施形態と同様であるので、説明を省略する。

【0088】

第1の実施形態で説明したようにして、画像データX1、X1/2、およびX1/4をDRAM320に格納した場合、画像データX1、X1/2、およびX1/4が格納された1ページにおいて、画像データが格納されていない領域(隙間領域と呼ぶ)が形成される可能性がある。

【0089】

そこで、第2の実施形態では、データ量の多い画像データの出力頻度比率のみを考慮して1ページに画像データを格納して、1ページの残りの領域にデータ量の少ない画像データを隙間領域が形成されないように格納する。これによって、DRAMの容量を効率よく使用する。

【0090】

図7は、図2に示すデータ転送制御装置におけるDRAMへの画像データの格納の他の例について説明するための図である。

【0091】

図1、図2、および図7を参照して、ここでは、前述のように、画像データX1およびX1/2データの出力頻度比率のみを考慮し、画像データX1/4についてはその出力頻度比率は考慮せずに画像データX1、X1/2、およびX1/4をDRAM320に格納する。ここで、DRAM320の1ページに格納する画像データX1およびX1/2のデータ量の比率は、出力頻度比率と同様の4:1とする。そして、画像データX1およびX1/2の出力頻度比率は、入力画像データの水平2ライン単位で4:1となる。したがって、水平2ライン分のデータ量の倍数である水平6ライン分のデータ量について、画像データX1およびX1/2が1ページに格納される。

【0092】

図示の例では、1ページについて、ロウアドレス"1"~"96"の領域の残りの領域に画像データX1/4が隙間領域が形成されないように格納される。このように、画像データX1およびX1/2データの出力頻度比率のみを考慮して、画像データX1、X1/2、およびX1/4をDRAM320に格納すると、画像データX1およびX1/2を格納する際のプリチャージ回数を抑えつつ、1ページにおける隙間領域も減らすことができる。

【0093】

画像データX1/4を格納する際には、プリチャージが発生するものの、画像データX1/4は、画像データX1およびX1/2と比較してデータ量が少ないので、プリチャージによる影響を極力抑えることができる。

【0094】

また、画像データを読み出す際ににおいても、DRAM320に対して同様にアクセスを行えば、画像データを効率よく読み出すことができる。この例で説明したデータ格納手法では、DRAM320に画像データが格納されない領域(隙間領域)を少なくすることができる。このため、プリチャージ回数を削減するとともに、DRAM容量の削減の両立を図りたい場合に特に有効である。このように、第2の実施形態では、DRAM320の1ページに格納する画像データX1/4のデータ量が、前述の出力頻度の比率と一致しないことになる。

【0095】

以上のように、第2の実施形態によれば、DRAMにおいて画像データが格納されない

10

20

30

40

50

隙間領域を少なくすることができ、かつ、プリチャージの回数も抑えることができる。この結果、DRAM容量を効率的に使用しつつ、画像データも効率よく転送することができる。

【0096】

なお、第2の実施形態においても、第1の実施形態と同様に、画像データの書き込みと読み出しどと並列して行ってもよい。また3種類の画像データX1、X1/2、およびX1/4をDRAM320に格納する例について説明したが、複数種類の画像データをDRAM320に格納する場合に、同様に適用することができる。

【0097】

さらに、3種類の画像データX1、X1/2、およびX1/4の出力頻度比率は16:4:1に限られず、他の出力頻度比率であっても同様にして適用することができる。そして、入力画像データの画素数を1024×768(1画素=8bit)、DRAMの容量を2048×4096(1ワード=32bit)としたが、これに限定されず、他の入力画素数およびDRAM容量であってもよい。

【0098】

加えて、画像データを8バースト長でDRAMに書き込むようにしたが、8バースト長以外のバースト長でDRAMにアクセスするようにしてもよい。さらに、画像データX1/4の出力頻度比率を考慮する必要がないので、画像データX1およびX1/2をDRAM320に格納した際に生じる残りの領域であれば、第2の実施形態と異なる領域に画像データX1/4を格納するようにしてもよい。また、第2の実施形態によるデータ転送制御装置においても、特にオフセットデータ転送長を設定する機能を備える必要はない。

【0099】

上述の説明から明らかなように、図1において、CPU205が設定手段として機能し、CPU205およびデータ転送制御装置310がメモリアクセス手段として機能する。また、ここでは、CPU205およびデータ転送制御装置310がデータ転送装置を構成する。

【0100】

以上、本発明について実施の形態に基づいて説明したが、本発明は、これらの実施の形態に限定されるものではなく、この発明の要旨を逸脱しない範囲の様々な形態も本発明に含まれる。

【0101】

例えば、上記の実施の形態の機能を制御方法として、この制御方法を、データ転送装置に実行させるようにすればよい。また、上述の実施の形態の機能を有する制御プログラムを、データ転送装置が備えるコンピュータに実行させるようにしてもよい。

【0102】

この際、制御方法及び制御プログラムの各々は、少なくともメモリアクセスステップおよび設定ステップを有することになる。なお、制御プログラムは、例えば、コンピュータに読み取り可能な記録媒体に記録される。

【0103】

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記録媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。

【符号の説明】

【0104】

205 CPU

301, 330 信号処理部

310 データ転送制御装置

320 DRAM

401 ~ 403 書込みダイレクトメモリアクセス制御部(WRDMAc)

10

20

30

40

50

4 1 1 ~ 4 1 3 読出しダイレクトメモリアクセス制御部 (R D D M A C)

4 2 0 メモリアクセス部

【図 1】

【図 2】

【 図 3 】

【 図 4 】

〔 四 5 〕

【 6 】

【 义 7 】

【 四 8 】

【 図 9 】

(a)

Diagram illustrating a memory hierarchy structure:

- DRAM:** The base layer is labeled DRAM.

- Page:** A 32Byte wide block is shown, divided into four 32Byte columns labeled X1/1, X1/2, X1/3, and X1/4.

- Row:** A 2048Byte row is shown, divided into 256 8Byte sub-blocks labeled X1:1 through X1:256.

- Block:** The X1/1 column is further divided into 256Byte blocks labeled X1:1 through X1:256.

- Byte:** The X1:1 block is divided into 8Byte bytes labeled X1:1 through X1:256.

(b)