(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4570868号

(P4570868)

(45) 発行日 平成22年10月27日(2010.10.27)

(24) 登録日 平成22年8月20日(2010.8.20)

|                      |                 |

|----------------------|-----------------|

| (51) Int.Cl.         | F 1             |

| H01L 23/12 (2006.01) | H01L 23/12 E    |

| H01L 21/60 (2006.01) | H01L 23/12 F    |

|                      | H01L 21/60 301N |

請求項の数 11 (全 17 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2003-433851 (P2003-433851)  |

| (22) 出願日  | 平成15年12月26日 (2003.12.26)      |

| (65) 公開番号 | 特開2005-191447 (P2005-191447A) |

| (43) 公開日  | 平成17年7月14日 (2005.7.14)        |

| 審査請求日     | 平成18年12月25日 (2006.12.25)      |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部1753番地 |

| (74) 代理人  | 100080001<br>弁理士 筒井 大和                               |

| (72) 発明者  | 宮木 美典<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内            |

| (72) 発明者  | 鈴木 一成<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内            |

| (72) 発明者  | 大橋 裕人<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内            |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1主面と、前記第1主面と対向する第1裏面と、前記第1主面に設けられたチップ搭載領域と、前記チップ搭載領域の周囲に設けられ、かつ電源電位または接地電位が供給される複数の第1ボンディング電極と、前記第1ボンディング電極よりも前記チップ搭載領域から遠い位置に設けられ、かつ信号が入力または出力される複数の第2ボンディング電極とを含む配線基板と、

第2主面と、前記第2主面と対向する第2裏面と、前記第2主面に設けられ、かつ前記第2主面の外周に沿って設けられた複数の第1電極と、前記第2主面に設けられ、かつ前記複数の第1電極よりも内側に設けられた複数の第2電極と、前記第2主面に設けられ、かつ前記複数の第2電極よりも内側の領域に設けられた複数の電源回路セルと、前記第2主面に設けられ、かつ前記複数の第2電極よりも内側の領域に設けられた複数の入出力回路セルとを含み、前記第2裏面が前記チップ搭載領域と対向するように前記配線基板に搭載された半導体チップと、

前記複数の第1ボンディング電極と前記複数の第1電極をそれぞれ電気的に接続する複数の第1ワイヤと、前記複数の第2ボンディング電極と前記複数の第2電極をそれぞれ電気的に接続する複数の第2ワイヤとを有し、

前記第1電極と前記第2電極は、前記半導体チップの外周に沿った方向で互い違いに配置され、

前記第1電極の外形サイズは、前記第2電極の外形サイズよりも大きく、

前記複数の電源回路セルと前記複数の第1電極を電気的に接続する複数の第1配線の幅は、前記複数の入出力回路セルと前記複数の第2電極を電気的に接続する複数の第2配線の幅よりも太く、

前記複数の電源回路セルは、前記接地電位が供給される第1電源回路セルと、前記電源電位のうちの外部電源電位が供給される第2電源回路セルと、前記電源電位のうちの内部電源電位が供給される第3電源回路セルとを有することを特徴とする半導体装置。

**【請求項2】**

請求項1記載の半導体装置において、

前記第1ワイヤの径は、前記第2ワイヤの径よりも太いことを特徴とする半導体装置。

**【請求項3】**

請求項1記載の半導体装置において、

前記第1電極に電気的に接続される第1ワイヤの数は、前記第2電極に電気的に接続される第2ワイヤの数よりも多いことを特徴とする半導体装置。

**【請求項4】**

請求項1記載の半導体装置において、

前記電源回路セルおよび前記入出力回路セルのそれぞれは、バッファ回路、静電破壊保護回路、プリバッファ回路、レベルシフト回路、および論理回路から形成されていることを特徴とする半導体装置。

**【請求項5】**

請求項1記載の半導体装置において、

前記第3電源回路セル上には、第3電極が形成されていることを特徴とする半導体装置。

。

**【請求項6】**

請求項5記載の半導体装置において、

前記複数の第1ボンディング電極は、前記接地電位が供給され、かつ前記チップ搭載領域の周囲にリング状に形成された第3ボンディング電極と、外部電源電位が供給され、かつ前記第3ボンディング電極よりも前記チップ搭載領域から遠い位置にリング状に形成された第4ボンディング電極を有することを特徴とする半導体装置。

**【請求項7】**

請求項6記載の半導体装置において、

前記複数の第1ボンディング電極は、更に、前記内部電源電位が供給され、かつ前記第3ボンディング電極と前記第4ボンディング電極との間にリング状に形成された第5ボンディング電極を有することを特徴とする半導体装置。

**【請求項8】**

請求項7記載の半導体装置において、

前記第3電極は、前記第5ボンディング電極とそれ電気的に接続されていることを特徴とする半導体装置。

**【請求項9】**

請求項1記載の半導体装置において、

前記配線基板は、さらに、前記複数の第1ボンディング電極よりも前記チップ搭載領域から遠い位置に設けられた複数の第6ボンディング電極と、前記複数の第6ボンディング電極よりも前記チップ搭載領域から遠い位置に設けられた複数の第7ボンディング電極を有することを特徴とする半導体装置。

**【請求項10】**

請求項9記載の半導体装置において、

前記半導体チップは、さらに、前記半導体チップの前記第2主面の外周に沿って、クロック信号を入力または出力する複数の第4電極を有し、

前記複数の第4電極は、前記複数の第6ボンディング電極と複数の第3ワイヤを介してそれ電気的に接続されていることを特徴とする半導体装置。

**【請求項11】**

10

20

30

40

50

請求項 1 記載の半導体装置において、

前記配線基板の前記第 1 裏面には、複数のはんだボールが設けられ、

前記複数のはんだボールは、前記複数の第 1 ボンディング電極および前記複数の第 2 ボンディング電極と複数の配線層を介してそれぞれ電気的に接続されていることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造技術に関し、特に、配線基板上に半導体チップが搭載された半導体装置に適用して有効な技術に関するものである。

10

【背景技術】

【0002】

たとえば、半導体装置の主表面において、複数の電極（パッド）を千鳥状に配置し、さらにその主表面を構成する各片に沿って延在し半導体装置の中央部分を包囲するような枠状の電源用電極および接地用電極を設けることにより、半導体装置の主表面における電極配置の自由度を向上し、半導体装置の高機能化に伴うそれら電極数の増加（多ピン化）と、半導体装置のサイズの小型化とへの対応を可能とする技術がある（たとえば、特許文献 1 参照）。

【特許文献 1】特開 2001-244293 号公報

20

【発明の開示】

【発明が解決しようとする課題】

【0003】

近年、半導体装置には、多機能化および高速化が求められ、それに伴って半導体チップ（以下、単にチップと記す）の正面に配置されるパッドの多ピン化が進んでいる。本発明者らは、このような多ピン化した半導体チップを有する半導体装置について検討しており、以下のような課題を見出した。

【0004】

すなわち、本発明者らが検討した半導体装置においては、電源系および接地系のパッドも他の信号入出力系のパッドも同じ仕様（サイズ）で設計され、これらのパッドに接続されているボンディングワイヤも同じ太さのものが用いられている。電源系および接地系については、その他の信号入出力系より大きな電流容量が求められることから、電源系および接地系のパッドとそれに接続するボンディングワイヤについては、その他の信号入出力系のパッドとそれに接続するボンディングワイヤより抵抗等を低減することが求められる。それに対応するためには、電源系および接地系のパッド数をさらに増加することになり、それらに接続するボンディングワイヤ数も増加してしまうことになる。そのため、さらに多ピン化が進み、チップサイズが増加してしまう課題が存在する。

30

【0005】

また、本発明者らが検討した半導体装置においては、パッドはチップ正面の外周に沿って一列で配列してある。このような半導体装置におけるチップサイズを大型化せずに多ピン化を進める場合には、このパッドのサイズが小さくなってしまうことになる。そのため、個々のパッドとそれに接続するボンディングワイヤとの接合面積が小さくなり、パッドとボンディングワイヤとの接続強度が低下してしまう課題が存在する。

40

【0006】

本発明の目的は、多機能化および高速化に伴った多ピン化に対応できる半導体装置を提供することにある。

【0007】

また、本発明の他の目的は、チップサイズの小型化および多ピン化が進んだ場合においても、ボンディングワイヤとパッドとの接続信頼性の低下を防ぐことにある。

【0008】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面か

50

ら明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0010】

本発明による半導体装置は、

第1主面および第1裏面を有し、前記第1主面において中央部にチップ搭載領域が設けられ、前記チップ搭載領域を囲む第1領域にリング状の複数の第1ボンディング電極が形成され、前記第1領域を囲む第2領域に複数の第2ボンディング電極が形成され、内部に前記第1ボンディング電極および前記第2ボンディング電極と電気的に接続する配線が形成された配線基板と、

10

第2主面および第2裏面を有し、前記第2裏面が前記チップ搭載領域と接するように前記配線基板に搭載され、前記第2主面において複数の電極が配置された半導体チップと、

前記複数の電極とこれに対応する前記第1ボンディング電極または前記第2ボンディング電極とを電気的に接続する複数のワイヤとを有し、

前記複数の第1ボンディング電極は電源電位もしくは基準電位と電気的に接続し、

前記複数の第2ボンディング電極は信号の入力もしくは出力に用いられ、

前記複数の電極は、前記第2主面の外周に沿って複数列で配列され、第1列に含まれる前記電極と、前記第2主面内において前記第1列の内側に位置する第2列に含まれる前記電極とは、前記第2主面の前記外周に沿った方向で互い違いに配置され、

20

前記複数の電極は、前記第1ボンディング電極と電気的に接続される複数の第1電極と、前記複数の第2ボンディング電極と電気的に接続される複数の第2電極とを含み、

(a) 前記複数のワイヤのうち、前記第1ボンディング電極と前記複数の第1電極とを電気的に接続する複数の第1ワイヤは、前記複数の第2ボンディング電極と前記複数の第2電極とを電気的に接続する複数の第2ワイヤ以上の径を有する、

もしくは、

(b) 1個の前記第1電極と前記第1ボンディング電極との間には、複数の前記ワイヤが接続されている、

を満たすものである。

30

【0011】

また、本発明による半導体装置の製造方法は、

(a) 第1主面および第1裏面を有し、前記第1主面において中央部にチップ搭載領域が設けられ、前記チップ搭載領域を囲む第1領域に電源電位もしくは基準電位と電気的に接続されるリング状の複数の第1ボンディング電極が形成され、前記第1領域を囲む第2領域に信号の入力もしくは出力に用いられる複数の第2ボンディング電極が形成され、内部に前記第1ボンディング電極および前記第2ボンディング電極と電気的に接続する配線が形成された配線基板を用意する工程、

(b) 第2主面および第2裏面を有し、前記第2主面において複数の電極が外周に沿って複数列で配置された半導体チップを用意する工程、

40

(c) 前記第2裏面が前記チップ搭載領域と接するように前記半導体チップを前記配線基板に搭載する工程、

(d) 前記複数の電極とこれに対応する前記第1ボンディング電極とを第1ワイヤによって電気的に接続する工程、

(e) 前記複数の電極とこれに対応する前記第2ボンディング電極とを第2ワイヤによって電気的に接続する工程、

を含み、

前記(b)工程は、

(b1) 第1列に含まれる前記電極と、前記第2主面内において前記第1列の内側に位置する第2列に含まれる前記電極とを、前記第2主面の前記外周に沿った方向で互い違いに

50

配置する工程、

を含み、

前記複数の電極は、前記第1ポンディング電極と電気的に接続される複数の第1電極と、前記複数の第2ポンディング電極と電気的に接続される複数の第2電極とを含み、

前記第1ワイヤの径は、前記第2ワイヤの径以上とするものである。

#### 【0012】

また、本発明による半導体装置の製造方法は、

(a) 第1主面および第1裏面を有し、前記第1主面において中央部にチップ搭載領域が設けられ、前記チップ搭載領域を囲む第1領域に電源電位もしくは基準電位と電気的に接続されるリング状の複数の第1ポンディング電極が形成され、前記第1領域を囲む第2領域に信号の入力もしくは出力に用いられる複数の第2ポンディング電極が形成され、内部に前記第1ポンディング電極および前記第2ポンディング電極と電気的に接続する配線が形成された配線基板を用意する工程、

(b) 第2主面および第2裏面を有し、前記第2主面において複数の電極が外周に沿って複数列で配置された半導体チップを用意する工程、

(c) 前記第2裏面が前記チップ搭載領域と接するように前記半導体チップを前記配線基板に搭載する工程、

(d) 前記複数の電極とこれに対応する前記第1ポンディング電極または前記第2ポンディング電極とを複数のワイヤによって電気的に接続する工程、

を含み、

前記(b)工程は、

(b1) 第1列に含まれる前記電極と、前記第2主面内において前記第1列の内側に位置する第2列に含まれる前記電極とを、前記第2主面の前記外周に沿った方向で互い違いに配置する工程、

を含み、

前記複数の電極は、前記第1ポンディング電極と電気的に接続される複数の第1電極と、前記複数の第2ポンディング電極と電気的に接続される複数の第2電極とを含み、

1個の前記第1電極と前記第1ポンディング電極との間には、前記複数のワイヤを接続するものである。

#### 【発明の効果】

#### 【0013】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

#### 【0014】

すなわち、多機能化および高速化に伴った多ピン化に対応可能な半導体装置を提供できる。

#### 【発明を実施するための最良の形態】

#### 【0015】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

#### 【0016】

(実施の形態1)

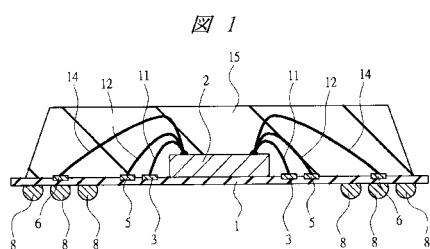

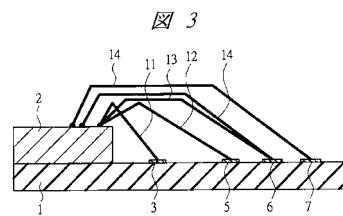

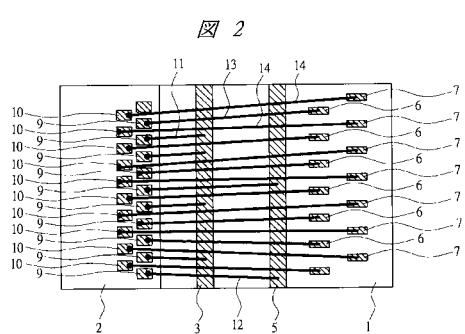

図1は本実施の形態1の半導体装置の構造の一例を示す断面図であり、図2は図1に示した半導体装置の要部平面図であり、図3は図1に示した半導体装置の要部断面図である。

#### 【0017】

本実施の形態1の半導体装置は、配線基板1上にチップ2が搭載された樹脂封止型の半導体パッケージであり、チップ2にはロジックICまたはロジックICを含む特定用途向けIC(Application Specific IC; ASIC)が形成されているものである。本実施の

10

20

30

40

50

形態 1においてはその半導体パッケージの一例として、図 1に示すような BGA (Ball Grid Array)を取り上げて説明する。

#### 【0018】

配線基板 1は正面(第1正面)と裏面(第1裏面)とを有しており、その正面の中央部のチップ搭載領域にはチップ2が搭載されている。そのチップ搭載領域の外周の領域(第1領域)においては、チップ領域を取り囲むリング状のボンディング電極(第1ボンディング電極)3、5が設けられている。また、ボンディング電極3、5が設けられた領域のさらに外周の領域(第2領域)には、ボンディング電極(第2ボンディング電極)6、7(図1中におけるボンディング電極7の図示は省略)がそれぞれボンディング電極3、5を取り囲んで並んで配置されている。配線基板1は、たとえばガラス繊維入りエポキシ基板などから形成されたものであり、絶縁層と配線とを交互に積み上げることによって形成されたビルトアップ配線板である。配線基板1の裏面には、複数の外部端子であるはんだボール8が取り付けられている。これらはんだボール8は、配線基板1内に形成された配線(配線層)を介して、ボンディング電極6以外のボンディング電極3～7と電気的に接続されている。ボンディング電極3は、配線基板1内に形成された配線および所定のはんだボール8を介して接地電位(基準電位)と電気的に接続している。また、ボンディング電極5には、配線基板1内に形成された配線および所定のはんだボール8を介して外部電源電位が供給されている。

#### 【0019】

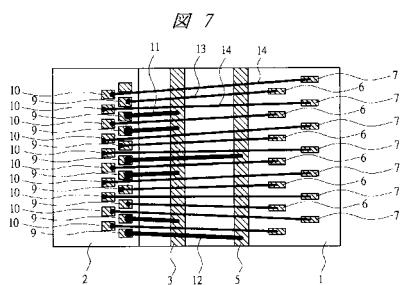

チップ2は、その裏面(第2裏面)が配線基板1の正面のチップ搭載領域と接するように搭載されている。チップ2の正面(第1裏面)においては、ボンディングパッド(電極、第1電極)9が外周に沿って並んで配置され、第1列を形成している。また、ボンディングパッド9が配置された領域の内側の領域には、ボンディングパッド9と同様にボンディングパッド(電極、第2電極)10がチップ2の正面の外周に沿って並んで配置され、第2列を形成している。ボンディングパッド9は前述の接地電位または外部電源電位と電気的に接続するものを含み、接地電位と電気的に接続するボンディングパッド9はワイヤ(第1ワイヤ)11を介してボンディング電極3と電気的に接続され、外部電源電位と電気的に接続するボンディングパッド9はワイヤ(第1ワイヤ)12を介してボンディング電極5と電気的に接続されている。また、ボンディングパッド9は、ワイヤ(第2ワイヤ)13を介してボンディング電極6と電気的に接続されている。前記ワイヤ13に接続するボンディングパッド9は、前記ワイヤ13を介して、データ信号やコマンド信号などの信号の入出力を行う。ボンディングパッド10は、信号のチップ2内への入出力に用いられ、ワイヤ(第2ワイヤ)14を介してボンディング電極6、7と電気的に接続されている。これらワイヤ11～14は、たとえばAu(金)から形成されている。

#### 【0020】

上記のような配線基板1の正面、チップ2およびワイヤ11～14は、封止体15によって樹脂封止されている。

#### 【0021】

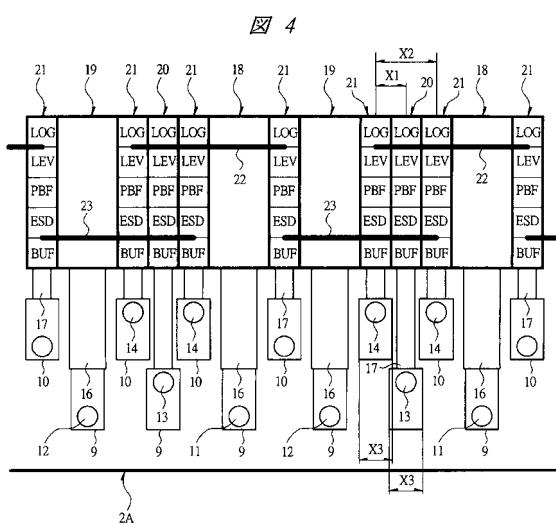

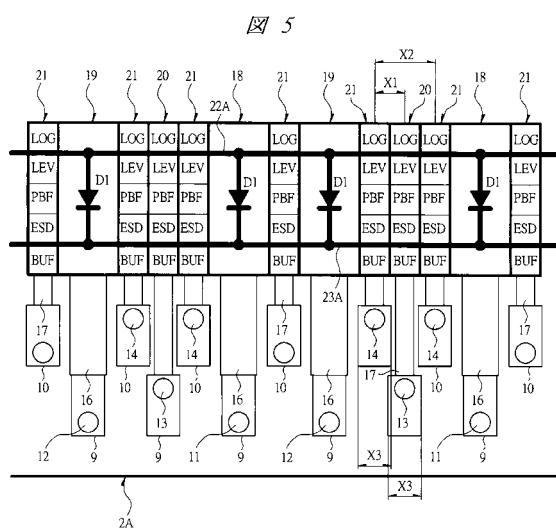

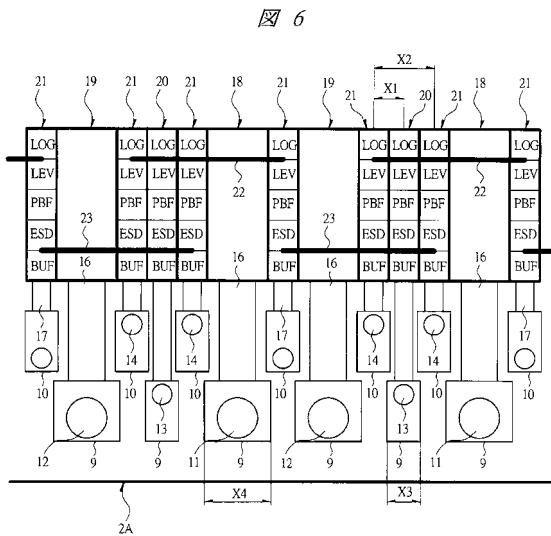

図4および図5は、チップ2内の要部における、ボンディングパッド9、10のそれぞれが電気的に接続する回路セルと、各回路セル間の電気的接続関係を示したものである。また、図4および図5中において、ボンディングパッド9、10のそれぞれと接続するワイヤ11～14は、ボンディングパッド9、10との接続部のみを示している。

#### 【0022】

前述したように、ボンディングパッド9、10は、それぞれチップ2の正面の外周(チップ端部2A)に沿って並んで配置されている。これらボンディングパッド9、10は、それぞれ、たとえばAl(アルミニウム)膜をパターニングすることで形成された配線16、17を介して所定の回路セルと電気的に接続されている。

#### 【0023】

ワイヤ11を介してボンディング電極3と電気的に接続するボンディングパッド9は、電源回路セル18と電気的に接続され、配線16と共に電源回路セル18を基準電位(接

10

20

30

30

40

50

地電位)に電気的に接続する。ワイヤ12を介してボンディング電極5と電気的に接続するボンディングパッド9は、電源回路セル19と電気的に接続され、配線16を介して電源回路セル19へ外部電源からの外部電源電位を供給する。ワイヤ13を介してボンディング電極6と電気的に接続するボンディングパッド9は、入出力回路セル20と電気的に接続され、入出力回路セル20より送られてくるクロック信号をワイヤ13を介してボンディング電極6へ送信、もしくはワイヤ13を介してボンディング電極6から送られてくる信号を配線17を介して入出力回路セル20へ送信する。ワイヤ14を介してボンディング電極6、7と電気的に接続するボンディングパッド10は、入出力回路セル21と電気的に接続され、ワイヤ14を介してボンディング電極6、7との間で種々の信号の送受信を行う。

10

#### 【0024】

入出力回路セル20、21は、たとえばバッファ回路BUF、静電破壊保護回路ESD、プリバッファ回路PBF、レベルシフト回路LEVおよび論理回路LOGなどから形成されている。

#### 【0025】

図4に示す各回路セル間の電気的接続関係の例では、1つの電源回路セル18は、配線22を介して4つの入出力回路セル20、21と電気的に接続し、その配線22を介して4つの入出力回路セル20、21中の所定の回路を基準電位(接地電位)に電気的に接続している。また、1つの電源回路セル19は、配線23を介して4つの入出力回路セル20、21と電気的に接続し、その配線23を介して4つの入出力回路セル20、21中の所定の回路に外部電源からの外部電源電位を供給している。一方、図5に示す各回路セル間の電気的接続関係の例では、すべての電源回路セル18と電気的に接続するリング状の配線22Aと、すべての電源回路セル19と電気的に接続するリング状の配線23Aとが設けられている。また、電源回路セル18、19中においては、基準電位に接続された配線22Aと、電源電位に接続された配線23Aとの間に、アノードを配線22Aに接続し、カソードを配線23Aに接続するダイオードD1を配置することによって静電破壊を防止している。また、前記ダイオードD1に限らず、周知の技術により、様々な静電破壊防止回路を配線22Aと配線23Aとの間に配置することが可能である。配線22Aは、すべての入出力回路セル20、21と電気的に接続し、入出力回路セル20、21中の所定の回路を基準電位(接地電位)に電気的に接続している。また、配線23Aもすべての入出力回路セル20、21と電気的に接続し、入出力回路セル20、21中の所定の回路に外部電源からの外部電源電位を供給している。このような配線22A、23Aを設けた場合でも、図4に示したような配線22、23を設けた場合と同様の効果を得ることができる。なお、以降の本実施の形態1では、配線22、23を設けた場合を例に取って説明を続ける。

20

#### 【0026】

本実施の形態1においては、ボンディングパッド9とボンディングパッド10とは、チップ2の正面の外周に沿った方向で互い違いに配置されている。このようにボンディングパッド9、10を配置することにより、たとえばボンディングパッド9、10をそれぞれ一列ずつ配置せずにすべてのボンディングパッド9、10を一列で配置した場合(以下、検討例1と記す)に比べて、大きな面積のボンディングパッド9、10を配置することが可能となる。たとえば、隣り合う入出力回路セル20と入出力回路セル21との配置ピッチX1(約40μm)、および間に1つの入出力回路セル20を挟んで隣り合う入出力回路セル21の配置ピッチX2(約80μm)が、本実施の形態1と検討例1とで変わらないとすると、検討例1では約35μmであったボンディングパッド9、10の幅X3を、本実施の形態1では約50μmに拡大することができる。それにより、ボンディングパッド9、10とワイヤ11～14とが接続可能な面積を大きく確保することができる。ワイヤ11～14の径を大きくすることができる。その結果、ボンディングパッド9、10とワイヤ11～14との接続強度を向上することが可能となる。また、ボンディングパッド9、10の面積が大きくなうことにより、これらボンディングパッド9、10

30

40

50

が配置された位置が認識しやすくなる。それにより、ボンディングパッドの位置の認識能力が低いワイヤボンダを用いてもワイヤ11～14を取り付けることが可能となる。

#### 【0027】

また、本実施の形態1においては、ボンディングパッド9のうち、接地電位と電気的に接続する（ワイヤ11が接続された）ボンディングパッド9と、外部電源より外部電源電位が供給される（ワイヤ12が接続された）ボンディングパッド9とに着目すると、隣接するボンディングパッド9間には、チップ2の正面の外周に沿った方向で奇数個のボンディングパッド（入出力回路セル20と電気的に接続するボンディングパッド9およびボンディングパッド10）が配置されている。このようなボンディングパッド9、10の配置および電気的接続とすることにより、接地電位と電気的に接続するボンディングパッドおよび外部電源より外部電源電位が供給されるボンディングパッド（以降、これらのボンディングパッド9を電源系のボンディングパッドと記す）を、チップ2の正面内においてボンディングパッド10より外周に配置されるボンディングパッド9とすることができます。このように、電源系のボンディングパッド9をボンディングパッド10より外周に配置し、これら電源系のボンディングパッド9が電気的に接続するボンディング電極3、5を配線基板1の正面内で相対的に内側に配置することにより、電源系のボンディングパッド9とボンディング電極3、5とをそれぞれ電気的に接続するワイヤ11、12の長さを短くすることができる。それにより、ワイヤ11、12の電気抵抗を下げる所以である。たとえばチップ2内に形成されたロジックICの動作の高速化を実現することが可能となる。

10

20

#### 【0028】

ところで、本実施の形態1のようなボンディングパッド9、10の配置方法とすることにより、電源回路セル18、19とボンディングパッド9との間に配置される配線16は、検討例1より長くなってしまうことになる。また、電源系のボンディングパッド9に接続する配線16相互の間には、他のボンディングパッド（以降、信号系のボンディングパッドと記す）と接続する配線17が少なくとも1本配置される。このようなレイアウトになることにより、電源電位に接続される配線16と基準電位に接続される配線16との距離が必然的に大きくなる。電源系の配線16同士の距離が大きくなることにより、電源を供給する配線と、前記電源電流に対して主要なリターンカレント経路となる近接する接地電位を供給する配線との間の距離が大きくなる。従って、電流ループが大きくなり、電源系配線の自己インダクタンスと相互インダクタンスが増大する傾向となる。

30

#### 【0029】

前述したように、本実施の形態1では、ボンディングパッド9とボンディングパッド10とは、チップ2の正面の外周に沿った方向で互い違いに配置されており、隣り合うボンディングパッド9間には配線が配置されていないことから、図6に示すように、電源系のボンディングパッド9の幅X4は、ボンディングパッド10の幅X3より大きく確保することができ、たとえば約100μmとすることができる。その結果、図6～図8に示すように、本実施の形態1においては電源系のボンディングパッド9と接続するワイヤ11、12の径を他のワイヤ13、14の径より大きくすることができる。本実施の形態1では、ワイヤ13、14の径が20μmであるのに対して、ワイヤ11、12の径を30μmにできることを例示できる。その結果、ワイヤ11、12におけるインピーダンスを低減するので、上記配線16で増加したインピーダンスをワイヤ11、12の低抵抗化により相殺することができる。すなわち、電源回路セル18、19と電気的に接続する配線16、ボンディングパッド9およびワイヤ11、12の総合的なインピーダンスを低減するので、チップ2内に形成されたロジックICの動作の高速化またはASICの多機能化を実現することができる。

40

#### 【0030】

ここで、ワイヤ13、14より径の大きくなったワイヤ11、12を接続する工程について説明する。まず、配線基板1の正面のチップ搭載領域にチップ2を搭載した後、第1のワイヤボンダ（第1ボンディング装置）を用いて電源系のボンディングパッド9とボン

50

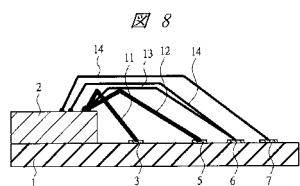

ディング電極 3、5との間にそれぞれワイヤ 11、12を接続する。この時、その第1のワイヤボンダの動く軌跡は、略三角形となる。図8においては、ワイヤ 11、12が略三角形となっているが、これは第1のワイヤボンダの動いた軌跡とする。このような軌跡となるように第1ワイヤボンダを動作させることにより、相対的に長さの短いワイヤ 11、12は短時間で電源系のボンディングパッド9とボンディング電極3、5との間にそれ取り付けることが可能となる。次いで、ワイヤボンダを第1のワイヤボンダから第2のワイヤボンダ(第2ボンディング装置)に代え、チップ2内に形成された入出力回路セル20と電気的に接続するボンディングパッド9とボンディング電極6との間にワイヤ 13を接続する。このようにワイヤボンダの種類を代えたのは、ワイヤボンダによって取り付けることのできるワイヤの太さが変わってくるからである。続いて、その第2のワイヤボンダを用いて、接続後のループがワイヤ 11～13より高くなるワイヤ 14をボンディングパッド10とボンディング電極6、7との間に接続する。この時、その第2のワイヤボンダの動く軌跡は、略台形となる。図8においては、ワイヤ 14が略台形となっているが、これは第2のワイヤボンダの動いた軌跡とする。このように、相対的にループが高くなるワイヤ 14を相対的にループが低くなるワイヤ 11～13の後に接続することにより、ワイヤ 14とワイヤ 11～13とが接触してしまう不具合を防ぐことができる。

#### 【0031】

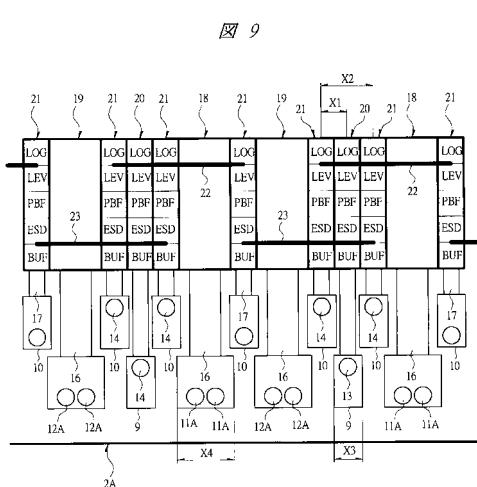

また、上記のような相対的に径の大きいワイヤ 11、12を用いる代わりに、図9に示すように、ワイヤ 13～14と同程度の径を有するワイヤ(第1ワイヤ) 11A、12Aを複数本、たとえば2本電源系のボンディングパッド9とボンディング電極3、5との間にそれぞれ接続してもよい。このようなワイヤ 11A、12Aとすることにより、ワイヤ 13、14の接続に用いる第2のワイヤボンダをワイヤ 11A、12Aを接続する工程にも用いることが可能となる。すなわち、ワイヤ 11A、12A、13、14を接続する工程を1台のワイヤボンダ(第2のワイヤボンダ)だけで実施することが可能となる。

#### 【0032】

##### (実施の形態2)

本実施の形態2の半導体装置も前記実施の形態1の半導体装置と同様に、配線基板上にチップが搭載された樹脂封止型の半導体パッケージである。

#### 【0033】

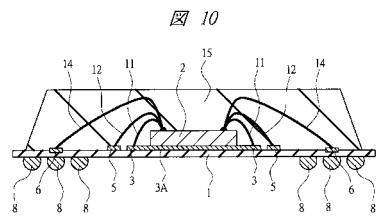

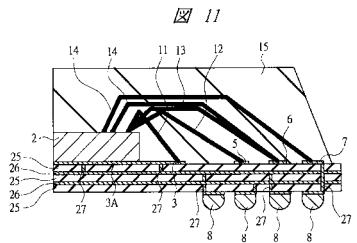

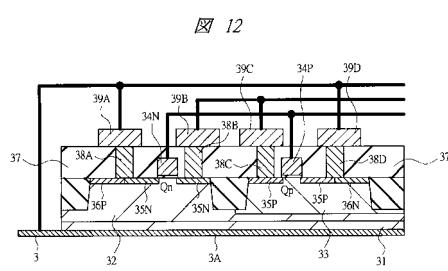

図10は本実施の形態2の半導体装置の構造の一例を示す断面図であり、図11は図10に示した半導体装置の要部平面図であり、図12は図10に示した半導体装置に含まれるチップの要部構造とチップ下に配置された電極と各部材の電気的接続関係とを示す要部断面図である。

#### 【0034】

本実施の形態2においては、前記実施の形態1の半導体装置に含まれる配線基板1において、正面のチップ搭載領域に電極(第3ボンディング電極)3Aを配置したものである。この電極3Aはその周囲を取り囲むボンディング電極3と連続しており、電極3Aとボンディング電極3Aとは、同じ材料から一体に形成されたものである。チップ2は、裏面が電極3Aと接するように配線基板1上に搭載されている。

#### 【0035】

前記実施の形態1でも説明したように、配線基板1は、絶縁層25と配線(配線層)26とを交互に積み上げることによって形成されたビルドアップ配線板である(図11参照)。また、配線基板1内に形成されたスルーホール内に配置された配線27によって、電極3A、ボンディング電極3～5、配線層25、およびはんだボール8の対応するもの同士が電気的に接続されている。

#### 【0036】

また、図12に示すように、チップ2は、たとえばSi(シリコン)からなるp型の半導体基板31の正面に形成されたpチャネル型MISFET(Metal Insulator Semiconductor Field Effect Transistor)Qpおよびnチャネル型MISFETQnを有している。半導体基板1の正面にはp型ウエル32およびn型ウエル33が形成され、p型ウエ

ル32およびn型ウエル33上にはそれぞれゲート電極34P、34Nが形成されている。ゲート電極34Pの両側のn型ウエル33にはp型半導体領域35Pが形成され、pチャネル型MISFETQpはこのp型半導体領域35Pをソースおよびドレインとしている。ゲート電極34Nの両側のp型ウエル32にはn型半導体領域35Nが形成され、nチャネル型MISFETQnはこのn型半導体領域35Nをソースおよびドレインとしている。また、pチャネル型MISFETQpのソースとなるp型半導体領域35Pに隣接する位置にはn型半導体領域36Nが形成され、nチャネル型MISFETQnのソースとなるn型半導体領域35Nに隣接する位置にはp型半導体領域36Pが形成されている。

nチャネル型MISFETQnおよびpチャネル型MISFETQpが形成された半導体基板1の主面上には層間絶縁膜37が成膜されており、その層間絶縁膜37に開孔されたコンタクトホール内にはプラグ38A、38B、38C、38Dが形成されている。プラグ38A、38B、38C、38D上には、それぞれと接続する配線39A、39B、39C、39Dが形成されている。プラグ38Aは、nチャネル型MISFETQnのソースであるn型半導体領域35Nおよびp型半導体領域36Pに達し、これらと配線39Aとに電気的に接続している。プラグ38Bは、nチャネル型MISFETQnのドレインであるn型半導体領域35Nに達し、これと配線39Bとに電気的に接続している。プラグ38Cは、pチャネル型MISFETQpのドレインであるp型半導体領域35Pに達し、これと配線39Cとに電気的に接続している。プラグ38Dは、pチャネル型MISFETQpのソースであるp型半導体領域35Pおよびn型半導体領域36Nに達し、これらと配線39Dとに電気的に接続している。配線39A、39Dは、さらに上層に形成された配線(図示は省略)を介してボンディング電極3と電気的に接続されている。また、半導体基板33は、その裏面が電極3と接している。

#### 【0037】

ところで、チップ2内に形成されたロジックICの電気特性を維持しつつ動作を高速化するには、ロジックICと外部電源との間およびロジックICと接地電位(基準電位)との間の電流容量の向上が求められ、そのため電源系のボンディングパッド9を増やすことと接続するワイヤ11、12も増やす手段が考えられる。このような手段を用いた場合、たとえばチップ2のサイズの小型化も求められると、電源系のボンディングパッド9を小型化し、ワイヤ11、12については細くすることで対応することとなる。そのため、ワイヤ11、12の電気抵抗が増大し、電流容量の向上とチップ2の小型化を同時に実現することが困難になってしまう。

#### 【0038】

一方、本実施の形態2の半導体装置によれば、電極3が接地電位(基準電位)と電気的に接続するボンディング電極3と一緒に形成されていることにより、チップ2は裏面全体で接地電位(基準電位)と電気的に接続することができる。それにより、チップ2内のロジックICと接地電位(基準電位)との間の電流容量を向上することができる。すなわち、ロジックICの電気特性を維持しつつ動作を高速化することが可能となる。また、ロジックICと接地電位(基準電位)との間の電流容量を向上できることにより、ロジックICに生じるノイズを低減することができる。また、チップ2が裏面全体で接地電位(基準電位)と電気的に接続することで、ロジックICと接地電位(基準電位)との間で十分大きな電流容量を確保することができるので、接地電位(基準電位)と電気的に接続するボンディングパッド9およびワイヤ11を低減することが可能となる。それにより、チップ2の小型化を実現することができる。また、接地電位(基準電位)と電気的に接続するボンディングパッド9およびワイヤ11が省略できた個所において、外部電源電位と電気的に接続するボンディングパッド9およびワイヤ12を配置し、ロジックICと外部電源との間の電流容量を向上させてもよい。

#### 【0039】

上記のような本実施の形態2によっても、前記実施の形態1と同様の効果を得ることができる。

#### 【0040】

10

20

30

40

50

(実施の形態 3)

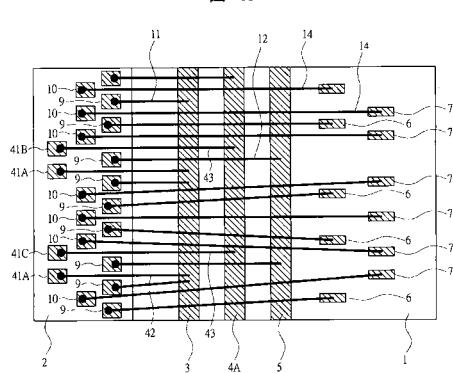

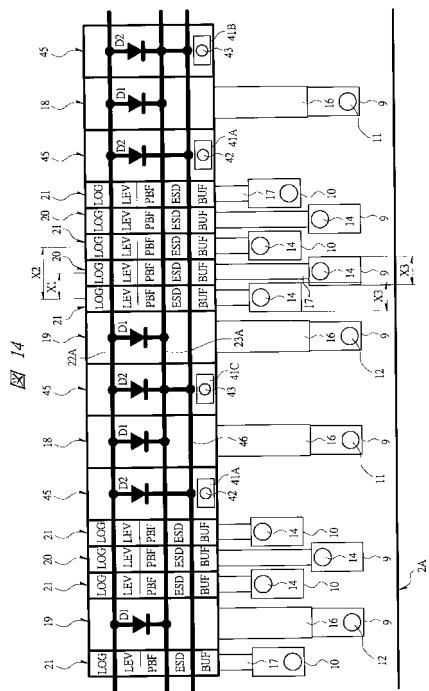

図 13 は本実施の形態 3 の半導体装置の要部平面図である。

【0041】

本実施の形態 3 の半導体装置は、前記実施の形態 1 の半導体装置に含まれるチップ 2 (図 1 参照) 内に内部電源回路が設けられたものである。本実施の形態 3 において、ボンディング電極 4 A は、その内部電源回路のみと電気的に接続するものである。その内部電源回路は、たとえば外部電源より供給される外部電源電圧 (たとえば約 5.5 V) を所定の電圧 (たとえば約 3.3 V) に変換し、内部動作電圧としてチップ 2 内の回路へ供給するものである。

【0042】

チップ 2 の正面においては、ボンディングパッド 10 が配置された領域の内側の領域にボンディングパッド 41A、41B、41C がチップ 2 の正面の外周に沿って並んで配置され、第 3 列を形成している。これらボンディングパッド 41A、41B、41C は、上記内部電源回路と電気的に接続するものである。また、ボンディングパッド 41A は、ワイヤ 42 を介してボンディング電極 3 と電気的に接続し、接地電位 (基準電位) と電気的に接続される。ボンディングパッド (第 3 電極、第 4 電極) 41B、41C は、ワイヤ 43 を介してボンディング電極 4 A と電気的に接続する。

【0043】

図 14 に示すように、ボンディングパッド 41A、41B、41C は、ボンディングパッド 9、10 と同様に、それぞれ、たとえば A1 膜をパターニングすることで形成された配線 44 を介して所定の回路セルと電気的に接続されている。

【0044】

ワイヤ 42 を介してボンディング電極 3 と電気的に接続するボンディングパッド 41A は、内部電源回路セル 45 と電気的に接続され、配線 44 と共に内部電源回路セル 45 を基準電位 (接地電位) に電気的に接続する。ワイヤ 43 を介してボンディング電極 4 A と電気的に接続するボンディングパッド 41B、41C は、配線 44 を介して内部電源回路セル 45 と電気的に接続され、配線 44 を介して内部電源回路セル 45 から送られてきた内部動作電圧をワイヤ 43 を介してボンディング電極 4 A へ送り出す役割、またはボンディング電極 4 A およびワイヤ 43 を経由して送られてきた内部動作電圧を配線 44 を介して内部電源回路セル 45 へ送り出す役割を果たしている。

【0045】

図 14 に示す各回路セル間の電気的接続関係の例では、前記実施の形態 1 において図 5 に示した例と同様のすべての電源回路セル 18 と電気的に接続するリング状の配線 22A と、すべての電源回路セル 19 と電気的に接続するリング状の配線 23A とが設けられ、電源回路セル 18、19 中においては、配線 22A、23A 間にダイオード D1 を配置することによって静電破壊を防止している。また、すべての内部電源回路セル 45 と電気的に接続するリング状の配線 46 が設けられ、内部電源回路セル 45 中においては、配線 22A、46 間にダイオード D2 を配置することによって静電破壊を防止している。また、配線 46 はすべての入出力回路セル 20、21 と電気的に接続し、入出力回路セル 20、21 中の所定の回路に内部電源電圧を供給している。

【0046】

本実施の形態 3 においては、ボンディングパッド 9、ボンディングパッド 10、およびボンディングパッド 41A、41B、41C は、チップ 2 の正面の外周に沿った方向で互い違いに配置されている (図 14 参照)。このようにボンディングパッド 9、10、41A、41B、41C を配置することにより、前記実施の形態 1 と同様に、たとえばすべてのボンディングパッド 9、10、41A、41B、41C を一列で配置した場合に比べて、大きな面積のボンディングパッド 9、10、41A、41B、41C を配置することが可能となる。

【0047】

また、ボンディングパッド 41A、41B、41C を内部電源回路セル 45 内に配置す

10

20

30

40

50

ることにより、半導体チップの小型化を図ることができる。

#### 【0048】

また、本実施の形態3においても、前記実施の形態1と同様に、ボンディングパッド9のうち、電源系のボンディングパッド9に着目すると、隣接するボンディングパッド9間には、チップ2の正面の外周に沿った方向で奇数個のボンディングパッド（入出力回路セル20と電気的に接続するボンディングパッド9、ボンディングパッド10およびボンディングパッド41A、41B、41C）が配置されている。このようなボンディングパッド9、10、41A、41B、41Cの配置および電気的接続とすることにより、本実施の形態3においても電源系のボンディングパッド9を、チップ2の正面内においてボンディングパッド10、41A、41B、41Cより外周に配置されるボンディングパッド9とすることができます。このように、電源系のボンディングパッド9をボンディングパッド10、41A、41B、41Cより外周に配置し、これら電源系のボンディングパッド9が電気的に接続するボンディング電極3、5を配線基板1の正面内で相対的に内側に配置することにより、電源系のボンディングパッド9とボンディング電極3、5とをそれぞれ電気的に接続するワイヤ11、12の長さを短くすることができる。それにより、ワイヤ11、12の電気抵抗を下げるることができますので、たとえばチップ2内に形成されたロジックICの動作の高速化を実現することが可能となる。10

#### 【0049】

上記のような本実施の形態3によっても、前記実施の形態1と同様の効果を得ることができます。20

#### 【0050】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【産業上の利用可能性】

#### 【0051】

本発明の半導体装置およびその製造方法は、多機能化および高速化に伴った多ピン化が求められる半導体装置およびその製造工程に広く適用することができる。

#### 【図面の簡単な説明】

#### 【0052】

30

【図1】本発明の実施の形態1である半導体装置の構造を示す断面図である。

【図2】図1に示した半導体装置の要部平面図である。

【図3】図1に示した半導体装置の要部断面図である。

【図4】チップ正面に配置されたボンディングパッドの各々が電気的に接続する回路セルと、各回路セル間の電気的接続関係とを示す説明図である。

【図5】チップ正面に配置されたボンディングパッドの各々が電気的に接続する回路セルと、各回路セル間の電気的接続関係とを示す説明図である。

【図6】チップ正面に配置されたボンディングパッドの各々が電気的に接続する回路セルと、各回路セル間の電気的接続関係とボンディングパッドに接続するワイヤとを示す説明図である。40

【図7】本発明の実施の形態1である半導体装置の要部平面図である。

【図8】本発明の実施の形態1である半導体装置の要部断面図である。

【図9】チップ正面に配置されたボンディングパッドの各々が電気的に接続する回路セルと、各回路セル間の電気的接続関係とボンディングパッドに接続するワイヤとを示す説明図である。

【図10】本発明の実施の形態2である半導体装置の構造を示す断面図である。

【図11】図10に示した半導体装置の要部断面図である。

【図12】本発明の実施の形態2である半導体装置に含まれるチップの要部構造とチップ下に配置された電極と各部材の電気的接続関係とを示す要部断面図である。

【図13】本発明の実施の形態1である半導体装置の要部平面図である。50

【図14】チップ正面に配置されたボンディングパッドの各々が電気的に接続する回路セルと、各回路セル間の電気的接続関係とボンディングパッドに接続するワイヤとを示す説明図である。

【符号の説明】

【0053】

|                     |                      |    |

|---------------------|----------------------|----|

| 1                   | 配線基板                 |    |

| 2                   | チップ                  |    |

| 2 A                 | チップ端部                |    |

| 3、5                 | ボンディング電極（第1ボンディング電極） |    |

| 3 A                 | 電極（第3ボンディング電極）       | 10 |

| 4 A                 | ボンディング電極             |    |

| 4 B、4 C             | ボンディング電極（第4ボンディング電極） |    |

| 6、7                 | ボンディング電極（第2ボンディング電極） |    |

| 8                   | はんだボール               |    |

| 9                   | ボンディングパッド（電極、第1電極）   |    |

| 10                  | ボンディングパッド（電極、第2電極）   |    |

| 11、12               | ワイヤ（第1ワイヤ）           |    |

| 11 A、12 A           | ワイヤ（第1ワイヤ）           |    |

| 13                  | ワイヤ（第2ワイヤ）           |    |

| 14                  | ワイヤ（第2ワイヤ）           | 20 |

| 15                  | 封止体                  |    |

| 16                  | 配線                   |    |

| 17                  | 配線                   |    |

| 18                  | 電源回路セル               |    |

| 19                  | 電源回路セル               |    |

| 20                  | 入出力回路セル              |    |

| 21                  | 入出力回路セル              |    |

| 22、22 A、23、23 A     | 配線                   |    |

| 25                  | 絶縁層                  |    |

| 26                  | 配線（配線層）              | 30 |

| 27                  | 配線                   |    |

| 31                  | 半導体基板                |    |

| 32                  | p型ウエル                |    |

| 33                  | n型ウエル                |    |

| 34 N、34 P           | ゲート電極                |    |

| 35 N、36 N           | n型半導体領域              |    |

| 35 P、36 P           | p型半導体領域              |    |

| 37                  | 層間絶縁膜                |    |

| 38 A、38 B、38 C、38 D | プラグ                  |    |

| 39 A、39 B、39 C、39 D | 配線                   | 40 |

| 41 A                | ボンディングパッド            |    |

| 41 B                | ボンディングパッド            |    |

| 41 C                | ボンディングパッド            |    |

| 42、43               | ワイヤ                  |    |

| 44                  | 配線                   |    |

| 45                  | 内部電源回路セル             |    |

| 46                  | 配線                   |    |

| B U F               | バッファ回路               |    |

| D 1、D 2             | ダイオード                |    |

| E S D               | 静电破壊保護回路             | 50 |

L E V レベルシフト回路

L O G 論理回路

P B F プリバッファ回路

Q n n チャネル型 M I S F E T

Q p p チャネル型 M I S F E T

【図 1】

図 1

【図 3】

図 3

【図 2】

図 2

【図 4】

図 4

【図5】

【図6】

9: ボンディングパッド(電極, 第1電極)

10: ボンディングパッド(電極, 第2電極)

11,12: ワイヤ(第1ワイヤ)

13,14: ワイヤ(第2ワイヤ)

【 図 7 】

【 四 9 】

( 8 )

【図10】

【図11】

【図13】

【図12】

【図14】

---

フロントページの続き

審査官 板谷 一弘

(56)参考文献 特開2003-133470(JP,A)

特開平06-112359(JP,A)

特開平08-078458(JP,A)

特開2000-235997(JP,A)

特開平11-074303(JP,A)

特開2005-277392(JP,A)

特開平02-196450(JP,A)

特開平11-284006(JP,A)

特開平11-087399(JP,A)

特開2003-197748(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H01L 21/60