(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-229961

(P2009-229961A)

(43) 公開日 平成21年10月8日(2009.10.8)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/36</b> (2006.01)  | G09G 3/36 | 2 H 09 3    |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 2 H 19 3    |

| <b>G02F 1/133</b> (2006.01) | G09G 3/20 | 5 C 00 6    |

|                             | G09G 3/20 | 5 C 08 0    |

|                             | G09G 3/20 | 6 1 2 T     |

|                             |           | 6 4 2 F     |

審査請求 未請求 請求項の数 10 O L (全 19 頁) 最終頁に続く

|           |                            |          |                                               |

|-----------|----------------------------|----------|-----------------------------------------------|

| (21) 出願番号 | 特願2008-77216 (P2008-77216) | (71) 出願人 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (22) 出願日  | 平成20年3月25日 (2008.3.25)     | (74) 代理人 | 100090387<br>弁理士 布施 行夫                        |

|           |                            | (74) 代理人 | 100090398<br>弁理士 大渕 美千栄                       |

|           |                            | (74) 代理人 | 100113066<br>弁理士 永田 美佐                        |

|           |                            | (72) 発明者 | 進藤 貴志<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内        |

|           |                            | (72) 発明者 | 小野 芳照<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内        |

|           |                            |          | 最終頁に続く                                        |

(54) 【発明の名称】 液晶表示制御装置及び電子機器

## (57) 【要約】

【課題】 画像表示用クロックの周波数を変更することにより、液晶表示装置を適切な消費電力で動作させることができる液晶表示制御装置及び電子機器を提供すること。

【解決手段】 本発明の液晶表示制御装置 10 (LCDコントローラ) は、液晶表示装置 40 (LCD) の画像表示を制御する。液晶表示制御装置 10 は、液晶表示装置 40 の画像表示用クロック 12 を生成する画像表示用クロック生成部 100 と、ホストCPU 20 から受け取った所定の信号又は内部レジスタの設定値に基づいて、画像表示用クロック 12 の周波数を変更するか否かを判断し、液晶表示装置 40 が画像表示を行わない期間に画像表示用クロック 12 の周波数を変更するように制御するクロック周波数変更制御部 200 と、を含む。

【選択図】 図 1

**【特許請求の範囲】****【請求項 1】**

液晶表示装置の画像表示を制御する液晶表示制御装置であって、

前記液晶表示装置の画像表示用クロックを生成する画像表示用クロック生成部と、

外部ホストから受け取った所定の信号又は内部レジスタの設定値に基づいて、前記画像表示用クロックの周波数を変更するか否かを判断し、前記液晶表示装置が画像表示を行わない期間に前記画像表示用クロックの周波数を変更するように制御するクロック周波数変更制御部と、を含むことを特徴とする液晶表示制御装置。

**【請求項 2】**

請求項 1において、

前記クロック周波数変更制御部は、

前記液晶表示装置がフレームの最後の画素を表示してから次のフレームの最初の画素を表示するまでの期間に前記画像表示クロックの周波数を変更するように制御することを特徴とする液晶表示制御装置。

**【請求項 3】**

請求項 1又は 2において、

前記画像表示用クロック生成部は、

所定の基準クロックを分周して前記画像表示用クロックを生成するクロック分周回路を含み、

前記クロック周波数変更制御部は、

前記クロック分周回路の分周比を変更することにより前記画像表示用クロックの周波数を変更するように制御することを特徴とする液晶表示制御装置。

**【請求項 4】**

請求項 1乃至 3のいずれかにおいて、

前記クロック周波数変更制御部は、

目標の周波数に達するまで前記画像表示用クロックの周波数を段階的に変更するように制御することを特徴とする液晶表示制御装置。

**【請求項 5】**

請求項 4において、

前記画像表示用クロックの周波数を段階的に変更するタイミングを設定するためのクロック周波数変更タイミング設定レジスタを含み、

前記クロック周波数変更制御部は、

前記クロック周波数変更タイミング設定レジスタの設定値に基づいて、前記画像表示用クロックの周波数を段階的に変更するように制御することを特徴とする液晶表示制御装置。

**【請求項 6】**

請求項 1乃至 5のいずれかにおいて、

前記クロック周波数変更制御部は、

外部ホストから受け取った、前記液晶表示装置に静止画を表示させる静止画モードであるか否かを示す信号に基づいて、前記画像表示クロックの周波数を変更するか否かを判断することを特徴とする液晶表示制御装置。

**【請求項 7】**

請求項 1乃至 6のいずれかにおいて、

前記クロック周波数変更制御部は、

外部ホストから受け取った、前記液晶表示装置の消費電力を下げる省電力モードであるか否かを示す信号に基づいて、前記画像表示クロックの周波数を変更するか否かを判断することを特徴とする液晶表示制御装置。

**【請求項 8】**

請求項 1乃至 7のいずれかにおいて、

前記クロック周波数変更制御部は、

10

20

30

40

50

光センサが検出した受光量を所定の基準値と比較し、比較結果に基づいて前記画像表示用クロックの周波数を変更するか否かを判断することを特徴とする液晶表示制御装置。

【請求項 9】

請求項 1 乃至 8 のいずれかにおいて、

前記液晶表示装置は低温ポリシリコン TFT で形成されたアクティブマトリックス型の液晶パネルを含むことを特徴とする液晶表示制御装置。

【請求項 10】

請求項 1 乃至 9 のいずれかに記載された液晶表示制御装置と、

前記液晶表示制御装置が生成する画像表示用クロックに基づいて画像表示を行う液晶表示装置と、を含むことを特徴とする電子機器。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶表示制御装置及び電子機器に関する。

【背景技術】

【0002】

携帯電話機、デジタルカメラ、モバイル PC 等、様々な電子機器において液晶表示装置 (LCD) が使用されている。一般に、液晶表示装置は、液晶表示制御装置 (LCD コントローラ) が生成する画像表示用クロック (PCLK) によって画像表示タイミングが制御される。解像度の高い画像ほど 1 フレーム中の画素数が多くなり、フレームレートを維持してフリッカを防止するためには画像表示用クロックの周波数を高くする必要がある。すなわち、表示画像の解像度に応じて画像表示用クロックの周波数を変更する必要があるが、表示画像の解像度が固定であれば一般的には画像表示用クロックの周波数は変更されない。一方、液晶表示装置を使用する携帯機器においては消費電力を低減することが要求される。そこで、例えば、特開平 7 - 239463 号公報には、アクティブマトリックス型表示装置において、フレーム間で変化の無い部分のある画像の表示において、画素への画像の書き込みの度数を減らすことにより、消費電力を低減する技術が提案されている。

20

【特許文献 1】特開平 7 - 239463 号公報

【発明の開示】

【発明が解決しようとする課題】

30

【0003】

しかし、特開平 7 - 239463 号公報に記載された表示装置では、1 フレーム前のデータと現在のフレームのデータを比較する比較回路が必要になり、一般的な液晶表示装置に比べて面積コストが増加する。また、特開平 7 - 239463 号公報に記載された表示装置では、比較回路が画像表示用クロックで動作するため消費電力がかなり増加することが予想され、動画を表示させる場合には一般的な液晶表示装置よりもむしろ消費電力が増加する可能性がある。

【0004】

本発明は、以上のような問題点に鑑みてなされたものであり、画像表示用クロックの周波数を変更することにより、液晶表示装置を適切な消費電力で動作させることができる液晶表示制御装置及び電子機器を提供することを目的とする。

40

【課題を解決するための手段】

【0005】

(1) 本発明は、

液晶表示装置の画像表示を制御する液晶表示制御装置であって、

前記液晶表示装置の画像表示用クロックを生成する画像表示用クロック生成部と、

外部ホストから受け取った所定の信号又は内部レジスタの設定値に基づいて、前記画像表示用クロックの周波数を変更するか否かを判断し、前記液晶表示装置が画像表示を行わない期間に前記画像表示用クロックの周波数を変更するように制御するクロック周波数変更制御部と、を含むことを特徴とする。

50

## 【0006】

液晶表示装置が画像表示を行わない期間は、例えば、液晶表示制御装置が、液晶表示装置による画像表示が行われない領域（画像非表示領域）のデータを出力する期間であってもよいし、液晶表示制御装置が、液晶表示装置による画像表示が行われる画像表示領域（画像表示領域）のデータを出力しない期間であってもよい。

## 【0007】

クロック周波数変更制御部は、画像表示用クロックの周波数が低くなるように変更してもよいし、高くなるように変更してもよい。例えば、液晶表示装置が動画を表示中に静止画表示に切り替える場合には、クロック周波数変更制御部は画像表示用クロックの周波数が低くなるように変更してもよい。また、例えば、液晶表示装置が静止画を表示中に動画表示に切り替える場合には、クロック周波数変更制御部は画像表示用クロックの周波数が高くなるように変更してもよい。

10

## 【0008】

本発明によれば、液晶表示装置が画像表示を行わない期間に画像表示用クロックの周波数が変更されるので、液晶表示装置の画像表示を中断させることなく画像表示用クロックの周波数を適切な周波数に変更することができる。従って、本発明によれば、液晶表示装置を適切な消費電力で動作させることができる。

## 【0009】

（2）本発明の液晶表示制御装置において、

前記クロック周波数変更制御部は、

20

前記液晶表示装置がフレームの最後の画素を表示してから次のフレームの最初の画素を表示するまでの期間に前記画像表示クロックの周波数を変更するように制御するようにしてもよい。

## 【0010】

本発明によれば、液晶表示装置が1フレーム分の画像を表示した後、次の1フレーム分の画像を表示する前に画像表示用クロックの周波数が変更されるので、液晶表示装置の表示途中の画像に乱れを生ずることなく画像表示用クロックの周波数を適切な周波数に変更することができる。

## 【0011】

（3）本発明の液晶表示制御装置において、

30

前記画像表示用クロック生成部は、

所定の基準クロックを分周して前記画像表示用クロックを生成するクロック分周回路を含み、

前記クロック周波数変更制御部は、

前記クロック分周回路の分周比を変更することにより前記画像表示用クロックの周波数を変更するように制御するようにしてもよい。

## 【0012】

所定の基準クロックは、例えば、VCO回路が output する発振クロックやPLL回路が output するクロックであってもよい。

## 【0013】

本発明によれば、基準クロックが安定するのに時間がかかるような場合であっても、基準クロックの周波数を変更することなく分周比を変更するだけで画像表示用クロックの周波数を容易に変更することができる。

40

## 【0014】

（4）本発明の液晶表示制御装置において、

前記クロック周波数変更制御部は、

目標の周波数に達するまで前記画像表示用クロックの周波数を段階的に変更するように制御するようにしてもよい。

## 【0015】

クロック周波数変更制御部は、画像表示用クロックの周波数が段階的に低くなるように

50

変更してもよいし、段階的に高くなるように変更してもよい。

【0016】

本発明によれば、画像表示用クロックの周波数が段階的に変更されるので、液晶表示装置の表示画像の画質を急激に変化させずにフレームレートを変更することができる。

【0017】

(5) 本発明の液晶表示制御装置は、

前記画像表示用クロックの周波数を段階的に変更するタイミングを設定するためのクロック周波数変更タイミング設定レジスタを含み、

前記クロック周波数変更制御部は、

前記クロック周波数変更タイミング設定レジスタの設定値に基づいて、前記画像表示用クロックの周波数を段階的に変更するように制御するようにしてもよい。 10

【0018】

画像表示用クロックの周波数を段階的に変更するタイミングは、それぞれ1フレーム期間の整数倍になるように設定するようにしてもよい。

【0019】

本発明によれば、画像表示用クロックの周波数を段階的に変更する場合に各段階の周波数に至るまでの時間を可変に設定することができるので、各段階の周波数を考慮して液晶表示装置の表示画像の画質の変化がより目立たないように調整することができる。

【0020】

(6) 本発明の液晶表示制御装置において、

前記クロック周波数変更制御部は、

外部ホストから受け取った、前記液晶表示装置に静止画を表示させる静止画モードであるか否かを示す信号に基づいて、前記画像表示クロックの周波数を変更するか否かを判断するようにしてもよい。 20

【0021】

クロック周波数変更制御部は、液晶表示装置が静止画モードになった場合には画像表示用クロックの周波数が低くなるように変更し、液晶表示装置が静止画モードでなくなった場合には画像表示用クロックの周波数が高くなるように変更するようにしてもよい。

【0022】

本発明によれば、液晶表示装置の静止画モードと連動させて画像表示用クロックの周波数を適切な周波数に自動的に変更することができる。 30

【0023】

(7) 本発明の液晶表示制御装置において、

前記クロック周波数変更制御部は、

外部ホストから受け取った、前記液晶表示装置の消費電力を下げる省電力モードであるか否かを示す信号に基づいて、前記画像表示クロックの周波数を変更するか否かを判断するようにしてもよい。

【0024】

クロック周波数変更制御部は、液晶表示装置が省電力モードになった場合には画像表示用クロックの周波数が低くなるように変更し、液晶表示装置が省電力モードでなくなった場合には画像表示用クロックの周波数が高くなるように変更するようにしてもよい。 40

【0025】

本発明によれば、液晶表示装置の省電力モードと連動させて画像表示用クロックの周波数を適切な周波数に自動的に変更することができる。

【0026】

(8) 本発明の液晶表示制御装置において、

前記クロック周波数変更制御部は、

光センサが検出した受光量を所定の基準値と比較し、比較結果に基づいて前記画像表示用クロックの周波数を変更するか否かを判断するようにしてもよい。

【0027】

10

20

30

40

50

クロック周波数変更処理部は、光センサが検出した受光量が所定の基準値よりも小さいと判断した場合は、画像表示用クロックの周波数を低くするようにしてもよい。また、クロック周波数変更処理部は、光センサが検出した受光量が所定の基準値よりも大きいと判断した場合は、画像表示用クロックの周波数を高くするようにしてもよい。さらに、クロック周波数変更処理部は、光センサが検出した受光量が所定の基準値と一致すると判断した場合は、画像表示用クロックの周波数を変更しないようにしてもよい。

【0028】

本発明によれば、光センサが検出した受光量と連動させて画像表示用クロックの周波数を適切な周波数に自動的に変更することができる。

【0029】

(9) 本発明の液晶表示制御装置において、

前記液晶表示装置は低温ポリシリコンTFTで形成されたアクティブマトリックス型の液晶パネルを含むようにしてもよい。

【0030】

低温ポリシリコンTFTで制御される液晶容量のリーコはアモルファスTFTで制御される液晶容量のリーコよりも小さいので、低温ポリシリコンTFTで形成された液晶パネルを含む液晶表示装置は、フレームレートが比較的小さくなても各画素の色彩や明度を保持することができる。従って、本発明によれば画像表示用クロックの周波数を低くすることができるので、液晶表示装置の消費電力をより低減することができる。

【0031】

(10) 本発明は、

上記のいずれかに記載された液晶表示制御装置と、

前記液晶表示制御装置が生成する画像表示用クロックに基づいて画像表示を行う液晶表示装置と、を含むことを特徴とする電子機器である。

【発明を実施するための最良の形態】

【0032】

以下、本発明の好適な実施形態について図面を用いて詳細に説明する。なお、以下に説明する実施の形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではない。また以下で説明される構成の全てが本発明の必須構成要件であるとは限らない。

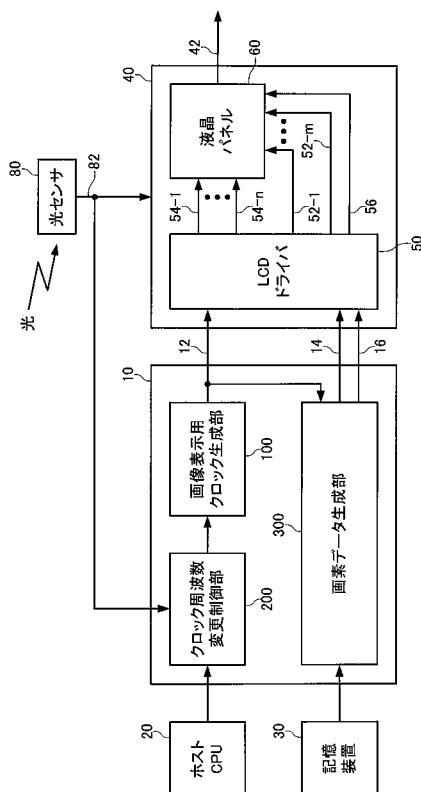

【0033】

1. 液晶表示制御装置

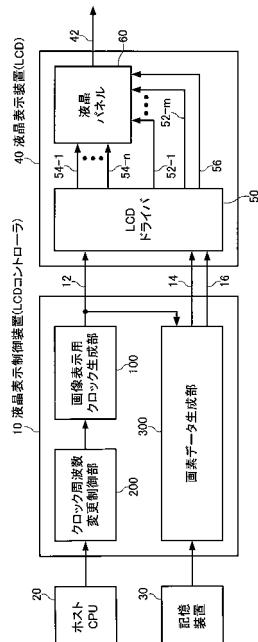

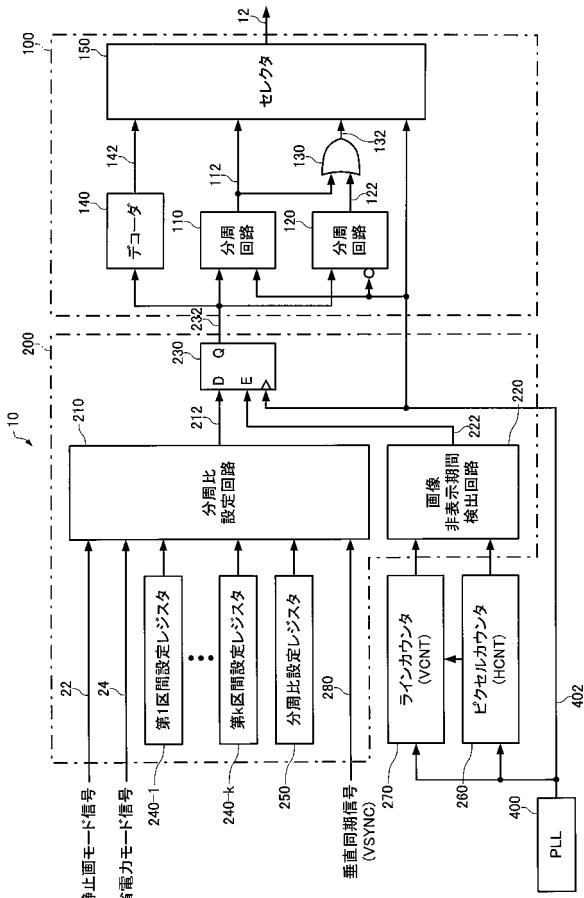

図1は、本実施形態の液晶表示制御装置の機能プロック図の一例である。

【0034】

液晶表示制御装置(LCDコントローラ)10は、液晶表示装置(LCD)40による画像表示のタイミングを制御する機能を果たす。

【0035】

液晶表示装置40は、液晶パネル60を含んで構成されている。また、液晶表示装置40は、液晶パネル60を駆動するLCDドライバ50を含んでいてもよい。液晶パネル60は、m列×n行のマトリックス状に配置された複数の素子で構成される。液晶パネル60は、単純マトリックス方式の液晶パネル(例えば、STN(Super Twisted Nematic Liquid Crystal)により構成された液晶パネル)であってもよいし、アクティブマトリックス型の液晶パネル(例えば、TFT(Thin Film Transistor liquid crystal)により構成された液晶パネル)であってもよい。

【0036】

液晶表示装置40は、液晶パネル60に光を透過させて画像42を表示する。液晶表示装置40は、内部の光源(バックライト)が発する光を液晶パネル60に透過させることにより画像42を表示する透過型の液晶表示装置であってもよいし、外部から取り込んだ光の反射光を液晶パネル60に透過させることにより画像42を表示する反射型の液晶装置であってもよい。

【0037】

10

20

30

40

50

液晶表示制御装置 10 は、画像表示用クロック生成部 100 及びクロック周波数変更制御部 200 を含んで構成されている。また、液晶表示制御装置 10 は、画像データ生成部 300 を含んでいてもよい。

【0038】

画像表示用クロック生成部 100 は、液晶表示装置 40 が画像 42 を構成する各画素を表示するタイミングを制御する画像表示用クロック (PCLK) 12 を生成する処理を行う。

【0039】

クロック周波数変更制御部 200 は、ホスト CPU 20 (外部ホストの一例) から受け取った制御信号 (所定の信号の一例) 又は内部レジスタ (図示しない) の設定値に基づいて、画像表示用クロック 12 の周波数を変更するか否かを判断し、液晶表示装置 40 が画像表示を行わない期間に画像表示用クロック 12 の周波数を変更するように制御する処理を行う。

10

【0040】

画像データ生成部 300 は、画像表示用クロック 12 に同期して、例えば、記憶装置 30 に格納された画素データに基づいて画像 42 を構成する各画素の画素データ 14 及び画素データ 14 が有効である期間を示すデータタイネーブル信号 16 を生成し、液晶表示装置 40 (LCD ドライバ 50) に供給する処理を行う。LCD ドライバ 50 は、画像表示用クロック 12、画素データ 14 及びデータタイネーブル信号 16 に基づいて、液晶パネル 60 の  $m$  列  $\times$   $n$  行のマトリックス状に配置された各素子に接続されたデータ線駆 52-1 ~ 52-m、操作線 54-1 ~ 54-m、VCOM 信号線 16 の駆動電圧を生成する処理を行う。

20

【0041】

なお、画像データ生成部 300 は、液晶表示制御装置 10 の必須の構成要素ではなく、液晶表示制御装置 10 の外部に存在していてもよい。また、液晶表示制御装置 10 は、1 つの I<sub>C</sub> チップで実現されていてもよいし、複数の I<sub>C</sub> チップを含んで構成されていてもよい。

20

【0042】

本実施形態の液晶表示制御装置によれば、液晶表示装置 40 が画像表示を行わない期間に画像表示用クロック 12 の周波数が変更されるので、液晶表示装置 40 の画像表示を中断させることなく画像表示用クロック 12 の周波数を適切な周波数に変更することができる。従って、本実施形態の液晶表示制御装置によれば、液晶表示装置 40 を適切な消費電力で動作させることができる。

30

【0043】

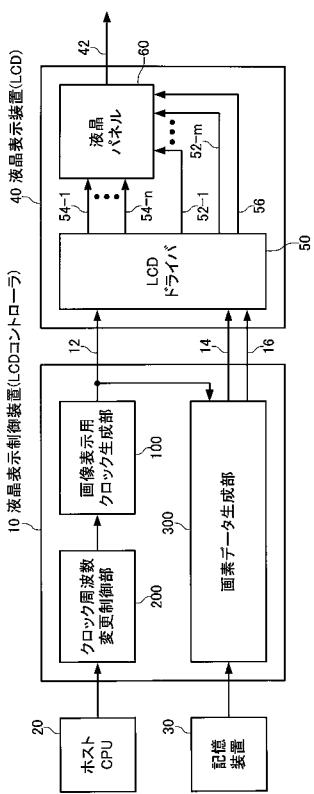

図 2 は、液晶表示装置に含まれる液晶パネルの構成例について説明するための図である。以下、図 1 を参照しながら図 2 について説明する。

【0044】

液晶パネル 60 は、例えば、1 フレーム分の画像 42 を構成する  $m \times n$  個の各画素に対応してマトリックス状に配置された  $m \times n$  個のスイッチ回路 62 を含んで構成されたアクティブラミットアクトリックス型の液晶パネルである。スイッチ回路 62 は、例えば、トランジスタ 64、液晶容量 66 及び保持容量 68 により構成されている。同一行に配置されたトランジスタ 64 のゲートは走査線 54-1 ~ 54-n のいずれかに共通接続されている。また、同一列に配置されたトランジスタ 64 のソースはデータ線走査線 52-1 ~ 52-m のいずれかに共通接続されている。さらに、各トランジスタ 64 のドレインは各液晶容量 66 の一端 (画素電極) に接続されている。液晶容量 66 の他端 (共通電極) は VCOM 信号線 56 に共通接続されている。

40

【0045】

各トランジスタ 64 が 1 フレームに 1 回の割合で周期的にオンし、各トランジスタ 64 がオンしている間、各液晶容量 66 の両端にはデータ線 52-1 ~ 52-m に印加された電圧と VCOM 信号線 56 に印加された電圧 (VCOM 電圧) の差の電圧が印加され、各

50

液晶容量 6 6 には各画素値に応じた電荷が蓄えられる。各トランジスタ 6 4 がオフしても各液晶容量 6 6 には電荷が蓄えられたままであるが、リーク電流のために電荷が徐々に減少していく。フレームレートがより小さいほど各液晶容量 6 6 に蓄えられた電荷がより減少するため画素の色彩や明度が劣化してしまう。そこで、各スイッチング回路 6 2 において、各液晶容量 6 6 と並列に保持容量 6 8 が付加されていてもよい。

【0046】

トランジスタ 6 4 は、アモルファスシリコン TFT であってもよいが、低温ポリシリコン TFT であることが望ましい。トランジスタ 6 4 が低温ポリシリコン TFT である場合は、液晶容量 6 6 のリークがより小さいのでフレームレートが比較的小さくなっても各画素の色彩や明度を保持することができる。従って、画像表示用クロック 1 2 の周波数を低くすることができるので、液晶表示装置 4 0 の消費電力をより低減することができる。また、画像表示用クロック 1 2 で動作する画像データ生成部 3 0 0 を含む液晶表示制御装置 1 0 の消費電力も低減することができる。

10

【0047】

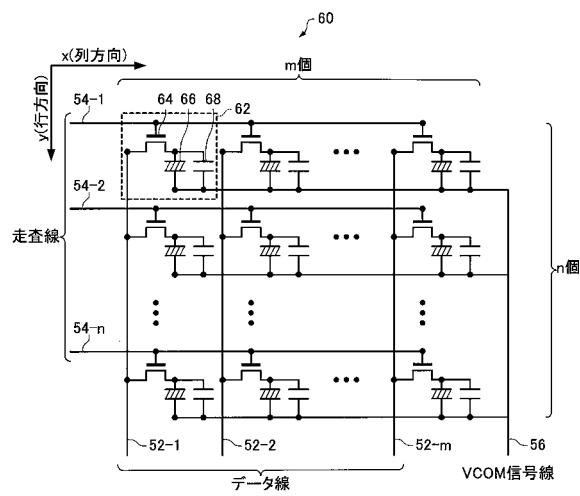

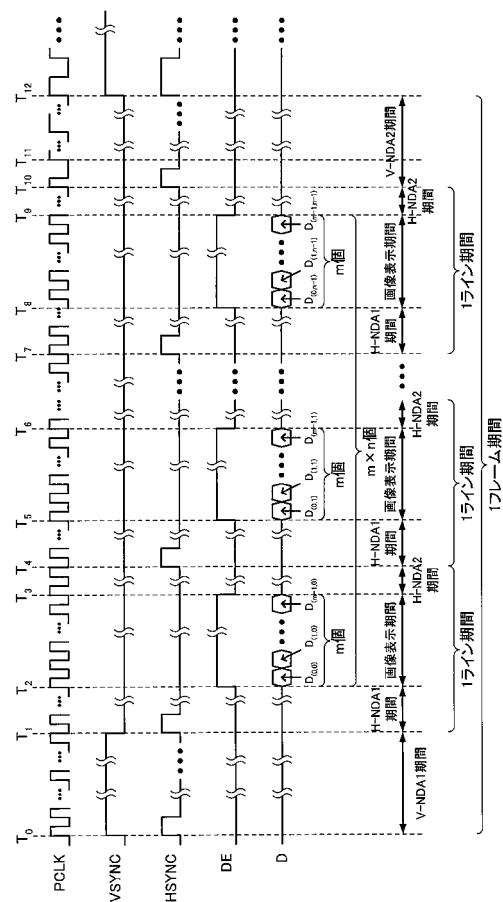

図 3 は、本実施形態の液晶表示制御装置が生成する画像表示用クロック及び画素データと液晶表示装置の表示画像の関係について説明するための図である。以下、図 1、図 2 を参照しながら図 3 について説明する。

【0048】

液晶表示制御装置 1 0 (具体的には、画像表示用クロック生成部 1 0 0) は、液晶表示装置 4 0 に  $m \times n$  個の画素により構成される 1 フレーム分の画像 4 2 を表示させるために  $M \times N$  周期分の画像表示用クロック 1 2 を生成する。

20

【0049】

液晶表示装置 4 0 は、1 フレーム分の画像 4 2 を画像表示領域 7 0 に表示する。そのため、液晶表示制御装置 1 0 は、画像表示領域 7 0 に対応する期間のみ液晶表示装置 4 0 に  $m \times n$  個の画素データ 1 4 及びデータイネーブル信号 1 6 を送信する。逆に、液晶表示制御装置 1 0 は、垂直方向画像非表示領域 7 2 - 1 (V - V N D A 1 (Vertical Non Display Area 1))、垂直方向画像非表示領域 7 2 - 2 (V - V N D A 2)、水平方向画像非表示領域 7 4 - 1 (H - V N D A 1 (Horizontal Non Display Area 1))、水平方向画像非表示領域 7 4 - 2 (H - V N D A 2) に対応する期間は液晶表示装置 4 0 に画素データ 1 4 及びデータイネーブル信号 1 6 を送信しない。

30

【0050】

また、液晶表示制御装置 1 0 は、垂直方向画像非表示領域 7 2 - 1 に対応する期間において液晶表示装置 4 0 に V S Y N C (垂直同期信号) を送信する。

【0051】

さらに、液晶表示制御装置 1 0 は、水平方向画像非表示領域 7 4 - 1 に対応する期間において液晶表示装置 4 0 に H S Y N C (水平同期信号) を送信する。

【0052】

なお、液晶表示制御装置 1 0 は、垂直方向画像非表示領域 7 2 - 1、垂直方向画像非表示領域 7 2 - 2、水平方向画像非表示領域 7 4 - 1、水平方向画像非表示領域 7 4 - 2 の各サイズを設定可能な構成であってもよい。

40

【0053】

図 4 は、本実施形態の液晶表示制御装置が、画像表示用クロックの周波数を変更するタイミングの一例について説明するためのタイミングチャート図である。以下、図 1 ~ 図 3 を参照しながら、図 4 について説明する。

【0054】

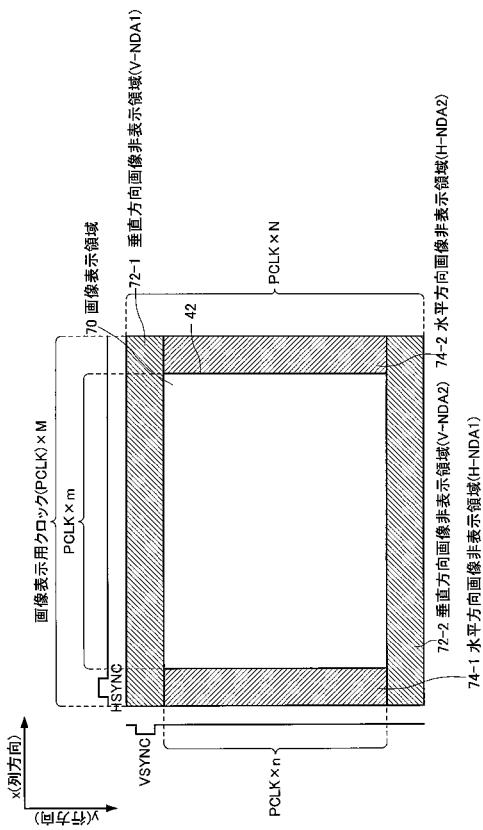

時刻  $T_0 \sim T_1$  は、垂直方向画像非表示領域 7 2 - 1 に対応する期間であり、液晶表示制御装置 1 0 は液晶表示装置 4 0 に垂直同期信号 (V S Y N C) 及び各ライン毎の水平同期信号 (H S Y N C) を送信する。時刻  $T_0 \sim T_1$  において、データイネーブル信号 1 6 (D E) 及び画素データ 1 4 (D) は液晶表示装置 4 0 に送信されない。

【0055】

50

時刻  $T_1 \sim T_2$  は、水平方向画像非表示領域 74-1 の 1 ライン目に対応する期間であり、液晶表示制御装置 10 は液晶表示装置 40 に 1 ライン目の水平同期信号 (H Sync) を送信する。時刻  $T_1 \sim T_2$  において、データタイネーブル信号 16 (DE) 及び画素データ 14 (D) は液晶表示装置 40 に送信されない。

## 【0056】

時刻  $T_2 \sim T_3$  は、液晶表示制御装置 10 が液晶表示装置 40 に画像表示領域 70 の 1 ライン目の  $m$  個の画素データ 14 (D<sub>(0,0)</sub>、D<sub>(1,0)</sub>、…、D<sub>(m-1,0)</sub>) 及びデータタイネーブル信号 16 (DE) を送信する期間である。

## 【0057】

時刻  $T_3 \sim T_4$  は、水平方向画像非表示領域 74-2 の 1 ライン目に対応する期間である。時刻  $T_3 \sim T_4$  において、データタイネーブル信号 16 (DE) 及び画素データ 14 (D) は液晶表示装置 40 に送信されない。

## 【0058】

すなわち、時刻  $T_1 \sim T_4$  において、1 ライン目の水平同期信号 (H Sync)、データタイネーブル信号 16 (DE)、画素データ 14 (D<sub>(0,0)</sub>、D<sub>(1,0)</sub>、…、D<sub>(m-1,0)</sub>) が液晶表示装置 40 に送信され、液晶表示装置 40 は液晶パネル 60 を通して画像表示領域 70 に 1 ライン目の画像を表示する。

## 【0059】

時刻  $T_4 \sim T_5$  は、水平方向画像非表示領域 74-1 (H-HVDA1) の 2 ライン目に対応する期間であり、液晶表示制御装置 10 は液晶表示装置 40 に 2 ライン目の水平同期信号 (H Sync) を送信する。時刻  $T_4 \sim T_5$  において、データタイネーブル信号 16 (DE) 及び画素データ 14 (D) は液晶表示装置 40 に送信されない。

## 【0060】

時刻  $T_5 \sim T_6$  は、液晶表示制御装置 10 が液晶表示装置 40 に画像表示領域 70 の 2 ライン目の  $m$  個の画素データ 14 (D<sub>(0,1)</sub>、D<sub>(1,1)</sub>、…、D<sub>(m-1,1)</sub>) 及びデータタイネーブル信号 16 (DE) を送信する期間である。

## 【0061】

時刻  $T_6 \sim T_7$  は、水平方向画像非表示領域 74-2 の 2 ライン目に対応する期間である。時刻  $T_6 \sim T_7$  において、データタイネーブル信号 16 (DE) 及び画素データ 14 (D) は液晶表示装置 40 に送信されない。

## 【0062】

すなわち、時刻  $T_4 \sim T_7$  において、2 ライン目の水平同期信号 (H Sync)、データタイネーブル信号 16 (DE)、画素データ 14 (D<sub>(0,1)</sub>、D<sub>(1,1)</sub>、…、D<sub>(m-1,1)</sub>) が液晶表示装置 40 に送信され、液晶表示装置 40 は液晶パネル 60 を通して画像表示領域 70 に 2 ライン目の画像を表示する。

## 【0063】

以下、同様の処理が繰り返され、時刻  $T_7 \sim T_{10}$  において、 $n$  ライン目の水平同期信号 (H Sync)、データタイネーブル信号 16 (DE)、画素データ 14 (D<sub>(0,n-1)</sub>、D<sub>(1,n-1)</sub>、…、D<sub>(m-1,n-1)</sub>) が液晶表示装置 40 に送信され、液晶表示装置 40 は液晶パネル 60 を通して画像表示領域 70 に  $m$  ライン目の画像を表示する。

## 【0064】

時刻  $T_{10} \sim T_{12}$  は、垂直方向画像非表示領域 72-2 に対応する期間である。時刻  $T_{10} \sim T_{12}$  において、データタイネーブル信号 16 (DE) 及び画素データ 14 (D) は液晶表示装置 40 に送信されない。

## 【0065】

以上説明したように、液晶表示制御装置 10 は、時刻  $T_0 \sim T_{12}$  において 1 フレーム分の画像を構成する  $m \times n$  個の画素データを液晶表示装置 40 に送信する。すなわち、 $1 / (T_{12} - T_0)$  により計算される単位時間当たりのフレーム数がフレームレートに相当する。例えば、液晶表示装置 40 が動画を表示する場合には、液晶表示制御装置 10 は

10

20

30

40

50

約 60 f p s (frame per second) のフレームレートとなるように画素データ 14 を液晶表示装置 40 に送信する。すなわち、液晶表示制御装置 10 (具体的には、画像表示用クロック生成部 100) は約 60 f p s のフレームレートを達成することができる周波数の画像表示用クロック 12 を生成する。

【0066】

一方、液晶表示装置 40 が静止画を表示する場合には、フレーム間の画像の変化がないため、液晶表示制御装置 10 は比較的小さいフレームレートで画像表示を行ってもよい。また、液晶表示装置 40 が省電力モードに設定され暗い画像を表示する場合には、液晶表示制御装置 10 は比較的小さいフレームレートで画像表示を行ってもよい。すなわち、このような場合には、液晶表示制御装置 10 (具体的には、クロック周波数変更制御部 200) は画像表示用クロック 12 の周波数をより低い周波数に変更することができる。従って、液晶表示装置 40 の消費電力をより低減することができる。

10

【0067】

ここで、液晶表示制御装置 10 (具体的には、クロック周波数変更制御部 200) は、ホスト C P U 20 から受け取った制御信号又は内部レジスタの設定値に基づいて、液晶表示装置 40 が画像表示を行わない期間 (垂直方向画像非表示領域 72-1、垂直方向画像非表示領域 72-2、水平方向画像非表示領域 74-1、水平方向画像非表示領域 74-2 のいずれかに対応する期間) に画像表示用クロック 12 の周波数を変更する。

20

【0068】

なお、画像表示用クロック 12 の周波数が 1 フレームの途中で変更されると、液晶表示装置 40 によって表示される画像に乱れが発生する等の問題が起こりうるので、液晶表示制御装置 10 (具体的には、クロック周波数変更制御部 200) は、垂直方向画像非表示領域 72-1 又は垂直方向画像非表示領域 72-2 のいずれかに対応する期間に画像表示用クロック 12 の周波数を変更するのが好ましい。

20

【0069】

そこで、例えば、液晶表示制御装置 10 (具体的には、クロック周波数変更制御部 200) が、垂直方向画像非表示領域 72-1 又は垂直方向画像非表示領域 72-2 のいずれかに対応する期間以外の期間にホスト C P U 20 からの制御信号や内部レジスタの設定命令を受け取った場合には、垂直方向画像非表示領域 72-1 又は垂直方向画像非表示領域 72-2 のいずれかに対応する期間になるまで画像表示用クロック 12 の周波数の変更処理を行わないようにしてよい。図 4 において、例えば、液晶表示制御装置 10 (具体的には、クロック周波数変更制御部 200) が時刻  $T_1 \sim T_{10}$  の期間においてホスト C P U 20 からの制御信号や内部レジスタの設定命令を受け取った場合には、液晶表示制御装置 10 (具体的には、クロック周波数変更制御部 200) は、時刻  $T_{10} \sim T_{12}$  の期間 (垂直方向画像非表示領域 72-2 に対応する期間) の時刻  $T_{11}$  において画像表示用クロック 12 の周波数を変更するようにしてよい。こうすることにより、液晶表示装置 40 が 1 フレーム分の画像 42 を表示した後、次の 1 フレーム分の画像 42 を表示する前に画像表示用クロック 12 の周波数が変更されるので、液晶表示装置 40 の表示途中の画像に乱れを生ずることなく画像表示用クロック 12 の周波数を適切な周波数に変更することができる。

30

【0070】

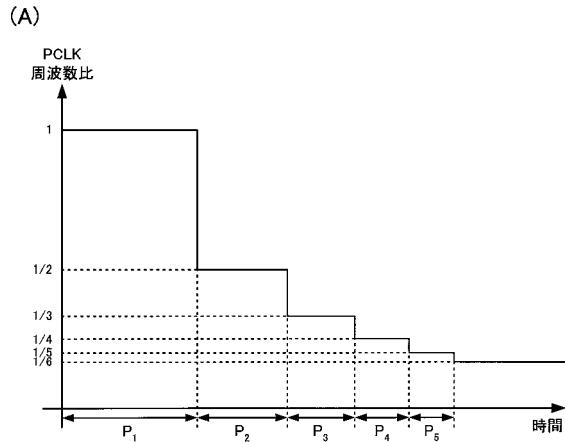

図 5 (A)、図 5 (B) は、本実施形態の液晶表示制御装置が、画像表示用クロックの周波数を段階的に変更する例について説明するための図である。以下、図 1 ~ 図 4 を参照しながら、図 5 (A)、図 5 (B) について説明する。

40

【0071】

図 5 (A)、図 5 (B) において、縦軸は所定の基準周波数に対する画像表示用クロック 12 の周波数を示し、横軸は時間を示す。

【0072】

図 5 (A) は、液晶表示制御装置 10 (具体的には、画像表示用クロック生成部 100) が基準周波数の画像表示用クロック 12 を生成している場合において、ホスト C P U 2

50

0 が液晶表示制御装置 10 (具体的には、クロック周波数変更制御部 200) に対して、画像表示用クロック 12 の周波数を基準周波数の 1/6 倍に変更するように指示した場合を示している。例えば、静止画モードや省電力モードが設定されたケースが想定される。

【0073】

図 5 (A) に示すように、液晶表示制御装置 10 (具体的には、クロック周波数変更制御部 200) は、例えば、画像表示用クロック 12 の周波数が基準周波数の 1/2 倍、1/3 倍、1/4 倍、1/5 倍、1/6 倍のように段階的に低くなるように制御するようにしてもよい。ここで、画像表示用クロック 12 の周波数が基準周波数の 1 倍、1/2 倍、1/3 倍、1/4 倍、1/5 倍である各区間  $P_1$ 、 $P_2$ 、 $P_3$ 、 $P_4$ 、 $P_5$  の長さは可変に設定できるようにしてもよい。例えば、 $P_1$  ~  $P_5$  の区間の長さが 1 フレーム期間の整数倍になるように設定するようにしてもよい。

10

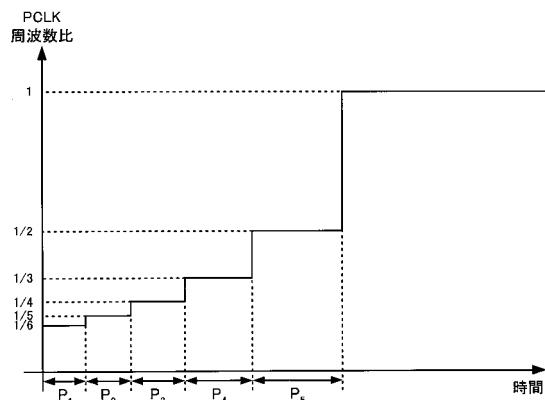

【0074】

図 5 (B) は、液晶表示制御装置 10 (具体的には、画像表示用クロック生成部 100) が基準周波数の 1/6 倍の画像表示用クロック 12 を生成している場合において、ホスト CPU 20 が液晶表示制御装置 10 (具体的には、クロック周波数変更制御部 200) に対して、画像表示用クロック 12 の周波数を基準周波数に変更するように指示した場合を示している。例えば、静止画モードや省電力モードが解除されたケースが想定される。

【0075】

図 5 (B) に示すように、液晶表示制御装置 10 (具体的には、クロック周波数変更制御部 200) は、例えば、画像表示用クロック 12 の周波数が基準周波数の 1/5 倍、1/4 倍、1/3 倍、1/2 倍、1 倍のように段階的に高くなるように制御するようにしてもよい。ここで、画像表示用クロック 12 の周波数が基準周波数の 1/6 倍、1/5 倍、1/4 倍、1/3 倍、1/2 倍である各区間  $P_1$ 、 $P_2$ 、 $P_3$ 、 $P_4$ 、 $P_5$  の長さは可変に設定できるようにしてもよい。例えば、 $P_1$  ~  $P_5$  の区間の長さが 1 フレーム期間の整数倍になるように設定するようにしてもよい。

20

【0076】

このように、画像表示用クロック 12 の周波数を段階的に変更することにより、液晶表示装置 40 の表示画像 42 の画質を急激に変化させずにフレームレートを変更することができる。

【0077】

また、各段階の周波数に至るまでの時間を可変にすることにより、各段階の周波数を考慮して液晶表示装置 40 の表示画像 42 の画質の変化がより目立たないように調整することができる。

30

【0078】

図 6 は、図 1 ~ 図 5 (A)、図 5 (B) で説明した処理を実現するための画像表示用クロック生成部及びクロック周波数変更制御部の構成例について説明するための図である。以下、図 1 ~ 図 5 (A)、図 5 (B) を参照しながら、図 6 について説明する。

【0079】

画像表示用クロック生成部 100 は、分周回路 110、分周回路 120、2 入力 OR 素子 130、デコーダ 140、セレクタ 150 等を含んで構成されており、PLL 400 が 40 出力する PLL クロック 402 を分周して画像表示用クロック 12 を生成する。

【0080】

分周回路 110 は、分周比設定データ 232 に従い、PLL クロック 402 の立ち上がりエッジに同期して、PLL クロック 402 の周波数 (基準周波数) の 1/2 倍、1/3 倍、1/4 倍、1/5 倍・・・のいずれかの周波数の分周クロック 112 を生成する。

【0081】

分周回路 120 は、分周比設定データ 232 に従い、PLL クロック 402 の立ち下がりエッジに同期して、基準周波数の 1/2 倍、1/3 倍、1/4 倍、・・・のいずれかの周波数の分周クロック 122 を生成する。

【0082】

50

ここで、分周クロック 112 及び分周クロック 122 の周波数が基準周波数の 1 / 2 倍、1 / 4 倍、・・・の時は、分周クロック 112 及び分周クロック 122 のデューティー比はほぼ 50 % になる。しかし、分周クロック 112 及び分周クロック 122 の周波数が基準周波数の 1 / 3 倍、1 / 5 倍、・・・の時は、分周クロック 112 のデューティー比が 50 % にならない。

#### 【0083】

そこで、分周クロック 112 及び分周クロック 122 は 2 入力 OR 素子 130 に入力されて分周クロック 132 が生成される。分周クロック 112 及び分周クロック 122 の周波数が基準周波数の 1 / 3 倍、1 / 5 倍、・・・の時、分周クロック 132 のデューティー比はほぼ 50 % になる。

10

#### 【0084】

デコーダ 140 は、分周比設定データ 232 をデコードしてクロック選択信号 142 を生成する。

#### 【0085】

セレクタ 150 は、選択信号 142 に従い、分周クロック 112、分周クロック 122 又は PLL クロック 402 のいずれかを選択して画像表示用クロック 12 を生成する。すなわち、セレクタ 150 は、基準周波数の 1 / 2 倍、1 / 4 倍、・・・の周波数の画像表示用クロック 12 を生成する時は分周クロック 112 を選択し、基準周波数の 1 / 3 倍、1 / 5 倍、・・・の周波数の画像表示用クロック 12 を生成する時は分周クロック 122 を選択する。また、セレクタ 150 は、基準周波数と同じ周波数の画像表示用クロック 12 を生成する時は PLL クロック 402 を選択する。

20

#### 【0086】

クロック周波数変更制御部 200 は、分周比設定回路 210、画像非表示期間検出回路 220、イネーブル端子付き D フリップフロップ 230、第 1 区間設定レジスタ 240-1 ~ 第 k 区間設定レジスタ 240-k (クロック周波数変更タイミング設定レジスタの一例)、分周比設定レジスタ 250 等を含んで構成されている。

30

#### 【0087】

分周比設定回路 210 は、分周比設定レジスタ 250 の設定値に従って、画像表示用クロック 12 の分周比を決定し、分周比設定データ 212 を生成する。また、分周比設定回路 210 は、ホスト CPU 20 からの静止画モード信号 22 や省電力モード信号 24 等の制御信号に基づいて、静止画モードや省電力モードが設定されたと判断した場合、静止画モードや省電力モードの設定が解除されたと判断した場合等に分周比設定レジスタ 250 の設定値が有効になるようにしてもよい。

#### 【0088】

画像非表示期間検出回路 220 は、ピクセルカウンタ 260 (H C N T) 及びラインカウンタ 270 (V C N T) で示される座標 (画像データ生成部 300 が処理中の座標) が、画像非表示領域に含まれるか否かを検出し、含まれる場合は画像非表示期間検出信号 222 を生成する。画像非表示期間検出回路 220 は、ピクセルカウンタ 260 及びラインカウンタ 270 で示される座標が、例えば、垂直方向画像非表示領域 72-1、垂直方向画像非表示領域 72-2、水平方向画像非表示領域 74-1 又は水平方向画像非表示領域 74-2 のいずれかに含まれるか否かを検出するようにしてもよいし、垂直方向画像非表示領域 72-1 又は垂直方向画像非表示領域 72-2 のいずれかに含まれるか否かを検出するようにしてもよい。なお、ピクセルカウンタ 260 及びラインカウンタ 270 は、例えば、画像データ生成部 300 に含まれており、各画素データ 14 及びデータイネーブル信号 16 を生成するタイミングを制御するために使用される。

40

#### 【0089】

イネーブル端子付き D フリップフロップ 230 は、画像非表示期間検出信号 222 が生成されている間 (画像非表示期間の間)、PLL クロック 402 の立ち上がりエッジで分周比設定データ 212 をラッチして分周比設定データ 232 を生成する。すなわち、画像非表示期間において分周比設定データ 232 が更新される。

50

## 【0090】

第1区間設定レジスタ240-1～第k区間設定レジスタ240-kは、図5(A)及び図5(B)で説明したように画像表示用クロック12の周波数を段階的に変更するため使用されるレジスタである。すなわち、第1区間設定レジスタ240-1～第5区間設定レジスタ240-5(k=5のケース)は、図5(A)及び図5(B)の各区間P<sub>1</sub>～P<sub>5</sub>の長さを設定するためのレジスタである。各区間P<sub>1</sub>～P<sub>5</sub>の長さは1フレーム期間の整数倍になるように設定するようにしてもよい。そして、分周比設定回路210は、例えば、垂直同期信号280(VSYNC)をカウントするカウンタ(図示しない)を含み、各区間P<sub>1</sub>～P<sub>5</sub>が経過する毎に分周比設定データ212を1ずつデクリメント又はインクリメントするようにしてもよい。

10

## 【0091】

本実施形態の液晶表示制御装置によれば、PLLクロック402が安定するのに時間がかかるような場合であっても、PLLクロック402の周波数を変更することなく分周比を変更するだけで画像表示用クロック12の周波数を容易に変更することができる。

## 【0092】

また、本実施形態の液晶表示制御装置によれば、画像表示用クロック12の周波数を段階的に変更する場合に各段階の周波数に至るまでの時間を可変に設定することができるので、各段階の周波数を考慮して液晶表示装置40の表示画像42の画質の変化がより目立たないように調整することができる。

20

## 【0093】

また、本実施形態の液晶表示制御装置によれば、液晶表示装置40の静止画モードや省電力モードと連動させて画像表示用クロック12の周波数を適切な周波数に自動的に変更することができる。

## 【0094】

従って、本実施形態の液晶表示制御装置によれば、液晶表示装置40を適切な消費電力で動作させることができる。

## 【0095】

図7は、本実施形態の液晶表示制御装置の機能ブロック図の他の一例である。図7において図1と同じ構成には同じ番号を付してあり、その説明を省略する。

30

## 【0096】

図7において、液晶表示装置40は、光源となるバックライト(図示しない)を含み、光センサ80が検出する受光量検出データ82に基づいてバックライトの発光量を調節する。すなわち、液晶表示装置40は、受光量検出データ82に基づいて、周囲が暗いと判断するとバックライトの発光量を小さくし、周囲が明るいと判断するとバックライトの発光量を大きくする。

## 【0097】

液晶表示制御装置10のクロック周波数変更処理部200は、受光量検出データ82に基づいて、光センサ80が検出した受光量を所定の基準値と比較し、比較結果に基づいて画像表示用クロック12の周波数を変更するか否かを判断する。

40

## 【0098】

クロック周波数変更処理部200は、光センサ80が検出した受光量が所定の基準値よりも小さいと判断した場合は、画像表示用クロック12の周波数を低くするようにしてもよい。また、クロック周波数変更処理部200は、光センサ80が検出した受光量が所定の基準値よりも大きいと判断した場合は、画像表示用クロック12の周波数を高くするようにしてもよい。さらに、クロック周波数変更処理部200は、光センサ80が検出した受光量が所定の基準値と一致すると判断した場合は、画像表示用クロック12の周波数を変更しないようにしてもよい。

## 【0099】

本実施形態の液晶表示制御装置によれば、光センサ80が検出した受光量と連動させて画像表示用クロック12の周波数を適切な周波数に自動的に変更することができる。従つ

50

て、本実施形態の液晶表示制御装置によれば、液晶表示装置40を適切な消費電力で動作させることができる。

#### 【0100】

##### 2. 電子機器

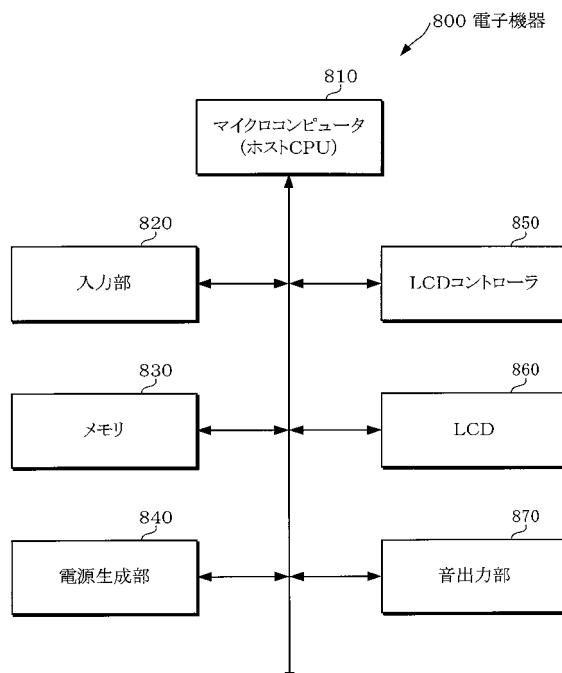

図8に、本実施の形態の電子機器のブロック図の一例を示す。本電子機器800は、マイクロコンピュータ(ホストCPU)810、入力部820、メモリ830、電源生成部840、LCDコントローラ850、LCD860、音出力部870を含む。

#### 【0101】

ここで、入力部820は、種々のデータを入力するためのものである。マイクロコンピュータ810は、この入力部820により入力されたデータに基づいて種々の処理を行うことになる。メモリ830は、マイクロコンピュータ810などの作業領域となるものである。電源生成部840は、電子機器800で使用される各種電源を生成するためのものである。LCD860は、電子機器が表示する各種の画像(文字、アイコン、グラフィック等)を出力するためのものである。LCDコントローラ850は、LCD860を制御して画像を表示させるためのものである。LCDコントローラ850及びLCD860は、例えば、それぞれ図1～図7で説明した液晶表示制御装置10及び液晶表示装置40であってもよい。

10

#### 【0102】

音出力部870は、電子機器800が出力する各種の音(音声、ゲーム音等)を出力するためのものであり、その機能は、スピーカなどのハードウェアにより実現できる。

20

#### 【0103】

図9(A)に、電子機器の1つである携帯電話950の外観図の例を示す。この携帯電話950は、入力部として機能するダイヤルボタン952や、電話番号や名前やアイコンなどを表示するLCD954や、音出力部として機能し音声を出力するスピーカ956を備える。

30

#### 【0104】

図9(B)に、電子機器の1つである携帯型ゲーム装置960の外観図の例を示す。この携帯型ゲーム装置960は、入力部として機能する操作ボタン962、十字キー964や、ゲーム画像を表示するLCD966や、音出力部として機能しゲーム音を出力するスピーカ968を備える。

#### 【0105】

図9(C)に、電子機器の1つであるパーソナルコンピュータ970の外観図の例を示す。このパーソナルコンピュータ970は、入力部として機能するキーボード972や、文字、数字、グラフィックなどを表示するLCD974、音出力部976を備える。

30

#### 【0106】

本実施の形態の液晶表示制御装置及び液晶表示装置を図9(A)～図9(C)の電子機器に組み込むことにより、消費電力を最適化したパフォーマンスの高い電子機器を提供することができる。

#### 【0107】

なお、本実施形態を利用できる電子機器としては、図9(A)～図9(C)に示すもの以外にも、携帯型情報端末、ペーパーライフ、電子卓上計算機、タッチパネルを備えた装置、プロジェクタ、ワードプロセッサ、ビューファインダ型又はモニタ直視型のビデオテープレコーダ、カーナビゲーション装置等の種々の電子機器を考えることができる。

40

#### 【0108】

なお、本発明は本実施形態に限定されず、本発明の要旨の範囲内で種々の変形実施が可能である。

#### 【0109】

本発明は、実施の形態で説明した構成と実質的に同一の構成(例えば、機能、方法及び結果が同一の構成、あるいは目的及び効果が同一の構成)を含む。また、本発明は、実施の形態で説明した構成の本質的でない部分を置き換えた構成を含む。また、本発明は、実

50

施の形態で説明した構成と同一の作用効果を奏する構成又は同一の目的を達成することができる構成を含む。また、本発明は、実施の形態で説明した構成に公知技術を付加した構成を含む。

【図面の簡単な説明】

【0110】

【図1】本実施形態の液晶表示制御装置の機能ブロック図の一例。

【図2】液晶表示装置に含まれる液晶パネルの構成例について説明するための図。

【図3】本実施形態の液晶表示制御装置が生成する画像表示用クロック及び画素データと液晶表示装置の表示画像の関係について説明するための図。

【図4】本実施形態の液晶表示制御装置が、画像表示用クロックの周波数を変更するタイミングの一例について説明するためのタイミングチャート図。 10

【図5】図5(A)、図5(B)は、本実施形態の液晶表示制御装置が、画像表示用クロックの周波数を段階的に変更する例について説明するための図。

【図6】画像表示用クロック生成部及びクロック周波数変更制御部の構成例について説明するための図。

【図7】本実施形態の液晶表示制御装置の機能ブロック図の他の一例。

【図8】液晶表示装置及び液晶表示制御装置を含む電子機器のブロック図の一例。

【図9】図9(A)～図9(C)は、種々の電子機器の外観図の例。

【符号の説明】

【0111】

10 液晶表示制御装置 (LCDコントローラ)、12 画像表示用クロック、14 画素データ、16 データイネーブル信号、20 ホストCPU、22 静止画モード信号、24 省電力モード信号、30 記憶装置、40 液晶表示装置 (LCD)、42 画像、50 LCDドライバ、52-1～52-m データ線、54-1～54-n 走査線、56 VCOM信号線、60 液晶パネル、62 スイッチング回路、64 トランジスタ、66 液晶容量、68 保持容量、70 画像表示領域、72-1～72-2 垂直方向画像非表示領域、74-1～74-2 水平方向画像非表示領域、80 光センサ、82 受光量検出データ、100 画像表示用クロック生成部、110 分周回路、112 分周クロック、122 分周クロック、120 分周回路、130 2入力OR素子、132 分周クロック、140 デコーダ、150 セレクタ、200 クロック周波数変更制御部、210 分周比設定回路、212 分周比設定データ、220 画像非表示期間検出回路、222 画像非表示期間検出信号、230 イネーブル端子付きDフリップフロップ、232 分周比設定データ、240-1～240-k 第1～第k区間設定レジスタ、250 分周比設定レジスタ、260 ピクセルカウンタ、270 ラインカウンタ、280 垂直同期信号、300 画像データ生成部、400 PLL、402 PLLクロック、800 電子機器、810 マイクロコンピュータ (ホストCPU)、820 入力部、830 メモリ、840 電源生成部、850 LCDコントローラ、860 LCD、870 音出力部、950 携帯電話、952 ダイヤルボタン、954 LCD、956 スピーカ、960 携帯型ゲーム装置、962 操作ボタン、964 十字キー、966 LCD、968 スピーカ、970 パーソナルコンピュータ、972 キーボード、974 LCD、976 音出力部 30

20

30

40

【図1】

【図2】

【図3】

【図4】

【 义 5 】

(B)

【 义 7 】

【 図 6 】

【 図 8 】

## 【図9】

## フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 8 0 S |

| G 0 9 G | 3/20  | 6 8 0 T |

| G 0 9 G | 3/20  | 6 8 0 R |

| G 0 9 G | 3/20  | 6 8 0 C |

| G 0 9 G | 3/20  | 6 8 0 Q |

| G 0 9 G | 3/20  | 6 8 0 V |

| G 0 9 G | 3/20  | 6 5 0 J |

| G 0 9 G | 3/20  | 6 6 0 U |

| G 0 2 F | 1/133 | 5 5 0   |

F ターム(参考) 2H093 NA16 NC34 NC42 ND39 NE03

2H193 ZA04 ZP03

5C006 AA02 AC17 AF44 AF53 AF63 AF69 AF72 AF73 AF78 BB16

BC06 BC16 BF02 BF06 BF09 BF15 BF16 BF22 BF23 BF24

BF26 BF39 FA48

5C080 AA10 DD26 FF11 JJ02 JJ03 JJ04 JJ05 JJ06 KK04 KK07

KK23 KK43 KK47 KK50