(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6722698号

(P6722698)

(45) 発行日 令和2年7月15日(2020.7.15)

(24) 登録日 令和2年6月24日(2020.6.24)

(51) Int.Cl.

F 1

|             |           |      |       |      |

|-------------|-----------|------|-------|------|

| HO1L 29/78  | (2006.01) | HO1L | 29/78 | 657D |

| HO1L 29/12  | (2006.01) | HO1L | 29/78 | 652T |

| HO1L 29/861 | (2006.01) | HO1L | 29/78 | 652D |

| HO1L 29/868 | (2006.01) | HO1L | 29/78 | 652F |

| HO1L 29/872 | (2006.01) | HO1L | 29/78 | 652M |

請求項の数 14 (全 24 頁) 最終頁に続く

(21) 出願番号 特願2017-560889 (P2017-560889)

(86) (22) 出願日 平成28年2月11日 (2016.2.11)

(65) 公表番号 特表2018-511184 (P2018-511184A)

(43) 公表日 平成30年4月19日 (2018.4.19)

(86) 國際出願番号 PCT/US2016/017518

(87) 國際公開番号 WO2016/130783

(87) 國際公開日 平成28年8月18日 (2016.8.18)

審査請求日 平成31年2月8日 (2019.2.8)

(31) 優先権主張番号 14/619,742

(32) 優先日 平成27年2月11日 (2015.2.11)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 517281691

モノリス セミコンダクター, インク.

MONOLITH SEMICONDUCTOR, INC.

アメリカ合衆国 78664 テキサス,

ラウンド ロック, ファニン アベニ

ュー 408

408 Fannin Avenue,

Round Rock, Texas 7

8664 (US)

(74) 代理人 110001139

SK特許業務法人

(74) 代理人 100130328

弁理士 奥野 彰彦

最終頁に続く

(54) 【発明の名称】高電圧半導体素子及びその素子を製造する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

n型基板上のn型ドリフト層と、

複数のMOSFETセルと、

n型ショットキー領域と、

ソース金属層と、

ショットキー金属層と、を備えるマルチセルMOSFET素子であって、

MOSFETセルの各々は、

第一及び第二p型ウェル領域と、

n型JFET領域と、

第一及び第二n型ソース領域と、

ソースオーム接点と、

ゲート誘電層と、

ゲート層と、

層間絶縁膜層と、

第一及び第二p型本体接触領域と、を備え、

前記第一及び第二p型ウェル領域は、前記n型ドリフト層上において間隔を置いて設置される関係にあり、

前記n型JFET領域は、前記第一及び第二p型ウェル領域間の前記n型ドリフト層上にあり

、

10

20

前記第一及び第二p型ウェル領域の各々は、前記JFET領域に隣接したチャネル領域を備え、

前記第一及び第二n型ソース領域は、前記第一及び第二p型ウェル領域の各々上にあり且つ前記JFET領域とは反対側の前記チャネル領域に隣接しており、

前記第一及び第二n型ソース領域は、前記n型ドリフト層よりもドーパント濃度が高く、前記ソースオーム接点は、前記第一及び第二n型ソース領域の各々上にあり、

前記ゲート誘電層は、前記JFET領域及びチャネル領域上にあり、

前記ゲート層は、前記ゲート誘電層上にあり、

前記層間絶縁膜層は、前記ゲート層上にあり、

前記第一及び第二p型本体接触領域は、前記n型ドリフト層上にあり且つ前記チャネル領域とは反対側の第一及び第二n型ソース領域に隣接しており、10

前記第一及び第二p型本体接触領域は、前記第一及び第二p型ウェル領域よりもドーパント濃度が高く、

前記n型ショットキー領域は、1又は複数の前記MOSFETセルに近接する前記n型ドリフト層上にあり、

前記ソース金属層は、前記ソースオーム接点上にあり且つそれと接触し、

前記ショットキー金属層は、前記n型ショットキー領域上にあり且つそれと接触し、

前記ショットキー金属層は、前記n型ショットキー領域とのショットキー接点を形成し、

前記マルチセルMOSFET素子は、前記ソースオーム接点及び前記1又は複数のn型ショットキー領域上に誘電体材料を更に備え、20

前記マルチセルMOSFET素子は、

前記ソースオーム接点上に前記誘電体材料を通じて形成された1又は複数のソースバリアと、

前記1又は複数のn型ショットキー領域上に前記誘電体材料を通じて形成された前記1又は複数のショットキーバリアと、を備え、

前記ソース金属層は、前記誘電体材料上にあり且つ前記ソース及びショットキーバリア中30

にあり、

前記ソース金属層は、ショットキーバリアの底部でショットキー領域と接触し、前記ソースバリアの底底部で前記ソースオーム接点と接触している、

マルチセルMOSFET素子。

#### 【請求項2】

1又は複数の前記n型ショットキー領域は、前記n型ドリフト層とはドーパント濃度が異なる、

請求項1に記載のマルチセルMOSFET素子。

#### 【請求項3】

前記n型JFET領域は、前記n型ドリフト層とはドーパント濃度が異なる、

請求項1に記載のマルチセルMOSFET素子。

#### 【請求項4】

前記第一及び第二p型ウェル領域は、x方向に互いが間隔を置いて配置され、x方向に対して垂直なy方向に延在する細長い領域であり、40

前記n型JFET領域は、前記第一及び第二p型ウェル領域間でx方向に延在する細長い領域である、

請求項1に記載のマルチセルMOSFET素子。

#### 【請求項5】

前記ショットキー領域は、隣接するMOSFETセルのp型本体接触領域間にy方向に延在する单一の連続した細長い領域を備える、

請求項4に記載のマルチセルMOSFET素子。

#### 【請求項6】

第一の前記複数のMOSFETセルのp型本体接触領域と第二の前記複数のMOSFETセルの隣接

するp型本体接触領域は、それぞれ、y方向に互いに間隔を置いて配置され且つ前記第一MOSFETセルのチャネル領域から前記第二MOSFETセルの隣接するチャネル領域までx-方向に延在する複数で別々のp型本体接触領域を備え、

前記第一MOSFETセルのn型ソース領域と前記第二MOSFETセルの隣接するn型ソース領域は、それぞれ、前記別々のp型本体接触領域間でy方向に間隔を置いて配置された複数で別々のn型ソース領域を備え、

前記第一及び第二MOSFETセル間の前記ショットキー領域は、y-方向の前記別々のp型本体接触領域間及びx方向の第一及び第二MOSFETセルの前記別々のn型ソース領域間の複数で別々のショットキー領域を備える、

請求項4に記載のマルチセルMOSFET素子。

10

#### 【請求項7】

前記第一及び第二p型本体接触領域に誘電体材料を更に備える、

請求項1に記載のマルチセルMOSFET素子。

#### 【請求項8】

前記素子は、SiC素子である、

請求項1に記載のマルチセルMOSFET素子。

#### 【請求項9】

p型ウェル領域形成工程と、

n型ソース領域形成工程と、

第一及び第二p型本体接触領域形成工程と、

ゲート酸化層蒸着工程と、

ゲート層蒸着工程と、

層間絶縁膜素材蒸着工程と、

ソースオーム接点形成工程と、

ソース金属層蒸着工程と、

金属蒸着形成工程と、を有し、

前記p型ウェル領域形成工程において、n型ドリフト層に第一及び第二p型ウェル領域を形成し、前記n型ドリフト層は、n型基板上にあり、

前記第一及び第二p型ウェル領域は、互いに離れるように間隔を置かれ、その間にn型ショットキー領域を形成し、

第一及び第二ウェル領域の隣接し且つ前記n型ショットキー領域とは反対側の前記ドリフト層のn型領域は、第一及び第二JFET領域を形成し、

前記n型ソース領域形成工程において、前記第一及び第二p型ウェル領域の各々にn型ソース領域を形成し、

前記n型ソース領域は、前記第一及び第二JFET領域から間隔を置いて配置され、前記n型ソース領域と前記JFET領域との間にp型チャネル領域を残し、

前記第一及び第二p型本体接触領域形成工程において、前記ショットキー領域と前記第一及び第二p型ウェル領域との間に第一及び第二p型本体接触領域をそれぞれ形成し、

前記ゲート酸化層蒸着工程において、前記第一及び第二JFET領域上に且つチャネル領域に隣接してゲート酸化層を蒸着し、

前記ゲート層蒸着工程において、前記ゲート酸化層上にゲート層を蒸着し、

前記層間絶縁膜素材蒸着工程において、前記ゲート層上に層間絶縁膜素材を蒸着し、

前記ソースオーム接点形成工程において、前記ソース領域上にソースオーム接点を形成し、

前記ソース金属層蒸着工程において、前記ソースオーム接点上に且つ前記n型ショットキー領域上にソース金属層を蒸着し、

前記ソース金属層は、前記n型ショットキー領域との前記ショットキー接点を形成し、

前記金属蒸着形成工程において、前記ソース金属層上に最終金属を蒸着し、

前記ソース金属層蒸着工程の前に、

誘電体材料形成工程と、

20

30

40

50

1又は複数のソースピア形成工程と、

1又は複数のショットキーピア形成工程と、を更に有し、

前記誘電体材料形成工程において、前記ソース接点とショットキー領域上に誘電体材料

が形成され、

前記1又は複数のソースピア形成工程において、前記ソース接点上に前記誘電体材料を

通じて1又は複数のソースピアを形成し、

前記1又は複数のショットキーピア形成工程において、前記ショットキー領域上に前記

誘電体材料を通じて1又は複数のショットキーピアを形成し、

前記ソース金属層蒸着工程は、前記ソース及びショットキーピアにソース金属を蒸着す

るソース金属蒸着工程を有し、

前記ソース金属層は、前記ソース及びショットキーピアの底部で前記ソース金属及びシ

ョットキー領域とそれぞれ接触する、

マルチセルMOSFET素子を製造する方法。

**【請求項 1 0】**

前記ショットキー金属層及びソース金属層上あり、そしてそれと接触した最終金属層を更に備える、請求項1に記載のマルチセルMOSFET素子。

**【請求項 1 1】**

前記ドリフト層上にn型電流拡散層を更に備え、

前記第一及び第二p型ウェル領域、前記n型JFET領域、前記第一及び第二p型本体接触領域並びに前記n型ショットキー領域は、電流拡散層上にある、

請求項1に記載のマルチセルMOSFET素子。

**【請求項 1 2】**

第一MOSFETセルと、隣接する第二MOSFETセルと、前記第一及び第二MOSFETセル間に複数のp型本体接点領域及びn型ショットキー領域を交互に備える周辺領域と、を備える、

請求項1に記載のマルチセルMOSFET素子。

**【請求項 1 3】**

前記周辺領域は、

前記周辺領域に隣接した前記第一MOSFETセルの周辺に沿って延在する第一p型本体接触領域と、

前記周辺領域に隣接し且つ前記第一p型本体接触領域とは反対側の前記第二MOSFETセルの周辺に沿って延在する第二p型本体接触領域と、を備え、

前記交互に備わるp型本体接触領域は、前記第一及び第二p型本体接触領域間に延在する、

請求項12に記載のマルチセルMOSFET素子。

**【請求項 1 4】**

前記第一MOSFETセルは、前記周辺領域に隣接して前記第一MOSFETセルの周辺に沿って延在する複数のp型本体接触領域及びn型ソース領域を交互に備え、

前記第二MOSFETセルは、前記周辺領域に隣接して前記第二MOSFETセルの周辺に沿って延在する複数のp型本体接触領域及びn型ソース領域を交互に備える、

請求項12に記載のマルチセルMOSFET素子。

**【発明の詳細な説明】****【背景技術】****【0 0 0 1】****【0 0 0 2】**

連邦委託研究に関する記載

**【0 0 0 3】**

本発明は、エネルギー省が与えるグラント番号DE-AR0000442の下で政府のサポートによってなされた。政府は、本発明についてある種の権利を有する。

**【0 0 0 4】**

背景

**【 0 0 0 5 】**

分野

**【 0 0 0 6 】**

本願は、一般的に、高電圧半導体素子及びその素子を製造する方法、特に、組込型ダイオードを備える高電圧半導体素子及びその素子を製造する方法に関する。

**【 0 0 0 7 】**

技術背景

**【 0 0 0 8 】**

酸化金属半導体電界効果トランジスター(即ち、MOSFET)は、一般的に、パワーエレクトロニクス回路(例えばDC/DCコンバーター)において利用されている。DC-DCコンバーターは、あるレベルから他のレベルへ電圧を変換するパワーMOSFET型スイッチを利用する。典型的なDC/DCコンバーターにおいて、制御回路は、電源から負荷への電力伝送を調節する2つのパワーMOSFETのゲートを駆動する。パワーMOSFETの1つは、同期整流器として作動することができる。10

**【 0 0 0 9 】**

シリコンカーバイドの特性は、例えばDC-DCコンバーター用のパワーMOSFETなどの高電圧パワーエレクトロニクスへの適用に理想的である。シリコン上のシリコンカーバイドの主要な利点の1つは、より高いその臨界絶縁破壊電界強度である。シリコンカーバイドは、シリコンのおよそ $0.3\text{MV}/\text{cm}$ と比較して、およそ $3\text{MV}/\text{cm}$ の絶縁破壊電界強度を有する。シリコンよりも、シリコンカーバイドの絶縁破壊電界強度が10倍高いと、逆阻止電圧が高く、オン抵抗が低い半導体スイッチ及び整流器が可能になり、優れたエレクトロニクスシステム性能が実現する。20

**【 0 0 1 0 】**

DC-DCコンバーターにおいて、パワーMOSFETは、1つのMOSFETがオンになり、もう1つがオフになる短い期間の間にオフになることで電源とグランドとの間の貫通電流を防ぐ必要がある。この不動時間の間、パワーMOSFET構造に集積されたpn接合ダイオードは、電流を流すことができる。SiC MOSFETに集積されたpn接合ダイオードを通る電流導電は、ショットキーダイオードと比較して、伝導電力損失が高いため好ましくない。SiC pn接合ダイオードの伝導電力損失がより高いのは、ターンオン電圧がより高いためであり、その結果、ダイオードの順電圧降下がより大きくなる。また、pn接合ダイオードは、スイッチング電力損失が高い。これは、バイポーラ素子であるためであり、ダイオードをオフにするために除去する必要がある少数キャリアーを保存するためである。30

**【 0 0 1 1 】**

このために、ショットキーダイオードは、DC-DCコンバーター回路においてフリーホイーリングダイオード(D1)としてSiCパワーMOSFETと逆並列で接続することができる。ショットキーダイオードは、ターンオン電圧がより低い(およそ $0.9\text{V}$ )ことから、およそ $3.5\text{V}$ の順電圧降下を有する組み込まれたpn接合ダイオードと比較して、伝導損失が低い。また、ショットキーダイオードは、多数キャリアー素子であることから、素子における少数キャリアーが保存されないため、スイッチング電力損失もpn接合ダイオードと比較して低い。40

**【 0 0 1 2 】**

フリーホイーリングショットキーダイオードをコンバーター回路に加えて変換効率を向上させることができる一方で、外部ショットキーダイオードの使用は、追加部品が必要なためコンバータユニットのコストを上昇させる。また、外部ショットキーダイオードは、基板上のスペースを占有し、コンバターフットプリントを小さくすることを妨げる。また、ショットキーダイオード及び基板上のその電気的接続の信頼性は、コンバーター全体の信頼性を低下させる可能性がある。加えて、ショットキーダイオードのワイヤーボンドは、コンバーターの高周波動作を制限する追加のインダクタンスをもたらす。

**【 0 0 1 3 】**

従って、MOSFET素子(特にSiC MOSFET素子)は、まだ、必要であり、ショットキーダイオードは、パワーMOSFET構造の中に組み込まれる。50

## 【0014】

概要

## 【0015】

n型基板上のn型ドリフト層と、

複数のMOSFETセルと、

n型ショットキー領域と、

ソース金属層と、

ショットキー金属層と、を備え、

MOSFETセルの各々は、

第一及び第二p型ウェル領域と、

n型JFET領域と、

第一及び第二n型ソース領域と、

ソースオーム接点と、

ゲート誘電層と、

ゲート層と、

層間絶縁膜層と、

第一及び第二p型本体接触領域と、を備え、

上記第一及び第二p型ウェル領域は、上記n型ドリフト層上において間隔を置いて設置される関係にあり、

上記n型JFET領域は、上記第一及び第二p型ウェル領域間の上記n型ドリフト層上にあり

、

上記第一及び第二p型ウェル領域の各々は、上記JFET領域に隣接したチャネル領域を備え、

上記第一及び第二n型ソース領域は、上記第一及び第二p型ウェル領域の各々上にあり且つ上記JFET領域とは反対側の上記チャネル領域に隣接しており、

上記第一及び第二n型ソース領域は、上記n型ドリフト層よりもドーパント濃度が高く、

上記ソースオーム接点は、上記第一及び第二n型ソース領域の各々上にあり、

上記ゲート誘電層は、上記JFET領域及びチャネル領域上にあり、

上記ゲート層は、上記ゲート誘電層上にあり、

上記層間絶縁膜層は、上記ゲート層上にあり、

上記第一及び第二p型本体接触領域は、上記n型ドリフト層上にあり且つ上記チャネル領域とは反対側の第一及び第二n型ソース領域に隣接しており、

上記第一及び第二p型本体接触領域は、上記第一及び第二p型ウェル領域よりもドーパント濃度が高く、

上記n型ショットキー領域は、1又は複数の上記MOSFETセルに近接する上記n型ドリフト層上にあり、

上記ソース金属層は、上記ソースオーム接点上にあり且つそれと接触し、

上記ショットキー金属層は、上記n型ショットキー領域上にあり且つそれと接触し、

上記ショットキー金属層は、上記n型ショットキー領域とのショットキー接点を形成している、

マルチセルMOSFET素子を提供する。

## 【0016】

p型ウェル領域形成工程と、

n型ソース領域形成工程と、

第一及び第二p型本体接触領域形成工程と、

ゲート酸化層蒸着工程と、

ゲート層蒸着工程と、

層間絶縁膜素材蒸着工程と、

ソースオーム接点形成工程と、

ソース金属層蒸着工程と、

10

20

30

40

50

金属蒸着形成工程と、を有し、

上記p型ウェル領域形成工程において、n型ドリフト層に第一及び第二p型ウェル領域を形成し、

上記n型ドリフト層は、n型基板上にあり、

上記第一及び第二p型ウェル領域は、互いに離れるように間隔を置いて設置され、その間にn型ショットキー領域を形成し、

第一及び第二ウェル領域の各々に隣接し且つ上記n型ショットキー領域とは反対側の上記ドリフト層のn型領域は、第一及び第二JFET領域を形成し、

上記n型ソース領域形成工程において、上記第一及び第二p型ウェル領域の各々にn型ソース領域を形成し、

上記n型ソース領域は、上記第一及び第二JFET領域から間隔を置いて配置され、上記n型ソース領域と上記JFET領域との間にp型チャネル領域を残し、

上記第一及び第二p型本体接触領域形成工程において、上記ショットキー領域と上記第一及び第二p型ウェル領域の各々との間に第一及び第二p型本体接触領域をそれぞれ形成し、

上記ゲート酸化層蒸着工程において、上記第一及び第二JFET領域上に且つチャネル領域に隣接してゲート酸化層を蒸着し、

上記ゲート層蒸着工程において、上記ゲート酸化層上にゲート層を蒸着し、

上記層間絶縁膜素材蒸着工程において、上記ゲート層上に層間絶縁膜素材を蒸着し、

上記ソースオーム接点形成工程において、上記ソース領域上にソースオーム接点を形成し、

上記ソース金属層蒸着工程において、上記ソースオーム接点上に且つ上記n型ショットキー領域上にソース金属層を蒸着し、

上記ソース金属層は、上記n型ショットキー領域との上記ショットキー接点を形成し、

上記金属蒸着形成工程において、上記ソース金属層上に最終金属を蒸着する、

マルチセルMOSFET素子を製造する方法も提供する。

#### 【0017】

n型ドリフト層エッティング工程と、

第一及び第二p型ウェル領域形成工程と、

n型ソース領域形成工程と、

第一及び第二p型本体接触領域形成工程と、

誘電体材料蒸着工程と、

ゲート酸化層蒸着工程と、

ゲート層蒸着工程と、

層間絶縁膜素材蒸着工程と、

ソースオーム接点形成工程と、

ソース金属層蒸着工程と、

金属蒸着工程と、を有し、

上記n型ドリフト層エッティング工程において、n型ドリフト層をエッティングして底部及び側壁を有する第一及び第二開口部を形成し、

上記n型ドリフト層は、n型基板上にあり、

上記第一及び第二開口部は、互いに離れるように間隔を置いて設置され、その間にn型ショットキー領域を形成し、

上記第一及び第二p型ウェル領域形成工程において、上記第一及び第二開口部に隣接したn型ドリフト層に第一及び第二p型ウェル領域をそれぞれ形成し、

上記第一及び第二p型ウェル領域は、上記n型ショットキー領域とは反対側に形成され、

上記第一及び第二ウェル領域に隣接した上記ドリフト層のn型領域は、第一及び第二JFET領域を形成し、

上記n型ソース領域形成工程において、上記第一及び第二p型ウェル領域の各々にn型ソース領域を形成し、

10

20

30

40

50

上記n型ソース領域は、上記第一及び第二JFET領域から間隔を置いて配置され、上記n型ソース領域と上記JFET領域との間にp型チャネル領域を残し、

上記第一及び第二p型本体接触領域形成工程において、第一及び第二開口部の上記底部及び側壁に隣接して第一及び第二p型本体接触領域を形成し、

上記誘電体材料蒸着工程において、上記第一及び第二開口部に誘電体材料を蒸着し、

上記ゲート酸化層蒸着工程において、上記第一及び第二JFET領域上に且つチャネル領域に隣接してゲート酸化層を蒸着し、

上記ゲート層蒸着工程において、上記ゲート酸化層上にゲート層を蒸着し、

上記層間絶縁膜素材蒸着工程において、上記ゲート層上に層間絶縁膜素材を蒸着し、

上記ソースオーム接点形成工程において、上記ソース領域上にソースオーム接点を形成し、10

上記ソース金属層蒸着工程において、上記ソースオーム接点上に且つ上記n型ショットキー領域にソース金属層を蒸着し、

上記ソース金属層は、上記n型ショットキー領域とのショットキー接点を形成し、

上記金属蒸着工程において、上記ソース金属層上に最終的な金属を蒸着する、マルチセルMOSFET素子を製造する方法も提供する。

#### 【0018】

第一MOSFETセルと、隣接する第二MOSFETセルと、上記第一及び第二MOSFETセル間に複数で交互のp型本体接点領域とn型ショットキー領域を備える周辺領域と、を備える、マルチセルMOSFET素子も提供する。ある実施形態によれば、上記周辺領域は、上記周辺領域に隣接した第一MOSFETセルの周辺に沿って延在する上記第一p型本体接触領域と、上記周辺領域に隣接し且つ上記第一p型本体接触領域とは反対側の上記第二MOSFETセルの周辺に沿って延在する第二p型本体接触領域と、を備え、上記交互のp型本体接触領域は、上記第一及び第二p型本体接触領域間に延在する。ある実施形態によれば、上記第一MOSFETセルは、上記周辺領域に隣接した上記第一MOSFETセルの周辺に沿って延在した複数で交互のp型本体接触領域とn型ソース領域を備え、上記第二MOSFETセルは、上記周辺領域に隣接した上記第二MOSFETセルの周辺に沿って延在している複数のp型本体接触領域とn型ソース領域を交互に備える。20

#### 【0019】

本教示のこれらの特徴及び他の特徴は、本願明細書に記載している。30

#### 【0020】

当業者であれば、後述する図面が図示の目的のためだけにあると理解する。

#### 【0021】

図面は、いかなる形であれ本教示の範囲を制限することを目的としない。

#### 【図面の簡単な説明】

#### 【0022】

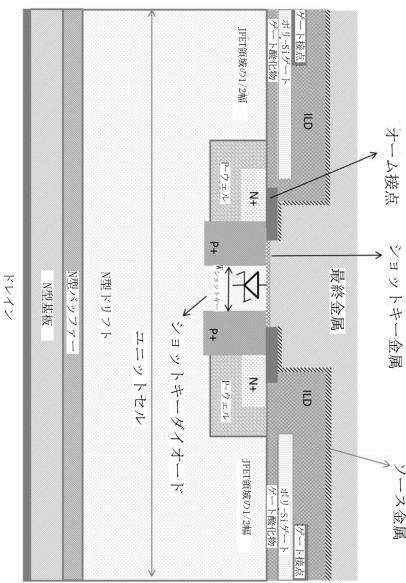

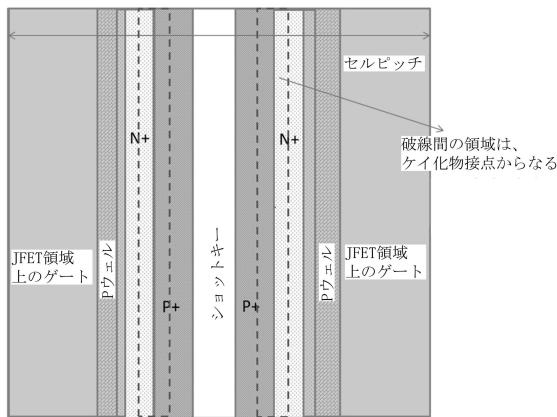

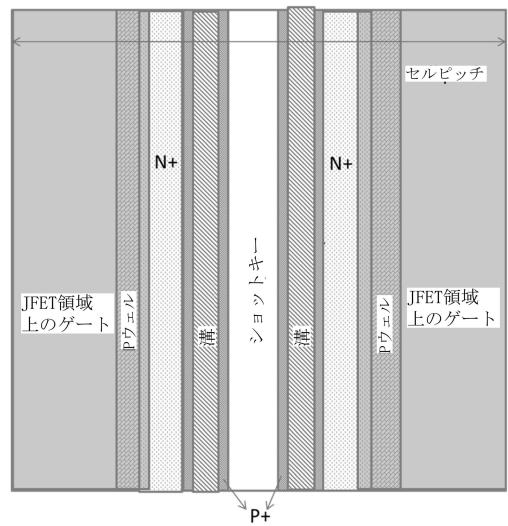

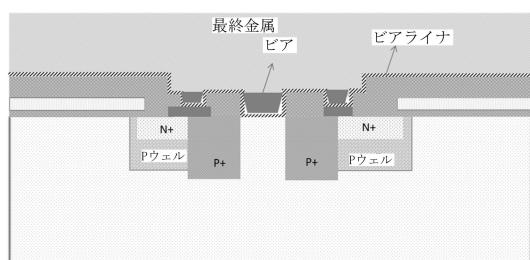

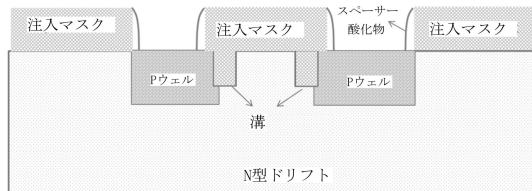

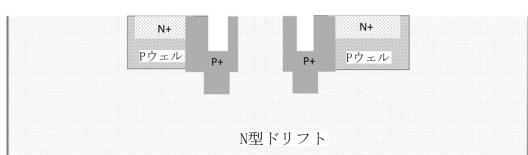

【図1A】図1Aは、組込型ショットキーダイオードを備えるマルチセルMOSFET半導体素子の模式断面図である。

#### 【0023】

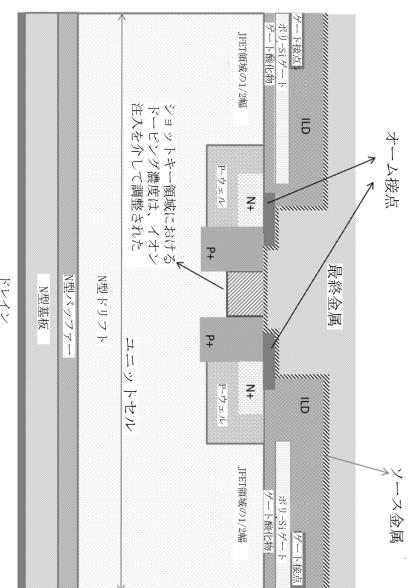

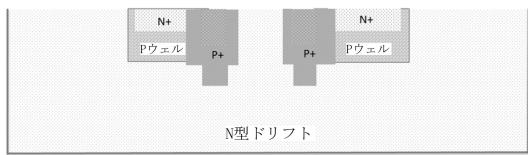

【図1B】図1Bは、組込型ショットキーダイオードを備えるマルチセルMOSFET半導体素子の模式断面図であり、上記素子のショットキー領域は、ドリフト層とは異なるドーピング濃度を有する。40

#### 【0024】

【図1C】図1Cは、組込型ショットキーダイオードを備えるマルチセルMOSFET半導体素子の模式断面図であり、上記素子のショットキー及びJFET領域は、ドリフト層とは異なるドーピング濃度を有する。

#### 【0025】

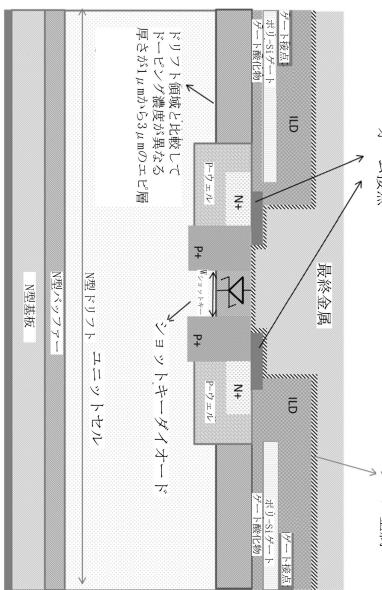

【図1D】図1Dは、組込型ショットキーダイオードを備えかつドリフト層上に電流拡散層を備えるMOSFET半導体素子の模式断面図である。

#### 【0026】

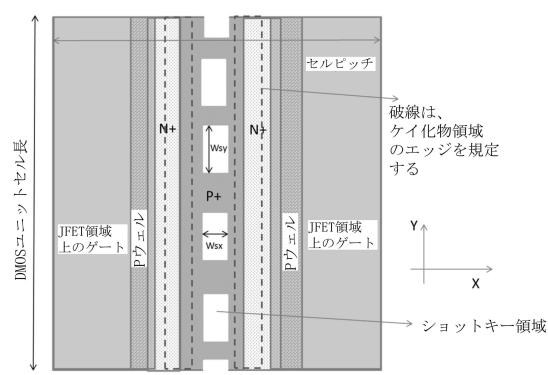

【図2】図2は、図1A-1Cに記載の組込型ショットキーダイオードを備えるマルチセルMOSFET半導体素子の配置図(即ち平面図)である。

【0027】

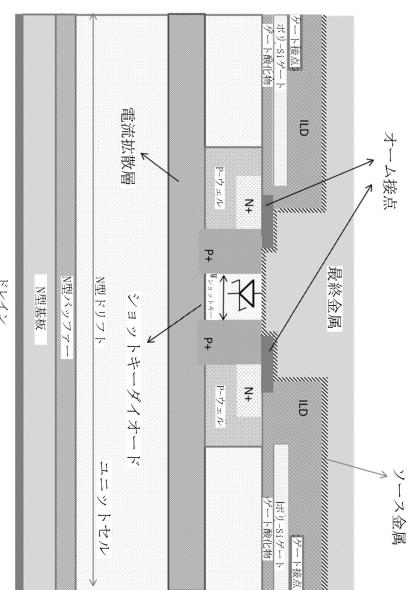

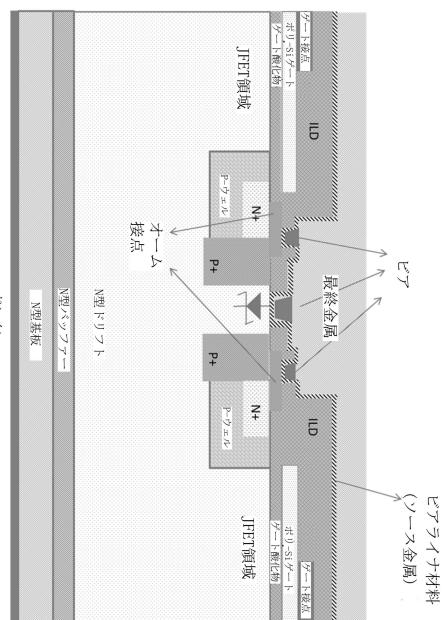

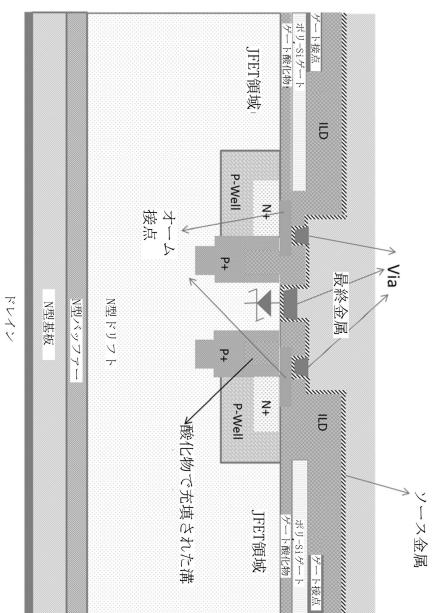

【図3】図3は、組込型ショットキーダイオードを備え、素子のソースオーム接点及びショットキー領域上に誘電体材料を通じて形成されたビアを備える、マルチセルMOSFET半導体素子の模式断面図であり、ソース金属は、ビアの底部でソースオーム接点及びショットキー領域と接触している。

【0028】

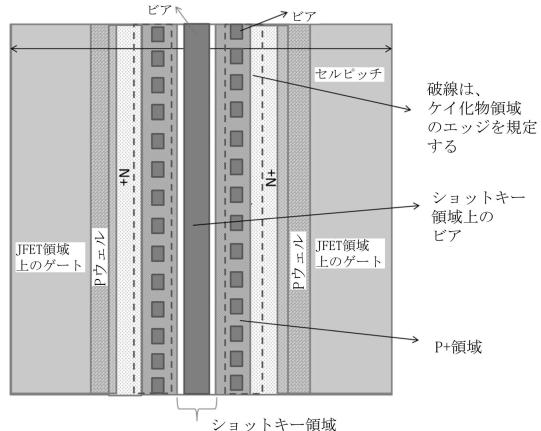

【図4】図4は、ソースオーム接点の各々上で一列に配置された複数のソースビアとショットキー領域上に単一の細長いショットキービアを備える、図3に図示のマルチセルMOSFET半導体素子の配置図(即ち平面図)である。

10

【0029】

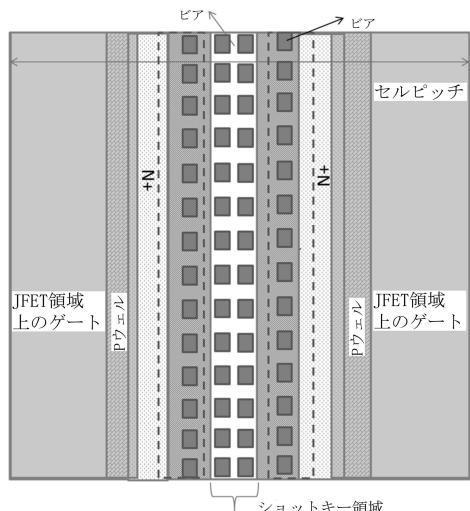

【図5】図5は、ソースオーム接点の各々上で一列に配置された複数のソースビアと、ショットキー領域上で複数の列で配置された複数のショットキービアを備える、図3に図示のマルチセルMOSFET半導体素子の配置図(即ち平面図)である。

【0030】

【図6】図6は、一列に配置され且つ連続したp型本体接触領域によって囲まれた、複数の不連続ショットキー接点領域を備える、図3に図示のマルチセルMOSFET半導体素子の配置図(即ち平面図)である。

20

【0031】

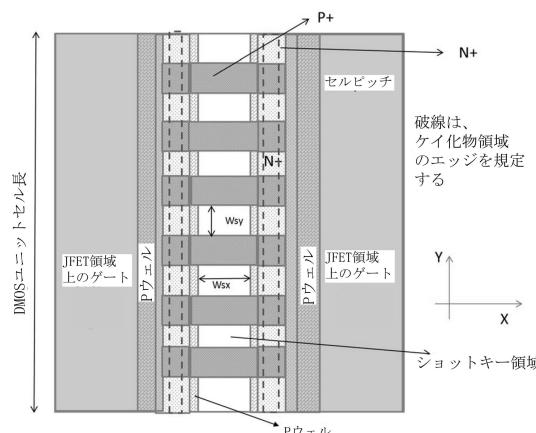

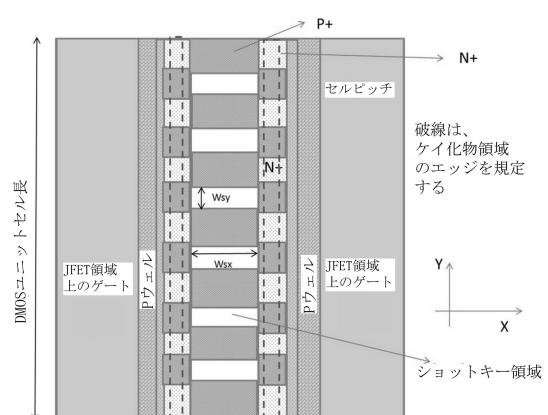

【図7A】図7Aは、マルチセルMOSFET半導体素子の配置図(即ち平面図)であり、ショットキー領域及びソース領域は、それぞれ、不連続p型本体接触領域と交互な複数の不連続領域を備え、ショットキー領域は、x方向でp型本体接触領域と隣接している。

【0032】

【図7B】図7Bは、マルチセルMOSFET半導体素子の配置図(即ち平面図)であり、ショットキー領域及びソース領域は、それぞれ、不連続p型本体接触領域と交互な複数の不連続領域を備え、ショットキー領域は、x方向でソース領域に隣接している。

【0033】

【図8】図8は、組込型ショットキーダイオードを備えるMOSFET素子の模式断面図であり、p型本体接触領域(P+)は、酸化物が充填された溝の底部及び側壁に隣接して形成されている。

30

【0034】

【図9】図9は、図8の素子の配置図(平面図)を示す模式図である。

【0035】

【図10】図10は、組込型ショットキーダイオードを備えるMOSFET素子の模式断面図であり、p型本体接触領域(P+)は、酸化物が充填された溝の底部及び側壁に隣接して形成され、ビアは、ソースオーム接点及びショットキー領域上の誘電体材料を通じて形成されている。

【0036】

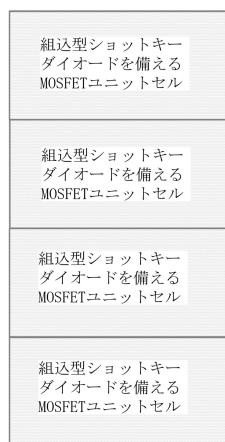

【図11】図11は、組込型ショットキーダイオードを備える複数のMOSFETを具備するマルチセルMOSFETのレイアウトを示す模式図である。

40

【0037】

【図12】図12は、組込型ショットキーダイオードを備えないMOSFETと、組込型ショットキーダイオードを備えるMOSFETを交互に具備するマルチセルMOSFETのレイアウトを示す模式図である。

【0038】

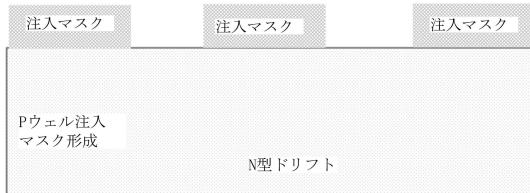

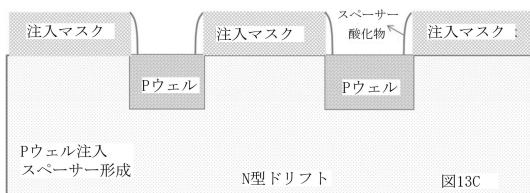

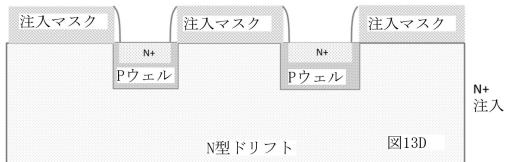

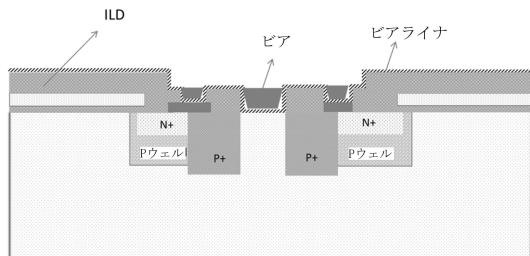

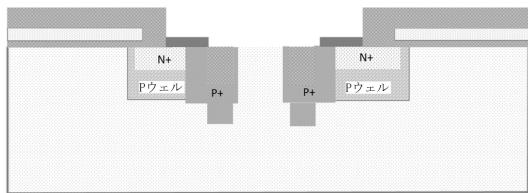

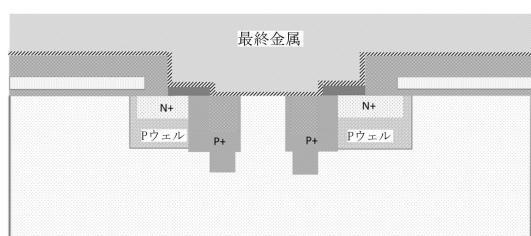

【図13A - 13I】図13Aから13Iは、図3に図示する、組込型ショットキーダイオードを備えるマルチセルMOSFET素子を製造する方法を図示している模式図である。

【0039】

【図14A - 14K】図14Aから14Kは、図8に図示する、組込型ショットキーダイオード

50

を備えるマルチセルMOSFET素子を製造する方法を図示している模式図である。

**【0040】**

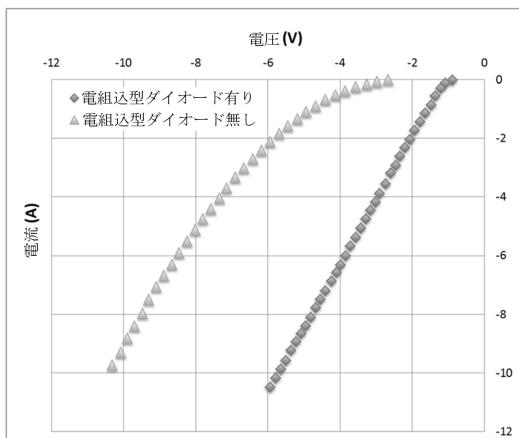

【図15】図15は、組込型ショットキーダイオードを備えていない従来型DMOS素子( )の動作と比較した、本願明細書に記載の組み込まれたショットキーを備えるDMOS( )の動作を示している、0Vのゲート-ソース電圧(Vgs)に対して第三象限のグラフである。

**【0041】**

【図16】図16は、組込型ショットキーダイオードを備えるパワーMOSFETを具備するDC-DCコンバーター回路の模式図である。

**【発明を実施するための形態】**

**【0042】**

各種実施形態の記述

**【0043】**

本明細書で用いられる、「周辺領域」は、セルの周辺又はその近くの領域である。ある実施形態によれば、セルの周辺領域は、セルの周辺に隣接することができる。

**【0044】**

本明細書で用いられるように、下位層"上"にある層は、下位層と直接接触することができる、又は、層と下位層との間に1又は複数の介在層があって下位層と間接的に接触することができる。

**【0045】**

酸化金属半導体電界効果トランジスター(MOSFET)素子は、パワーエレクトロニクス回路(例えばDC/DCコンバーター)に用いることができる。一般に使用されるパワー半導体スイッチは、二重拡散MOSFET又はDMOSFETである。拡散は、製造プロセスを指す。特に、Pウェル及びNソース領域は、二重拡散プロセス(即ち、p型ウェルの拡散に続いてn型ソース領域上への拡散)によって得られる。

**【0046】**

ドーパントの拡散がSiCにおいて極僅かであるため、ドーパントは、イオン注入プロセスを介してSiCに導入される。このため、SiC DMOSFETは、二重イオン注入MOSFETと称する。従来型のSiC DMOSFET素子は、N型基板上のn型ドリフト層に埋め込まれた2つのp型ウェル領域を備える。p型ウェル領域間のn型材料は、素子のJFET領域を形成する。N+ソース領域は、p型ウェル領域に埋め込まれ、p型ウェル領域の内側のエッジからオフセットしている。このオフセットは、素子のチャネル領域を形成する。高融点ゲート電極は、JFET及びチャネル領域上に形成される。

**【0047】**

マルチセルDMOSFET素子において、間隔を置いて配置された複数のp型ウェル領域及びN+ソース領域は、ドリフト層に埋め込まれる。P+本体接触領域は、N+ソース領域及び下層のp型ウェル領域を通じて埋め込まれて、隣接するセルのソース/ウェル領域を分離する。マルチセル素子において、ユニットセルの幅(即ち、セルピッチ)は、隣接するJFET領域の中心間距離として規定される。所定の領域におけるDMOSセルの充填密度が大きくなることを確実にするために、セルピッチは、より小さいほうが一般的に望ましい。セルのデザインは、ストライプ、「ラダー」タイプ又は「3DMOS」であってもよい。

**【0048】**

DMOSFETがオン状態の間、閾値電圧よりも大きいゲートバイアスを加えると、電流の流れが素子のドレインターミナルから素子のソースターミナルへとなる。DMOSFETがオフ状態の間、ドレインターミナルは、高電圧でバイアスされ(例えば、電源電圧に対するドレインは、1200ボルトとすることが可能)、ゲート及びソースターミナルは、0ボルトに対応する接地電位でバイアスされる。大きい逆電圧は、P-ウェルからN-ドリフト領域によって形成されたPN接合ダイオードの空乏領域でサポートされる。DMOSFETは、P-ウェルからN-ドリフト領域の間に形成される内蔵型PN接合ダイオードを備える。ある種の動作条件下で、PN接合ダイオードは、順バイアスされて電流を導く。前述のように、SiC MOSFETに組み込まれたpn接合ダイオードを通る電流導電は、ショットキーダイオードと比較して伝導及

10

20

30

40

50

びスイッチング電力損失が高いため好ましくない。従って、MOSFET構造の中でショットキーダイオードを組み込むことができる種々の素子構造及びレイアウトを提供する。

#### 【0049】

ある実施形態によれば、組込型ショットキーダイオードを備えるMOSFETが提供され、素子のソース金属皮膜は、ショットキー接点も形成する。図1Aは、このタイプのマルチセル素子のユニットセルの模式断面図である。図1Aから分かるように、MOSFET素子は、隣接するMOSFETセル間にショットキーダイオードを備える。図1Aに示すように、ショットキーダイオードは、ショットキー金属とN型ドリフト領域の間に形成され、本体接点(P+)領域によって側面が囲まれている。ショットキー金属がN型ドリフト領域上に蒸着されて、ショットキー接点が形成される。ソース金属がオーム接点に蒸着されて、ソース接点が形成される。次に、最終ソース金属がソース金属及びショットキー金属上に、そしてそれと接触するように蒸着される。ショットキー金属及びソース金属は、同じ素材であってもよく異なる素材であってもよい。MOSFETが逆阻止モードにあり、高電圧(例えば1200V)がドレンインターミナルに印加されると、本体接点(P+)領域を囲んでいるショットキーダイオードは、高い電界からショットキー領域を保護することができる。本体接点(P+)領域は、MOSFETの逆阻止状態下でショットキーダイオードの漏れ電流を低減する役割を担うこともできる。素子のセルピッチは、1つのMOSFETセルのJFET領域の中心から、隣接するMOSFETセルのJFET領域の中心までの距離として規定される。10

#### 【0050】

ショットキー領域のドーピング濃度は、N型ドリフト領域のドーピング濃度と異なっていてもよい。ショットキー領域における正味のドーピング濃度がドリフト領域と異なる素子の模式図を図1Bに示している。ある実施形態によれば、ショットキー領域におけるドーピング濃度は、 $5 \times 10^{15}$ から $5.0 \times 10^{16} \text{ cm}^{-3}$ であってもよい。ある実施形態によれば、ショットキー領域は、ショットキー領域におけるドーピング濃度がN-ドリフトドーピング濃度よりも低くなるように、カウンタードープすることができる。カウンタードーピングは、逆阻止状態の間、電界を低下させるために用いることができる。ある実施形態によれば、ショットキー領域におけるドーピング濃度は、N-ドリフト領域におけるドーピング濃度よりも高くてよい。これは、ダイオード順電圧降下を低下させるために行なうことができる。20

#### 【0051】

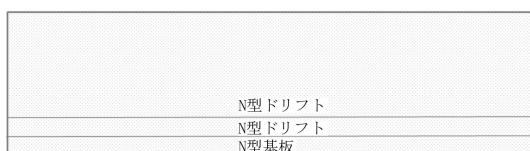

また、MOSFET素子のJFET領域は、ドリフト層とはドーピング濃度が異なっていてもよい。ある実施形態によれば、JFET領域及びショットキー領域は、それぞれドーピング濃度が異なっていてもよく、かかるドーピング濃度は、ドリフト層のドーピング濃度とも異なる。例えば、JFET領域のドーピング濃度及びショットキー領域のドーピング濃度は、イオン注入法を介して互いに独立して規定することができる。ある実施形態によれば、n型エピタキシャル層(即ち、エピ層)は、ドリフト層とはドーピング濃度が異なるJFET及びショットキー領域を形成するために、Nドリフト領域上に成長させることができる。Nドリフト領域上に成長したn型エピタキシャル層を備える素子の模式図を図1Cに示している。ある実施形態によれば、エピ層は、 $0.2 \mu\text{m}$ から $3.0 \mu\text{m}$ の厚さを有することができる。ある実施形態によれば、エピ層のドーピング濃度は、 $5 \times 10^{15}$ から $1.0 \times 10^{17} \text{ cm}^{-3}$ とすることができる。このエピ層領域は、MOSFETのショットキー領域及び/又はJFET領域の性能調整を助けるために、ドリフト領域のドーピング濃度よりも高い又は低いドーピング濃度を有することができる。30

#### 【0052】

図1Dは、組込型ショットキーダイオード及びドリフト層上の電流拡散層を備える、ある実施形態によるMOSFET半導体素子の模式断面図である。電流拡散層は、JFET領域からドレンの方への電流の流れを拡散させることができ、JFET抵抗の低下を可能にする。電流拡散層のドーピング濃度は、 $5 \times 10^{15}$ から $5.0 \times 10^{17} \text{ cm}^{-3}$ とすることができる。40

#### 【0053】

図1に示すように、素子は、隣接する本体接点(P+)領域間に、单一の連続したn型ショッ

50

トキー領域を有することができる。図1にも示されるように、JFET領域の上面は、ソース及び/又はショットキー領域の上面と位置が合っていてもよく、ゲート酸化膜は、JFET領域の上面にある。

#### 【0054】

図1B、1C及び1Dにおいて、単一のソース金属層は、ショットキー領域上、及び、ソースオーム接点領域上に示されている。これらの実施形態のために、ショットキー領域上の金属は、図1Aに示す通りソース領域上の金属とは異なっていてもよい。

#### 【0055】

図2は、図1A-1Cに示す素子の配置図(即ち、平面図)を示す模式図である。図2に示すように、破線の領域は、ソースオーム接点を表す。セルピッチ(即ち、隣接するMOSFET素子のJFET領域の中心間の距離)は、図2にも明示している。10

#### 【0056】

ソース金属被覆は、限定するものではないが、チタン、窒化チタン、アルミニウム、タングステン及びそれらの組み合わせを含む1又は複数の導電層からなることができる。

#### 【0057】

ある実施形態によれば、同じ1又は複数ソース金属被覆層は、ソースオーム接点を接触させて、ショットキー接点を形成し、ワイヤーボンディング及びアセンブリプロセスの最終ソース金属被覆として機能するために用いることができる。

#### 【0058】

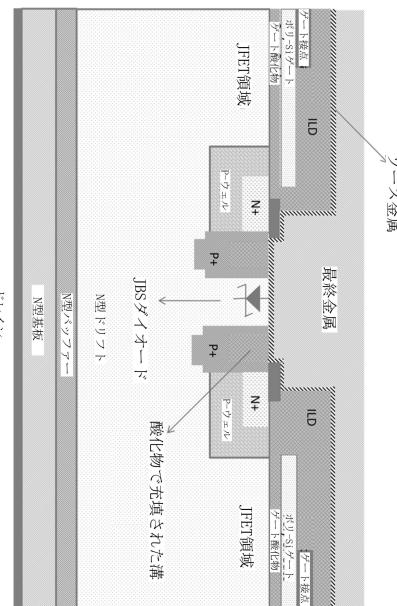

図3は、組込型ショットキーダイオードを備えるMOSFET素子の断面を示している模式図であり、1又は複数のビアは、MOSFETのソースオーム接点とソース最終金属被覆との間に電気的接続を形成するために用いられる。図3に示すように、1又は複数のビアは、ソース金属(即ち、ソースライナー)とソース最終金属被覆との間に電気的接続を形成するために用いることもできる。特に、誘電体材料は、JFET領域上及びソースオーム接点上に形成することができる。誘電体材料は、MOSFETの層間絶縁膜層(ILD)を形成するために用いる同一材料でありえる。次に、ビアは、ソースオーム接点上及びJFET領域上の誘電体材料を通じて形成することができる。ソース金属は、ビアを配線して、ビアの底部でソースオーム接点及びショットキー領域と接触する。20

#### 【0059】

図3に示すように、ビアライナ材料(即ち、ソース金属層)は、ソースビアの底部でソースオーム接点と接触する。また、図3に示すように、ビアライナ材料(即ち、ソース金属)は、ショットキー領域上のビアの底部でショットキー領域と接触して、ショットキーダイオードを形成する。ある実施形態によれば、ビアライナ材料は、チタン(Ti)及び窒化チタン(TiN)を含む。ある実施形態によれば、ビアは、ビアフィラー材料を用いて完全又は部分的に充填されている。ある実施形態によれば、ビアフィラー材料は、タングステン(W)である。タングステンを含むビアの充填及びビアライナ材料の蒸着は、標準タングステン(W)プラグプロセスを使用して行なうことができる。30

#### 【0060】

ある実施形態によれば、完全なJFET領域の幅は、 $1.5\mu\text{m}$ から $6\mu\text{m}$ であり、ショットキー領域を囲んでいるP+領域の幅は、 $0.6\mu\text{m}$ から $3\mu\text{m}$ である、及び/又は、ショットキー領域の幅は、 $1\mu\text{m}$ から $4\mu\text{m}$ である。40

#### 【0061】

図4は、ショットキー領域の単一の連続したビア及び一列に配置された、ソースオーム接点上の複数で別々の不連続なビアを備える、図3に示す配置図(即ち、平面図)を示している模式図である。矩形のソースビアがソースオーム接点領域を通じて示されているが、ソースビアは、限定するものではないが、正方形及び矩形を含む任意の形状とすることができます。正方形又は矩形のソースビアが用いる場合、ビアの典型的な寸法は、 $0.5\mu\text{m} \times 0.5\mu\text{m}$ から $1\mu\text{m} \times 1\mu\text{m}$ である。ソースオーム接点領域にわたるビア間隔は、プロセス技術に応じて変えることができる。ある実施形態によれば、ビア間隔は、 $0.5\mu\text{m}$ から $1\mu\text{m}$ の間で変えることができる。50

**【 0 0 6 2 】**

ソースビアの1つの列を図4のソースオーム接点領域上に示しているが、複数列のソースビアを用いることもできる。図4に示すように、ショットキー領域上のビアは、MOSFETセル長に沿って延在する単一の細長いビアであってもよい。

**【 0 0 6 3 】**

図5は、ショットキー領域に複数列で配置された複数のソースビア及びソースオーム接点の各々上に单一の列で配置された複数のソースビアを備える、図3に示すMOSFET素子の配置図を示している。ソースオーム接点領域及びショットキー領域におけるビアの形状、ビアのサイズ及びビア間隔は、図4に示す素子と同じであってもよい。図5は、ショットキー領域における2つの列のビア及びソースオーム接点領域における1つの列のビアを示している。ソースオーム接点領域、ショットキー領域又はその両方は、1列又は複数列のビアを有することができる。オーム接点領域及びショットキー領域上での同じビア形状、サイズ及びビア間隔の使用は、より確固としたビアプロセスを可能にする。

10

**【 0 0 6 4 】**

ある実施形態によれば、オーム接点材料は、ニッケル、チタン及びアルミニウムとすることができる。

**【 0 0 6 5 】**

ある実施形態によれば、ソースビアは、正方形又は矩形である。

**【 0 0 6 6 】**

ある実施形態によれば、MOSFET素子は、ソースオーム接点上において1列又は複数列で配置された複数のビア及びショットキー領域上の単一の細長いビアを備える。ある実施形態によれば、MOSFET素子は、ソースオーム接点上において1列又は複数列で配置された複数のビア及びショットキー領域上において1列又は複数列で配置された複数のビアを備える。

20

**【 0 0 6 7 】**

図6は、組込型ショットキーダイオードを備えるMOSFET素子の配置図を示しており、ショットキー領域は、MOSFETセルに沿って連続していない。図6に示すように、素子は、DMOSセル長に沿って周期的に設置された別々のショットキー領域を備える。別々のショットキー領域は、正方形又は矩形(図示)を含む任意の形状とすることができます。図6に示すように、ショットキー領域は、p型本体接点材料(即ち、図6のP+)によって完全に囲まれている。

30

**【 0 0 6 8 】**

別々の不連続なショットキー領域を使用することによって、MOSFETユニットセルにおけるショットキー領域の割合を独立して制御することができる。例えば、ユニットセルにおけるショットキーダイオード量を増加させるために、Y方向のショットキー領域の幅(Wsy)は、固定のままにして、X方向のショットキー領域の幅(Wsx)を増加させることができる。Y方向のショットキー領域の幅(Wsy)は、高電圧からショットキー領域を効果的に保護するために、P+領域に関して適切な値で固定することができる。

**【 0 0 6 9 】**

単一のフォトリソグラフィ開口部は、図4及び5に示す素子に必要とされる2つのフォトリソグラフィ開口部と比較して、p型本体接触領域を埋め込む必要があるため、図6のレイアウトを使用することでより小さなセルピッチが可能になる。また、ショットキー領域の寸法に応じて、ショットキー領域を囲んでいるp型本体接触領域の存在に起因する逆阻止中の高電位からショットキー領域の保護を向上させることができる。

40

**【 0 0 7 0 】**

ショットキー金属は、ショットキー領域上に蒸着され、最終ソース金属の蒸着前にショットキー接点を形成する。上述のプロセスと類似のビアプロセスは、ショットキー接点及び/又はソース金属とソースオーム接点との間の電気接点を形成するために用いることができる。

**【 0 0 7 1 】**

50

素子のソース金属被覆は、素子のショットキー領域に対するショットキー接点としても機能することができる。ソース金属被覆は、チタン、窒化チタン、アルミニウム又はタンゲステンを含むことができる。同じ1又は複数の金属被覆層は、ソースオーム接点に対する電気接点を作るために用いることができ、ショットキー接点を形成することは、ワイヤーボンディング及びアセンブリプロセス間の最終ソース金属被覆としても機能することができる。

#### 【 0 0 7 2 】

図7A及び7Bは、組込型ショットキーダイオードを備える第一及び第二MOSFET素子の配置図を示している模式図であり、ショットキー領域及びソース領域は、DMOSセルに沿って連続していない。図7Aに示すように、複数で別々のショットキー領域は、DMOSセル長に沿って周期的に設置される。矩形状の領域を示しているが、ショットキー領域は、正方形又は矩形を含む任意の形状にすることができる。また、図7Aから明らかなように、ソース(N+)領域は、ユニットセル長に沿って(即ち、y方向に)連続していない。特に、図7Aに示す素子において、ソース(N+)及び本体接点(P+)領域は、ユニットセル長に沿って交互に設置される。別々のショットキー領域の各々は、隣接するMOSFETセルの本体接点(P+)領域間に設置される。ショットキー領域は、また、y-方向が本体接点(P+)領域によって囲まれている。図7Bに示す素子において、素子の別々のショットキー領域は、x-方向における隣接するMOSFETのp型本体接触領域ではなくソース領域(N+)間にある。p型本体接触領域(P+)は、y方向に間隔を置いて配置されて、隣接するMOSFET素子のp型チャネル領域間に延在する、別々の領域の単一の列として配置される。図7A及び7Bに示すレイアウトは、ユニットのショットキー領域を独立して調整することを可能にする。これらのレイアウトは、図6に示す素子と比較して、より小さなセルピッチを可能にする。

#### 【 0 0 7 3 】

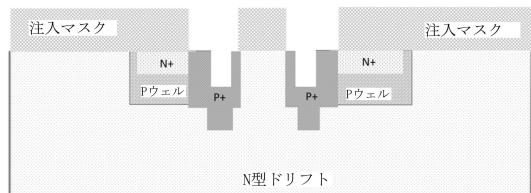

図8は、組込型ショットキーダイオードを備えるMOSFET素子の模式断面図であり、p型本体接触領域(P+)は、誘電体材料(例えば、酸化物)で充填された溝の底部及び側壁に隣接して形成される。p型本体接触領域は、溝を形成した後にイオン注入法を介して形成することができ、これによって、より深いp型インプラント領域となる。より深いp型インプラント領域は、高電圧がSiC MOSFETのドレインに印加された場合の高電位からショットキー領域をより良好に保護することができる。この構造は、また、ショットキー領域のより高いドーピング濃度がダイオードの順電圧降下を更に低下させることを可能にする。順電圧の低下は、ダイオードにおける電力損失を低下させる。

#### 【 0 0 7 4 】

図9は、図8の素子の配置図を示している模式図である。図9から明らかなように、溝及びショットキー領域は、DMOSユニットセル長に沿って(即ち、y-方向に)延在している。ショットキー金属は、上記の通り、ソース金属の蒸着前に、ショットキー領域上に蒸着することができる。また、p型本体接触領域(P+)は、幅又はx方向で溝と隣接して示されている。セルピッチも、図9に示している。

#### 【 0 0 7 5 】

図10は、組込型ショットキーダイオードを備えるMOSFET素子の模式断面図であり、p型本体接触領域(P+)は、酸化物で充填された溝の底部及び側壁に隣接して形成され、ビアは、ソースオーム接点領域及びショットキー領域上に形成される。図10に示すように、ビアライナ材料は、上記の通り、ショットキー金属として機能する。

#### 【 0 0 7 6 】

図11及び図12は、組込型ショットキーダイオードを備えるMOSFETを具備するマルチセルMOSFET素子の種々の配置の配置図を示している。図11において、マルチセルMOSFETのレイアウトは、それぞれ組込型ショットキーダイオードを備えるMOSFETのユニットセルからなる。図12において、マルチセルMOSFETのレイアウトは、組込型ショットキーダイオードを備えるMOSFETと、組込型ショットキーダイオードを備えないMOSFETと、を具備する。図12が組込型ショットキーダイオードを備える及び備えないMOSFETのユニットセルを交互に示す一方で、これらのユニットセルの他の配置を用いることもできる。例えば、2番目、3番

10

20

30

40

50

目等毎に、ユニットセルは、組込型ショットキーダイオードを備える又は備えないユニットセルとすることができます。

#### 【0077】

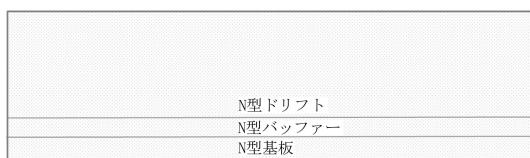

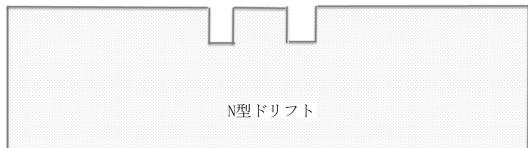

図13Aから13Iは、図3に示すように、組込型ショットキーダイオードを備えるマルチセルMOSFET素子を製造する方法を示している模式図である。図13Aに示すように、出発材料は、N型基板上にN型ドリフト領域を備える。N-ドリフトの厚さは、数マイクロメートル(例えば、 $2\mu\text{m}$ )から100マイクロメートル以上まで変えることができる。基板の厚さも変えることができる。基板は、350マイクロメートルの厚さを有することができる。また、n型バッファー層は、n型ドリフト層と基板との間に示されている。バッファー層は任意であり、ドリフト層は直接基板上に形成することができる。

10

#### 【0078】

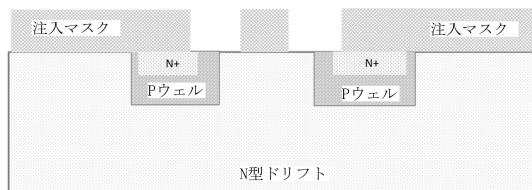

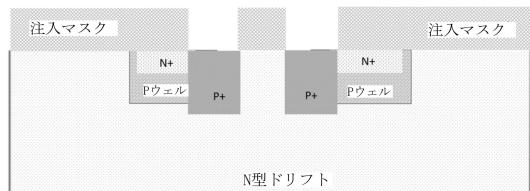

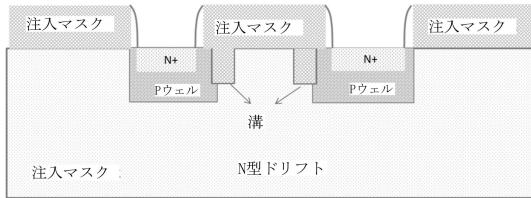

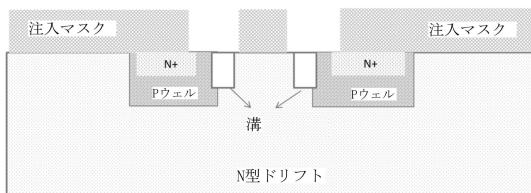

図13Bに示すように、注入マスク(例えば、二酸化珪素)を蒸着させて、パターニングし、エッチングしてP-ウェル注入のための開口部を規定する。次に、P型ウェルをドリフト層に注入する。図13Cに示すように、P-ウェル注入後、マスク材料(例えば、二酸化珪素)の層を蒸着させて、エッチバックし、P-ウェル注入マスキング材料のエッジ上のスペーサーを規定する。図13Dに示すように、次に、N+注入を実行してN+ソース領域を規定する。スペーサーは、p型ウェル領域のエッジからソース領域をオフセットし、これによって、ソース領域と隣接するJFET領域との間にp型チャネルが規定される。

#### 【0079】

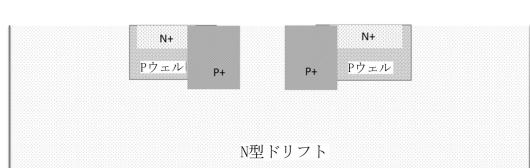

図13Eに示すように、注入マスク(例えば、二酸化珪素)を蒸着して、パターニングし、エッチングをしてP+インプラントのための開口部を規定する。P+領域は、MOSFETのための本体接点として機能する。次に、本体接触領域は、図13Fに示すように形成される。図13Gで示す注入マスクの除去後、注入物は、高温(例えば、1650 )でのアニーリングを通じて活性化することができる。

20

#### 【0080】

次に、ゲート酸化膜を形成して、ポリシリコンゲート蒸着、パターニング及びエッチング並びに層間誘電体(例えば、二酸化珪素)蒸着、パターニング及びエッチングを行なうことができる。次に、ソースオーム接点を形成して、エッチングし、アニーリングすることができる。次に、誘電体材料(例えば、二酸化珪素)を、ソースオーム接点、p+領域及びショットキー領域上に蒸着して、パターニングし、エッチングしてソース及びショットキービアを形成する。そして、ソース金属/ビアライナ材料を蒸着する。電気接点は、ビアライナ材料を通じたオーム接点となる。また、ビアライナ材料は、ショットキー領域と接触してショットキー接点を形成する。この材料は、チタン(Ti)及び窒化チタン(TiN)の層とすることができる。次に、ビアは、ビアフィラー材料(例えば、タングステン)を用いて充填される。これらのプロセス工程後の素子を図13Hに示している。そして、最終ソース金属(例えば、アルミニウム)を蒸着することができる。これらのプロセス工程後の素子を図13Iに示している。

30

#### 【0081】

小さい改変を伴う図13A-13Iに示すプロセスは、図1A-1Cに示すソース及びショットキー領域上にビアを備えない素子を生産するために用いることができる。バッファー及び基板層は、図13B-13Iに示されていない。

40

#### 【0082】

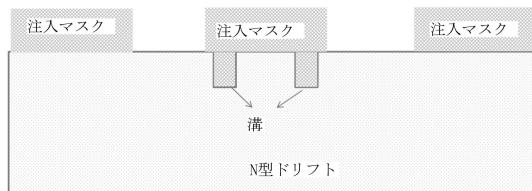

図14Aから14Kは、図8に示す組込型ショットキーダイオードを備えるマルチセルMOSFET素子を製造する方法を示している模式図である。図14Aに示すように、出発材料は、上にN-基板を備えるN型ドリフト領域であってもよい。n型ドリフト層の厚さは、変えることができ、例示的な厚さは、2マイクロメートルから100マイクロメートル以上の範囲である。基板の厚さも変えることができる。例示的な基板の厚さは、350マイクロメートルである。任意のn型バッファー層を基板とドリフト層との間に用いることができる。

#### 【0083】

図14Bに示すように、溝は、n型ドリフト層において異方的にエッチングされる。溝は、

50

フォトリソグラフィープロセスに必要とされるアライメントマークを規定するために用いる同じエッチングプロセスを使用して規定することができる。図14Cに示すように、注入マスク(例えば、二酸化珪素)を蒸着して、パターニングし、エッチングしてP-ウェル注入のための開口部を規定する。次に、P-ウェル領域をドリフト層に注入する。図14Dに示すように、P-ウェル注入後、マスキング材料(例えば、二酸化珪素)の層を蒸着して、異方的にバックエッチし、P-ウェル注入マスキング酸化物のエッジ上のスペーサーを規定する。

#### 【0084】

図14Eに示すように、次に、N+注入を、マスクの開口部を通じて実行し、N+ソース領域を規定する。スペーサーによって、注入されたソース領域がp型ウェル領域のエッジから間隔を置いて配置することができ、これにより、ソース領域と隣接するJFET領域との間のウェル領域にチャネルを規定する。

10

#### 【0085】

図14Fに示すように、注入マスキング材料(例えば、二酸化珪素)を蒸着して、パターニングし、エッチングしてP+インプラントのための開口部を規定する。P+領域は、DMOSFETのための本体接触領域として機能をする。P+注入後の素子を図14Gに示している。図14Gから明らかなように、P+注入は、溝より深い。

#### 【0086】

図14Hは、注入マスクの除去後の素子を示している。プロセスにおけるこの段階で、注入物を、高温(例えば、1650 )でアニーリングすることによって活性化させることができる。図14Iは、注入活性化アニーリング後の素子を示している。図14Iに示すように、溝は、二酸化珪素を充填されて平坦化される。酸化物及び平坦化は、確立した蒸着工程(例えば、化学気相成長法)及び研磨工程(例えば化学機械研磨又は乾式エッチング平坦化技術)を使用して行なうことができる。

20

#### 【0087】

溝が充填され平坦化された後、ゲート酸化膜を形成して、ポリシリコンゲート蒸着、パターニング及びエッチング並びに層間誘電体(例えば、二酸化珪素)蒸着、パターニング及びエッチングを行なうことができる。次に、ソースオーム接点を形成して、エッチングし、アニーリングすることができる。これらのプロセス工程後の素子を図14Jに示している。

。

#### 【0088】

次に、ショットキー金属(例えば、チタン)を蒸着して、最終ソース金属(例えば、アルミニウム)の蒸着を行なうことができる。これらのプロセス工程後の素子を図14Kに示している。

30

#### 【0089】

バッファー及び基板層は、図14B-14Kに示されていない。

#### 【0090】

図15は、従来型DMOS素子( )の動作と比較して、本願明細書に記載の組込型ショットキーを備えるDMOS( )の動作を示している、0Vのゲート-ソース電圧(Vgs)に対する第三象限のグラフである。第三象限において、従来型の素子における電流導電は、主に、内部P-ウェルからN-ドリフトpn接合ダイオードを通して行われる。本願明細書に記載されている素子において、電流導電は、組込型ショットキーダイオードによって支配される。図15から明らかなように、組込型ショットキーダイオードは、任意の所定の電流において、内部ダイオードと比較して電圧降下が非常に小さい。順電圧降下が小さいと、より良好なパワー・エレクトロニクスシステム性能になる。

40

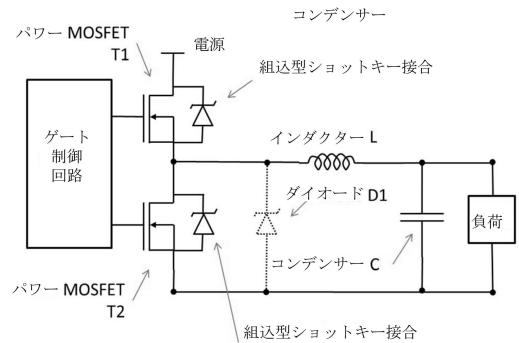

#### 【0091】

図16は、組込型ショットキーダイオードを備えるパワーMOSFETを具備するDC-DCコンバーターの回路の模式図である。図16に示すように、本願明細書に記載されているように、回路は、組み込まれたショットキー接合によって2つのパワーMOSFET T1及びT2を備える。パワーMOSFETのゲートは、電源から負荷への電力伝送を調節するためにゲート制御回路によって駆動される。パワーMOSFETは、組み込まれたショットキー接合を備えるため、(ハ

50

ツチングされたラインで示す)フリーホイーリングダイオードD1を必要としない。

### 【0092】

前述の明細書は、例示のために提供した例によって本発明の原理を説明しているが、形態及び詳細についての様々な変更を本発明の真の範囲を逸脱しない範囲でなすことができることを、当業者であればこの開示を読み込むことで理解するだろう。

【図1A】

図1A

【図1B】

図1B

【図 1C】

図 1C

【図 1D】

図 1D

【図 2】

図 2

【図 3】

図 3

ビアライナ材料

(ソース金属)

【図4】

図4

【図5】

図5

【図6】

図6

【図7B】

図7B

【図7A】

図7A

【図 8】

図 8

【図 9】

図 9

【図 10】

図 10

【図 11】

図 11

【図12】

図12

【図13A】

図13A

【図13E】

図13E

【図13F】

図13F

【図13G】

図13G

【図13B】

図13B

【図13C】

図13C

【図13D】

図13D

【図13H】

図13H

【図13I】

図13I

【図14A】

図14A

【図 14B】

図 14B

【図 14C】

図 14C

【図 14D】

図 14D

【図 14E】

図 14E

【図 14F】

図 14F

【図 14G】

図 14G

【図 14H】

図 14H

【図 14I】

図 14I

【図 14J】

図 14J

【図 14K】

図 14K

【図 15】

図 15

【図 16】

図 16

---

フロントページの続き

| (51)Int.Cl.              | F I                  |

|--------------------------|----------------------|

| H 01 L 21/336 (2006.01)  | H 01 L 29/91 K       |

| H 01 L 21/8234 (2006.01) | H 01 L 29/86 3 0 1 F |

| H 01 L 27/088 (2006.01)  | H 01 L 29/86 3 0 1 D |

| H 01 L 29/47 (2006.01)   | H 01 L 29/78 6 5 2 S |

| H 01 L 21/329 (2006.01)  | H 01 L 29/78 6 5 8 B |

| H 02 M 3/155 (2006.01)   | H 01 L 27/088 B      |

|                          | H 01 L 29/48 F       |

|                          | H 01 L 29/48 P       |

|                          | H 01 L 29/48 D       |

|                          | H 02 M 3/155 T       |

(74)代理人 100130672

弁理士 伊藤 寛之

(72)発明者 マトーカ , ケビン

アメリカ合衆国 7 8 6 8 1 テキサス , ラウンド ロック , コロンビア フォールズ ドラ

イブ 8 5 2 4

(72)発明者 チャティ , キラン

アメリカ合衆国 7 8 6 6 4 テキサス , ラウンド ロック , シルバー トレイル 8 2 4

(72)発明者 バナルジー , サジット

アメリカ合衆国 7 8 6 8 1 テキサス , ラウンド ロック , アンジェリコ レーン 4 4 1

2

審査官 棚田 一也

(56)参考文献 国際公開第2014 / 038110 (WO , A1 )

特開平11 - 008399 (JP , A )

特開2014 - 090057 (JP , A )

(58)調査した分野(Int.Cl. , DB名)

|        |               |

|--------|---------------|

| H 01 L | 2 9 / 7 8     |

| H 01 L | 2 1 / 3 2 9   |

| H 01 L | 2 1 / 3 3 6   |

| H 01 L | 2 1 / 8 2 3 4 |

| H 01 L | 2 7 / 0 8 8   |

| H 01 L | 2 9 / 1 2     |

| H 01 L | 2 9 / 4 7     |

| H 01 L | 2 9 / 8 6 1   |

| H 01 L | 2 9 / 8 6 8   |

| H 01 L | 2 9 / 8 7 2   |

| H 02 M | 3 / 1 5 5     |