(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5342422号

(P5342422)

(45) 発行日 平成25年11月13日(2013.11.13)

(24) 登録日 平成25年8月16日(2013.8.16)

(51) Int.Cl.

G01R 31/26 (2006.01)

H01L 23/12 (2006.01)

F 1

G01R 31/26

H01L 23/12 501B

請求項の数 7 (全 28 頁)

(21) 出願番号 特願2009-280469 (P2009-280469)

(22) 出願日 平成21年12月10日 (2009.12.10)

(65) 公開番号 特開2011-122924 (P2011-122924A)

(43) 公開日 平成23年6月23日 (2011.6.23)

審査請求日 平成24年8月27日 (2012.8.27)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 丸山 一哉

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 石川 智和

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 松橋 潤

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

以下の工程を含むことを特徴とする半導体装置の製造方法：

(a) 上面、前記上面に形成された第1電極パッド、前記上面に形成された第2電極パッド、前記上面とは反対側の下面、前記下面に形成され、かつ前記第1電極パッドと電気的に接続された第1ランド、前記下面に形成され、かつ前記第2電極パッドと電気的に接続され、かつ前記第1ランドの径よりも大きい径から成る第2ランド、前記第1ランドおよび前記第2ランドのそれぞれの表面を露出するように前記下面に形成された絶縁性樹脂被膜、および前記第1ランドの前記表面に形成された外部端子と成る導電性部材を有する配線基板と、前記配線基板の前記上面に搭載された半導体チップとを含む組立体を準備する工程；

(b) 前記組立体をプローブソケットに装着し、前記プローブソケットの第1コンタクトピンと前記導電性部材とを接触させ、前記プローブソケットの第2コンタクトピンと前記第2ランドとを接触させ、前記組立体の電気特性検査を行う工程；

ここで、

前記第2ランドの前記表面には外部端子と成る導電性部材が接続されず、前記第2ランドの前記表面は露出している。

## 【請求項 2】

前記第1コンタクトピンの先端部の平面形状は円形から成り、

前記第1コンタクトピンの前記先端部の周縁部に沿って複数の突起が形成されており、

前記第2コンタクトピンの先端部の平面形状は円形から成り、

前記第2コンタクトピンの前記先端部の中央部に一つの突起が形成されていることを特徴とする請求項1記載の半導体装置の製造方法。

【請求項3】

前記プローブソケットは、第1ピンガイドと、前記第1ピンガイドと繋がるボールガイドと、前記第2ピンガイドとを備えたソケット本体を有しており、

前記第1コンタクトピンは、前記第1ピンガイド内に配置されており、

前記第2コンタクトピンは、前記第2ピンガイド内に配置されており、

前記第1および第2コンタクトピンの表面と、前記第1および第2ピンガイドの内壁面との間には隙間が形成され、

前記(b)工程では、前記配線基板の前記下面が前記ソケット本体の凹部の底面と対向し、かつ前記導電性部材が前記ボールガイド内に位置するように、前記組立体を前記凹部内に収納することを特徴とする請求項2記載の半導体装置の製造方法。

【請求項4】

前記配線基板の上面において、前記半導体チップの周囲にはダムが形成されており、

前記配線基板の平面形状は四角形から成り、

前記第1ランドは、前記配線基板の前記下面における中央部から、前記配線基板の前記下面における第1辺に向かう方向に沿って複数列に亘って配列されており、

前記ダムは、前記配線基板の前記上面において、複数列に亘って配列された複数の第1ランド列の中央部と平面的に重なる位置に配置され、

前記(b)工程では、前記プローブソケットのキャップに設けられた凸部を前記ダムに押し付けることによって、前記プローブソケットの前記第1コンタクトピンと前記導電性部材とを接触させ、前記プローブソケットの前記第2コンタクトピンと前記第2ランドとを接触させ、前記組立体の電気特性検査を行うことを特徴とする請求項3記載の半導体装置の製造方法。

【請求項5】

前記第2ランドの平面形状は四角形であることを特徴とする請求項4記載の半導体装置の製造方法。

【請求項6】

上面、前記上面に形成された複数の電極パッド、前記上面とは反対側の下面、前記下面に形成され、前記複数の電極パッドとそれ電気的に接続された複数のランド、および前記複数のランドのそれぞれの表面を露出するように前記下面に形成された絶縁性樹脂被膜を有する配線基板と、前記配線基板の前記上面に搭載された半導体チップとを含む半導体装置であって、

前記複数のランドは、前記半導体装置の外部端子となる導電性部材が表面に接続された第1ランドと、外部端子となる導電性部材が表面に接続されず、前記表面が露出した第2ランドとを有し、

前記第2ランドの径は、前記第1ランドの径よりも大きいことを特徴とする半導体装置。

【請求項7】

前記第2ランドの平面形状が四角形であることを特徴とする請求項6記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造技術に関し、特に、半導体チップが搭載された配線基板の下面にテスト用ランドを設けた面実装型の半導体装置およびその製造に適用して有効な技術に関するものである。

【背景技術】

【0002】

10

20

30

40

50

S i P (システムインパッケージ) や B G A (ボールグリッドアレイ) のような面実装パッケージ形態を有する半導体装置は、パッケージ基板と呼ばれる配線基板の上面に搭載した 1 枚または複数枚の半導体チップ (以下、単にチップという) を樹脂で封止した構造を有している。

【 0 0 0 3 】

上記配線基板の上面には複数の配線が形成されており、これらの配線の一端 (ボンディンググリード) とチップとは、金属ワイヤあるいはバンプ電極を介して電気的に接続される。一方、配線基板の下面には、配線基板内のビアホールを通じて上記配線に電気的に接続された複数のランドが設けられる。これらのランドは、半導体装置の外部端子を構成しており、半導体装置は、これらのランドに接続された半田バンプを介して各種電子機器のマザーボード (実装基板) に実装される。

10

【 0 0 0 4 】

また、配線基板の下面には、上記した外部端子としてのランドの他に、半導体製造メーカーがチップの電気特性検査を行うためのテスト用ランドが設けられる。この電気特性検査は、上記半田バンプおよびテスト用ランドのそれぞれの表面にプローブ針と呼ばれる金属製のコンタクトピンを接触させ、チップに形成された集積回路の良否や、チップから配線基板のランドに至る配線経路の導通・非導通などを判別する試験である。

【 0 0 0 5 】

例えは特許文献 1 (特開 2006-93189 号公報) には、配線基板の上面にマイコンチップとメモリチップとを 2 段に積み重ねて実装し、これらのチップをモールド樹脂で封止した S i P 型の半導体装置において、配線基板の下面の周辺部に複数の電極 (5 c) を外部端子として配置し、これらの電極 5 c の内側にメモリチップの評価、信頼度試験および不良解析などを行う複数の電極 (5 d) を試験端子として配置する技術が開示されている。

20

【 0 0 0 6 】

上記 S i P の外部端子を構成する電極 5 c には半田バンプが接続されるのに対し、試験端子を構成する電極 5 d には半田バンプが接続されず、平坦な L G A (Land Grid Array) 構成となっている。また、互いに隣接する電極 5 d のピッチは、互いに隣接する電極 5 c のピッチと同じであるが、電極 5 d の直径は電極 5 c の直径よりも小さい。さらに、電極 5 d の表面は、電極 5 c に接続された半田バンプとの短絡ポテンシャルを低減するために、ソルダレジストで被覆されている。メモリチップの試験時には、電極 5 d の表面を覆うソルダレジストを除去し、露出した電極 5 d にプローブ針を接触させる。

30

【 0 0 0 7 】

特許文献 2 (特開 2009-49170 号公報) は、S i P や B G A のような面実装パッケージ形態を有する半導体装置において、外部端子に接続されるバンプを、径およびピッチが大きなバンプと小さなバンプとに分け、前者よりも後者を配線基板の中央寄りに配置する技術を開示している。

【 0 0 0 8 】

ここで、上記した大きなバンプの一部は半導体装置と実装基板との接続に用いられ、大きなバンプの他部は、実装基板との接続には用いないがスクリーニングテスタへの接続に用いられる。一方、小さなバンプは、実装基板との接続にもスクリーニングテスタとの接続にも用いられない。すなわち、小さなバンプは、半導体製造メーカーが出荷前に電気特性検査を行うテスト用バンプである。

40

【 0 0 0 9 】

上記した構成によれば、大きなバンプを介して半導体装置を実装基板に実装したときには、小さなバンプの領域直下の実装基板上に配線パターンが配置されていても、この配線パターンとテスト用バンプとの不所望な短絡が回避される。これにより、実装基板に配線パターンを配置しない領域を設けなくとも済むので、テスト用バンプとの不所望な短絡を抑制するための実装基板側の制約が緩和される。

【先行技術文献】

50

**【特許文献】****【0010】**

【特許文献1】特開2006-93189号公報

【特許文献2】特開2009-49170号公報

**【発明の概要】****【発明が解決しようとする課題】****【0011】**

本発明者らは、第1の半導体パッケージの上に第2の半導体パッケージを積層し、それ 10

ぞの半導体パッケージに搭載されたチップ同士を電気的に接続してシステムを構成する、いわゆるパッケージ・オン・パッケージ(Package on Package: P O P)型の半導体装置を開発している。

**【0012】**

P O P型半導体装置は、それぞれの半導体パッケージに搭載するチップの機能や記憶容量を個別に変更することができるので、前述したS i PやB G Aに比べて、製品の用途に応じた種々のシステムを短期間で安価に実現することができる。また、積層前の第1および第2半導体パッケージをそれぞれテスト工程で選別し、良品のみを選別してから両者を組立てるので、完成品の製造歩留まりを改善できるという利点もある。

**【0013】**

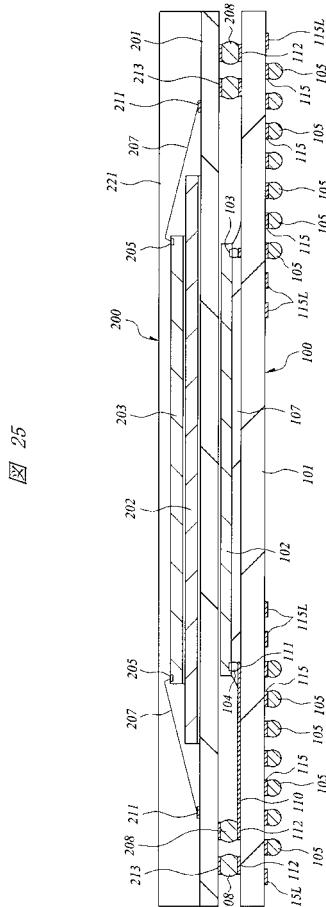

図25は、本発明者らが開発しているP O P型半導体装置の全体構成を示す断面図である。図25に示すように、このP O P型半導体装置は、第1半導体パッケージ100と、その上部に積層された第2半導体パッケージ200とで構成されている。 20

**【0014】**

下段側の第1半導体パッケージ100は、第1配線基板101と、この第1配線基板101の上面に搭載されたコントローラチップ102とを備えている。コントローラチップ102の正面には、複数の電極パッド103および図示しない集積回路が形成されている。この集積回路は、第2半導体パッケージ200に搭載されたメモリチップ(D R A Mチップ202およびフラッシュメモリチップ203)を制御するための制御回路を含んでいる。コントローラチップ102は、その正面が第1配線基板101の上面と対向するように配置され、第1配線基板101の上面の中央部にフェイスタウン実装されている。 30

**【0015】**

第1配線基板101の上面に形成された複数の配線110の一端はボンディングリード111を構成し、他端は上面側ランド112を構成している。ここで、この上面側ランド112は、後程詳細に説明する第2半導体パッケージ200の半田ボール208が接続(形成)されるランドである。そして、複数のボンディングリード111のそれと、これに対応するコントローラチップ102の電極パッド103は、導電性部材(ここでは、半田ボール)104を介して電気的に接続されている。また、第1配線基板101の上面とコントローラチップ102の正面との間には、コントローラチップ102の正面を保護するためのアンダーフィル樹脂107が充填されている。

**【0016】**

第1配線基板101の下面(裏面)には、図示しないビア配線を介して上記配線110に電気的に接続された複数の下面側ランド115および複数のテスト用ランド115Lが形成されている。そして、下面側ランド115には、半導体装置と外部電子機器との間で信号および電源電位(又は基準電位)の入出力を行うための外部端子(伝導経路)と成り、かつ導電性部材から成る半田ボール105が接続(形成)される。すなわち、P O P型半導体装置は、これらの下面側ランド115に接続された半田ボール105を介してデジタルカメラや携帯電話などの外部電子機器に実装される。一方、テスト用ランド115Lは、第1半導体パッケージ100の完成後に行われる電気特性検査工程で使用されるテスト用端子を構成している。テスト用ランド115Lは、P O P型半導体装置を外部電子機器に実装する顧客にとって不要の端子であるため、半田ボール105は接続されない。

## 【0017】

上記第1半導体パッケージ100の完成後の電気特性検査工程では、テスト用ランド115Lにプローブ針を接触させ、コントローラチップ102からテスト用ランド115Lに至る配線経路の導通／非導通を検査する。また、このテスト工程では、下面側ランド115に接続された半田ボール105にもプローブ針を接触させ、コントローラチップ102に対するA C / D C テストや、コントローラチップ102から半田ボール105に至る配線経路の導通／非導通を検査する。すなわち、下面側ランド115は、外部端子だけでなく、テスト用端子としても機能する。

## 【0018】

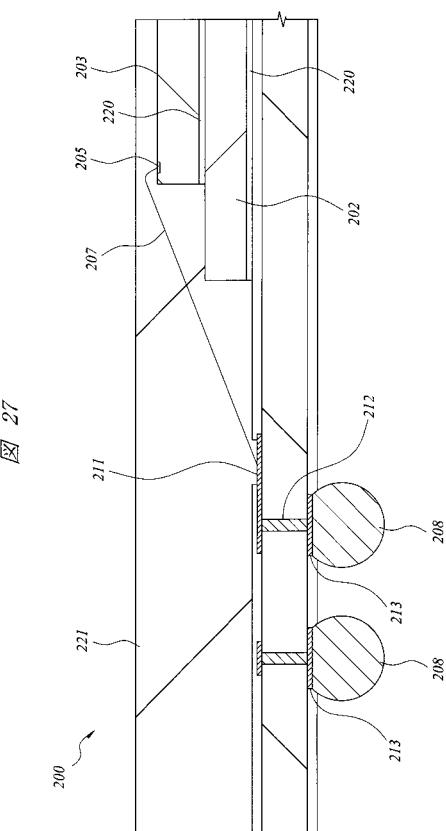

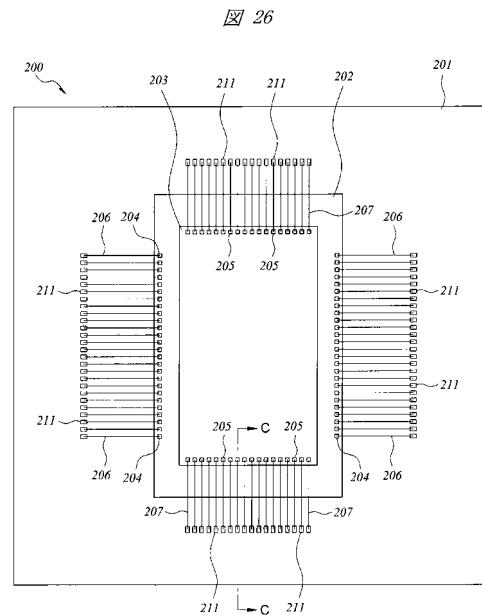

図26は、上記第1半導体パッケージ100の上部に積層された第2半導体パッケージ200の第2配線基板201を示す平面図、図27は、図26のC-C線に沿った断面図である。

10

## 【0019】

図25、図26および図27に示すように、第1半導体パッケージ100の上部に積層された第2半導体パッケージ200は、第1半導体パッケージ100の第1配線基板101とほぼ同一の外形寸法を有する第2配線基板201と、この第2配線基板201の上面の中央部に搭載されたD R A Mチップ202と、このD R A Mチップ202の上部に積層されたフラッシュメモリチップ203とを備えている。D R A Mチップ202は、その裏面が第2配線基板201の上面と対向するように、接着剤220によって第2配線基板201の上面の中央部に搭載される。また、フラッシュメモリチップ203は、接着剤220によってD R A Mチップ202の上面に搭載されている。

20

## 【0020】

上記D R A Mチップ202の正面には複数の電極パッド204が形成されている。これらの電極パッド204は、A uワイヤ206を介して第2配線基板201のボンディングリード211に電気的に接続されている。また、フラッシュメモリチップ203の正面には、複数の電極パッド205が形成されている。これらの電極パッド205は、A uワイヤ207を介して第2配線基板201のボンディングリード211に電気的に接続されている。D R A Mチップ202、フラッシュメモリチップ203、ボンディングリード211およびA uワイヤ206、207は、樹脂封止体221によって封止されている。なお、図26は、樹脂封止体221の図示を省略している。

30

## 【0021】

第2配線基板201の下面（裏面）には、ビア配線212を介して上記ボンディングリード211に電気的に接続された複数の下面側ランド213が形成されている。下面側ランド213の数は、前記第1半導体パッケージ100の第1配線基板101の上面に形成された上面側ランド112の数と同じであり、第1半導体パッケージ100の上に第2半導体パッケージ200を積層した時に、第2半導体パッケージ200の下面側ランド213とそれに対応する第1半導体パッケージ100の上面側ランド112とが互いに対向するようになっている。

## 【0022】

第2半導体パッケージ200の外部端子を構成する上記複数の下面側ランド213の表面には、半田ボール208が接続されている。これらの半田ボール208は、第1半導体パッケージ100の下面側ランド115に接続された半田ボール105よりも融点が高い半田材料からなる。そして、第2半導体パッケージ200は、これらの半田ボール208を介して下段の第1半導体パッケージ100に電気的に接続されている。

40

## 【0023】

上記したP O P型半導体装置の組み立て前に行われる第1半導体パッケージ100のテスト工程では、プローブカードが内蔵されたプローブソケットに第1半導体パッケージ100を装着する。そして、プローブソケットに設けられた複数のプローブ針（以下、コントクトピンということもある）を第1配線基板101の下面の半田ボールおよびテスト用ランドに接触させながら各種の電気特性検査を行う。

50

## 【0024】

しかし、本発明者の検討によると、POP型半導体装置の小型化が進み、上記第1配線基板101の下面に形成されたランド（下面側ランド115およびテスト用ランド115L）の径やランド間ピッチが小さくなると、プローブ針とランドとの位置合わせ精度が低下し、最悪の場合、プローブ針とランドとが非接触となるために、正確な電気特性検査を行うことができなくなるという問題が生じる。

## 【0025】

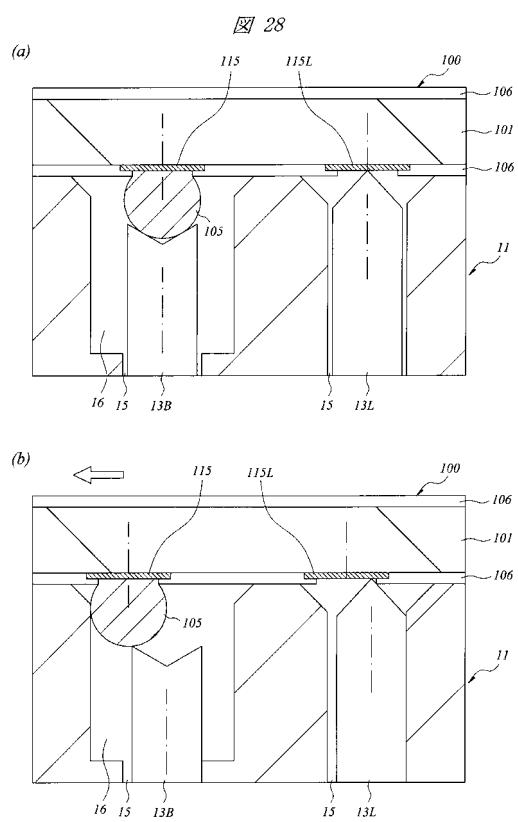

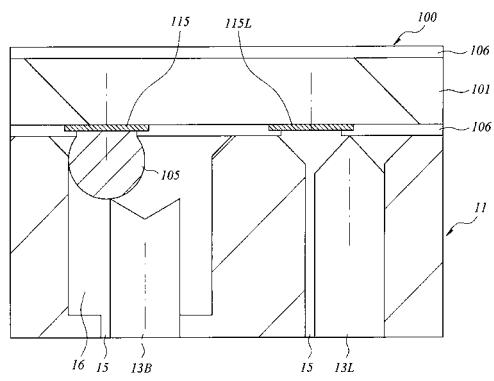

図28は、第1配線基板101の下面に形成されたランド（下面側ランド115およびテスト用ランド115L）とプローブソケットに設けられたプローブ針（コンタクトピン）との接触部を示す概略断面図である。

10

## 【0026】

プローブソケットのソケット本体11には、複数個のボール接続用コンタクトピン13Bと複数個のランド接続用コンタクトピン13Lとが内蔵されている。図28には、ボール接続用コンタクトピン13Bおよびランド接続用コンタクトピン13Lが1本ずつ示してある。ボール接続用コンタクトピン13Bは、第1配線基板101の下面側ランド115に取り付けられた半田ボール105と接触するプローブ針であり、ランド接続用コンタクトピン13Lは、テスト用ランド115Lと接触するプローブ針である。

## 【0027】

ボール接続用コンタクトピン13Bおよびランド接続用コンタクトピン13Lのそれぞれは、ソケット本体11に設けられたピンガイド15内をコイルバネの弾性力によって上下動する構造になっている。ボール接続用コンタクトピン13Bが挿入されるピンガイド15の先端部近傍（ボールガイド16）には半田ボール105が挿入されるので、その径はピンガイド15の径よりも広くなっている。言い換えると、半田ボール105がピンガイド15と繋がるボールガイド16内に配置される。

20

## 【0028】

図28(a)は、ボール接続用コンタクトピン13Bと半田ボール105、およびランド接続用コンタクトピン13Lとテスト用ランド115Lがそれぞれ理想的な状態で接触した状態を示している。このとき、ボール接続用コンタクトピン13Bの中心は半田ボール105の中心と一致し、ランド接続用コンタクトピン13Lの中心はテスト用ランド115Lの中心と一致する。

30

## 【0029】

一方、図28(b)は、ボール接続用コンタクトピン13Bと半田ボール105との位置ずれ、およびランド接続用コンタクトピン13Lとテスト用ランド115Lとの位置ずれがそれぞれ最大になった状態を示している。なお、ここでは、第1配線基板101がソケット本体11に対して左方向（図の矢印方向）にずれた場合を示している。このとき、半田ボール105は、ボールガイド16の内壁面（左側の内壁面）に接触した状態になる。また、ランド接続用コンタクトピン13Lおよびボール接続用コンタクトピン13Bは、それぞれピンガイド15の内壁面（右側の内壁面）に接触した状態になる。

## 【0030】

第1配線基板101は、上記のように、ボール接続用コンタクトピン13Bと半田ボール105との位置ずれ、およびランド接続用コンタクトピン13Lとテスト用ランド115Lとの位置ずれがそれぞれ最大になった場合でも、ボール接続用コンタクトピン13Bと半田ボール105、およびランド接続用コンタクトピン13Lとテスト用ランド115Lがそれぞれ非接触にならないように設計される。

40

## 【0031】

ところが、実際には、第1配線基板101およびプローブソケット10にそれぞれ加工ばらつきが存在する。また、第1配線基板101とその上面に搭載されたコントローラチップ102は、熱膨張係数が互いの異なる材料で構成されているので、コントローラチップ102の動作時に発生する熱などによって第1配線基板101に反りが発生する。そして、この反りは、第1配線基板101の中心部よりも周辺部でより大きくなるため、この

50

反りに起因するランドとプローブ針の位置ずれは、第1配線基板101の周辺部に配置されたランドで顕著になる。また、それぞれのコンタクトピン13B, 13Lは、それぞれのピンガイド15内において上下動を可能するために、ピンガイド15の内壁面とコンタクトピン13B, 13Lの表面との間に隙間が設けられている。言い換えると、コンタクトピンの径が、ガイドの径よりも小さい。さらに、配線基板の下面には複数の半田ボール105が形成されるが、半田ボール105が配置される下面側ランド115の位置が、加工ばらつきにより本来の位置からずれるおそれがある。そして、下面側ランド115がずれると、このずれた下面側ランド115に形成された半田ボール105の位置もずれる。そのため、半田ボール105がソケット本体11に設けられたガイド(ボールガイド16)内に確実に収納できるように、ボールガイド16の径をピンガイド15の径よりも大きく形成している。10

#### 【0032】

その結果、第1配線基板101をプローブソケットのソケット本体11に装着した時に、ボール接続用コンタクトピン13Bと半田ボール105との位置ずれ量、またはランド接続用コンタクトピン13Lとテスト用ランド115Lとの位置ずれ量が前記図28(b)に示した設計上の許容範囲を超てしまうことがある。

#### 【0033】

このとき、第1配線基板101の下面に形成されたランド(下面側ランド115およびテスト用ランド115L)の径が十分に大きい場合には、両者が非接触状態になることはない。しかし、第1配線基板101の小型化が進み、これに伴ってランドの径やランド間ピッチが小さくなると、プローブ針とランドとの位置ずれ量が上記した許容範囲を超えたときに、ランド接続用コンタクトピン13Lとテスト用ランド115Lとが非接触状態になるおそれがある。20

#### 【0034】

すなわち、ランド接続用コンタクトピン13Lとテスト用ランド115Lとの接触部に着目すると、ランド接続用コンタクトピン13Lの先端部(上端部)の形状は、平坦なテスト用ランド115Lと一点で接触する、いわゆる一本針形状になっている。詳細に説明すると、ランド接続用コンタクトピン13Lの先端部(上端部)の平面形状(図28において、テスト用ランド115L側から見たコンタクトピン13Lの平面形状)は円形から成り、針の頂点はこのランド接続用コンタクトピン13Lの先端部(上端部)の中央部に配置されている。言い換えると、1つの突起がランド接続用コンタクトピン13Lの先端部(上端部)の中央部に形成されている。そのため、ランド接続用コンタクトピン13Lの開口半径(テスト用ランド115Lの周辺部を覆うソルダレジスト106から露出した部分の半径)が上記した許容範囲よりも小さくなると、図29に示すように、両者が非接触状態になるおそれがある。30

#### 【0035】

これに対し、下面側ランド115には、第1配線基板101の下面よりも下方に突出する半田ボール105が接続されている。また、ボール接続用コンタクトピン13Bの先端部(上端部)の形状は、球状の半田ボール105と多点で接触する、いわゆるクラウン形状になっている。詳細に説明すると、ボール接続用コンタクトピン13Bの先端部(上端部)の平面形状(図28において、下面側ランド115側から見たコンタクトピン13Bの平面形状)が円形から成り、複数の突起はこの先端部の周縁部に沿って配置(形成)されている。そのため、たとえ下面側ランド115や半田ボール105の半径が上記した許容範囲より小さくなっ場合でも、半田ボール105とボール接続用コンタクトピン13Bとの非接触は生じ難い。40

#### 【0036】

このように、POP型半導体装置の小型化に伴って、第1配線基板101の下面に形成されるランド(下面側ランド115およびテスト用ランド115L)の径が小さくなると、特に、半田ボール105が接続されないテスト用ランド115Lとランド接続用コンタクトピン13Lとの接触不良が発生し易くなり、テスト用ランド115Lを使った第1半50

導体パッケージ 100 の電気特性検査を精度よく行うことができなくなる。

【0037】

本発明の目的は、チップが搭載された配線基板の下面にテスト用ランドを備えた面実装型半導体装置において、配線基板を小型化した場合でも、テスト用ランドを使った電気特性検査を精度よく行う技術を提供することにある。

【0038】

本発明の他の目的は、チップが搭載された配線基板の下面にテスト用ランドを備えた面実装型半導体装置の小型化を推進する技術を提供することにある。

【0039】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。 10

【課題を解決するための手段】

【0040】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

(1) 本発明の好ましい一実施形態である半導体装置の製造方法は、第1ランド、前記第1ランドの径よりも大きい径から成る第2ランド、および前記第1ランドに形成され、外部端子と成る導電性部材を有する配線基板と、前記配線基板の前記上面に搭載された半導体チップとを含む組立体を準備する工程と、前記組立体をプローブソケットに装着し、前記プローブソケットの第1コンタクトピンと前記導電性部材とを接触させ、前記プローブソケットの第2コンタクトピンと前記第2ランドとを接触させ、前記組立体の電気特性検査を行う工程とを含む半導体装置の製造方法であって、前記第2ランドには前記導電性部材が接続されず、かつ前記半導体装置の電気特性検査時にのみ使用される。 20

(2) 本発明の好ましい一実施形態である半導体装置は、複数のランドを有する配線基板と、前記配線基板に搭載された半導体チップとを含む半導体装置であって、前記複数のランドは、前記半導体装置の外部端子となる導電性部材が接続された第1ランドと、前記導電性部材が接続されず、かつ前記半導体装置の電気特性検査時にのみ使用される第2ランドとを有し、前記第2ランドの径は、前記第1ランドの径よりも大きい。

【発明の効果】

【0041】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下の通りである。 30

【0042】

上記した本発明の好ましい一実施形態によれば、チップが搭載された配線基板の下面にテスト用ランドを備えた面実装型の半導体装置において、配線基板を小型化した場合でも、テスト用ランドを使った電気特性検査を精度よく行うことが可能となる。

【図面の簡単な説明】

【0043】

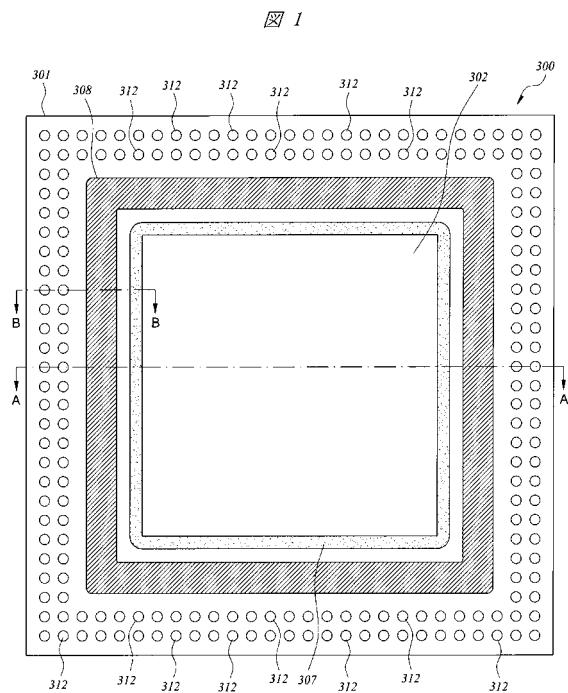

【図1】本発明の実施の形態であるPOP型半導体装置の第1半導体パッケージを示す平面図である。 40

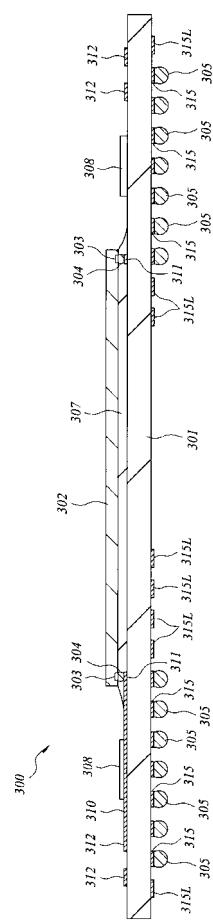

【図2】図1のA-A線に沿った第1半導体パッケージの断面図である。

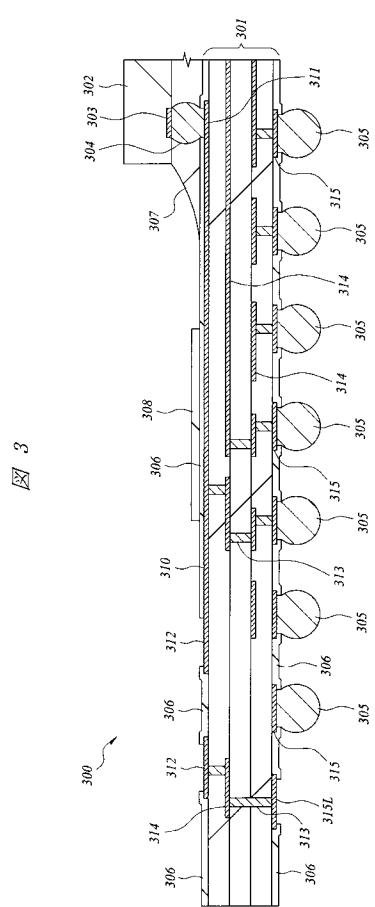

【図3】図1のB-B線に沿った第1半導体パッケージの要部拡大断面図である。

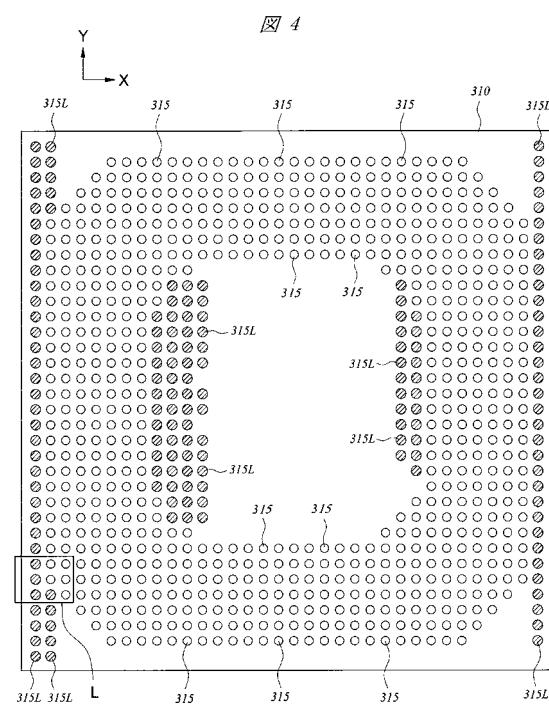

【図4】第1半導体パッケージの配線基板に形成された下面側ランドおよびテスト用ランドのレイアウトを示す平面図である。

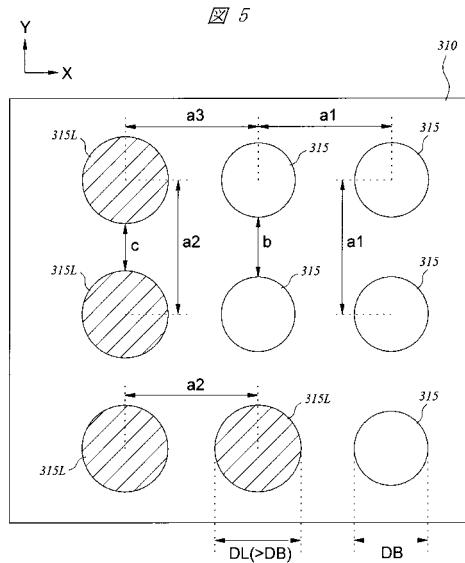

【図5】図4の一部を拡大して示す平面図である。

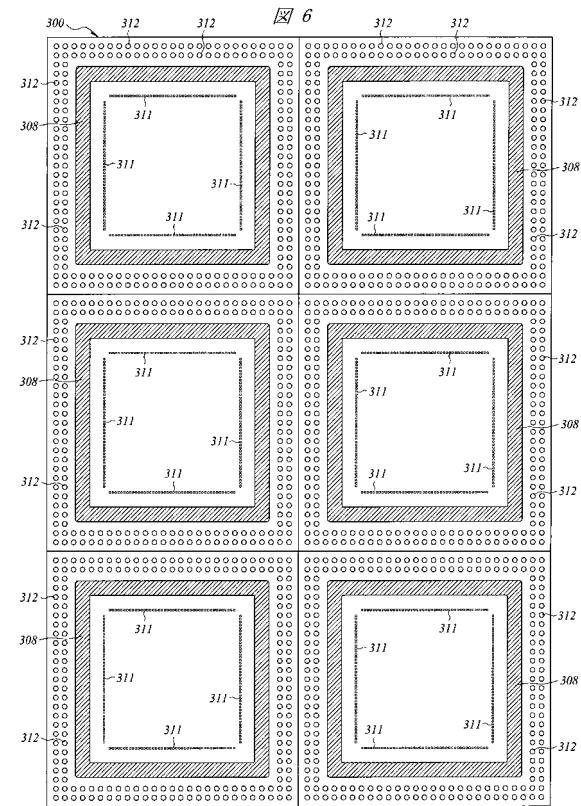

【図6】第1半導体パッケージの製造に用いるマトリクス基板の上面を示す平面図である。

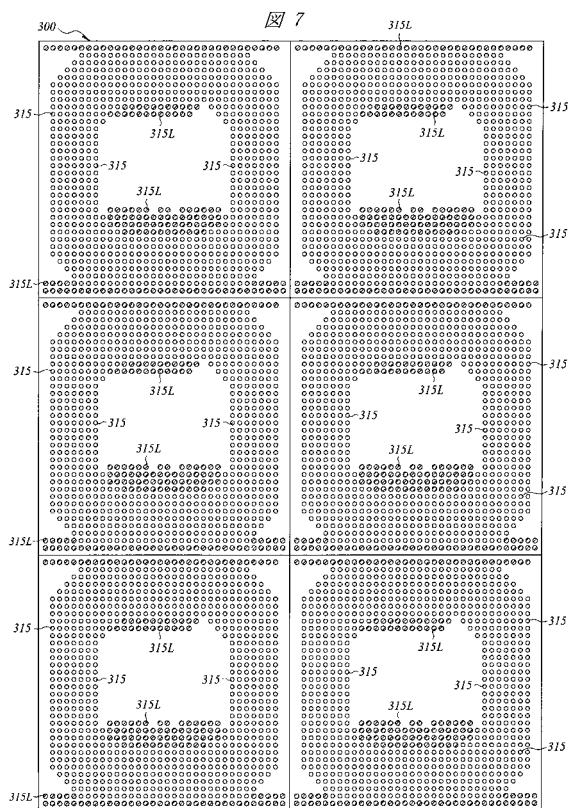

【図7】第1半導体パッケージの製造に用いるマトリクス基板の下面を示す平面図である。

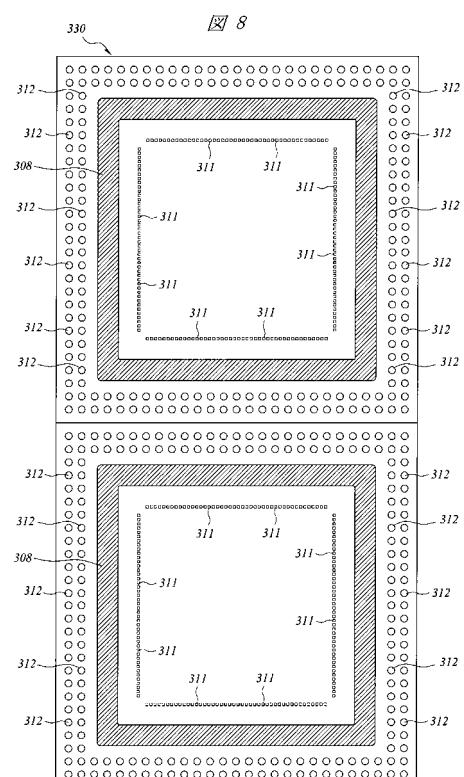

【図8】図6の一部を拡大して示す平面図である。 50

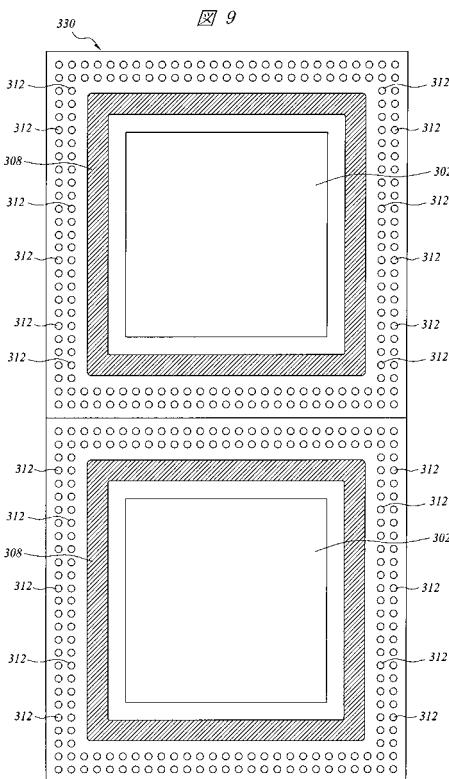

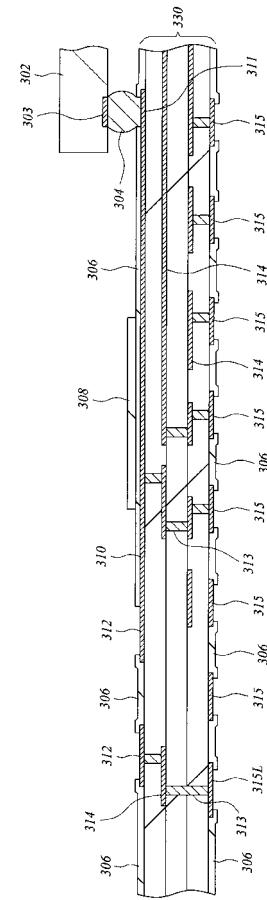

【図9】第1半導体パッケージの製造方法を示すマトリクス基板の一部拡大平面図である。

【図10】第1半導体パッケージの製造方法を示すマトリクス基板の一部拡大断面図である。

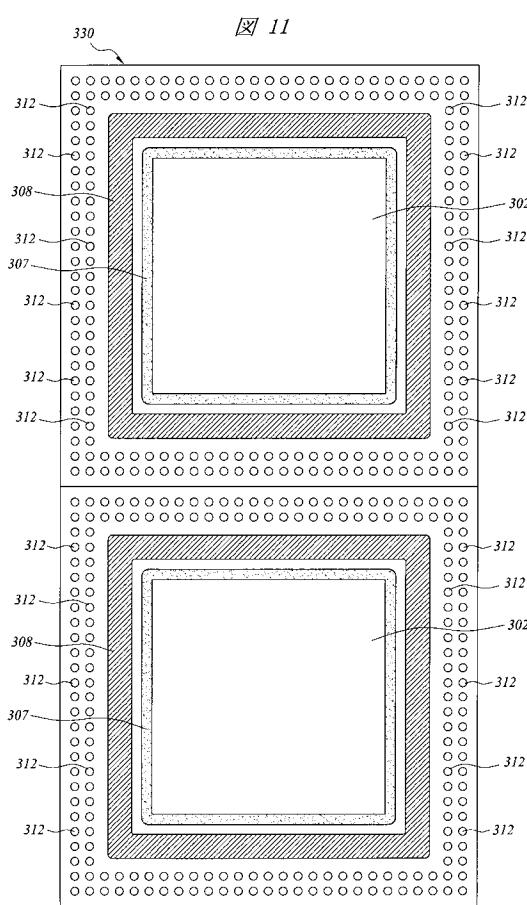

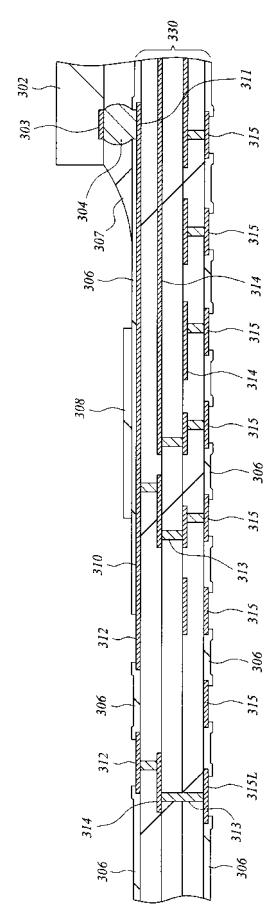

【図11】第1半導体パッケージの製造方法を示すマトリクス基板の一部拡大平面図である。

【図12】第1半導体パッケージの製造方法を示すマトリクス基板の一部拡大断面図である。

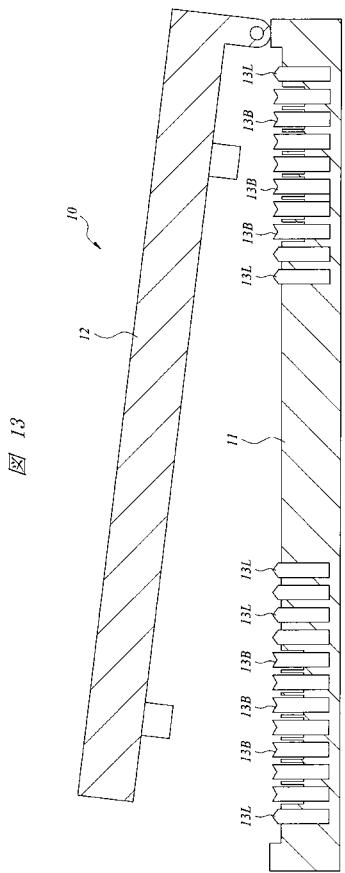

【図13】第1半導体パッケージの電気特性検査に用いるプローブソケットの要部を示す概略断面図である。

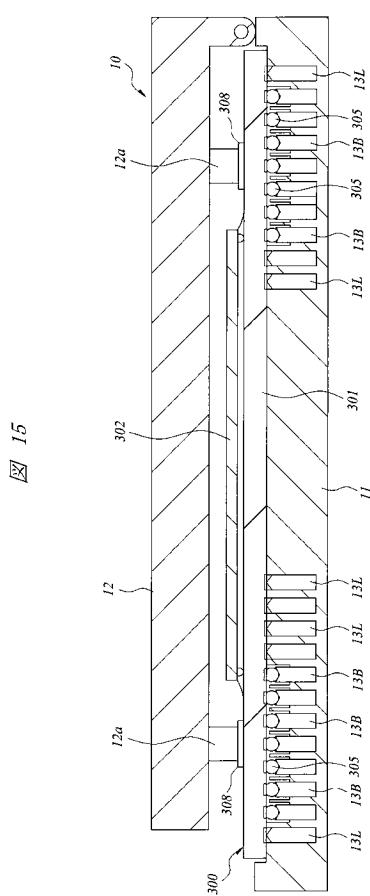

【図14】図13に示すプローブソケットに内蔵されたコンタクトピンの要部を示す概略断面図である。

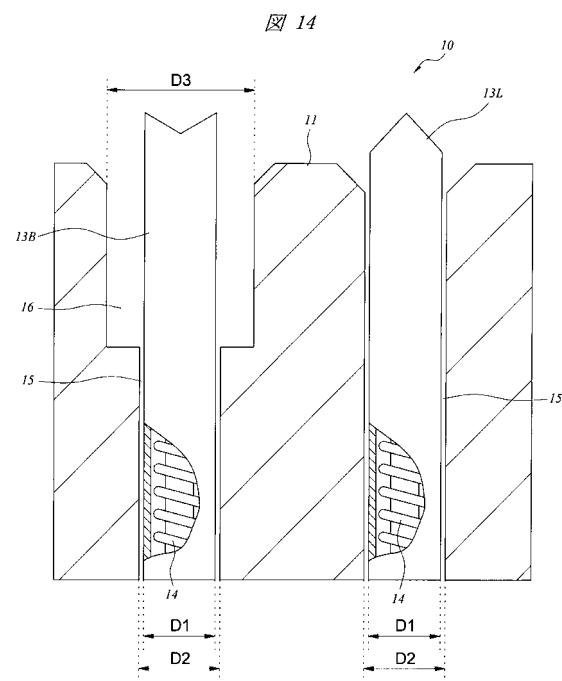

【図15】第1半導体パッケージをプローブソケットに装着した状態を示す概略断面図である。

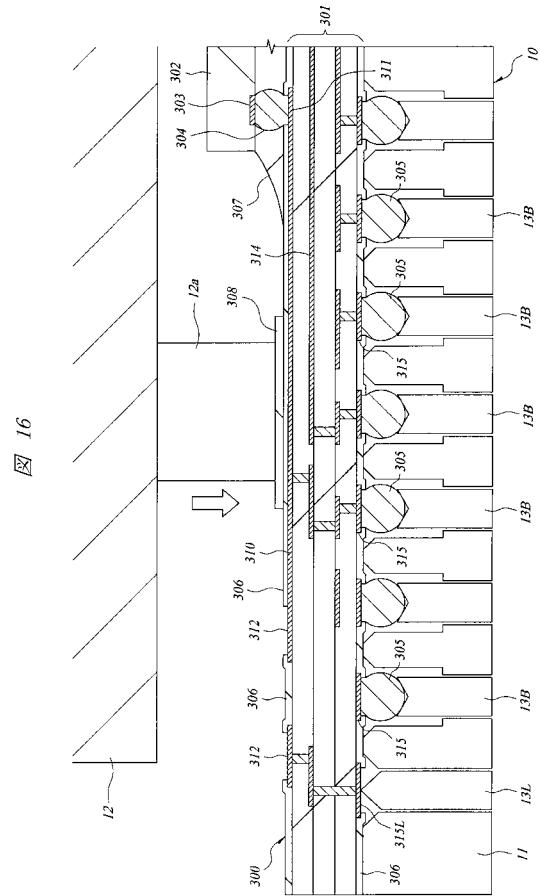

【図16】プローブソケットのキャップに設けられた凸部と配線基板のダムとの接触部を示す拡大断面図である。

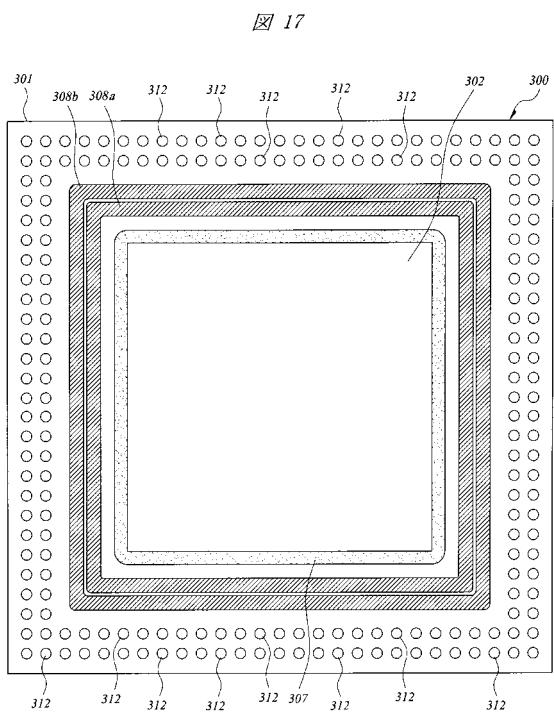

【図17】第1半導体パッケージの配線基板上に設けられたダムの別例を示す平面図である。

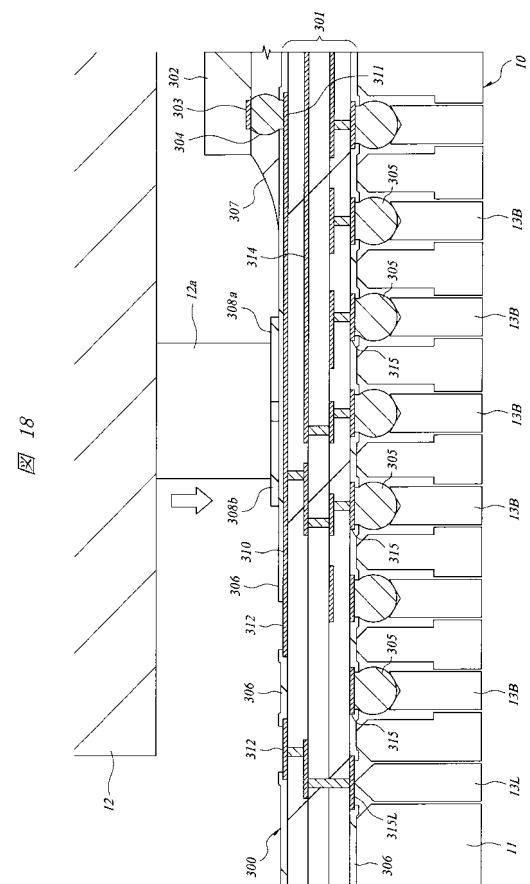

【図18】プローブソケットのキャップに設けられた凸部と図17に示すダムとの接触部を示す拡大断面図である。

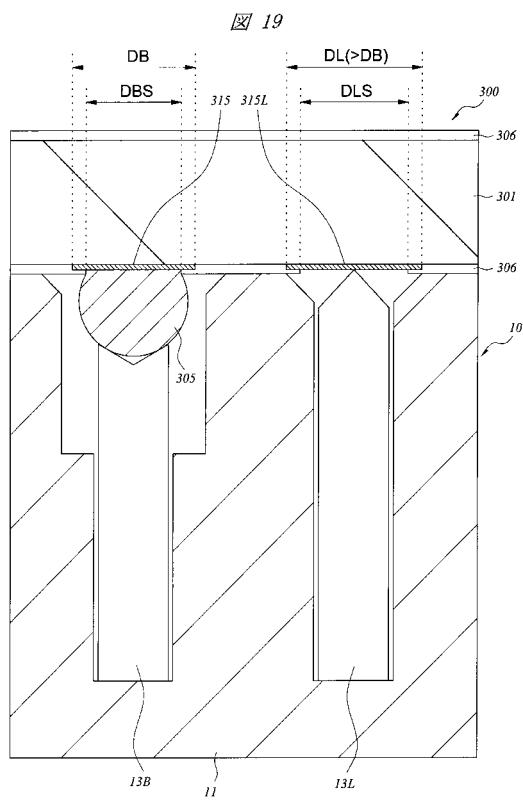

【図19】配線基板の下面側ランドに接続された半田ボールとボール接続用コンタクトピンとの接触部およびテスト用ランドとランド接続用コンタクトピンとの接触部を示す概略断面図である。

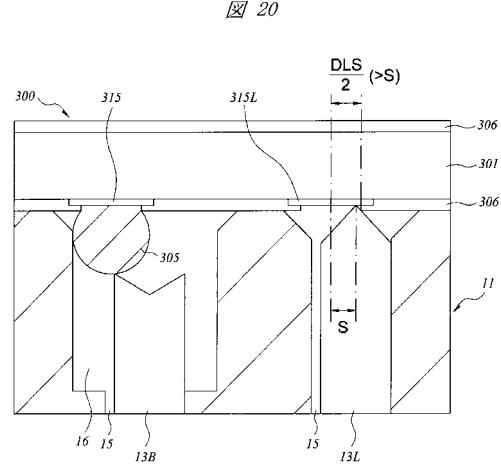

【図20】ランド接続用コンタクトピンとテスト用ランドの位置ずれ量が最大になった状態を示す説明図である。

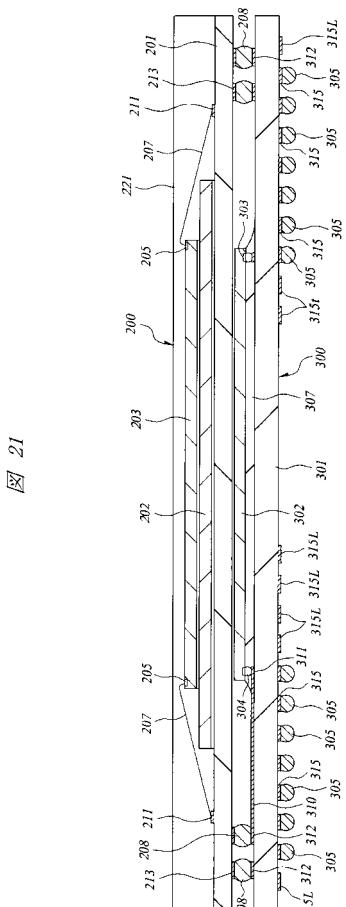

【図21】本発明の実施の形態であるPOP型半導体装置の全体構成を示す断面図である。

【図22】配線基板の下面に形成されるテスト用ランドの別例を示す平面図である。

【図23】第1半導体パッケージの別例を示す平面図である。

【図24】第1半導体パッケージの別例を示す要部拡大断面図である。

【図25】本発明者らが検討したPOP型半導体装置の全体構成を示す断面図である。

【図26】図25に示すPOP型半導体装置の第2配線基板を示す平面図である。

【図27】図26のC-C線に沿った断面図である。

【図28】(a)、(b)は、図25に示すPOP型半導体装置の第1配線基板に形成されたランドとプローブ針との接触部を示す概略断面図である。

【図29】図25に示すPOP型半導体装置の第1配線基板に形成されたランド接続用コンタクトピンランドとプローブ針との接触不良状態を示す概略断面図である。

【図30】本発明の実施の形態の変形例であるBGA型半導体装置の全体構成を示す断面図である。

【発明を実施するための形態】

【0044】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なときを除き、同一または同様な部分の説明を原則として繰り返さない。また、以下の実施の形態を説明する図面においては、構成を分かり易くするために、平面図であってもハッチングを付す場合がある。

【0045】

本実施の形態は、コントローラ系チップが搭載された第1半導体パッケージ(第1半導体装置、下段側パッケージ)の上部に、メモリ系チップが搭載された第2半導体パッケージ(第2半導体装置、上段側パッケージ)を積層してシステムを構成するPOP型半導体

10

20

30

40

50

装置に適用したものである。

【0046】

<第1半導体パッケージ(第1半導体装置)>

図1は、POP型半導体装置の第1半導体パッケージを示す平面図、図2は、図1のA-A線に沿った第1半導体パッケージの断面図、図3は、図1のB-B線に沿った第1半導体パッケージの要部拡大断面図である。

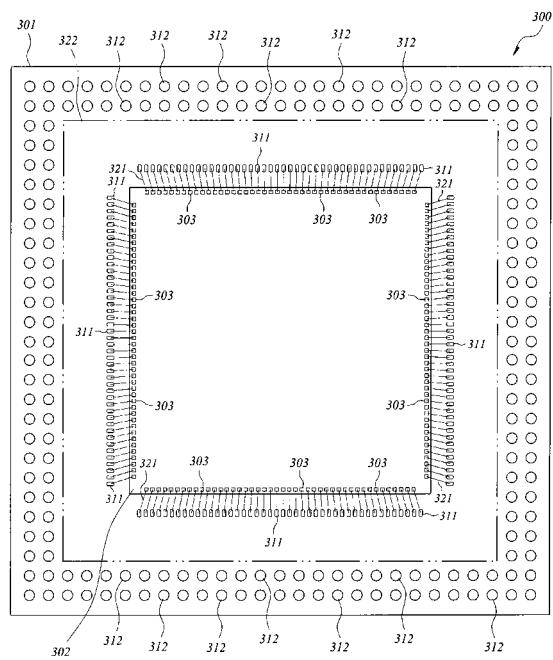

【0047】

POP型半導体装置の下段側パッケージを構成する第1半導体パッケージ300は、配線基板301と、この配線基板301の上面の中央部に搭載されたコントローラチップ(第1半導体チップ)302とを備えている。

10

【0048】

配線基板301は、例えばガラスエポキシ樹脂のような汎用樹脂と配線層とを主体として構成された多層配線基板であり、その平面形状は、例えば四角形(正方形)である。配線基板301の上面(表面、正面)には複数の配線310が形成されており、これらの配線310のそれぞれの一端がボンディングリード(電極パッド)311を構成し、他端が上面側ランド(電極パッド)312を構成している。なお、図1は複数の配線310のそれぞれの他端(上面側ランド312)のみを図示している。

【0049】

図3に示すように、配線基板301の上面は、複数の配線310のそれぞれの一端(ボンディングリード311)の表面および他端(上面側ランド312)の表面を除き、配線310を保護するための絶縁性樹脂被膜であるソルダレジスト306によって被覆されている。このソルダレジスト306から露出したボンディングリード311の表面および上面側ランド312の表面には、例えばニッケル(Ni)層の上にAu層を積層した2層の金属膜からなるメッキ層(図示せず)が形成されている。

20

【0050】

配線基板301の下面(裏面)には、複数の下面側ランド(ボール搭載用ランド)315および複数のテスト用ランド315Lが形成されている。下面側ランド315およびテスト用ランド315Lのそれぞれは、配線基板301の内部に形成された複数のビア配線313および複数層(例えば2層)の内部配線314を介して、配線基板301の上面の配線310に電気的に接続されている。すなわち、配線基板301は、その上面の配線310を第1配線層、下面側ランド315およびテスト用ランド315Lを第2配線層、2層の内部配線314を第3および第4配線層とする4層配線基板である。これら4層の配線(配線310、内部配線314、下面側ランド315、テスト用ランド315L)およびそれらを接続するビア配線313は、例えば銅(Cu)のような低抵抗金属からなる。また、配線基板301の下面は、下面側ランド315の表面およびテスト用ランド315Lの表面を除き、ソルダレジスト306によって被覆されている。

30

【0051】

配線基板301の下面に形成された下面側ランド315には、半導体装置と外部電子機器との間で信号および電源電位(又は基準電位)の入出力を行うための外部端子(伝導経路)が接続(形成)されている。本実施の形態では、この外部端子は導電性部材から成り、例えば半田ボール(以後、半田ボール305と呼ぶ)である。POP型半導体装置は、これらの半田ボール305をマザーボード(実装基板)の電極パッドと接続し、この半田ボール305を介してデジタルカメラや携帯電話のような外部電子機器のマザーボード(実装基板)に実装される。半田ボール305は、例えば錫(Sn)単体、またはSnに少量のビスマス(Bi)、亜鉛(Zn)、銀(Ag)、Cuのいずれかを添加したSn合金などからなる。

40

【0052】

配線基板301の下面に形成されたテスト用ランド315Lは、第1半導体パッケージ(組立体)300の完成後に行われる電気特性検査時にのみ使用される端子である。すなわち、テスト用ランド315Lは、POP型半導体装置を外部電子機器のマザーボードに

50

実装する顧客が使用しない端子である。そのため、テスト用ランド 315L の表面には半田バンプが接続されておらず、平坦な LGA 構成となっている。なお、テスト用ランド 315L を使用した第 1 半導体パッケージ 300 の電気特性検査については後述する。

#### 【0053】

配線基板 301 の上面に搭載されたコントローラチップ 302 は、平面形状がほぼ正方形の単結晶シリコン基板からなる。このコントローラチップ 302 は、その正面（集積回路形成面）が配線基板 301 の上面と対向するように、配線基板 301 の上面の中央部にフェイスダウン実装されている。コントローラチップ 302 の正面の周辺部には複数の電極パッド 303 が形成されている。図示はしないが、これらの電極パッド 303 の内側のシリコン基板には、第 1 半導体パッケージ 300 の上に積層される第 2 半導体パッケージのメモリチップを制御するための制御回路が形成されている。

10

#### 【0054】

コントローラチップ 302 の正面に形成された電極パッド 303 と、配線基板 301 の上面に形成された配線 310 の一端（ボンディングリード 311）とは、半田ボール 304 を介して電気的に接続されている。すなわち、コントローラチップ 302 は、半田ボール 304 を介して配線基板 301 の上面にフリップチップ実装されている。半田ボール 304 は、配線基板 301 の下面側ランド 315 に接続された半田ボール 305 と同じく、Sn に少量の Bi、Zn、Ag、Cu を添加した Sn 合金などからなるが、その融点は半田ボール 305 のそれよりも高い。

20

#### 【0055】

配線基板 301 の上面とコントローラチップ 302 の正面との間には、コントローラチップ 302 の正面を保護するためのアンダーフィル樹脂 307 が充填されている。アンダーフィル樹脂 307 は、コントローラチップ 302 と配線基板 301 との熱膨張係数差に起因して両者の界面に加わる熱応力を緩和する機能も備えている。アンダーフィル樹脂 307 は、例えば一液型熱硬化性エポキシ樹脂からなる。

#### 【0056】

配線基板 301 の上面に搭載されたコントローラチップ 302 の外周近傍には、四角枠状の平面形状を有するダム 308 が設けられている。コントローラチップ 302 の周囲を囲むように配置されたこのダム 308 は、配線基板 301 の上面とコントローラチップ 302 の正面との間に液状のアンダーフィル樹脂 307 を供給した際、このアンダーフィル樹脂 307 が配線基板 301 の上面の周辺部に拡散し、配線 310 の端部（上面側ランド 312）の表面を覆うのを防ぐために形成されている。ダム 308 は、配線基板 301 の上面を覆うソルダレジスト 306 と同じ材料（例えばエポキシ樹脂）からなる絶縁性樹脂被膜であり、図 3 に示すように、ソルダレジスト 306 の上面に接合されている。

30

#### 【0057】

図 4 は、配線基板 301 の下面に形成された下面側ランド 315 およびテスト用ランド 315L のレイアウトを示す平面図である。なお、下面側ランド 315 に接続されている半田ボール 305 の図示は省略する。また、下面側ランド 315 と区別するために、テスト用ランド 315L にはハッチングを付している。

40

#### 【0058】

図 4 に示すように、下面側ランド 315 およびテスト用ランド 315L は、配線基板 301 の下面にアレイ状に配置されている。このうち、下面側ランド 315 は、配線基板 301 の中央部から各辺に向かう方向、すなわち図の X 方向（配線基板 301 の一辺に平行な方向）およびこれと直交する Y 方向に沿って、主として 7 列に配置されている。一方、テスト用ランド 315L は、主として配線基板 301 の中央部近傍（下面側ランド列の内側）と最外周部（下面側ランド列の外側）とに配置されている。

#### 【0059】

図示は省略するが、本実施の形態の第 1 半導体パッケージ 300 の上に積層される第 2 半導体パッケージは、配線基板と、この配線基板の上面に搭載された 2 枚のメモリチップとを備えている。2 枚のメモリチップの一方は DRAM が形成されたチップであり、もう

50

一方はフラッシュメモリが形成されたチップである。

【0060】

そして、配線基板301の下面に形成されたテスト用ランド315Lのうち、配線基板301の中央部近傍（下面側ランド列の内側）に配置されたテスト用ランド315Lは、主としてフラッシュメモリチップインターフェース用ランドを構成している。一方、配線基板301の最外周部（下面側ランド列の外側）に配置されたテスト用ランド315Lは、主としてDRAMチップインターフェース用ランドを構成している。また、配線基板301の内部に形成されたビア配線313のうち、配線基板301の中央部寄りに配置されたビア配線313は、主としてフラッシュメモリチップインターフェース用ビア配線を構成し、配線基板301の外周部寄りに配置された下面側ランド315は、主としてDRAMチップインターフェース用ビア配線を構成している。 10

【0061】

一般に、DRAMの駆動周波数は、フラッシュメモリの駆動周波数よりも高い。そのため、コントローラチップ302からDRAMチップインターフェース用ランドに至る経路の配線長が長くなると、その分、配線のインピーダンス成分が増加し、かつ配線が不要ノイズを拾う可能性も高くなるので、POP型半導体装置の信頼性（電気特性）が低下する恐れがある。これに対し、上記のように、DRAMチップインターフェース用ランドを配線基板301の最外周部に配置し、かつDRAMチップインターフェース用のビア配線313を配線基板301の外周部寄りに配置した場合は、配線基板301の上面に搭載されたコントローラチップ302からDRAMチップインターフェース用のテスト用ランド315Lに至る経路の配線長が最短化されるので、上記した不具合が回避される。 20

【0062】

図5は、図4の実線で囲んだ矩形の領域Lを拡大して示す平面図である。図5に示すように、下面側ランド315同士のピッチa1、テスト用ランド315L同士のピッチa2、下面側ランド315とテスト用ランド315Lとのピッチa3は、いずれも同一（a1=a2=a3）であり、例えばそれぞれ0.4mmである。すなわち、下面側ランド315およびテスト用ランド315Lのそれぞれは、X方向およびY方向に沿って、互いに等しいピッチで配置されている。

【0063】

また、上記X方向およびY方向に沿った下面側ランド315同士の間隔bは、例えばそれぞれ0.1mmである。これに対し、X方向およびY方向に沿ったテスト用ランド315L同士の間隔cは、例えばそれぞれ0.07mmである。すなわち、本実施の形態の配線基板301は、テスト用ランド315Lの直径DLが、下面側ランド315（半田ボール305が接続される外部端子）の直径DBよりも大きい。テスト用ランド315Lの直径DLは、例えば0.33mmであり、下面側ランド315の直径DBは、例えば0.3mmである。テスト用ランド315Lの直径DLを下面側ランド315の直径DBよりも大きくした効果については、後述する。 30

【0064】

＜第1半導体パッケージの製造方法＞

次に、上記のように構成された第1半導体パッケージ300の製造方法について、図6～図12を参照しながら説明する。 40

【0065】

図6は、第1半導体パッケージ300の製造に用いるマトリクス基板（大型配線基板）330の上面（表面）を示す平面図、図7は、マトリクス基板330の下面（裏面）を示す平面図、図8は、図6の一部（配線基板2個分の領域）を拡大して示す平面図である。

【0066】

マトリクス基板330は、前述した配線基板301の導体パターン（配線310、ボンディングリード311、上面側ランド312、ビア配線313、内部配線314、下面側ランド315、テスト用ランド315L）を繰り返し形成した構造を有している。マトリクス基板330は、第1半導体パッケージ300の配線基板301の母体となる基板である。 50

り、これをダイシングすることにより、多数（例えば6個）の配線基板301が得られるようになっている。

【0067】

第1半導体パッケージ300を製造するには、まず、図9および図10に示すように、マトリクス基板330の上面にコントローラチップ302を搭載し、あらかじめコントローラチップ302の電極パッド303に接続しておいた半田ボール（パンプ電極）304をボンディングリード311上に位置決めする。続いて、マトリクス基板330を加熱炉内で加熱し、半田ボール304をリフローさせることにより、半田ボール304と電極パッド303とを接続する。

【0068】

次に、図11および図12に示すように、マトリクス基板330の上面とコントローラチップ302の正面との間に液状のアンダーフィル樹脂307を供給し、続いて、マトリクス基板330を加熱炉内で加熱してアンダーフィル樹脂307を硬化させる。

【0069】

その後、マトリクス基板330の下面の下面側ランド315に半田ボール305を接続し、続いてマトリクス基板330を加熱炉内で加熱して半田ボール305をリフローさせた後、マトリクス基板330をダイシングすることにより、前記図1～図3に示した第1半導体パッケージ300が得られる。

【0070】

＜第1半導体パッケージの電気特性検査＞

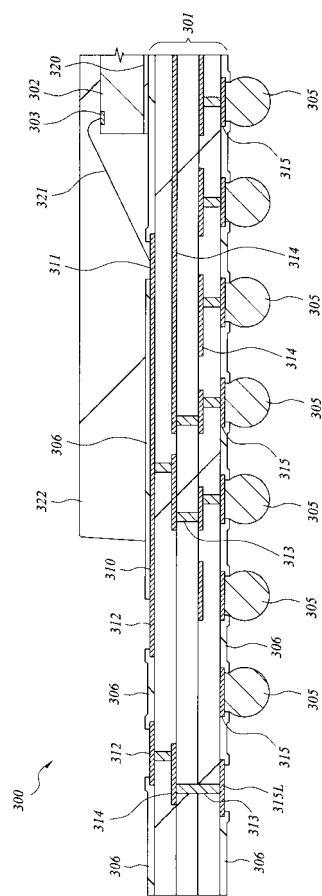

次に、上記のような方法で製造された第1半導体パッケージ（組立体）300の電気特性検査を行う。図13は、第1半導体パッケージ300の電気特性検査に用いるプローブソケット10の要部を示す概略断面図、図14は、図13に示すプローブソケット10に内蔵されたコンタクトピン（ボール接続用コンタクトピン13Bおよびランド接続用コンタクトピン13L）の要部を示す概略断面図である。

【0071】

図13に示すように、プローブソケット10は、ソケット本体11と、このソケット本体11に開閉可能に取り付けられたキャップ12とを備えており、ソケット本体11には、複数個のボール接続用コンタクトピン13Bと複数個のランド接続用コンタクトピン13Lとが内蔵されている。

【0072】

ボール接続用コンタクトピン（第1コンタクトピン）13Bは、第1半導体パッケージ300の配線基板301の下面側ランド315に取り付けられた半田ボール305と接触するプローブ針であり、ランド接続用コンタクトピン13Lは、テスト用ランド315Lと接触するプローブ針である。ボール接続用コンタクトピン13Bの数は、配線基板301の下面に形成された下面側ランド315の数と同じであり、ランド接続用コンタクトピン（第2コンタクトピン）13Lの数は、テスト用ランド315Lの数と同じである。

【0073】

図14に示すように、ボール接続用コンタクトピン13Bとランド接続用コンタクトピン13Lのそれぞれは、金属製の管の中に収納されたコイルバネ14の弾性力によってピンガイド15内を上下動するポゴピン（POGO pin）構造を有している。また、ボール接続用コンタクトピン13Bとランド接続用コンタクトピン13Lのそれぞれの下端部は、ソケット本体11に内蔵された図示しないコンタクトプローブに接続されている。このとき、図14に示すように、それぞれのコンタクトピン13B, 13Lは、それぞれのピンガイド15内において上下動を可能するために、ピンガイド15の内壁面とコンタクトピン13B, 13Lの表面との間に隙間が設けられている。

【0074】

ボール接続用コンタクトピン13Bの先端部（上端部）の形状は、球状の半田ボール305と多点で接触する、いわゆるクラウン形状になっている。詳細に説明すると、ボール接続用コンタクトピン13Bの先端部（上端部）の平面形状（図28において、下面側ラ

10

20

30

40

50

ンド 115 側から見たコンタクトピン 13B の平面形状) が円形から成り、複数の突起はこの先端部の周縁部に沿って配置(形成)されている。このように、ボール接続用コンタクトピン 13B の先端部(上端部)の形状を、所謂、クラウン形状にすることで、球状の半田ボール(バンブ電極) 305 との接触点(接触面積)を増やすことができる。一方、ランド接続用コンタクトピン 13L の先端部(上端部)の形状は、平坦なテスト用ランド 315L と一点で接触する、いわゆる一本針形状になっている。詳細に説明すると、ランド接続用コンタクトピン 13L の先端部(上端部)の平面形状(図 28 において、テスト用ランド 115L 側から見たコンタクトピン 13L の平面形状)は円形から成り、針の頂点はこのランド接続用コンタクトピン 13L の先端部(上端部)の中央部に配置されている。言い換えると、1 つの突起がランド接続用コンタクトピン 13L の先端部(上端部)の中央部に形成されている。なお、図に示したボール接続用コンタクトピン 13B の先端部は、半田ボール 305 と 2 点で接触する形状になっているが、半田ボール 305 と 3 点以上で接触する形状であってもよいことは勿論である。 10

#### 【0075】

上記プローブソケット 10 を使用して第 1 半導体パッケージ 300 の電気特性検査を行う際は、図 15 に示すように、第 1 半導体パッケージ 300 をソケット本体 11 の上面に位置決めし、配線基板 301 の上面を上方からキャップ 12 で押さえ付けることによって、ソケット本体 11 の上面に固定する。詳細に説明すると、図 15 に示すように、ソケット本体 11 の上面には、凹部(収納部)が形成されており、第 1 半導体パッケージ 300 の下面がこのソケット本体 11 の凹部における底面と対向するように、第 1 半導体パッケージ 300 をこのソケット本体 11 の凹部内に配置する。 20

#### 【0076】

このように、第 1 半導体パッケージ 300 の電気特性検査を行う間、配線基板 301 の上面を上方からキャップ 12 で押さえ付けておくことにより、配線基板 301 上に搭載されたコントローラチップ 302 の発熱などに起因する配線基板 301 の反りが抑制される。これにより、配線基板 301 の反りに起因するランド(下面側ランド 315 およびテスト用ランド 315L) とプローブ針(ボール接続用コンタクトピン 13B およびランド接続用コンタクトピン 13L)との位置合わせ精度の低下を抑制することができる。 20

#### 【0077】

また、配線基板 301 の上面をキャップ 12 で押さえ付ける際には、キャップ 12 との接触による配線基板 301 の上面の損傷を防ぐために、キャップ 12 の下面に平坦な底面を有する凸部 12a を設け、この凸部 12a の底面を配線基板 301 の上面に形成されたダム 308 と接触させる。図 15 には示さないが、この凸部 12a は、配線基板 301 の上面のダム 308 と同様、四角柱状の平面形状を有している。 30

#### 【0078】

図 16 は、キャップ 12 の凸部 12a と配線基板 301 のダム 308 との接触部を示す拡大断面図である。図 16 に示すように、ダム 308 の幅は、キャップ 12 の下面に設けられた凸部 12a とダム 308 とが接触する領域、すなわち凸部 12a の底面の幅よりも広くすることが望ましい。このようにすると、凸部 12a の底面全体がダム 308 の上面と接触するので、ダム 308 の上面に対して均等な押圧力を印加することができる。他方、ダム 308 の幅を凸部 12a の幅よりも狭くした場合には、凸部 12a の底面の一部がダム 308 の上面と非接触になり、ダム 308 の上面に印加される押圧力が不均等になることがある。 40

#### 【0079】

また、配線基板 301 の上面にダム 308 を設ける際には、配線基板 301 の上面において、配線基板 301 の中央部から一辺に向かう方向に沿って複数列に亘って配列された半田ボール列の中央部(中央近傍)と平面的に重なる位置にダム 308 を配置することが望ましい。図 16 に示す例では、7 列に配置された半田ボール列の中央に位置する半田ボール 305 の上方にダム 308 を配置している。これにより、キャップ 12 の凸部 12a および配線基板 301 を介して複数の半田ボール列のそれぞれに印加される押圧力をほぼ 50

均等にすることができる。

【0080】

前述したように、配線基板301の上面にダム308を設ける目的の一つは、配線基板301の上面とコントローラチップ302の正面との間に供給した液状のアンダーフィル樹脂307が配線基板301の周辺部に広がることを防止することにある。そのため、例えば図17に示すように、アンダーフィル樹脂307の広がり防止効果を高める目的で、コントローラチップ302の周囲を2つのダム308a、308bで二重に囲む場合もある。この場合においても、図18に示すように、2つのダム308a、308bの幅を凸部12aの幅をよりも広くし、凸部12aの底面全体をダム308a、308bの上面と接觸させることにより、ダム308a、308bの上面に対して均等な押圧力を印加することができる。10

【0081】

なお、前述した第1半導体パッケージ300の製造方法において、マトリクス基板330の上面とコントローラチップ302の正面との間に液状のアンダーフィル樹脂307を供給する工程（図11、図12参照）では、コントローラチップ302とその周囲を囲むダム308との狭い隙間にディスペンサノズルの先端を挿入し、コントローラチップ302の一辺または二辺に沿ってディスペンサノズルを移動させながらアンダーフィル樹脂307を供給する。そのため、ダム308の幅を前述した凸部12aの幅よりも広くすると、コントローラチップ302とダム308との隙間がさらに狭くなり、この隙間にディスペンサノズルの先端を挿入することができなくなる場合がある。このような場合は、コントローラチップ302を囲むダム308の四辺のうち、対向する二辺のみ幅を広くしてもよい。20

【0082】

また、ダム308の外側の領域には、配線310の一端を構成する複数の上面側ランド312が配置されているが、上面側ランド312の数によってはダム308の幅を広げることが困難が場合がある。このような場合も、コントローラチップ302を囲むダム308の四辺のうち、対向する二辺のみ幅を広くすればよい。

【0083】

図19は、配線基板301の下面側ランド315に接続された半田ボール305とボール接続用コンタクトピン13Bとの接觸部、およびテスト用ランド315Lとランド接続用コンタクトピン13Lとの接觸部を示す概略断面図である。30

【0084】

ここで、各部材の寸法の一例を示すと、下面側ランド315の直径DBおよびテスト用ランド315Lの直径DLは、前述したように、例えばDB=0.3mmおよびDL=0.33mmである。また、テスト用ランド315Lおよび下面側ランド315のそれぞれの周辺部はソルダレジスト306で覆われているので、実際に配線基板301の下面に露出している領域の径を開口径と定義すると、下面側ランド315の開口径DBSは、例えば0.23mmであり、テスト用ランド315Lの開口径DLSは、例えば0.27mmである。

【0085】

一方、ボール接続用コンタクトピン13Bとランド接続用コンタクトピン13Lのそれぞれの直径D1は、例えば0.15mmであり、ピンガイド15の直径D2は、例えば0.19mmである。また、ボール接続用コンタクトピン13Bが挿入されるピンガイド15の先端部近傍（ボールガイド16）の直径D3は、半田ボール305の径を例えば0.25mmとしたとき、例えば0.35mmである。40

【0086】

ここで、ボール接続用コンタクトピン13Bと半田ボール305との位置ずれ量、およびランド接続用コンタクトピン13Lとテスト用ランド315Lとの位置ずれ量がいずれも0である場合には、図19に示すように、ボール接続用コンタクトピン13Bの中心が半田ボール305の中心と一致し、ランド接続用コンタクトピン13Lの中心がテスト用

ランド315Lの中心と一致する。

【0087】

しかし、実際の配線基板301の下面に形成された下面側ランド315の位置およびテスト用ランド315Lの位置は、配線基板301の加工ばらつきのために、設計上の位置からずれていることがある。同様に、実際のソケット本体11に設けられたボール接続用コンタクトピン13Bの位置およびランド接続用コンタクトピン13Lの位置は、ソケット本体11の加工ばらつきのために、設計上の位置からずれていることがある。さらに、第1半導体パッケージ300をプローブソケット10に装着して電気特性検査を行うと、配線基板301に搭載されたコントローラチップ302の発熱のために、配線基板301に反りが発生し、特に配線基板301の周辺部近傍において、ボール接続用コンタクトピン13Bと半田ボール305との位置ずれ、およびランド接続用コンタクトピン13Lとテスト用ランド315Lとの位置ずれが発生する。

10

【0088】

そのため、POP型半導体装置の小型化に伴って配線基板301の外形寸法が小さくなり、配線基板301の下面に形成されるランド（下面側ランド315およびテスト用ランド315L）の径およびランド間ピッチが小さくなると、前述したように、特に、半田ボール305が接続されていないテスト用ランド315Lとランド接続用コンタクトピン13Lとの間に接触不良が発生し易くなる。

【0089】

そこで、本実施の形態の第1半導体パッケージ300は、配線基板301の下面に形成されたテスト用ランド315Lの直径DLを下面側ランド315の直径DBより大きくしている。これにより、テスト用ランド315Lの開口径DLSも下面側ランド315の開口径DBSより大きくなるので、配線基板301の外形寸法が縮小され、ランド（下面側ランド315およびテスト用ランド315L）の径およびランド間ピッチが小さくなつても、テスト用ランド315Lとランド接続用コンタクトピン13Lとの接触不良の発生を抑制することができる。

20

【0090】

図20は、上記した配線基板301およびソケット本体11の加工ばらつきや、配線基板301に反りなどによって、ランド接続用コンタクトピン13Lとテスト用ランド315Lの位置ずれ量が最大になった状態を示している。そこで、この状態におけるテスト用ランド315Lの中心からランド接続用コンタクトピン13Lの先端までの距離を上記した位置ずれ量の最大値Sと定義すると、テスト用ランド315Lの開口部の半径（DLS/2）を位置ずれ量の最大値Sよりも大きくすることにより、テスト用ランド315Lとランド接続用コンタクトピン13Lとの非接触を確実に防止することができる。

30

【0091】

なお、下面側ランド315に接続された半田ボール305は、配線基板301の下面よりも下方に突出しており、かつボール接続用コンタクトピン13Bの先端部（上端部）の形状は、球状の半田ボール305と多点で接触する、いわゆるクラウン形状になっている。そのため、たとえ半田ボール305の開口部の半径（DBS/2）が上記した位置ずれ量の最大値Sよりも小さくなつた場合でも、両者が非接触状態になることはない。

40

【0092】

次に、この状態で第1半導体パッケージ300に対する各種の電気特性検査を行う。この電気特性検査は、例えば配線基板301上のコントローラチップ302からテスト用ランド315Lに至る配線経路の導通／非導通を確認する検査、コントローラチップ302に対するAC/DCテスト、コントローラチップ302から半田ボール305に至る配線経路の導通／非導通を確認する検査などを含んでいる。

【0093】

本実施の形態によれば、POP型半導体装置の小型化に伴って配線基板301の外形寸法が小さくなつた場合でも、テスト用ランド315Lを使った第1半導体パッケージ300の電気特性検査を精度よく行うことができるので、POP型半導体装置の小型化を推進

50

することができる。

【0094】

このようにして、前記マトリクス基板330から取得した複数個の第1半導体パッケージ(組立体)300のそれぞれに対して上記の電気特性検査を行い、良品の第1半導体パッケージ300を選別した後、良品の第1半導体パッケージ300上に、例えば前記図25～図27に示した第2半導体パッケージ(組立体)200を積層することによって、本実施の形態のPOP型半導体装置を取得することができる。

【0095】

図21は、組み立てが完了したPOP型半導体装置の全体構成を示す断面図である。POP型半導体装置の第1半導体パッケージ300上に積層する第2半導体パッケージ200の構成については前述したので、その繰り返しの説明は省略する。また、第2半導体パッケージ200を第1半導体パッケージ300上に積層する方法は、第2半導体パッケージ200を前述した第1半導体パッケージ100上に積層する方法と同じでよいので、その説明は省略する。

【0096】

なお、上記POP型半導体装置の組み立て方法としては、半導体製造メーカーが第1半導体パッケージ300上に第2半導体パッケージ200を積層し、完成品として出荷する方式と、半導体製造メーカーから第1半導体パッケージ300を購入した顧客が、電子機器製品の用途に応じて選定した第2パッケージ200を第1半導体パッケージ300上に積層する方式とがある。

【0097】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0098】

例えば、前記実施の形態では、第1半導体パッケージ300の配線基板301の上面に搭載されたコントローラチップ302は、導電性部材として、半田ボール(バンプ電極)304を介して配線基板301の電極パッドと電気的に接続したが、ワイヤを介して配線基板301の電極パッドと電気的に接続してもよい。なお、ワイヤの材料は、例えば金(Au)である。

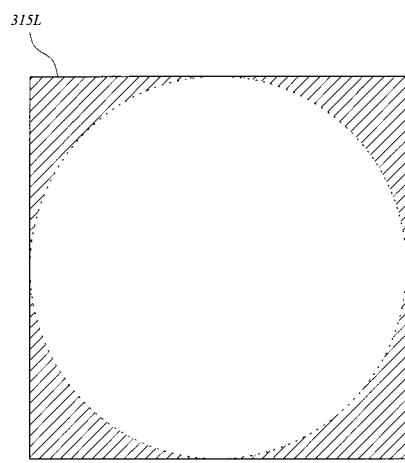

【0099】

また、図22に示すように、配線基板301の下面に形成されるテスト用ランド315Lの平面形状を四角形にしてもよい。図22には示さないが、この場合は、ソルダレジストで覆われていないテスト用ランド315Lの開口形状も四角形にする。例えばテスト用ランド315Lの平面形状を正方形にした場合は、この正方形の一辺と同じ長さの直径を有する円に比べて面積が約1.27倍増加する(図22の斜線を付した部分)ので、テスト用ランド315Lとランド接続用コントラクトピン13Lとの接触不良の発生をさらに有效地に抑制することができる。

【0100】

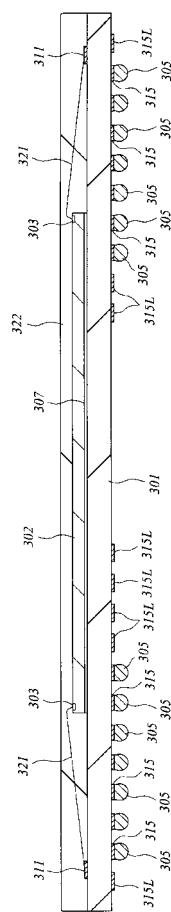

また、前記実施の形態の第1半導体パッケージ300は、配線基板301の上面にコントローラチップ302をフリップチップ実装したが、例えば図23および図24に示すように、配線基板301の上面に接着剤320を介してコントローラチップ302をフェイスアップ実装し、コントローラチップ302の正面の電極パッド303と配線基板301の上面のボンディングリード311をAuワイヤ321で電気的に接続してもよい。この場合は、コントローラチップ302、Auワイヤ321およびボンディングリード311を樹脂封止体322で封止する。

【0101】

前記実施の形態は、POP型半導体装置に適用したものであるが、本発明は、例えばSiP(システムインパッケージ)型の半導体装置に適用してもよい。さらには、図30に示すように、配線基板301の上面には、配線基板301の上面に搭載されるチップ(例

10

20

30

40

50

えばコントローラチップ302)の電極パッド(ボンディングパッド)303と電気的に接続される電極パッド(ボンディングリード311)しか形成されていない。言い換えると、配線基板301の上面に第2半導体パッケージ200と電気的に接続される電極パッド(上面側ランド312)が形成されていない、所謂、BGA(ボールグリッドアレイ)といった面実装パッケージ形態を有する他の半導体装置にも適用することができる。この理由として、本願発明は、上記したように、外部端子となる半田ボール305が接続される下面側ランド(第1ランド)315と、外部端子となる半田ボール305が接続されず、かつ半導体装置(組立体)の電気特性検査時にのみ使用されるテスト用ランド(第2ランド)315Lとを有する配線基板301を備えた組立体の電気特性検査を行う際に生じる課題について対策するものである。すなわち、前記実施の形態は、半導体装置の小型化が進み、各ランド(315、315L)の径が小さくなると、プローブ針とランドとの位置合わせ精度が低下し、最悪の場合、プローブ針とランドとが非接触となるために、正確な電気特性検査を行うことができなくなるという問題に着目したものであるため、POP型の半導体装置に限られるものではない。

【産業上の利用可能性】

【0102】

本発明は、チップが搭載された配線基板の下面に設けたテスト用ランドを使用して電気特性検査を行う面実装パッケージ型の半導体装置に適用することができる。

【符号の説明】

【0103】

100 プローブソケット

101 ソケット本体

102 キャップ

102a 凸部

103B ボール接続用コンタクトピン(第1コンタクトピン)

103L ランド接続用コンタクトピン(第2コンタクトピン)

104 コイルバネ

105 ピンガイド

106 ボールガイド

1000 第1半導体パッケージ

1001 第1配線基板

1002 コントローラチップ

1003 電極パッド

1004 半田ボール

1005 半田ボール

1006 ソルダレジスト

1007 アンダーフィル樹脂

1010 配線

1011 ボンディングリード(電極パッド)

1012 上面側ランド(電極パッド)

1015 下面側ランド(ボール搭載用ランド)

1015L テスト用ランド

2000 第2半導体パッケージ(組立体)

2001 第2配線基板

2002 DRAMチップ

2003 フラッシュメモリチップ

2004 電極パッド

2005 電極パッド

2006 Auワイヤ

2007 Auワイヤ

10

20

30

40

50

|                       |                                  |    |

|-----------------------|----------------------------------|----|

| 2 0 8                 | 半田ボール（外部端子）                      |    |

| 2 1 1                 | ボンディングリード                        |    |

| 2 1 2                 | ピア配線                             |    |

| 2 1 3                 | 下面側ランド                           |    |

| 2 2 0                 | 接着剤                              |    |

| 2 2 1                 | 樹脂封止体                            |    |

| 3 0 0                 | 第1半導体パッケージ（組立体、第1半導体装置、下段側パッケージ） |    |

| 3 0 1                 | 配線基板                             |    |

| 3 0 2                 | コントローラチップ                        |    |

| 3 0 3                 | 電極パッド                            | 10 |

| 3 0 4                 | 半田ボール（バンブ電極）                     |    |

| 3 0 5                 | 半田ボール（外部端子）                      |    |

| 3 0 6                 | ソルダレジスト                          |    |

| 3 0 7                 | アンダーフィル樹脂                        |    |

| 3 0 8、3 0 8 a、3 0 8 b | ダム                               |    |

| 3 1 0                 | 配線                               |    |

| 3 1 1                 | ボンディングリード                        |    |

| 3 1 2                 | 上面側ランド                           |    |

| 3 1 3                 | ピア配線                             |    |

| 3 1 4                 | 内部配線                             | 20 |

| 3 1 5                 | 下面側ランド                           |    |

| 3 1 5 L               | テスト用ランド                          |    |

| 3 2 0                 | 接着剤                              |    |

| 3 2 1                 | Auワイヤ                            |    |

| 3 2 2                 | 樹脂封止体                            |    |

| 3 3 0                 | マトリクス基板（大型配線基板）                  |    |

【 四 1 】

【図2】

【図3】

【図4】

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

【図10】

### 【図11】

【図12】

### 【図13】

【図15】

【図14】

【図16】

【図17】

【図18】

【 図 1 9 】

### 【図20】

13L: ランド接続用コンタクトピン

315: 下面側ランド 315L: テスト用ランド

### 【図21】

### 【図23】

【図22】

图 22

【図24】

24

## 【図25】

【図27】

【図26】

【図28】

## 【図29】

【図30】

---

フロントページの続き

(72)発明者 菊池 卓

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

審査官 藤原 伸二

(56)参考文献 特開2006-093189 (JP, A)

特開2003-068974 (JP, A)

特開2008-070146 (JP, A)

特開2001-318119 (JP, A)

特開2009-200101 (JP, A)

特開2009-054969 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G01R 31/26

G01R 31/28

H01L 23/12

H01L 25/04 - 25/18

H01R 33/00 - 33/975