등록특허 10-2087437

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2020년03월10일

(11) 등록번호 10-2087437

(24) 등록일자 2020년03월04일

(51) 국제특허분류(Int. Cl.)

*G11C 7/22* (2015.01) *G11C 7/10* (2015.01)

(73) 특허권자

에스케이하이닉스 주식회사

경기도 이천시 부발읍 경충대로 2091

(21) 출원번호 10-2013-0069281

(22) 출원일자 2013년06월17일

심사청구일자 2018년06월04일

(65) 공개번호 10-2014-0146483

(43) 공개일자 2014년12월26일

(72) 발명자

송근수

경기 이천시 부발읍 경충대로2041번길 54, 109동

113호 (현대사원아파트)

(56) 선행기술조사문헌

US20050111602 A1\*

US20060157688 A1\*

(74) 대리인

특허법인아주

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 3 항

심사관 : 송상용

(54) 발명의 명칭 수신장치를 포함하는 반도체시스템

**(57) 요 약**

반도체시스템은 데이터스트로브신호 및 데이터를 인가하는 송신장치; 및 상기 데이터스트로브신호로부터 내부클럭을 생성하고, 상기 내부클럭을 지연시켜 지연내부클럭을 생성하며, 상기 내부클럭 및 상기 지연내부클럭에 응답하여 상기 데이터를 버퍼링하여 입력데이터를 생성하는 수신장치를 포함한다.

**대 표 도** - 도1

## 명세서

### 청구범위

#### 청구항 1

데이터스트로브신호 및 데이터를 인가하는 송신장치; 및

상기 데이터스트로브신호로부터 내부클럭을 생성하고, 상기 내부클럭을 지연시켜 지연내부클럭을 생성하며, 상기 내부클럭 및 상기 지연내부클럭에 응답하여 상기 데이터를 버퍼링하여 입력데이터를 생성하는 수신장치를 포함하되, 상기 내부클럭의 주기는 상기 데이터스트로브신호의 주기보다 N 배 크게 설정되고, N은 2 이상의 자연수로 설정되는 반도체시스템.

#### 청구항 2

◆ 청구항 2은(는) 설정등록료 납부시 포기되었습니다.◆

제 1 항에 있어서, 상기 수신장치는 상기 내부클럭에 따라 상기 데이터를 버퍼링하고, 상기 지연내부클럭에 따라 상기 버퍼링된 데이터를 버퍼링하여 상기 입력데이터를 생성하는 반도체시스템.

#### 청구항 3

◆ 청구항 3은(는) 설정등록료 납부시 포기되었습니다.◆

제 2 항에 있어서, 상기 수신장치는

상기 데이터스트로브신호를 분주하여 상기 내부클럭을 생성하는 내부클럭생성회로; 및

상기 내부클럭을 입력받아 상기 지연내부클럭을 생성하고, 상기 내부클럭에 따라 상기 데이터를 버퍼링한 후 상기 지연내부클럭에 따라 상기 버퍼링된 데이터를 버퍼링하여 상기 입력데이터를 생성하는 데이터입력회로를 포함하는 반도체시스템.

#### 청구항 4

◆ 청구항 4은(는) 설정등록료 납부시 포기되었습니다.◆

제 3 항에 있어서, 상기 데이터입력회로는

상기 내부클럭에 동기하여 상기 데이터를 버퍼링하여 내부데이터를 생성하는 제1 버퍼부;

상기 내부클럭을 기설정된 지연구간만큼 지연시켜 상기 지연내부클럭을 생성하는 지연부; 및

상기 지연내부클럭에 동기하여 상기 내부데이터를 버퍼링하여 상기 입력데이터를 생성하는 제2 버퍼부를 포함하는 반도체시스템.

#### 청구항 5

◆ 청구항 5은(는) 설정등록료 납부시 포기되었습니다.◆

제 4 항에 있어서, 상기 제1 및 제2 버퍼부는 크로스커플드래치(cross coupled latch)로 구현되는 반도체시스템.

**청구항 6**

◆ 청구항 6은(는) 설정등록료 납부시 포기되었습니다.◆

제 5 항에 있어서, 상기 지연부는 인버터체인(inverter chain)으로 구현되는 반도체시스템.

**청구항 7**

◆ 청구항 7은(는) 설정등록료 납부시 포기되었습니다.◆

제 1 항에 있어서, 상기 수신장치는

상기 데이터스트로브신호를 분주하여 제1 내부클럭 및 제2 내부클럭을 생성하는 내부클럭생성회로; 및

상기 제1 및 제2 내부클럭을 입력받아 제1 및 제2 지연내부클럭을 생성하고, 상기 제1 및 제2 내부클럭에 따라 상기 데이터를 베피링한 후 상기 제1 및 제2 지연내부클럭에 따라 상기 베피링된 데이터를 베피링하여 제1 및 제2 입력데이터를 생성하는 데이터입력회로를 포함하는 반도체시스템.

**청구항 8**

◆ 청구항 8은(는) 설정등록료 납부시 포기되었습니다.◆

제 7 항에 있어서, 상기 제2 내부클럭은 상기 제1 내부클럭보다  $90^{\circ}$  만큼 위상이 늦은 반도체시스템.

**청구항 9**

◆ 청구항 9은(는) 설정등록료 납부시 포기되었습니다.◆

제 8 항에 있어서, 상기 데이터입력회로는

상기 제1 내부클럭에 동기하여 상기 데이터를 베피링하여 제1 내부데이터를 생성하는 제1 베피부;

상기 제1 내부클럭을 기설정된 제1 지연구간만큼 지연시켜 상기 제1 지연내부클럭을 생성하는 제1 지연부;

상기 제1 지연내부클럭에 동기하여 상기 제1 내부데이터를 베피링하여 상기 제1 입력데이터를 생성하는 제2 베피부;

상기 제2 내부클럭에 동기하여 상기 데이터를 베피링하여 제2 내부데이터를 생성하는 제3 베피부;

상기 제2 내부클럭을 기설정된 제2 지연구간만큼 지연시켜 상기 제2 지연내부클럭을 생성하는 제2 지연부; 및

상기 제2 지연내부클럭에 동기하여 상기 제2 내부데이터를 베피링하여 상기 제2 입력데이터를 생성하는 제4 베피부를 포함하는 반도체시스템.

**청구항 10**

제1 내부클럭에 동기하여 데이터를 베피링하여 제1 내부데이터를 생성하는 제1 베피부;

상기 제1 내부클럭을 기설정된 제1 지연구간만큼 지연시켜 제1 지연내부클럭을 생성하는 제1 지연부; 및

상기 제1 지연내부클럭에 동기하여 상기 제1 내부데이터를 베피링하여 제1 입력데이터를 생성하는 제2 베피부를 포함하되, 상기 제1 내부클럭의 주기는 송신장치에서 인가되는 데이터스트로브신호의 주기보다 N 배 크게 설정되고, N은 2 이상의 자연수로 설정되는 수신장치.

**청구항 11**

◆ 청구항 11은(는) 설정등록료 납부시 포기되었습니다.◆

제 10 항에 있어서, 상기 제1 및 제2 버퍼부는 크로스커플드래치(cross coupled latch)로 구현되는 수신장치.

### 청구항 12

◆ 청구항 12은(는) 설정등록료 납부시 포기되었습니다.◆

제 11 항에 있어서, 상기 제1 지연부는 인버터체인(inverter chain)으로 구현되는 수신장치.

### 청구항 13

◆ 청구항 13은(는) 설정등록료 납부시 포기되었습니다.◆

제 10 항에 있어서,

제2 내부클럭에 동기하여 상기 데이터를 버퍼링하여 제2 내부데이터를 생성하는 제3 버퍼부;

상기 제2 내부클럭을 기설정된 제2 지연구간만큼 지연시켜 제2 지연내부클럭을 생성하는 제2 지연부; 및

상기 제2 지연내부클럭에 동기하여 상기 제2 내부데이터를 버퍼링하여 제2 입력데이터를 생성하는 제4 버퍼부를 더 포함하는 수신장치.

### 청구항 14

◆ 청구항 14은(는) 설정등록료 납부시 포기되었습니다.◆

제 13 항에 있어서, 상기 제2 내부클럭은 상기 제1 내부클럭보다  $90^\circ$  만큼 위상이 늦은 수신장치.

### 청구항 15

◆ 청구항 15은(는) 설정등록료 납부시 포기되었습니다.◆

제 14 항에 있어서, 상기 제3 및 제4 버퍼부는 크로스커플드래치(cross coupled latch)로 구현되는 수신장치.

### 청구항 16

◆ 청구항 16은(는) 설정등록료 납부시 포기되었습니다.◆

제 15 항에 있어서, 상기 제2 지연부는 인버터체인(inverter chain)으로 구현되는 수신장치.

### 청구항 17

제1 및 제2 내부클럭과 데이터를 인가하는 송신장치; 및

상기 제1 및 제2 내부클럭을 지연시켜 제1 및 제2 지연내부클럭을 생성하고, 상기 제1 및 제2 내부클럭에 따라 상기 데이터를 버퍼링한 후 상기 제1 및 제2 지연내부클럭에 따라 상기 버퍼링된 데이터를 버퍼링하여 제1 및 제2 입력데이터를 생성하는 수신장치를 포함하되, 상기 제1 내부클럭 및 상기 제2 내부클럭의 주기는 상기 송신장치에서 인가되는 데이터스트로브신호의 주기보다 N 배 크게 설정되고, N은 2 이상의 자연수로 설정되는 반도체시스템.

### 청구항 18

◆ 청구항 18은(는) 설정등록료 납부시 포기되었습니다.◆

제 17 항에 있어서, 상기 제2 내부클럭은 상기 제1 내부클럭보다  $90^\circ$  만큼 위상이 늦은 반도체시스템.

## 청구항 19

◆ 청구항 19은(는) 설정등록료 납부시 포기되었습니다.◆

제 18 항에 있어서, 상기 수신장치는

상기 제1 내부클럭에 동기하여 상기 데이터를 버퍼링하여 제1 내부데이터를 생성하는 제1 버퍼부;

상기 제1 내부클럭을 기설정된 제1 지연구간만큼 지연시켜 상기 제1 지연내부클럭을 생성하는 제1 지연부;

상기 제1 지연내부클럭에 동기하여 상기 제1 내부데이터를 버퍼링하여 상기 제1 입력데이터를 생성하는 제2 버퍼부;

상기 제2 내부클럭에 동기하여 상기 데이터를 버퍼링하여 제2 내부데이터를 생성하는 제3 버퍼부;

상기 제2 내부클럭을 기설정된 제2 지연구간만큼 지연시켜 상기 제2 지연내부클럭을 생성하는 제2 지연부; 및

상기 제2 지연내부클럭에 동기하여 상기 제2 내부데이터를 버퍼링하여 상기 제2 입력데이터를 생성하는 제4 버퍼부를 포함하는 반도체시스템.

## 청구항 20

◆ 청구항 20은(는) 설정등록료 납부시 포기되었습니다.◆

제 19항에 있어서, 상기 제1 내지 제4 버퍼부는 크로스커플드래치(cross coupled latch)로 구현되고, 상기 제1 및 제2 지연부는 인버터체인(inverter chain)으로 구현되는 반도체시스템.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 데이터를 수신하는 수신장치를 포함하는 반도체시스템에 관한 것이다.

### 배경 기술

[0002]

반도체시스템은 집적도의 증가와 더불어 그 동작 속도의 향상을 위하여 계속적으로 개선되어 왔다. 동작속도를 향상시키기 위하여 반도체장치 외부에서 주어지는 클록과 동기되어 동작할 수 있는 소위 동기식(Synchronous) 장치가 등장하였다.

[0003]

처음 제안된 것은 반도체장치의 외부로부터의 클록의 상승 예지(rising edge)에 동기되어 하나의 데이터 핀에서 클록의 한 주기에 걸쳐 하나의 데이터를 입출력하는 이른바 SDR(single data rate) 반도체장치이다.

[0004]

그러나 SDR 동기식 반도체장치 역시 고속 동작을 요구하는 반도체시스템의 속도를 만족하기에는 불충분하며, 이에 따라 하나의 클록 주기에 두 개의 데이터를 처리하는 방식인 DDR(Double Data Rate) 동기식 반도체장치가 제안되었다.

[0005]

DDR 동기식 반도체장치의 각 데이터 입출핀에서는 외부에서 입력되는 클록의 상승 예지(rising edge)와 하강예지(falling edge)에 동기되어 연속적으로 두 개의 데이터가 입출력되는바, 클록의 주파수를 증가시키지 않더라도 종래의 SDR 동기식 반도체장치에 비하여 최소한 두 배 이상의 대역폭(band width)을 구현할 수 있어 그만큼 고속동작이 구현 가능하다.

## 발명의 내용

## 해결하려는 과제

[0006]

본 발명은 내부클럭에 동기하여 데이터를 버퍼링하여 입력받는 수신장치를 포함하는 반도체시스템을 제공한다.

## 과제의 해결 수단

[0007]

이를 위해 본 발명은 데이터스트로브신호 및 데이터를 인가하는 송신장치; 및 상기 데이터스트로브신호로부터 내부클럭을 생성하고, 상기 내부클럭을 지연시켜 지연내부클럭을 생성하며, 상기 내부클럭 및 상기 지연내부클럭에 응답하여 상기 데이터를 버퍼링하여 입력데이터를 생성하는 수신장치를 포함하는 반도체시스템을 제공한다.

[0008]

또한, 본 발명은 제1 및 제2 내부클럭과 데이터를 인가하는 송신장치; 및 상기 제1 및 제2 내부클럭을 지연시켜 제1 및 제2 지연내부클럭을 생성하고, 상기 제1 및 제2 내부클럭에 따라 상기 데이터를 버퍼링한 후 상기 제1 및 제2 지연내부클럭에 따라 상기 버퍼링된 데이터를 버퍼링하여 제1 및 제2 입력데이터를 생성하는 수신장치를 포함하는 반도체시스템을 제공한다.

[0009]

또한, 본 발명은 제1 내부클럭에 동기하여 데이터를 버퍼링하여 제1 내부데이터를 생성하는 제1 버퍼부; 상기 제1 내부클럭을 기설정된 제1 지연구간만큼 지연시켜 제1 지연내부클럭을 생성하는 제1 지연부; 및 상기 제1 지연내부클럭에 동기하여 상기 제1 내부데이터를 버퍼링하여 제1 입력데이터를 생성하는 제2 버퍼부를 포함하는 수신장치를 제공한다.

## 발명의 효과

[0010]

본 발명에 의하면 내부클럭 및 내부클럭을 지연시켜 생성된 지연내부클럭에 동기하여 데이터를 버퍼링하여 입력 받음으로써, 고속동작에서도 안정적으로 데이터를 입력받을 수 있는 효과가 있다.

## 도면의 간단한 설명

[0011]

도 1은 본 발명의 일 실시예에 따른 반도체시스템의 구성을 도시한 블럭도이다.

도 2는 도 1에 도시된 반도체시스템에 포함된 데이터입력회로의 구성을 도시한 블럭도이다.

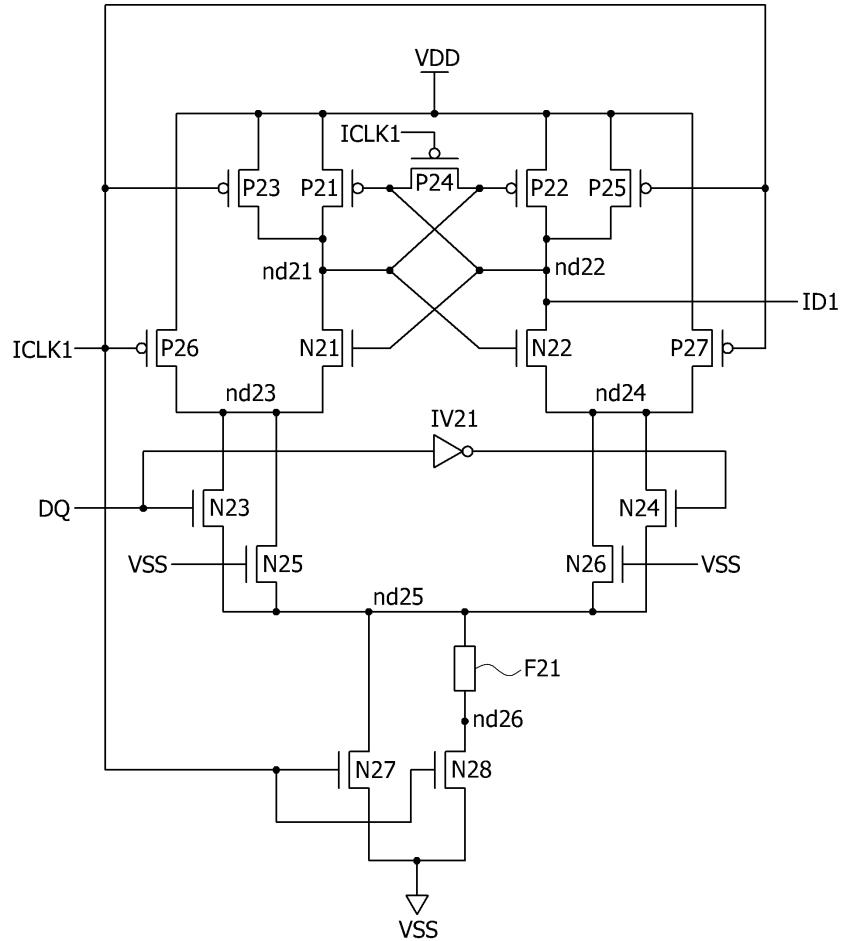

도 3은 도 2에 도시된 데이터입력회로에 포함된 제1 버퍼부의 일 실시예에 따른 회로도이다.

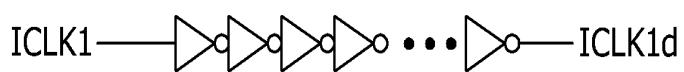

도 4는 도 2에 도시된 데이터입력회로에 포함된 제1 지연부의 일 실시예에 따른 회로도이다.

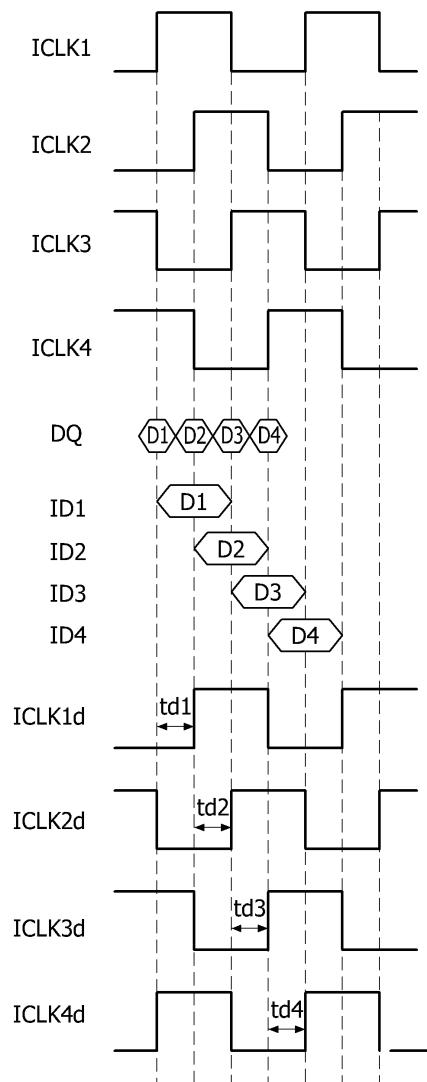

도 5는 도 1에 도시된 반도체시스템의 동작을 설명하기 위한 타이밍도이다.

도 6은 본 발명의 다른 실시예에 따른 반도체시스템의 구성을 도시한 블럭도이다.

## 발명을 실시하기 위한 구체적인 내용

[0012]

이하, 실시예를 통하여 본 발명을 더욱 상세히 설명하기로 한다. 이들 실시예는 단지 본 발명을 예시하기 위한 것이며, 본 발명의 권리 보호 범위가 이들 실시예에 의해 제한되는 것은 아니다.

[0013]

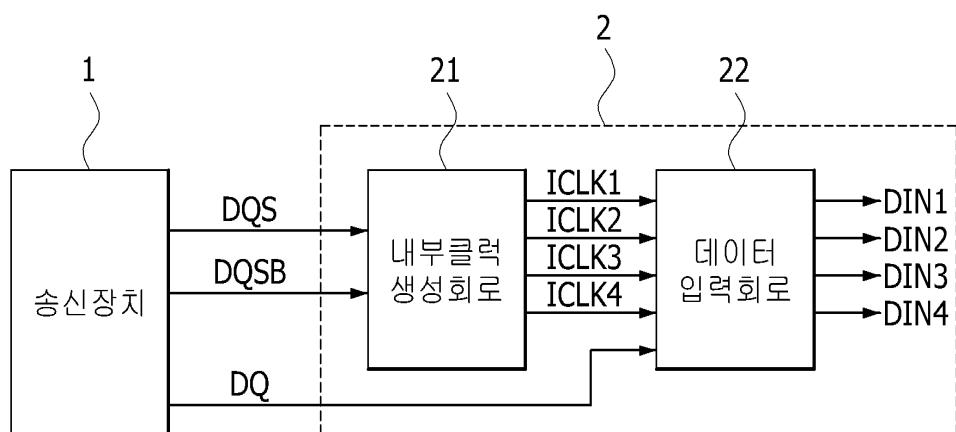

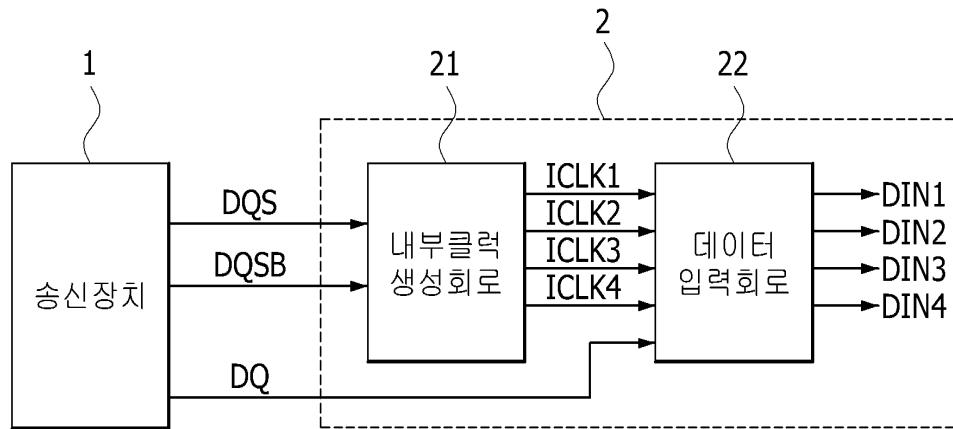

도 1을 참고하면 본 발명의 일실시예에 따른 반도체시스템은 송신장치(1) 및 수신장치(2)를 포함한다. 송신장치(1)는 데이터스트로브신호(DQS, DQSB) 및 데이터(DQ)를 인가한다. 수신장치(2)는 내부클럭생성회로(21) 및 데이터입력회로(22)를 포함한다. 내부클럭생성회로(21)는 데이터스트로브신호(DQS, DQSB)를 분주하여 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)을 생성한다. 내부클럭생성회로(21)는 입력 클럭의 주기를 정수배만큼 증가시켜 출력시키는 분주기로 구현된다. 본 실시예에서 제2 내부클럭(ICLK2)은 제1 내부클럭(ICLK1)보다  $90^\circ$  만큼 위상이 늦고, 제3 내부클럭(ICLK3)은 제2 내부클럭(ICLK2)보다  $90^\circ$  만큼 위상이 늦으며, 제4 내부클럭(ICLK4)은 제3 내부클럭(ICLK3)보다  $90^\circ$  만큼 위상이 늦다. 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)의 위상은 실시예에 따라 다양하게 설정할 수 있다. 데이터입력회로(22)는 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제

4 내부클럭(ICLK4)에 응답하여 데이터(DQ)를 버퍼링하여 제1 입력데이터(DIN1), 제2 입력데이터(DIN2), 제3 입력데이터(DIN3) 및 제4 입력데이터(DIN4)를 생성한다.

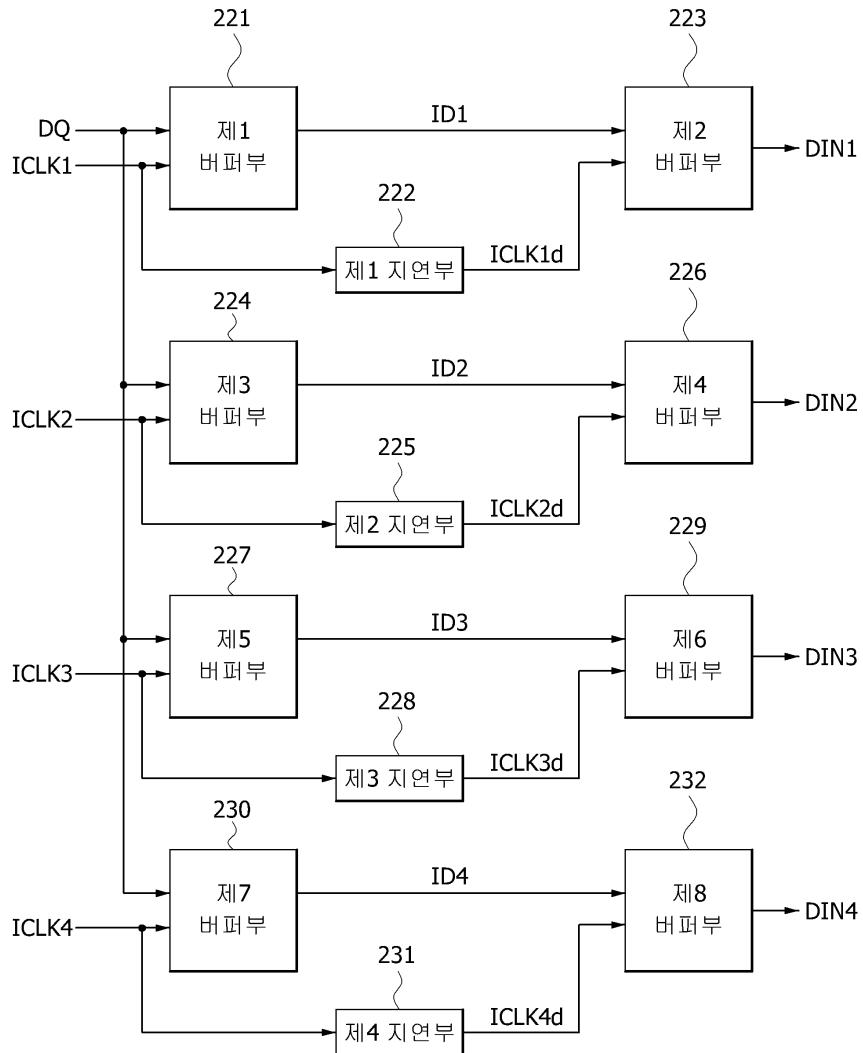

[0014] 도 2를 참고하면 데이터입력회로(22)는 제1 버퍼부(221), 제1 지연부(222), 제2 버퍼부(223), 제3 버퍼부(224), 제2 지연부(225), 제4 버퍼부(226), 제5 버퍼부(227), 제3 지연부(228), 제6 버퍼부(229), 제7 버퍼부(230), 제4 지연부(231) 및 제8 버퍼부(232)로 구성된다. 제1 버퍼부(221)는 제1 내부클럭(ICLK1)에 동기하여 데이터(DQ)를 버퍼링하여 제1 내부데이터(ID1)를 생성한다. 제1 버퍼부(221)는 제1 내부클럭(ICLK1)의 특정 상태, 예를 들어 라이징에지 또는 로직하이레벨 상태에서 동작한다. 데이터(DQ)를 버퍼링한다는 것은 제1 버퍼부(221)에 공급되는 전원으로 데이터(DQ)를 구동하는 것을 의미하므로, 제1 버퍼부(221)는 데이터(DQ)를 증폭하여 제1 내부데이터(ID1)로 출력하는 동작을 수행한다. 제1 지연부(222)는 제1 내부클럭(ICLK1)을 지연시켜 제1 지연내부클럭(ICLK1d)을 생성한다. 제1 지연부(222)는 인버터체인과 같은 수동소자로 구성되어 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)에 무관하게 제1 내부클럭(ICLK1)을 지연시킨다. 제2 버퍼부(223)는 제1 지연내부클럭(ICLK1d)에 동기하여 제1 내부데이터(ID1)를 버퍼링하여 제1 입력데이터(DIN1)를 생성한다. 제3 버퍼부(224)는 제2 내부클럭(ICLK2)에 동기하여 데이터(DQ)를 버퍼링하여 제2 내부데이터(ID2)를 생성한다. 제2 지연부(225)는 제2 내부클럭(ICLK2)을 지연시켜 제2 지연내부클럭(ICLK2d)을 생성한다. 제2 지연부(225)는 인버터체인과 같은 수동소자로 구성되어 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)에 무관하게 제2 내부클럭(ICLK2)을 지연시킨다. 제4 버퍼부(226)는 제2 지연내부클럭(ICLK2d)에 동기하여 제2 내부데이터(ID2)를 버퍼링하여 제2 입력데이터(DIN2)를 생성한다. 제5 버퍼부(227)는 제3 내부클럭(CLK3)에 동기하여 데이터(DQ)를 버퍼링하여 제3 내부데이터(ID3)를 생성한다. 제3 지연부(228)는 제3 내부클럭(CLK3)을 지연시켜 제3 지연내부클럭(ICLK3d)을 생성한다. 제3 지연부(228)는 인버터체인과 같은 수동소자로 구성되어 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)에 무관하게 제3 내부클럭(CLK3)을 지연시킨다. 제6 버퍼부(229)는 제3 지연내부클럭(ICLK3d)에 동기하여 제3 내부데이터(ID3)를 버퍼링하여 제4 내부데이터(ID4)를 생성한다. 제7 버퍼부(230)는 제4 내부클럭(CLK4)에 동기하여 데이터(DQ)를 버퍼링하여 제4 내부데이터(ID4)를 생성한다. 제4 지연부(231)는 제4 내부클럭(CLK4)을 지연시켜 제4 지연내부클럭(ICLK4d)을 생성한다. 제4 지연부(231)는 인버터체인과 같은 수동소자로 구성되어 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)에 무관하게 제4 내부클럭(CLK4)을 지연시킨다. 제8 버퍼부(232)는 제4 지연내부클럭(ICLK4d)에 동기하여 제4 내부데이터(ID4)를 버퍼링하여 제4 입력데이터(DIN4)를 생성한다.

[0015] 도 3을 참고하면 제1 버퍼부(221)는 제1 내부클럭(ICLK1)이 로직하이레벨인 상태에서 데이터(DQ)를 버퍼링하여 제1 내부데이터(ID1)로 출력하는 크로스커플드래치(cross coupled latch)로 구현된다. 제1 버퍼부(221)는 다수의 PMOS 트랜지스터(P21~P27), 퓨즈(F21) 및 NMOS 트랜지스터(N21~N28)를 포함한다. PMOS 트랜지스터(P21)는 전원전압(VDD)과 노드(nd21) 사이에 연결되어 노드(nd22)의 전압에 응답하여 턴온된다. PMOS 트랜지스터(P22)는 전원전압(VDD)과 노드(nd22) 사이에 연결되어 노드(nd21)의 전압에 응답하여 턴온된다. PMOS 트랜지스터(P23)는 전원전압(VDD)과 노드(nd21) 사이에 연결되어 제1 내부클럭(ICLK1)에 응답하여 턴온된다. PMOS 트랜지스터(P24)는 노드(nd21)와 노드(nd22) 사이에 연결되어 제1 내부클럭(ICLK1)에 응답하여 턴온된다. PMOS 트랜지스터(P25)는 전원전압(VDD)과 노드(nd22) 사이에 연결되어 제1 내부클럭(ICLK1)에 응답하여 턴온된다. PMOS 트랜지스터(P26)는 전원전압(VDD)과 노드(nd23) 사이에 연결되어 제1 내부클럭(ICLK1)에 응답하여 턴온된다. PMOS 트랜지스터(P27)는 전원전압(VDD)과 노드(nd24) 사이에 연결되어 제1 내부클럭(ICLK1)에 응답하여 턴온된다. NMOS 트랜지스터(N21)는 노드(nd21)와 노드(nd23) 사이에 연결되어 노드(nd22)의 전압에 응답하여 턴온된다. NMOS 트랜지스터(N22)는 노드(nd22)와 노드(nd24) 사이에 연결되어 노드(nd21)의 전압에 응답하여 턴온된다. NMOS 트랜지스터(N23)는 노드(nd23)와 노드(nd25) 사이에 연결되어 데이터(DQ)에 응답하여 턴온된다. NMOS 트랜지스터(N24)는 노드(nd24)와 노드(nd25) 사이에 연결되어 인버터(IV21)의 출력신호에 응답하여 턴온된다. NMOS 트랜지스터(N25)는 노드(nd23)와 노드(nd25) 사이에 연결되어 접지전압(VSS)의 전압에 응답하여 턴온된다. NMOS 트랜지스터(N26)는 노드(nd24)와 노드(nd25) 사이에 연결되어 접지전압(VSS)의 전압에 응답하여 턴온된다. NMOS 트랜지스터(N25) 및 NMOS 트랜지스터(N26)는 데이터(DQ) 외에 증폭이 필요한 다른 신호가 접지전압(VSS) 대신 입력될 수 있도록 예비한 더미소자들이다. NMOS 트랜지스터(N27)는 노드(nd25)와 접지전압(VSS) 사이에 연결되어 제1 내부클럭(ICLK1)에 응답하여 턴온된다. 퓨즈(F21)는 노드(nd25)와 노드(nd26) 사이에 연결된다. 퓨즈(F21)는 제1 내부클럭(ICLK1)이 로직하이레벨인 상태에서 제1 버퍼부(221)가 구동될 때 풀다운 구동력을 조절하기 위해 구비된다. 즉, 퓨즈(F21)가 커팅되지 않은 상태에서는 NMOS 트랜지스터(N28)도 동작하여 퓨즈(F21)가 커팅된 상태에 비해 풀다운 구동력이 증가한다. NMOS 트랜지스터(N28)는 노드(nd26)와 접지전압(VSS) 사이에 연결되어 제1 내부클럭(ICLK1)에 응답하여 턴온된다.

- [0016] 제1 버퍼부(221)는 제1 내부클럭(ICLK1)이 로직로우레벨일 때 턴온되는 PMOS 트랜지스터들(P23, P24, P25, P26, P27)과 턴오프되는 NMOS 트랜지스터들(N27, N28)에 의해 버퍼링동작이 중단되고, 누설전류를 차단한다. 한편, 제1 버퍼부(221)는 제1 내부클럭(ICLK1)이 로직하이레벨일 때 턴오프되는 PMOS 트랜지스터들(P23, P24, P25, P26, P27)과 턴온되는 NMOS 트랜지스터들(N27, N28)에 의해 데이터(DQ)를 버퍼링하여 제1 내부데이터(ID1)를 생성한다. 데이터(DQ)가 로직하이레벨인 경우 노드(nd23)의 전압이 노드(nd24)의 전압에 비해 상대적으로 로직로우레벨이므로 NMOS 트랜지스터(N21)가 NMOS 트랜지스터(N22)보다 상대적으로 많이 턴온된다. 따라서, 노드(nd21)의 전압은 노드(nd22)의 전압보다 상대적으로 낮아져 PMOS 트랜지스터(P21)가 PMOS 트랜지스터(P22)보다 상대적으로 적게 턴온된다. 따라서, 노드(nd21)의 전압은 지속적으로 낮아져 로직로우레벨로 설정되고, 노드(nd22)의 전압은 지속적으로 높아져 로직하이레벨로 설정된다. 제2 버퍼부(223), 제3 버퍼부(224), 제4 버퍼부(226), 제5 버퍼부(227), 제6 버퍼부(229), 제7 버퍼부(230) 및 제8 버퍼부(232)는 제1 버퍼부(221)와 입출력신호의 종류만 다를뿐 동일한 구성의 회로로 구현할 수 있으므로, 자세한 구성 및 동작에 대한 설명은 생략한다.

- [0017] 도 4를 참고하면 제1 지연부(222)는 인버터체인으로 구현된다. 인버터체인은 비동기적으로 동작하는 수동소자인 인버터들로 구성된다. 따라서, 제1 지연부(222)는 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)에 무관하게 제1 내부클럭(ICLK1)을 지연시켜 제1 지연내부클럭(ICLK1d)을 생성한다. 제2 지연부(225), 제3 지연부(228) 및 제4 지연부(231)는 제1 지연부(222)와 입출력신호의 종류만 다를뿐 동일한 구성의 회로로 구현할 수 있으므로, 자세한 구성 및 동작에 대한 설명은 생략한다.

- [0018] 이와 같이 구성된 반도체시스템의 동작을 도 5를 참고하여 구체적으로 살펴보면 다음과 같다.

- [0019] 우선, 수신장치(2)는 송신장치(1)에서 인가된 데이터스트로브신호(DQS, DQSB)를 분주하여 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)을 생성한다. 제2 내부클럭(ICLK2)은 제1 내부클럭(ICLK1)보다  $90^\circ$  만큼 위상이 늦고, 제3 내부클럭(ICLK3)은 제2 내부클럭(ICLK2)보다  $90^\circ$  만큼 위상이 늦으며, 제4 내부클럭(ICLK4)은 제3 내부클럭(ICLK3)보다  $90^\circ$  만큼 위상이 늦게 생성된다.

- [0020] 다음으로, 데이터입력회로(22)는 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)에 동기하여 데이터(DQ)를 버퍼링하여 제1 내부데이터(ID1), 제2 내부데이터(ID2), 제3 내부데이터(ID3) 및 제4 내부데이터(ID4)를 생성한다. 제1 내부데이터(ID1), 제2 내부데이터(ID2), 제3 내부데이터(ID3) 및 제4 내부데이터(ID4)는 각각 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)에 동기되어 버퍼링되어 생성된다. 따라서, 데이터(DQ)에 포함된 제1 데이터(D1), 제2 데이터(D2), 제3 데이터(D3) 및 제4 데이터(D4)가 제1 내부데이터(ID1), 제2 내부데이터(ID2), 제3 내부데이터(ID3) 및 제4 내부데이터(ID4)로 순차적으로 출력된다.

- [0021] 다음으로, 데이터입력회로(22)는 제1 내부데이터(ID1), 제2 내부데이터(ID2), 제3 내부데이터(ID3) 및 제4 내부데이터(ID4)를 각각 제1 지연내부클럭(ICLK1d), 제2 지연내부클럭(ICLK2d), 제3 지연내부클럭(ICLK3d) 및 제4 지연내부클럭(ICLK4d)에 동기하여 버퍼링하여 제1 입력데이터(DIN1), 제2 입력데이터(DIN2), 제3 입력데이터(DIN3) 및 제4 입력데이터(DIN4)로 출력한다. 여기서, 제1 지연내부클럭(ICLK1d), 제2 지연내부클럭(ICLK2d), 제3 지연내부클럭(ICLK3d) 및 제4 지연내부클럭(ICLK4d)은 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)과 무관하게 동작하는 수동소자들로 구성된 제1 지연부(222), 제2 지연부(225), 제3 지연부(228) 및 제4 지연부(231)로부터 생성된다. 따라서, 제1 지연내부클럭(ICLK1d)을 생성하기 위해 제1 내부클럭(ICLK1)을 지연시키는 제1 지연구간(td1), 제2 지연내부클럭(ICLK2d)을 생성하기 위해 제2 내부클럭(ICLK2)을 지연시키는 제2 지연구간(td2), 제3 지연내부클럭(ICLK3d)을 생성하기 위해 제3 내부클럭(ICLK3)을 지연시키는 제3 지연구간(td3) 및 제4 지연내부클럭(ICLK4d)을 생성하기 위해 제4 내부클럭(ICLK4)을 지연시키는 제4 지연구간(td4)은 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)에 무관하게 설정할 수 있다. 제1 내부데이터(ID1), 제2 내부데이터(ID2), 제3 내부데이터(ID3) 및 제4 내부데이터(ID4)의 데이터원도우 중앙에 제1 지연내부클럭(ICLK1d), 제2 지연내부클럭(ICLK2d), 제3 지연내부클럭(ICLK3d) 및 제4 지연내부클럭(ICLK4d)의 라이징에지가 위치하도록 제1 지연구간(td1), 제2 지연구간(td2), 제3 지연구간(td3) 및 제4 지연구간(td4)을 설정함으로써, 제1 내부데이터(ID1), 제2 내부데이터(ID2), 제3 내부데이터(ID3) 및 제4 내부데이터(ID4)가 완전한 레벨로 구동되기전 다시 버퍼링되는 현상이 발생하는 것을 방지할 수 있다.

- [0022] 이상 설명한 바와 같이, 본 실시예에 따른 반도체시스템은 데이터(DQ)를 2단계로 증폭함에 있어, 동작속도가 빨라져 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)의 주기가 짧아

쳐도 수동소자에 의해 설정되는 제1 지연구간(td1), 제2 지연구간(td2), 제3 지연구간(td3) 및 제4 지연구간(td4)을 조절함으로써 오동작이 발생하는 것을 방지할 수 있다. 즉, 2 단계 증폭 시점을 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3) 및 제4 내부클럭(ICLK4)에 무관하게 설정함으로써, 고속동작에서도 안정적으로 데이터를 입력받을 수 있다.

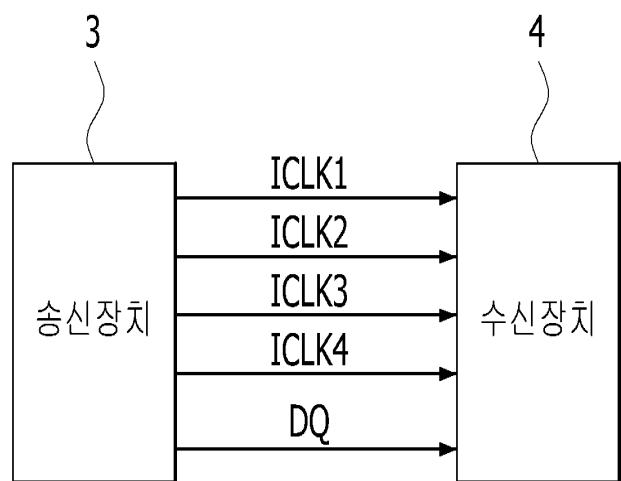

[0023] 도 6을 참고하면 본 발명의 다른 실시예에 따른 반도체시스템은 송신장치(3) 및 수신장치(4)를 포함한다. 송신장치(3)는 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3), 제4 내부클럭(ICLK4) 및 데이터(DQ)를 인가한다. 본 실시예에서 제2 내부클럭(ICLK2)은 제1 내부클럭(ICLK1)보다  $90^\circ$  만큼 위상이 늦고, 제3 내부클럭(ICLK3)은 제2 내부클럭(ICLK2)보다  $90^\circ$  만큼 위상이 늦으며, 제4 내부클럭(ICLK4)은 제3 내부클럭(ICLK3)보다  $90^\circ$  만큼 위상이 늦다. 수신장치(4)는 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3), 제4 내부클럭(ICLK4)에 동기하여 데이터(DQ)를 수신한다. 본 실시예에 따른 반도체시스템은 앞서 도 1 내지 도 5에서 설명한 반도체시스템과 달리 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3), 제4 내부클럭(ICLK4)을 수신장치(4) 내부에서 데이터스트로브신호(DQS, DQSB)를 분주하여 생성하지 않고, 송신장치(3)에서 인가받는다.

[0024] 수신장치(4)는 도 2에 도시된 데이터입력회로(22)와 동일하게 구현된다. 즉, 수신장치(4)는 인버터체인 등의 수동소자들로 구현된 지연부를 통해 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3), 제4 내부클럭(ICLK4)을 지연시켜 제1 지연내부클럭(ICLK1d), 제2 지연내부클럭(ICLK2d), 제3 지연내부클럭(ICLK3d) 및 제4 지연내부클럭(ICLK4d)을 생성한다. 또한, 수신장치(4)는 제1 내부클럭(ICLK1), 제2 내부클럭(ICLK2), 제3 내부클럭(ICLK3), 제4 내부클럭(ICLK4)에 동기하여 데이터(DQ)를 버퍼링하여 제1 내부데이터(ID1), 제2 내부데이터(ID2), 제3 내부데이터(ID3) 및 제4 내부데이터(ID4)를 생성한 후 제1 지연내부클럭(ICLK1d), 제2 지연내부클럭(ICLK2d), 제3 지연내부클럭(ICLK3d) 및 제4 지연내부클럭(ICLK4d)에 동기하여 제1 내부데이터(ID1), 제2 내부데이터(ID2), 제3 내부데이터(ID3) 및 제4 내부데이터(ID4)를 다시 한번 버퍼링한다.

[0025]

### 부호의 설명

|              |              |

|--------------|--------------|

| 1: 송신장치      | 2: 수신장치      |

| 21: 내부클럭생성회로 | 22 및 데이터입력회로 |

| 221: 제1 버퍼부  | 222: 제1 지연부  |

| 223: 제2 버퍼부  | 224: 제3 버퍼부  |

| 2245: 제2 지연부 | 226: 제4 버퍼부  |

| 227: 제5 버퍼부  | 228: 제3 지연부  |

| 229: 제6 버퍼부  | 230: 제7 버퍼부  |

| 231: 제4 지연부  | 232: 제8 버퍼부  |

도면

도면1

## 도면2

도면3

221

도면4

222

도면5

도면6