(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년09월18일

(11) 등록번호 10-1184096

(24) 등록일자 2012년09월12일

- (51) 국제특허분류(Int. Cl.)

*B32B 27/00* (2006.01) *G02B 5/30* (2006.01)

*H05K 3/12* (2006.01) *G06K 19/07* (2006.01)

- (21) 출원번호 10-2007-7007397

- (22) 출원일자(국제) 2005년08월24일

심사청구일자 2010년06월29일

- (85) 번역문제출일자 2007년03월30일

- (65) 공개번호 10-2007-0062535

- (43) 공개일자 2007년06월15일

- (86) 국제출원번호 PCT/EP2005/009137

- (87) 국제공개번호 WO 2006/024441

국제공개일자 2006년03월09일

(30) 우선권주장

10 2004 042 111.0 2004년08월30일 독일(DE)

(56) 선행기술조사문헌

JP2000124663 A\*

JP2000098132 A\*

JP11186773 A\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 23 항

심사관 : 한상일

(54) 발명의 명칭 전기 전도성 코팅을 구비한 상이한 미세구조 영역을 갖는다층체

**(57) 요 약**

본 발명은 복제 광택층(22)을 포함하는 다층체(11, 12)에 관한 것이다. 다층체의 제1 영역 내의 좌표축 x 및 y로 정의되는 평면 상의 상기 복제 광택층(22)에 제1 릴리프 구조(25, 125, 65)가 몰딩되고, 다층체(11, 12)의 제1 영역 및 그 제2 인접 영역 내의 복제 광택층(22)에 전기 전도성 일정 표면 밀도 코팅(23l, 23n, 123n)이 도포된다. 제1 릴리프 구조(25, 125, 65)는 그 다른 구성요소들이 높은 깊이/폭 비 특히 >2가 되는 방식으로 구현된다. 릴리프 구조의 전체 또는 전체에 가까운 깊이를 따라 적어도 하나의 수직 또는 수직에 가까운 플랭크가 연장함으로써, 코팅 전기 전도성을 감소시키거나 제거한다.

**대 표 도 - 도1**

## 특허청구의 범위

### 청구항 1

복제 래커층(22)을 구비한 다층체(11, 12)로서, 상기 다층체의 제1 영역 내의 좌표축 x 및 y로 정의되는 평면의 상기 복제 래커층(22)에 제1 릴리프 구조(25, 125, 65)가 형성되고, 상기 다층체(11, 12)의 상기 제1 영역 내 및 상기 다층체(11, 12)의 인접한 제2 영역 내의 상기 복제 래커층(22)에 일정한 표면 밀도의 전기 전도성 코팅(231, 23n, 123n)이 도포되는 다층체에 있어서,

상기 제1 릴리프 구조(25, 125, 65)는 개별 구성요소의 깊이-대-폭 비 > 2인 구조이고, 상기 릴리프 구조의 깊이부분까지 연장하는 적어도 하나의 수직인 플랭크를 가지며, 상기 제1 릴리프 구조(25, 125, 65)의 상기 플랭크에, 상기 제1 릴리프 구조에 도포되는 상기 전도성 코팅(231, 23n, 123n)이 피착되지 않거나 상기 제1 영역에서의 상기 코팅(231, 23n, 123n)의 전기 전도도가 상기 제2 영역에 비하여 현저하게 감소되는 그러한 작은 층 두께로만 피착되는 영역이 존재하는 것을 특징으로 하는 다층체.

### 청구항 2

청구항 1에 있어서, 상기 코팅은 금속층인 것을 특징으로 하는 다층체.

### 청구항 3

청구항 1에 있어서, 상기 코팅은 투명한 전도체를 포함하는 것을 특징으로 하는 다층체.

### 청구항 4

청구항 1 내지 3 중 어느 한 항에 있어서, 상기 제1 릴리프 구조(25, 125, 65)는, 상기 제1 릴리프 구조(25, 125, 65)의 깊이를 상기 x 방향 및 상기 y 방향 중 하나 이상의 방향으로 주기적으로 변화시키는, 상기 좌표 x 및 y 중 하나 이상의 함수의 형태인 것을 특징으로 하는 다층체.

### 청구항 5

청구항 4에 있어서, 상기 제1 릴리프 구조(25)는, 상기 제1 릴리프 구조(25)의 깊이를 상기 x 방향으로 또는 상기 y 방향으로 주기적으로 변화시키는, 좌표 x 또는 y의 구형파(rectangular) 함수의 형태인 것을 특징으로 하는 다층체.

### 청구항 6

청구항 4에 있어서, 상기 제1 릴리프 구조(125)는, 상기 제1 릴리프 구조(125)의 깊이를 상기 x 방향으로 또는 상기 y 방향으로 주기적으로 변화시키는, 좌표 x 또는 y의 톱니 함수의 형태인 것을 특징으로 하는 다층체.

### 청구항 7

청구항 4에 있어서, 상기 제1 릴리프 구조(65)는, 상기 제1 릴리프 구조(65)의 깊이를 상기 x 방향으로 및 상기 y 방향으로 주기적으로 변화시키는, 상기 좌표 x 및 y의 구형파 함수 또는 톱니 함수의 형태이고, 상기 함수들의 수직 플랭크는 자체로 단혀 있는 볼록 곡선을 형성하는 것을 특징으로 하는 다층체.

### 청구항 8

청구항 1에 있어서, 상기 인접한 제2 영역 내의 상기 복제 래커층(22)에 제2 릴리프 구조(26)가 형성되는 것을 특징으로 하는 다층체.

### 청구항 9

청구항 8에 있어서, 상기 제2 릴리프 구조(26)는 평탄한 것을 특징으로 하는 다층체.

### 청구항 10

청구항 8에 있어서, 상기 제2 릴리프 구조(26)는 상기 제2 릴리프 구조(26)의 깊이를 상기 x 방향 및 y 방향 중 하나 이상으로 변화시키는, 상기 좌표 x 및 y 중 하나 이상의 함수의 형태이고, 그 함수는 수직 플랭크 없

이 형성되는 것을 특징으로 하는 다층체.

### 청구항 11

청구항 8에 있어서, 제2 릴리프 구조(26)에 도포되는 상기 코팅(231)은 투명한 것을 특징으로 하는 다층체.

### 청구항 12

청구항 11에 있어서, 상기 투명한 코팅은 1nm와 100nm 사이의 두께의 금속층의 형태인 것을 특징으로 하는 다층체.

### 청구항 13

청구항 1 내지 3 중 어느 한 항에 있어서, 상기 다층체는 전사 필름인 것을 특징으로 하는 다층체.

### 청구항 14

청구항 1 내지 3 중 어느 한 항에 기재된 다층체를 구비한 회로.

### 청구항 15

청구항 1 내지 3 중 어느 한 항에 기재된 다층체를 구비한, 선형 편광기.

### 청구항 16

청구항 15에 기재된 선형 편광기의 형태의 영역들을 갖는 시큐리티 소자로서, 상기 영역들은 정보 캐리어의 형태인, 시큐리티 소자.

### 청구항 17

청구항 1 내지 3 중 어느 한 항에 기재된 다층체를 구비한, 시큐리티 문서.

### 청구항 18

다층체(11, 12)의 제조 프로세스로서, 상기 프로세스에서 상기 다층체(11, 12)의 제1 영역 내의 상기 다층체의 복제 래커층(22)에 제1 릴리프 구조(25, 125)가 형성되고, 상기 다층체(11, 12)의 상기 제1 영역 내 및 상기 다층체(11, 12)의 인접한 제2 영역 내의 상기 복제 래커층(22)에 일정한 표면 밀도의 전기 전도성 코팅(231, 23n, 123n)이 도포되는 다층체의 제조 프로세스에 있어서,

상기 제1 릴리프 구조(25, 125)는 개별 구성요소의 깊이-대-폭 비  $> 2$  인 구조이고, 적어도 하나의 수직인 플랭크를 가지고 형성되며, 상기 제1 릴리프 구조(25, 125)의 상기 플랭크에, 상기 제1 릴리프 구조에 도포되는 상기 전도성 코팅(231, 23n, 123n)이 피착되지 않거나 상기 제1 영역에서의 상기 코팅(231, 23n, 123n)의 전기 전도도가 상기 제2 영역에 비하여 현저하게 감소되는 그러한 작은 층 두께로만 피착되는 영역이 존재하는 것을 특징으로 하는 다층체의 제조 프로세스.

### 청구항 19

청구항 18에 있어서, 상기 코팅(231, 23n, 123n)은 스퍼터링에 의해 상기 복제 래커층(22)에 도포되는 것을 특징으로 하는 다층체의 제조 프로세스.

### 청구항 20

청구항 19에 있어서, 상기 코팅(231, 23n, 123n)은 전자빔 기상 증착에 의해 상기 복제 래커층(22)에 도포되는 것을 특징으로 하는 다층체의 제조 프로세스.

### 청구항 21

청구항 20에 있어서, 상기 코팅(231, 23n, 123n)은 저항 가열에 의한 열 기상 증착에 의해 상기 복제 래커층(22)에 도포되는 것을 특징으로 하는 다층체의 제조 프로세스.

### 청구항 22

청구항 18 내지 21 중 어느 한 항에 있어서, 상기 코팅(231, 23n, 123n)은 갈바니전류로 보강되는 것을 특징으로 하는 다층체의 제조 프로세스.

### 청구항 23

청구항 18에 있어서, 상기 릴리프 구조는 UV 복제에 의해 상기 복제 래커층(22) 내에 형성되는 것을 특징으로 하는 다층체의 제조 프로세스.

## 명세서

### 기술 분야

[0001] 본 발명은 릴리프 구조(relief structure)가 형성되어 있고 전기 전도성 코팅을 구비하는 복제 래커층을 갖는 다층체에 관한 것이다.

### 배경기술

[0002] 필름 엘리먼트 형태의 다층체는 예를 들면, 광학 효과를 생성하는 시큐리티 소자(security element)로서 다수의 영역에서 사용된다. 그러한 다층체는 또한 전기 회로 장치의 일부로서 사용되거나, 그러한 다층체 자체가 전기 회로 장치 예컨대, 스위칭 장치를 형성한다. 그러한 회로는 예컨대, 소위 RFID 태그(RFID = radio frequency identification: 라디오 주파수 식별) 즉, 라디오 주파수에 의해 물품을 식별하기 위한 물품 라벨(article label)로서 사용된다. 용어 RF 식별은 통상적으로 물체나 사람과 관련되는 트랜스폰더(transponder)와 판독 디바이스 사이의 비접촉식 RF 통신을 나타내는 데 사용된다. 그 경우에, 트랜스폰더는 예를 들면, 공진 회로의 일부분이고/하거나 반도체 칩에 접속되는 안테나를 갖는다.

[0003] 그러한 사용 목적을 위해, 전도성 구조가 필름 엘리먼트 상이나 내에, 그러한 구조가 매우 작은 치수로 제조되어야 한다. 여러 가지 처리 단계가 그러한 목적으로 실행되어야 하는데, 그것은 예컨대, 전기 전도층을 에칭하는 것과 같이 노동 집약적, 환경 오염적 또는 품질 저하적이다. 예컨대, 전도성 구조 아래에 배치되는 반도체 층이 오염될 수 있는 에칭 동작으로 인해, 그 점에 있어서는 매우 소량의 외래 원자(foreign atoms)가 바로 중요한 인터럽트원일 수 있다.

[0004] 회로의 층 구조로 인해, 통상적으로는 그러한 처리 단계의 복수의 사이클이 필요하게 되어, 정확한 레지스터 관계로 제조하기 위해서는 추가의 지출이 초래된다.

### 발명의 상세한 설명

[0005] 그래서, 본 발명의 목적은 특정 결점을 회피하고 높은 레벨의 정확도 및 높은 레벨의 해상도를 갖고 저비용으로 제조될 수 있는 전기 전도성 코팅을 구비한 다층체를 제공하는 것이다.

[0006] 본 발명의 목적은 복제 래커층을 갖는 다층체에 의해 달성되며, 여기에서 상기 다층체의 제1 영역 내의 좌표축 x 및 y로 정의되는 평면의 상기 복제 래커층에 제1 릴리프 구조가 형성되고, 상기 다층체의 상기 제1 영역 내 및 상기 다층체의 인접한 제2 영역 내의 상기 복제 래커층에 일정한 표면 밀도의 전기 전도성 코팅이 도포된다. 제1 릴리프 구조는 개별 구성요소의 높은 깊이-대-폭 비를 갖는, 특히 깊이-대-폭 비  $> 2$ 인 구조이고, 상기 릴리프 구조의 깊이의 전체 또는 상당한 부분까지 연장하는 적어도 하나의 수직이거나 거의 수직인 플랭크를 가지며, 상기 제1 릴리프 구조의 상기 플랭크에, 상기 제1 릴리프 구조에 도포되는 상기 전도성 코팅이 피착되지 않거나 상기 플랭크의 영역에서의 상기 코팅의 전기 전도도가 현저하게 감소되는 그러한 작은 충 두께로만 피착되는 영역이 존재한다.

[0007] 본 발명의 목적은 또한 다층체를 제조하는 프로세스에 의해서 달성되며, 상기 프로세스에서, 상기 다층체의 제1 영역 내의 상기 다층체의 복제 래커층에 제1 릴리프 구조가 형성되고, 상기 다층체의 상기 제1 영역 내 및 상기 다층체의 인접한 제2 영역 내의 상기 복제 래커층에 일정한 표면 밀도의 전기 전도성 코팅이 도포된다. 제1 릴리프 구조는 개별 구성요소의 높은 깊이-대-폭 비를 갖는, 특히 깊이-대-폭 비  $> 2$ 인 구조이고, 적어도 하나의 수직이거나 거의 수직인 플랭크를 가지며, 상기 제1 릴리프 구조의 상기 플랭크에, 상기 제1 릴리프 구조에 도포되는 상기 전도성 코팅이 피착되지 않거나 상기 플랭크의 영역에서의 상기 코팅의 전기 전도도가 현저하게 감소되는 그러한 작은 충 두께로만 피착되는 영역이 존재한다.

[0008] 제1 릴리프 구조가 그러한 높은 깊이-대-폭 비를 갖고 적어도 하나의 수직이거나 거의 수직인 플랭크를 갖고 제

조되는 사실은, 릴리프 구조의 플랭크에 상기 제1 릴리프 구조에 도포되는 상기 전도성 코팅이 피착되지 않거나, 상기 플랭크의 영역에서의 상기 코팅의 전기 전도도가 현저하게 감소되는 그러한 작은 충 두께로만 피착되는 영역이 존재하거나, 코팅이 거기에서 전체적으로 인터럽트되는 것을 의미한다. 달성될 수 있는 높은 레벨의 해상도는 그 점에서 특히 이점이 되며, 즉, 후속 에칭과 함께 노광 프로세스에 의해 구현될 수 없는 것과 같은 매우 미세한 전도 구조를 생성하는 것이 가능하게 된다. 본 발명에 의해, 전도 영역의 표면 저항을 정밀하게 조정하고, 그 방식으로 판독될 수 있는 정보의 아이템을 시큐리티 소자로 인코드하는 것도 또한 가능하다.

[0009] 무차원 깊이-대-폭 비는 구조 특히 마이크로구조의 특징부여에 관한 특징적인 특성이다. 그것은 바람직하게는, 주기적인 구조 예컨대, 톱니형상 구조를 설명하는 데 사용된다. 여기에서, 구조의 최고 및 최저의 연속적인 점들간의 간격은 깊이로 식별되고, 즉, 이것은 "피크"와 "골(trough)" 사이의 간격을 포함한다. 2개의 인접한 최고점들 사이, 즉, 2개의 "피크" 사이의 간격은 폭(주기)이라고 한다. 이하, 깊이-대-폭 비가 더 높을수록, 대응하여 "피크 플랭크"가 더 경사가 커진다. 설명하는 모델은 비주기적인 구조에도 적용될 수 있다. 예를 들면, 이것은 "골"의 형태로만 있는 이산 분포된 라인형상 영역을 포함할 수 있고, 2개의 "골" 사이의 간격은 "골"의 깊이보다 배수만큼 더 크다. 상술한 정의의 공식 적용 시에, 그러한 방식으로 계산된 깊이-대-폭 비는 대략 0이 되고 특징적인 물리적 조건을 반영하지 않는다. 따라서, 실질적으로 "골"로부터만 형성되는 이산 배열된 구조의 경우에, "골"의 깊이는 "골"의 폭과 관련될 것이다.

[0010] 상술한 이점에도 불구하고, 본 발명에 따르는 제조 프로세스는 도체 트랙을 구성하는 복잡한 고가의 프로세스를 회피하고 있으므로 저가이다.

[0011] 제1 릴리프 구조는 상기 제1 릴리프 구조의 깊이를 상기 x 방향으로 및/또는 상기 y 방향으로 주기적으로 변화시키는, 상기 좌표 x 및/또는 y의 함수의 형태인 것이 제공된다. 그 점에 있어서, 바람직한 함수는 적어도 하나의 수직 플랭크 또는 측면을 제공하는 것이다. 톱니 함수 및 구형파(rectangular) 함수가 바람직하다. 날카로운 에지를 갖는 수직 플랭크가 전도성 코팅이 에지를 따라 정해진 외곽에 의해 인터럽트되는 방식으로 형성된다. 그러한 방식으로, 제1 릴리프 구조 상의 코팅은 에지에 수직인 방향으로 전기적으로 비전도성이거나, 매우 높은 레벨의 전기 저항을 포함한다.

[0012] 수평에 대해 각도  $\alpha$ 로 경사져 있는 경사진 플랭크 상에 피착되는 코팅의 두께  $t$ 는 아래 관계에 의해 주어진다.

$$t = t_0 \cdot \cos \alpha$$

[0014] 이 관계에서,  $t_0$ 은 수평면 상에 피착된 코팅의 두께이다. 그 점에 있어서, 두께  $t_0$ 은 경사진 플랭크가 "스머지(smudged)"되지 않는, 즉 코팅 재료가 없거나 평坦한 표면에 관련하여 현저히 감소되는 충 두께만이 거기에 피착되는, 방식으로 코팅 재료에 따라 조정되어야 한다. 증가한 두께  $t_0$ 으로, 예를 들어, 코팅 재료의 입자가 입자 스트림의 일반적인 궤적으로 이동하지 않으면 수직이거나 거의 수직인 팽팽크 상에 중착이 또한 형성될 수도 있다. 최적값은 바람직하게는 일련의 실험에 의해 확인될 수 있다. 두께  $t_0$ 의 최적값은, 제1 릴리프 구조의 플랭크에서, 제1 릴리프 구조에 도포된 전도성 코팅이 피착되지 않거나 코팅의 전기 전도도가 플랭크의 영역에서 현저하게 감소되는 그러한 작은 충 두께만으로 피착되는 영역들의 생성에 지향되고 있다.

[0015] 비구조화 영역의 두께  $t_0$ 은 500nm 미만, 바람직하게는 50nm 미만이 되어야 한다. 최적 두께  $t_0$ 은 유리하게는 테스팅에 의해 결정될 수 있으므로, 코팅 재료의 전기 및 다른 성질에 대한 코팅 재료의 영향을 고려하는 것도 가능하게 된다.

[0016] 코팅될 릴리프 구조가 높은 깊이-대-폭 비를 가지면, 제1 릴리프 구조에 도포된 전도성 코팅이 피착되지 않거나 코팅의 전기 전도도가 플랭크의 영역에서 현저하게 감소되는 그러한 작은 충 두께로만 피착되는 제1 릴리프 구조의 수직이거나 거의 수직인 플랭크 상에 영역들을 형성하는 효과가 유리하게 향상된다. 바람직하게는 릴리프 구조의 깊이-대-폭 비는 >2인 것이 제공될 수 있다.

[0017] 도시된 테스트와 같이, 플랭크의 각도  $\alpha$ 는 설명한 효과에 대한 의심 없이, 수직에서 약 10° 만큼의 크기가 상이할 수 있다.

[0018] 플랭크 상의 코팅의 두께  $t$ 는 각도  $\alpha$ 의 선택에 의해 조정될 수 있다. 그러한 점에 있어서, 각도  $\alpha$ 는 곡선의 제1 미분계수에 의해 결정될 수 있는 곡선 부분의 그레디언트 각도일 수도 있다.

- [0019] 제1 릴리프 구조가 좌표의 함수의 형태이면, 릴리프 구조는 특히 간단한 구성으로 된다. 특히, 제1 릴리프 구조는 예컨대, 50nm와 10μm 사이의 범위의 작은 격자 주기를 갖는 회절 구조일 수 있다. 그러한 릴리프 구조는 선형 회절 격자일 수 있다.

- [0020] 선형 편광기가 그러한 방식으로 바람직하게는 100nm와 800nm 사이의 주기 길이를 갖고 형성된다. 바람직하게는 코팅은 두께  $t_0 < 10\text{nm}$ 로 될 수 있다. 제1 릴리프 구조의 높은 가능성의 해상도에 의해, 선형 편광기의 구성은 발진면에서의 편광을 위한 구성으로 제한되지 않는다. 오히려, 그러한 방식으로 서로 병렬 관계의 영역들이 다른 편광 방향으로 제공될 수 있고, 그러한 점에 있어서 영역들은 정보 캐리어의 형태일 수 있는 것이 제공될 수 있다. 예로서, 영역들은 머신 판독 가능한 바 코드를 형성할 수 있거나 영숫자 문자(alphanumeric character)나 이미지나 그래픽 표시의 형태일 수 있다. 그들 영역은, 예를 들면, 그것에 또는 그것을 통해 방사되는 광의 방향에 수직하게 편광면이 배향되는 것처럼 배향되면, 편광된 광으로 보여질 수 있으므로, 그들 영역은 배경으로부터 음영을 두드러지게 한다. 상술한 구조와 관련하여 편광되지 않은 광으로 조명 시에, 숨겨진 정보의 아이템이 나타나게 하는 "복호" 필름을 제공하는 것도 가능하게 된다.

- [0021] 그러나, 제1 릴리프 구조는 2개의 좌표의 함수의 형태이고, 제공된 수직 플랭크는 자체로 닫혀 있는 곡선의 형태인 것이 제공될 수도 있다. 도포된 코팅의 전기 전도성은 그러한 방식으로 모든 방향으로 인터럽트된다. 바람직하게는, 닫힌 곡선은 원, 타원, 사각형, 직사각형 및 마름모꼴의 형태인 것이 제공될 수 있다.

- [0022] 그러나, 닫힌 곡선은 제2 릴리프 구조가 형성되는 인접한 제2 영역의 외형에 따르는 것이 제공될 수도 있다. 바람직하게는, 제2 릴리프 구조는 평탄한 구성으로 된 것이 제공된다. 그러한 방식으로, 제2 릴리프 구조에 도포되는 전기 전도성 코팅은 전체 두께  $t_0$ 의 전기 도체의 형태이다. 임의의 원하는 방식으로 외형을 나타내는 전기 전도성 제2 영역이 제1 전기 비전도성 영역에 의해 둘러싸일 수 있기 때문에, 그러한 방식으로 일반적인 코팅 단계에 의해 높은 레벨의 정확도 및 해상도를 갖는 임의의 기하학적 형상의 상호 전기 절연성 도체 경로를 생성하는 것이 가능하다.

- [0023] 종속하는 청구항에 추가의 유리한 구성이 나타나 있다.

- [0024] 바람직하게는 전기 전도성 코팅은, 바람직하게는 알루미늄, 구리, 은 또는 금과 같은 양호한 전기 도체로부터 형성되는 금속층의 형태인 것이 제공된다. 그러나, 코팅은 예컨대, 디스플레이에 사용되는 것과 같이, "비가시성(invisible)" 도체 트랙을 형성하기 위해 그 투명도에 의해 선호되는 예컨대, 인듐-주석 산화물층(ITO)과 같은 투명한 전도체의 형태인 것이 제공될 수 있다. 태양광 발전용 전극층은 동일한 원리에 기초하여 제조될 수 있다.

- [0025] 그러나, 금속성 코팅은 예컨대, 1nm와 100nm 사이의 두께, 바람직하게는 5nm와 30nm 사이의 두께를 갖고 형성되어 너무 얇아 투명하게 나타내는 것이 제공될 수도 있다. 그것은 예컨대, LCD 디스플레이용으로 제공되는 것과 같은 저전류용 "비가시성" 도체 트랙이 그러한 방식으로 제조되면 유리할 수 있다.

- [0026] 특히, 도체 트랙을 제조할 때, 코팅은 도체 트랙의 에지에서 확실히 인터럽트되는 것이 중요하다. 그러한 목적으로, 바람직한 층 두께  $t_0$ 은 5nm와 50nm 사이의 범위에 있을 수 있다. 지금까지 설명한 바와 같이, 그들 얇은 도체 트랙의 전도도는 갈바니전류 요법에 의해 필요한 경우 증가될 수 있다.

- [0027] 바람직하게는, 다층체는 필름 엘리먼트의 형태 예컨대, 전사 필름 특히 적층 필름의 형태나 스티커 필름의 형태의 핫스탬핑 필름이다. 그 경우, 필름 엘리먼트는 전사 필름의 도포된 전사층에 의해 형성될 수도 있다. 그러나, 다층체는 강성 기판층 예컨대, 얇은 유리층을 포함하는 것이 제공될 수도 있다.

- [0028] 전기 전도성 코팅은 예컨대, 스퍼터링, 전자빔 기상 증착 또는 저항 가열에 의한 열 기상 증착에 의해 시큐리티 소자의 제조로부터 알려진 프로세스로 도포될 수 있다. 그들 프로세스는 코팅이 표면 영역에 관하여 일정한 밀도를 갖는 스프레잉에 의해 좌표축 x 및 y에 의해 정의된 평면에 대하여 도포되는 것과 구별된다. 바람직하게는 원자나 분자가 평면, 즉, 코팅될 표면에 대략 동일한 각도로 충돌한다.

- [0029] 원자나 분자가 코팅될 표면 상으로 수직으로 충돌하여 수직이거나 거의 수직인 플랭크에 증착되지 않게 되는 것이 유리하게 제공될 수 있다.

- [0030] 따라서, 이들은 원자나 분자가 무방향식으로 증착되는 코팅 프로세스를 포함하지 않음으로써, 대략 동일한 층 두께의 층에 플랭크 경사에 무관하게 피착된다. 무방향성 증착은 예를 들면, 가스 상태 외의 증착을 포함할 수 있다.

- [0031] 바람직하게는 릴리프 구조가 복제 래커층에 UV 복제에 의해 형성되는 것이 제공된다.

- [0032] 본 발명에 따르는 구조 및 본 발명에 따르는 프로세스의 사용은 다수의 상이한 방법으로 가능하고, 회절성 필름 엘리먼트가 전기 회로 배열을 보유하기 위한 것이거나 그 자체로 전기 회로의 일부일 때, 항상 특히 유리하다.

- [0033] 폴리머 전자기기의 반도체 부품의 전극층이 본 발명에 의해 구성되는 것도 가능하다. 본 발명은 높은 레벨의 해상도를 달성하는 것을 가능하게 만든다. 폴리머 회로의 도체 트랙이나 다른 전기 부품 예컨대, RFID 태그 (RFID = 라디오 주파수 식별)용 코일 및 커패시터가 설명한 방식으로 제조되는 것이 또한 제공된다. 그러한 점에 있어서, 본 발명은 그러한 종류의 구조의 제조를 위해 낮은 폐기물 거부율을 갖는 저가의 제조 기술을 제공하는 것이 특히 유리하다. 본 발명에 따르는 프로세스에 의해 달성될 수 있는 미세 구조화로 인해, 그러한 방식으로 그들 반도체 부품의 한계 주파수가 더욱 현저하게 증가되는 것이 가능하게 된다.

- [0034] 전도성 코팅이 갈바니전류로 강화되는 것이 제공될 수 있으며, 그러한 방식으로 특히 양호한 전도성 표면층이 도포되거나 괴착된 층의 두께가 전기 저항을 감소시키도록 증가된다. 상술한 증착 프로세스는 바람직하게는 얇은 층의 도포용으로 적합하다. 밝혀진 바와 같이, 릴리프 구조는 갈바니전류 요법 시행 시에 변경되지 않는다, 즉, 전기적으로 비전도성 영역이 덮여지지 않는다.

- [0035] 본 발명에 따르는 프로세스에 의해 필름 제조의 형태로 특히 저렴하게 선형 편광기와 같은 추가의 부품을 제조하는 것이 가능하다.

- [0036] 본 발명은 첨부하는 도면을 참조하여 이하 다수의 실시예에 의해 예로서 설명한다.

### 실시예

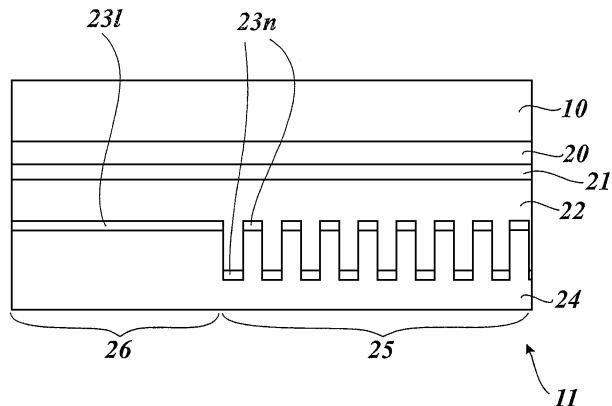

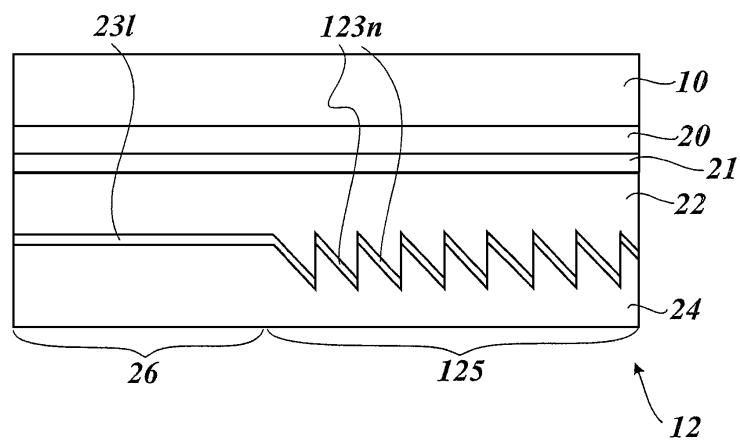

- [0044] 도 1은 이하 필름 엘리먼트(11)라고 하는 필름 엘리먼트의 형태로 다층체를 도시한다. 필름 엘리먼트(11)는 캐리어막 또는 캐리어층(10), 릴리즈막(20), 보호 래커층(21), 릴리프 구조(25 및 26)를 갖는 복제 래커층(22), 릴리프 구조(25 및 26)와 접착층(24) 상에 배치되는 코팅(231, 23n)을 포함한다. 릴리프 구조(26)는 평탄한 릴리프 구조의 형태이다. 릴리프 구조(25)는 높은 폭 대 깊이비를 갖는 구조이므로, 릴리프 구조는 예를 들면, 시큐리티 소자에 광학 효과를 생성하도록 형성되는 보통의 릴리프 구조보다 높은 배수인 유효 표면적을 갖는다. 릴리프 구조(25)는 평탄한 릴리프 구조(26)의 표면에 수직인 플랭크(flank)를 갖는 미엔드형상(meander-shaped)의 구성으로 되어 있다. 예시된 실시예에서, 릴리프 구조는 동등한 방향으로 연장한다. 그러한 방식으로, 영역 관계로 도포되는 코팅(23n)은 평탄한 릴리프 구조(26)의 표면에 평행한 릴리프 구조(25)의 부분 상에만 배치되며, 즉, 코팅은 동등한 방향으로 인터럽트되는 코팅이다. 그러한 동등한 방향으로 인터럽트되는 릴리프 구조는 이하 1차원 릴리프 구조라고 한다. 도 1에 도시된 바와 같이, 인터럽트는 전체에 걸쳐 계속된다. 반대로, 평탄한 릴리프 구조(26) 상에 배치된 코팅(231)은 닫힌 구조로 되어 있다.

- [0045] 예시된 실시예에서는, 릴리프 구조의 구성에 의해 그리고 재료의 선택에 의해 다른 효과들이 산출될 수 있다. 예를 들어, 코팅(231, 23n)이 금속층의 형태이면, 코팅(23n)은 릴리프 구조의 수직 플랭크에서 전체적으로 인터럽트되기 때문에, 비전도성 금속층이다. 반대로, 평탄한 릴리프 구조(26)에 도포된 금속층은 인터럽트되지 않기 때문에 전기 전도되고 있다. 코팅(23n)은 예컨대, 스퍼터링에 의해 즉, 릴리프 구조 상에 대략 동일한 코팅 방향의 입자가 충돌하는 코팅 프로세스에 의해 도포될 수 있다. 따라서, 코팅 방향에 평행하게 배치되는 수직 플랭크에서의 입자 충돌이 없거나 상당히 적어, 코팅(23n)이 인터럽트되거나, 예컨대, 수직 플랭크 외부의 전도성 코팅(231)의 단위 표면적당 저항보다 적어도 10의 계수만큼 높은, 바람직하게는 계수 1000만큼 높은 상당히 높은 단위 표면적당 저항을 갖는다.

- [0046] 그러한 코팅 프로세스는 좌표축 x 및 y에 의해 정의되는 면에 대하여, 표면적에 관련하여 일정한 밀도를 갖는 코팅을 도포하는 것에 더욱 차이가 있으며, 유리하게는 코팅 방향이 그 면에 수직이거나 대략 수직으로 배향된, 릴리프 구조의 플랭크에 평행하게 배향될 수 있다.

- [0047] 유리하게는 >2인 릴리프 구조(25)의 높은 깊이-대-폭 비는 플랭크 각도에 의존하는 코팅의 두께의 제공에 관해서술된 효과에 실질적인 공헌을 한다. 한편, 높은 깊이-대-폭 비는 급격한 경사의 플랭크를 제공하는 반면에, 설정된 코팅 방향에서 벗어난 입자의 랜덤 증착이 더욱 어렵게 되게 한다.

- [0048] 평탄한 릴리프 구조(26)에 생성되는 코팅의 두께가 추가의 영향을 주는 인자이다. 테스트가 나타내는 바와 같이, 상술한 효과는 두께 < 500nm인 경우에 발생한다.

- [0049] 바람직하게는, 평탄한 릴리프 구조(26) 상에 생성되는 전도성 코팅의 두께는, 적어도 영역방향으로 전도성 코팅

이 형성되지 않는 릴리프 구조에서 수직이거나 대략 수직인 플랭크를 얻기 위해 < 50nm일 수 있다.

[0050] 그러한 층은 예컨대, 약 10nm의 두께로 된 투명하게 되는 것이 제공될 수 있다. 그런 방식으로, 그 아래 배치되는 구조 예컨대, LCD 표시 소자를 가시적으로 덮지 않는 반도체 트랙을 형성하는 것이 가능하게 된다.

[0051] 필름 엘리먼트(11)는 스템핑(stamping) 또는 양각(embossing) 필름, 특히 핫 스템핑 필름이다. 그러나, 필름 엘리먼트(11)가 적층 필름이나 스티커 필름의 형태 또는 회로 특히 폴리머 회로용 캐리어의 형태가 되게 할 수 있다.

[0052] 캐리어막 또는 캐리어층(10)은 10μm와 50μm 사이의 층 두께의, 바람직하게는 19μm와 23μm 사이의 두께의 PET 또는 POPP 필름을 포함한다. 릴리즈층(20) 및 보호 래커층(21)은 그 후 음각 인쇄 스크린 실린더에 의해 캐리어 필름에 도포된다. 그 경우에, 릴리즈 및 보호 래커층(20 및 21)은 바람직하게는 0.2μm와 1.2μm 사이의 두께이다. 또한 그들 층을 생략하는 것도 가능하다.

[0053] 복제 래커층(22)이 그 후 도포된다.

[0054] 복제 래커층(22)은 바람직하게는 방사 교차 결합 가능(radiation-crosslinkable) 복제 래커를 포함한다. 바람직하게는 UV 복제 프로세스가 복제 래커층(22)에 릴리프 구조(25 및 26)를 형성하는 데 사용된다. 그 경우에, UV 경화성 래커가 복제 래커로서 사용된다. 그런 상황에서, UV 경화성 복제 래커층으로의 릴리프 구조(25 및 26)의 도입은 예를 들면, 래커층에 릴리프 구조를 형성할 때 그것이 여전히 연성이거나 유체일 때 UV 조사에 의해, 또는 UV 교차 결합 가능 래커층의 경화 및 부분 조사에 의해 영향을 받는다. 그 경우에, UV 교차 결합 가능 래커 대신에, 다른 방사 교차 결합 가능 래커를 사용하는 것도 가능하다.

[0055] 또한, 복제 래커층(22)이 투명한 열가소성 재료를 포함하는 것이 또한 가능하다. 릴리프 구조나 복수의 릴리프 구조 예컨대, 릴리프 구조(25 및 26)는 스템핑 도구에 의해 복제 래커층(22)에 스템핑된다.

[0056] 복제 래커층(22)에 대해 선택되는 두께는 릴리프 구조(25)에 대해 선택된 프로파일(profile) 깊이에 의해 결정된다. 복제 래커층(22)은 릴리프 구조(25 및 26)가 형성될 수 있기에 충분한 깊이로 되어 있는 것을 확실하게 할 필요가 있다. 바람직하게는 그 경우에, 복제 래커층(22)은 0.1μm와 10μm 사이의 두께로 되어 있다.

[0057] 예로서, 복제 래커층(22)은 라인 래스터 음각 인쇄 실린더에 의해 건조하기 전에 2.2g/m<sup>2</sup>의 도포 무게로 보호 래커층(21)에 포함되는 전체 표면 영역 상에 도포된다. 그 경우에, 아래의 조성의 래커가 복제 래커로 선택된다:

| [0058] | <u>조성</u>     | <u>무게와의 비율</u> |

|--------|---------------|----------------|

| [0059] | 고분자 PMMA 수지   | 2000           |

| [0060] | 실리콘 알카드 오일-프리 | 300            |

| [0061] | 비이온 가습제       | 50             |

| [0062] | 저점도 니트로셀룰로스   | 12000          |

| [0063] | 톨루엔           | 2000           |

| [0064] | 디아세톤 알콜       | 2500           |

[0065] 복제 래커층(22)은 그 후 100°C와 120°C 사이의 온도로 건조 통로에서 건조된다.

[0066] 릴리프 구조(25 및 26)는 약 130°C에서 예컨대, 니켈을 포함하는 다이(die)에 의해 복제 래커층(22)에 스템핑된다. 복제 래커층으로 릴리프 구조(25 및 26)를 스템핑하기 위해, 다이는 바람직하게는 전기로 가열된다. 스템핑 동작 후에 복제 래커층(22)에서 다이가 상승되기 전에, 다이는 그 경우에 다시 냉각될 수 있다. 릴리프 구조(25 및 26)가 복제 래커층(22)으로 스템핑된 후, 복제 래커층(22)의 복제 래커는 교차 결합이나 어떤 다른 방식으로 경화된다.

[0067] 또한, 릴리프 구조(25 및 26)가 삭마(ablation) 프로세스에 의해 복제 래커층(22)에 도입되는 것도 가능하다.

[0068] 그 점에 있어서, 릴리프 구조(25 및 26)는 통상의 코팅 프로세서 예컨대, 스퍼터링에서 코팅(231, 23n)으로 코팅되는 릴리프 구조를 포함한다.

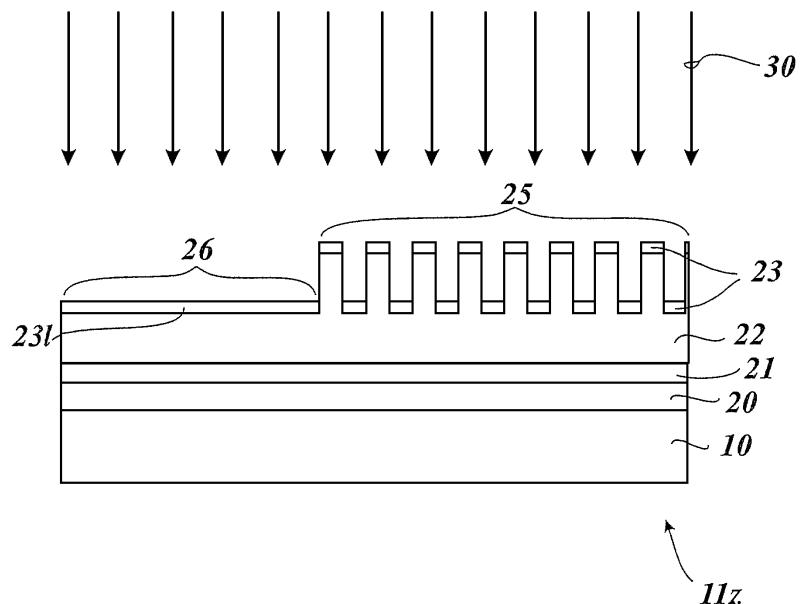

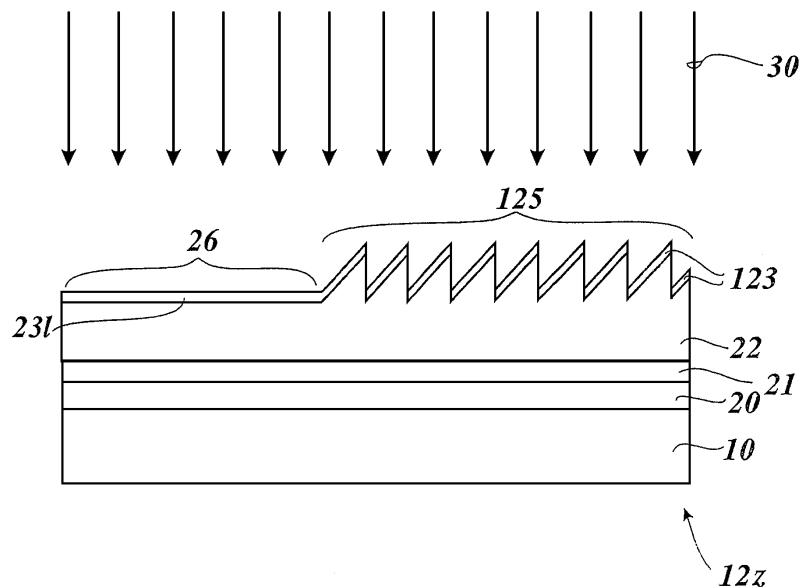

[0069] 도 2로부터 알 수 있는 바와 같이, 코팅(231, 23n)의 증착을 위한 코팅 방향은 평탄한 릴리프 구조(16)의 표면

에 수직으로 배향된다. 배향 방향은 도 2에서 화살표 30으로 식별된다. 그 점에 있어서, 코팅 장치는, 재료가 일정한 표면 영역 밀도를 갖고 릴리프 구조(25 및 26) 상에 피착되어, 그러한 프로세스 단계의 결과 릴리프 구조(25 및 26) 상의 코팅(231, 23n)의 표면 영역 밀도가 같고 일정하게 되는 방식으로 설계된다. 따라서, 그러한 방식으로, 예를 들면, 코팅(231, 23n)의 전도성을 상이하게 만들기 위해 및/또는 코팅(231, 23n)의 기하학적 형상을 생성하기 위해 어떠한 사전조치도 필요없다. 그것에 관하여, 코팅(231, 23n)의 구성이 하나의 제조 단계에서의 정확한 레지스터 관계로 이루어질 수 있고, 릴리프 구조의 미세 구조화로 인해, 예컨대, 회로를 생성할 때 필요하게 되는 만큼의 특히 높은 레벨의 해상도가 달성되는 것이 특히 유리하다.

[0070] 접착층(24)이 그 후 코팅(231, 23n)에 도포된다. 접착층(24)은 바람직하게는 열활성(thermally activatable) 접착제를 포함하는 층이다. 그러나, 시큐리티 소자(11)의 개별 사용에 따라, 접착층(24)을 없애는 것도 가능하다.

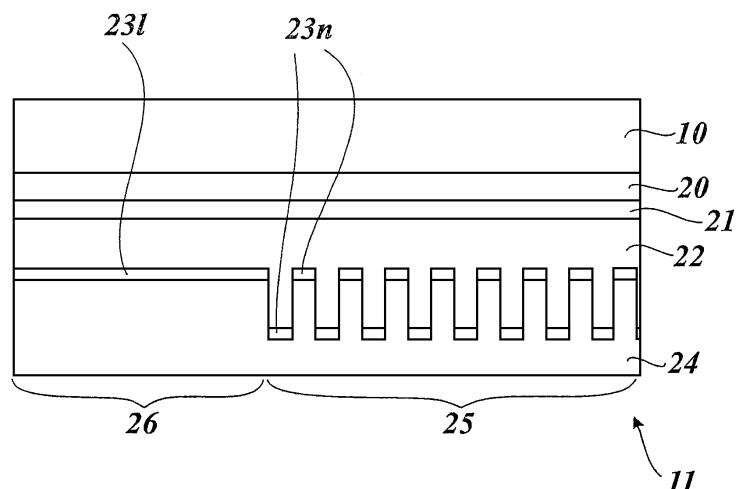

[0071] 도 3은 1차원 릴리프 구조를 갖는 필름 엘리먼트(12)의 형태로 다층체의 제2 실시예를 도시하고, 이러한 배열은 릴리프 구조의 구성에 관해서만 상술한 실시예와 상이하다. 동일한 구성요소는 따라서 동일한 참조부호로 나타난다. 도 1에서의 미엔드형상 릴리프 구조(25) 대신에, 필름 엘리먼트(12)가 톱니형상 릴리프 구조(125)로 설계된다. 릴리프 구조(125)는 평탄한 릴리프 구조(26)에 수직하게 배열되는 제1 플랭크와, 제1 플랭크와 각을 이루는 관계로 배열되는 제2 플랭크를 갖는다. 그러한 구성은 코팅(23n)이 릴리프 구조(125)의 제2 플랭크 상에만 배열되는, 즉 코팅이 인터럽트되는 구성으로 되는 것을 제공한다.

[0072] 도 4는 코팅(123n 및 231)을 갖는 도 3에서의 릴리프 구조(125 및 26)의 코팅을 도시한다. 지금까지 도 2를 참조하여 이미 설명한 바와 같이, 코팅(123n 및 231)이 예컨대, 스퍼터링에 의해 통상의 제조 단계에서 릴리프 구조(125 및 26)에 각각 도포된다. 도 4로부터 명확히 알 수 있는 바와 같이, 이 경우에, 코팅(123n)은, 도포 방향에 수직으로 배열되는 릴리프 구조(26) 상에서 보다 작은 두께로, 릴리프 구조(125)의 경사진 제2 플랭크 상에 생성된다. 코팅(123n)은 재료가 코팅되지 않는 릴리프 구조(125)의 수직 제1 플랭크에 의해 인터럽트되기 때문에, 예를 들면, 이러한 방식으로 도포된 금속층은 전기적으로 비전도성이다.

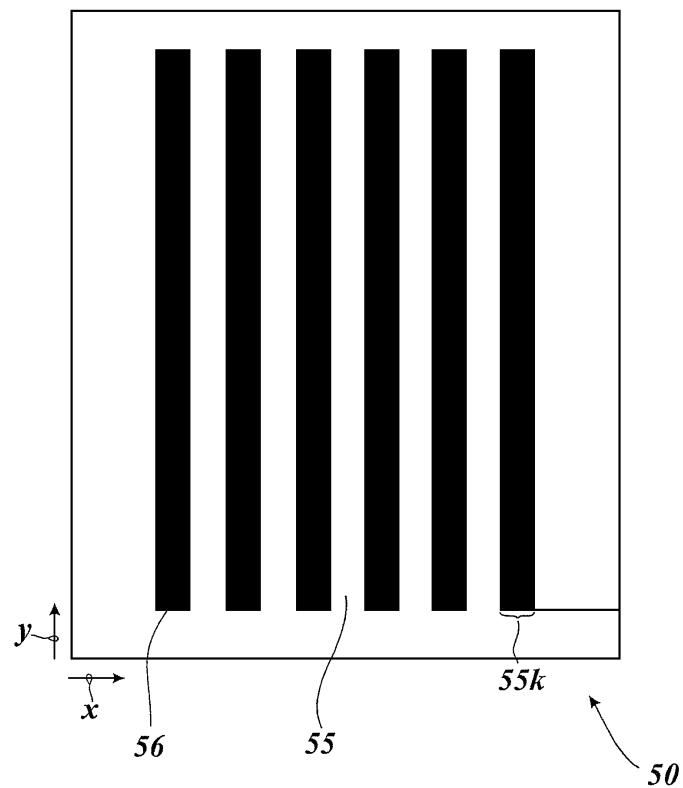

[0073] 도 5a는 예시된 실시예에서는 금속으로 코팅된, 1차원 릴리프 구조를 갖는 필름 엘리먼트(50)의 형태의 다층체의 평면도를 도시한다. 이 경우에, 높은 깊이-대-폭 비를 갖는 1차원 릴리프 구조를 갖는 전기적으로 비전도성의 영역(55)이 도 1 및 3에(각각 참조번호 25 및 125) 도시된 바와 같이, 제공되며, 그 내에 도 5에 흑색으로 도시된 전도성의 평탄한 영역(56)이 둘러싸여 있다. 이들은 여기에 도시되지 않은 전기 소자를 함께 접속하는 도체 트랙을 포함한다.

[0074] 전기적으로 비전도성의 영역(55)이 x로 분류된 좌표 방향으로만 코팅되지 않은 수직 플랭크에 의해 인터럽트되고, y방향으로 전기 전도성 영역(56)과 인접하는 부분(55k)에서 전기적으로 단락되더라도, 전체 전기 전도도는 영역(56)의 전도도보다 낮은 차수의 크기이다.

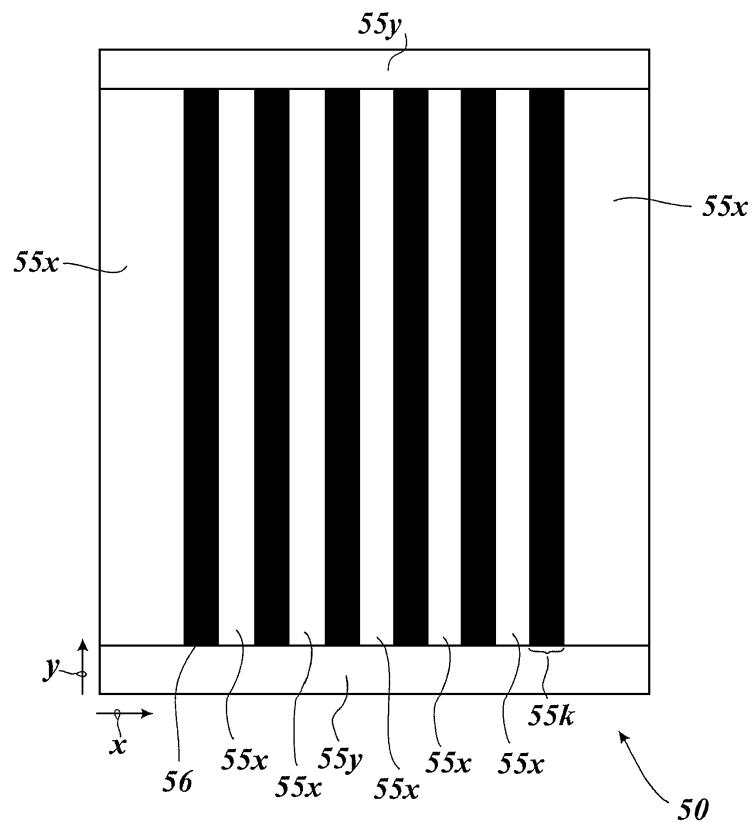

[0075] 도 5b는 전도성 영역(56)에 의해 상술한 국부 단락을 회피하는 것이 어떻게 가능한지를 도시한다. 그러한 목적으로, 영역(55)은 영역(55x) 및 영역(55y)으로 세분할되며, 그 릴리프 구조는 각각 x방향 및 y방향으로 변화한다. 그러한 배열은 전도성 영역(56)이 서로 평행한 관계로 배열되지 않거나 곡선 구성으로 되어 있을때 제공될 수 있다.

[0076] 그러나, 본 발명에 따른 프로세스로 도포된 영역(56)이 갈바니전류로 보강된(galvanically reinforced) 것이 제공될 수도 있다. 영역(55, 55x 및 55y)은 전기적으로 비전도성이기 때문에, 갈바니전류 요법 시행 시에 거기에 금속이 피착되지 않는다. 따라서, 전도성 영역(56)만 갈바니전류로 보강하기 위해 부가적인 사전조치가 취해질 필요가 없다. 그러한 방식으로, 전도성의 평탄한 영역(56)은 갈바니 전류 요법 시행 전보다 더 낮은 레벨의 특정 저항을 갖는 도체 트랙의 형태로 된다. 따라서, 영역(56)의 전기 전도성이 영역(55)의 전기 전도성에 비교하여 상당히 더 크기 때문에, 상이하게 배향된 영역(55x 및 55y)(도 5b 참조)의 형태로 영역(55)의 형성(도 5a 참조)을 없애는 것이 가능하다.

[0077] 도 5a 및 도 5b에 도시된 영역(56)은 예를 들면, 대략 10nm 크기의 매우 얇은 금속층이 거기에 도포되면, 포함되는 금속의 각 종류에 따라 다르지만, 투명할 수 있다.

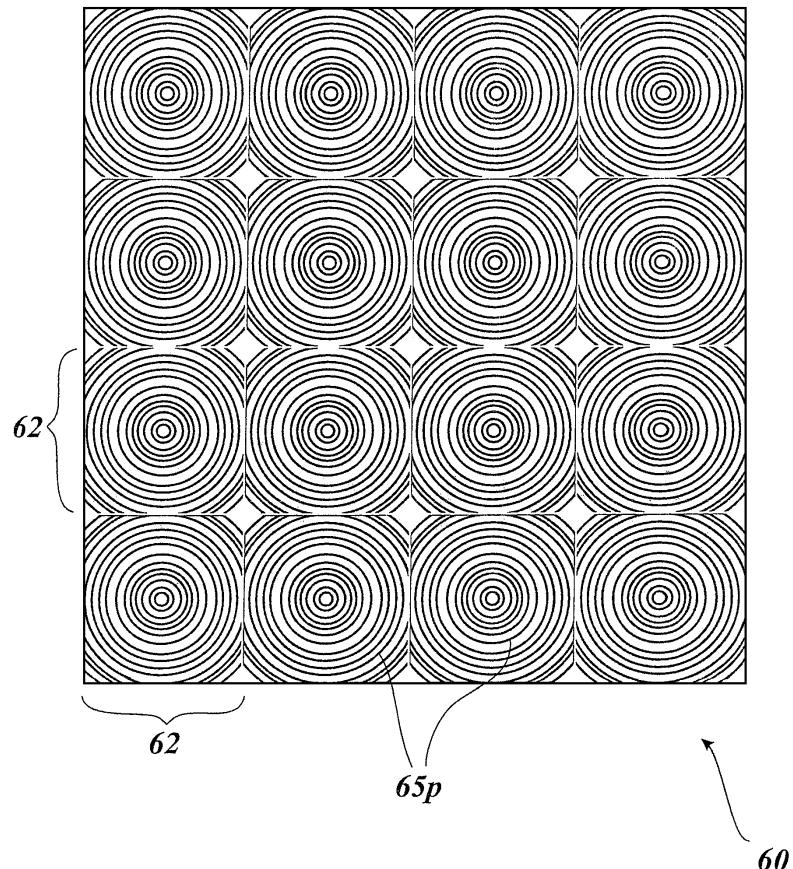

[0078] 도 6은 자체로 단혀 있는 프로파일 곡선(65p)을 형성하는 수직 플랭크와 높은 깊이-대-폭 비를 갖는 릴리프 구조(65)를 구비하는 래스터 스크린 엘리먼트(62)를 갖는 필름 엘리먼트(60)의 형태로 다층체의 평면도를 도시한다. 예시된 실시예에서는, 프로파일 곡선이 원 및 마름모의 형태이다. 필름 엘리먼트(60)는 릴리프 구조(65)로 인해 비전도성인 금속층(도시 생략)으로 코팅된다. 이것은 전기 전도성 영역에 의해 가능한 단락의 상술한

결점을 회피하는 2차원 릴리프 구조를 수반한다. 도 6으로부터 명확히 알 수 있는 바와 같이, 릴리프 구조(65)는 사각형 래스터 소자(62) 내에 내접되어 있는 동심원으로 배열된 원들로 형성된다. 그러한 방식으로, 래스터 소자(62)의 코너 영역에 원의 단편(segments)이 형성된다. 그러한 방식에서, 코너 영역의 원의 단편은 마름 모꼴 프로파일 곡선을, 3개의 추가의 래스터 소자(62)의 원의 단편이 그 코너 영역에서 인접한 상태로, 형성한다.

[0079] 래스터 소자(62)는 동일한 구성 및 동일한 크기로, 즉 이등변 삼각형, 사각형 또는 육각형의 형태로 생성되는 것이 제공될 수 있다. 래스터 소자(62)는 불규칙적인 구성으로 되는 것, 즉 상이한 구성 및 크기의 래스터 소자(62)를 갖는 필름 엘리먼트(60)의 영역을 채우는 것이 제공될 수도 있다. 단지 중요한 고려사항은 릴리프 구조(65)의 수직 플랭크가 닫힌 곡선을 형성하는 것이다.

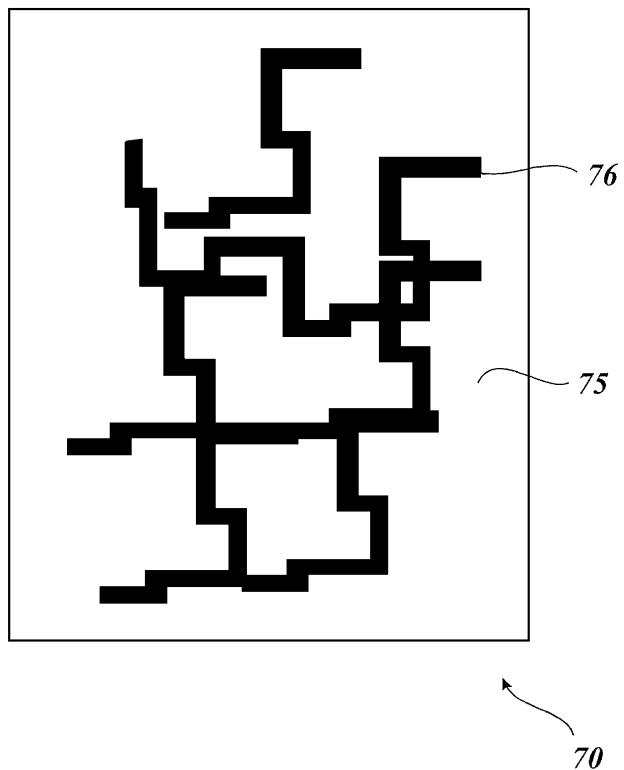

[0080] 도 7은 높은 깊이-대-폭 비를 갖는 릴리프 구성이 제공되는 영역(75)로 둘러싸인 구성된 도체(76)를 갖는 필름 엘리먼트(70)의 형태로, 금속이 코팅되는 다층체를 도시한다. 릴리프 구성은 높은 깊이-대-폭 비를 갖는 2차원 릴리프 구성(도 6 참조)이나 1차원 릴리프 구성(도 5 참조)의 형태일 수 있다. 바람직한 배열은 2차원 릴리프 구성이고 깊이-대-폭 비  $> 2$ 이다.

[0081] 필름 엘리먼트(70)는 마이크로 전자 회로의 부분의 형태 예컨대, 필름 시스템의 형태의 폴리머 회로의 부분일 수 있다. 그 점에 있어서, 회로는 지금까지 설명한 바와 같이 투명할 수 있다(도 5 참조).

[0082] 구성된 도체(76)의 하나 이상의 부분이 높은 깊이-대-폭 비를 갖는 릴리프 구조로 형성되어, 도체(76)의 전기 전도도가 그러한 부분에서 감소되는 그러한 용도와 관련하여 제공될 수 있다. 그러한 방식으로 예를 들면, 도체(76) 내에 전기 저항을 형성하는 것이 가능하다.

### 도면의 간단한 설명

[0037] 도 1은 본 발명에 따르는 다층체의 제1 실시예의 필름 엘리먼트 형태로 도시하는 단면도이다.

[0038] 도 2는 금속층을 갖는 도 1의 필름 엘리먼트의 코팅을 도시한 도면이다.

[0039] 도 3은 본 발명에 따르는 다층체의 제2 실시예의 필름 엘리먼트 형태로 도시하는 단면도이다.

[0040] 도 4는 금속층을 갖는 도 3의 필름 엘리먼트의 코팅을 도시한 도면이다.

[0041] 도 5는 다층체의 일 실시예를 1차원 릴리프 구조를 갖는 필름 엘리먼트의 형태로 도시한 평면도이다.

[0042] 도 6은 다층체의 일 실시예를 2차원 릴리프 구조를 갖는 필름 엘리먼트의 형태로 도시한 평면도이다.

[0043] 도 7은 다층체의 일 실시예를 전기 도체 트랙을 갖는 필름 엘리먼트의 형태로 도시한 평면도이다.

### 도면

#### 도면1

도면2

도면3

도면4

도면5a

도면5b

도면6

도면7