(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5990574号

(P5990574)

(45) 発行日 平成28年9月14日(2016.9.14)

(24) 登録日 平成28年8月19日(2016.8.19)

(51) Int.Cl.

F 1

H01L 33/38 (2010.01)

H01L 33/32 (2010.01)H01L 33/38

H01L 33/32

請求項の数 15 (全 10 頁)

(21) 出願番号 特願2014-511976 (P2014-511976)

(86) (22) 出願日 平成24年4月25日 (2012.4.25)

(65) 公表番号 特表2014-515557 (P2014-515557A)

(43) 公表日 平成26年6月30日 (2014.6.30)

(86) 國際出願番号 PCT/IB2012/052062

(87) 國際公開番号 WO2012/160455

(87) 國際公開日 平成24年11月29日 (2012.11.29)

審査請求日 平成27年4月21日 (2015.4.21)

(31) 優先権主張番号 61/489,280

(32) 優先日 平成23年5月24日 (2011.5.24)

(33) 優先権主張国 米国(US)

(73) 特許権者 590000248

コーニンクレッカ フィリップス エヌ

ヴェ

KONINKLIJKE PHILIPS

N. V.

オランダ国 5656 アーネー アイン

ドーフェン ハイテック キャンパス 5

High Tech Campus 5,

NL-5656 AE Eindhoven

(74) 代理人 100107766

弁理士 伊東 忠重

(74) 代理人 100070150

弁理士 伊東 忠彦

最終頁に続く

(54) 【発明の名称】 フリップチップLEDのためのP-N分離メタルフィル

## (57) 【特許請求の範囲】

## 【請求項1】

第1の導電層、活性層、及び、第2の導電層を含み、サブマウントに対向する底面、及び、光が発せられる上面を持つ、半導体層と、

前記底面に対向し、前記第1の導電層に電気的に接続される第1の電極と、

前記底面に対向し、前記第2の導電層に電気的に接続される第2の電極であって、前記第1の電極と前記第2の電極との間に少なくとも1つのギャップがある、前記第2の電極と、

前記少なくとも1つのギャップの側壁を絶縁する第1の誘電体層と、

前記第1の電極及び前記第2の電極とは別個に形成された第1の金属層であって、前記第1の金属層の第1の部分は、前記少なくとも1つのギャップを少なくとも部分的に満たしており、前記第1の電極に電気的に接続され、且つ前記第2の電極から電気的に絶縁されている、前記第1の金属層と、

を有する、発光ダイオード(LED)フリップチップ構造体。

## 【請求項2】

前記第1の誘電体層の第1の部分が、前記第2の電極の一部を覆っており、前記第1の金属層の第2の部分が、前記第1の誘電体層の前記第1の部分の上に位置するように形成されている、請求項1記載の構造体。

## 【請求項3】

前記第1の金属層の前記第2の部分が、前記サブマウント上のパッドに接触するスタッ

10

20

ドバンプの第1のグループを形成している、請求項2記載の構造体。

【請求項4】

前記スタッドバンプの第1のグループが、前記第1の電極、前記第2の電極、及び、前記第1の金属層の前記第1の部分から電気的に絶縁されている、請求項3記載の構造体。

【請求項5】

前記第1の導電層がp型導電層を有し、前記第2の導電層がn型導電層を有し、前記p型導電層の一部と前記活性層の一部とが、前記第2の電極に対する電気的コンタクトを作る前記n型導電層の一部を露出するために、除去されている、請求項1記載の構造体。

【請求項6】

前記第1の金属層が、メッキ金属である、請求項1記載の構造体。

10

【請求項7】

前記第1の金属層が、前記第1の電極及び前記第2の電極の上に位置するスタッドバンプを有する、請求項1記載の構造体。

【請求項8】

前記構造体が、パッドを持つサブマウントを更に有し、前記第1の電極、前記第2の電極、及び、前記第1の金属層の一部が前記パッドに接合される、請求項1記載の構造体。

【請求項9】

前記少なくとも1つのギャップを少なくとも部分的に満たしている前記第1の金属層の前記第1の部分が、前記第1の誘電体層の端部に亘って延在している前記第1の金属層の第2の部分により、前記第1の電極に電気的に接続される、請求項1記載の構造体。

20

【請求項10】

前記構造体が、パッドを持つサブマウントを更に有し、前記第1の電極、前記第2の電極、及び、前記第1の金属層の一部が前記パッドに接合され、

前記第1の金属層の一部が、前記第1の電極及び前記第2の電極の上に位置するスタッドバンプを形成し、

前記第2の電極の上の前記スタッドバンプが、前記少なくとも1つのギャップを少なくとも部分的に満たしている前記第1の金属層の前記第1の部分から電気的に絶縁される、請求項1記載の構造体。

【請求項11】

前記第1の電極の上の前記スタッドバンプが、前記第1の電極に電気的に接続されるとともに、前記第1の金属層の前記第1の部分に電気的に接続される、請求項10記載の構造体。

30

【請求項12】

前記第1の金属層が、前記半導体層を少なくとも部分的に機械的に支持する、請求項1記載の構造体。

【請求項13】

前記サブマウントが、複数のLEDフリップチップがマウントされているサブマウントウェハであり、前記第1の電極、前記第2の電極、及び、前記第1の金属層が、前記複数のLEDのウェハレベルプロセッシングの間に、前記サブマウントウェハのパッドに接合されるときに、前記第1の金属層が、前記半導体層を少なくとも部分的に機械的に支持する、請求項1記載の構造体。

40

【請求項14】

第1の導電層、活性層、及び、第2の導電層を含み、サブマウントに対向する底面、及び、光が発せられる上面を持つ、半導体層を形成するステップと、

前記第2の導電層の一部を露出するために、前記第1の導電層の一部と前記活性層の一部とをエッチングするステップと、

前記底面に対向し、前記第1の導電層に電気的に接続される第1の電極を形成するステップと、

前記底面に対向し、前記第2の導電層に電気的に接続される第2の電極であって、前記第1の電極と前記第2の電極との間に少なくとも1つのギャップがある、前記第2の電極

50

を形成するステップと、

前記少なくとも1つのギャップの側壁を絶縁する第1の誘電体層を形成するステップと、

前記第1の電極及び前記第2の電極とは別個に形成された第1の金属層であって、前記第1の金属層の第1の部分は、前記少なくとも1つのギャップを少なくとも部分的に満たしており、前記第1の電極に電気的に接続され、且つ前記第2の電極から電気的に絶縁されている、前記第1の金属層を形成するステップと、

を有する、発光ダイオード(LE D)フリップチップ構造体を形成するための方法。

#### 【請求項15】

前記第1の誘電体層の第1の部分が、前記第2の電極の一部を覆い、前記第1の金属層の第2の部分が、前記第1の誘電体層の前記第1の部分の上に位置するように形成される、請求項14記載の方法。 10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、発光ダイオード(LE D)に関し、特に、ロバスト機械的支持構造及び改善された熱耐性を持つフリップチップLE Dに関する。 20

##### 【背景技術】

##### 【0002】

フリップチップLE Dは、ワイヤボンディングを用いないため、多くのアプリケーションにおいて望ましい。両電極は、サブマウント上の金属パッドへの直接接合(ダイレクトボンディング)のために、LE Dの底面に配置される。当該接合は、超音波接合、はんだ付け、導電性接着剤、又は、他の手段によって達成され得る。光は、電極に対向するLE Dの表面から出て行く。 20

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0003】

典型的なLE Dフリップチップでは、エピタキシャルp型層が、底面層であり、底面アノード電極によって接触されている。p型層の一部と活性層の一部とが、エピタキシャルn型層の下側を露出するために、エッティングにより取り除かれなければならず、このことは、底面カソード電極への接続を可能とする。このエッティングは、n型層の底面を露出させるp型層を通じた分散されたビアを作る。当該ビア開口は、絶縁され、n型層との接触のための開口に金属が堆積される。 30

##### 【0004】

かかるトポグラフィーは、一般的に、プラズマ環境下での半導体材料(例えば、GaN)のドライエッティングによって達成される。

##### 【0005】

n型層に接触している金属とp型層に接触している金属とは、ギャップによって分離される。従って、金属電極間の脆い半導体層に対する機械的支持が存在しない。

##### 【0006】

ウェハレベルプロセッシングの終わりで、LE Dウェハの成長基板は、薄くされて、個別のダイが、個片化によって形成される。次いで、LE D電極が、サブマウントタイル上の金属パッドに接合され、多くの他のLE Dが装着される。半導体層の破損を回避するために、半導体層とサブマウントとの間に誘電体、有機物ベースのアンダーフィル材料を注入することが知られている。当該注入プロセスは、サブマウントタイルが数百ものLE Dを支持し得るため、時間がかかる。 40

##### 【0007】

光抽出を増やすため、LE D電極がサブマウントタイルに接合され、アンダーフィルが注入された後、成長基板が、除去され、一般的には、約5ミクロンの厚みを有する薄い半導体層が露出される。かかるLE D構造は、薄膜フリップチップ(TFFC:Thin Film

Flip Chip) LEDと称される。半導体層は、極めて繊細であり、破損しやすく、薄膜化及び基板除去プロセスは、半導体層に応力を与える。従って、アンダーフィルが要求される。次いで、サブマウントが個片化され、マウントされたデバイスが次のレベルのパッケージングに準備される。

#### 【0008】

シリコーン又はエポキシベースの複合材料(例えば、成形材料)などのアンダーフィル材料は、先天的に、熱膨張係数(CTE: Coefficient of Thermal Expansion)不整合及びヤング係数不整合などの、半導体層に対する幾らかの材料不整合を有する。このことは、温度サイクル又は他の応力状態において、層間剥離、又は、他の信頼性についての問題につながる。

10

#### 【0009】

必要なのは、機械的支持のためのアンダーフィルを要することなく、ロバストなTFFCを形成するための技術である。

#### 【課題を解決するための手段】

#### 【0010】

本発明の一実施形態では、成長基板の上に、n型層、活性層、及び、p型層を成長させることによって、フリップチップLEDが形成される。次いで、p型層の一部と活性層の一部とが、電気的コンタクトのためにn型層を露出させるべく、エッチングにより取り除かれる。その後、n型層及びp型層のための金属電極が形成され、ここで、n電極とp電極とは、短絡を避けるためのギャップによって分離されている。

20

#### 【0011】

電極間のLEDの底面の機械的支持を供給するために、ギャップの側壁及び底面が誘電体層で絶縁され、ギャップが、電気メッキにより金属で満たされる。ギャップを満たしている金属は、短絡を避けるために、電極のうちの少なくとも一方から電気的に絶縁されている。LED電極がサブマウントのパッドに接合されている場合、ギャップを満たしている金属は、パッドのうちの一方の隣にある。従って、サブマウントタイル上にLEDがマウントされた後、LEDの底面全体は、電極とギャップを満たしている金属との組み合わせによって実質的に支持され、アンダーフィルを必要としない。従って、アンダーフィルの欠点が回避される。金属のCTE及びヤング係数は、有機物ベースのアンダーフィル材料のCTE及びヤング係数よりも、半導体層のCTE及びヤング係数により近いので、動作中に生じる熱応力におけるLEDの信頼性が大幅に増加する。

30

#### 【0012】

タイルレベルのアンダーフィルプロセスを必要としないことで、より多くのLEDパッケージングステップがウェハレベルで処理されるので、よりよい生産スケーラビリティ及び製造コストの低減につながる。例としては、LEDウェハが、対応し合う電極パッドを適切にアライメントしてキャリアウェハに接合され、又は、メッキされた構造体が、ウェハ担体を形成するのに、十分に厚く、且つ、機械的に硬いことである。次いで、キャリアウェハ上のLEDが、成長基板の除去、光抽出向上のための半導体層の上部の粗面化、LEDのカプセル化、次のレベルのパッケージングのための個片化などによって、ウェハレベルで同時に処理される。半導体層の底面を実際に覆っている金属は、ウェハレベルプロセッシングにおいて、半導体層のための良好な機械的支持を供給する。

40

#### 【0013】

また、上記方法及び構造体の他の実施形態についても説明される。

#### 【図面の簡単な説明】

#### 【0014】

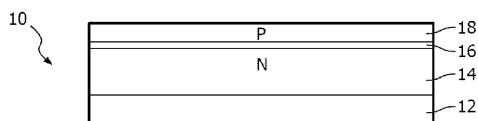

【図1】図1は、成長基板上に成長したLED半導体層の単純化された断面図である。p型層、活性層、n型層が、多層をそれぞれ有していてもよい。

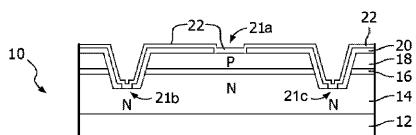

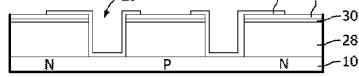

【図2】図2は、フリップチップを形成するためのn型層へのオーミックコンタクトを可能とするようにエッチングにより除去されたp型層及び活性層の部分と、構造体の上に形成された誘電体層及び銅シード層とを示している。

50

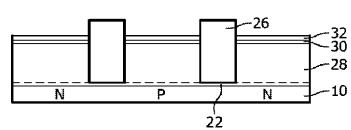

【図3】図3は、表面上にフォトレジスト部分が形成され、次いで、n型層及びp型層に電気的に接觸する少なくとも一層の銅を形成するためのメッキステップが行なわれた、LED半導体層の単純化された（p型層及び活性層の厚みが、単純化のために無視されている）図を示している。

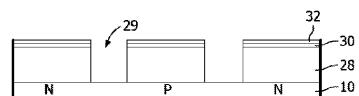

【図4】図4は、フォトレジスト部分が剥離され、露出されたシード層がエッチングにより除去された後の図3の構造体を示している。

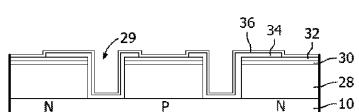

【図5】図5は、金属電極間のギャップの側壁及び底面を絶縁している誘電体層を示している。

【図6】図6は、誘電体層の表面上にスパッタリングされた金のシード層を示している。次いで、フォトレジスト部分（図示省略）が、金がメッキされる金のシード層の領域を露出させるように形成される。

10

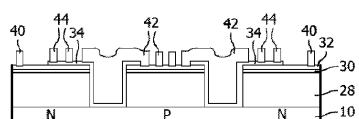

【図7】図7は、露出されたシード層が金でメッキされ、シード層がエッチングされた後の構造体を示している。金は、銅電極間のギャップを満たし、n電極及びp電極の一部を覆う。

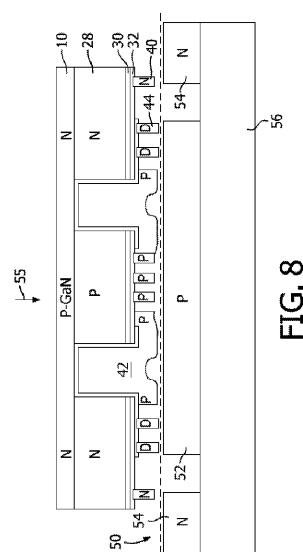

【図8】図8は、更なるプロセッシングのためにサブマウントウェハにマウントされたLEDチップを示している。

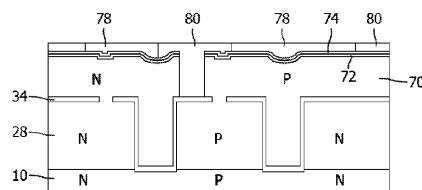

【図9】図9は、ギャップを満たしている金属によって、電気的接点がn型層とp型層との両方に作られた、他の電極構成を持つLEDダイの一剖面図を示している。各図面において、同一の符号が付された要素は、同一又は同様のものであってもよい。

#### 【発明を実施するための形態】

##### 【0015】

図1乃至図7は、単一のLEDのみを示しているLEDウェハのごく一部の断面図を示しており、ここで、単一のLEDの中央部分は、側端の詳細を示すように、横方向に大きく短縮されている。説明を簡略化するために、各LEDにおいて、n型層の周辺のみが電極によって接觸されている。実際のデバイスでは、n型層は、改善された電流拡散のために分散された電極によって接觸され得る。

##### 【0016】

図1は、サファイア基板12の上にエピタキシャル成長した従来のLED半導体GaN層10を示しており、成長した層の順に、核形成層、応力緩和層、n層14、（光を発する）活性層16、p層18、及び、LEDを形成するために用いられる任意の他の半導体層を示している。ウェハ上に形成されたLEDは、所望のピーク波長に依存して、AlInGaN LEDであってもよい。あるいは、LEDは、GaNベースのものである必要はなく、任意のタイプの成長基板を用いる任意の他のタイプのLEDであってもよい。本発明は、フリップチップとして任意のLEDを形成することに適用可能である。

30

##### 【0017】

図2は、LEDの端部周辺のn層14の表面を露出させるために、ウェハが、マスクされ、p層18及び活性層16をLEDの端部から除去するためにドライエッチングされることを示している。これは、ウェハ上の全てのLEDのために実行される。かかるプロセスは、フリップチップを形成するための従来のものである。

##### 【0018】

また、図2は、ウェハの表面の上に堆積され、従来の技術を用いて、p層18の表面の一部を露出するために領域21aがエッチングされ、n層14の表面の一部を露出するために領域21b, 21cがエッチングされたSiNxなどの誘電体層20を示している。上記堆積は、スプレー被覆によるものであってもよい。任意の適切な誘電体材料が用いられてもよい。誘電体層20は、p層18及び活性層16の中の開口の側壁を覆うとともに、p層18の表面の一部を覆う。

40

##### 【0019】

銅のシード層22が、ウェハの表面の上に形成され、これは、領域21a乃至21cにおいて、誘電体層20内の開口を通じて、n層及びp層へのオームックコンタクトを作る。ニッケル、タンクステン、クロム、バナジウム、及び/又は、チタンなどのバリア層が

50

、Cu原子の移動を防ぐために、銅のシード層22と半導体層との間に形成されてもよい。銅のシード層22及びバリア層は、CVD、スパッタリングなどの任意の多くの既知の技術を用いてウェハ全体の上に堆積されてもよい。

#### 【0020】

図3乃至図8では、GaN層10が、単一の半導体GaN層10として称され、単純化のために、成長基板が省略されている。p層18及び活性層16の厚みは、5ミクロンのオーダなど、数ミクロンしかなく、より厚みのある後述のメッキされた電極（例えば、50乃至100ミクロンのオーダ）と比較して、実質的に平らである。従って、図2に示される半導体メサ（層16, 18）の高さは、単純化のために、省略されている。図面における様々な層の厚みは、縮尺通りではない。

10

#### 【0021】

図3では、銅でメッキされるシード層22の該当部分のみを露出させるために、フォトレジスト部分26が、従来のリソグラフィ技術により堆積及びパターン化されている。これらの露出された領域は、銅のシード層22が図2の領域21a乃至21cにおいて半導体層に電気的に接触している領域を含む。酸化物又は窒化物などの他の誘電体材料が、フォトレジストの代わりにマスクとして用いられてもよい。

#### 【0022】

シード層22の露出された部分は、次いで、銅28で、所望の厚さまでメッキされる。シード層22が、電位に結合され、ウェハが、電極から銅原子を移送するための電解液に浸される、様々な既知の電気メッキ技術が用いられ得る。また、化学メッキが用いられてもよい。銅28が、LED表面の上の熱拡散及び電流拡散のために好適である。他の金属及び堆積技術が用いられてもよい。

20

#### 【0023】

次いで、サブマウントパッドに対する良好な接合インターフェースを供給するために、薄いニッケルの層30及び金の層32が、銅28の上にメッキされる。

#### 【0024】

図4では、フォトレジスト部分26が溶液中で除去され、ギャップ29が残り、次いで、露出されたシード層22が従来技術を用いてエッチングにより除去される。銅28の下のシード層は、もはや別個に識別しないこととする。

30

#### 【0025】

p層に電気的に接触している銅28の電極は、ギャップ29によって、n層に電気的に接触している銅28の電極から隔離されている。

#### 【0026】

図5では、例えば、SiN<sub>x</sub>の誘電体層34が、従来技術を用いて、ウェハの上に堆積され、パターン化されている。当該堆積は、スプレー被覆によるものであってもよいし、又は、他の適切な方法によるものであってもよい。任意の適切なlow-K（低誘電率）材料が用いられてもよい。誘電体層34は、銅28がメッキされた隣接する電極間のギャップ29における側壁及び底面を覆うように、パターン化されている。また、パターン化された誘電体層34は、後述のように、メッキされた電極の側面が露出されないことを確実にするために、且つ、金属層を支持するための誘電体表面を供給するために、金の層32の上面の上のごく一部を覆う。

40

#### 【0027】

図6では、薄い金のシード層36が、ウェハ表面の上でスパッタリングされている。

#### 【0028】

次いで、フォトレジスト（図示省略）が、金でメッキされる領域のみを露出するようにシード層36の上にパターン化される。

#### 【0029】

図7に示されるように、露出されたシード層36は、コンフォーマル成長でギャップ29（図6）を満たすために、及び、後続のダイ取り付けアプリケーションのために同時にスタッドバンプを形成するために、単一の金属メッキステップにおいて、金で電気メッキ

50

される。フォトレジスト除去後、露出されたシード層36がエッチングバックされて、(1)金の層32を介してn型層に電気的に接触している金のスタッドバンプ40、(2)金の層32を介してp型層に電気的に接触している金のスタッドバンプ42、及び、(3)n型層とp型層との両方から電気的に隔離された、誘電体層34の上の金のスタッドバンプ44からなる、金のスタッドバンプのグループが形成される。金のスタッドバンプ44は、n型層のための銅28の電極上の誘電体層34の上に位置するように形成されることに留意すべきである。金のスタッドバンプ44は、近接して離されているn電極とp電極との間の隔離バッファとして作用し、ギャップの隣の表面のための機械的支持を供給する。

## 【0030】

10

金のスタッドバンプを供給することによって、LED電極をサブマウントパッドに超音波接合する際、金のより大きな層よりもむしろ、金は、サブマウントの金パッドにおいてより容易に溶解する。

## 【0031】

次いで、結果として得られたLEDウェハは、ダイ取り付けのために個片化されることができ、又は、ウェハレベルでの更なるプロセッシングのためにキャリアウェハに接合することができる。あるいは、銅28の層の構造体は、後続のウェハレベルのパッケージングプロセスのためのキャリアウェハとして作用するように、十分に厚く、且つ、機械的に硬くてよい。

## 【0032】

20

一実施形態において、図8に示されるように、個別のLEDダイ各自が、各LEDダイのために、pコンタクトのための中央の金パッド52と、nコンタクトのための周辺の金パッド54とを持つサブマウントウェハ50上にマウントされる。コンタクトパッド及び電極構成は、図8に示されるものよりも更に複雑であってもよい。例えば、LEDダイのためのn電極が、p層及び活性層を通じたビアによって、LEDダイの表面の上に分散されてもよく、サブマウントウェハ上のパッドが、LEDダイ上の電極の配置に対応してもよい。サブマウントウェハ50のボディ56は、セラミックであってもよいし、又は、他の適切な熱伝導性材料であってもよい。

## 【0033】

LEDダイ上の金のスタッドバンプの極性は、p、n、及び、d(極性無し)として示されている。金のスタッドバンプ40, 42, 44間の空間は、極めて正確に作れることのできる、メッキのためのマスキングによって決定されるため、極めて小さくてもよい。少なくとも部分的にギャップを満たしている金のスタッドバンプ42は、他の金のスタッドバンプ40, 44に対して平らではないが、金のスタッドバンプ42は、ギャップ領域の機械的支持を供給する。また、金の属性に比較的富む性質のために、サブマウントパッドに対するLED電極の超音波接合は、任意の高い位置を幾らか平らにし、このことは、LEDダイの底面全体の上に略均一なコンタクトを供給する。従って、LEDダイの底面の略全体が、略均一に、金のスタッドバンプによって支持され、後続のプロセッシングにおいて、半導体層のための良好な機械的支持を供給する。

## 【0034】

30

金のスタッドバンプ44は、電気的に隔離され、ずれにより、バンプ44の幾つかがp金属パッド52に接触し、バンプ44の幾つかが隣接するn金属パッド54に接触する場合であっても短絡しないため、サブマウントウェハ50上のパッド52, 54は、LEDダイの配置のための過度の公差要求なしで、互いに近接して形成されてもよい。

## 【0035】

金のスタッドバンプ42が、銅28の間のギャップを満たすことによって機械的支持を提供することに加えて、それらは、追加された電極領域のために、p型層へのサブマウントパッド52の導電性を増加させる。

## 【0036】

一実施形態では、サブマウントウェハ50上のLEDダイは、LEDダイがレーザバル

40

スに晒された後でサファイア成長基板がリフトオフされる、基板レーザリフトオフプロセスの対象となる。これは、半導体層上に下向きの高い圧力 5 5 を作る。半導体層は、LED ダイの背面全体に実際に亘る金のスタッドバンプの金属支持のために、破壊から防がれる。

#### 【 0 0 3 7 】

次いで、LED ダイは、化学機械的研磨 ( C M P : Chemical-Mechanical Polishing ) 又は他の技術を用い得る薄層化プロセスの対象となり、半導体層は、たった数ミクロンまで薄くされる。露出された上面は、次いで、光抽出を増加させるため、エッティングプロセスにより粗面化される。

#### 【 0 0 3 8 】

LED ダイは、次いで、ダイ全体に亘ってレンズをモールドすることによって、カプセル化されてもよい。

#### 【 0 0 3 9 】

サブマウントウェハ 5 0 は、個別の LED を形成するために、次いで、個片化される ( 例えば、切られる ) 。

#### 【 0 0 4 0 】

図 9 は、LED ダイ上の電極構成の他の実施形態を示している。スタッドバンプが形成されていない。銅 2 8 が、n 層及び p 層に電気的に接触するように半導体層の上にメッキされた後、誘電体層 3 4 が、n 及び p の銅 2 8 の電極の一部を露出させるように堆積及びパターン化される。銅のシード層 ( 図示省略 ) が、次いで、表面の上に堆積され、メッキされる部分だけ露出させるようにフォトレジストでマスクされる。銅 7 0 の層が、次いで、銅 2 8 の電極間のギャップを満たすために、露出されたシード層の上に電気メッキされる。銅 7 0 は、次いで、ニッケルの層 7 2 と金の層 7 4 とでメッキされる。従来のはんだマスク材料 8 0 が、次いで、表面の上でパターン化され、はんだペースト 7 8 が、サブマウントのパッドへのダイ取り付けのために、露出された金の層 7 4 に付与される。加熱の際、はんだペースト 7 8 が、サブマウントパッドに接合する。

#### 【 0 0 4 1 】

また、他の電極構成が、想定される。

#### 【 0 0 4 2 】

LED が活性化された場合、光が、p 型層及び活性層を覆っている n 型層を通じて発せられる。電極金属 ( 例えば、金又はニッケルのバリア層 ) は、光を反射して、LED を通じて戻す。

#### 【 0 0 4 3 】

本発明を詳細に説明してきたが、当該技術分野における当業者は、所与の上記開示から、ここで説明された本発明の概念の範囲から逸脱しない範囲で本発明が修正され得ることを理解するであろう。従って、本発明の範囲を、図示及び説明された特定の実施形態に限定する意図はない。

【図1】

(従来技術)

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

---

フロントページの続き

(74)代理人 100091214

弁理士 大貴 進介

(74)代理人 100087789

弁理士 津軽 進

(74)代理人 100122769

弁理士 笹田 秀仙

(74)代理人 100171701

弁理士 浅村 敬一

(72)発明者 レイ ジブ

オランダ国 5656 アーエー アンドーフェン ハイ テック キャンパス 44 フィリ

ップス アイピーアンドエス - エヌエル

(72)発明者 ウェイ ヤジュン

オランダ国 5656 アーエー アンドーフェン ハイ テック キャンパス 44 フィリ

ップス アイピーアンドエス - エヌエル

(72)発明者 ニッケル アレクサンダー エイチ

オランダ国 5656 アーエー アンドーフェン ハイ テック キャンパス 44 フィリ

ップス アイピーアンドエス - エヌエル

(72)発明者 シアフィーノ ステファノ

オランダ国 5656 アーエー アンドーフェン ハイ テック キャンパス 44 フィリ

ップス アイピーアンドエス - エヌエル

(72)発明者 スタイガーワールド ダニエル アレクサンダー

オランダ国 5656 アーエー アンドーフェン ハイ テック キャンパス 44 フィリ

ップス アイピーアンドエス - エヌエル

審査官 金高 敏康

(56)参考文献 特開2007-300063(JP,A)

特開平05-007019(JP,A)

特表2010-508669(JP,A)

特開2011-071339(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64