**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>5</sup>

G11B 20/10

(45) 공고일자 1991년08월21일

(11) 공고번호 91-006360

---

|           |               |           |               |

|-----------|---------------|-----------|---------------|

| (21) 출원번호 | 특1988-0010699 | (65) 공개번호 | 특1990-0003863 |

| (22) 출원일자 | 1988년08월23일   | (43) 공개일자 | 1990년03월27일   |

---

(71) 출원인 삼성전자 주식회사 안시환

경기도 수원시 매단동 416번지

(72) 발명자 서정훈

서울특별시 구로구 고척동 318-3

서성모

경기도 수원시 인계동 562-2

(74) 대리인 이건주

**심사관 : 박용렬 (책자공보 제2432호)**

---

**(54) 디지털 오디오기기의 뮤트회로**

---

**요약**

내용 없음.

**대표도**

**도1**

**영세서**

[발명의 명칭]

디지털 오디오기기의 뮤트회로

[도면의 간단한 설명]

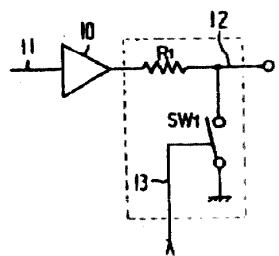

제1도는 종래의 회로도.

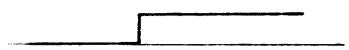

제2도는 제1도에 대한 각부분의 파형도.

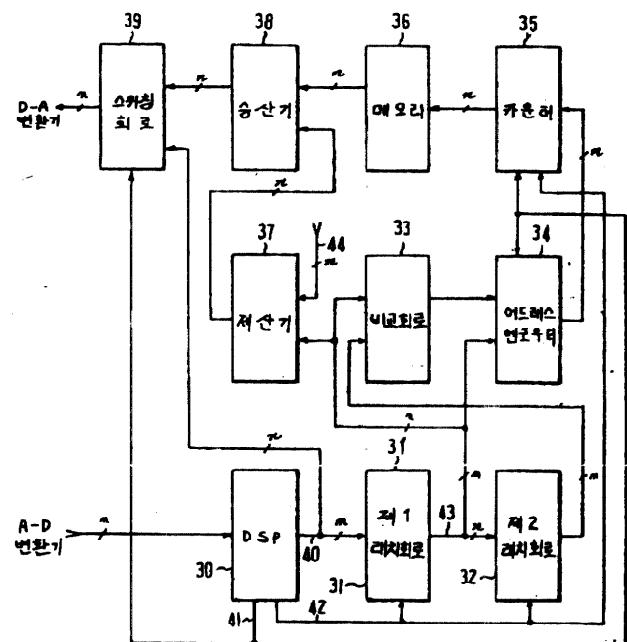

제3도는 본 발명의 일실시예의 회로도.

제4도는 본 발명의 또 다른 실시예의 회로도.

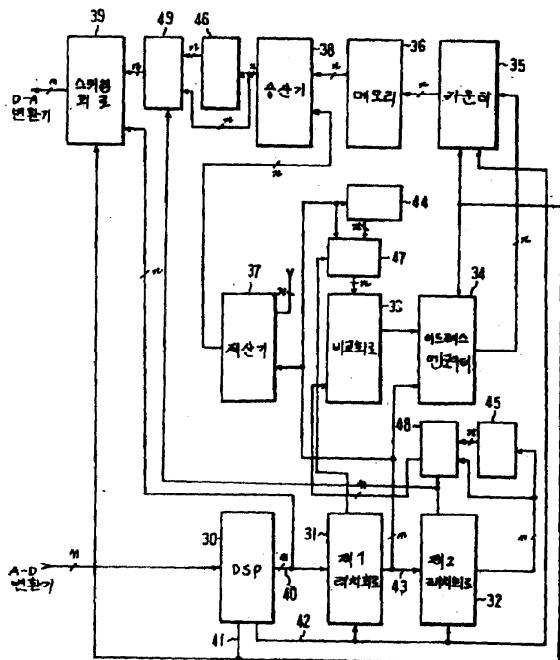

\* 도면의 주요부분에 대한 부호의 설명

|            |                   |

|------------|-------------------|

| 30 : DSP   | 31, 32 : 제1,2래치회로 |

| 33 : 비교회로  | 34 : 어드레스 엔코더     |

| 35 : 카운터   | 36 : 메모리          |

| 37 : 제산기   | 38 : 승산기          |

| 39 : 스위칭회로 |                   |

[발명의 상세한 설명]

본 발명은 음성신호를 디지털 데이터로 변환하여 처리하는 디지털 오디오(Digital Audio) 기기에 관한 것으로, 특히 전원오프(Power Off)시의 순간적인 잡음이나 시스템의 회로적인 영향 또는 외부영향에 의해 데이터가 손상될시 발생되는 무데이터 상태로 잡음을 뮤트하는 회로에 관한 것이다.

통상적으로 디지털 오디오기기는 기록매체나 방송되는 RF 신호를 입력하여 디지털 데이터 형태로 변환한 다음 디지털 데이터를 처리한 다음 아날로그신호 형태 변환하여 가청할수 있는 음성을 출력한다.

상기 디지털 오디오기기에는 디지털 테이프 레코오더(Digital Tape Recorder) 및 콤팩트디스크 플레이어(Compact Disc Player), 펄스코드 모듈레이션 프로세서(Pulse Code Modulation Processor), 디

지탈 튜너(Digital Tuner), 디지탈 증폭기(Digital Amplifier)등 많은 종류가 있다.

상기와 같은 디지탈 오디오기기에 있어서 종래의 뮤트회로는 제1도와 같이 처리되어 변화되어진 아날로그 음성신호를 증폭 출력하는 저주파증폭기(10)의 출력단과 접지사이에 전자스위치(SW1)를 접속하여 시스템 콘트롤러로 부터 라인(13)을 통해 인가되는 뮤트요구 신호에 의해 전자스위치(SW1)를 작동시킴으로 상기 저주파증폭기(10)의 출력을 접지로 통과시킴으로 발생되는 잡음을 뮤트하였다. 그러나 제2도와 (가)와 같은 저주파증폭기(10)의 음성신호는 제2도(나)와 같은 뮤트요구 신호가 하이노리 상태로 변화하는 순간 턴온되는 전자스위치(SW1)의 순간적인 팝노이즈(POP Noise)에 의해 제2도(다)와 같은 음성신호가 출력되므로서 뮤트되는 순간 팝노이즈 즉 과도현상에 의해 비트음과 같이 듣기 거북한 날카로운 비트음이 발생되는 문제점이 있었다.

따라서 본 발명은 전원오프시 팝노이즈나 시스템 자체 및 외부의 영향으로 데이터 손상되어 뮤트하고자 할때 생성되는 팝노이즈에 의한 듣기 거북한 비트음 발생을 방지할수 있는 디지탈 오디오기기의 뮤트회로를 제공함에 있다.

이하 본 발명을 첨부한 도면을 참조하여 상세히 설명한다.

제3도는 본 발명의 회로도로서, 아날로그-디지탈(Aalog-Digital : 이하 A-D라 함) 변환기로 부호 소정 비트의 디지탈 음성신호를 입력하여 제어처리하여 처리한 소정비트의 디지탈 데이터와 워드클럭(Word Clock)열 및 뮤트 제어신호를 출력하는 디지탈 시그널 프로세서(Digital Signal Processor : 이하 DSP라 함) (30)와, 상기 DSP(30)로부터 디지탈 데이터와 워드클럭을 입력하여 상기 워드클럭에 의해 상기 디지탈 데이터를 래치하는 제1래치회로(31)와, 상기 제1래치회로(31)로부터 입력되는 디지탈 데이터를 상기 DSP(30)로부터 인가되는 워드클럭에 의해 래치하여 지연시키는 제2래치회로(32)와, 상기 제1래치회로(31) 및 제2래치회로(32)의 디지탈 데이터를 비교하여 음성신호의 파형 증가 또는 감소변화를 검출한 비교신호를 발생하는 비교회로(33)와, 상기 DSP(30)로부터 인가되는 뮤트제어신호에 의해 상기 비교회로(33)의 비교신호와 상기 제1래치회로(31)로부터 최상위 비트데이터 즉 부호데이터를 입력하여 상기 두입력신호의 논리값에 따라 미리 세팅된 다른 어드레스를 발생하는 어드레스 엔코더(34)와, 상기 어드레스 엔코더(Address Encoder) (34)로부터 출력되는 어드레스를 상기 DSP(30)로부터 인가되는 뮤트제어신호에 의해 입력한 다음 상기 DSP(30)로부터 인가되는 워드클럭열에 의해 상기 입력한 어드레스 부터 일정수번 1씩 증가하는 순차어드레스를 발생하는 카운터(35)와, 상기 카운터(35)의 일정수번 1씩 증가하는 순차어드레스에 해당하는 번지에 미리 저장되어진 제2디지탈 데이터를 독출하는 메모리(36)와, 상기 제1래치회로(31)로부터 제1입력포트로 입력되는 제1디지탈 데이터를 제2 입력포트로 항상 인가되고 있는 고정데이터와 제산하여 제산한 제3디지탈 데이터를 발생하는 제산기(37)와, 상기 메모리(36)로부터 독출되는 제2디지탈 데이터와 상기 제산기(37)에서 발생된 제3디지탈 데이터와 승산하여 승산한 제4디지탈 데이터를 발생하는 승산기(38)와, 상기 DSP(30)로부터 뮤트제어신호 및 제1디지탈 데이터를 그리고 상기 승산기(38)로부터 제4디지탈 데이터를 입력하여 상기 뮤트제어신호의 논리상태에 의해 상기 제1 또는 제4 디지탈 데이터를 디지탈-아날로그(Digital-Analog : 이하 D-A이라함) 변환기로 선택 출력하는 스위치회로(39)로 구성한다.

상술한 제3도를 참조하여 본 발명을 상세히 설명한다. 전원 온된 상태에서 DSP(30)는 항상 워드클럭 열을 발생하여 라인(42)로 출력한다. 그리고 DSP(30)는 정상적인 동작시 즉 A-D 변환기로 부터 입력되는 음성디지탈 신호를 제어처리한 제1디지탈 데이터를 버스라인(40) 및 스위칭회로(39)를 통해 A-D 변환기로 출력하고자 할시는 저저논리상태의 뮤트제어신호를 라인(41)로 출력하고 뮤트작동시에는 일정 논리상태의 뮤트제어신호를 라인(41)로 출력한다. 그러면 스위칭회로(39)는 기전논리상태의 뮤트제어신호에 의해 상기 버스라인(40)상의 제1디지탈 데이터를 입력하여 D-A 변환기로 출력한다. 한편 이때 제1래치회로(31)는 상기 DSP(30)로부터 라인(42)을 통해 인가되는 워드클럭열에 의해 상기 DSP(30)로부터 버스라인(40)을 통해 입력되는 제1디지탈 데이터를 래치하여 버스라인(43)으로 출력한다. 그리고 제2래치회로(32)는 상기 라인(42)을 통해 인가되는 워드클럭에 의해 상기 버스라인(43)상의 제1디지탈 데이터를 래치함으로서 워드클럭 주기만큼 지연시켜 비교회로(33)로 인가하고 출력한다.

이상태에서 DSP(30)는 자체시스템에 의해 손상된 음성디지탈 데이터가 A-D 변환기로 부터 입력되거나 청취자에 의해 뮤트요구가 있을시 라인(41)상에 출력하고 있는 기저논리상태의 뮤트제어신호를 일정논리상태의 뮤트제어신호로 논리상태를 반전시켜 출력한다. 이때 비교회로(33)는 상기 버스라인(43)상에 출력된 제1래치회로(31)의 출력인 뮤트상태가 되기전의 제1디지탈 데이터와 상기 제2래치회로(32)로부터 상기 제1래치회로(31)의 출력의 바로 앞서 출력된 제1디지탈 데이터를 입력하여 상기 두입력 데이터를 비교함으로서 음성정보의 파형이 증가상태였는가 또는 감소상태였는가를 논리상태로 알수 있는 비교신호를 어드레스 엔코더(34)로 출력한다. 그러면 어드레스 엔코더(34)는 상기 DSP(30)로부터 라인(41)을 통해 인가되는 뮤트제어신호의 논리상태가 기저논리상태에서 일정논리상태로 변화할때 상기 비교회로(33)의 비교신호 및 상기 제1래치회로(31)의 최상위 비트 즉 부호데이터의 논리상태를 검사하여 상기 입력신호 논리상태로 음성정보의 파형변화 상태를 감지함으로 음성정보의 파형변화에 따라 미리 세팅된 각기 다른 논리값을 갖는 어드레스중 다수의 어드레스중 한 어드레스를 카운터(35)로 선택 출력한다.

이때 카운터(35)도 상기 라인을 통해 인가되는 뮤트제어신호의 논리상태가 기저논리상태에서 일정논리상태로 변화할때 상기 어드레스 엔코더(34)에서 출력되는 어드레스를 로드한 다음 상기 라인(42)를 통해 DSP(30)로부터 인가되는 워드클럭열에 의해 상기 로드된 어드레스의 논리값에서부터 1씩 증가하는 소정수의 순차어드레스를 메모리(36)로 출력한다. 그러면 메모리(36)는 상기 카운터(35)로부터 출력되는 순차 어드레스들이 지정하는 번지에 미리 저장되어진 제2디지탈 데이터를 독출하여 승산기(38)으로 출력한다.

한편 제1래치회로(31)로부터 버스라인(43)을 통해 제1디지탈 데이터를 입력하는 제산기(37)는 버스라인(44)을 통해 항상 인가되고 있는 고정디지탈 데이터로 상기 제1디지탈 데이터를 제산하여 제산

된 제3디지털 데이터를 생성하여 승산기(38)로 출력한다.

이때 상기 메모리(36)로부터 제2디지털 데이터와 상기 제산기(37)로부터 제3디지털 데이터를 입력하는 승산기(38)는 상기 제2디지털 데이터와 제3디지털 데이터를 승산하여 제4디지털 데이터를 스위칭회로(39)로 출력한다. 그러면 스위칭회로(39)는 라인(41)을 통해 인가되는 일정 논리상태의 뮤트제어신호에 의해 상기 승산기(38)의 출력인 제4디지털 데이터를 입력하여 D-A 변환기로 출력한다. 부가적으로 상기 메모리(36)에 저장되어진 제2디지털 데이터는 일정주파수대의 1주기에 대한 파형을 워드클럭 주기로 샘플링한 다음 n비트로 양자화하여 순차적으로 세팅해 둔다. 그리고 상기 승산기(38)에서 출력되는 제4디지털 데이터는 음성정보의 1주기 파형에 있어서  $90^\circ$ 의 위상에  $180^\circ$ 의 위상에 이르는 구간에 대한 것으로 양의 값에서 "0"으로 감소하는 파형형태  $270^\circ$ 의 위상에서  $360^\circ$ 의 위상에 이르는 구간에 대한 것으로 음의 값에서 "0"으로 증가하는 파형이 출력된다.

제4도는 본 발명의 또 다른 실시예의 회로도로서, 제3도의 동일기능과 동일부호를 갖는 DSP(30) 및 제1,2래치회로(31,32), 비교회로(33), 어드레스 엔코오더(34), 카운터(35), 메모리(36), 제산기(37), 승산기(38), 스위칭회로(39)와, 상기 제1래치회로(31)과 비교회로(33) 사이에 설치되어 상기 제1래치회로(31)의 출력을 보수치환하는 제1보수치환회로(44)와, 상기 제1래치회로(31)와 비교회로(33) 사이에 접속되어 상기 제1래치회로(31)의 최상위 비트 즉 부호데이터에 의해 상기 제1보수치환회로(44)의 출력이나 상기 제1래치회로(31)의 출력을 비교회로(33)로 스위칭 출력하는 제2스위칭회로(47)와, 상기 제2래치회로(32)와 비교회로(33) 사이에 설치되어 상기 제2래치회로(32)의 출력을 보수치환하는 제2보수치환회로(45)와, 상기 제2래치회로(32)의 출력중 최상위 비트 즉 부호데이터에 의해 상기 제2보수치환회로(45)의 출력이나 상기 제2래치회로(32)의 출력을 비교회로(33)로 선택적으로 스위칭 출력하는 제3스위칭회로(48)와, 상기 승산기(38)과 스위칭회로(39) 사이에 설치되어 상기 승산기(38)의 출력인 제4디지털 데이터를 보수치환하는 제3보수치환회로(46)와, 상기 승산기(38)와 스위칭회로(39) 사이에 접속되어 상기 제1래치회로(31)로부터 인가되는 제1디지털 데이터의 최상위 비트 즉 부호데이터에 의해 상기 승산기(38)의 출력이나 상기 제3보수치환회로(47)의 출력을 상기 스위칭회로(39)로 선택적으로 출력하는 제4스위칭회로(49)로 구성한다.

상술한 구성에 의해 본 발명의 또 다른 실시예를 설명한다.

제4도의 상세한 작동은 제3도와 동일하게 작동하여 상세한 설명은 약하며, 제1,2래치회로(31,32)와 비교회로(33)간의 데이터 흐름과 승산기(38)와 스위칭회로(39)간의 데이터전송 흐름만을 설명한다. 제1,2래치회로(31,32)가 각각 워드클럭의 1주기와 2주기만큼 지연한 제1디지털 데이터를 출력하는데 이때 상기 제1디지털 데이터가 양수일시 제1디지털 데이터는 하이논리상태의 최상위 비트데이터를 출력하게 되어 제2,3스위칭 회로(47,48)는 각각 제1,2래치회로(31,32)의 출력을 입력하여 비교회로(33)로 출력하고, 제4스위칭회로(49)도 승산기(38)의 제4디지털 데이터를 입력하여 스위칭회로(39)로 출력한다.

상기와는 달리 제1디지털 데이터가 음수일시 제1디지털 데이터는 로우논리상태의 최상위 비트데이터를 출력하게 되어 제2,3스위칭회로(47,48)는 각각 보수치환된 제1,2보수치환회로(44,45)의 출력을 입력하여 비교회로(33)로 출력하고, 제4스위칭회로(49)는 보수치환된 승산기(38)의 출력을 입력하여 스위칭회로(39)로 출력한다.

상기와 같이 제1-3보수치환회로(44-46) 및 제2-4스위칭회로(47-49)를 사용하면 디지털 데이터를 양수 형태를 처리하게 되며 이경우 메모리(36)는 종전의 1주기에 대해 샘플링하고 양자화양의 1/4에 해당하는 데이터량 즉 지역하면 1주기 정현파형중  $90^\circ$ 의 위상에서부터  $180^\circ$ 의 위상에 이르는 구간만을 샘플링한 다음 양자화하여 저장시켜 작동시킬수 있다. 그리고 제3보수치환회로(46)를 설치한 것은  $270^\circ$  위상에서  $360^\circ$ 의 위상에 이르는 구간을 상기  $90^\circ$ 의 위상에서  $180^\circ$ 의 위상에 이르는 구간을 반전시켜 구현하게 한다.

상술한 바와같이 본 발명은 뮤트개시시에 음성정보 파형을 서서히 "0"에 도달하게 함으로서 팝노이즈 발생을 방지하여 듣기 거북한 비트음 발생을 방지할수 있는 이점이 있다.

## (57) 청구의 범위

### 청구항 1

디지털 오디오기기에 있어서, 아날로그-디지털 변환기로부터 소정 비트의 디지털 음성신호를 입력하여 제어처리하여 처리한 소정비트의 디지털 데이터와 워드클럭열 및 뮤트 제어신호를 출력하는 디지털 시그널 프로세서(30)와, 상기 DSP(30)로부터 디지털 데이터와 워드클럭을 입력하여 상기 워드클럭에 의해 상기 디지털 데이터를 래치하는 제1래치회로(31)와, 상기 제1래치회로(31)로부터 입력되는 디지털 데이터를 상기 DSP(31)로부터 인가되는 워드클럭에 의해 래치하여 지연시키는 제2래치회로(32)와, 상기 제1래치회로(31) 및 제2래치회로(32)의 디지털 데이터를 비교하여 음성신호의 파형증가 또는 감소변화를 검출한 비교신호를 발생하는 비교회로(33)와, 상기 DSP(30)로부터 인가되는 뮤트제어신호에 의해 상기 비교회로(33)의 비교신호와 상기 제1래치회로(31)로부터 최상위 비트데이터 즉 부호데이터를 입력하여 상기 두 입력신호의 논리값에 따라 미리 세팅된 다른 어드레스를 발생하는 어드레스 엔코오더(34)와, 상기 어드레스 엔코오더(34)로부터 출력되는 어드레스를 상기 DSP(30)로부터 인가되는 뮤트제어신호에 의해 입력한 다음 상기 DSP(30)로부터 인가되는 워드클럭 열에 의해 상기 입력한 어드레스로부터 일정수번 1씩 증가하는 순차어드레스를 발생하는 카운터(35)와, 상기 카운터(35)의 일정수번 1씩 증가하는 순차어드레스에 해당하는 번지에 미리 저장되어진 제2디지털 데이터를 독출하는 메모리(36)와, 상기 제1래치회로(31)로부터 제1입력포트로 입력되는 제1디지털 데이터를 제2입력포트로 항상 인가되고 있는 고정데이터와 제산하여 제산한 제3디지털 데이터를 발생하는 제산기(37)와, 상기 메모리(36)로부터 독출되는 제2디지털 데이터와 상기 제산기(37)에서 발생된 제3디지털 데이터와 승산하여 승산한 제4디지털 데이터를 발생하는 승산기(38)와, 상기 DSP(30)로부터 뮤트제어신호 및 제1디지털 데이터를 그리고 상기 승산기(38)로부터 제4디지털 데이터를 입력하여 상기 뮤트제어신호의 논리상태에 의해 상기 제1 또는 제4디지털

이터를 디지털-아날로그 변환기로 선택 출력하는 스위치회로(39)로 구성함을 특징으로 하는 뮤타회로.

### 도면

#### 도면1

#### 도면2-가

#### 도면2-나

#### 도면2-다

#### 도면3

도면4