(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4421144号

(P4421144)

(45) 発行日 平成22年2月24日(2010.2.24)

(24) 登録日 平成21年12月11日(2009.12.11)

(51) Int.Cl.

H01L 29/78 (2006.01)

F 1

H01L 29/78 652K

H01L 29/78 652H

H01L 29/78 653A

請求項の数 6 (全 15 頁)

(21) 出願番号 特願2001-198552 (P2001-198552)

(22) 出願日 平成13年6月29日 (2001.6.29)

(65) 公開番号 特開2003-17696 (P2003-17696A)

(43) 公開日 平成15年1月17日 (2003.1.17)

審査請求日 平成16年11月26日 (2004.11.26)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100108062

弁理士 日向寺 雅彦

(72) 発明者 小野 昇太郎

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

審査官 後谷 陽一

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【特許請求の範囲】

## 【請求項 1】

第1導電型のドレイン層と、

前記ドレイン層の上に設けられ前記ドレイン層よりも不純物濃度が低い第1導電型のドリフト層と、

前記ドリフト層の上に設けられた第2導電型のベース層と、

前記ベース層の上に設けられた第1導電型のソース領域と、

前記ベース層と前記ドリフト層を貫通して前記ドレイン層に達するトレンチの内壁面に形成されたゲート絶縁膜及びこれを介して前記トレンチの内部に設けられたゲート電極とを有するトレンチ・ゲートと、

を備え、

前記ドリフト層は、前記ドレイン層の近傍において、前記トレンチの深さ方向に沿って前記ドレイン層に近づくに従って前記第1導電型の不純物濃度が上昇する濃度勾配を有し、

前記ドリフト層は、前記ベース層の近傍において、前記トレンチの深さ方向に沿って前記ベース層に近づくに従って前記第1導電型の不純物濃度が上昇する濃度勾配を有し、

前記ドリフト層は、前記ドレイン層との界面近傍の不純物濃度の遷移する領域を除く部分において、前記トレンチの深さ方向に沿って上部と下部との間に前記第1導電型の不純物濃度が極小となる部分を有することを特徴とする半導体装置。

## 【請求項 2】

10

20

前記ドリフト層の前記不純物濃度は、前記ベース層と隣接した部分において  $1 \times 10^{17}$  乃至  $3 \times 10^{17} \text{ cm}^{-3}$  の範囲内にあり、前記極小となる部分において  $1 \times 10^{16}$  乃至  $9 \times 10^{16} \text{ cm}^{-3}$  の範囲内にあり、前記ドレイン層と隣接した部分において  $1 \times 10^{17}$  乃至  $3 \times 10^{17} \text{ cm}^{-3}$  の範囲内にあることを特徴とする請求項 1 記載の半導体装置。

【請求項 3】

隣接する一対の前記トレンチ・ゲートの間に設けられた前記ベース層の幅が、 $0.5 \mu \text{m}$  以下であることを特徴とする請求項 1 または 2 に記載の半導体装置。

【請求項 4】

前記ゲート絶縁膜は、前記ベース層に隣接した部分よりも前記ドリフト層に隣接した部分において厚く形成されたことを特徴とする請求項 1 ~ 3 のいずれか 1 つに記載の半導体装置。

【請求項 5】

前記ゲート絶縁膜の膜厚は、前記トレンチの深さ方向に沿って前記ドレイン層に近づくにつれて順次増加することを特徴とする請求項 1 ~ 4 のいずれか 1 つに記載の半導体装置。

【請求項 6】

前記ゲート絶縁膜の膜厚は、前記トレンチの深さ方向に沿って前記ドレイン層に近づくにつれて段階的に増加することを特徴とする請求項 1 ~ 4 のいずれか 1 つに記載の半導体装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、半導体装置に関し、特に縦型 MOS (Metal-Oxide-Semiconductor) ゲート構造を有する半導体装置に関する。

【0002】

【従来の技術】

半導体中にトレンチ (trench: 溝) を形成し、これをを利用して形成するトレンチ・ゲート構造は、IGBT (Insulated Gate Bipolar Transistor) や MOSFET (Field Effect Transistor) などの半導体素子に応用され、特に電力用などの用途において有利な構造である。例えば、トレンチ・ゲート構造を有する MOSFET は、スイッチング速度が速く、電流容量が大きく、数 10 ボルト ~ 100 ボルト程度の耐圧が得られるため、携帯型端末やパーソナル・コンピュータなどのスイッチング電源などに広く利用されつつある。

【0003】

以下、このような MOS ゲートパワー半導体装置の一例として、n チャネル型トレンチ MOSFET を例に挙げて説明する。

【0004】

図 10 は、本発明者が本発明に至る過程で試作した n チャネル型トレンチ MOSFET の要部断面構造を表す模式図である。

【0005】

すなわち、同図は、パワー MOSFET として半導体ウェーハ上に並列形成された複数の素子単位のうちのひとつの素子単位の半分 (ハーフピッチ) の断面構造を表す。

【0006】

その概略構造を説明すると、n<sup>-</sup> 型ドリフト層 108 と p 型ベース層 110 が積層形成された半導体ウェーハに、トレンチ T が形成され、このトレンチ T の内壁面に形成されたゲート絶縁膜 102 を介してゲート電極 104 が形成されている。n<sup>-</sup> 型ドリフト層 108 の裏面側には n<sup>+</sup> 型ドレイン領域 112 を介してドレイン電極 114 が形成されている。一方、p 型ベース層 110 の上には、ゲートに隣接して形成された n<sup>+</sup> 型ソース領域 116 と、これに隣接して形成された p<sup>+</sup> 型領域 118 とが設けられ、これらを跨ぐようにソース電極 120 が形成されている。

10

20

30

40

50

## 【0007】

このようなパワーMOSFETにおいて、ゲート電極104に所定の電圧を印加すると、p型ベース層110のうちのゲート絶縁膜102に隣接した領域に反転層が形成され、ソースとドレインとの間でオン状態が形成される。

## 【0008】

## 【発明が解決しようとする課題】

しかし、図10に例示したようなMOSFETにおいては、素子を微細化してもオン抵抗を効果的に低減できないという問題があった。

## 【0009】

すなわち、図10に例示したようなMOSFETの場合、オン時の素子の抵抗、すなわち「オン抵抗」は、主に「チャネル抵抗成分」と「ドリフト抵抗成分」とにより決定される。<sup>10</sup>「チャネル抵抗成分」とは、オン時にp型ベース領域110に形成されるチャネル領域の抵抗成分であり、一方、「ドリフト抵抗成分」とは、n<sup>-</sup>型ドリフト層108においてオン電流が受ける抵抗成分である。

## 【0010】

素子のオン抵抗を下げるために、当初は、図10における素子単位のピッチaを縮小することによって素子密度すなわちチャネル密度を増加させ、素子のオン抵抗を低減させてきた。

## 【0011】

しかしながら、近年の半導体微細加工技術の急速な進展により、チャネル密度は急速に増大し、「チャネル抵抗成分」は大幅に低下しつつある。具体的には、素子ピッチaが、0.5 μmを下回るまで微細化が進められつつある。つまり、図10には素子単位の半分(ハーフピッチ)を表したが、この図示した構造を左右に展開した実際の素子においては、隣接する2つのトレンチ・ゲートの間に挟まれたp型ベース層110の幅は、素子ピッチaにほぼ等しく、0.5 μmを下回るまでに微細化されつつある。<sup>20</sup>

## 【0012】

そして、このような状況において、最新のパワーMOSFETにおけるオン抵抗は、前述したドリフト抵抗成分によるものが抵抗全体の約2/3を占めるまでになりつつある。

## 【0013】

つまり、製造プロセスをさらに改良して素子ピッチaをさらに微細化させたとしても、素子のオン抵抗の顕著な低下は望めないという問題が生じている。<sup>30</sup>

## 【0014】

例えば、素子耐圧が30ボルト系のMOSFETの場合、素子のオン抵抗を20 m<sup>2</sup>以下に下げるることは非常に困難になっている。

## 【0015】

この問題に対処するためには、ドリフト層108の層厚tを薄くして「ドリフト抵抗成分」を下げる必要がある。このために、ゲート絶縁膜を厚くして、ゲート(ソース)・ドレイン間に電圧が印加された時に、印加電圧の一部をゲート絶縁膜に分担させることによって、ドリフト層の厚さを薄くする方法も考えられる。

## 【0016】

図11は、この発想に基づいて作成したMOSFETの断面構造を表す模式図である。<sup>40</sup>すなわち、同図に例示したMOSFETの場合、ゲート絶縁膜102を厚く形成することにより印加電圧を負担させ、これによってドリフト層108の層厚tを薄くしている。

## 【0017】

しかし、このようにゲート絶縁膜102を厚く形成すると、閾値電圧が上昇してしまう。その結果として、同一のゲート電圧を印加した場合のオン抵抗は、チャネル抵抗が高くなる分だけ上昇し、素子全体のオン抵抗を効果的に低減することができないという問題があった。

## 【0018】

以上説明したように、従来のパワーMOSFETにおいては、オン抵抗が「ドリフト抵抗

10

20

30

40

50

成分」により決定されているために、素子を微細化してもそのオン抵抗を効率良く低下できないという問題があった。

【0019】

本発明は、かかる課題の認識に基づいてなされたものであり、その目的は、ドリフト抵抗成分を効果的に下げるによって、素子を微細化するとオン抵抗をさらに低減できるような独特の構造を有するパワーMOSFETなどの半導体装置を提供することにある。

【0020】

【課題を解決するための手段】

上記目的を達成するために、本発明の一態様によれば、第1導電型のドレイン層と、前記ドレイン層の上に設けられ前記ドレイン層よりも不純物濃度が低い第1導電型のドリフト層と、前記ドリフト層の上に設けられた第2導電型のベース層と、前記ベース層の上に設けられた第1導電型のソース領域と、前記ベース層と前記ドリフト層を貫通して前記ドレイン層に達するトレンチの内壁面に形成されたゲート絶縁膜及びこれを介して前記トレンチの内部に設けられたゲート電極とを有するトレンチ・ゲートと、を備え、前記ドリフト層は、前記ドレイン層の近傍において、前記トレンチの深さ方向に沿って前記ドレイン層に近づくに従って前記第1導電型の不純物濃度が上昇する濃度勾配を有し、前記ドリフト層は、前記ベース層の近傍において、前記トレンチの深さ方向に沿って前記ベース層に近づくに従って前記第1導電型の不純物濃度が上昇する濃度勾配を有し、前記ドリフト層は、前記ドレイン層との界面近傍の不純物濃度の遷移する領域を除く部分において、前記トレンチの深さ方向に沿って上部と下部との間に前記第1導電型の不純物濃度が極小となる部分を有することを特徴とする半導体装置が提供される。

【0021】

上記構成によれば、耐圧を維持しつつドリフト抵抗成分を効果的に低減することができる。

【0024】

ここで、前記ドリフト層の前記不純物濃度は、前記ベース層と隣接した部分において  $1 \times 10^{17}$  乃至  $3 \times 10^{17} \text{ cm}^{-3}$  の範囲内にあり、前記極小となる部分において  $1 \times 10^{16}$  乃至  $9 \times 10^{16} \text{ cm}^{-3}$  の範囲内にあり、前記ドレイン層と隣接した部分において  $1 \times 10^{17}$  乃至  $3 \times 10^{17} \text{ cm}^{-3}$  の範囲内にあることを特徴とすると、耐圧とオン抵抗のバランスの点で特に好ましい。

【0025】

また、隣接する一対の前記トレンチ・ゲートの間に設けられた前記ベース層の幅が、 $0.5 \mu\text{m}$  以下であるような微細化を実施した際に、本発明は特に有効に作用する。

【0026】

また、前記トレンチ・ゲートは、前記ドレイン層に達するものとすることにより、ドリフト層の厚みを薄くしてドリフト抵抗成分を顕著に低減することができる。

【0027】

【発明の実施の形態】

以下、図面を参照しつつ本発明の実施の形態について説明する。

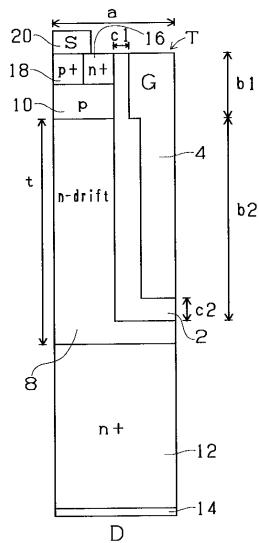

【0028】

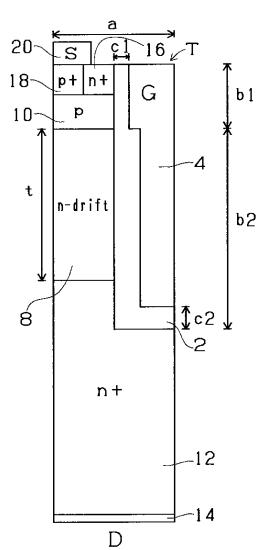

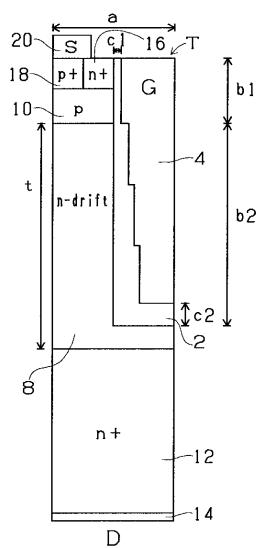

図1は、本発明の実施の形態にかかるnチャネルトレンチMOSFETの要部断面構造を表す模式図である。

【0029】

すなわち、同図は、パワーMOSFETとして半導体ウェーハ上に並列形成された複数の素子単位のうちのひとつの素子単位の半分(ハーフピッチ)の断面構造を表す。

【0030】

その構造を概説すると、n<sup>+</sup>型ドレイン層12、n型ドリフト層8およびp型ベース層10が積層形成された半導体ウェーハに、トレンチTが形成され、このトレンチTの内壁面に形成されたゲート絶縁膜2を介してゲート電極4が形成されている。すなわち、トレンチ・ゲートは、ウェーハの表面側からn型ドリフト層8を貫通してn<sup>+</sup>型ドレイン層12

10

20

30

40

50

に達するように形成されている。

【0031】

p型ベース層10の上には、トレンチ・ゲートに隣接して形成されたn<sup>+</sup>型ソース領域16と、これに隣接して形成されたp<sup>+</sup>型領域18とが設けられ、これらを跨ぐようにソース電極20が形成されている。

【0032】

一方、n<sup>+</sup>型ドレイン領域12の裏面側には、ドレイン電極14が形成されている。

【0033】

ここで、図1に例示したMOSFETにおいては、ゲート絶縁膜2の厚みが2段階に変化している点にひとつの特徴がある。つまり、トレンチ・ゲートのうちの、p型ベース層10まではゲート絶縁膜2は薄く、ドリフト層8とn<sup>+</sup>ドレイン層12に隣接する部分においては、ゲート絶縁膜2は厚く形成されている。このようにゲート絶縁膜2の厚みに分布を設けることにより、素子の閾値を上げることなく、ゲート絶縁膜2に電圧を分担させてドリフト層8の厚みを薄くすることができる。10

【0034】

すなわち、チャネルが形成されるp型ベース層10の部分b1においては、ゲート絶縁膜2の膜厚C1は薄く形成されている。このように、ベース層10に隣接したゲート絶縁膜2を薄くすると、同じ電圧値が印加されたときに、絶縁膜が厚い場合と比較して閾値を下げることができ、同時に、チャネルの反転度が増すため電流の流量が多くなりオン抵抗を低減することができる。20

【0035】

そして、ドリフト層8以下の部分b2においてはゲート絶縁膜2の膜厚C2を厚く形成することにより、ゲート(ソース)・ドレイン間に印加される電圧の一部を分担させることができが可能となる。その結果として、ドリフト層8の層厚tを薄くして「ドリフト抵抗成分」を効果的に下げることができる。その結果として、素子のオン抵抗を下げることが可能となる。

【0036】

このようにしてドリフト層8の層厚tを薄くできるため、図1に例示した構造の場合、トレンチ・ゲートが、薄いドリフト層8を貫通してドレイン層12にまで貫通した構造となっている。但し、後に本発明の変型例として紹介するように、トレンチ・ゲートは、ドリフト層8を必ずしも貫通する必然性はなく、ドリフト層8の途中まで形成されていてもよい。30

【0037】

さて、本発明のMOSFETの2つ目の特徴は、ドリフト層8の不純物濃度勾配にある。すなわち、本発明においては、ドリフト層8の不純物濃度勾配を深さ方向に見て一定ではなく、独特的の分布とすることにより、「ドリフト抵抗成分」をさらに効果的に下げることができる。

【0038】

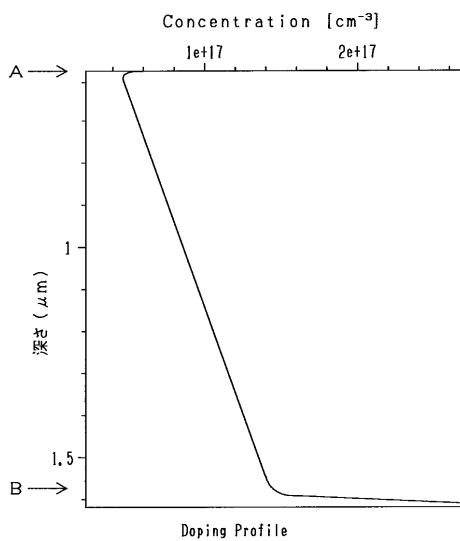

図2は、本発明のMOSFETのドリフト層8における深さ方向の不純物濃度勾配を例示するグラフ図である。本発明においては、まず、同図に表したように、ドリフト層8のn型不純物の濃度を深さ方向に見て順次増加するように分布させる。本発明者の試作検討の結果によれば、同図に例示した如く、ドリフト層8の上端A、すなわちp型ベース層10に隣接した部分における不純物濃度は、 $1 \times 10^{16}$  乃至  $9 \times 10^{16} \text{ cm}^{-3}$  の範囲内にあることが望ましいことが分かった。上端Aにおける濃度がこれよりも高いと、素子の耐圧が不足し、逆に濃度がこれよりも低いと、オン抵抗が十分に下がらないからである。40

【0039】

さらに、素子の耐圧とオン抵抗とのバランスを考慮すると、上端Aにおけるドリフト層8の不純物濃度は、より実用的には、 $3 \times 10^{16}$  乃至  $7 \times 10^{16} \text{ cm}^{-3}$  の範囲内にあることが望ましく、さらに好適には、 $4 \times 10^{16}$  乃至  $6 \times 10^{16} \text{ cm}^{-3}$  の範囲内にあることがさらに望ましい。50

## 【0040】

次に、ドリフト層8の不純物濃度を図2の如く変化させた場合の下端B、すなわちドレイン層12に隣接した部分の不純物濃度について説明する。

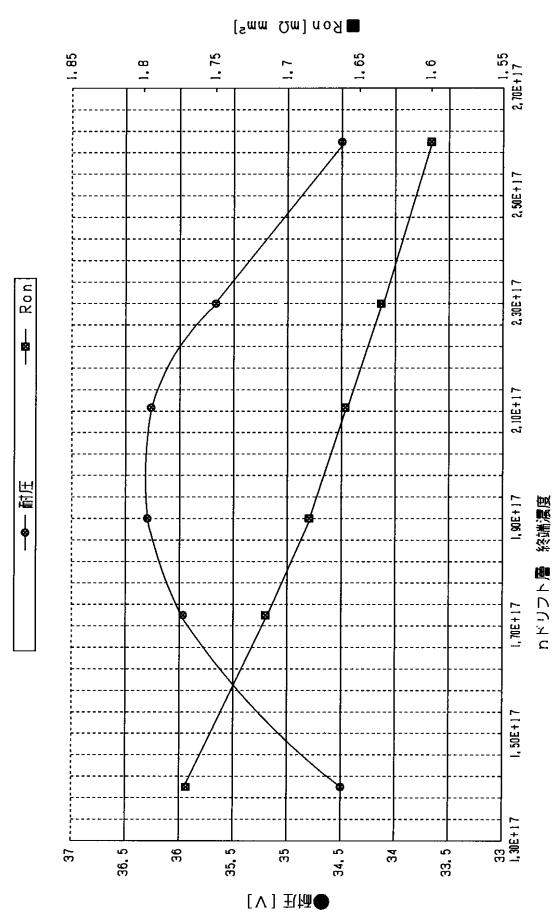

## 【0041】

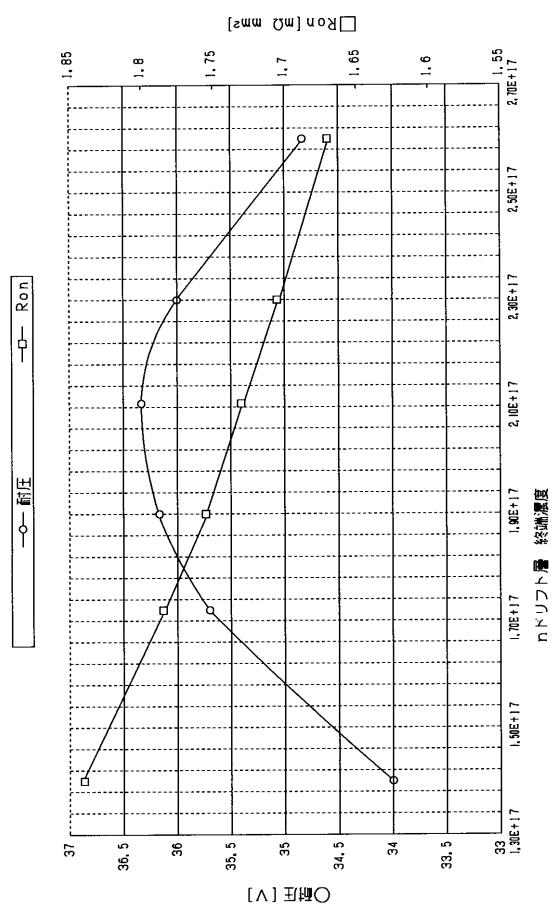

図3は、ドリフト層8の下端の不純物濃度に対するMOSFETの耐圧Vとオン抵抗Ronの依存性を表すグラフ図である。

## 【0042】

すなわち、同図の横軸はドリフト層8の下端Bにおける不純物濃度を表し、同図の左縦軸はMOSFETの耐圧V、右縦軸はオン抵抗Ronをそれぞれ表す。なお、ここでドリフト層8の上端Aにおける不純物濃度は $5.5 \times 10^{16} \text{ cm}^{-3}$ に固定した。 10

## 【0043】

またここで用いた素子構造パラメータとしては、図1に表した素子単位のハーフピッチa = 0.4 μm、ドリフト層8の層厚t = 1.2 μm、薄いゲート絶縁膜の部分b1 = 0.5 μm、厚いゲート絶縁膜の部分b2 = 1.5 μm、薄いゲート絶縁膜の膜厚c1 = 0.015 μm、厚いゲート絶縁膜の膜厚c2 = 0.15 μmとした。

## 【0044】

図3から、素子のオン抵抗Ronは、下端Bの不純物濃度を上げるに従って低下する一方、素子の耐圧Vは、不純物濃度に対して極大値を有することが分かる。例えば、ドリフト層の不純物濃度が約 $2.1 \times 10^{17} \text{ cm}^{-3}$ において耐圧は約36.3ボルトのピーク値を達成し、この時のオン抵抗は、約 $1.73 \text{ m mm}^2$ である。 20

## 【0045】

また、ドリフト層8下端の不純物濃度を $2.3 \times 10^{17} \text{ cm}^{-3}$ とすると、素子の耐圧Vは36ボルトで、オン抵抗Ronは約 $1.7 \text{ m mm}^2$ となる。

ドリフト層の不純物濃度を一定としたこれまでのMOSFETと比較すると、上記具体例の場合、オン抵抗を約1/10に低減できる。

## 【0046】

より一般的には、ドリフト層8の前記不純物濃度は、ドレイン層12と隣接した部分において、 $1 \times 10^{17}$ 乃至 $3 \times 10^{17} \text{ cm}^{-3}$ の範囲内にあることが望ましい。さらに、素子の耐圧とオン抵抗とのバランスを考慮すると、ドリフト層8の前記不純物濃度は、ドレイン層12と隣接した部分において、 $1.7 \times 10^{17}$ 乃至 $2.4 \times 10^{17} \text{ cm}^{-3}$ の範囲内にあることが望ましい。さらに、ドレイン層12と隣接した部分において、 $1.8 \times 10^{17}$ 乃至 $2.3 \times 10^{17} \text{ cm}^{-3}$ の範囲内とすると、36ボルトを越える高耐圧が得られる点でさらに望ましい。 30

## 【0047】

本発明によれば、このように、ドリフト層8の不純物濃度を深さ方向に見て順次増加するような分布とすることにより、耐圧を維持しつつ、「ドリフト抵抗成分」を効果的に下げることができる。つまり、耐圧を維持しつつ、素子のオン抵抗を低下させることができるとなる。

## 【0048】

ドリフト層8とドレイン層12の不純物濃度は、2桁ほども異なるために、その境界面での電界集中が問題となる。本発明によれば、ゲート絶縁膜2を厚くすることによって臨界電界を上げることができるが、さらにドリフト層8にこのような濃度勾配を設けることによって電界が境界部のみに集中することを抑制し、ドリフト層の下部（ドレイン層に近い部分）から中部に向けて電界集中領域を拡げて緩和させることによって耐圧が上昇し、そのぶんドリフト層濃度の底上げができることによりオン抵抗を下げることが可能となる。 40

## 【0049】

なお、図2においては、ドリフト層8の不純物濃度がほぼ直線状に変化する分布を例示したが、本発明はこれには限定されず、不純物濃度は、曲線状あるいは階段状に変化しても良い。すなわち、ドリフト層8の不純物濃度が深さ方向にみて順次増加するような分布であって、同様の効果が得られる限りにおいては、本発明の範囲に包含される。従って、例 50

えば、ドリフト層8の形成にあたって、不純物濃度が異なる複数の層を順次形成しても良い。

【0050】

さらに、本発明者は、ドリフト層8の不純物濃度にもうひとつの工夫を加えることにより、耐圧を維持しつつオン抵抗をさらに下げることができるこことを知得するに至った。

【0051】

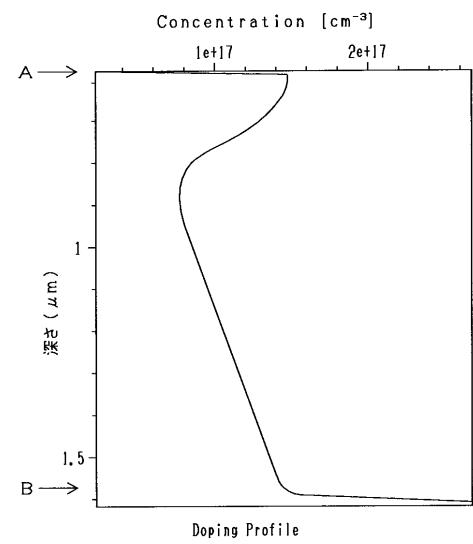

図4は、本発明におけるドリフト層8の不純物濃度分布のもうひとつの例を表すグラフ図である。すなわち、同図の横軸はドリフト層8の深さ方向の距離を表し、縦軸はドリフト層8の不純物濃度を表す。

【0052】

図4に例示した不純物濃度分布は、深さ方向に見て「略V字状」の不純物濃度分布を有する。これは換言すると、図2に例示したような不純物濃度分布において、上側すなわちp型ベース層10と接する部分に、高い不純物濃度の領域を付加した分布であると言える。

【0053】

本発明者は、図4に例示した不純物濃度分布を有する素子についても定量的な評価を行った。

【0054】

図5は、図4に表した不純物濃度分布を与えた場合のドリフト層8の下端の不純物濃度に対するMOSFETの耐圧Vとオン抵抗Ronの依存性の一例を表すグラフ図である。

【0055】

すなわち、同図の横軸はドリフト層8の下端Bにおける不純物濃度を表し、同図の左縦軸はMOSFETの耐圧V、右縦軸はオン抵抗Ronをそれぞれ表す。なお、ここでの素子構造パラメータは図3に関して前述したのと同様である。また、ドリフト層の上端Aにおける不純物濃度は、 $1.5 \times 10^{17} \text{ cm}^{-3}$ に固定した。

【0056】

図5から、素子のオン抵抗Ronは、下端Bの不純物濃度を上げるに従って低下する一方、素子の耐圧Vは、不純物濃度に対して極大値を有することが分かる。これらの傾向は、図3に例示したものと同様であるが、図3と比較すると、耐圧はほぼ同一レベルを維持しつつ、オン抵抗Ronが有意に下がっていることが分かる。

【0057】

例えば、図5においては、ドリフト層の不純物濃度が約 $1.9 \times 10^{17} \text{ cm}^{-3}$ ～ $2.1 \times 10^{17} \text{ cm}^{-3}$ において耐圧は約36.3ボルトのピーク値を達成している。そして、この時のオン抵抗は、不純物濃度が約 $1.9 \times 10^{17} \text{ cm}^{-3}$ の場合に、約1.68ボルトであり、不純物濃度が $2.1 \times 10^{17} \text{ cm}^{-3}$ においては約1.66ボルトまで低下している。つまり、図3と比較すると、耐圧はほぼ同一で、オン抵抗を約10パーセント下げることができる。

【0058】

ここで、再び図4に戻ってより一般的な場合について説明をすると、ドリフト層8の上端A、すなわちp型ベース層10に隣接した部分における不純物濃度は、 $1 \times 10^{17}$ 乃至 $3 \times 10^{17} \text{ cm}^{-3}$ の範囲内にあることが望ましい。上端Aにおける濃度がこれよりも高いと、素子の耐圧が不足し、逆に濃度がこれよりも低いと、オン抵抗が十分に下がらないからである。

【0059】

さらに、素子の耐圧とオン抵抗とのバランスを考慮すると、上端Aにおけるドリフト層8の不純物濃度は、より実用的には、 $1.4 \times 10^{17}$ 乃至 $2 \times 10^{17} \text{ cm}^{-3}$ の範囲内にあることが望ましい。

【0060】

一方、ドリフト層8の不純物濃度が極小となる部分においては、その値は、 $1 \times 10^{16}$ 乃至 $9 \times 10^{16} \text{ cm}^{-3}$ の範囲内にあることが望ましい。

【0061】

10

20

30

40

50

また、ドリフト層8の前記不純物濃度は、ドレイン層12と隣接した部分においては、 $1 \times 10^{17}$ 乃至 $3 \times 10^{17} \text{ cm}^{-3}$ の範囲内にあることが望ましい。さらに、素子の耐圧とオン抵抗とのバランスを考慮すると、ドリフト層8の前記不純物濃度は、ドレイン層12と隣接した部分において、 $1.4 \times 10^{17}$ 乃至 $2.6 \times 10^{17} \text{ cm}^{-3}$ の範囲内にあることが望ましい。さらに、この部分の不純物濃度を $1.7 \times 10^{17}$ 乃至 $2.2 \times 10^{17} \text{ cm}^{-3}$ の範囲内とすれば、36ボルトを越える耐圧が得られる点で顕著な効果が得られる。

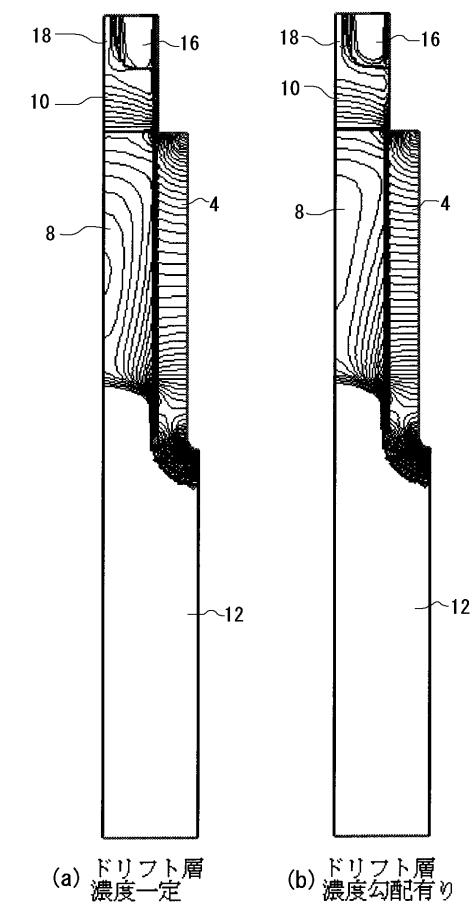

#### 【0062】

図6は、素子内部におけるブレイクダウン時の電界分布の一例を表す模式図である。すなわち、同図(a)は、ドリフト層の不純物濃度分布が深さ方向に一定の場合の電界分布を表し、同図(b)は、ドリフト層の不純物濃度分布が図4に表した分布を有する素子の電界分布をそれぞれ表す。

#### 【0063】

ここで、図6(a)の素子の場合、本発明による同図(b)の素子とほぼ同程度のオン抵抗とするために、n型不純物の濃度をドリフト層全体に亘って $1.45 \times 10^{17} \text{ cm}^{-3}$ とした。この評価の結果、ドリフト層の不純物濃度が一定の場合(図6(a))の耐圧は約34ボルトであったのに対し、本発明に基づき略V字状の濃度分布を与えた場合(図6(b))は、耐圧を約36.3ボルトまで高めることができた。つまり、ドリフト層の不純物濃度を一定とした場合と比較すると、本発明によれば、素子のオン抵抗を同程度とした場合に耐圧を高くすることができる。

#### 【0064】

ドリフト層に図4に例示したような略V字状の濃度分布を設けると素子の特性が向上する理由は、以下の通りである。

#### 【0065】

すなわちまず、ドリフト層8の下側においてドレイン層12へ向けて上昇する濃度勾配を与えることにより、前述したように、ドリフト層8とドレイン層12との間の電界集中を緩和して耐圧の向上とオン抵抗の低減を果たせる。

#### 【0066】

さらに、チャネルがオンして電流が流れるドリフト層8の上側(ベース層側)に適度な高濃度領域を挿入することによって、電界緩和と同時にオン抵抗の低減を実現できる。これは下側の電界集中領域から離れ、影響の少ない上側は濃度を上げても目的とする電界緩和を果たせるためである。

#### 【0067】

図6に表したブレイクダウン時の電界分布を見ても、ドリフト層の濃度一定の場合(図6(a))は耐圧が34.0V程度にとどまるのに対し、略V字状の濃度勾配を設けた場合(図6(b))は耐圧が36.4Vまで上昇しており、ブレイクダウン電圧が高い(印加電圧が高い)のにもかかわらず、ドリフト層8とドレイン層12とゲート絶縁膜2の交わる部分の電界集中度を同等に抑制ができていることが見てとれる。

#### 【0068】

このように、本発明によれば、ドリフト層の深さ方向の濃度分布を略V字状とすることにより、耐圧を下げる事なく、素子のオン抵抗を効果的に下げることができる。これは、素子のオン状態における抵抗成分のうちの「ドリフト抵抗成分」すなわち、ドリフト層8における抵抗成分を効果的に下げたことを意味する。

#### 【0069】

その結果として、素子のオン抵抗に占める「チャネル抵抗成分」の割合が増加する。従つて、素子ピッチ(図1における幅a)を縮小することによりチャネル密度を上げて「チャネル抵抗成分」を下げれば、素子のオン抵抗をさらに低下させることが可能となる。つまり、素子単位を微細化することによるオン抵抗の低減を果たせるようになる。

#### 【0070】

本発明のこの効果は、図1に例示した素子単位を左右に展開した場合に形成される実際の

10

20

30

40

50

素子構造において、隣接するトレンチ・ゲートの間に挟まれたp型ベース層10の幅が0.5μmを下回るほどに微細化が進んだ時に、特に顕著となる。

【0071】

つまり、本発明によれば、このように素子を微細化して、オン抵抗に占める「ドリフト抵抗成分」の割合が顕著となった時に、その「ドリフト抵抗成分」を効果的に下げ、結果として、素子のオン抵抗を大幅に低下させることが可能となる。

【0072】

なお、図4においては、ドリフト層8の不純物濃度がほぼ連続的な曲線状に変化する分布を例示したが、本発明はこれには限定されず、不純物濃度は、直線状あるいは階段状に変化しても良い。すなわち、ドリフト層8の不純物濃度が深さ方向にみて極小値を有する略V字状の分布を有する限りにおいては、本発明の範囲に包含される。従って、例えば、ドリフト層8の形成にあたって、不純物濃度が異なる複数の層を順次形成しても良い。

【0073】

次に、本発明のMOSFETの変型例のいくつかを紹介する。

【0074】

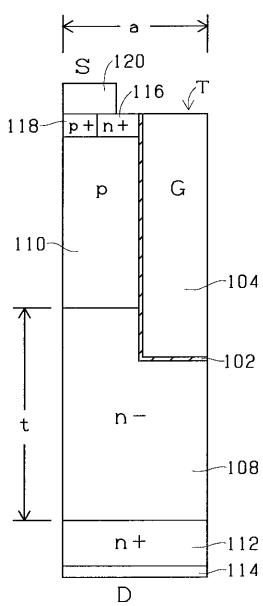

図7は、本発明のMOSFETの第1の変型例を表す要部断面図である。同図についても、図1乃至図6に関して前述した要素に同一の符号を付して詳細な説明は省略する。

【0075】

本変型例においても、ドリフト層8は、図2あるいは図4に例示したような不純物濃度分布を有する。そしてさらに、本変型例においては、トレンチ・ゲートがn型ドリフト層8を貫通しておらず、ドリフト層8の途中で終端している。素子のオン抵抗よりも耐圧のほうがより優先されるような用途においては、このような構造が好適である場合もある。

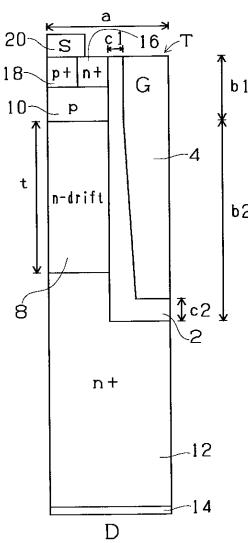

【0076】

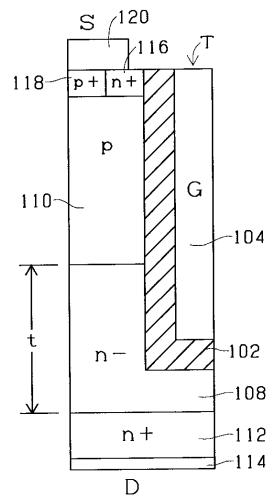

図8は、本発明のMOSFETの第2の変型例を表す要部断面図である。同図についても、図1乃至図7に関して前述した要素に同一の符号を付して詳細な説明は省略する。

【0077】

本変型例においても、ドリフト層8は、図2あるいは図4に例示したような不純物濃度分布を有する。そしてさらに、本変型例においては、ゲート絶縁膜2の膜厚が、トレンチTの深さ方向に沿って順次増加するような分布を有する。このようにしても、素子の閾値を上げることなく、ドリフト層に隣接した部分においては、ゲート(ソース)・ドレイン間に印加された電圧の一部を厚いゲート絶縁膜2に分担させて、ドリフト層8の膜厚tを薄くして「ドリフト抵抗成分」を低下させることができる。

【0078】

なお、図8に表した具体例においては、トレンチ・ゲートがドリフト層8を貫通しているが、これの代わりに図7に例示した如く、トレンチ・ゲートがドリフト層8の途中で終端していてもよいことはもちろんである。

【0079】

図9は、本発明のMOSFETの第3の変型例を表す要部断面図である。同図についても、図1乃至図8に関して前述した要素に同一の符号を付して詳細な説明は省略する。

【0080】

本変型例においても、ドリフト層8は、図2あるいは図4に例示したような不純物濃度分布を有する。そしてさらに、本変型例においては、ゲート絶縁膜2の膜厚が、トレンチTの深さ方向に沿って段階的に増加するような分布を有する。このようにしても、素子の閾値を上げることなく、ドリフト層に隣接した部分においては、ゲート(ソース)・ドレイン間に印加された電圧の一部を厚いゲート絶縁膜2に分担させて、ドリフト層8の膜厚tを薄くして「ドリフト抵抗成分」を低下させることができる。

【0081】

なお、図9に表した具体例においては、トレンチ・ゲートがドリフト層8の途中で終端しているが、これの代わりに図1乃至図8に例示した如く、トレンチ・ゲートがドリフト層8を貫通していてもよいことはもちろんである。

10

20

30

40

50

## 【0082】

以上、具体例を参照しつつ本発明の実施の形態について説明した。しかし、本発明は、これらの具体例に限定されるものではない。

## 【0083】

例えば、各具体例における各要素の寸法や形状、導電型、不純物濃度、材料などについては、当業者が公知の範囲から適宜選択して本発明と同様の作用効果が得られるものも本発明の範囲に包含される。

## 【0084】

## 【発明の効果】

以上詳述したように、本発明によれば、チャネル部のゲート絶縁膜は薄く、ドリフト層に隣接したゲート絶縁膜は厚く形成することにより、素子の閾値を上げることなく、ゲート絶縁膜に電圧を分担させてドリフト層の厚みを薄くすることができる。その結果として、ドリフト抵抗成分を低下させ、素子のオン抵抗を効果的に下げることができる。10

## 【0085】

また、本発明によれば、ドリフト層の不純物濃度を深さ方向に見て順次増加するような分布とすることにより、耐圧を維持しつつ、ドリフト抵抗成分を効果的に下げることができる。つまり、耐圧を維持しつつ、素子のオン抵抗を低下させることができるとなる。

## 【0086】

また、本発明によれば、ドリフト層の深さ方向の濃度分布を略V字状とすることにより、耐圧を下げることなく、素子のオン抵抗のうちのドリフト抵抗成分を効果的に下げることができる。その結果として、素子のオン抵抗に占める「チャネル抵抗成分」の割合が増加し、素子ピッチを縮小することによりチャネル密度を上げて「チャネル抵抗成分」を下げれば、素子のオン抵抗をさらに低下させることができるとなる。20

## 【0087】

つまり、本発明によれば、耐圧を維持しつつオン抵抗を低減した半導体装置を提供することができるようになり、産業上のメリットは多大である。

## 【図面の簡単な説明】

【図1】本発明の実施の形態にかかるnチャネルトレンチMOSFETの要部断面構造を表す模式図である。

【図2】本発明のMOSFETのドリフト層8における深さ方向の不純物濃度勾配を例示するグラフ図である。30

【図3】ドリフト層8の下端の不純物濃度に対するMOSFETの耐圧Vとオン抵抗R<sub>on</sub>の依存性を表すグラフ図である。

【図4】本発明におけるドリフト層8の不純物濃度分布のもうひとつの例を表すグラフ図である。

【図5】図4に表した不純物濃度分布を与えた場合のドリフト層8の下端の不純物濃度に対するMOSFETの耐圧Vとオン抵抗R<sub>on</sub>の依存性を表すグラフ図である。

【図6】素子内部におけるブレイクダウン時の電界分布の一例を表す模式図である。

【図7】本発明のMOSFETの第1の変型例を表す要部断面図である。

【図8】本発明のMOSFETの第2の変型例を表す要部断面図である。40

【図9】本発明のMOSFETの第3の変型例を表す要部断面図である。

【図10】本発明者が本発明に至る過程で試作したnチャネルトレンチMOSFETの要部断面構造を表す模式図である。

【図11】ゲート絶縁膜を厚くしたMOSFETの断面構造を表す模式図である。

## 【符号の説明】

2 ゲート絶縁膜

4 ゲート電極

8 ドリフト層

10 ベース層

12 ドレイン層

- 1 4 ドレイン電極

1 6 ソース領域

1 8 p型領域

2 0 ソース電極

1 0 2 ゲート絶縁膜

1 0 4 ゲート電極

1 0 8 ドリフト層

1 1 0 ベース層

1 1 2 ドレイン領域

1 1 4 ドレイン電極

1 1 6 ソース領域

1 1 8 p<sup>+</sup>型領域

1 2 0 ソース電極

T トレンチ

- 10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(56)参考文献 米国特許第05637898(US, A)

特開昭63-174373(JP, A)

特開昭57-042164(JP, A)

特開平09-283535(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78

H01L 21/336