(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4122113号

(P4122113)

(45) 発行日 平成20年7月23日(2008.7.23)

(24) 登録日 平成20年5月9日(2008.5.9)

(51) Int.Cl.

H01L 29/06 (2006.01)

H01L 29/78 (2006.01)

F 1

H01L 29/78 652P

請求項の数 1 (全 9 頁)

(21) 出願番号 特願平11-177950

(22) 出願日 平成11年6月24日(1999.6.24)

(65) 公開番号 特開2001-7322(P2001-7322A)

(43) 公開日 平成13年1月12日(2001.1.12)

審査請求日 平成17年7月26日(2005.7.26)

(73) 特許権者 000002037

新電元工業株式会社

東京都千代田区大手町2丁目2番1号

(74) 代理人 100102875

弁理士 石島 茂男

(74) 代理人 100106666

弁理士 阿部 英樹

(72) 発明者 中村 秀幸

埼玉県飯能市南町10番13号 新電元工

業株式会社飯能工場内

(72) 発明者 宮腰 宣樹

埼玉県飯能市南町10番13号 新電元工

業株式会社飯能工場内

審査官 小野田 誠

最終頁に続く

(54) 【発明の名称】高破壊耐量電界効果型トランジスタ

## (57) 【特許請求の範囲】

## 【請求項 1】

ドレイン層と、

前記ドレイン層内に形成され、前記ドレイン層とは異なる導電型のリング状の固定電位拡散層と、

前記ドレイン層の前記固定電位拡散層の内側の領域で構成される能動領域内に形成され、前記ドレイン層とは異なる導電型のベース拡散層と、

前記ベース拡散層に接続され、前記ベース拡散層と同じ導電型のチャネル拡散層と、

前記ベース拡散層と前記チャネル拡散層内に形成され、該ベース拡散層とは異なる導電型のソース拡散層と、

前記ソース拡散層の端部と前記チャネル拡散層の端部の間の前記チャネル拡散層で構成されるチャネル領域上に形成されたゲート酸化膜と、

前記ゲート酸化膜上に形成されたゲート電極膜と、

前記ソース拡散層と前記ベース拡散層に接続されたソース電極膜と、

前記ドレイン層に接続されたドレイン電極膜とを有し、前記固定電位拡散層は前記ソース電極膜に接続され、

前記固定電位拡散層の外側の領域には、前記ドレイン層とは異なる導電型で浮遊電位に置かれたガードリング拡散層が、前記固定電位拡散層とは非接触の状態で形成され、前記固定電位拡散層は前記ガードリング拡散層で囲まれ、

前記ガードリング拡散層は互いに非接触の状態で複数本配置され、

10

20

前記ゲート電極膜に接続され、外部端子に接続されるゲートパッドが、前記能動領域の外側の前記ドレイン層上に絶縁膜を介して配置され、

前記ゲートパッド直下の前記ドレイン層内には、前記ドレイン層とは異なる導電型のパッド拡散層が形成され、

該パッド拡散層は、前記固定電位拡散層に隣接する前記ガードリング拡散層に接続され、

前記ベース拡散層は前記固定電位拡散層と前記ガードリング拡散層よりも浅くされ、

前記固定電位拡散層上には前記固定電位拡散層の延在方向に沿って複数の窓開部が形成され、

前記固定電位拡散層の表面には、前記窓開部底面の前記固定電位拡散層と接触した金属膜が形成され、前記金属膜は前記ソース電極膜に電気的に接続され、前記固定電位拡散層が前記ソース電極膜と同電位にされた電界効果型トランジスタ。 10

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は電界効果型トランジスタの技術分野にかかり、特に、電界効果型トランジスタの破壊耐量を向上させる技術に関する。

【0002】

【従来の技術】

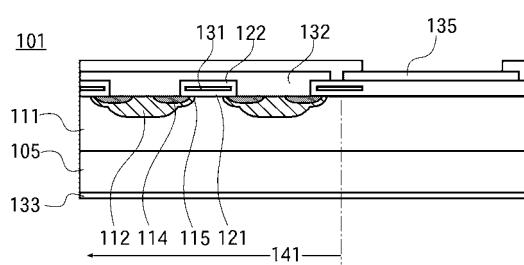

図10の符号101は従来技術のMOSFETを示している。このMOSFET101は、n<sup>+</sup>型のシリコン単結晶基板105表面に、n<sup>-</sup>型のシリコン単結晶がエピタキシャル成長で形成され、ドレイン層111が構成されている。このドレイン層111内には、フォトリソグラフ工程や拡散工程を経て、p型のベース拡散層112が形成されている。 20

【0003】

ベース拡散層112内には、n<sup>+</sup>型のソース領域114が形成されており、ドレイン層111表面のベース拡散層112外周部分とソース領域114の外周部分の間でチャネル領域115が形成されている。

【0004】

ベース拡散層112の表面の形状は正方形になっており、ドレイン層111表面に、各ベース拡散層112の辺同士が向かい合うように、多数個配置されている。 30

【0005】

チャネル領域115表面にはゲート酸化膜121が形成されており、該ゲート酸化膜121表面にはゲート電極膜131が形成されている。

【0006】

ベース拡散層112とソース領域114上にはソース電極膜132が形成されている。このソース電極膜132とゲート電極膜131とは層間絶縁膜122で絶縁された状態になっている。

【0007】

ソース電極膜132を形成するときに、ゲートパッド135が同時に形成されている。このゲートパッド135は、ソース電極膜132とは分離されており、ゲート電極膜131に接続されている。このMOSFET101は樹脂パッケージ中に封止されている。ゲートパッド135にはボンディングワイヤーの一端が接続されており、ゲート端子としてパッケージ外部に導出されている。 40

【0008】

また、ドレイン層111の裏面にはドレイン電極膜133が形成されている。ソース電極膜132とドレイン電極膜133もソース端子とドレイン端子として外部に導出されている。

【0009】

上記のような構造のMOSFET101では、ソース電極膜132を接地させ、ドレイン電極膜133に正電圧を印加した状態で、ゲート電極膜131に正電圧を印加するとチャ 50

ネル領域 115 表面に n 型の反転層が形成され、ソース領域 114 とドレイン層 111 とが反転層によって接続され、ドレイン電極膜 133 からソース電極膜 132 に向けて電流が流れる。

#### 【0010】

次に、ゲート電極膜 132 の電圧が接地電位付近になると反転層が消滅し、電流は遮断される。

#### 【0011】

一般に、MOSFET 101 では、ドレイン層 111 とベース拡散層 112 との間の p-n 接合により寄生ダイオードが形成されている。ソース電極膜 132 の電位がドレイン電極膜 133 よりも高い場合、寄生ダイオードが順バイアスされ、ソース電極膜 132 からドレイン電極膜 133 に向けて電流が流れようになっている。10

#### 【0012】

上記のような寄生ダイオードを通じて電流が流れる場合、ドレイン層 111 内に少数キャリアが注入されることになる。そして、寄生ダイオードが順バイアスされた状態から逆バイアスされると、ドレイン層 111 内に注入された少数キャリアはベース拡散層 112 に流れ込むが、能動領域 141 の周辺部分の外側には、ベース拡散層が存在しないため、その部分が破壊してしまう場合がある。

#### 【0013】

##### 【発明が解決しようとする課題】

本発明は上記従来技術の不都合を解決するために創作されたものであり、その目的は、破壊耐量の高い電界効果トランジスタを提供することにある。20

#### 【0014】

##### 【課題を解決するための手段】

上記課題を解決するために、請求項 1 記載の発明は、ドレイン層と、前記ドレイン層内に形成され、前記ドレイン層とは異なる導電型のリング状の固定電位拡散層と、前記ドレイン層の前記固定電位拡散層の内側の領域で構成される能動領域内に形成され、前記ドレイン層とは異なる導電型のベース拡散層と、前記ベース拡散層に接続され、前記ベース拡散層と同じ導電型のチャネル拡散層と、前記ベース拡散層と前記チャネル拡散層内に形成され、該ベース拡散層とは異なる導電型のソース拡散層と、前記ソース拡散層の端部と前記チャネル拡散層の端部の間の前記チャネル拡散層で構成されるチャネル領域上に形成されたゲート酸化膜と、前記ゲート酸化膜上に形成されたゲート電極膜と、前記ソース拡散層と前記ベース拡散層に接続されたソース電極膜と、前記ドレイン層に接続されたドレイン電極膜とを有し、前記固定電位拡散層は前記ソース電極膜に接続され、前記固定電位拡散層の外側の領域には、前記ドレイン層とは異なる導電型で浮遊電位に置かれたガードリング拡散層が、前記固定電位拡散層とは非接触の状態で形成され、前記固定電位拡散層は前記ガードリング拡散層で囲まれ、前記ガードリング拡散層は互いに非接触の状態で複数本配置され、前記ゲート電極膜に接続され、外部端子に接続されるゲートパッドが、前記能動領域の外側の前記ドレイン層上に絶縁膜を介して配置され、前記ゲートパッド直下の前記ドレイン層内には、前記ドレイン層とは異なる導電型のパッド拡散層が形成され、該パッド拡散層は、前記固定電位拡散層に隣接する前記ガードリング拡散層に接続され、前記ベース拡散層は前記固定電位拡散層と前記ガードリング拡散層よりも浅くされ、前記固定電位拡散層上には前記固定電位拡散層の延在方向に沿って複数の窓開部が形成され、前記固定電位拡散層の表面には、前記窓開部底面の前記固定電位拡散層と接触した金属膜が形成され、前記金属膜は前記ソース電極膜に電気的に接続され、前記固定電位拡散層が前記ソース電極膜と同電位にされた電界効果型トランジスタである。30

#### 【0018】

本発明は上記のように構成されており、能動領域が固定電位拡散層によって囲われている。固定電位拡散層はソース電極に接続されており、能動領域内に注入された少数キャリアのうち、能動領域周辺部分に存在するものを効率よく集められるようになっている。従つて、能動領域周辺部分での少数キャリアの集中が起こらず、破壊耐量の高いMOSFET40

を得ることができる。

**【0019】**

ゲートパッドは固定電位拡散層の外部に配置し、その下方のドレイン層中にはドレイン層とは異なる導電型のパッド拡散層を形成し、そのパッド拡散層を最内周のガードリング拡散層に接続し、浮遊電位に置くようにしたので、パッド拡散層もガードリング拡散層の一部となり、降伏電圧を高くすることができる。

**【0020】**

**【発明の実施の形態】**

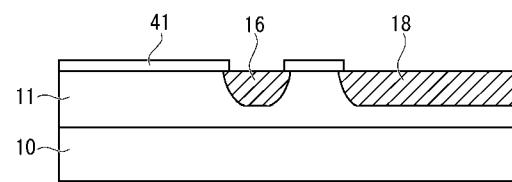

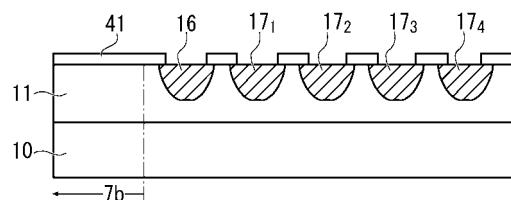

図1を参照し、符号11はn<sup>-</sup>型のシリコンエピタキシャル層から成るドレイン層を示している。このドレイン層11は、n型のシリコン単結晶から成る基板10表面に形成されている。

10

**【0021】**

ドレイン層11上には、窓開けされた酸化膜41が形成されている。酸化膜41の窓開部分からp型の不純物が深く拡散されている。

**【0022】**

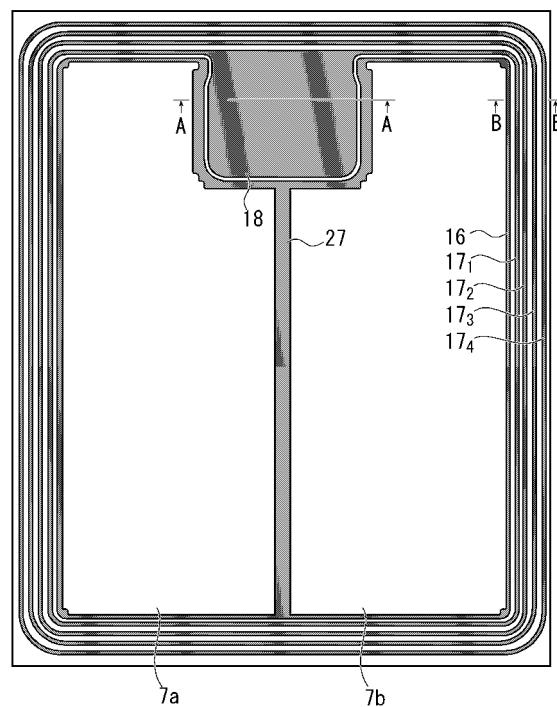

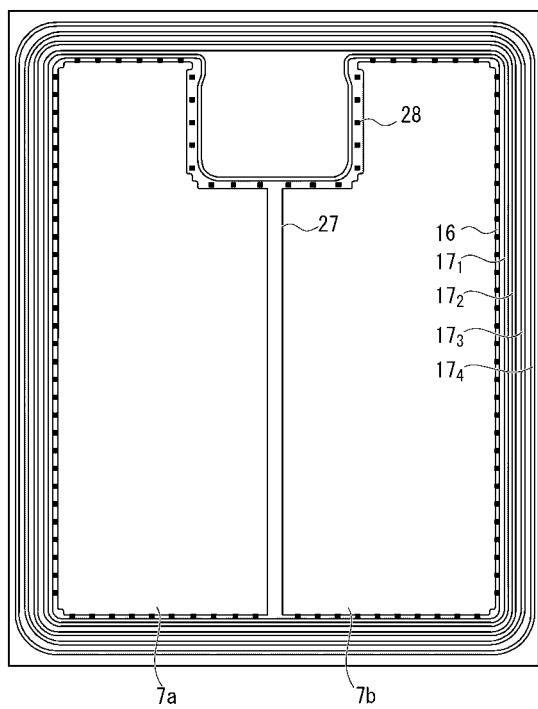

図8は、ドレイン層11の平面図であり、p型の不純物が深く拡散されたことにより、リング状の固定電位拡散層16と、該固定電位拡散層16周囲を4重に取り囲むガードリング拡散層17<sub>1</sub>～17<sub>4</sub>が形成されている。固定電位拡散層16及びガードリング拡散層17<sub>1</sub>～17<sub>4</sub>は互いに離間した状態で配置されている。

20

**【0023】**

固定電位拡散層16とガードリング拡散層17<sub>1</sub>～17<sub>4</sub>を形成するときに、略正方形のパッド拡散層18も形成されている。そのパッド拡散層18は、4本のガードリング拡散層17<sub>1</sub>～17<sub>4</sub>のうちの最内周のガードリング拡散層17<sub>1</sub>に接続されている。図1は、この図8のA-A線断面図であり、図5はB-B線断面図である。図8に示されているとおり、固定電位拡散層16は、固定電位拡散層16やガードリング拡散層17<sub>1</sub>～17<sub>4</sub>と同じ構造の拡散層から成る接続部分27(によって中央部分が接続されている)。

**【0024】**

図8の符号7a、7bは、固定電位拡散層16で囲まれたドレイン層11である能動領域である。固定電位拡散層16で囲まれた部分は接続部分27によって2つの能動領域7a、7bに分けられている。後述するベース拡散層やチャネル拡散層はこの能動領域7a、7b内に形成される。

30

**【0025】**

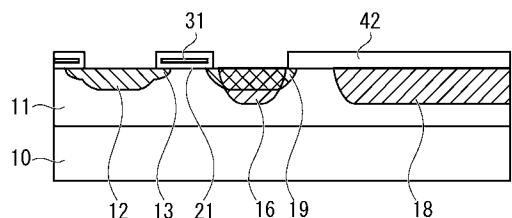

固定電位拡散層16及びガードリング拡散層17<sub>1</sub>～17<sub>4</sub>を形成した後、ドレイン層11表面に、図2に示すように、所定パターンのゲート酸化膜21とゲート電極膜31とをこの順序で形成し、ゲート電極膜31及びゲート酸化膜21の窓開け部分からドレイン層11内に2回に分けてp型の不純物を拡散させ、ベース拡散層12とチャネル拡散層13を形成する。符号19は、固定電位拡散層16の一部分に重ねて形成されたベース拡散層を示している。

**【0026】**

ベース拡散層12、19は、固定電位拡散層16やガードリング拡散層17<sub>1</sub>～17<sub>4</sub>よりも浅く、低濃度になっており、また、チャネル拡散層13はベース拡散層12、19よりも浅く、低濃度になっている。

40

**【0027】**

チャネル拡散層13を形成する際のp型不純物は、ベース拡散層12の外部からはみ出す大きさで拡散されており、チャネル拡散層13は、ベース拡散層12からはみ出した部分で構成されている。従って、チャネル拡散層13は、ベース拡散層12の端部に接続されている。

**【0028】**

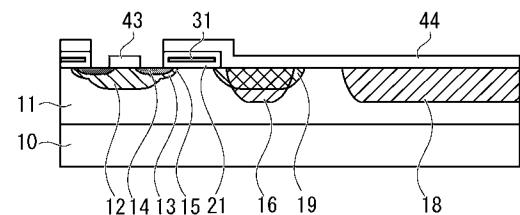

次に、図3に示すように、ベース拡散層12表面と、チャネル拡散層13のベース拡散層12に接続された部分の表面とを窓開けした状態で、ベース拡散層12の中央部分表面と

50

、固定電位拡散層16表面と、ガードリング拡散層17<sub>1</sub>～17<sub>4</sub>表面と、及びビパッド拡散層18表面とを、パターニングした酸化膜43でマスクし、n<sup>+</sup>型不純物を拡散すると、ベース拡散層12及びチャネル拡散層13で構成されるp型の拡散領域の表面に、n<sup>+</sup>型のソース拡散層14が形成される。

## 【0029】

このソース拡散層14表面の端部とチャネル拡散層13表面の端部との間のp型拡散領域でチャネル領域15が形成される。

## 【0030】

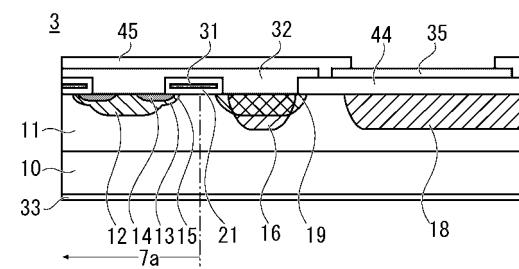

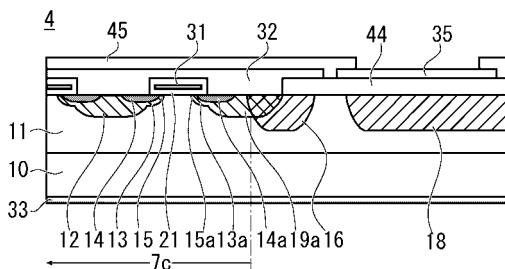

次に、ベース拡散層12上の酸化膜43を除去し、ソース拡散層14とベース拡散層12とを露出させ、金属薄膜を形成すると、その金属薄膜によって図4に示すようにソース電極膜32が形成される。

10

## 【0031】

このとき、固定電位拡散層16中に重ねて拡散されたベース拡散層19表面に窓開部を設け、窓開部底面にベース拡散層19表面を露出させておくと、固定電位拡散層16表面にも金属薄膜が形成される。図9の符号28は、その窓開部であり、固定電位拡散層16上の位置に略等間隔で複数個配置されている。

## 【0032】

その金属薄膜はソース電極膜32と分離せず、電気的に接続させておき、固定電位拡散層16を、ベース拡散層12及びソース拡散層14に電気的に接続させると、ソース電極膜32を接地電位に接続すると、固定電位拡散層16も接地電位に接続される。

20

## 【0033】

他方、ガードリング拡散層17<sub>1</sub>～17<sub>4</sub>とビパッド拡散層18は露出させず、ソース電極膜32には接続しないでおく。

## 【0034】

また、ソース電極膜32を形成するときに、ソース電極膜32を形成した金属薄膜によって、ドレイン層11上の絶縁膜44表面に大面積のゲートパッド35を形成しておく。このゲートパッド35は、絶縁膜44によって、ドレイン層11やドレイン層11内に形成された拡散層とは絶縁させおき、ゲート電極膜31にだけ接続されている。ここでは、この絶縁膜44にはシリコン酸化膜が用いられている。

30

## 【0035】

次に、ゲートパッド35表面と、ソース電極膜32に接続された図示しないソースパッド表面を露出させた状態で保護膜45を形成する。最後に、ドレイン層11の裏面に金属薄膜を形成し、その金属薄膜によってドレイン電極膜33を構成させるとMOSFET3が得られる。

## 【0036】

このMOSFET3を使用する場合、ソース電極膜32を接地させ、ドレイン電極膜33に正電圧を印加しておき、ゲート電極膜31に正電圧を印加すると、チャネル領域15表面が反転し、ドレイン電極膜33からソース電極膜32に向けて電流を流すことができる。

## 【0037】

40

その状態からゲート電極膜31に接地電圧を印加すると、チャネル領域15表面の反転層は消滅し、電流は遮断される。

## 【0038】

また、このMOSFET3において、ソース電極膜32にドレイン電極膜33よりも高い電圧が印加された場合には、ドレイン層11と、ベース拡散層12及びチャネル拡散層13で形成される寄生pnダイオードが順バイアスされ、その寄生pnダイオードを通って電流が流れる。その電流により、ドレイン層11内に少数キャリアが注入される。

## 【0039】

その状態でソース電極膜32とドレイン電極膜33の間の電圧が反転すると、注入された少数キャリアは、ソース電極膜32に接続されたベース拡散層12及びチャネル拡散層1

50

3に流れ込む。

**【0040】**

能動領域7a、7b端部では、少数キャリアは最外周に位置するベース拡散層12やチャネル拡散層15に集中しやすいが、このMOSFET3では、能動領域7a、7bの周囲は固定電位拡散層16で囲われており、固定電位拡散層16はソース電極膜32に接続されているから、少数キャリアは固定電位拡散層16に流れ込み、集中が起こらない。

**【0041】**

また、このMOSFET3では、ガードリング拡散層17<sub>1</sub>～17<sub>4</sub>及びパッド拡散層18は、ソース電極膜32、ゲート電極膜31及びドレイン電極膜33に接続されておらず、浮遊電位の状態で、固定電位拡散層16の外周に配置されているから、ソース電極膜32が接地され、ドレイン電極膜33に高電圧が印加された状態で、ベース拡散層12から伸びる空乏層が広がりやすく、降伏電圧が高くなっている。10

**【0042】**

なお、上記実施例では、固定電位拡散層16に接続されたベース拡散層19内には、ソース拡散層14は形成されていなかったが、図6のMOSFET4では、固定電位拡散層16に端部が接続されたベース拡散層7aが設けられている。そのベース拡散層19aにはチャネル拡散層13aが接続されており、該ベース拡散層19a及びチャネル拡散層13a表面にソース拡散層14aが形成されている。

**【0043】**

このソース拡散層14a端部とチャネル拡散層13a端部とでチャネル領域15が形成されており、その表面に、ゲート酸化膜21とゲート電極膜31が配置されている。このようなMOSFET4では、固定電位拡散層16に接続されたベース拡散層19aの一部が能動領域となり、MOSFETの動作に寄与するようになる。20

**【0044】**

このMOSFET4でも、能動領域7c端部の少数キャリアは固定電位拡散層16に流れ込み、集中しない。

なお、このMOSFET4において、図4に示したMOSFET3と共に部分には共通の符号を付してある。

**【0045】**

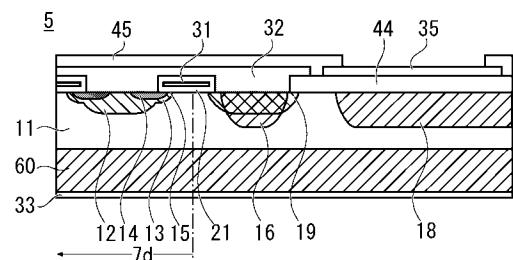

図7の符号5は、IGBTであり、図4のMOSFET3と異なる点は、p型のシリコン基板10の代わりにp型のシリコン基板60を有している点である。30

図3のMOSFET3と同じ部分には同じ符号を付して説明を省略する。

**【0046】**

このIGBT5では、n型のシリコンエピタキシャル層11はp<sup>+</sup>型のシリコン基板60上に形成されている。

**【0047】**

このIGBT5では、ガードリング拡散層の本数が増え、耐圧が向上し、また、ソース電極膜32には接地電位、ドレイン電極膜33には正電圧が印加された状態で導通した場合、p<sup>+</sup>型のシリコン基板60からドレイン層11内に少数キャリアが注入されるが、その少数キャリアのうち、能動領域7dの端部に注入された少数キャリアは固定電位拡散層16に流れ込み、集中しないと考えられる。40

**【0048】**

なお、以上の例では、固定電位拡散層を接地電位に接続したが、チップ上でソース電極と同じ電位に接続されればよい。pチャネル型のMOSFETやIGBTの場合、ドレン領域がp型シリコン単結晶であり、固定電位拡散層やガードリング拡散層はn型になる。この場合でも固定電位拡散層はソース電極と同じ電位に接続されればよい。

**【0049】**

**【発明の効果】**

能動領域周辺部分での少数キャリアの集中が無いので、破壊耐量が向上する。ゲートパッドの下方位置には、ガードリング拡散層に接続されたパッド拡散層が設けられているので50

、ゲートパッド下方で空乏層が広がりやすく、降伏電圧が高くなる。

【図面の簡単な説明】

【図1】固定電位拡散層とパッド拡散層を説明するための断面工程図

【図2】ゲート電極膜とベース拡散層とチャネル拡散層を説明するための断面工程図

【図3】ソース拡散層を説明するための断面工程図

【図4】ソース電極膜とゲートパッドを形成した後の本発明のMOSFETを説明するための断面図

【図5】固定電位拡散層とガードリング拡散層を説明するための断面工程図

【図6】本発明の他のMOSFETの例を説明するための断面図

【図7】本発明のIGBTの例を説明するための断面図

【図8】ガードリング拡散層とパッド拡散層と固定拡散層の配置を説明するための平面図

【図9】固定電位拡散層と窓開部の位置関係を説明するための図

【図10】従来技術のMOSFETを説明するための図

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(56)参考文献 特開昭61-285764(JP,A)

特開平06-291322(JP,A)

特開平03-156977(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/06

H01L 29/78