(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6014612号

(P6014612)

(45) 発行日 平成28年10月25日(2016.10.25)

(24) 登録日 平成28年9月30日(2016.9.30)

(51) Int.Cl.

F 1

H03K 17/687 (2006.01)

H03K 17/687

17/687

G

H03M 1/12 (2006.01)

H03M 1/12

1/12

A

H03K 17/693 (2006.01)

H03K 17/693

17/693

A

請求項の数 10 (全 11 頁)

(21) 出願番号 特願2013-555585 (P2013-555585)

(86) (22) 出願日 平成24年2月24日 (2012.2.24)

(65) 公表番号 特表2014-511619 (P2014-511619A)

(43) 公表日 平成26年5月15日 (2014.5.15)

(86) 国際出願番号 PCT/US2012/026430

(87) 国際公開番号 WO2012/116251

(87) 国際公開日 平成24年8月30日 (2012.8.30)

審査請求日 平成27年2月3日 (2015.2.3)

(31) 優先権主張番号 13/034,438

(32) 優先日 平成23年2月24日 (2011.2.24)

(33) 優先権主張国 米国(US)

(73) 特許権者 390020248

日本テキサス・インスツルメンツ株式会社

東京都新宿区西新宿六丁目24番1号

(73) 特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

-5474 ダラス メイル ステイショ

ン 3999 ピーオーボックス 655

474

(74) 上記1名の代理人 100098497

弁理士 片寄 恒三

最終頁に続く

(54) 【発明の名称】高速、高電圧マルチブレクサ

## (57) 【特許請求の範囲】

## 【請求項1】

装置であって、

負の電圧レールと、

正の電圧レールと、

複数のマルチブレクサセルであって、各マルチブレクサセルが複数の選択信号の少なくとも1つにより制御され、制御信号がディアサートされるときに各マルチブレクサセルが不活性化され、各マルチブレクサセルが、

入力端子と、

出力端子と、

前記負の電圧レールに結合されるスイッチネットワークと、

前記入力端子と前記出力端子と前記スイッチネットワークとに結合されるブーストされたスイッチと、

を含む、前記複数のマルチブレクサセルと、

前記マルチブレクサセルの各自の前記出力端子と各マルチブレクサセルの前記スイッチネットワークと前記正の電圧レールとに結合され、前記制御信号により制御されるブースト回路と、

を含み、

前記ブースト回路が、

前記正の電圧レールに及び各マルチブレクサセルの前記スイッチネットワークに結合さ

10

20

れる第1のスイッチであって、前記制御信号がアサートされるときに活性化される前記第1のスイッチと、

接地に及び各マルチプレクサセルの前記出力端子に結合される第2のスイッチであって、前記制御信号がアサートされるときに活性化される前記第2のスイッチと、

前記第1及び第2のスイッチ間に結合されるキャパシタと、

を更に含み、

各ブーストされたスイッチが、そのソースで前記入力端子に、そのドレインで前記出力端子に、及びそのゲートで前記スイッチネットワークに結合されるN M O Sトランジスタを更に含み、

各スイッチネットワークが、

10

前記N M O Sトランジスタの前記ソースに結合される第3のスイッチと、

前記第3のスイッチと前記出力端子との間に結合される第4のスイッチと、

前記第3及び第4のスイッチ間のノードに及び接地に結合される第5のスイッチと、

前記負の電圧レールと前記N M O Sトランジスタの前記ゲートとの間に結合される第6のスイッチと、

前記第1のスイッチと前記N M O Sトランジスタの前記ゲートとの間に結合される第7のスイッチと、

を更に含む、装置。

#### 【請求項2】

請求項1に記載の装置であって、

20

前記装置の入力範囲が、+/-12V、+/-10V、+/-5V、0V~10V、及び0V~5Vである、装置。

#### 【請求項3】

請求項1に記載の装置であって、

前記負の電圧レールが約-15Vの電圧を有する、装置。

#### 【請求項4】

装置であって、

負の電圧レールと、

正の電圧レールと、

複数のマルチプレクサセルを有するマルチプレクサであって、各マルチプレクサセルが選択信号複数のセットの少なくとも1つにより制御され、各マルチプレクサセルが、

30

入力端子と、

出力端子と、

前記負の電圧レールに結合されるスイッチネットワークと、

前記入力端子と前記出力端子と前記スイッチネットワークとに結合されるブーストされたスイッチと、

を含む、前記複数のマルチプレクサセルと、

前記マルチプレクサセルの各々の前記出力端子と各マルチプレクサセルの前記スイッチネットワークと前記正の電圧レールとに結合されるブースト回路であって、制御信号により制御される、前記ブースト回路と、

40

各マルチプレクサセルの前記出力端子に結合されるアナログデジタルコンバータ(ADC)であって、サンプリング位相の間に前記マルチプレクサからの出力信号をサンプリングし、変換位相の間に変換を実行し、変換位相の間に各マルチプレクサセルが不活性化される、前記ADCと、

を含み、

前記ブースト回路が、

前記正の電圧レールに及び各マルチプレクサセルの前記スイッチネットワークに結合される第1のスイッチと、

接地に及び各マルチプレクサセルの前記出力端子に結合される第2のスイッチであって、前記サンプル位相の少なくとも一部の間に前記制御信号がアサートされるときに前記第

50

1 及び第 2 のスイッチが活性化される、前記第 2 のスイッチと、

前記第 1 及び第 2 のスイッチ間に結合されるキャパシタと、

を更に含み、

選択信号の各セットが第 1 の選択信号と第 2 の選択信号を更に含み、

各ブーストされたスイッチが、そのソースで前記入力端子に、そのドレインで前記出力

端子に、及びそのゲートで前記スイッチネットワークに結合される N M O S トランジスタ

を更に含み、

各スイッチネットワークが、

前記 N M O S トランジスタの前記ソースに結合され、前記選択信号のセットの前記第 1

の選択信号により制御される第 3 のスイッチと、

前記第 3 のスイッチと前記出力端子との間に結合され、前記選択信号のセットの前記第

1 の選択信号により制御される第 4 のスイッチと、

前記第 3 及び第 4 のスイッチ間のノードに及び接地に結合される第 5 のスイッチであつ

て、前記選択信号のセットの前記第 2 の選択信号により制御される前記第 5 のスイッチと

、

前記負の電圧レールと前記 N M O S トランジスタの前記ゲートとの間に結合される第 6

のスイッチであつて、前記選択信号のセットの前記第 2 の選択信号により制御される前記

第 6 のスイッチと、

前記第 1 のスイッチと前記 N M O S トランジスタの前記ゲートとの間に結合される第 7

のスイッチであつて、前記選択信号のセットの前記第 1 の選択信号により制御される前記

第 7 のスイッチと、

を更に含む、装置。

【請求項 5】

請求項 4 に記載の装置であつて、

前記マルチプレクサの入力範囲が、+ / - 1 2 V、+ / - 1 0 V、+ / - 5 V、0 V ~

1 0 V、及び 0 V ~ 5 V である、装置。

【請求項 6】

請求項 4 に記載の装置であつて、

前記負の電圧レールが約 - 1 5 V の電圧を有する、装置。

【請求項 7】

請求項 4 に記載の装置であつて、

前記第 1 、第 2 、第 3 、第 4 、第 5 、第 6 及び第 7 のスイッチが C M O S スイッチであ

る、装置。

【請求項 8】

請求項 4 に記載の装置であつて、

前記変換位相の間に前記複数の選択信号のセットの各々をディアサートするブーストロ

ジックを更に含む、装置。

【請求項 9】

複数のチャネルを有するマルチプレクサを用いることにより、複数のアナログ入力信号

の選択されたアナログ入力信号の少なくとも一部をデジタル化するための方法であつて、

各チャネルが前記アナログ入力信号の少なくとも 1 つに関連付けられ、各チャネルが一対

の選択信号に関連付けられ、各チャネルが、入力端子と出力端子とブーストされた N M O

S スイッチとを有するセルを含み、

前記方法が、

各セルに対する前記入力端子及び出力端子を分離するために選択信号の各対から第 1 の

選択信号をアサートする工程と、

選択信号の各対から前記第 1 の選択信号がアサートされる間にサンプル位相の初期部分

中にブーストキャパシタを充電する工程と、

前記選択されたアナログ入力信号に関連付けられる前記セルに対する前記入力端子及び

出力端子を共に結合するように、関連付けられたブーストされた N M O S スイッチに前記

10

20

30

40

50

ブーストキャパシタにストアされた電圧を提供するように、前記選択されたアナログ入力信号に関連付けられる第2の選択信号をアサートする工程と、

前記選択されたアナログ入力信号の前記部分をデジタル化する工程と、

を含む、方法。

【請求項 10】

請求項9に記載の方法であって、

前記第1の選択信号をアサートする工程が、各セルにおける前記入力端子と出力端子との間のノードを接地するように各セルにおける前記ノードに結合されるスイッチを活性化することを更に含む、方法。

【発明の詳細な説明】

10

【技術分野】

【0001】

本願は、概してマルチプレクサに関し、更に特定して言えば、概してアナログデジタルコンバータ(ADC)と共に用いられる、高速、高電圧マルチプレクサに関連する。

【背景技術】

【0002】

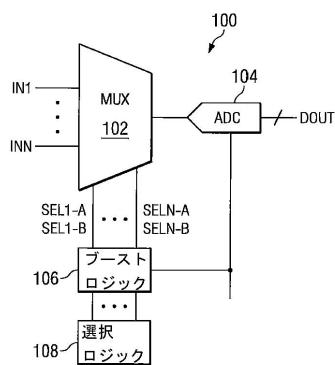

図1及び図2は従来のマルチチャネルデータコンバータシステム100を示す。システム100は、マルチプレクサ(MUX)102、例えば250kサンプル数毎秒(SPS)で動作する逐次比較レジスタ(SAR)アナログデジタルコンバータ(ADC)であり得る、ADC104、ブーストロジック106、及び選択ロジック108を概して含む。

20

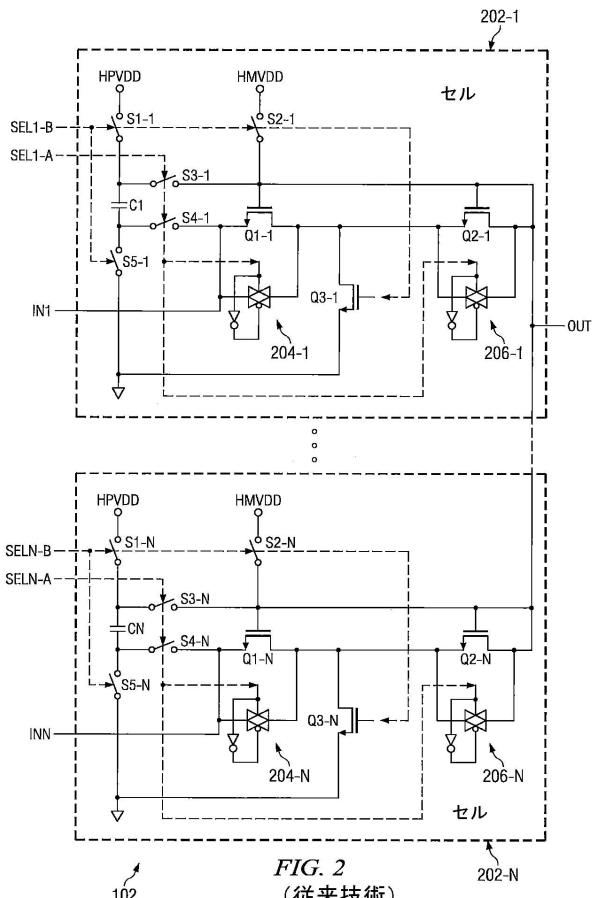

典型的に、MUX102は、幾つかのアナログ入力信号IN1～INNを受け取り、ADC104に、ADC104によって変換された多重化されたアナログ信号をデジタル出力信号DO OUTに提供するようにする。ブーストロジック106及び選択ロジック108は概して、サンプル信号SAMPLEに基づいて(選択信号SEL1～SELNを用いて)アナログ入力信号IN1～INNのインターリーブを実行する。MUX102(これは、図2において更に詳細に見ることができる)は概して、セル202-1～202-N(各々がMUX102のチャネルに対応する)で構成される。各セル202-1～202-Nは概して及びそれぞれ、スイッチS1-1～S5-1からS1-N～S5-N、キャパシタC1～CN、トランジスタQ1-1～Q3-1からQ1-N～Q3-N(これらは各々概してNMOSトランジスタである)、及び伝送ゲート204-1/206-1～204-N/206-Nを含む。

30

【0003】

MUX102(図2に更に詳細に示す)のオペレーションは概してサンプル信号SAMPLEの位相に依存する。まず、キャパシタC1～CNが、選択信号SEL1-A～SELN-Aをディアサートすること及び選択信号SEL1-B～SELN-Bをアサートすることにより、正のレールHPVDD上の電圧まで充電される。キャパシタC1～CNの充電後及び一例として、チャネル1(セル202-1)が選択されると仮定する場合、選択信号SEL1-Aがアサートされ、一方、SEL1-B(及びSEL2-A/SEL2-B～SELN-A/SELN-B)がディアサートされる。これにより、サンプリング時点の入力信号IN1からの電圧に加えてキャパシタC1にストアされた電圧(即ち、+15V)が、スイッチQ1-1及びQ2-1のゲートにまず印加され得る。ブーストされた電圧が印加されると、サンプリング時点の入力信号のIN1電圧が、スイッチQ1-1及び伝送ゲート204-1を介してスイッチQ2-1及び伝送ゲート206-1(これらは概してスイッチQ1-1及び伝送ゲート204-1と同じ機能を実行する)へ伝送される。スイッチQ2-1/Q3-1～Q2-N/Q3-N及び伝送ゲート206-1は、これらの構成要素が概して入力及び出力間の寄生容量をなくすため、概してクロストークを低減するように提供される。

40

【0004】

セル202-1～202-Nは概して、(部分的に、スイッチQ3-1～Q3-Nを介して提供される接地のため)クロストークを低減する一方で、幾つか欠点がある。即ち、

50

スイッチQ2-1～Q2-Nの反復は問題となり得る。スイッチQ1-1/Q2-1～Q1-N/Q2-Nは、高周波数オペレーションでの入力抵抗を低減するために大きいため、これらのスイッチは、かなりの量のエリアを占める。また、直列スイッチQ1-1/Q2-1～Q1-N/Q2-Nは、A D C 1 0 4の動作速度を制限する。従って、改良されたM U Xが必要とされている。

#### 【0005】

従来の回路の幾つかの例は、下記文献に記載されている。

【特許文献1】米国特許番号第6,404,237号

【特許文献2】米国特許番号第7,064,599号

【特許文献3】米国特許番号第7,268,610号

10

【特許文献4】米国特許番号第7,471,135号

【特許文献5】米国特許公開番号2002/0175740

#### 【発明の概要】

#### 【0006】

例示の一実施例は或る装置を提供する。この装置は、負の電圧レール、正の電圧レール、複数のマルチプレクサセル、及びマルチプレクサセルの各々の出力端子と、各マルチプレクサセルのスイッチネットワークと、正の電圧レールとに結合されるブースト回路を含む。各マルチプレクサセルは複数の選択信号の少なくとも1つにより制御され、制御信号がディアサートされるとき各マルチプレクサセルが不活性化される。各マルチプレクサセルは、入力端子、出力端子、負の電圧レールに結合されるスイッチネットワーク、及び、入力端子と出力端子とスイッチネットワークとに結合されるブーストされたスイッチを含む。ブースト回路は制御信号により制御される。

20

#### 【0007】

例示の一実施例において、ブースト回路は、正の電圧レールに及び各マルチプレクサセルのスイッチネットワークに結合される第1のスイッチであって、制御信号がアサートされるとき活性化される第1のスイッチと、接地に及び各マルチプレクサセルの出力端子に結合される第2のスイッチであって、制御信号がアサートされるとき活性化される第2のスイッチと、第1及び第2のスイッチ間に結合されるキャパシタとを更に含む。

#### 【0008】

例示の一実施例において、各ブーストされたスイッチが、そのソースでその入力端子に、そのドレインでその出力端子に、及びそのゲートでそのスイッチネットワークに結合されるN M O Sトランジスタを更に含む。

30

#### 【0009】

例示の一実施例において、各スイッチネットワークが、そのN M O Sトランジスタのソースに結合される第3のスイッチ、第3のスイッチとその出力端子との間に結合される第4のスイッチ、第3及び第4のスイッチ間のノードに及び接地に結合される第5のスイッチ、負の電圧レールとそのN M O Sトランジスタのゲートとの間に結合される第6のスイッチ、及び第1のスイッチとそのN M O Sトランジスタのゲートとの間に結合される第7のスイッチを更に含む。

#### 【0010】

40

例示の一実施例において、装置の入力範囲が、+/-12V、+/-10V、+/-5V、0V～10V、及び0V～5Vである。

#### 【0011】

例示の一実施例において、負の電圧レールは約-15Vの電圧を有する。

#### 【0012】

例示の一実施例において、各マルチプレクサセルが、その出力端子とブースト回路との間に結合される伝送ゲートを更に含む。

#### 【0013】

例示の一実施例において或る装置が提供される。この装置は、負の電圧レール、正の電圧レール、複数のマルチプレクサセルを有するマルチプレクサ、及び各マルチプレクサセ

50

ルの出力端子に結合されるアナログデジタルコンバータ（A D C）を含む。各マルチブレクサセルは選択信号複数のセットの少なくとも1つにより制御される。各マルチブレクサセルは、入力端子、出力端子、負の電圧レールに結合されるスイッチネットワーク、入力端子と出力端子とスイッチネットワークとに結合されるブーストされたスイッチ、及び、マルチブレクサセルの各々の出力端子と、各マルチブレクサセルのスイッチネットワークと、正の電圧レールとに結合され、制御信号により制御されるブースト回路を含む。A D Cは、サンプリング位相の間マルチブレクサからの出力信号をサンプリングし、変換位相の間変換を実行し、変換位相の間各マルチブレクサセルが不活性化される。

【0014】

例示の一実施例において、ブースト回路が、正の電圧レールに及び各マルチブレクサセルのスイッチネットワーク結合される第1のスイッチと、接地に及び各マルチブレクサセルの出力端子に結合される第2のスイッチと、第1及び第2のスイッチ間に結合されるキヤパシタとを更に含む。サンプル位相の少なくとも一部の間制御信号がアサートされるとき第1及び第2のスイッチが活性化される。

10

【0015】

例示の一実施例において、選択信号の各セットが、第1の選択信号及び第2の選択信号を更に含む。

【0016】

例示の一実施例において、各ブーストされたスイッチが、そのソースでその入力端子に、そのドレインでその出力端子に、及びそのゲートでそのスイッチネットワークに結合されるN M O Sトランジスタを更に含む。

20

【0017】

例示の一実施例において、各スイッチネットワークが、そのN M O Sトランジスタのソースに結合され、選択信号のそのセットの第1の選択信号により制御される第3のスイッチ、第3のスイッチとその出力端子との間に結合され、選択信号のそのセットの第1の選択信号により制御される第4のスイッチ、第3及び第4のスイッチ間のノードに及び接地に結合される第5のスイッチであって、選択信号のそのセットの第2の選択信号により制御される第5のスイッチ、負の電圧レールとそのN M O Sトランジスタのゲートとの間に結合される第6のスイッチであって、選択信号のそのセットの第2の選択信号により制御される第6のスイッチ、及び第1のスイッチとそのN M O Sトランジスタのゲートとの間に結合される第7のスイッチであって、選択信号のそのセットの第1の選択信号により制御される第7のスイッチを更に含む。

30

【0018】

例示の一実施例において、第1、第3、第3、第4、第5、第6、及び第7のスイッチがC M O Sスイッチである。

【0019】

例示の一実施例において、この装置は、変換位相の間、複数のセットの各々の選択信号をディアサートするブーストロジックを更に含む。

【0020】

例示の一実施例において、複数のチャネルを有するマルチブレクサを用いることにより、複数のアナログ入力信号の選択されたアナログ入力信号の少なくとも一部をデジタル化するための方法が提供される。各チャネルがアナログ入力信号の少なくとも1つに関連付けられ、各チャネルが一対の選択信号に関連付けられ、各チャネルが、入力端子と、出力端子と、ブーストされたN M O Sスイッチとを有するセルを含む。この方法は、各セルに対する入力端子及び出力端子を分離するため選択信号の各対から第1の選択信号をアサートすること、選択信号の各対から第1の選択信号がアサートされる一方で、サンプル位相の初期部分の間ブーストキャパシタを充電すること、選択されたアナログ入力信号に関連付けられるセルに対する入力端子及び出力端子を共に結合するように、及びブーストキャパシタにストアされた電圧を、関連付けられたブーストされたN M O Sスイッチに提供するように、選択されたアナログ入力信号に関連付けられる第2の選択信号をアサートする

40

50

こと、及び選択されたアナログ入力信号の前記部分をデジタル化することを含む。

【0021】

例示の一実施例において、第1の選択信号をアサートする工程が、各セルにおけるノードを接地するように各セルにおける入力端子と出力端子との間のノードに結合されるスイッチを活性化することを更に含む。

【図面の簡単な説明】

【0022】

例示の実施例を添付の図面を参照して説明する。

【0023】

【図1】図1は従来のシステムの例を示す。

10

【0024】

【図2】図2は図1のマルチプレクサ(MUX)の例を示す。

【0025】

【図3】図3は例示のシステムを示す。

【0026】

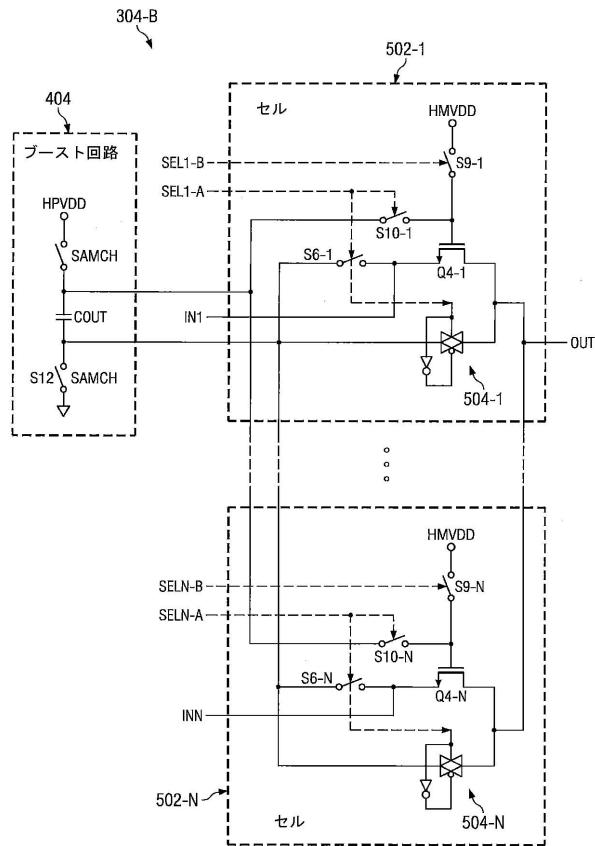

【図4】図4は、図3のMUXの例を示す。

【図5】図5は、図3のMUXの例を示す。

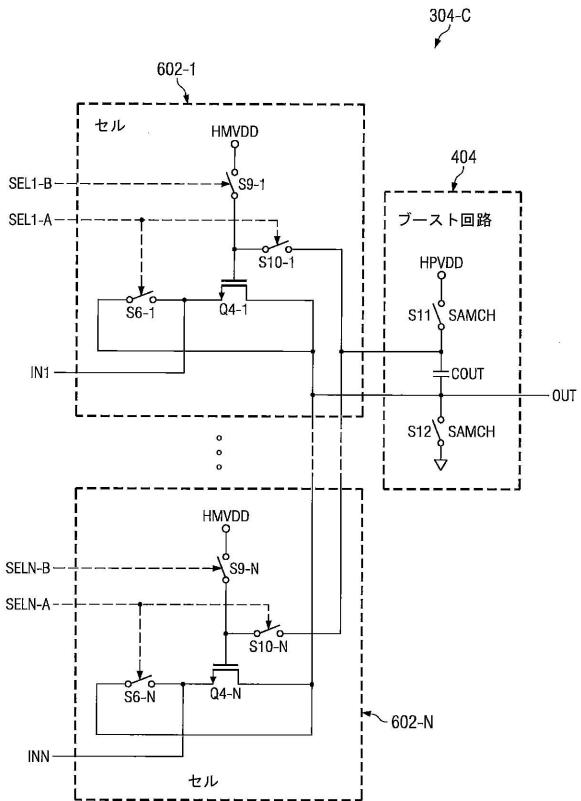

【図6】図6は、図3のMUXの例を示す。

【発明を実施するための形態】

【0027】

20

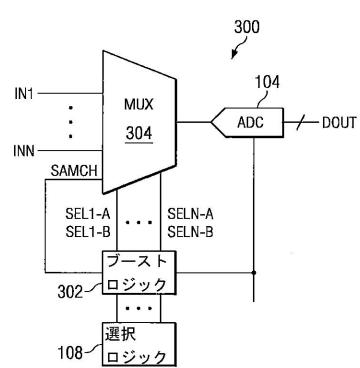

図3はシステム300の例を示す。システム300は概して、+/-12V、+/-10V、+/-5V、0V~10V、及び0V~5Vの入力範囲を有し、システム300において、マルチプレクサ(MUX)304及びブーストロジック302は概して、システム100のMUX102及びブーストロジック106を置き換える。MUX102と同様、MUX304(その例を図4~図6において更に詳細に見ることができ、これらは、それぞれ、304-A、304-B、及び304-Cで示す)は概して、セル402-1~402-N、501-1~502-N、又は602-1~602-Nで構成されるが、MUX304-A、304-B、及び304-Cの各々が、ブースト回路404(図4)を更に含む。このブースト回路404は、ブーストキャパシタ(これらはセル202-1~202-Nの各々に提供されていた)の数を低減することができる。

30

【0028】

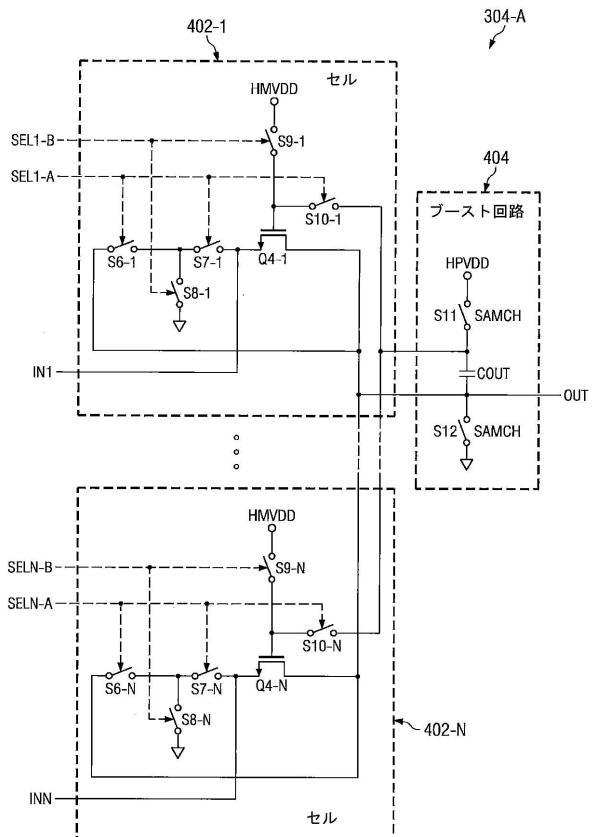

図4に示すMUX304-Aの実装において、セル402-1~402-Nは概して、スイッチS6-1~S10-1からS6-N~S10-N(これらはCMOSスイッチであり得る)及びブーストされたスイッチQ4-1~Q4-N(これらはNMOSトランジスタであり得る)を含む。ブースト回路404は、スイッチS11及びS12(これらはCMOSスイッチであり得る)及びブーストキャパシタCOUTを概して含み、サンプル充電信号SAMCH(これは、概してブーストロジック302によって提供され、概して非サンプリング位相又は変換位相の間生じる)により制御される。(例えば)セル402-1に関連付けられるチャネルが選択されると仮定すると、その入力信号IN1が、サンプルクロック信号SAMPLEのサンプリング位相の間、ADC104に伝送され得る。この例では非サンプリング又は変換位相の間、選択信号SEL1-B~SELN-Bがアサートされ、一方、選択信号SEL1-A~SELN-Aがディアサートされる。これは、スイッチS8-1~S8-Nを作動させて各セル402-1~402-Nに対する入力と出力間のノードを接地させ、スイッチS9-1~S9-Nを作動させて(概してスイッチQ4-1~Q4-Nを確実に「オフ」にするため)スイッチQ4-1~Q4-Nのゲートを負の電圧レールHMVDDに結合する。また、スイッチS11及びS12はサンプル充電信号SAMCH(これは、概してブーストロジック302によって提供される)により作動されて、ブーストキャパシタCOUTを正の電圧レールHPVDD上の電圧(即ち、+15V)まで充電させる。ブーストキャパシタCOUTが充電されると、サンプル充電信号SAMCHがスイッチS11及びS12を不活性化し、一方、(この例では)選択

40

50

信号 S E L 1 - A がアサートされ、選択信号 S E L 1 - B ~ S E L N - B がディアサートされる。選択信号 S E L 1 - A のアサートは、スイッチ S 6 - 1、S 7 - 1、及び S 1 0 - 1 を作動させて、セル 4 0 2 - 1 の出力及び入力端子がスイッチ S 7 - 1 及び S 6 - 1 を介して共に結合されるようにする。また、ブーストキャパシタ C O U T の頂部プレートが、スイッチ Q 4 - 1 のゲートに結合されて、サンプリング時点の入力信号 I N 1 からの電圧に加えてキャパシタ C 1 にストアされた電圧（即ち、+ 1 5 V）が、スイッチ Q 4 - 1 のゲートに印加され得る。そのため、サンプリング時点の入力信号 I N 1 からの電圧は、M U X 3 0 4 の出力信号 O U T として A D C 1 0 4 に提供され得る。その後、変換位相の間、選択信号 S E L 1 - A / S E L 1 - B ~ S E L N - A / S E L N - B がディアサートされる。選択ロジック 1 0 8 により選択される場合、この同じプロセスが、その後セル 4 0 2 - 2 ~ 4 0 2 - 4 の各々に対し適用され得る。

10

#### 【 0 0 2 9 】

M U X 3 0 4 は、図示するように、M U X 1 0 2 と同じ利点の多くを提供することができるが、同じ欠点は有さない。M U X 3 0 4 において、チャネル毎又はセル毎（即ち、4 0 2 - 1）スイッチ（即ち、Q 4 - 1）の数が低減され、これはM U X 1 0 2 に対し M U X 3 0 4 によって占められるエリアを低減し、A D C 1 0 4 の速度を制限しない。また、スイッチ S 8 - 1 ~ S 8 - N が、変換位相の間及びサンプル位相の間（選択されないチャネル又はセルに対し）、各セル 4 0 2 - 1 ~ 4 0 2 - N の入力端子と出力端子との間のノードを接地するため、クロストークが低減される。また、ブースト回路 4 0 4 が用いられるため、ブーストキャパシタ（これは典型的に、かなりの量のエリアを占める）の数が低減され得る。

20

#### 【 0 0 3 0 】

図 5 は、M U X 3 0 4 - A と同様の方式で動作する M U X 3 0 4 - B の別の実装を示す。M U X 3 0 4 - A と 3 0 4 - B の間の差は概して、スイッチ S 7 - 1 ~ S 7 - N 及び S 8 - 1 ~ S 8 - N がなくっている点、及び伝送ゲート 5 0 4 - 1 ~ 5 0 4 - N が含まれている点で、セル 5 0 2 - 1 ~ 5 0 2 - N の構成にある。この構成において、ブーストキャパシタ C O U T の底部プレートが、セル（M U X 3 0 4 - A など）の各々の出力端子の代わりに、（「離れた」端子で）伝送ゲート 5 0 4 - 1 ~ 5 0 4 - N の各々に結合される。これは概して、M U X 1 0 2 に較べて低い周波数でのクロストークを低減する。また、伝送ゲート 5 0 4 - 1 ~ 5 0 4 - N は、一層小さくされ、寄生容量を低減し、セトリング時間が改善されるように、低減された抵抗を有する並列であると考えることができる。

30

#### 【 0 0 3 1 】

図 6 は、M U X 3 0 4 - A と同様の方式で動作する M U X 3 0 4 - C の別の実装を示す。M U X 3 0 4 - B と同様、M U X 3 0 4 - A と 3 0 4 - C との間の差は概して、スイッチ S 7 - 1 ~ S 7 - N 及び S 8 - 1 ~ S 8 - N の点で、セル 6 0 2 - 1 ~ 6 0 2 - N の構成にある。M U X 3 0 4 - C は、伝送ゲート 5 0 4 - 1 ~ 5 0 4 - N がなくなる（エリアが低減される）点で M U X 3 0 4 - B より利点を有する。しかし、M U X 3 0 4 - C は、M U X 3 0 4 - A がするように、サンプリングの間（及び変換中の全てのセル）、各選択されていないセルの入力端子と出力端子との間のノードを接地に結合することなく、そのため、クロストークの点で M U X 3 0 4 - A に対し M U X 3 0 4 - C に性能欠点がある。しかし、M U X 3 0 4 - C は、M U X 3 0 4 - A より小さなエリアを占める（これは、幾つかの応用例において好ましい可能性がある）。

40

#### 【 0 0 3 2 】

当業者であれば、本発明の特許請求の範囲内で、説明した例示の実施例に変形が成され得ること、及び多くの他の実施例が可能であることが分かるであろう。

【図1】

FIG. 1 (従来技術)

【図2】

FIG. 2 (従来技術)

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

【図6】

FIG. 5

FIG. 6

---

フロントページの続き

(72)発明者 シャンカール ティルナッカラス

アメリカ合衆国 85711 アリゾナ州 トゥーソン 13304, イー ウィリアムズ サークル 5400

(72)発明者 ロバート イー シーモア

アメリカ合衆国 85711 アリゾナ州 トゥーソン, エス カレ ド マドリッド 120

審査官 栗栖 正和

(56)参考文献 米国特許出願公開第2011/0304492(US, A1)

米国特許第07064599(US, B1)

特開2006-332838(JP, A)

特開2005-117619(JP, A)

特開平06-216733(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03K 17/687

H03K 17/693

H03M 1/12