(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5442871号

(P5442871)

(45) 発行日 平成26年3月12日(2014.3.12)

(24) 登録日 平成25年12月27日(2013.12.27)

(51) Int.Cl.

F 1

H01L 21/336 (2006.01)

H01L 29/78 (2006.01)H01L 29/78 301G

H01L 29/78 301F

請求項の数 14 (全 21 頁)

(21) 出願番号 特願2012-531562 (P2012-531562)

(86) (22) 出願日 平成22年10月2日 (2010.10.2)

(65) 公表番号 特表2013-506986 (P2013-506986A)

(43) 公表日 平成25年2月28日 (2013.2.28)

(86) 國際出願番号 PCT/JP2010/005926

(87) 國際公開番号 WO2011/040047

(87) 國際公開日 平成23年4月7日 (2011.4.7)

審査請求日 平成24年8月13日 (2012.8.13)

(31) 優先権主張番号 12/573,138

(32) 優先日 平成21年10月4日 (2009.10.4)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 000219967

東京エレクトロン株式会社

東京都港区赤坂五丁目3番1号

(74) 代理人 100088155

弁理士 長谷川 芳樹

(74) 代理人 100113435

弁理士 黒木 義樹

(74) 代理人 100122507

弁理士 柏岡 潤二

(72) 発明者 佐々木 勝

兵庫県尼崎市扶桑町1-8 東京エレクトロン技術研究所株式会社内

審査官 岩本 勉

最終頁に続く

(54) 【発明の名称】半導体デバイスの製造方法および半導体デバイスの製造装置

## (57) 【特許請求の範囲】

## 【請求項1】

基板の表面にゲート絶縁膜を介したゲート電極を形成し、

前記ゲート電極の側面に絶縁膜を形成し、該絶縁膜を形成するときに、フルオロカーボンを含む堆積物が発生し、

前記基板の前記表面を酸素プラズマに曝して前記堆積物を除去し、当該酸素プラズマの前記基板の前記表面の近傍の電子温度が約1.5eV以下であり、

前記酸素プラズマは、100mtorr以上200mtorr以下の圧力で励起される

、

半導体デバイスの製造方法。

10

## 【請求項2】

前記絶縁膜は、オフセットスペーサである、請求項1に記載の半導体デバイスの製造方法。

## 【請求項3】

前記オフセットスペーサ上にサイドウォールスペーサが形成される、請求項2に記載の半導体デバイスの製造方法。

## 【請求項4】

前記絶縁膜は、サイドウォールスペーサである、請求項1に記載の半導体デバイスの製造方法。

## 【請求項5】

20

前記酸素プラズマに曝することは、ラジアルラインスロットアンテナを用いたマイクロ表面波プラズマを用いることによって行われる、請求項1に記載の半導体デバイスの製造方法。

【請求項6】

少なくとも1つのオフセットスペーサとサイドウォールスペーサがプロセスチャンバー内で形成され、前記酸素プラズマは当該プロセスチャンバー内で励起される、請求項1に記載の半導体デバイスの製造方法。

【請求項7】

前記酸素プラズマは、シリコンからなる前記基板の前記表面に励起される、請求項1に記載の半導体デバイスの製造方法。

10

【請求項8】

前記酸素プラズマの電子温度は、前記基板の前記表面から約20mm離れたところで、約1.0eVから1.5eVである、請求項1に記載の半導体デバイスの製造方法。

【請求項9】

前記酸素プラズマの電子温度は、前記基板の前記表面から約20mm離れたところで、約1.0eVから1.2eVである、請求項8に記載の半導体デバイスの製造方法。

【請求項10】

前記基板は、サセプター上に配置され、該サセプターの温度が酸素プラズマ励起時に約20度から30度である、請求項1に記載の半導体デバイスの製造方法。

【請求項11】

プラズマを生成するためのマイクロ波出力が、約2000Wから3000Wである、請求項1に記載の半導体デバイスの製造方法。

20

【請求項12】

ゲート電極を基板表面上にゲート絶縁膜を介して形成するユニットと、

ゲート電極の側面に絶縁膜を形成するユニットと、

前記基板表面を酸素プラズマに曝して、前記絶縁膜を形成するときに発生するフルオロカーボンを含む堆積物を除去するユニットであり、当該酸素プラズマを100mto r r以上200mto r r以下の圧力で励起させ、当該酸素プラズマの前記基板の前記表面の近傍の電子温度を約1.5eV以下とする、該ユニットと、

を備える、半導体デバイスの製造装置。

30

【請求項13】

前記ゲート電極が、該ゲート電極の前記側面上に前記絶縁膜を形成するよう、炭素原子及びフッ素原子を含有するガスを用いたプラズマによってエッチングされる、請求項1に記載の半導体デバイスの製造方法。

【請求項14】

前記基板の前記表面を前記酸素プラズマに曝すことによって、該基板の該表面に、約1nmより小さい膜厚を有する酸化部分が形成される、請求項1に記載の半導体デバイスの製造方法。

【発明の詳細な説明】

【技術分野】

40

【0001】

本発明は半導体デバイスと、半導体デバイスの製造方法と、半導体デバイスの製造装置とに関する。

【背景技術】

【0002】

日本特許出願公開第10-22382号において、半導体デバイスの製造方法についての開示がある。この方法において、半導体基板上に金属配線が形成される。その後、プラズマTEOS膜を半導体基板上に形成して、金属配線を被覆する。有機SOG膜をプラズマTEOS膜上に形成した後、有機SOG膜をエッチバックする。このエッチング時において、材料Xを有機SOG膜およびプラズマTEOS膜上に堆積させる。堆積された材料

50

Xを除去するために、酸素プラズマを2.2トールだけ付加する。本明細書中、同文献の内容全体を参考のため援用する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】日本特許出願公開第10-22382号

【発明の概要】

【課題を解決するための手段】

【0004】

本発明の実施例によれば、半導体デバイスの製造方法は、ゲート絶縁膜を介して基板表面上にゲート電極を形成する工程と、ゲート電極の側面上に絶縁膜を形成する工程と、基板の表面上に酸素プラズマで曝す工程とを含む。基板の表面の近隣の酸素プラズマの電子温度は、約1.5eV以下である。絶縁膜は、オフセットスペーサ、側壁スペーサ、またはオフセットスペーサ上に形成された側壁スペーサであり得る。

10

【0005】

本発明の別の実施例によれば、半導体デバイスは、ソース領域およびドレイン領域を有する半導体基板を含む。半導体基板の表面上にゲート絶縁膜を介してゲート電極が形成される。ゲート電極の側面上に絶縁膜が形成される。ソース領域およびドレイン領域上の表面のうち一領域は、酸化部分を実質的に含まない。

20

【0006】

本発明のさらなる別の実施例によれば、半導体デバイスの製造装置は、基板の表面上にゲート絶縁膜を介してゲート電極を形成するように構成されたユニットと、ゲート電極の側面上に絶縁膜を形成するように構成されたユニットと、基板の表面上に酸素プラズマを露出させるように構成されたユニットとを含む。絶縁膜は、オフセットスペーサ、側壁スペーサ、またはオフセットスペーサ上に形成された側壁スペーサであり得る。基板の表面の近隣の酸素プラズマの電子温度は、約1.5eV以下である。

【図面の簡単な説明】

【0007】

以下の詳細な説明を添付図面と共に参照すればより深い得られる。本発明およびその付随する効果のさらなる理解が得られるであろう。

30

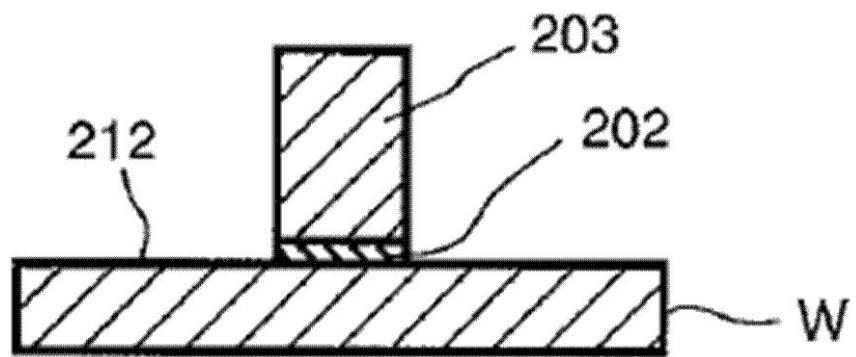

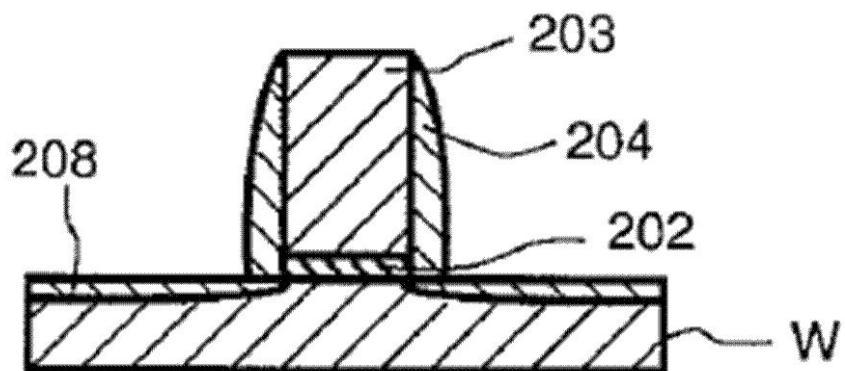

【図1A】本発明の実施形態による半導体デバイスの製造方法を説明する図である。

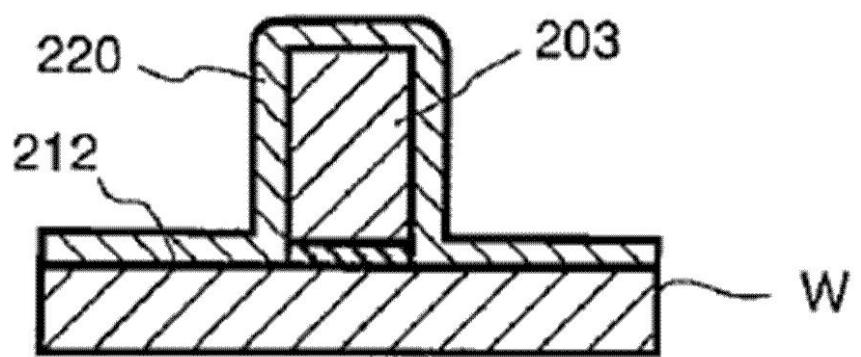

【図1B】本発明の実施形態による半導体デバイスの製造方法を説明する図である。

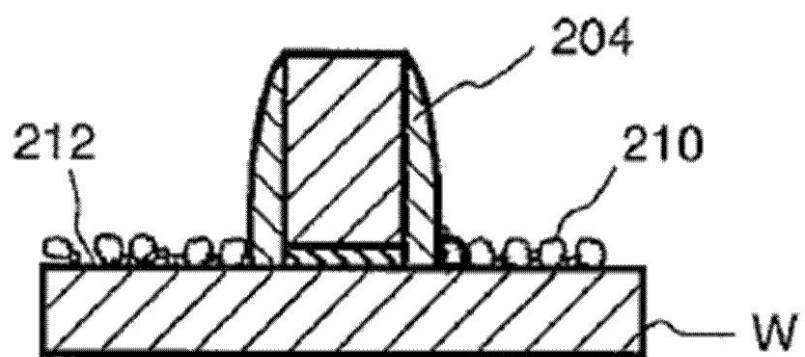

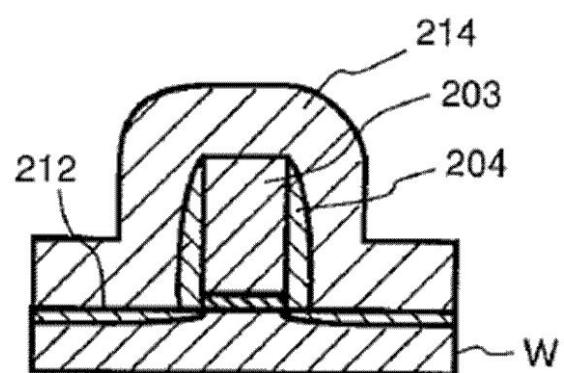

【図1C】本発明の実施形態による半導体デバイスの製造方法を説明する図である。

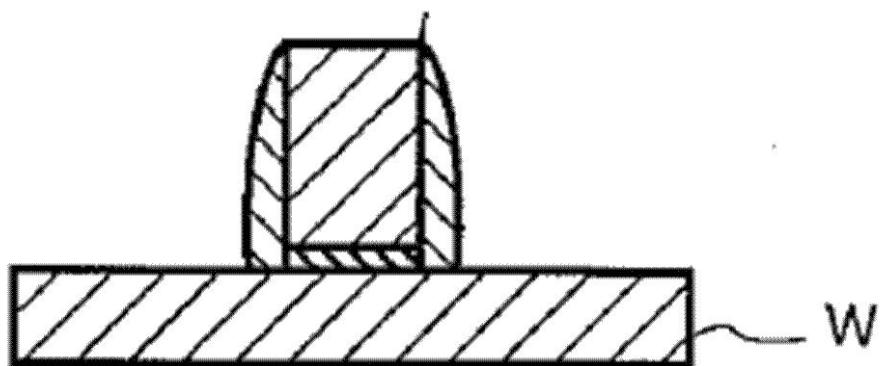

【図1D】本発明の実施形態による半導体デバイスの製造方法を説明する図である。

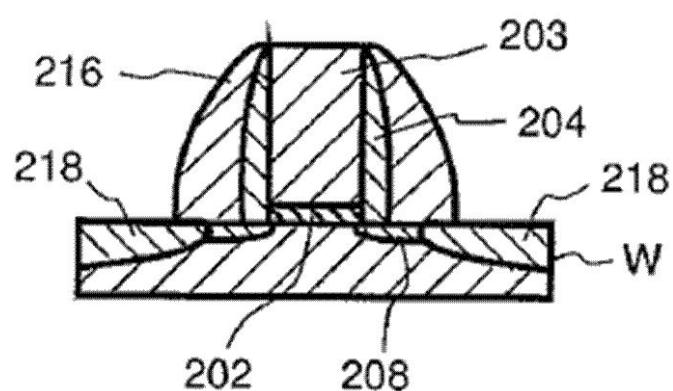

【図1E】本発明の実施形態による半導体デバイスの製造方法を説明する図である。

【図1F】本発明の実施形態による半導体デバイスの製造方法を説明する図である。

【図1G】本発明の実施形態による半導体デバイスの製造方法を説明する図である。

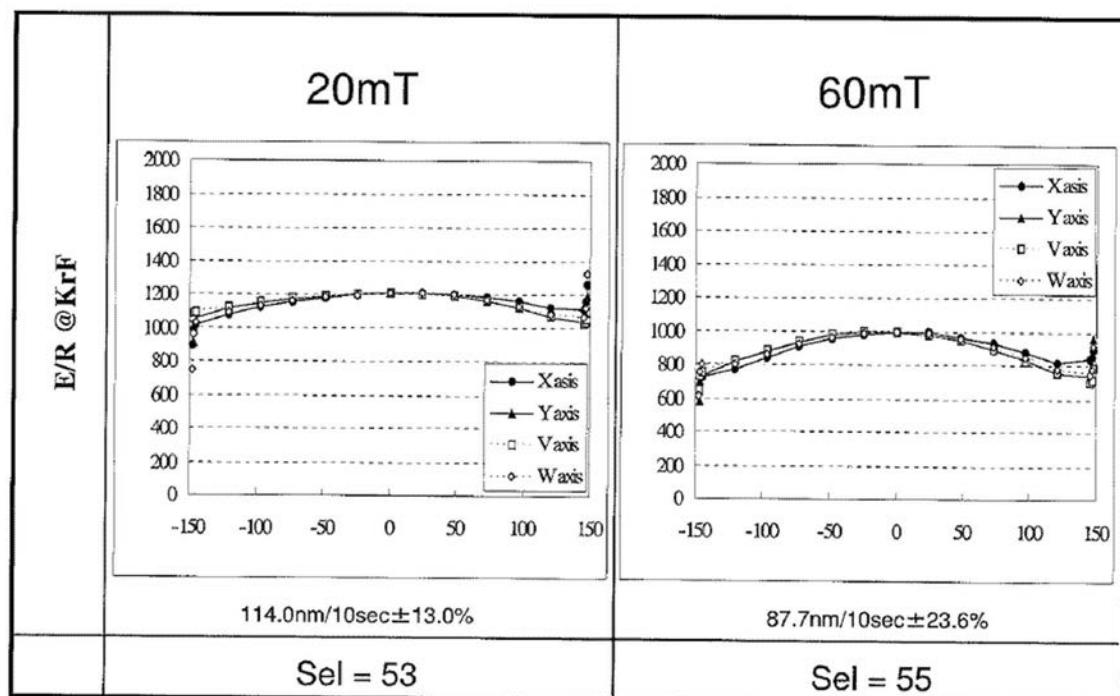

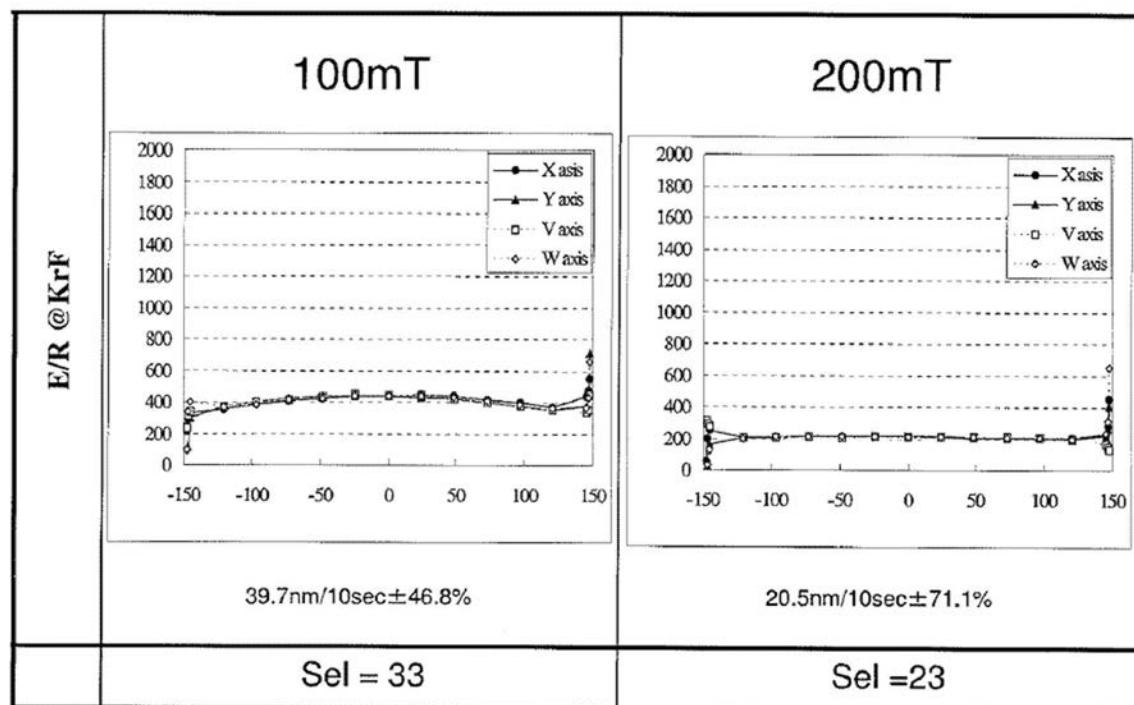

【図2A】異なる圧力下における堆積除去率を示す。

【図2B】異なる圧力下における堆積除去率を示す。

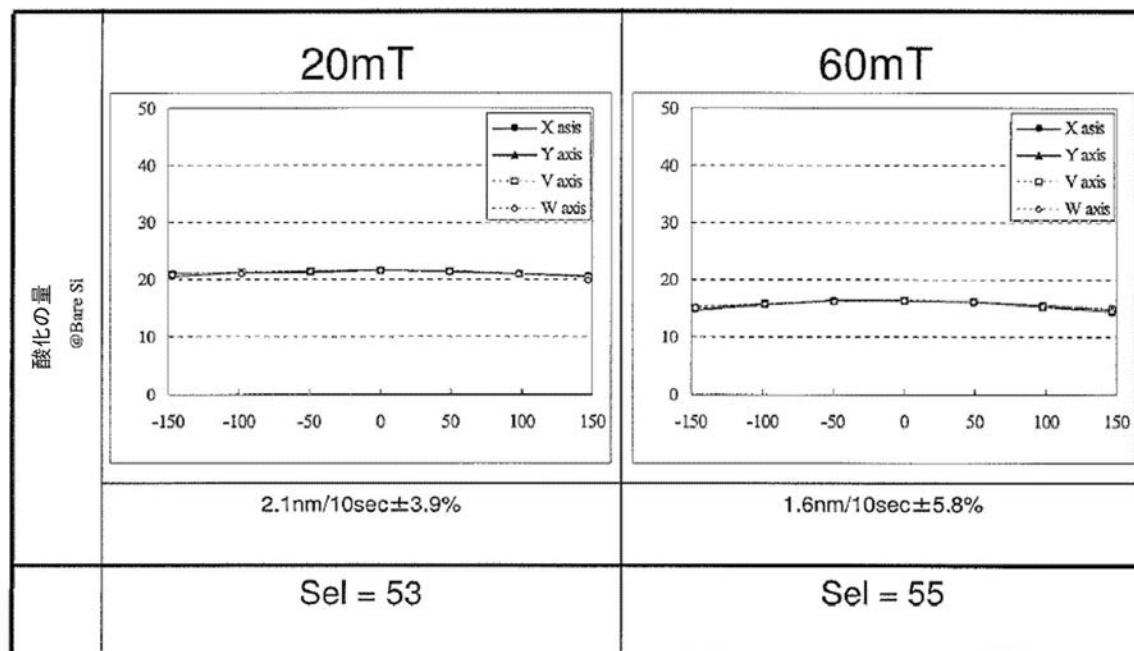

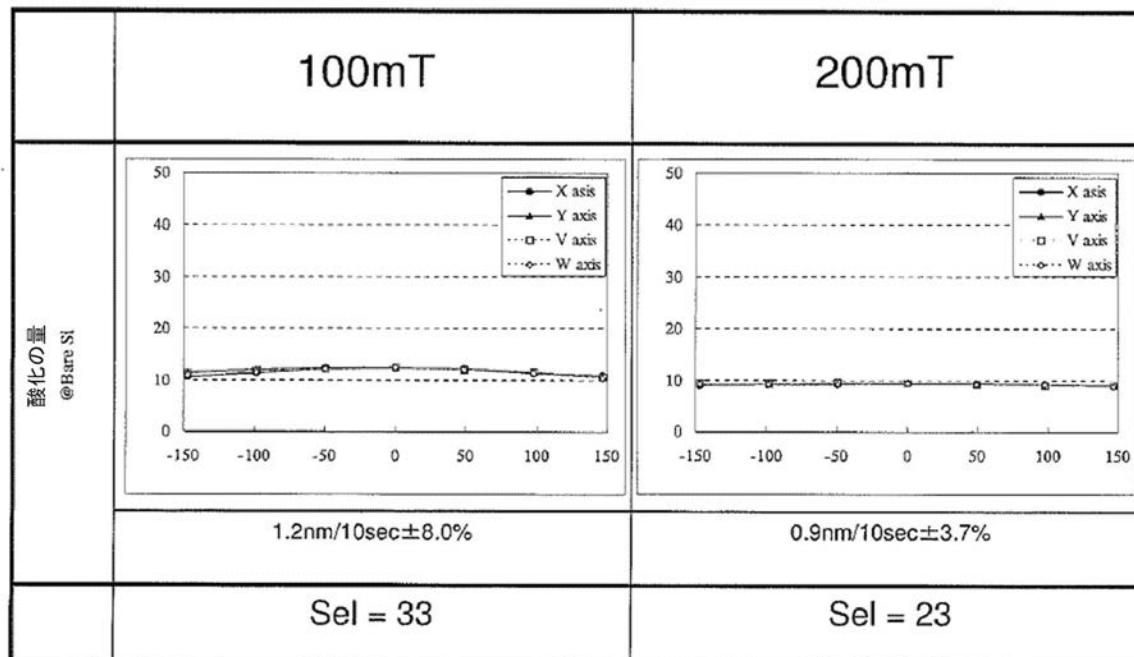

【図2C】異なる圧力下における酸化量を示す。

40

【図2D】異なる圧力下における酸化量を示す。

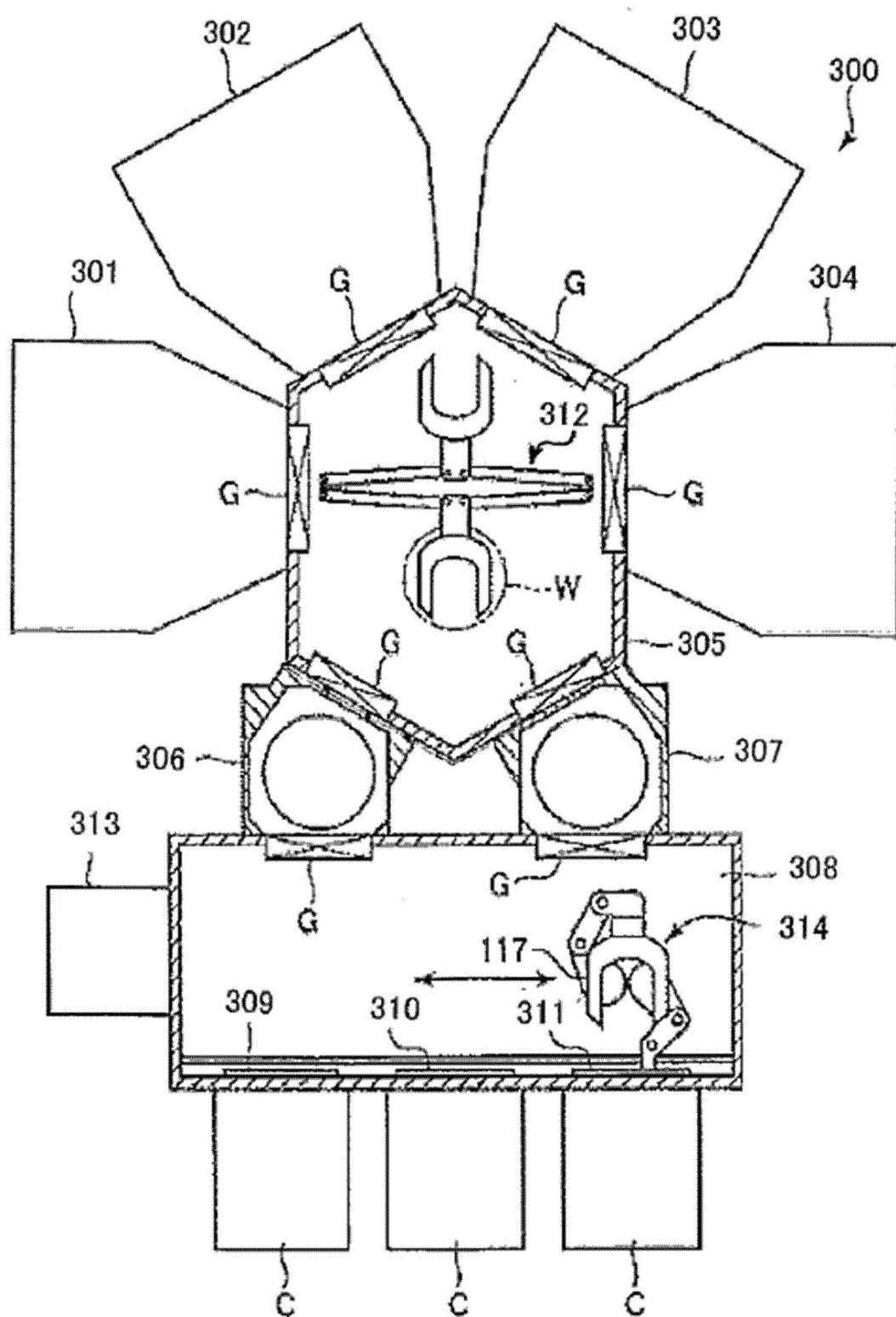

【図3】本発明の実施形態による半導体デバイスの製造装置を示す模式平面図を示す。

【図4】RLSAエッチング装置の模式切断透視図である。

【図5】図4に示すRLSAエッチング装置の部分拡大図である。

【図6】図4に示すRLSAエッチング装置において用いられるスロットアンテナの平面図である。

【発明を実施するための形態】

【0008】

以下、実施形態について、添付図面を参照しながら説明する。多様な図面中、類似の参考符号は、対応する要素または同一の要素を指す。

50

## 【0009】

図1A～図1Gを参照して、本発明の実施形態による半導体デバイス（例えば、MOSFET）の製造方法について説明する。図1Aを参照して、基板Wの表面212上にゲート絶縁膜202（例えば、酸化ケイ素（SiO<sub>2</sub>）膜を介してポリSi製のゲート電極203を形成する。その後、図1Bを参照して、ガス（例えば、Si含有ガス（SiH<sub>4</sub>および酸素ガス））を供給することによってRLSACVD装置内において化学蒸着を行うことにより、酸化ケイ素（SiO<sub>2</sub>）220をゲート電極203および表面212上に堆積させる。RLSACVD装置は、ラジアルラインスロットアンテナを含む。

## 【0010】

その後、シリコン基板WをRLSAエッティング装置へと移動させる。RLSAエッティング装置において、堆積された酸化ケイ素（SiO<sub>2</sub>）をエッティングして、オフセットスペーサ204をゲート電極203の側面上に形成する（図1Cを参照）。このエッティングプロセスは、2つの工程を有する。表1中に、第1の工程および第2の工程における条件を示す。各工程を停止するタイミングは、第1の工程および第2の工程が行われる継続時間それぞれに基づいて、決定される。第1のエッティングプロセスの後、約1nm～約2nmの厚さの堆積材料が残留する。第2のエッティングプロセスにおいて、エッティング対象である堆積材料のうちほとんど全てが除去される。

## 【0011】

第1の工程および第2の工程において、マイクロ波出力は約1,500W～約4,000Wであり、圧力は約5morr～約200morrであり、サセプタのバイアスは約30W～約200Wであり、シリコン基板Wの保持台となるサセプタの温度は約0～約80である。使用すべきガスを挙げると、例えば、CHF<sub>3</sub>、CH<sub>2</sub>F<sub>2</sub>、O<sub>2</sub>、N<sub>2</sub>および/またはH<sub>2</sub>がある。エッティングにおいて用いられるガスは、エッティング対象となる材料に従って決定される。エッティングプロセスの継続時間は、エッティング対象となる膜の厚さによって異なり、例えば5nmをエッティングするために1分間がかかる。しかし、最大継続時間は約3分以内におさめるべきである。

## 【0012】

## 【表1】

| 使用ガス    | 第1の工程                                                                         | 第2の工程                                                                         |

|---------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

|         | CH <sub>2</sub> F <sub>2</sub> :1000sccm<br>O <sub>2</sub> :5sccm<br>Ar:2sccm | CH <sub>2</sub> F <sub>2</sub> :360sccm<br>O <sub>2</sub> :20sccm<br>Ar:2sccm |

| マイクロ波出力 | 2000W                                                                         | 2000W                                                                         |

| 圧力      | 20mT                                                                          | 10mT                                                                          |

| バイアス    | 150W                                                                          | 90W                                                                           |

## 【0013】

シリコン基板表面内におけるSi間の結合エネルギーは、エッティング対象となる酸化ケイ素膜内におけるSiとOとの間の結合エネルギーよりも小さい。そのため、シリコン基板の表面のエッティングがより容易になる。また、Si間の結合エネルギーは、エッティング対象となる窒化ケイ素膜中のSiとNとの間の結合エネルギーよりも低い。そのため、Si基板のエッティングがSiNの場合よりもより容易になる。SiO<sub>2</sub>およびシリコン双方を有する基板に対してエッティングが行われるため、Siが保護された状態でSiO<sub>2</sub>に対してエッティングが行われる。そのため、エッティング対象となる膜に対して高い選択性がプロセスにおいて必要となる。側壁スペーサとしてのSiNが利用可能であり、その場合、高エッティング選択性のSiNおよびシリコンが必要となる。

## 【0014】

本実施形態において、表1中に示す。エッティング条件が異なる第1のエッティング工程および第2のエッティング工程を行う。本プロセスにおいて、主に堆積に貢献するガスと、主にエッティングに貢献する他のガスとを用いて、堆積とエッティングとの間のバランスをとり

10

20

30

40

50

、これにより Si 表面を保護する。よって、エッティングが行われている間、堆積（主に CF<sub>x</sub>）が表面上に蓄積する。そのため、シリコン基板が実質的にエッティングされることが回避される。その結果、エッティングプロセス時においてシリコン基板の表面が保護される。

【 0 0 1 5 】

堆積物は、反応生成物（主に CF<sub>x</sub>）であり、少なくとも炭素およびフッ素を含む。一般的に、CF<sub>x</sub>堆積物はガス含有酸素を用いて除去される。このような堆積物の除去は、アッシングを用いて行われる。アッシングプロセスにおいて、比較的肉厚の酸化領域が形成される。そのため、アッシングプロセス時においてシリコン基板表面を酸化から保護する必要が出てくる。

10

【 0 0 1 6 】

エッティングプロセスにおいて、堆積物 210 を表面 212 上に堆積させる。表面 212 の下側には、Si 製の基板 W が形成される（図 1C を参照）。堆積物 210 を除去するために、エッティングプロセスの後、RLSA エッティング装置中の基板 W の表面 212 上に酸素プラズマを励起させる。この O<sub>2</sub> の励起時において、表 2 に示すような条件下において酸素プラズマを励起させる。

【 0 0 1 7 】

【表 2】

|        |                          |

|--------|--------------------------|

| 使用ガス   | O <sub>2</sub> (350sccm) |

| 出力     | 2000W                    |

| 圧力     | 100mTorr 以上              |

| バイアス   | なし                       |

| サセプタ温度 | 約20°C～約30°C              |

| 時間     | 5s                       |

20

【 0 0 1 8 】

シリコン基板 W を支持するサセプタの温度は、約 20 ～ 約 30 である。O<sub>2</sub> の励起時において、出力は約 2,000W ～ 約 3,000W であり、圧力は約 100 mTorr 以上である。シリコン基板 W の表面 212 の近隣の酸素プラズマの電子温度（例えば、シリコン基板 W の表面 212 から 20 mm における酸素プラズマの電子温度）は好適には、約 1 eV ～ 約 1.5 eV である（プラズマ電位は約 5 eV ～ 7 eV である）。より好適には、シリコン基板 W の表面 212 から 20 mm における酸素プラズマの電子温度は、約 1 eV ～ 約 1.2 eV である。一般的に、プラズマ電位は、プラズマの電子温度の約 3 ～ 5 倍であることが多い。そのため、プラズマの電子温度が 1.0 eV ～ 1.5 eV である場合、プラズマ電位は約 3 eV ～ 約 7.5 eV である。プラズマの電子温度が 1.0 eV ～ 約 1.2 eV である場合、プラズマ電位は約 3 eV ～ 6 eV である。プラズマ電位の測定は、例えばシリコン基板の表面 212 から約 10 mm 上方の測定位置において行われる。測定位置は、例えば、チャンバ壁側である。プラズマ電位は、サセプタに付加されるバイアス電位によって異なる点に留意すべきである。しかし、O<sub>2</sub> の励起を用いた本発明の実施形態によれば、バイアスはサセプタに付加されない。そのため、バイアスに起因する変動は考慮しなくてよい。シリコン基板 W の表面 212 の近隣の酸素プラズマの電子温度が高い場合、O<sub>2</sub> の励起時におけるシリコン基板 W の表面 212 がより激しく酸化し、損傷を受ける。そのため、ソース領域およびドレイン領域上の表面 212 の一領域中に酸化部分（意図されない凹部）が発生する。この酸化部分に起因する、半導体デバイスを設計通りに製造することができなくなる。

30

【 0 0 1 9 】

図 2A および図 2B は、異なる圧力の下における堆積除去率を示す。堆積除去率を測定するために、3,000W のマイクロ波出力を KrF レジスト（堆積物）に付加することにより、エッティング（O<sub>2</sub> 励起）を 10 秒間行う。この実験において、KrF レジストを

40

50

堆積物として仮定する。図2Cおよび図2Dは、異なる圧力下の酸化量を示す。酸化量を測定するために、3,000Wのマイクロ波出力をベアシリコン基板に付加することにより、エッティング( $O_2$ 励起)を10秒間行う。酸化量は、シリコン基板内における酸化量である。図2A～図2Dにおいて、横軸の単位は「mm」であり、縦軸の単位はオングストロームである。

【0020】

図2Aの左側および図2Cの左側によれば、20mTを下回っているときの酸化量は高いまま保持されており、堆積除去率は高いまま保持されている。酸化量を低下させるためには、20mTを越える圧力下において $O_2$ の励起を行えばよい。

【0021】

図2Cの左側によれば、20mTを下回っているときの酸化量は $2.1\text{ nm} / 10\text{ 秒} \pm 3.9\%$ (10秒間で厚さ $2.1\text{ nm}$ )である。本発明による実施形態において、 $O_2$ の励起を5秒間行う。これによって、実施形態における酸化量は $1.05\text{ nm}$ となるはずである。

【0022】

図2Aの右側および図2Cの右側によれば、60mTを下回っているときの酸化量は高いまま保持されており、堆積除去率も高いまま保持されている。酸化量を低減させるためには、60mTを越える高圧力下において $O_2$ の励起を行えばよい。

【0023】

図2Cの右側によれば、60mTを下回っているときの酸化量は $1.6\text{ nm} / 10\text{ sec} \pm 5.8\%$ (10秒間で厚さ $1.6\text{ nm}$ )である。本発明による実施形態において、 $O_2$ の励起を5秒間行う。よって、実施形態において、酸化量は $0.8\text{ nm}$ となるはずである。

【0024】

図2Bの左側および図2Dの左側によれば、100mTを下回っているときの酸化量は低いまま保持されており、堆積除去率は高いまま維持されている。酸化量を低下させるためには、より高い圧力下において $O_2$ の励起を行えばよい。

【0025】

図2Dの左側によれば、100mTを下回っているときの酸化量は、 $1.2\text{ nm} / 10\text{ sec} \pm 8.0\%$ (10秒間で厚さ $1.2\text{ nm}$ )である。本発明による実施形態において、 $O_2$ の励起を5秒間行う。よって、実施形態において、酸化量は $0.6\text{ nm}$ となるはずである。

【0026】

図2Bの右側および図2Dの右側によれば、200mTを下回っているときの酸化量は低いまま保持され、堆積除去率は高いまま維持されている。よって、100mTの場合と同様に、酸化量が低いため、 $O_2$ の励起を200mT下において行うことが可能になる。

【0027】

図2Dの右側によれば、200mTを下回っているときの酸化量は $0.9\text{ nm} / 10\text{ sec} \pm 3.7\%$ (10秒間で厚さ $0.9\text{ nm}$ )である。本発明による実施形態において、 $O_2$ の励起を5秒間行う。よって、実施形態において、酸化量は $0.45\text{ nm}$ となるはずである。

【0028】

実際、シリコン基板の移動時にシリコン基板が酸素に露出されることに起因して、シリコン基板上に自然酸化膜が非意図的に形成される。自然酸化膜の厚さは約 $1\text{ nm}$ である。

【0029】

$O_2$ の励起を2回行ったとしても、酸化膜の厚さは単純に2倍になるのではない点に留意すべきである。その場合、厚さが増加するのではなく、 $SiO_2$ の濃度が増加し得る。

【0030】

本実施形態において、酸素プラズマの電子温度(例えば、シリコン基板Wの表面212から20mmにおける酸素プラズマの電子温度)は、シリコン基板W上のソース領域およ

10

20

30

40

50

びドレイン領域上の表面 212 の領域内の深酸化部分を酸化させないような、十分に低い温度である。本実施形態によれば、ソース領域およびドレイン領域上の表面 212 上の領域内において、O<sub>2</sub> の励起時において酸化部分は実質的に形成されない（図 1D を参照）。本実施形態によれば、ソース領域およびドレイン領域上の表面 212 上の領域内において O<sub>2</sub> の励起時において酸化部分が形成された場合でも、酸化部分の厚さは好適には約 1 nm 未満であり得る。

#### 【0031】

本実施形態において、エッティングプロセスが行われた RLSA エッティング装置内においても O<sub>2</sub> の励起を行う。そのため、シリコン基板 W 上に形成される膜の劣化を実質的に回避することが可能になる。なぜならば、シリコン基板 W がエッティングのための 1 つの処理チャンバから O<sub>2</sub> の励起のための別の処理チャンバへと移動される際にシリコン基板 W が雰囲気に露出されず、また、エッティング堆積物を別の処理チャンバの前に除去することが可能であるからである。

#### 【0032】

リンイオンをシリコン基板 W 中に注入して、延長部 208 を形成する（図 1E を参照）。その後、側壁スペーサ 216 を形成するために、酸化物膜または窒化物膜（例えば、SiN 膜 214）をシリコン基板 W の表面上に形成して、表面 212 およびゲート電極 203 をオフセットスペーサ 204 で被覆する（図 1F を参照）。RLSACVD 装置内における化学蒸着を用いて、シリコン基板 W の表面上に SiN を堆積させる。SiN 膜 214 の厚さは、延長部の長さに基づいて決定される。その後、RLSA エッティング装置内において、堆積された SiN をエッティングして、ゲート電極 203 側に側壁スペーサ 216 を形成する（図 1G を参照）。

#### 【0033】

エッティングプロセス時において、堆積物 210 を表面 212 上に堆積させる。表面 212 の下側には、シリコン製の基板 W が形成される。堆積物 210 を除去するために、エッティングプロセス後、RLSA エッティング装置内の基板 W の表面 212 上に酸素プラズマを励起する。O<sub>2</sub> の励起時において、表 2 に示すような条件下において酸素プラズマを励起する。

#### 【0034】

シリコン基板 W を支持するサセプタの温度は、約 20 ~ 約 30 である。O<sub>2</sub> の励起時において、出力は約 2,000 W ~ 約 3,000 W で、圧力は約 100 mtorr 以上である。シリコン基板 W の表面 212 の近隣の酸素プラズマの電子温度（例えば、シリコン基板 W の表面 212 から 20 mm における酸素プラズマの電子温度）は好適には、約 1 eV ~ 約 1.5 eV である。より好適には、シリコン基板 W の表面 212 から 20 mm における酸素プラズマの電子温度は、約 1 eV ~ 約 1.2 eV である。シリコン基板 W の表面 212 の近隣の酸素プラズマの電子温度が高い場合、O<sub>2</sub> の励起時においてシリコン基板 W の表面 212 が容易に酸化する。そのため、ソース領域およびドレイン領域上の表面 212 の一領域内に酸化部分（意図されない凹部）が発生する。この酸化部分に起因して、半導体デバイスを設計通りに製造することが不可能になる。

#### 【0035】

本実施形態において、酸素プラズマの電子温度（例えば、シリコン基板 W の表面 212 から 20 mm における酸素プラズマの電子温度）は、ソース領域およびドレイン領域上の表面 212 の領域内の深酸化部分を酸化させないような、十分に低い温度である。本実施形態によれば、ソース領域およびドレイン領域上の表面 212 上の領域内において、O<sub>2</sub> の励起時において酸化部分は実質的に形成されない（図 1G を参照）。本実施形態によれば、ソース領域およびドレイン領域上の表面 212 上の領域内において O<sub>2</sub> の励起時において酸化部分が形成された場合でも、酸化部分の厚さは好適には約 1 nm 未満であり得る。

#### 【0036】

その後、シリコン基板 W 中にヒ素イオンを注入して、ソース / ドレイン領域を形成する

10

20

30

40

50

(図1Gを参照)。側壁スペーサ216の厚さに起因して、高濃度のソース／ドレイン領域218が延長部208の外部に形成される。

【0037】

上述した方法によれば、例えば図1Gに示すようなMOSFETが製造される。この半導体デバイスは、ソース領域と、ドレイン領域218とを有する。ソース領域およびドレイン領域218上の表面212の領域内の酸化部分の厚さは、実質的に約1nm未満であり得る。

【0038】

本実施形態において、オフセットスペーサ204および側壁スペーサ216双方が形成され、O<sub>2</sub>の励起プロセスが2回行われる。しかし、側壁スペーサ216のみが形成され、オフセットスペーサ204は形成されない。この場合、O<sub>2</sub>の励起プロセスは1回だけ行われる。

【0039】

例えば、O<sub>2</sub>の励起は、プラズマ処理装置を用いることによって行われる。シリコン基板Wの近傍における電子温度が約1.5eVと低い酸素プラズマを生成することが可能な任意のプラズマ処理装置を用いて、O<sub>2</sub>の励起を行うことが可能である。一例として、以下、RLSAエッチング装置について説明する。

【0040】

図3は、半導体デバイスを製造するためのシステム300を示す。システム300は、処理装置301、302、303および304と、移動チャンバ305と、ロードロックモジュール306および307と、ローダーチャンバ308と、シャッター309、310および311と、第1の移動機構312と、方向付けユニット313と、第2の移動機構314とを含む。この種のシステムは通常「クラスターツール」と呼ばれ、いくつかの処理装置301、302、303および304を移動チャンバ305の周囲において備える。各処理装置は、所望のプロセス（例えば、エッチング、膜形成および他の処理）に応じて選択することができる。ローダーチャンバ308内の第2の移動機構314により、基板WをカセットCから処理装置301、302、303および304内へと移動させた後、移動チャンバ305内の第1の移動機構312により、処理装置へと移動させる。移動チャンバ305において、所定のプロセスが真空状態において実行される。基板Wの処理時において、処理装置301、302、303および304の内部空間および移動チャンバ305を各真空ポンプ（図示せず）によって真空排気し、所定の真空状態に維持する。プロセスの完了後、基板をカセットCへと戻す。処理装置のさらなる詳細については後述する。

【0041】

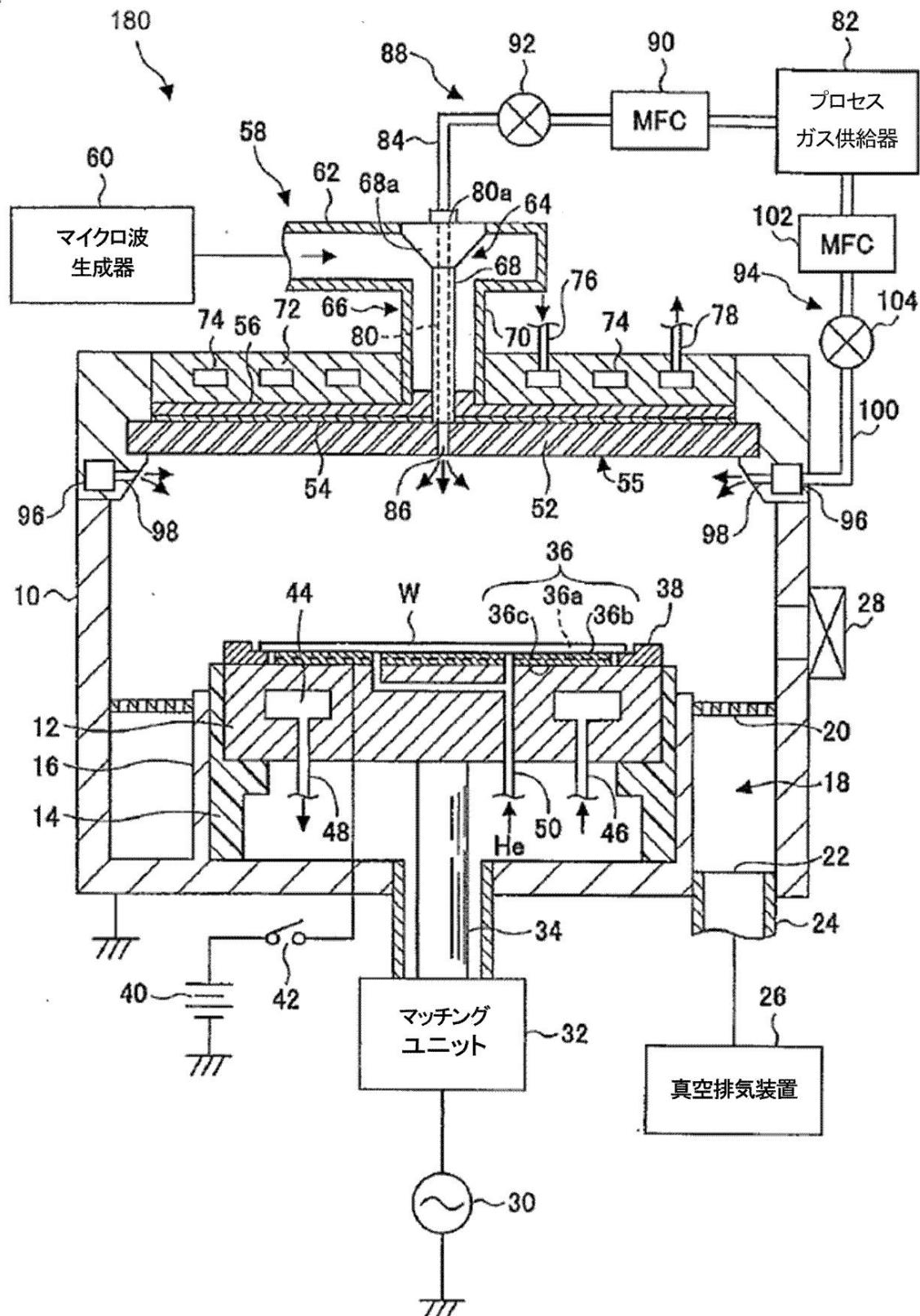

図4は、RLSAエッチング装置180の模式切断透視図である。図4を参照して、マイクロ波プラズマエッチング装置180が図示されている。マイクロ波プラズマエッチング装置180は、表面波プラズマ型プラズマ処理装置として構成され、金属（例えば、アルミニウムまたはステンレススチール）製の円筒形状のチャンバ（プロセスチャンバ）10を有する。チャンバ10は、セキュリティ上の理由のために接地している。

【0042】

先ず、マイクロ波プラズマエッチング装置180のチャンバ10におけるマイクロ波プラズマ生成に直接寄与しない部品または部材について説明する。

【0043】

チャンバ10の下側中央部分において、サセプタ12が設けられる。サセプタ12上に、半導体基板W（以下、基板Wと呼ぶ）が配置される。サセプタ12は、チャンバ10の底部から上方に延びる円筒形支持部14によって水平方向に保持される。円筒形支持部14は、絶縁材料によって構成される。さらに、サセプタ12は、円形板状に形成され、例えばアルミニウム製であり、下側電極としても機能する。下側電極に対し、無線周波数が付加される。

【0044】

10

20

30

40

50

輪状の真空排気経路 18 を、チャンバ 10 の内壁と、チャンバ 10 の底部から上方において円筒形支持部 14 の外周表面に沿って延びる別の円筒形支持部 16 との間に設ける。円筒形支持部 16 は、導電性である。輪状のバッフル板 20 が真空排気経路 18 の上部（または入口部）に配置され、真空排気ポート 22 が真空排気経路 18 の下側に設けられる。チャンバ 10 内のサセプタ 12 上の基板 W に関する対称に分散した均一なガス流パターンが得られるようにするために、複数の真空排気ポート 22 を円周方向において均等な角度間隔で設けると好適である。真空排気ポート 22 はそれぞれ、真空排気パイプ 24 を通じて真空排気装置 26 へと接続される。真空排気装置 26 は、所望の圧力に低下するまでチャンバ 10 を真空排気することが可能な真空ポンプ（例えば、ターボ分子ポンプ（TMP））を持ち得る。ゲート弁 28 が、チャンバ 10 の外壁上に取り付けられる。ゲート弁 28 が、移送開口部を開閉させる。移送開口部を通じて、基板 W をチャンバ 10 内へとまたはチャンバ 10 から移送させる。10

#### 【0045】

サセプタ 12 は、無線周波数電源 30 へと電気的に接続される。無線周波数電源 30 は、マッチングユニット 32 および電力供給ロッド 34 を通じて、RFバイアス電圧をサセプタ 12 へと付加する。電源 30 は、比較的低周波数（例えば、13.56 MHz）を有する無線周波数波を所定の電力レベルにおいて出力する。このような低周波数は、サセプタ 12 上の基板 W に引き寄せられるイオンエネルギーを制御するのに適している。マッチングユニット 32 は、マッチング要素を含む。マッチング要素は、電源 30 の出力インピーダンスと、負荷（例えば、電極（サセプタ）、チャンバ 10 内において発生するプラズマ、チャンバ 10）のインピーダンスとをマッチングさせるためのものである。マッチング要素は、自己バイアスを生成するための阻止コンデンサを有する。20

#### 【0046】

サセプタ 12 の面上には、静電チャック 36 が設けられる。静電チャック 36 は、サセプタ 12 上への静電力により、基板 W を保持する。静電チャック 36 は、導電膜によって形成された電極 36a と、電極 36a を挟む一対の絶縁膜 36b および 36c とを有する。DC 電源 40 が、スイッチ 42 を介して電極 36a へと電気的に接続される。DC 電源 40 から静電チャック 36 へと付加される DC 電圧によってクーロン力が発生し、このクーロン力により、基板 W が静電チャック 36 上において保持される。静電チャック 36 の外部において、基板 W を包囲するようにフォーカスリング 38 が設けられる。30

#### 【0047】

冷媒チャンバ 44 が、サセプタ 12 の内側に設けられる。冷媒チャンバ 44 は環形状をしており、円周方向に延びる。所定の温度の冷媒または冷却水が、冷媒チャンバ 44 および導管 46 および 48 内を循環するように、冷却装置ユニット（図示せず）から導管 46 および 48 を通じて冷媒チャンバ 44 へと供給される。冷媒などを温度制御しておくことで、静電チャック 36 上の基板 W の温度の制御が可能となる。加えて、熱伝導ガス供給部（図示せず）からのガス供給パイプ 50 を通じて、熱伝導ガス（例えば、ヘリウムガス）が基板 W と静電チャック 36 との間に供給される。さらに、上昇可能なリフトピン（図示せず）がチャンバ 10 に設けられる。このピンは、基板 W がチャンバ 10 内にロードされた際またはチャンバ 10 からロードされた際に、サセプタ 12 を垂直方向に貫通し、基板 W を昇降させる。これらのリフトピンは、昇降機構（図示せず）により、駆動され得る。40

#### 【0048】

次に、マイクロ波プラズマエッティング装置 180 のチャンバ 10 中のマイクロ波プラズマの生成に寄与する構成要素または部材について説明する。マイクロ波をチャンバ 11 内に導入するために、平面アンテナ 55 がサセプタ 12 の上方に設けられる。

#### 【0049】

平面アンテナ 55 は、誘電体窓としての円形水晶板 52 と、円形ラジアルラインスロットアンテナ（RLSA）54 とを含む。詳細には、水晶板 52 は、密閉状態でチャンバ 10 へと取り付けられ、サセプタ 12 に対向するチャンバ 11 の天井面として機能する。RLSA 54 は、水晶板 52 の面上に配置され、複数の溝部を有する。これらの溝部は、同50

心円に沿って分散している。R L S A 5 4 は、誘電材料（例えば、石英）で形成された波長短縮板 5 6 を介して、マイクロ波伝送線 5 8 に電磁的に接続される。

#### 【 0 0 5 0 】

マイクロ波伝送線 5 8 は、導波路パイプ 6 2 と、導波路パイプ / 同軸パイプコンバーター 6 4 と、同軸パイプ 6 6 とを有する。マイクロ波伝送線 5 8 は、マイクロ波出力をマイクロ波生成器 6 0 から R L S A 5 4 へと伝送する。導波路パイプ 6 2 は、例えば四角パイプによって形成され、T E モードにおいてそのマイクロ波をマイクロ波生成器 6 0 から導波路パイプ同軸パイプコンバーター 6 4 を通じて伝送する。

#### 【 0 0 5 1 】

導波路パイプ / 同軸パイプコンバーター 6 4 は、導波路パイプ 6 2 を同軸パイプ 6 6 と接続し、導波路パイプ 6 2 中の T E モードマイクロ波を同軸パイプ 6 6 中の T E M モードマイクロ波に変換する。コンバーター 6 4 は好適には、導波路パイプ 6 2 に接続された上部において直径がより大きくなっている、同軸パイプ 6 6 の内側導体 6 8 に接続された下部において直径がより小さくなっている、これにより、高出力伝送レベルにおいて存在し得る電磁場の集中を回避する。換言すれば、コンバーター 6 4 は好適には、図 14 および図 15 に示すように逆円錐型（またはドアノブ型）形状にされる。以下の説明を簡潔にするために、コンバーター 6 4 を逆円錐型部 6 8 a と呼ぶ場合がある。

10

#### 【 0 0 5 2 】

同軸パイプ 6 6 は、コンバーター 6 4 から垂直方向において下方にチャンバ 1 0 の上中央部へと延び、R L S A 5 4 へと接続される。詳細には、同軸パイプ 6 6 は、外側導体 7 0 および内側導体 6 8 を有する。外側導体 7 0 は、上端部において導波路パイプ 6 2 へと接続され、遅波板 5 6 へと到達するように下方に延びる。内側導体 6 8 は、上端部においてコンバーター 6 4 へと接続され、R L S A 5 4 へと到達するように下方に延びる。マイクロ波は、内側導体 6 8 と外側導体 7 0 との間で T E M モードにおいて伝播する。

20

#### 【 0 0 5 3 】

マイクロ波生成器 6 0 からのマイクロ波出力は、マイクロ波伝送線 5 8（導波路パイプ 6 2、コンバーター 6 4 および同軸パイプ 6 6 を含む）を通じて伝送され、遅波板 5 6 を通過する R L S A 5 4 へと供給される。その後、マイクロ波は遅波板 5 6 内においてラジアル方向において分散し、R L S A 5 4 の溝部を通じてチャンバ 1 0 へ向かって出射される。溝部から出射されたマイクロ波は、水晶板 5 2 の下面に沿って表面波として伝播し、水晶板 5 2 の下面の近隣においてガスをイオン化し、これによりチャンバ 1 0 中においてプラズマを生成する。

30

#### 【 0 0 5 4 】

遅波板 5 6 の面上に、アンテナ後面プレート 7 2 が設けられる。アンテナ後面プレート 7 2 は、例えばアルミニウム製である。アンテナ後面プレート 7 2 は、冷却装置ユニット（図示せず）が接続された流体導管 7 4 を含み、これにより、所定の温度の冷媒または冷却水が導管 7 4 ならびにパイプ 7 6 および 7 8 を通じて循環される。すなわち、アンテナ後面プレート 7 2 は、水晶板 5 2 中に発生する熱を吸収し、熱を外部へと移動させる冷却ジャケットとして機能する。

40

#### 【 0 0 5 5 】

図 4 に示すように、本実施形態において、同軸パイプ 6 6 の内側導体 6 8 を貫通するようにガス導管 8 0 が設けられる。加えて、第 1 のガス供給パイプ 8 4（図 4）は、一端においてガス導管 8 0 の上側開口部へと接続され、他端においてプロセスガス供給器 8 2 へと接続される。その上、ガス射出開口部 8 6 が水晶板 5 2 の中央に形成され、チャンバ 1 0 に対して開口する。上記構成を有する第 1 のプロセスガス導入部 8 8 において、プロセスガス供給器 8 2 からのプロセスガスが同軸パイプ 6 6 内において第 1 のガス供給パイプ 8 4 およびガス導管 8 0 を流れ、ガス射出開口部 8 6 の下側に配置されたサセプタ 1 2 に向かってガス射出開口部 8 6 から出射される。出射されたプロセスガスは、チャンバ 1 0 内において下方にラジアル方向に分散する。これは、サセプタ 1 2 を包囲している真空排気経路 1 8 へとプロセスガスが真空排気装置 2 6 によって牽引されたことに部分的に起因

50

する。ところで、第1のガス供給パイプ84には、中央部においてマスフローコントローラ(MFC)90およびオンオフ弁92が設けられる。

【0056】

この実施形態において、第2のプロセスガス導入部94が第1のプロセスガス導入部88に加えて設けられ、これにより、プロセスガスがチャンバ10へと導入される。第2のプロセスガス導入部94は、バッファチャンバ96と、複数の側方出射穴部98と、ガス供給パイプ100とを含む。バッファチャンバ98は中空環部形状にされ、チャンバ10の側壁部の内側において側壁部の円周方向に沿って延び、水晶板52よりも若干下側に配置される。複数の側方出射穴部98は、チャンバ10内においてプラズマ領域に向かって開口し、チャンバ10の内壁に沿って均等な角度間隔で配置され、バッファチャンバ96とガス連通する。ガス供給パイプ100は、バッファチャンバ96をプロセスガス供給器82へと接続する。ガス供給パイプ100には、中央においてMFC102およびオンオフ弁104が設けられる。

【0057】

第2のプロセスガス導入部94において、プロセスガス供給器82からのプロセスガスは、第2のプロセスガス供給パイプ100を通じて、チャンバ10の側壁部中のバッファチャンバ96内へと導入される。プロセスガスが充填されたバッファチャンバ96内の圧力は、バッファチャンバ96の円周方向にそって均一となり、その結果、プロセスガスは、複数の出射穴部98から水平方向にチャンバ10内のプラズマ領域へ向かって均一に出射される。この場合、出射穴部98から出射されたプロセスガスを基板Wの上方において分散させることが困難になり得る。なぜならば、プロセスガスが真空排気経路18上において流れる際にプロセスガスが真空排気ポート22へと牽引されるからである。しかし、水晶板52の中央に配置されたガス射出開口部86から出射されたプロセスガスは、外側ラジアル方向に分散され、上述したように真空排気経路18に向かって流れ、側方出射穴部98から出射されたプロセスガスは、本実施形態における真空排気装置26によって広い範囲において影響を受けない。そのため、サセプタ12上の基板Wの上方においてプラズマを均等に分散させることができる。

【0058】

それぞれ第1のプロセスガス導入部88および第2のプロセスガス導入部94からチャンバ10内に導入されるプロセスガスは、同じであってもよいし、あるいは異なっていてもよい。ガスの流量は、それぞれMFC90および102によって制御することも可能であるし、あるいは、ガスを所定の流量比においてチャンバ内に導入することも可能であり、これにより、ガスおよびよってプラズマがラジアル方向において均一に分散される。

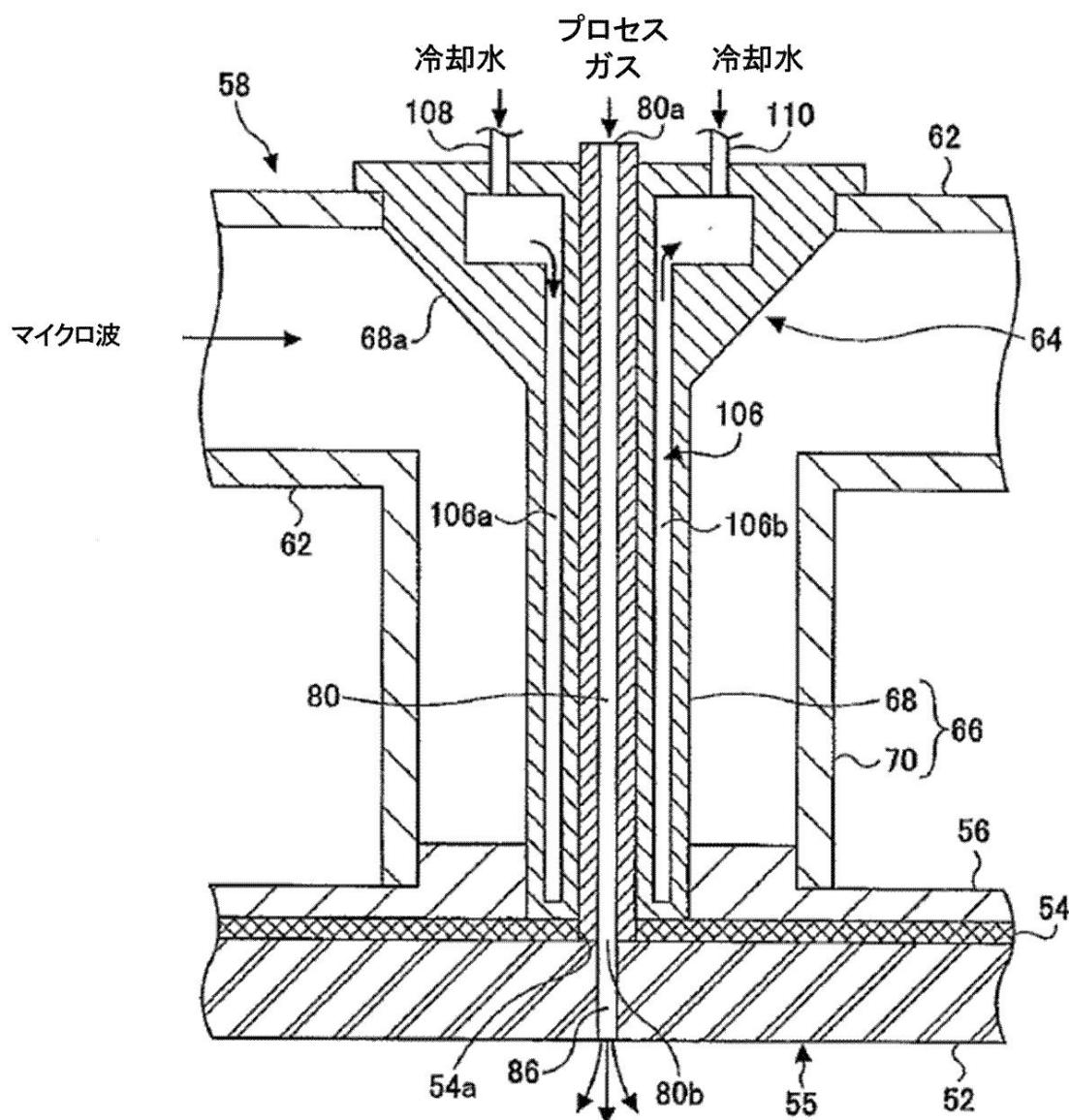

【0059】

図5を参照して、導波路パイプ同軸パイプコンバーター64および同軸パイプ66が詳細に図示されている。内側導体68は、例えばアルミニウム製である。ガス導管80は、内側導体68の中心軸に沿って内側導体68を貫通する。加えて、冷媒導管106は、ガス導管80と平行に形成される。

【0060】

冷媒導管106は、入来経路106aおよび送出経路106bを含む。入来経路106aおよび送出経路106bは、垂直パーティション(図示せず)によって分割される。倒立円錐部68aの上側部において、パイプ108が冷媒導管106の入来経路106aへと接続される。パイプ108の反対側端部は、冷却装置ユニット(図示せず)へと接続される。加えて、パイプ110は、冷媒導管106の送出経路106bへと接続される。パイプ110の反対側端部は、同一冷却装置ユニットへと接続される。この構成により、冷却装置ユニットから供給された冷媒または冷却水は、入来経路106aを通じて下方に流れ、入来経路106aの底部へと到達し、送出経路106bを通じて上方に戻ってパイプ110内に流入する。このようにして、内側導体68の冷却が可能になる。

【0061】

RLSA54の中央部において、開口部54aが設けられる。開口部54a内には、図

5 に示すようにガス導管 8 0 が取り付けられる。加えて、開口部 5 4 a が、水晶板 5 2 のガス射出開口部 8 6 と同軸に整列された様態で配置される。この構成により、R L S A 5 4 から放射される電磁波（マイクロ波）はガス射出開口部 8 6 に到達しないため、ガス射出開口部 8 6 内において放電は発生しない。ところで、ガス射出開口部 8 6 を分岐することで、複数の穴部が水晶板 5 2 内において得られる。これらの複数の穴部は、水晶板 5 2 のラジアル方向において特定範囲内に配置され得る。

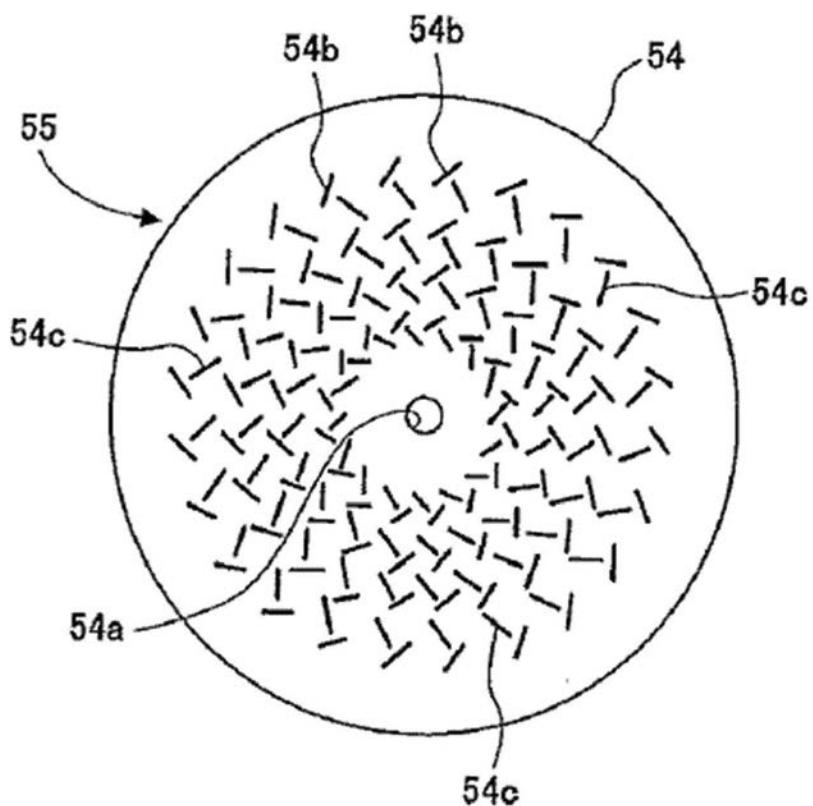

#### 【 0 0 6 2 】

図 6 は、本実施形態における R L S A 5 4 における溝部パターンを示す。図示のように、R L S A 5 4 は、同軸円状に分散した複数の溝部を有する。すなわち、長手方向が実質的に直角を形成している 2 種類の溝部 5 4 b および 5 4 c が、交互の同軸円状に分散される。これらの同軸円は、R L S A 5 4 のラジアル方向において伝播するマイクロ波の波長に応じて、ラジアル間隔において配置される。このような溝部パターンによれば、マイクロ波は、相互に交差する 2 つの偏光成分を有する円形偏光平面波へと変換され、平面波は R L S A 5 4 から放射される。上記のように構成された R L S A 5 4 は、アンテナの実質的に全体の領域からマイクロ波を均一にチャンバ 1 0 内へと放射させることができ（図 4）、均一かつ安定したプラズマを生成するのに適しているという点において有利である。

#### 【 0 0 6 3 】

ところで、真空排気装置 2 6 、R F 出力供給器 3 0 、D C 出力供給器 4 0 のスイッチ 4 2 、マイクロ波生成器 6 0 、プロセスガス導入部 8 8 および 9 4 、冷却装置ユニット（図示せず）、および熱伝導ガス供給部（図示せず）の多様な動作ならびに全体的動作は、制御部（図示せず）によって制御される。制御部は、例えば、本発明の第 1 の実施形態によるマイクロ波プラズマエッティング装置 1 8 0 におけるマイクロコンピュータによって構成される。

#### 【 0 0 6 4 】

誘電体窓の真下における電子温度が数 e V である装置 1 8 0 内においてマイクロ波 2.4 5 G H z によって生成されたプラズマは、下方に拡散する。その後、プラズマの電子温度は、処理対象基板の周囲において約数 e V まで低下する。電子温度が低下しているため、基板上の膜中において、プラズマ損傷はほとんど発生しない。また、R L S A を用いて高密度プラズマが実現され、処理速度の上昇が可能となる。

#### 【 0 0 6 5 】

上記の開示内容を鑑みれば明らかなように、本発明の多数の改変および変更が可能である。よって、添付の特許請求の範囲内において、本発明は、本明細書中に具体的に記載された様態以外の様態で実施することが可能である。

#### 【 符号の説明 】

#### 【 0 0 6 6 】

2 0 2 . . . ゲート絶縁膜

2 0 3 . . . ゲート電極

2 0 4 . . . オフセットスペーサー

2 0 8 . . . 延長部

2 1 0 . . . 堆積物

2 1 2 . . . 表面

2 2 0 . . . 酸化ケイ素

10

20

30

40

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図2A】

【図2B】

【図2C】

【図2D】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(56)参考文献 特開平10-135189(JP,A)

特開2009-059850(JP,A)

特開2008-098640(JP,A)

特開2008-277844(JP,A)

特開2006-332634(JP,A)

特開2000-114372(JP,A)

特開平07-142447(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/302、21/3065-21/336、21/461、

29/76、29/772-29/78