(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-107976

(P2010-107976A)

(43) 公開日 平成22年5月13日(2010.5.13)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>G09F 9/30</b> (2006.01)   | G09F 9/30  | 338 2H092   |

| <b>H01L 29/786</b> (2006.01) | H01L 29/78 | 623A 4M104  |

| <b>H01L 21/822</b> (2006.01) | H01L 29/78 | 618B 5C094  |

| <b>H01L 27/04</b> (2006.01)  | H01L 27/04 | H 5FO33     |

| <b>H01L 21/768</b> (2006.01) | H01L 21/90 | A 5FO38     |

審査請求 未請求 請求項の数 3 O L (全 44 頁) 最終頁に続く

|              |                              |          |                                                |

|--------------|------------------------------|----------|------------------------------------------------|

| (21) 出願番号    | 特願2009-229378 (P2009-229378) | (71) 出願人 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成21年10月1日 (2009.10.1)       | (72) 発明者 | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2008-259063 (P2008-259063) | (72) 発明者 | 秋元 健吾<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (32) 優先日     | 平成20年10月3日 (2008.10.3)       | (72) 発明者 | 小森 茂樹<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (33) 優先権主張国  | 日本国 (JP)                     | (72) 発明者 | 魚地 秀貴<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備え、占有面積が小さい保護回路等が必要となる。

【解決手段】ゲート電極を被覆するゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と端部が重畳する第1配線層及び第2配線層と、少なくともゲート電極と重畳しゲート絶縁膜及び該第1配線層及び該第2配線層における導電層の側面部及び上面部と接する酸化物半導体層とを有する非線形素子を用いて保護回路を構成する。非線形素子のゲート電極は走査線又は信号線と接続され、非線形素子の第1配線層又は第2配線層がゲート電極の電位が印加されるようにゲート電極層と直接接続されていることで、接続抵抗の低減による安定動作と接続部分の占有面積を縮小する。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

絶縁表面を有する基板上に走査線と信号線が交差して設けられ、

画素電極がマトリクス状に配列する画素部を有する表示装置であり、

前記画素部は、酸化物半導体層にチャネル形成領域が形成される薄膜トランジスタを有し、

前記薄膜トランジスタは、前記走査線と接続するゲート電極と、

前記信号線と接続し前記酸化物半導体層に接する第1配線層を有し、

前記基板の周辺部に配設される信号入力端子と前記画素部の間には、非線形素子が設けられ、

前記非線形素子は、ゲート電極及び該ゲート電極を被覆するゲート絶縁膜と、

前記ゲート絶縁膜上において前記ゲート電極と端部が重畳する第1配線層及び第2配線層と、

少なくとも前記ゲート電極と重畳し前記ゲート絶縁膜及び前記第1配線層及び前記第2配線層の側面部及び上面部と接する酸化物半導体層とを有し、

前記非線形素子のゲート電極は走査線又は信号線と接続され、前記非線形素子の第1配線層又は第2配線層が、前記ゲート電極の電位が印加されるようにゲート電極層と直接接続されていることを特徴とする表示装置。

10

20

30

40

50

**【請求項 2】**

絶縁表面を有する基板上に走査線と信号線が交差して設けられ、

画素電極がマトリクス状に配列する画素部を有する表示装置であり、

前記画素部は、酸化物半導体層にチャネル形成領域が形成される薄膜トランジスタを有し、

前記薄膜トランジスタは、前記走査線と接続するゲート電極と、

前記信号線と接続し前記酸化物半導体層に接する第1配線層と、

前記画素電極と接続し前記酸化物半導体層に接する第2配線層とを有し、

前記基板上であり前記画素部の外側領域に、前記走査線と共に接続する保護回路と、

前記信号線と共に接続する保護回路とが設けられ、

前記保護回路は、ゲート電極及び該ゲート電極を被覆するゲート絶縁膜と、

前記ゲート絶縁膜上において前記ゲート電極と端部が重畳する第1配線層及び第2配線層と、

少なくとも前記ゲート電極と重畳し前記ゲート絶縁膜及び前記第1配線層及び前記第2配線層の側面部及び上面部と接する酸化物半導体層とを有する非線形素子を有し、

前記非線形素子のゲート電極と、第1配線層又は第2配線層が直接接続されていることを特徴とする表示装置。

**【請求項 3】**

請求項1又は2において、

前記酸化物半導体層は、インジウム、ガリウム、及び亜鉛を含むことを特徴とする表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、酸化物半導体を用いる表示装置に関する。

**【背景技術】****【0002】**

液晶表示装置に代表されるように、ガラス基板等の平板に形成される薄膜トランジスタは、アモルファスシリコン、多結晶シリコンによって作製されている。アモルファスシリコンを用いた薄膜トランジスタは、電界効果移動度が低いもののガラス基板の大面積化に対応することができ、一方、結晶シリコンを用いた薄膜トランジスタは電界効果移動度は高

いものの、レーザアニール等の結晶化工程が必要であり、ガラス基板の大面積化には必ずしも適応しないといった特性を有している。

### 【0003】

これに対し、酸化物半導体を用いて薄膜トランジスタを作製し、電子デバイスや光デバイスに応用する技術が注目されている。例えば、酸化物半導体膜として酸化亜鉛( $ZnO$ )や、インジウム、ガリウム、及び亜鉛を含む酸化物半導体を用いて薄膜トランジスタを作製し、画像表示装置のスイッチング素子などに用いる技術が特許文献1及び特許文献2で開示されている。

### 【先行技術文献】

#### 【特許文献】

#### 【0004】

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

酸化物半導体をチャネル形成領域とする薄膜トランジスタは、アモルファスシリコンを用いた薄膜トランジスタよりも動作速度が速く、多結晶シリコンを用いた薄膜トランジスタよりも製造工程が簡単であるといった特性を有している。すなわち、酸化物半導体を用いることによって、プロセス温度が室温から300℃以下の低温であっても、電界効果移動度が高い薄膜トランジスタを作製することが可能である。

#### 【0006】

動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かし、信頼性を保証するためには、適切な構成を備えた保護回路等が必要となる。また、表示装置の小型化を図る上で、保護回路の占有面積を小さくすることが必要になってくる。

#### 【0007】

本発明は、保護回路として適した構造を提供することを目的の一とする。

#### 【0008】

本発明は、酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置において、保護回路の機能を高め動作の安定化を図ることを目的の一とする。

### 【課題を解決するための手段】

#### 【0009】

本発明の一態様は、酸化物半導体を用いて構成される非線形素子で保護回路が形成された表示装置である。この保護回路を構成する非線形素子が有する第1配線層及び第2配線層の少なくとも一方が、ゲート電極もしくはゲート電極と同じ工程で形成された導電膜に直接接続している。

#### 【0010】

本発明の例示的な一態様は、絶縁表面を有する基板上に走査線と信号線が交差して設けられ、画素電極がマトリクス状に配列する画素部と、該画素部の外側領域に酸化物半導体で形成された非線形素子を有する表示装置である。画素部は、酸化物半導体層にチャネル形成領域が形成される薄膜トランジスタを有する。画素部の薄膜トランジスタは、走査線と接続するゲート電極と、信号線と接続し酸化物半導体層に接する第1配線層と、画素電極と接続し酸化物半導体層に接する第2配線層とを有する。基板の周辺部に配設される信号入力端子と画素部の間には非線形素子が設けられている。非線形素子は、ゲート電極及び該ゲート電極を被覆するゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と端部が重畳する導電層からなる第1配線層及び第2配線層と、少なくともゲート電極と重畳しゲート絶縁膜及び該第1配線層及び該第2配線層における導電層の側面部及び上面部と接する酸化物半導体層とを有している。また、非線形素子のゲート電極は走査線又は信号線と接続され、非線形素子の第1配線層又は第2配線層がゲート電極の電位が印加されるようにゲート電極層と直接接続されている。

## 【0011】

本発明の例示的な一態様は、絶縁表面を有する基板上に走査線と信号線が交差して設けられ、画素電極がマトリクス状に配列する画素部と、該画素部の外側領域に保護回路を有する表示装置である。画素部は、酸化物半導体層にチャネル形成領域が形成される薄膜トランジスタを有する。画素部の薄膜トランジスタは、走査線と接続するゲート電極と、信号線と接続し酸化物半導体層に接する第1配線層と、画素電極と接続し酸化物半導体層に接する第2配線層とを有する。画素部の外側領域には、走査線と共に接続する保護回路と、信号線と共に接続する保護回路とが設けられている。保護回路は、ゲート電極及び該ゲート電極を被覆するゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と端部が重畳する導電層からなる第1配線層及び第2配線層と、少なくともゲート電極と重畳しゲート絶縁膜及び該第1配線層及び該第2配線層の側面部及び上面部と接する酸化物半導体層とを有する非線形素子を有している。また、保護回路が有している非線形素子のゲート電極と、第1配線層又は第2配線層が直接接続されている。

## 【0012】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

## 【発明の効果】

## 【0013】

本発明の一態様によれば、酸化物半導体を用いた非線形素子で保護回路を構成することにより、保護回路として適した構造を有する表示装置を得ることができる。

## 【0014】

また、第1配線層又は第2配線層に達するコンタクトホールと、ゲート電極もしくはゲート電極と同じ層で形成した配線に達するコンタクトホールを設け、別の配線層で第1配線層又は第2配線層と、ゲート電極又はゲート電極と同じ層で形成した配線を接続する方法がある。しかし、この方法を用いると一つの接続で界面およびコンタクトホールが各二つ形成される。

## 【0015】

本発明の一態様の保護回路を構成する非線形素子は、第1配線層又は第2配線層の導電層がゲート電極もしくはゲート電極と同じ層で形成した配線に直接接続するため、一つの接続で形成される界面およびコンタクトホールは各一つに過ぎない。接続に伴い形成される界面が一つであるため、別の配線層を介して接続する方法に比べて接触抵抗を抑制することができる。その結果、非線形素子を用いた保護回路が安定動作する。また、接続に必要なコンタクトホールがひとつであるため、別の配線層を介して接続する方法に比べて接続部分が占有する面積を抑制することでき、その結果、保護回路の占有面積を小さくして、表示装置の小型化を図ることができる。

## 【図面の簡単な説明】

## 【0016】

【図1】表示装置を構成する、信号入力端子、走査線、信号線、非線形素子を含む保護回路及び画素部の位置関係を説明する図。

【図2】保護回路の一例を示す図。

【図3】保護回路の一例を示す図。

【図4】保護回路の一例を示す平面図。

【図5】保護回路の一例を示す断面図。

【図6】保護回路の作製工程を説明する断面図。

【図7】保護回路の作製工程を説明する断面図。

【図8】保護回路の一例を示す平面図。

【図9】保護回路の一例を示す平面図。

【図10】電子ペーパーの断面図。

【図11】半導体装置のプロック図を説明する図。

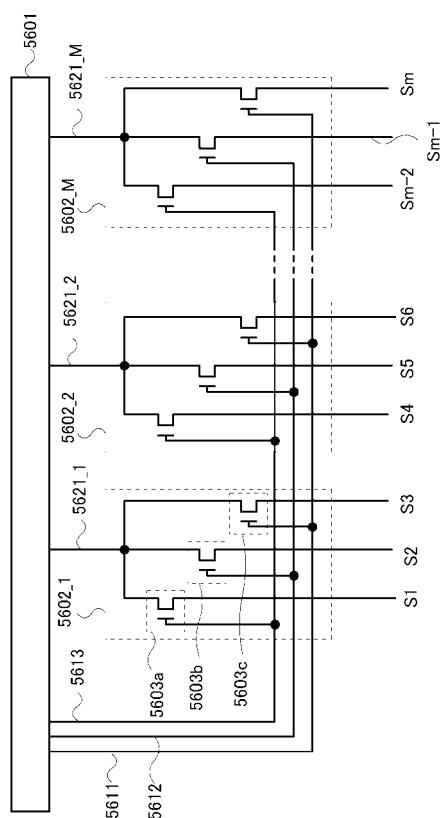

- 【図12】信号線駆動回路の構成を説明する図。

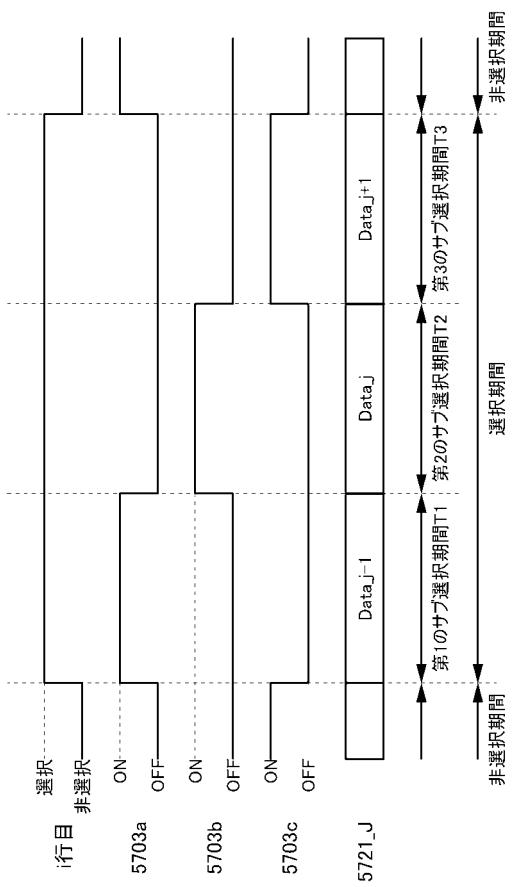

- 【図13】信号線駆動回路の動作を説明するタイミングチャート。

- 【図14】信号線駆動回路の動作を説明するタイミングチャート。

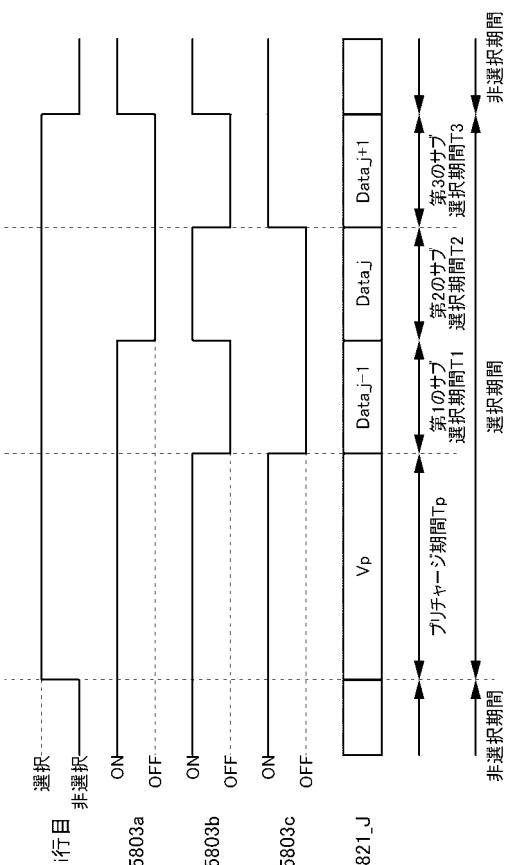

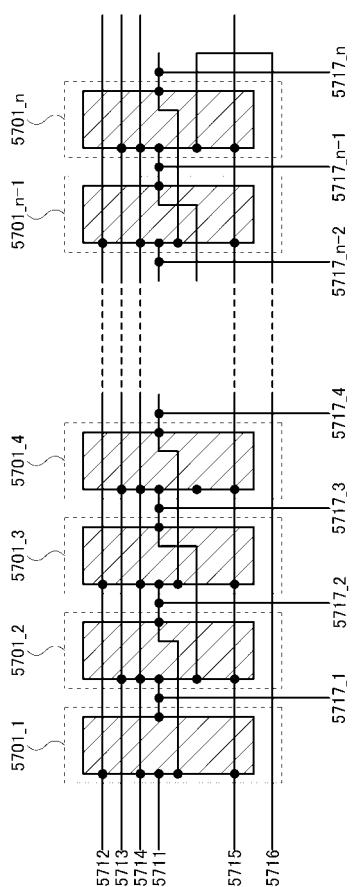

- 【図15】シフトレジスタの構成を説明する図。

- 【図16】図14に示すフリップフロップの接続構成を説明する図。

- 【図17】本発明の一態様の半導体装置を説明する上面図及び断面図。

- 【図18】本発明の一態様の半導体装置を説明する断面図。

- 【図19】本発明の一態様の半導体装置の画素等価回路を説明する図。

- 【図20】本発明の一態様の半導体装置を説明する図。

- 【図21】本発明の一態様の半導体装置を説明する上面図及び断面図。

- 【図22】電子ペーパーの使用形態の例を説明する図。

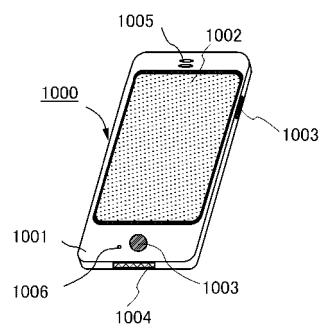

- 【図23】電子書籍の一例を示す外観図。

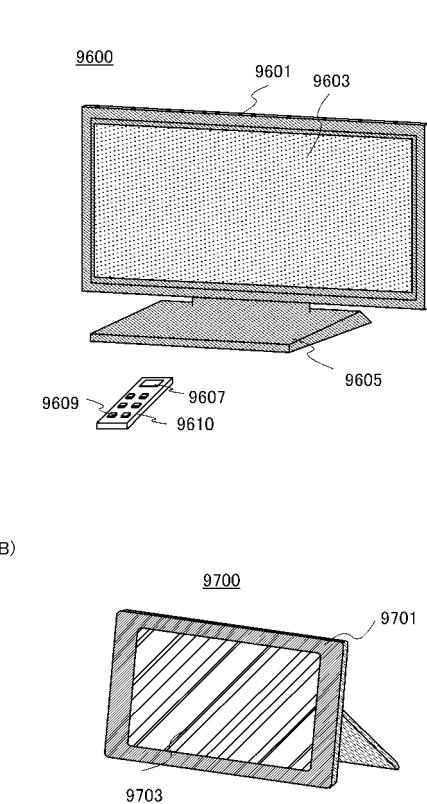

- 【図24】テレビジョン装置およびデジタルフォトフレームの例を示す外観図。

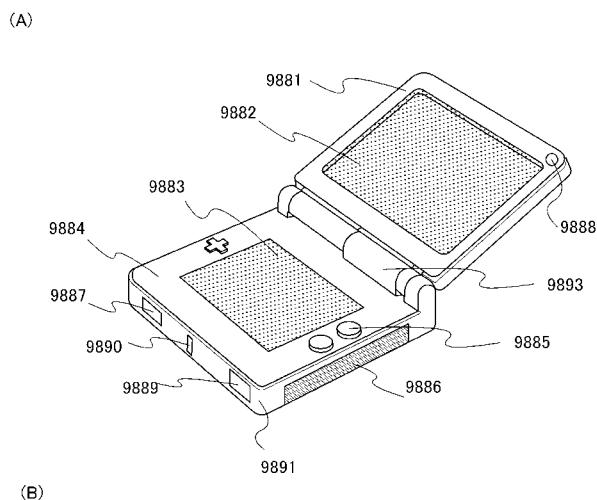

- 【図25】遊技機の例を示す外観図。

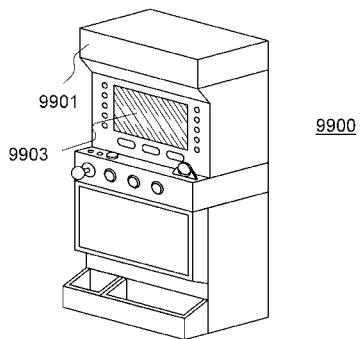

- 【図26】携帯電話機の一例を示す外観図。

- 【発明を実施するための形態】

- 【0017】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細をさまざまに変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

【0018】

(実施の形態1)

本実施の形態では、画素部とその周辺に非線形素子を含む保護回路が形成された表示装置の一態様を図面を参照して説明する。

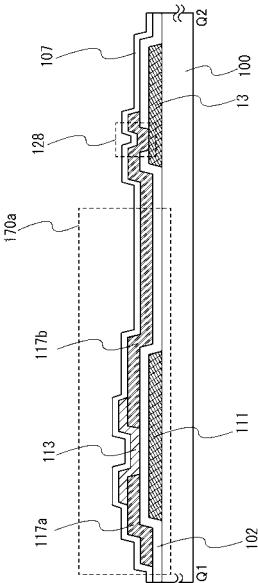

【0019】

図1は表示装置を構成する、信号入力端子、走査線、信号線、非線形素子を含む保護回路及び画素部の位置関係を説明する図である。絶縁表面を有する基板10上に走査線13と信号線14が交差して画素部17が構成されている。

【0020】

画素部17は複数の画素18がマトリクス状に配列して構成されている。画素18は走査線13と信号線14に接続する画素トランジスタ19、保持容量部20、画素電極21を含んで構成されている。

【0021】

ここで例示する画素構成において、保持容量部20は一方の電極が画素トランジスタ19と接続し、他方の電極が容量線22と接続する場合を示している。また、画素電極21は表示素子(液晶素子、発光素子、コントラスト媒体(電子インク)など)を駆動する一方の電極を構成する。これらの表示素子の他方の電極は共通端子23に接続される。

【0022】

保護回路は画素部17と、走査線入力端子11及び信号線入力端子12との間に配設されている。本実施の形態では複数の保護回路を配設して、走査線13、信号線14及び容量バス線27に静電気等によりサージ電圧が印加され、画素トランジスタ19などが破壊されないように構成されている。そのため、保護回路はサージ電圧が印加されたときに共通配線29又は共通配線28に電荷を逃がすように構成されている。

【0023】

本実施の形態では、保護回路24、保護回路25、保護回路26を表示装置内に配設する例を示している。尤も、保護回路の構成はこれに限定されない。

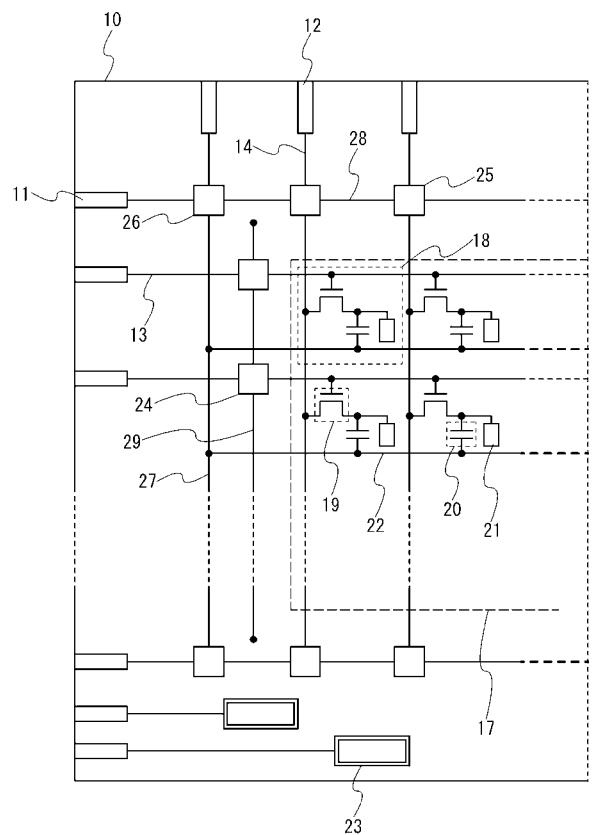

【0024】

図2は保護回路の一例を示す。この保護回路は、走査線13と共通配線29との間に並列

10

20

30

40

50

に配置された非線形素子 3 0 及び非線形素子 3 1 によって構成されている。非線形素子 3 0 及び非線形素子 3 1 は、ダイオードのような二端子素子又はトランジスタのような三端子素子で構成される。例えば、画素部の画素トランジスタと同じ工程で形成することも可能であり、例えばゲート端子とドレイン端子を接続することによりダイオードと同様の特性を持たせることができる。

【 0 0 2 5 】

非線形素子 3 0 の第 1 端子（ゲート）と第 3 端子（ドレイン）は走査線 1 3 に接続され、第 2 端子（ソース）は共通配線 2 9 に接続されている。また、非線形素子 3 1 の第 1 端子（ゲート）と第 3 端子（ドレイン）は共通配線 2 9 に接続され、第 2 端子（ソース）は走査線 1 3 に接続されている。すなわち、図 2 で示す保護回路は、二つのトランジスタのそれぞれが、整流方向を互いに逆向きにして、走査線 1 3 と共通配線 2 9 を接続する構成である。言い換えると、走査線 1 3 と共通配線 2 9 の間に、整流方向が走査線 1 3 から共通配線 2 9 に向かうトランジスタと整流方向が共通配線 2 9 から走査線 1 3 に向かうトランジスタを接続する構成である。

10

【 0 0 2 6 】

図 2 で示す保護回路は、共通配線 2 9 に対し、走査線 1 3 が静電気等により正又は負に帯電した場合、その電荷を打ち消す方向に電流が流れる。例えば、走査線 1 3 が正に帯電した場合は、その正電荷を共通配線 2 9 に逃がす方向に電流が流れる。この動作により、帯電した走査線 1 3 に接続している画素トランジスタ 1 9 の静電破壊又はしきい値電圧のシフトを防止することができる。また、帯電している走査線 1 3 と絶縁層を介して交差する他の配線との間で、絶縁層の絶縁破壊を防止することができる。

20

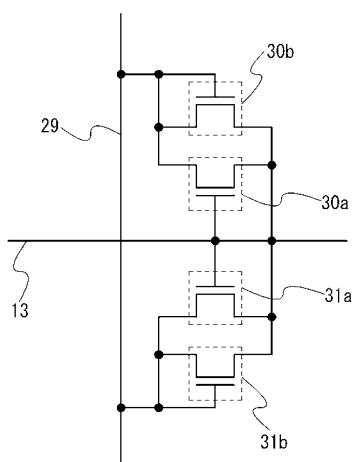

【 0 0 2 7 】

なお、図 2 は走査線 1 3 に第 1 端子（ゲート）を接続した非線形素子 3 0 と、共通配線 2 9 に第 1 端子（ゲート）を接続した非線形素子 3 1 、すなわち整流方向が逆向きの二個一組の非線形素子を用い、それぞれの第 2 端子（ソース）と第 3 端子（ドレイン）で共通配線 2 9 と走査線 1 3 を接続している。すなわち、非線形素子 3 0 と非線形素子 3 1 は並列である。他の構成として、さらに並列して接続する非線形素子を付加して、保護回路の動作安定性を高めても良い。例えば、図 3 は走査線 1 3 と共通配線 2 9 との間に設けられた、非線形素子 3 0 a と非線形素子 3 0 b 及び非線形素子 3 1 a と非線形素子 3 1 b により構成される保護回路を示す。

30

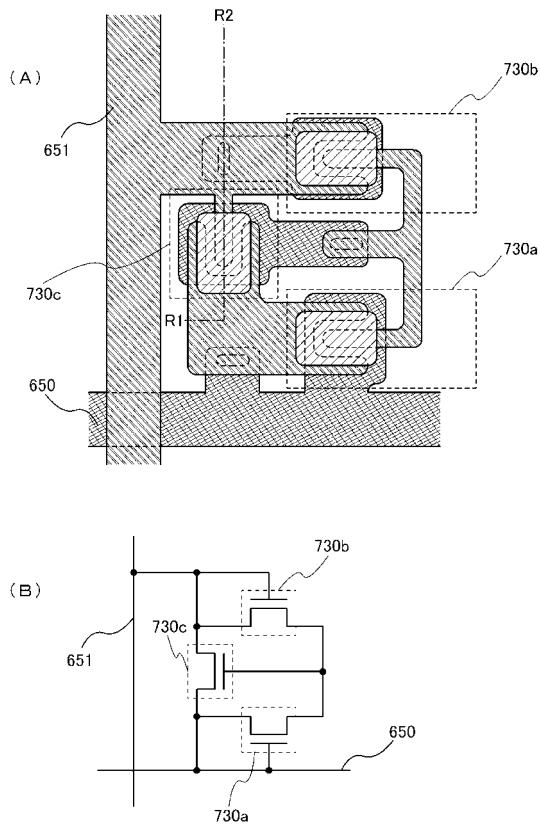

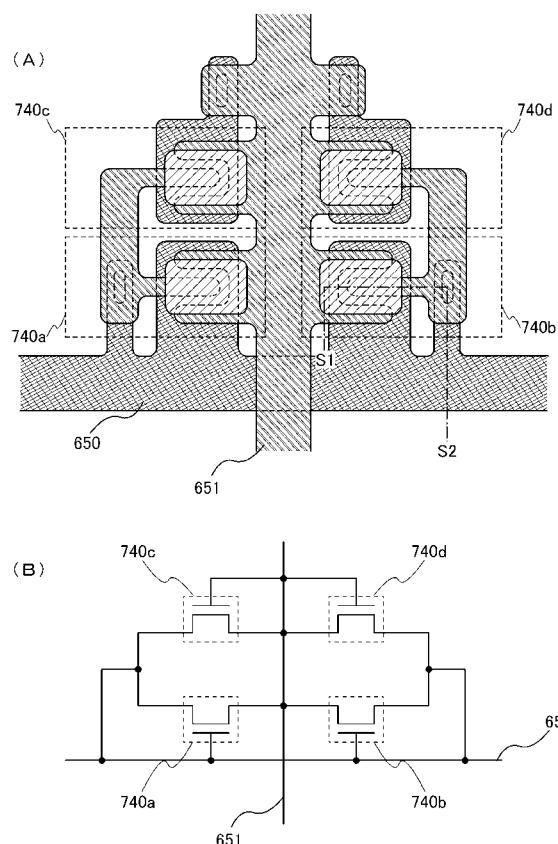

この保護回路は、共通配線 2 9 に第 1 端子（ゲート）及び第 3 端子（ドレイン）を接続し、走査線 1 3 に第 2 端子（ソース）を接続した二つの非線形素子（3 0 b 、 3 1 b ）と、走査線 1 3 に第 1 端子（ゲート）及び第 3 端子（ドレイン）を接続し、走査線 1 3 に第 2 端子（ソース）を接続した二つの非線形素子（3 0 a 、 3 1 a ）の計四つの非線形素子を用いている。すなわち、整流方向が互いに逆向きになるよう 2 つの非線形素子を接続した一組を、共通配線 2 9 と走査線 1 3 の間に二組接続している。言い換えると、走査線 1 3 と共通配線 2 9 の間に、整流方向が走査線 1 3 から共通配線 2 9 に向かう 2 つのトランジスタと、整流方向が共通配線 2 9 から走査線 1 3 に向かう 2 つのトランジスタを接続する構成である。このように、共通配線 2 9 と走査線 1 3 を四つの非線形素子で接続することで、走査線 1 3 にサージ電圧が印加された場合のみならず、共通配線 2 9 静電気等により帯電した場合であっても、その電荷がそのまま走査線 1 3 に流れ込んでしまうのを防止することができる。なお、図 9 に、4 つの非線形素子を基板上に配置する場合の一態様を等価回路図と共に示す。図 9 ( B ) に例示する等価回路図は図 3 と等価であり、図 9 ( B ) に記載されたそれぞれの非線形素子は図 3 に記載された非線形素子に対応する。具体的には、非線形素子 7 4 0 a は非線形素子 3 0 b に対応し、非線形素子 7 4 0 b は非線形素子 3 1 b に対応し、非線形素子 7 4 0 c は非線形素子 3 0 a に対応し、7 4 0 d は 3 1 a に対応する。また、図 9 の走査線 6 5 1 は走査線 1 3 に対応し、共通配線 6 5 0 は共通配線 2 9 に対応する。従って、図 9 ( A ) に例示する 4 つの非線形素子を基板上に配置して形成した保護回路の一態様は、図 3 に例示する保護回路の一態様である。

40

【 0 0 2 8 】

50

また、奇数個の非線形素子を使った保護回路の例として、非線形素子の基板への配置例を図8(A)に、等価回路図を図8(B)に示す。この回路では非線形素子730cに対し、非線形素子730b、非線形素子730aがスイッチング素子として接続している。このように非線形素子を直列に接続することで、保護回路を構成する非線形素子に加わる瞬間的な負荷を分散できる。

## 【0029】

図2は走査線13側に設ける保護回路の例を示したが、同様な構成の保護回路は信号線14側においても適用することができる。

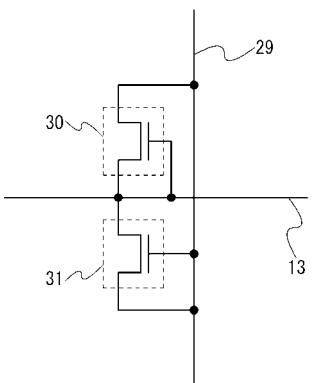

## 【0030】

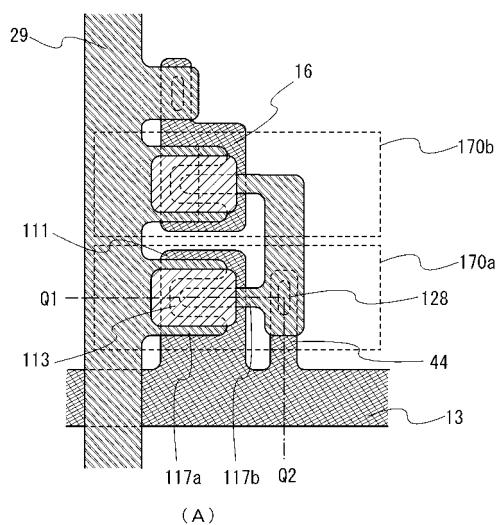

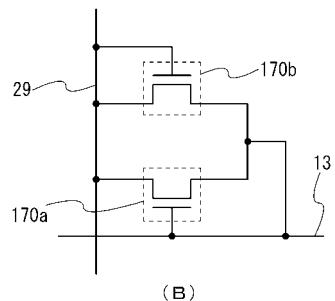

図4(A)は保護回路の一例を示す平面図であり、(B)はその等価回路図を示す。また、図4中に示されるQ1-Q2切断線に対応した断面図を図5に示す。以下の説明では図4及び図5を参照して保護回路の一構成例を説明する。

10

## 【0031】

図4の非線形素子170a及び非線形素子170bは、走査線13と同じ層で形成されるゲート電極111及びゲート電極16を有している。ゲート電極111及びゲート電極16上にはゲート絶縁膜102が形成されている。ゲート絶縁膜102上にはゲート電極111上で相対するように第1配線層117a及び第2配線層117bが設けられている。なお、非線形素子170a及び非線形素子170bは主要部において同じ構成を有している。

20

## 【0032】

本発明の一態様ではゲート絶縁膜102に設けたコンタクトホール128を介して、ゲート電極111と同じ層で形成される走査線13と、非線形素子170aの第三端子(ドレン)とを直接接続することで、接続に伴う界面の形成を一つに抑制できるだけでなく、接続に伴うコンタクトホールの形成を一つに抑制できる。

20

## 【0033】

酸化物半導体層113は、ゲート電極111上で相対する第1配線層117a及び第2配線層117bの間を被覆するように設けられている。すなわち酸化物半導体層113は、ゲート電極111と重疊し、ゲート絶縁膜102、第1配線層117a及び第2配線層117bと接するように設けられている。

30

## 【0034】

酸化物半導体膜は成膜条件により導電率が変化する。ここでは、膜中の酸素濃度が高くなる条件で成膜し、導電率を低くする。また、導電率を低くすることによってオフ電流の低減を図ることができるために、オン・オフ比の高い薄膜トランジスタを得ることができる。

30

## 【0035】

本明細書中で用いる酸化物半導体は、 $InMnO_3 (ZnO)_m (m > 0)$ で表記される薄膜を形成し、その薄膜を半導体層として用いた非線形素子および薄膜トランジスタを作製する。なお、Mは、Ga、Fe、Ni、Mn及びCoから選ばれた一の金属元素又は複数の金属元素を示す。例えばMとして、Gaの場合があることの他、GaとNi又はGaとFeなど、Ga以外の上記金属元素が含まれる場合がある。また、上記酸化物半導体において、Mとして含まれる金属元素の他に、不純物元素としてFe、Niその他の遷移金属元素、又は該遷移金属の酸化物が含まれているものがある。本明細書においてはこの薄膜をIn-Ga-Zn-O系非単結晶膜とも呼ぶ。

40

## 【0036】

誘導結合プラズマ質量分析法( ICP-MS : Inductively Coupled Plasma Mass Spectrometry )によるIn-Ga-Zn-O系非単結晶膜の測定結果を表1に示す。酸化インジウム(  $In_2O_3$  )と酸化ガリウム(  $Ga_2O_3$  )と酸化亜鉛(  $ZnO$  )の組成比を  $1:1:1$  ( =  $In_2O_3:Ga_2O_3:ZnO$  )としたターゲット(  $In:Ga:Zn = 1:1:0.5$  )を用い、スパッタ法でのアルゴンガス流量を  $40\text{ sccm}$  とした条件1で得られた酸化物半導体膜を測定した結果は、 $InGa_{0.95}Zn_{0.41}O_{3.33}$  であった。また、スパッタ法でのアル

50

ゴンガス流量を 10 sccm、酸素を 5 sccm とした条件 2 で得られた酸化物半導体膜を測定した結果は、 $\text{InGa}_{0.94}\text{Zn}_{0.40}\text{O}_{3.31}$  であった。

【0037】

【表 1】

| 流量比<br>Ar/O <sub>2</sub> | 組成(atomic%) |      |     |      | 組成式                                                 |

|--------------------------|-------------|------|-----|------|-----------------------------------------------------|

|                          | In          | Ga   | Zn  | O    |                                                     |

| 40/0                     | 17.6        | 16.7 | 7.2 | 58.6 | $\text{InGa}_{0.95}\text{Zn}_{0.41}\text{O}_{3.33}$ |

| 10/5                     | 17.7        | 16.7 | 7   | 58.6 | $\text{InGa}_{0.94}\text{Zn}_{0.40}\text{O}_{3.31}$ |

【0038】

10

また、測定方法をラザフォード後方散乱分析法 (RBS : Rutherford Backscattering Spectrometry) に変えて定量化した結果を表 2 に示す。

【0039】

【表 2】

| 流量比<br>Ar/O <sub>2</sub> | 組成(atomic%) |      |     |      |     | 組成式                                                 |

|--------------------------|-------------|------|-----|------|-----|-----------------------------------------------------|

|                          | In          | Ga   | Zn  | O    | Ar  |                                                     |

| 40/0                     | 17          | 15.8 | 7.5 | 59.4 | 0.3 | $\text{InGa}_{0.93}\text{Zn}_{0.44}\text{O}_{3.49}$ |

| 10/5                     | 16          | 14.7 | 7.2 | 61.7 | 0.4 | $\text{InGa}_{0.92}\text{Zn}_{0.45}\text{O}_{3.86}$ |

20

【0040】

条件 1 の試料を RBS 分析で測定した結果、酸化物半導体膜は、 $\text{InGa}_{0.93}\text{Zn}_{0.44}\text{O}_{3.49}$  であった。また、条件 2 の試料を RBS 分析で測定した結果、酸化物半導体膜は、 $\text{InGa}_{0.92}\text{Zn}_{0.45}\text{O}_{3.86}$  であった。

【0041】

In - Ga - Zn - O 系非単結晶膜の結晶構造はアモルファス構造が X 線回折 (XRD : X-ray diffraction) の分析によりアモルファス構造が観察された。なお、測定したサンプルの In - Ga - Zn - O 系非単結晶膜は、スパッタ法で成膜した後、加熱処理を 200 ~ 500 、代表的には 300 ~ 400 で 10 分 ~ 100 分行っている。また、薄膜トランジスタの電気特性もゲート電圧  $\pm 20\text{ V}$  において、オン・オフ比が  $10^9$  以上、移動度が  $10\text{ cm}^2/\text{V}\cdot\text{s}$  以上のものを作製することができる。

30

【0042】

酸化物半導体層 113 上には層間絶縁膜 107 が設けられている。層間絶縁膜 107 は、酸化シリコン又は酸化アルミニウムなどの酸化物で形成される。また、酸化シリコン又は酸化アルミニウム上に窒化シリコン、窒化アルミニウム、酸化窒化シリコン又は酸化窒化アルミニウムを積層することで、保護膜としてより機能を高めることができる。

【0043】

いずれにしても、酸化物半導体層 113 と接する層間絶縁膜 107 を酸化物とすることで、酸化物半導体層 113 から酸素が引き抜かれ、酸素欠乏型に変質してしまうことを防ぐことができる。また、酸化物半導体層 113 が窒化物による絶縁層と直接的に接しない構成とすることで、窒化物中の水素が拡散して酸化物半導体層 113 に水酸基などに起因する欠陥を生成するのを防ぐことができる。

40

【0044】

このように、本実施の形態によれば、酸化物半導体により構成される保護回路を有する表示装置を得ることができる。また、ゲート絶縁膜 102 に設けたコンタクトホール 128 を介して、ゲート電極 111 と同じ層で形成される走査線 13 と、非線形素子 170a の第三端子 (ドレイン) とを直接接続することで、接続に伴う界面の形成を一つに抑制できるだけでなく、接続のためのコンタクトホールの形成を一つに抑制できる。その結果、保護回路の機能を高め動作の安定化を図ることができるだけでなく、保護回路の占有面積を

50

小さくして、表示装置の小型化を図ることができる。特に、保護回路を構成する非線形素子が3つ、4つに増えるほど、接続に伴う界面の形成とコンタクトホールの形成を抑制する効果が大きくなる。

【0045】

なお、図4及び図5では走査線13に設けられる保護回路の一例を示すが、同様の保護回路を信号線、容量バス線などに適用することができる。

【0046】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0047】

(実施の形態2)

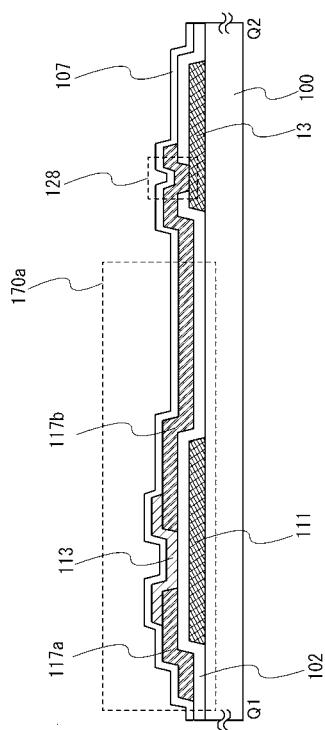

本実施の形態では、実施の形態1において図4(A)に示した保護回路の作製工程の一様態を図6及び図7を参照して説明する。図6及び図7は図4(A)中のQ1-Q2切断線に対応した断面図を表している。

【0048】

図6(A)において、透光性を有する基板100には市販されているバリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス及びアルミニノシリケートガラスなどのガラス基板を用いることができる。例えば、成分比としてホウ酸( $B_2O_3$ )よりも酸化バリウム( $BaO$ )を多く含み、歪み点が730以上ガラス基板を用いると好ましい。酸化物半導体層を700程度の高温で熱処理する場合でも、ガラス基板が歪まないで済むからである。

【0049】

次に、ゲート電極111および走査線13を含むゲート配線、容量配線および端子部の端子となる導電膜を基板100全面に成膜する。導電膜は、アルミニウム(A1)や銅(Cu)などの低抵抗導電性材料で形成することが望ましいが、A1単体では耐熱性が劣り、また腐蝕しやすい等の問題点があるので耐熱性導電性材料と組み合わせて形成する。耐熱性導電性材料としては、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、モリブデン(Mo)、クロム(Cr)、Nd(ネオジム)、Sc(スカンジウム)から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜、または上述した元素を成分とする窒化物で形成する。

【0050】

ゲート電極111及び走査線13を含むゲート配線となる導電膜は厚さ50nm以上300nm以下で形成する。ゲート電極111及び走査線13を含むゲート配線となる導電膜の厚さを300nm以下とすることで、後に形成される半導体膜や配線の段切れ防止が可能である。また、ゲート電極111及び走査線13を含むゲート配線となる導電膜の厚さを150nm以上とすることで、ゲート電極の抵抗を低減することが可能であり、大面積化が可能である。

【0051】

なお、ここでは基板100全面に導電膜としてアルミニウムを主成分とする膜とチタン膜をスパッタリング法により積層して成膜する。

【0052】

次いで、本実施の形態における第1のフォトマスクを用いて形成したレジストマスクを使い、基板上に形成された導電膜の不要な部分をエッティングして除去して配線及び電極(ゲート電極111および走査線13を含むゲート配線、容量配線、及び端子)を形成する。このとき少なくともゲート電極111の端部にテーパー形状が形成されるようにエッティングする。この段階での断面図を図6(A)に示す。

【0053】

次にゲート絶縁膜102を形成する。ゲート絶縁膜102として利用できる絶縁膜としては、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化アルミニウム、酸化マグネシウム、窒化アルミニウム、酸化イットリウム、酸化ハフニウム、酸化タンタル

10

20

30

40

50

膜をその例に挙げることができる。

【0054】

ここでは、酸化窒化珪素膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、濃度範囲として酸素が55～65原子%、窒素が1～20原子%、Siが25～35原子%、水素が0.1～10原子%の範囲で含まれるものという。また、窒化酸化珪素膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、濃度範囲として酸素が15～30原子%、窒素が20～35原子%、Siが25～35原子%、水素が15～25原子%の範囲で含まれるものという。

【0055】

ゲート絶縁膜は単層であっても、絶縁膜を2層または3層積層して形成してもよい。例えば、基板に接するゲート絶縁膜を窒化珪素膜、または窒化酸化珪素膜を用いて形成することで、基板とゲート絶縁膜の密着力が高まり、基板としてガラス基板を用いた場合、基板からの不純物が酸化物半導体層に拡散するのを防止することが可能であり、さらにゲート電極111及び走査線13を含むゲート配線の酸化を防止できる。即ち、膜剥れを防止することができると共に、後に形成される薄膜トランジスタの電気特性を向上させることができる。

【0056】

また、ゲート絶縁膜102の厚さは50～250nmとする。ゲート絶縁膜の厚さが50nm以上であると、ゲート電極111及び走査線13を含むゲート配線の凹凸を被覆できるため好ましい。ここでは、ゲート絶縁膜102としてプラズマCVD法またはスパッタリング法により100nmの厚みの酸化珪素膜を成膜する。

【0057】

次に、本実施の形態における第2のフォトマスクを用いて形成したレジストマスクにより、ゲート絶縁膜102をエッチングして、走査線13に達するコンタクトホール128を形成する。この段階での断面図を図6(B)に示す。

【0058】

次に、ソース電極層及びドレイン電極層となる導電膜をスパッタ法や真空蒸着法で形成する。導電膜の材料としては、Al、Cr、Ta、Ti、Mo、Wから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。

【0059】

また、200～600の熱処理を行う場合には、この熱処理に耐える耐熱性を導電膜に持たせることが好ましい。Al単体では耐熱性が劣り、また腐蝕しやすい等の問題点があるので耐熱性導電性材料と組み合わせて形成する。Alと組み合わせる耐熱性導電性材料としては、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、Nd(ネオジム)、Sc(スカンジウム)から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜、または上述した元素を成分とする窒化物で形成する。

【0060】

ここでは、導電膜としてTi膜と、そのTi膜上に重ねてNdを含むアルミニウム(Al-Nd)膜を積層し、さらにその上にTi膜を成膜する3層構造とする。また、導電膜は、2層構造としてもよく、アルミニウム膜上にチタン膜を積層してもよい。また、導電膜は、シリコンを含むアルミニウム膜の単層構造や、チタン膜の単層構造としてもよい。

【0061】

なお、ゲート絶縁膜102にはコンタクトホール128が形成されているため、ソース電極層及びドレイン電極層となる導電膜は成膜の際にコンタクトホール128を介して走査線13と接続する。

【0062】

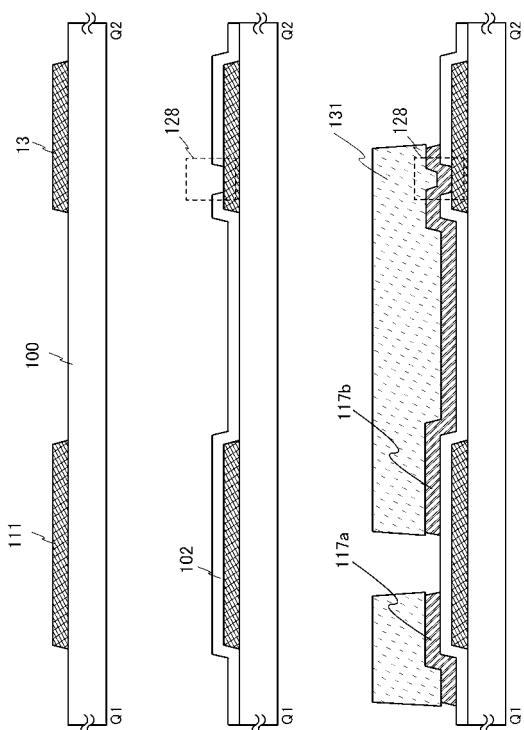

次に、本実施の形態における第3のフォトマスクを用いて導電膜上にレジストマスク131を形成し、エッチングにより不要な部分を除去してソース電極層及びドレイン電極層(

10

20

30

40

50

117a、117b)を形成する。この際エッティング方法としてウェットエッティングまたはドライエッティングを用いる。ここでは、SiCl<sub>4</sub>とCl<sub>2</sub>とBCl<sub>3</sub>の混合ガスを反応ガスとしたドライエッティングにより、Ti膜とAl-Nd膜とTi膜を順次積層した導電膜をエッティングしてソース電極層及びドレイン電極層(117a、117b)を形成する。この段階での断面図を図6(C)に示す。

#### 【0063】

次に、レジストマスクを除去した後、プラズマ処理を行う。ここでは酸素ガスとアルゴンガスを導入してプラズマを発生させる逆スパッタを行い、露出しているゲート絶縁膜に酸素ラジカル又は酸素を照射する。こうして、表面に付着しているゴミを除去する。この段階での断面図を図7(A)に示す。

10

#### 【0064】

次いで、プラズマ処理後、プラズマ処理された基板を大気に曝すことなく酸化物半導体膜を成膜する。プラズマ処理後、大気に曝すことなく酸化物半導体膜を成膜することは、ゲート絶縁膜102と酸化物半導体膜の界面にゴミや水分を付着させない点で有用である。なお、酸化物半導体膜の成膜は、先に逆スパッタを行ったチャンバーと同一チャンバーを用いてもよいし、大気に曝すことなく成膜できるのであれば、先に逆スパッタを行ったチャンバーと異なるチャンバーで成膜してもよい。

#### 【0065】

ここでは、直径8インチのIn、Ga、及びZnを含む酸化物半導体ターゲット(組成比として、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1)を用いて、基板とターゲットの間との距離を170mm、圧力0.4Pa、直流(DC)電源0.5kW、酸素雰囲気下(又は酸素ガス流量がアルゴンガス流量と等しいかそれ以上)で成膜する。なお、パルス直流(DC)電源を用いると、ごみが軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜の膜厚は、5nm～200nmとする。本実施の形態では酸化物半導体膜の膜厚は、100nmとする。

20

#### 【0066】

酸化物半導体膜は、膜中の酸素濃度が高くなる条件で成膜する。多くの酸素を酸化物半導体膜中に含ませることによって、導電率を低くすることができます。また、多くの酸素を酸化物半導体膜中に含ませることによってオフ電流の低減を図ることができるため、オン・オフ比の高い薄膜トランジスタを得ることができる。

30

#### 【0067】

次いで、200～600、代表的には300～500の熱処理を行うことが好ましい。ここでは炉に入れ、窒素雰囲気下または大気雰囲気下で350、1時間の熱処理を行う。この熱処理によりIn-Ga-Zn-O系非単結晶膜の原子レベルの再配列が行われる。この熱処理によりキャリアの移動を阻害する歪が解放されるため、ここでの熱処理(光アニールも含む)は重要である。なお、熱処理を行うタイミングは、酸化物半導体膜の成膜後であれば特に限定されず、例えば画素電極形成後に行ってもよい。

#### 【0068】

次に、本実施の形態における第4のフォトマスクを用いてレジストマスクを形成し、エッティングにより不要な部分を除去して酸化物半導体層113を形成する。ここではITOON(関東化学社製)を用いたウェットエッティングにより、酸化物半導体膜を除去して酸化物半導体層113を形成する。なお、酸化物半導体層113のエッティングは、ウェットエッティングに限定されずドライエッティングを用いてもよい。以上の工程で酸化物半導体層113をチャネル形成領域とする非線形素子170aが作製できる。この段階での断面図を図7(B)に示した。

40

#### 【0069】

さらに、酸化物半導体層113にプラズマ処理を行ってもよい。プラズマ処理を行うことにより、酸化物半導体層113のエッティングによるダメージを回復することができる。プラズマ処理はO<sub>2</sub>、N<sub>2</sub>O、好ましくは酸素を含むN<sub>2</sub>、He、Ar雰囲気下で行うことが好ましい。また、上記雰囲気にCl<sub>2</sub>、CF<sub>4</sub>を加えた雰囲気下で行ってもよい。なお

50

、プラズマ処理は、無バイアスで行うことが好ましい。

【0070】

次いで、非線形素子170aを覆う層間絶縁膜107を形成する。層間絶縁膜107はスパッタ法などを用いて得られる窒化シリコン膜、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化タンタル膜などを用いることができる。こうして4回のフォトリソグラフィー工程により、4枚のフォトマスクを使用して、複数の非線形素子を有する（本実施の形態では、170aおよび170bの二つの非線形素子を有する）保護回路を完成させることができる（この段階での断面図を図7（c）に示す。）。

【0071】

保護回路の形成に引き続き、非線形素子と共に同一のプロセスで一体形成した表示装置の画素部分の薄膜トランジスタに、画素電極を形成する。なお、画素部分の薄膜トランジスタは図示していない。第5のレジストマスクを用いて、画素部分の薄膜トランジスタのドレイン電極層に達するコンタクトホールを層間絶縁膜107に形成する。

10

【0072】

次いで、レジストマスクを除去した後、透明導電膜を成膜する。透明導電膜の材料としては、酸化インジウム（In<sub>2</sub>O<sub>3</sub>）や酸化インジウム酸化スズ合金（In<sub>2</sub>O<sub>3</sub>—SnO<sub>2</sub>、ITOと略記する）などをスパッタ法や真空蒸着法などを用いて形成する。このような材料のエッチング処理は塩酸系の溶液により行う。しかし、特にITOのエッチングは残渣が発生しやすいので、エッチング加工性を改善するために酸化インジウム酸化亜鉛合金（In<sub>2</sub>O<sub>3</sub>—ZnO）を用いても良い。

20

【0073】

次に、第6のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッチングにより透明導電膜の不要な部分を除去して画素電極を形成する。また、容量部におけるゲート絶縁膜102及び層間絶縁膜107を誘電体として、容量配線と画素電極とで保持容量を形成する。また、端子部に透明導電膜を残し、FPCとの接続に用いる電極または配線や、ソース配線の入力端子として機能する接続用の端子電極を形成する。

30

【0074】

こうして、非線形素子と同一のプロセスで一体形成した複数の薄膜トランジスタに画素電極を形成すると、nチャネル型TFTを有する画素部の作製と保護回路の作製を同時におこなうことができる。また、ゲート絶縁膜102に設けたコンタクトホール128を介して、ゲート電極111と同じ層で形成される走査線13と、非線形素子170aの第三端子（ドレイン）とを直接接続することで、接続に伴う界面の形成を一つに抑制できるだけでなく、接続のためのコンタクトホールの形成を一つに抑制できる。その結果、保護回路の機能を高め動作の安定化を図ることができるだけでなく、保護回路の占有面積を小さくして、表示装置の小型化を図ることができる。すなわち、本実施の形態に示した工程に従えば、保護回路の機能を高め動作の安定化を図ることができるだけでなく、占有面積が小さい保護回路を搭載したアクティブマトリクス型の表示装置用基板を作製できる。

30

【0075】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

40

【0076】

（実施の形態3）

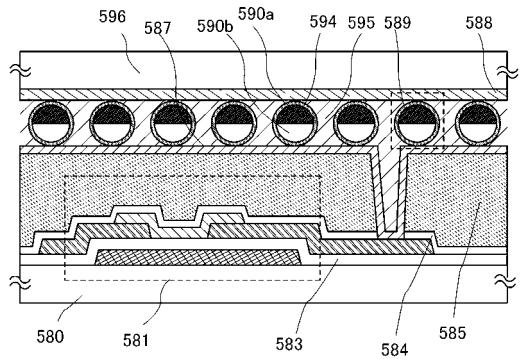

本実施の形態では、本発明の一態様を適用した表示装置として同一基板上に保護回路と、画素部に配置する薄膜トランジスタを有する電子ペーパーの例を示す。

【0077】

図10は、本発明の一態様を適用した表示装置の例としてアクティブマトリクス型の電子ペーパーを示す。半導体装置に用いられる薄膜トランジスタ581としては、実施の形態2で示す非線形素子と同様に作製でき、In、Ga、及びZnを含む酸化物半導体を半導体層に用いた電気特性の高い薄膜トランジスタである。

【0078】

50

図10の電子ペーパーは、ツイストボール表示方式を用いた表示装置の例である。ツイストボール表示方式とは、白と黒に塗り分けられた球形粒子を表示素子に用いる電極層である第1の電極層及び第2の電極層の間に配置し、第1の電極層及び第2の電極層に電位差を生じさせての球形粒子の向きを制御することにより、表示を行う方法である。

【0079】

薄膜トランジスタ581はボトムゲート構造の薄膜トランジスタであり、絶縁層585に形成する開口を介して、ソース電極層又はドレイン電極層が第1の電極層587と電気的に接続している。第1の電極層587と第2の電極層588との間には黒色領域590a及び白色領域590bを有し、周りに液体で満たされているキャビティ594を含む球形粒子589が設けられており、球形粒子589の周囲は樹脂等の充填材595で充填されている(図10参照。)。

10

【0080】

また、ツイストボールの代わりに、電気泳動素子を用いることも可能である。透明な液体と、正に帯電した白い微粒子と負に帯電した黒い微粒子とを封入した直径 $10\text{ }\mu\text{m} \sim 20\text{ }\mu\text{m}$ 程度のマイクロカプセルを用いる。第1の電極層と第2の電極層との間に設けられるマイクロカプセルは、第1の電極層と第2の電極層によって、電場が与えられると、白い微粒子と、黒い微粒子が逆の方向に移動し、白または黒を表示することができる。この原理を応用した表示素子が電気泳動表示素子であり、一般的に電子ペーパーとよばれている。電気泳動表示素子は、液晶表示素子に比べて反射率が高いため、補助ライトは不要であり、また消費電力が小さく、薄暗い場所でも表示部を認識することが可能である。また、表示部に電源が供給されない場合であっても、一度表示した像を保持することが可能である。従って、例えば電源供給源となる電波発信源から表示機能付き半導体装置(単に表示装置、又は表示装置を具備する半導体装置ともいう)を遠ざけた場合であっても、表示された像を保存しておくことが可能となる。

20

【0081】

以上の工程により作製した電子ペーパーが搭載している保護回路は、第1配線層又は第2配線層の導電層がゲート電極もしくはゲート電極と同じ層で形成した配線に直接接続する非線形素子を用いており、動作の安定化が図られている。また、保護回路の占有面積が小さいため、信頼性が高く小型化された電子ペーパーを作製することができる。

30

【0082】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0083】

(実施の形態4)

本実施の形態では、本発明の一態様の半導体装置の一例である表示装置において、同一基板上に少なくとも保護回路と、駆動回路の一部と、画素部に配置する薄膜トランジスタを作製する例について図11乃至図16を用いて以下に説明する。

【0084】

保護回路と同一基板上の画素部に配置する薄膜トランジスタは、実施の形態2で示す非線形素子と同様に形成する。また、形成した薄膜トランジスタはnチャネル型TFTであるため、駆動回路のうち、nチャネル型TFTで構成することができる駆動回路の一部を画素部の薄膜トランジスタと同一基板上に形成する。

40

【0085】

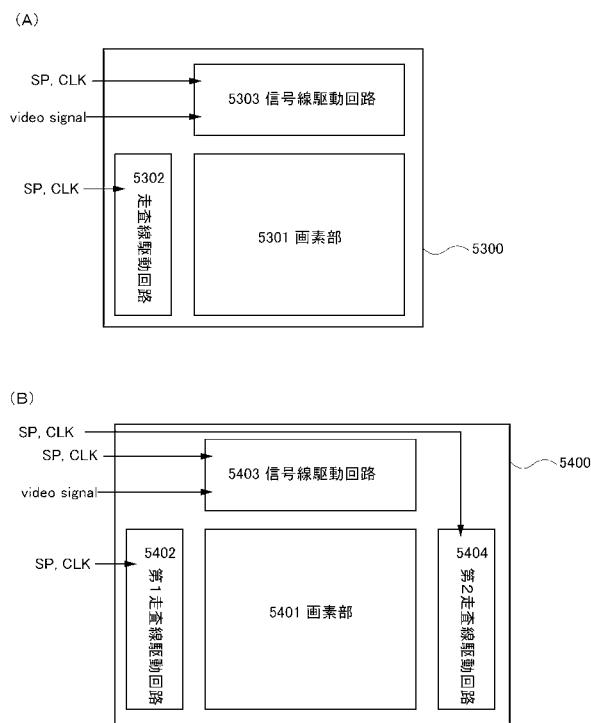

本発明の一態様の半導体装置の一例であるアクティブマトリクス型液晶表示装置のブロック図の一例を図11(A)に示す。図11(A)に示す表示装置は、基板5300上に表示素子を備えた画素を複数有する画素部5301と、各画素を選択する走査線駆動回路5302と、選択された画素へのビデオ信号の入力を制御する信号線駆動回路5303とを有する。

【0086】

画素部5301は、信号線駆動回路5303から列方向に伸張して配置された複数の信号

50

線 S 1 ~ S m ( 図示せず。 ) により信号線駆動回路 5 3 0 3 と接続され、走査線駆動回路 5 3 0 2 から行方向に伸張して配置された複数の走査線 G 1 ~ G n ( 図示せず。 ) により走査線駆動回路 5 3 0 2 と接続され、信号線 S 1 ~ S m 並びに走査線 G 1 ~ G n に対応してマトリクス状に配置された複数の画素 ( 図示せず。 ) を有する。そして、各画素は、信号線 S j ( 信号線 S 1 ~ S m のうちいずれか一 ) 、走査線 G i ( 走査線 G 1 ~ G n のうちいずれか一 ) と接続される。

【 0 0 8 7 】

また、実施の形態 2 で示す非線形素子と共に同様の方法で形成できる薄膜トランジスタは、n チャネル型 TFT であり、n チャネル型 TFT で構成する信号線駆動回路について図 12 を用いて説明する。

10

【 0 0 8 8 】

図 12 に示す信号線駆動回路は、ドライバ IC 5 6 0 1 、スイッチ群 5 6 0 2 \_ 1 ~ 5 6 0 2 \_ M 、第 1 の配線 5 6 1 1 、第 2 の配線 5 6 1 2 、第 3 の配線 5 6 1 3 及び配線 5 6 2 1 \_ 1 ~ 5 6 2 1 \_ M を有する。スイッチ群 5 6 0 2 \_ 1 ~ 5 6 0 2 \_ M それぞれは、第 1 の薄膜トランジスタ 5 6 0 3 a 、第 2 の薄膜トランジスタ 5 6 0 3 b 及び第 3 の薄膜トランジスタ 5 6 0 3 c を有する。

20

【 0 0 8 9 】

ドライバ IC 5 6 0 1 は第 1 の配線 5 6 1 1 、第 2 の配線 5 6 1 2 、第 3 の配線 5 6 1 3 及び配線 5 6 2 1 \_ 1 ~ 5 6 2 1 \_ M に接続される。そして、スイッチ群 5 6 0 2 \_ 1 ~ 5 6 0 2 \_ M それぞれは、第 1 の配線 5 6 1 1 、第 2 の配線 5 6 1 2 、第 3 の配線 5 6 1 3 及びスイッチ群 5 6 0 2 \_ 1 ~ 5 6 0 2 \_ M それぞれに対応した配線 5 6 2 1 \_ 1 ~ 5 6 2 1 \_ M に接続される。そして、配線 5 6 2 1 \_ 1 ~ 5 6 2 1 \_ M それぞれは、第 1 の薄膜トランジスタ 5 6 0 3 a 、第 2 の薄膜トランジスタ 5 6 0 3 b 及び第 3 の薄膜トランジスタ 5 6 0 3 c を介して、3 つの信号線に接続される。例えば、J 列目の配線 5 6 2 1 \_ J ( 配線 5 6 2 1 \_ 1 ~ 配線 5 6 2 1 \_ M のうちいずれか一 ) は、スイッチ群 5 6 0 2 \_ J が有する第 1 の薄膜トランジスタ 5 6 0 3 a 、第 2 の薄膜トランジスタ 5 6 0 3 b 及び第 3 の薄膜トランジスタ 5 6 0 3 c を介して、信号線 S j - 1 、信号線 S j 、信号線 S j + 1 に接続される。

20

【 0 0 9 0 】

なお、第 1 の配線 5 6 1 1 、第 2 の配線 5 6 1 2 、第 3 の配線 5 6 1 3 には、それぞれ信号が入力される。

30

【 0 0 9 1 】

なお、ドライバ IC 5 6 0 1 は、単結晶基板上に形成されていることが望ましい。さらに、スイッチ群 5 6 0 2 \_ 1 ~ 5 6 0 2 \_ M は、画素部と同一基板上に形成されていることが望ましい。したがって、ドライバ IC 5 6 0 1 とスイッチ群 5 6 0 2 \_ 1 ~ 5 6 0 2 \_ M とは FPC などを介して接続するとよい。

40

【 0 0 9 2 】

次に、図 12 に示した信号線駆動回路の動作について、図 13 のタイミングチャートを参照して説明する。なお、図 13 のタイミングチャートは、i 行目の走査線 G i が選択されている場合のタイミングチャートを示している。さらに、i 行目の走査線 G i の選択期間は、第 1 のサブ選択期間 T 1 、第 2 のサブ選択期間 T 2 及び第 3 のサブ選択期間 T 3 に分割されている。さらに、図 12 の信号線駆動回路は、他の行の走査線が選択されている場合でも図 13 と同様の動作をする。

【 0 0 9 3 】

なお、図 13 のタイミングチャートは、J 列目の配線 5 6 2 1 \_ J が第 1 の薄膜トランジスタ 5 6 0 3 a 、第 2 の薄膜トランジスタ 5 6 0 3 b 及び第 3 の薄膜トランジスタ 5 6 0 3 c を介して、信号線 S j - 1 、信号線 S j 、信号線 S j + 1 に接続される場合について示している。

【 0 0 9 4 】

なお、図 13 のタイミングチャートは、i 行目の走査線 G i が選択されるタイミング、第

50

1 の薄膜トランジスタ 5 6 0 3 a のオン・オフのタイミング 5 7 0 3 a 、第 2 の薄膜トランジスタ 5 6 0 3 b のオン・オフのタイミング 5 7 0 3 b 、第 3 の薄膜トランジスタ 5 6 0 3 c のオン・オフのタイミング 5 7 0 3 c 及び J 列目の配線 5 6 2 1 \_ J に入力される信号 5 7 2 1 \_ J を示している。

【 0 0 9 5 】

なお、配線 5 6 2 1 \_ 1 ~ 配線 5 6 2 1 \_ M には第 1 のサブ選択期間 T 1 、第 2 のサブ選択期間 T 2 及び第 3 のサブ選択期間 T 3 において、それぞれ別のビデオ信号が入力される。例えば、第 1 のサブ選択期間 T 1 において配線 5 6 2 1 \_ J に入力されるビデオ信号は信号線 S j - 1 に入力され、第 2 のサブ選択期間 T 2 において配線 5 6 2 1 \_ J に入力されるビデオ信号は信号線 S j に入力され、第 3 のサブ選択期間 T 3 において配線 5 6 2 1 \_ J に入力されるビデオ信号は信号線 S j + 1 に入力される。さらに、第 1 のサブ選択期間 T 1 、第 2 のサブ選択期間 T 2 及び第 3 のサブ選択期間 T 3 において、配線 5 6 2 1 \_ J に入力されるビデオ信号をそれぞれ Data \_ j - 1 、 Data \_ j 、 Data \_ j + 1 とする。

10

【 0 0 9 6 】

図 1 3 に示すように、第 1 のサブ選択期間 T 1 において第 1 の薄膜トランジスタ 5 6 0 3 a がオンし、第 2 の薄膜トランジスタ 5 6 0 3 b 及び第 3 の薄膜トランジスタ 5 6 0 3 c がオフする。このとき、配線 5 6 2 1 \_ J に入力される Data \_ j - 1 が、第 1 の薄膜トランジスタ 5 6 0 3 a を介して信号線 S j - 1 に入力される。第 2 のサブ選択期間 T 2 では、第 2 の薄膜トランジスタ 5 6 0 3 b がオンし、第 1 の薄膜トランジスタ 5 6 0 3 a 及び第 3 の薄膜トランジスタ 5 6 0 3 c がオフする。このとき、配線 5 6 2 1 \_ J に入力される Data \_ j が、第 2 の薄膜トランジスタ 5 6 0 3 b を介して信号線 S j に入力される。第 3 のサブ選択期間 T 3 では、第 3 の薄膜トランジスタ 5 6 0 3 c がオンし、第 1 の薄膜トランジスタ 5 6 0 3 a 及び第 2 の薄膜トランジスタ 5 6 0 3 b がオフする。このとき、配線 5 6 2 1 \_ J に入力される Data \_ j + 1 が、第 3 の薄膜トランジスタ 5 6 0 3 c を介して信号線 S j + 1 に入力される。

20

【 0 0 9 7 】

以上のことから、図 1 2 の信号線駆動回路は、1 ゲート選択期間を 3 つに分割することで、1 ゲート選択期間中に 1 つの配線 5 6 2 1 から 3 つの信号線にビデオ信号を入力することができる。したがって、図 1 2 の信号線駆動回路は、ドライバ I C 5 6 0 1 が形成される基板と、画素部が形成されている基板との接続数を信号線の数に比べて約 1 / 3 にすることができる。接続数が約 1 / 3 になることによって、図 1 2 の信号線駆動回路は、信頼性、歩留まりなどを向上できる。

30

【 0 0 9 8 】

なお、図 1 2 のように、1 ゲート選択期間を複数のサブ選択期間に分割し、複数のサブ選択期間それぞれにおいて、ある 1 つの配線から複数の信号線それぞれにビデオ信号を入力することができれば、薄膜トランジスタの配置や数、駆動方法などは限定されない。

【 0 0 9 9 】

例えば、3 つ以上のサブ選択期間それぞれにおいて 1 つの配線から 3 つ以上の信号線それぞれにビデオ信号を入力する場合は、薄膜トランジスタ及び薄膜トランジスタを制御するための配線を追加すればよい。ただし、1 ゲート選択期間を 4 つ以上のサブ選択期間に分割すると、1 つのサブ選択期間が短くなる。したがって、1 ゲート選択期間は、2 つ又は 3 つのサブ選択期間に分割されることが望ましい。

40

【 0 1 0 0 】

別の例として、図 1 4 のタイミングチャートに示すように、1 つの選択期間をプリチャージ期間 T p 、第 1 のサブ選択期間 T 1 、第 2 のサブ選択期間 T 2 、第 3 のサブ選択期間 T 3 に分割してもよい。さらに、図 1 4 のタイミングチャートは、i 行目の走査線 G i が選択されるタイミング、第 1 の薄膜トランジスタ 5 6 0 3 a のオン・オフのタイミング 5 8 0 3 a 、第 2 の薄膜トランジスタ 5 6 0 3 b のオン・オフのタイミング 5 8 0 3 b 、第 3 の薄膜トランジスタ 5 6 0 3 c のオン・オフのタイミング 5 8 0 3 c 及び J 列目の配線 5

50

621\_J に入力される信号 5821\_J を示している。図 14 に示すように、プリチャージ期間 Tp において第 1 の薄膜トランジスタ 5603a、第 2 の薄膜トランジスタ 5603b 及び第 3 の薄膜トランジスタ 5603c がオンする。このとき、配線 5621\_J に入力されるプリチャージ電圧 Vp が第 1 の薄膜トランジスタ 5603a、第 2 の薄膜トランジスタ 5603b 及び第 3 の薄膜トランジスタ 5603c を介してそれぞれ信号線 Sj-1、信号線 Sj、信号線 Sj+1 に入力される。第 1 のサブ選択期間 T1 において第 1 の薄膜トランジスタ 5603a がオンし、第 2 の薄膜トランジスタ 5603b 及び第 3 の薄膜トランジスタ 5603c がオフする。このとき、配線 5621\_J に入力される Data\_j-1 が、第 1 の薄膜トランジスタ 5603a を介して信号線 Sj-1 に入力される。第 2 のサブ選択期間 T2 では、第 2 の薄膜トランジスタ 5603b がオンし、第 1 の薄膜トランジスタ 5603a 及び第 3 の薄膜トランジスタ 5603c がオフする。このとき、配線 5621\_J に入力される Data\_j が、第 2 の薄膜トランジスタ 5603b を介して信号線 Sj に入力される。第 3 のサブ選択期間 T3 では、第 3 の薄膜トランジスタ 5603c がオンし、第 1 の薄膜トランジスタ 5603a 及び第 2 の薄膜トランジスタ 5603b がオフする。このとき、配線 5621\_J に入力される Data\_j+1 が、第 3 の薄膜トランジスタ 5603c を介して信号線 Sj+1 に入力される。

10

20

30

40

50

#### 【0101】

以上のことから、図 14 のタイミングチャートを適用した図 12 の信号線駆動回路は、サブ選択期間の前にプリチャージ選択期間を設けることによって、信号線をプリチャージできるため、画素へのビデオ信号の書き込みを高速に行うことができる。なお、図 14 において、図 13 と同様なものに関しては共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

20

30

#### 【0102】

また、走査線駆動回路の構成について説明する。走査線駆動回路は、シフトレジスタ、バッファを有している。また場合によってはレベルシフタを有していても良い。走査線駆動回路において、シフトレジスタにクロック信号 (CLK) 及びスタートパルス信号 (SP) が入力されることによって、選択信号が生成される。生成された選択信号はバッファにおいて緩衝増幅され、対応する走査線に供給される。走査線には、1 ライン分の画素のトランジスタのゲート電極が接続されている。そして、1 ライン分の画素のトランジスタを一斉に ON にしなくてはならないので、バッファは大きな電流を流すことが可能なものが用いられる。

30

#### 【0103】

走査線駆動回路の一部に用いるシフトレジスタの一形態について図 15 及び図 16 を用いて説明する。

30

#### 【0104】

図 15 にシフトレジスタの回路構成を示す。図 15 に示すシフトレジスタは、フリップフロップ 5701\_1 ~ 5701\_n という複数のフリップフロップで構成される。また、第 1 のクロック信号、第 2 のクロック信号、スタートパルス信号、リセット信号が入力されて動作する。

40

#### 【0105】

図 15 のシフトレジスタの接続関係について説明する。図 15 のシフトレジスタは、i 段目のフリップフロップ 5701\_i (フリップフロップ 5701\_1 ~ 5701\_n のうちいずれか一) は、図 16 に示した第 1 の配線 5501 が第 7 の配線 5717\_i-1 に接続され、図 16 に示した第 2 の配線 5502 が第 7 の配線 5717\_i+1 に接続され、図 16 に示した第 3 の配線 5503 が第 7 の配線 5717\_i に接続され、図 16 に示した第 6 の配線 5506 が第 5 の配線 5715 に接続される。

40

#### 【0106】

また、図 16 に示した第 4 の配線 5504 が奇数段目のフリップフロップでは第 2 の配線 5712 に接続され、偶数段目のフリップフロップでは第 3 の配線 5713 に接続され、図 16 に示した第 5 の配線 5505 が第 4 の配線 5714 に接続される。

50

## 【0107】

ただし、1段目のフリップフロップ5701\_1の図16に示す第1の配線5501は第1の配線5711に接続され、n段目のフリップフロップ5701\_nの図16に示す第2の配線5502は第6の配線5716に接続される。

## 【0108】

なお、第1の配線5711、第2の配線5712、第3の配線5713、第6の配線5716を、それぞれ第1の信号線、第2の信号線、第3の信号線、第4の信号線と呼んでもよい。さらに、第4の配線5714、第5の配線5715を、それぞれ第1の電源線、第2の電源線と呼んでもよい。

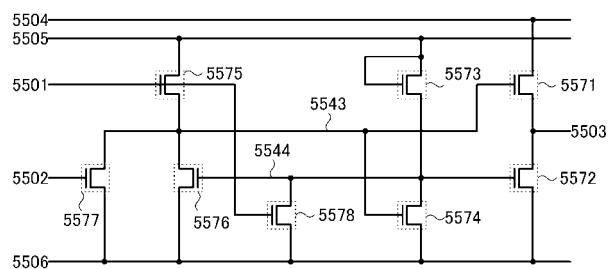

## 【0109】

次に、図15に示すフリップフロップの詳細について、図16に示す。図16に示すフリップフロップは、第1の薄膜トランジスタ5571、第2の薄膜トランジスタ5572、第3の薄膜トランジスタ5573、第4の薄膜トランジスタ5574、第5の薄膜トランジスタ5575、第6の薄膜トランジスタ5576、第7の薄膜トランジスタ5577及び第8の薄膜トランジスタ5578を有する。なお、第1の薄膜トランジスタ5571、第2の薄膜トランジスタ5572、第3の薄膜トランジスタ5573、第4の薄膜トランジスタ5574、第5の薄膜トランジスタ5575、第6の薄膜トランジスタ5576、第7の薄膜トランジスタ5577及び第8の薄膜トランジスタ5578は、nチャネル型トランジスタであり、ゲート・ソース間電圧(Vgs)がしきい値電圧(Vth)を上回ったとき導通状態になるものとする。

10

20

## 【0110】

次に、図16に示すフリップフロップの接続構成について、以下に示す。

## 【0111】

第1の薄膜トランジスタ5571の第1の電極(ソース電極またはドレイン電極の一方)が第4の配線5504に接続され、第1の薄膜トランジスタ5571の第2の電極(ソース電極またはドレイン電極の他方)が第3の配線5503に接続される。

## 【0112】

第2の薄膜トランジスタ5572の第1の電極が第6の配線5506に接続され、第2の薄膜トランジスタ5572の第2の電極が第3の配線5503に接続される。

30

## 【0113】

第3の薄膜トランジスタ5573の第1の電極が第5の配線5505に接続され、第3の薄膜トランジスタ5573の第2の電極が第2の薄膜トランジスタ5572のゲート電極に接続され、第3の薄膜トランジスタ5573のゲート電極が第5の配線5505に接続される。

## 【0114】

第4の薄膜トランジスタ5574の第1の電極が第6の配線5506に接続され、第4の薄膜トランジスタ5574の第2の電極が第2の薄膜トランジスタ5572のゲート電極に接続され、第4の薄膜トランジスタ5574のゲート電極が第1の薄膜トランジスタ5571のゲート電極に接続される。

## 【0115】

第5の薄膜トランジスタ5575の第1の電極が第5の配線5505に接続され、第5の薄膜トランジスタ5575の第2の電極が第1の薄膜トランジスタ5571のゲート電極に接続され、第5の薄膜トランジスタ5575のゲート電極が第1の配線5501に接続される。

40

## 【0116】

第6の薄膜トランジスタ5576の第1の電極が第6の配線5506に接続され、第6の薄膜トランジスタ5576の第2の電極が第1の薄膜トランジスタ5571のゲート電極に接続され、第6の薄膜トランジスタ5576のゲート電極が第2の薄膜トランジスタ5572のゲート電極に接続される。

## 【0117】

50

第7の薄膜トランジスタ5577の第1の電極が第6の配線5506に接続され、第7の薄膜トランジスタ5577の第2の電極が第1の薄膜トランジスタ5571のゲート電極に接続され、第7の薄膜トランジスタ5577のゲート電極が第2の配線5502に接続される。第8の薄膜トランジスタ5578の第1の電極が第6の配線5506に接続され、第8の薄膜トランジスタ5578の第2の電極が第2の薄膜トランジスタ5572のゲート電極に接続され、第8の薄膜トランジスタ5578のゲート電極が第1の配線5501に接続される。

【0118】

なお、第1の薄膜トランジスタ5571のゲート電極、第4の薄膜トランジスタ5574のゲート電極、第5の薄膜トランジスタ5575の第2の電極、第6の薄膜トランジスタ5576の第2の電極及び第7の薄膜トランジスタ5577の第2の電極の接続箇所をノード5543とする。さらに、第2の薄膜トランジスタ5572のゲート電極、第3の薄膜トランジスタ5573の第2の電極、第4の薄膜トランジスタ5574の第2の電極、第6の薄膜トランジスタ5576のゲート電極及び第8の薄膜トランジスタ5578の第2の電極の接続箇所をノード5544とする。

10

【0119】

なお、第1の配線5501、第2の配線5502、第3の配線5503及び第4の配線5504を、それぞれ第1の信号線、第2の信号、第3の信号線、第4の信号線と呼んでもよい。さらに、第5の配線5505を第1の電源線、第6の配線5506を第2の電源線と呼んでもよい。

20

【0120】

また、信号線駆動回路及び走査線駆動回路を、実施の形態2で示す非線形素子と共に同様の方法で形成できるnチャネル型TFTのみをつかって作製することも可能である。実施の形態2で示す非線形素子と共に同様の方法で形成できるnチャネル型TFTはトランジスタの移動度が大きいため、駆動回路の駆動周波数を高くすることが可能となる。例えば、実施の形態2で示す非線形素子と共に同様の方法で形成できるnチャネル型TFTを用いた走査線駆動回路は、高速に動作させることができるために、フレーム周波数を高くすること、または、黒画面挿入を実現することなども実現することができる。

20

【0121】

さらに、走査線駆動回路のトランジスタのチャネル幅を大きくすることや、複数の走査線駆動回路を配置することなどによって、さらに高いフレーム周波数を実現することができる。複数の走査線駆動回路を配置する場合は、偶数行の走査線を駆動する為の走査線駆動回路を片側に配置し、奇数行の走査線を駆動するための走査線駆動回路をその反対側に配置することにより、フレーム周波数を高くすることを実現することができる。また、複数の走査線駆動回路により、同じ走査線に信号を出力すると、表示装置の大型化に有利である。

30

【0122】

また、本発明の一態様を適用した半導体装置の一例であるアクティブマトリクス型発光表示装置を作製する場合、少なくとも一つの画素に複数の薄膜トランジスタを配置するため、走査線駆動回路を複数配置することが好ましい。アクティブマトリクス型発光表示装置のブロック図の一例を図11(B)に示す。

40

【0123】

図11(B)に示す発光表示装置は、基板5400上に表示素子を備えた画素を複数有する画素部5401と、各画素を選択する第1の走査線駆動回路5402及び第2の走査線駆動回路5404と、選択された画素へのビデオ信号の入力を制御する信号線駆動回路5403とを有する。

【0124】

図11(B)に示す発光表示装置の画素に入力されるビデオ信号をデジタル形式とする場合、画素はトランジスタのオンとオフの切り替えによって、発光もしくは非発光の状態となる。よって、面積階調法または時間階調法を用いて階調の表示を行うことができる。面

50

積階調法は、1画素を複数の副画素に分割し、各副画素を独立にビデオ信号に基づいて駆動させることによって、階調表示を行う駆動法である。また時間階調法は、画素が発光する期間を制御することによって、階調表示を行う駆動法である。

【0125】

発光素子は、液晶素子などに比べて応答速度が高いので、液晶素子よりも時間階調法に適している。具体的に時間階調法で表示を行なう場合、1フレーム期間を複数のサブフレーム期間に分割する。そしてビデオ信号に従い、各サブフレーム期間において画素の発光素子を発光または非発光の状態にする。複数のサブフレーム期間に分割することによって、1フレーム期間中に画素が実際に発光する期間のトータルの長さを、ビデオ信号により制御することができ、階調を表示することができる。

10

【0126】

なお、図11(B)に示す発光表示装置では、一つの画素に2つのスイッチング用TFTを配置する場合、一方のスイッチング用TFTのゲート配線である第1の走査線に入力される信号を第1走査線駆動回路5402で生成し、他方のスイッチング用TFTのゲート配線である第2の走査線に入力される信号を第2の走査線駆動回路5404で生成している例を示しているが、第1の走査線に入力される信号と、第2の走査線に入力される信号とを、共に1つの走査線駆動回路で生成するようにしても良い。また、例えば、1つの画素が有するスイッチング用TFTの数によって、スイッチング素子の動作を制御するのに用いられる走査線が、各画素に複数設けられることもあり得る。この場合、複数の走査線に入力される信号を、全て1つの走査線駆動回路で生成しても良いし、複数の各走査線駆動回路で生成しても良い。

20

【0127】

また、発光表示装置においても、駆動回路のうち、nチャネル型TFTで構成することができる駆動回路の一部を画素部の薄膜トランジスタと同一基板上に形成することができる。また、信号線駆動回路及び走査線駆動回路を実施の形態2で示す非線形素子と共に同様の方法で形成できるnチャネル型TFTのみで作製することも可能である。

30

【0128】

また、上述した駆動回路は、液晶表示装置や発光表示装置に限らず、スイッチング素子と電気的に接続する素子を利用して電子インクを駆動させる電子ペーパーに用いてもよい。電子ペーパーは、電気泳動表示装置(電気泳動ディスプレイ)も呼ばれており、紙と同じ読みやすさ、他の表示装置に比べ低消費電力、薄くて軽い形状とすることが可能という利点を有している。

40

【0129】

電気泳動ディスプレイは、様々な形態が考えられ得るが、プラスの電荷を有する第1の粒子と、マイナスの電荷を有する第2の粒子とを含むマイクロカプセルが溶媒または溶質に複数分散されたものであり、マイクロカプセルに電界を印加することによって、マイクロカプセル中の粒子を互いに反対方向に移動させて一方側に集合した粒子の色のみを表示するものである。なお、第1の粒子または第2の粒子は染料を含み、電界がない場合において移動しないものである。また、第1の粒子の色と第2の粒子の色は異なるもの(無色を含む)とする。

【0130】

このように、電気泳動ディスプレイは、誘電定数の高い物質が高い電界領域に移動する、いわゆる誘電泳動的効果を利用したディスプレイである。電気泳動ディスプレイは、液晶表示装置には必要な偏光板、対向基板も電気泳動表示装置には必要なく、厚さや重さが半減する。

【0131】

上記マイクロカプセルを溶媒中に分散させたものが電子インクと呼ばれるものであり、この電子インクはガラス、プラスチック、布、紙などの表面に印刷することができる。また、カラーフィルタや色素を有する粒子を用いることによってカラー表示も可能である。

50

【0132】

また、アクティブマトリクス基板上に適宜、二つの電極の間に挟まれるように上記マイクロカプセルを複数配置すればアクティブマトリクス型の表示装置が完成し、マイクロカプセルに電界を印加すれば表示を行うことができる。例えば、実施の形態2で示す非線形素子と共に同様の方法で形成できる薄膜トランジスタによって得られるアクティブマトリクス基板を用いることができる。

【0133】

なお、マイクロカプセル中の第1の粒子および第2の粒子は、導電体材料、絶縁体材料、半導体材料、磁性材料、液晶材料、強誘電性材料、エレクトロルミネセント材料、エレクトロクロミック材料、磁気泳動材料から選ばれた一種の材料、またはこれらの複合材料を用いればよい。

10

【0134】

以上の工程により、接続のためのコンタクトホールを減らしたことで、機能を高め動作が安定化した、占有面積が小さい保護回路を搭載した信頼性の高い表示装置を作製することができる。

【0135】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0136】

(実施の形態5)

本発明の一態様においては非線形素子と共に薄膜トランジスタを作製し、該薄膜トランジスタを画素部、さらには駆動回路に用いて表示機能を有する半導体装置（表示装置ともいう）を作製することができる。また、本発明の一態様においては非線形素子と薄膜トランジスタを駆動回路の一部または全体に用い、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

20

【0137】

表示装置は表示素子を含む。表示素子としては液晶素子（液晶表示素子ともいう）、発光素子（発光表示素子ともいう）を用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL（E l e c t r o L u m i n e s c e n c e）、有機EL等が含まれる。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体も適用することができる。

30

【0138】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。さらに本発明の一態様は、該表示装置を作製する過程における、表示素子が完成する前の形態に相当する素子基板に関し、該素子基板は、電流を表示素子に供給するための手段を複数の各画素に備える。素子基板は、具体的には、表示素子の画素電極のみが形成された状態であっても良いし、画素電極となる導電膜を成膜した後であって、エッチングして画素電極を形成する前の状態であっても良いし、あらゆる形態があつてはまる。

【0139】

なお、本明細書中における表示装置とは、画像表示デバイス、表示デバイス、もしくは光源（照明装置含む）を指す。また、コネクター、例えばFPC（F l e x i b l e p r i n t e d c i r c u i t）もしくはTAB（Tape Automated Bonding）テープもしくはTCP（Tape Carrier Package）が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG（C h i p O n G l a s s）方式によりIC（集積回路）が直接実装されたモジュールも全て表示装置に含むものとする。

40

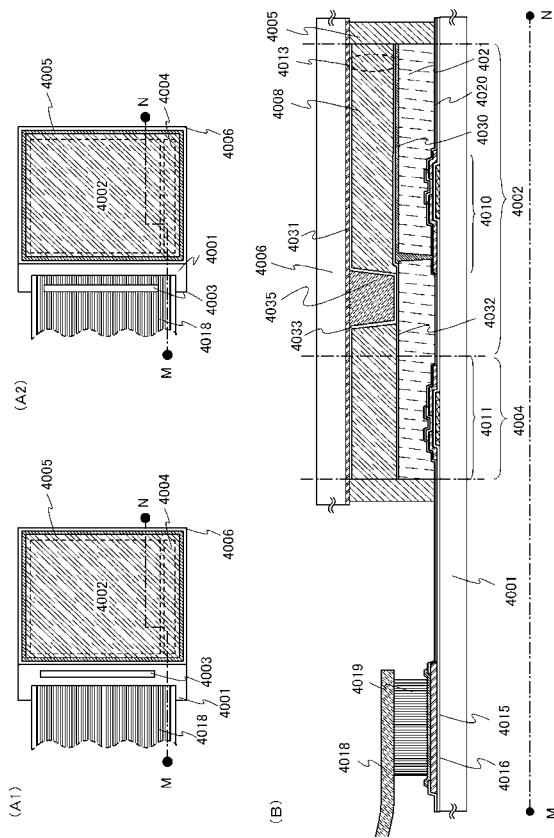

【0140】

本実施の形態では、本発明の一態様の表示装置の形態に相当する液晶表示パネルの外観及び断面について、図17を用いて説明する。図17は、非線形素子と同様に第1の基板4001上に形成されたIn、Ga、及びZnを含む酸化物半導体を半導体層に用いた電

50

気特性の高い薄膜トランジスタ 4010、4011、及び液晶素子 4013 を、第 2 の基板 4006 との間にシール材 4005 によって封止した、パネルの上面図であり、図 17 (B) は、図 17 (A1) (A2) の M-N における断面図に相当する。

【0141】

第 1 の基板 4001 上に設けられた画素部 4002 と、走査線駆動回路 4004 とを囲むようにして、シール材 4005 が設けられている。また画素部 4002 と、走査線駆動回路 4004 の上に第 2 の基板 4006 が設けられている。よって画素部 4002 と、走査線駆動回路 4004 とは、第 1 の基板 4001 とシール材 4005 と第 2 の基板 4006 とによって、液晶層 4008 と共に封止されている。また第 1 の基板 4001 上のシール材 4005 によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された信号線駆動回路 4003 が実装されている。

10

【0142】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG 方法、ワイヤボンディング方法、或いは TAB 方法などを用いることができる。図 17 (A1) は、COG 方法により信号線駆動回路 4003 を実装する例であり、図 17 (A2) は、TAB 方法により信号線駆動回路 4003 を実装する例である。

【0143】

また第 1 の基板 4001 上に設けられた画素部 4002 と、走査線駆動回路 4004 は、薄膜トランジスタを複数有しており、図 17 (B) では、画素部 4002 に含まれる薄膜トランジスタ 4010 と、走査線駆動回路 4004 に含まれる薄膜トランジスタ 4011 とを例示している。薄膜トランジスタ 4010、4011 上には絶縁層 4020、4021 が設けられている。

20

【0144】

薄膜トランジスタ 4010、4011 は、In、Ga、及びZn を含む酸化物半導体を半導体層に用いた電気特性の高い薄膜トランジスタに相当し、実施の形態 2 で示す非線形素子と共に同様の方法で、非線形素子の形成と平行して形成できる薄膜トランジスタを適用することができる。本実施の形態において、薄膜トランジスタ 4010、4011 は n チャネル型薄膜トランジスタである。

【0145】

また、液晶素子 4013 が有する画素電極層 4030 は、薄膜トランジスタ 4010 と電気的に接続されている。そして液晶素子 4013 の対向電極層 4031 は第 2 の基板 4006 上に形成されている。画素電極層 4030 と対向電極層 4031 と液晶層 4008 とが重なっている部分が、液晶素子 4013 に相当する。なお、画素電極層 4030、対向電極層 4031 はそれぞれ配向膜として機能する絶縁層 4032、4033 が設けられ、絶縁層 4032、4033 を介して液晶層 4008 を挟持している。

30

【0146】

なお、第 1 の基板 4001、第 2 の基板 4006 としては、ガラス、金属（代表的にはステンレス）、セラミックス、プラスチックを用いることができる。プラスチックとしては、FRP (Fiberglass-Reinforced Plastics) 板、PVF (ポリビニルフルオライド) フィルム、ポリエスチルフィルム、ポリエスチルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルを PVF フィルムやポリエスチルフィルムで挟んだ構造のシートを用いることもできる。

40

【0147】

また 4035 は絶縁膜を選択的にエッチングすることで得られる柱状のスペーサであり、画素電極層 4030 と対向電極層 4031 との間の距離（セルギャップ）を制御するため設けられている。なお球状のスペーサを用いていても良い。

【0148】

また、配向膜を用いないブルー相を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善

50

するために5重量%以上のカイラル剤を混合させた液晶組成物を用いて液晶層4008に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が10μs～100μsと短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。

#### 【0149】

なお本実施の形態は透過型液晶表示装置の例であるが、本発明の一態様は反射型液晶表示装置でも半透過型液晶表示装置でも適用できる。

#### 【0150】

また、本実施の形態の液晶表示装置では、基板の外側（視認側）に偏光板を設け、内側に着色層、表示素子に用いる電極層という順に設ける例を示すが、偏光板は基板の内側に設けてもよい。また、偏光板と着色層の積層構造も本実施の形態に限定されず、偏光板及び着色層の材料や作製工程条件によって適宜設定すればよい。また、ブラックマトリクスとして機能する遮光膜を設けてもよい。

10

#### 【0151】

また、本実施の形態では、薄膜トランジスタの表面凹凸を低減するため、及び薄膜トランジスタの信頼性を向上させるため、実施の形態2で示す非線形素子と、非線形素子と共に同様の方法で形成できる薄膜トランジスタを保護膜や平坦化絶縁膜として機能する絶縁層（絶縁層4020、絶縁層4021）で覆う構成となっている。なお、保護膜は、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純物の侵入を防ぐためのものであり、緻密な膜が好ましい。保護膜は、スパッタ法を用いて、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、又は窒化酸化アルミニウム膜の単層、又は積層で形成すればよい。本実施の形態では保護膜をスパッタ法で形成する例を示すが、特に限定されず種々の方法で形成すればよい。

20

#### 【0152】

ここでは、保護膜として積層構造の絶縁層4020を形成する。ここでは、絶縁層4020の一層目として、スパッタ法を用いて酸化珪素膜を形成する。保護膜として酸化珪素膜を用いると、ソース電極層及びドレイン電極層として用いるアルミニウム膜のヒロック防止に効果がある。

30

#### 【0153】

また、保護膜の二層目として絶縁層を形成する。ここでは、絶縁層4020の二層目として、スパッタ法を用いて窒化珪素膜を形成する。保護膜として窒化珪素膜を用いると、ナトリウム等の可動イオンが半導体領域中に侵入して、TFTの電気特性を変化させることを抑制することができる。

#### 【0154】

また、保護膜を形成した後に、酸化物半導体層のアニール（300～400）を行ってもよい。

#### 【0155】

また、平坦化絶縁膜として絶縁層4021を形成する。絶縁層4021としては、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）等を用いることができる。

40

シロキサン系樹脂は、置換基に水素の他、フッ素、アルキル基、またはアリール基のうち少なくとも1種を有していてもよい。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁層4021を形成してもよい。

#### 【0156】

なおシロキサン系樹脂とは、シロキサン系材料を出発材料として形成されたSi-O-Si結合を含む樹脂に相当する。シロキサン系樹脂は、置換基に水素の他、フッ素、アルキル基、または芳香族炭化水素のうち、少なくとも1種を有していてもよい。

50

## 【0157】

絶縁層4021の形成法は、特に限定されず、その材料に応じて、スパッタ法、SOG法、スピニコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーラー、カーテンコーラー、ナイフコーラー等を用いることができる。絶縁層4021を材料液を用いて形成する場合、ベークする工程で同時に、酸化物半導体層のアニール（300～400）を行ってもよい。絶縁層4021の焼成工程と酸化物半導体層のアニールを兼ねることで効率よく半導体装置を作製することが可能となる。

## 【0158】

画素電極層4030、対向電極層4031は、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物（以下、ITOと示す。）、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

10

## 【0159】

また、画素電極層4030、対向電極層4031として、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、シート抵抗が10000 / 以下、波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

20

## 【0160】

導電性高分子としては、いわゆる電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはこれらの2種以上の共重合体などがあげられる。

## 【0161】

また別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、FPC4018から供給されている。

## 【0162】

本実施の形態では、接続端子電極4015が、液晶素子4013が有する画素電極層4030と同じ導電膜から形成され、端子電極4016は、薄膜トランジスタ4010、4011のソース電極層及びドレイン電極層と同じ導電膜で形成されている。

30

## 【0163】

接続端子電極4015は、FPC4018が有する端子と、異方性導電膜4019を介して電気的に接続されている。

## 【0164】

また図17においては、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているが、本実施の形態はこの構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

40

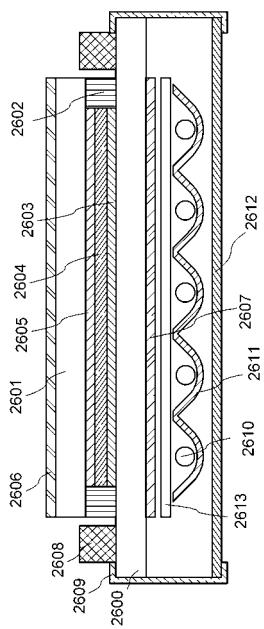

## 【0165】

図18は、本発明の一態様を適用して作製されるTFT基板2600を用いて半導体装置として液晶表示モジュールを構成する一例を示している。

## 【0166】

図18は液晶表示モジュールの一例であり、TFT基板2600と対向基板2601がシール材2602により固着され、その間にTFT等を含む画素部2603、液晶層を含む表示素子2604、着色層2605が設けられ表示領域を形成している。着色層2605はカラー表示を行う場合に必要であり、RGB方式の場合は、赤、緑、青の各色に対応した着色層が各画素に対応して設けられている。TFT基板2600と対向基板2601の外側には偏光板2606、偏光板2607、拡散板2613が配設されている。光源は冷陰極管2610と反射板2611により構成され、回路基板2612は、フレキシブル配

50

線基板 2609 により TFT 基板 2600 の配線回路部 2608 と接続され、コントロール回路や電源回路などの外部回路が組みこまれている。また偏光板と、液晶層との間に位相差板を有した状態で積層してもよい。

【0167】

液晶表示モジュールには、TN (Twisted Nematic) モード、IPS (In-Plane-Switching) モード、FFS (Fringe Field Switching) モード、MVA (Multi-domain Vertical Alignment) モード、PVA (Patterned Vertical Alignment)、ASM (Axially Symmetric aligned Micro-cell) モード、OCB (Optical Compensated Birefringence) モード、FLC (Ferroelectric Liquid Crystal) モード、AFLC (AntiFerroelectric Liquid Crystal) などを用いることができる。

10

【0168】

以上の工程により、動作の安定化が図られただけでなく、占有面積が小さい保護回路を搭載した信頼性の高い液晶パネルを作製することができる。

【0169】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

20

【0170】

(実施の形態 6)

本発明の一態様においては非線形素子と共に薄膜トランジスタを作製し、該薄膜トランジスタを画素部、さらには駆動回路に用いて表示機能を有する半導体装置（表示装置ともいう）を作製することができる。

30

【0171】

本実施の形態では、本発明の一態様の表示装置として発光表示装置の例を示す。表示装置の有する表示素子としては、ここではエレクトロルミネッセンスを利用する発光素子を用いて示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

【0172】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア（電子および正孔）が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

【0173】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー-アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機EL素子を用いて説明する。

40

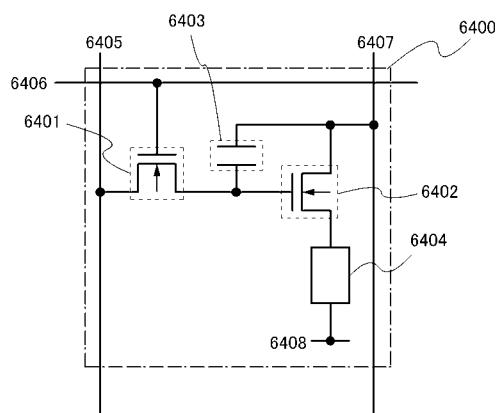

【0174】

図19は、本発明の一態様を適用した半導体装置の例としてデジタル時間階調駆動を適用可能な画素構成の一例を示す図である。

【0175】

デジタル時間階調駆動を適用可能な画素の構成及び画素の動作について説明する。ここでは実施の形態2で示す非線形素子と共に同様の方法で形成できる酸化物半導体層をチャネ

50

ル形成領域に用いるnチャネル型のトランジスタを1つの画素に2つ用いる例を示す。

【0176】

画素6400は、スイッチング用トランジスタ6401、駆動用トランジスタ6402、発光素子6404及び容量素子6403を有している。スイッチング用トランジスタ6401はゲートが走査線6406に接続され、第1電極（ソース電極及びドレイン電極の一方）が信号線6405に接続され、第2電極（ソース電極及びドレイン電極の他方）が駆動用トランジスタ6402のゲートに接続されている。駆動用トランジスタ6402は、ゲートが容量素子6403を介して電源線6407に接続され、第1電極が電源線6407に接続され、第2電極が発光素子6404の第1電極（画素電極）に接続されている。発光素子6404の第2電極は共通電極6408に相当する。

10

【0177】

なお、発光素子6404の第2電極（共通電極6408）には低電源電位が設定されている。なお、低電源電位とは、電源線6407に設定される高電源電位を基準にして低電源電位<高電源電位を満たす電位であり、低電源電位としては例えばGND、0Vなどが設定されていても良い。この高電源電位と低電源電位との電位差を発光素子6404に印加して、発光素子6404に電流を流して発光素子6404を発光させるため、高電源電位と低電源電位との電位差が発光素子6404の順方向しきい値電圧以上となるようにそれぞれの電位を設定する。

【0178】

なお、容量素子6403は駆動用トランジスタ6402のゲート容量を代用して省略することも可能である。駆動用トランジスタ6402のゲート容量については、チャネル領域とゲート電極との間で容量が形成されていてもよい。

20

【0179】

ここで、電圧入力電圧駆動方式の場合には、駆動用トランジスタ6402のゲートには、駆動用トランジスタ6402が十分にオンするか、オフするかの二つの状態となるようなビデオ信号を入力する。つまり、駆動用トランジスタ6402は線形領域で動作させる。駆動用トランジスタ6402は線形領域で動作させるため、電源線6407の電圧よりも高い電圧を駆動用トランジスタ6402のゲートにかける。なお、信号線6405には、（電源線電圧+駆動用トランジスタ6402のVth）以上の電圧をかける。

30

【0180】

また、デジタル時間階調駆動に代えて、アナログ階調駆動を行う場合、信号の入力を異なることで、図19と同じ画素構成を用いることができる。

【0181】

アナログ階調駆動を行う場合、駆動用トランジスタ6402のゲートに発光素子6404の順方向電圧+駆動用トランジスタ6402のVth以上の電圧をかける。発光素子6404の順方向電圧とは、所望の輝度とする場合の電圧を指しており、少なくとも順方向しきい値電圧を含む。なお、駆動用トランジスタ6402が飽和領域で動作するようなビデオ信号を入力することで、発光素子6404に電流を流すことができる。駆動用トランジスタ6402を飽和領域で動作させるため、電源線6407の電位は、駆動用トランジスタ6402のゲート電位よりも高くする。ビデオ信号をアナログとすることで、発光素子6404にビデオ信号に応じた電流を流し、アナログ階調駆動を行うことができる。

40

【0182】

なお、図19に示す画素構成は、これに限定されない。例えば、図19に示す画素に新たにスイッチ、抵抗素子、容量素子、トランジスタ又は論理回路などを追加してもよい。

【0183】

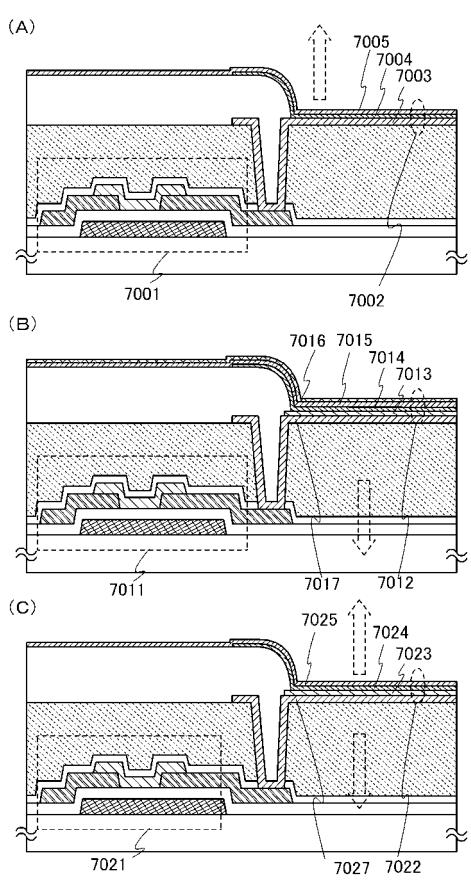

次に、発光素子の構成について、図20を用いて説明する。ここでは、駆動用TFTがn型の場合を例に挙げて、画素の断面構造について説明する。図20(A)(B)(C)の半導体装置に用いられる駆動用TFTであるTFT7001、7011、7021は、実施の形態2で示す非線形素子と共に同様の方法で形成できる薄膜トランジスタであり、In、Ga、及びZnを含む酸化物半導体を半導体層に用いた電気特性の高い薄膜トランジ

50

スタである。

【0184】

発光素子は発光を取り出すために少なくとも陽極又は陰極の一方が透明であればよい。そして、基板上に薄膜トランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、本発明の一態様の画素構成はどの射出構造の発光素子にも適用することができる。

【0185】

上面射出構造の発光素子について図20(A)を用いて説明する。

【0186】

図20(A)に、駆動用TFTであるTFT7001がn型で、発光素子7002から発せられる光が陽極7005側に抜ける場合の、画素の断面図を示す。図20(A)では、発光素子7002の陰極7003と駆動用TFTであるTFT7001が電気的に接続されており、陰極7003上に発光層7004、陽極7005が順に積層されている。陰極7003は仕事関数が小さく、なおかつ光を反射する導電膜であれば様々な材料を用いることができる。例えば、Ca、Al、CaF、MgAg、AlLi等が望ましい。そして発光層7004は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。複数の層で構成されている場合、陰極7003上に電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層する。なおこれらの層を全て設ける必要はない。陽極7005は光を透過する透光性を有する導電性材料を用いて形成し、例えば酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性導電膜を用いても良い。

【0187】

陰極7003及び陽極7005で発光層7004を挟んでいる領域が発光素子7002に相当する。図20(A)に示した画素の場合、発光素子7002から発せられる光は、矢印で示すように陽極7005側に射出する。

【0188】

次に、下面射出構造の発光素子について図20(B)を用いて説明する。駆動用TFT7011がn型で、発光素子7012から発せられる光が陰極7013側に射出する場合の、画素の断面図を示す。図20(B)では、駆動用TFT7011と電気的に接続された透光性を有する導電膜7017上に、発光素子7012の陰極7013が成膜されており、陰極7013上に発光層7014、陽極7015が順に積層されている。なお、陽極7015が透光性を有する場合、陽極上を覆うように、光を反射または遮蔽するための遮蔽膜7016が成膜されていてもよい。陰極7013は、図20(A)の場合と同様に、仕事関数が小さい導電性材料であれば様々な材料を用いることができる。ただしその膜厚は、光を透過する程度(好ましくは、5nm~30nm程度)とする。例えば20nmの膜厚を有するアルミニウム膜を、陰極7013として用いることができる。そして発光層7014は、図20(A)と同様に、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。陽極7015は光を透過する必要はないが、図20(A)と同様に、透光性を有する導電性材料を用いて形成することができる。そして遮蔽膜7016は、例えば光を反射する金属等を用いることができるが、金属膜に限定されない。例えば黒の顔料を添加した樹脂等を用いることもできる。

【0189】

陰極7013及び陽極7015で、発光層7014を挟んでいる領域が発光素子7012に相当する。図20(B)に示した画素の場合、発光素子7012から発せられる光は、矢印で示すように陰極7013側に射出する。

【0190】

次に、両面射出構造の発光素子について、図20(C)を用いて説明する。図20(C)

10

20

30

40

50

では、駆動用 TFT 7021 と電気的に接続された透光性を有する導電膜 7027 上に、発光素子 7022 の陰極 7023 が成膜されており、陰極 7023 上に発光層 7024、陽極 7025 が順に積層されている。陰極 7023 は、図 20 (A) の場合と同様に、仕事関数が小さい導電性材料であれば様々な材料を用いることができる。ただしその膜厚は、光を透過する程度とする。例えば 20 nm の膜厚を有する Al を、陰極 7023 として用いることができる。そして発光層 7024 は、図 20 (A) と同様に、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。陽極 7025 は、図 20 (A) と同様に、光を透過する透光性を有する導電性材料を用いて形成することができる。

## 【0191】

10

陰極 7023 と、発光層 7024 と、陽極 7025 とが重なっている部分が発光素子 7022 に相当する。図 20 (C) に示した画素の場合、発光素子 7022 から発せられる光は、矢印で示すように陽極 7025 側と陰極 7023 側の両方に射出する。

## 【0192】

なお、ここでは、発光素子として有機 EL 素子について述べたが、発光素子として無機 EL 素子を設けることも可能である。

## 【0193】

なお本実施の形態では、発光素子の駆動を制御する薄膜トランジスタ（駆動用 TFT）と発光素子が電気的に接続されている例を示したが、駆動用 TFT と発光素子との間に電流制御用 TFT が接続されている構成であってもよい。

20

## 【0194】

なお本実施の形態で示す半導体装置は、図 20 に示した構成に限定されるものではなく、本発明の一態様の技術的思想に基づく各種の変形が可能である。

## 【0195】

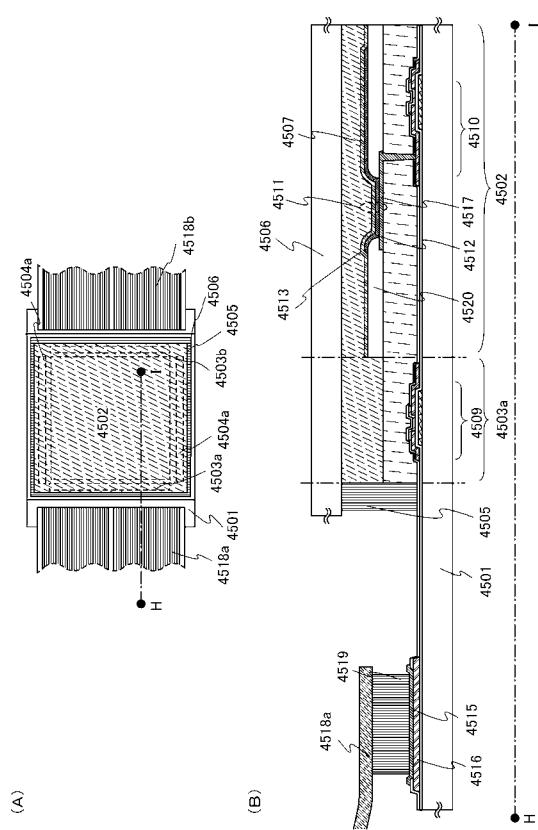

次に、本発明の一態様の半導体装置の一形態に相当する発光表示パネル（発光パネルともいう）の外観及び断面について、図 21 (A) を用いて説明する。図 21 は、本発明の一態様における非線形素子と同様に In、Ga、及び Zn を含む酸化物半導体を半導体層に用いた電気特性の高い薄膜トランジスタ及び発光素子を、第 2 の基板との間にシール材によって封止した、パネルの上面図であり、図 21 (B) は、図 21 (A) の H - I における断面図に相当する。

30

## 【0196】

第 1 の基板 4501 上に設けられた画素部 4502、信号線駆動回路 4503a、4503b、及び走査線駆動回路 4504a、4504b を囲むようにして、シール材 4505 が設けられている。また画素部 4502、信号線駆動回路 4503a、4503b、及び走査線駆動回路 4504a、4504b の上に第 2 の基板 4506 が設けられている。よって画素部 4502、信号線駆動回路 4503a、4503b、及び走査線駆動回路 4504a、4504b は、第 1 の基板 4501 とシール材 4505 と第 2 の基板 4506 によって、充填材 4507 と共に密封されている。このように外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム（貼り合わせフィルム、紫外線硬化樹脂フィルム等）やカバー材でパッケージング（封入）することが好みしい。

40

## 【0197】

また第 1 の基板 4501 上に設けられた画素部 4502、信号線駆動回路 4503a、4503b、及び走査線駆動回路 4504a、4504b は、薄膜トランジスタを複数有しており、図 21 (B) では、画素部 4502 に含まれる薄膜トランジスタ 4510 と、信号線駆動回路 4503a に含まれる薄膜トランジスタ 4509 とを例示している。

## 【0198】

薄膜トランジスタ 4509、4510 は、In、Ga、及び Zn を含む酸化物半導体を半導体層に用いた電気特性の高い薄膜トランジスタに相当し、実施の形態 2 で示す非線形素子と共に同様の方法で形成できる薄膜トランジスタを適用することができる。本実施の形態において、薄膜トランジスタ 4509、4510 は n チャネル型薄膜トランジスタであ

50

る。

【0199】

また 4511 は発光素子に相当し、発光素子 4511 が有する画素電極である第 1 の電極層 4517 は、薄膜トランジスタ 4510 のソース電極層またはドレイン電極層と電気的に接続されている。なお発光素子 4511 の構成は、第 1 の電極層 4517、電界発光層 4512、第 2 の電極層 4513 の積層構造であるが、本実施の形態に示した構成に限定されない。発光素子 4511 から取り出す光の方向などに合わせて、発光素子 4511 の構成は適宜変えることができる。

【0200】

隔壁 4520 は、有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。特に感光性の材料を用い、第 1 の電極層 4517 上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

【0201】

電界発光層 4512 は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。

【0202】

発光素子 4511 に酸素、水素、水分、二酸化炭素等が侵入しないように、第 2 の電極層 4513 及び隔壁 4520 上に保護膜を形成してもよい。保護膜としては、窒化珪素膜、窒化酸化珪素膜、DLC 膜等を形成することができる。

【0203】

また、信号線駆動回路 4503a、4503b、走査線駆動回路 4504a、4504b、または画素部 4502 に与えられる各種信号及び電位は、FPC4518a、4518b から供給されている。

【0204】

本実施の形態では、接続端子電極 4515 が、発光素子 4511 が有する第 1 の電極層 4517 と同じ導電膜から形成され、端子電極 4516 は、薄膜トランジスタ 4509、4510 が有するソース電極層及びドレイン電極層と同じ導電膜から形成されている。

【0205】

接続端子電極 4515 は、FPC4518a が有する端子と、異方性導電膜 4519 を介して電気的に接続されている。

【0206】

発光素子 4511 からの光の取り出し方向に位置する第 2 の基板 4506 は透光性でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透光性を有する材料を用いる。

【0207】

また、充填材 4507 としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。本実施の形態は充填材として窒素を用いた。

【0208】

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板(楕円偏光板を含む)、位相差板(1/4 板、1/2 板)、カラーフィルタなどの光学フィルムを適宜設けてよい。また、偏光板又は円偏光板に反射防止膜を設けてよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

【0209】

信号線駆動回路 4503a、4503b、及び走査線駆動回路 4504a、4504b は、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜によって形成された駆動回路で実装されていてもよい。また、信号線駆動回路のみ、或いは一部、又は走査線駆動回路のみ、或いは一部のみを別途形成して実装しても良く、本実施の形態は図 21 の構成に

10

20

30

40

50

限定されない。

【0210】

以上の工程により、動作の安定化が図られただけでなく、占有面積が小さい保護回路を搭載した信頼性の高い発光表示装置（表示パネル）を作製することができる。

【0211】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

【0212】

（実施の形態7）

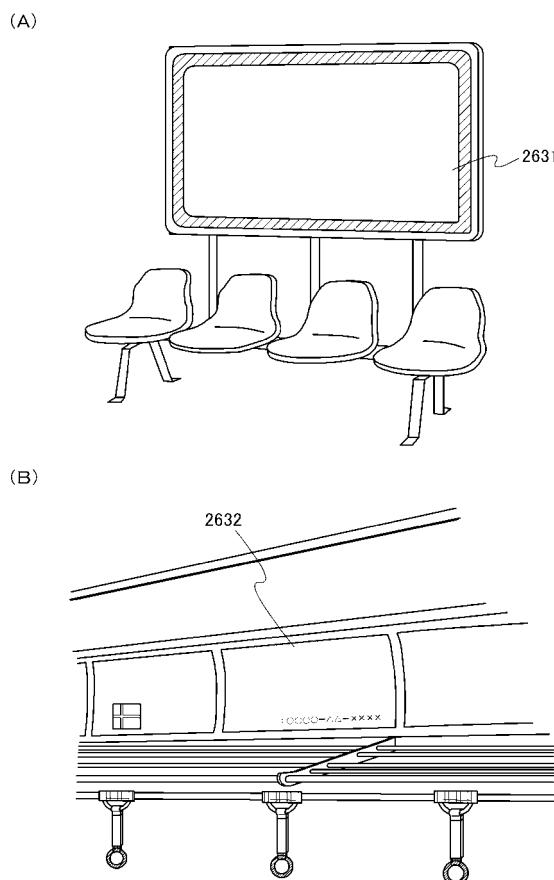

本発明の一態様の表示装置は、電子ペーパーとして適用することができる。電子ペーパーは、情報を表示するものであればあらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパーを用いて、電子書籍（電子ブック）、ポスター、電車などの乗り物の車内広告、クレジットカード等の各種カードにおける表示等に適用することができる。電子機器の一例を図22、図23に示す。

10

【0213】

図22（A）は、電子ペーパーで作られたポスター2631を示している。広告媒体が紙の印刷物である場合には、広告の交換は人手によって行われるが、本発明の一態様を適用した電子ペーパーを用いれば短時間で広告の表示を変えることができる。また、表示も崩れることなく安定した画像が得られる。なお、ポスターは無線で情報を送受信できる構成としてもよい。

20

【0214】

また、図22（B）は、電車などの乗り物の車内広告2632を示している。広告媒体が紙の印刷物である場合には、広告の交換は人手によって行われるが、本発明の一態様を適用した電子ペーパーを用いれば人手を多くかけることなく短時間で広告の表示を変えることができる。また表示も崩れることなく安定した画像が得られる。なお、車内広告は無線で情報を送受信できる構成としてもよい。

20

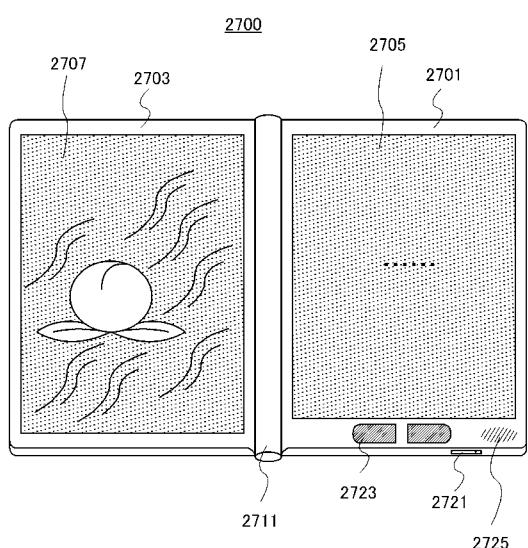

【0215】

また、図23は、電子書籍2700の一例を示している。例えば、電子書籍2700は、筐体2701および筐体2703の2つの筐体で構成されている。筐体2701および筐体2703は、軸部2711により一体とされており、該軸部2711を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

30

【0216】

筐体2701には表示部2705が組み込まれ、筐体2703には表示部2707が組み込まれている。表示部2705および表示部2707は、継ぎ画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成として、例えば右側の表示部（図23では表示部2705）に文章を表示し、左側の表示部（図23では表示部2707）に画像を表示することができる。

【0217】

また、図23では、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源2721、操作キー2723、スピーカ2725などを備えている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングディバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子（イヤホン端子、USB端子、またはACアダプタおよびUSBケーブルなどの各種ケーブルと接続可能な端子など）、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍2700は、電子辞書としての機能を持たせた構成としてもよい。

40

【0218】

また、電子書籍2700は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすること

50

も可能である。

【0219】

以上の工程により、動作の安定化が図られただけでなく、占有面積が小さい保護回路を搭載した表示装置を用いて信頼性の高い電子機器を作製できる。

【0220】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0221】

(実施の形態8)

本発明の一態様に係る半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。

10

【0222】

図24(A)は、テレビジョン装置9600の一例を示している。テレビジョン装置9600は、筐体9601に表示部9603が組み込まれている。表示部9703により、映像を表示することが可能である。また、ここでは、スタンド9605により筐体9601を支持した構成を示している。

20

【0223】

テレビジョン装置9600の操作は、筐体9601が備える操作スイッチや、別体のリモコン操作機9610により行うことができる。リモコン操作機9610が備える操作キー9609により、チャンネルや音量の操作を行なうことができ、表示部9603に表示される映像を操作することができる。また、リモコン操作機9610に、当該リモコン操作機9610から出力する情報を表示する表示部9607を設ける構成としてもよい。

30

【0224】

なお、テレビジョン装置9600は、受信機やモデムなどを備えた構成とする。受信機により一般的のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

30

【0225】

図24(B)は、デジタルフォトフレーム9700の一例を示している。例えば、デジタルフォトフレーム9700は、筐体9701に表示部9703が組み込まれている。表示部9703は、各種画像を表示することができる、例えばデジタルカメラなどで撮影した画像データを表示させることで、通常の写真立てと同様に機能させることができる。

40

【0226】

なお、デジタルフォトフレーム9700は、操作部、外部接続用端子(USB端子、USBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成とする。これらの構成は、表示部と同一面に組み込まれていてもよいが、側面や裏面に備えるとデザイン性が向上するため好ましい。例えば、デジタルフォトフレームの記録媒体挿入部に、デジタルカメラで撮影した画像データを記憶したメモリを挿入して画像データを取り込み、取り込んだ画像データを表示部9703に表示させることができる。

【0227】

また、デジタルフォトフレーム9700は、無線で情報を送受信出来る構成としてもよい。無線により、所望の画像データを取り込み、表示させる構成とすることもできる。

【0228】

図25(A)は携帯型遊技機であり、筐体9881と筐体9891の2つの筐体で構成されており、連結部9893により、開閉可能に連結されている。筐体9881には表示部9882が組み込まれ、筐体9891には表示部9883が組み込まれている。また、図

50

25 (A) に示す携帯型遊技機は、その他、スピーカ部 9884、記録媒体挿入部 9886、LED ランプ 9890、入力手段（操作キー 9885、接続端子 9887、センサ 9888（力、変位、位置、速度、加速度、角速度、回転数、距離、光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、におい又は赤外線を測定する機能を含むもの）、マイクロフォン 9889）等を備えている。もちろん、携帯型遊技機の構成は上述のものに限定されず、少なくとも本発明の一態様に係る半導体装置を備えた構成であればよく、その他付属設備が適宜設けられた構成とすることができる。図 25 (A) に示す携帯型遊技機は、記録媒体に記録されているプログラム又はデータを読み出して表示部に表示する機能や、他の携帯型遊技機と無線通信を行って情報を共有する機能を有する。なお、図 25 (A) に示す携帯型遊技機が有する機能はこれに限定されず、様々な機能を有することができる。

10

## 【0229】

図 25 (B) は大型遊技機であるスロットマシン 9900 の一例を示している。スロットマシン 9900 は、筐体 9901 に表示部 9903 が組み込まれている。また、スロットマシン 9900 は、その他、スタートレバーやストップスイッチなどの操作手段、コイン投入口、スピーカなどを備えている。もちろん、スロットマシン 9900 の構成は上述のものに限定されず、少なくとも本発明の一態様に係る半導体装置を備えた構成であればよく、その他付属設備が適宜設けられた構成とすることができる。

20

## 【0230】

図 26 は、携帯電話機 1000 の一例を示している。携帯電話機 1000 は、筐体 1001 に組み込まれた表示部 1002 の他、操作ボタン 1003、外部接続ポート 1004、スピーカ 1005、マイク 1006 などを備えている。

20

## 【0231】

図 26 に示す携帯電話機 1000 は、表示部 1002 を指などで触ることで、情報を入力ことができる。また、電話を掛ける、或いはメールを打つなどの操作は、表示部 1002 を指などで触ることにより行うことができる。

30

## 【0232】

表示部 1002 の画面は主として 3 つのモードがある。第 1 は、画像の表示を主とする表示モードであり、第 2 は、文字等の情報の入力を主とする入力モードである。第 3 は表示モードと入力モードの 2 つのモードが混合した表示 + 入力モードである。

30

## 【0233】

例えば、電話を掛ける、或いはメールを作成する場合は、表示部 1002 を文字の入力を主とする文字入力モードとし、画面に表示させた文字の入力操作を行えばよい。この場合、表示部 1002 の画面のほとんどにキーボードまたは番号ボタンを表示させることが好みしい。

## 【0234】

また、携帯電話機 1000 内部に、ジャイロ、加速度センサ等の傾きを検出するセンサを有する検出装置を設けることで、携帯電話機 1000 の向き（縦か横か）を判断して、表示部 1002 の画面表示を自動的に切り替えるようにすることができる。

40

## 【0235】

また、画面モードの切り替えは、表示部 1002 を触ること、又は筐体 1001 の操作ボタン 1003 の操作により行われる。また、表示部 1002 に表示される画像の種類によって切り替えるようにすることもできる。例えば、表示部に表示する画像信号が動画のデータであれば表示モード、テキストデータであれば入力モードに切り替える。

## 【0236】

また、入力モードにおいて、表示部 1002 の光センサで検出される信号を検知し、表示部 1002 のタッチ操作による入力が一定期間ない場合には、画面のモードを入力モードから表示モードに切り替えるように制御してもよい。

## 【0237】

表示部 1002 は、イメージセンサとして機能させることもできる。例えば、表示部 10

50

02に掌や指を触ることで、掌紋、指紋等を撮像することで、本人認証を行うことができる。また、表示部に近赤外光を発光するバックライトまたは近赤外光を発光するセンシング用光源を用いれば、指静脈、掌静脈などを撮像することもできる。

【0238】

以上の工程により、動作の安定化が図られただけでなく、占有面積が小さい保護回路を搭載した表示装置を用いて信頼性の高い電子機器を作製できる。

【0239】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【符号の説明】

【0240】

|         |          |    |

|---------|----------|----|

| 1 0     | 基板       | 10 |

| 1 1     | 走査線入力端子  |    |

| 1 2     | 信号線入力端子  |    |

| 1 3     | 走査線      |    |

| 1 4     | 信号線      |    |

| 1 6     | ゲート電極    |    |

| 1 7     | 画素部      |    |

| 1 8     | 画素       |    |

| 1 9     | 画素トランジスタ | 20 |

| 2 0     | 保持容量部    |    |

| 2 1     | 画素電極     |    |

| 2 2     | 容量線      |    |

| 2 3     | 共通端子     |    |

| 2 4     | 保護回路     |    |

| 2 5     | 保護回路     |    |

| 2 6     | 保護回路     |    |

| 2 7     | 容量バス線    |    |

| 2 8     | 共通配線     |    |

| 2 9     | 共通配線     | 30 |

| 3 0     | 非線形素子    |    |

| 3 0 a   | 非線形素子    |    |

| 3 0 b   | 非線形素子    |    |

| 3 1     | 非線形素子    |    |

| 3 1 a   | 非線形素子    |    |

| 3 1 b   | 非線形素子    |    |

| 1 0 0   | 基板       |    |

| 1 0 2   | ゲート絶縁膜   |    |

| 1 0 7   | 層間絶縁膜    |    |

| 1 1 1   | ゲート電極    | 40 |

| 1 1 3   | 酸化物半導体層  |    |

| 1 1 7 a | 配線層      |    |

| 1 1 7 b | 配線層      |    |

| 1 2 8   | コンタクトホール |    |

| 1 3 1   | レジストマスク  |    |

| 1 7 0 a | 非線形素子    |    |

| 1 7 0 b | 非線形素子    |    |

| 5 8 1   | 薄膜トランジスタ |    |

| 5 8 5   | 絶縁層      |    |

| 5 8 7   | 電極層      | 50 |

|         |            |    |

|---------|------------|----|

| 5 8 8   | 電極層        |    |

| 5 8 9   | 球形粒子       |    |

| 5 9 0 a | 黒色領域       |    |

| 5 9 0 b | 白色領域       |    |

| 5 9 4   | キャビティ      |    |

| 5 9 5   | 充填材        |    |

| 6 5 0   | 共通配線       |    |

| 6 5 1   | 走査線        |    |

| 7 3 0 a | 非線形素子      | 10 |

| 7 3 0 b | 非線形素子      |    |

| 7 3 0 c | 非線形素子      |    |

| 7 4 0 a | 非線形素子      |    |

| 7 4 0 b | 非線形素子      |    |

| 7 4 0 c | 非線形素子      |    |

| 7 4 0 d | 非線形素子      |    |

| 1 0 0 0 | 携帯電話機      |    |

| 1 0 0 1 | 筐体         |    |

| 1 0 0 2 | 表示部        |    |

| 1 0 0 3 | 操作ボタン      |    |

| 1 0 0 4 | 外部接続ポート    | 20 |

| 1 0 0 5 | スピーカ       |    |

| 1 0 0 6 | マイク        |    |

| 2 6 0 0 | TFT基板      |    |

| 2 6 0 1 | 対向基板       |    |

| 2 6 0 2 | シール材       |    |

| 2 6 0 3 | 画素部        |    |

| 2 6 0 4 | 表示素子       |    |

| 2 6 0 5 | 着色層        |    |

| 2 6 0 6 | 偏光板        |    |

| 2 6 0 7 | 偏光板        | 30 |

| 2 6 0 8 | 配線回路部      |    |

| 2 6 0 9 | フレキシブル配線基板 |    |

| 2 6 1 0 | 冷陰極管       |    |

| 2 6 1 1 | 反射板        |    |

| 2 6 1 2 | 回路基板       |    |

| 2 6 1 3 | 拡散板        |    |

| 2 6 3 1 | ポスター       |    |

| 2 6 3 2 | 車内広告       |    |

| 2 7 0 0 | 電子書籍       |    |

| 2 7 0 1 | 筐体         | 40 |

| 2 7 0 3 | 筐体         |    |

| 2 7 0 5 | 表示部        |    |

| 2 7 0 7 | 表示部        |    |

| 2 7 1 1 | 軸部         |    |

| 2 7 2 1 | 電源         |    |

| 2 7 2 3 | 操作キー       |    |

| 2 7 2 5 | スピーカ       |    |

| 4 0 0 1 | 基板         |    |

| 4 0 0 2 | 画素部        |    |

| 4 0 0 3 | 信号線駆動回路    | 50 |

|           |          |    |

|-----------|----------|----|

| 4 0 0 4   | 走査線駆動回路  |    |

| 4 0 0 5   | シール材     |    |

| 4 0 0 6   | 基板       |    |

| 4 0 0 8   | 液晶層      |    |

| 4 0 1 0   | 薄膜トランジスタ | 10 |

| 4 0 1 1   | 薄膜トランジスタ |    |

| 4 0 1 3   | 液晶素子     |    |

| 4 0 1 5   | 接続端子電極   |    |

| 4 0 1 6   | 端子電極     |    |

| 4 0 1 8   | F P C    |    |

| 4 0 1 9   | 異方性導電膜   |    |

| 4 0 2 0   | 絶縁層      |    |

| 4 0 2 1   | 絶縁層      |    |

| 4 0 3 0   | 画素電極層    |    |

| 4 0 3 1   | 対向電極層    |    |

| 4 0 3 2   | 絶縁層      |    |

| 4 5 0 1   | 基板       |    |

| 4 5 0 2   | 画素部      |    |

| 4 5 0 3 a | 信号線駆動回路  | 20 |

| 4 5 0 4 a | 走査線駆動回路  |    |

| 4 5 0 5   | シール材     |    |

| 4 5 0 6   | 基板       |    |

| 4 5 0 7   | 充填材      |    |

| 4 5 0 9   | 薄膜トランジスタ |    |

| 4 5 1 0   | 薄膜トランジスタ |    |

| 4 5 1 1   | 発光素子     |    |

| 4 5 1 2   | 電界発光層    |    |

| 4 5 1 3   | 電極層      | 30 |

| 4 5 1 5   | 接続端子電極   |    |

| 4 5 1 6   | 端子電極     |    |

| 4 5 1 7   | 電極層      |    |

| 4 5 1 8 a | F P C    |    |

| 4 5 1 9   | 異方性導電膜   |    |

| 4 5 2 0   | 隔壁       |    |

| 5 3 0 0   | 基板       |    |

| 5 3 0 1   | 画素部      |    |

| 5 3 0 2   | 走査線駆動回路  |    |

| 5 3 0 3   | 信号線駆動回路  |    |

| 5 4 0 0   | 基板       |    |

| 5 4 0 1   | 画素部      | 40 |

| 5 4 0 2   | 走査線駆動回路  |    |

| 5 4 0 3   | 信号線駆動回路  |    |

| 5 4 0 4   | 走査線駆動回路  |    |

| 5 5 0 1   | 配線       |    |

| 5 5 0 2   | 配線       |    |

| 5 5 0 3   | 配線       |    |

| 5 5 0 4   | 配線       |    |

| 5 5 0 5   | 配線       |    |

| 5 5 0 6   | 配線       |    |

| 5 5 4 3   | ノード      | 50 |

|           |               |    |

|-----------|---------------|----|

| 5 5 4 4   | ノード           |    |

| 5 5 7 1   | 薄膜トランジスタ      |    |

| 5 5 7 2   | 薄膜トランジスタ      |    |

| 5 5 7 3   | 薄膜トランジスタ      |    |

| 5 5 7 4   | 薄膜トランジスタ      |    |

| 5 5 7 5   | 薄膜トランジスタ      |    |

| 5 5 7 6   | 薄膜トランジスタ      |    |

| 5 5 7 7   | 薄膜トランジスタ      |    |

| 5 5 7 8   | 薄膜トランジスタ      |    |

| 5 6 0 1   | ドライバ I C      | 10 |

| 5 6 0 2   | スイッチ群         |    |

| 5 6 0 3 a | 薄膜トランジスタ      |    |

| 5 6 0 3 b | 薄膜トランジスタ      |    |

| 5 6 0 3 c | 薄膜トランジスタ      |    |

| 5 6 1 1   | 配線            |    |

| 5 6 1 2   | 配線            |    |

| 5 6 1 3   | 配線            |    |

| 5 6 2 1   | 配線            |    |

| 5 7 0 1   | フリップフロップ      |    |

| 5 7 0 3 a | タイミング         | 20 |

| 5 7 0 3 b | タイミング         |    |

| 5 7 0 3 c | タイミング         |    |

| 5 7 1 1   | 配線            |    |

| 5 7 1 2   | 配線            |    |

| 5 7 1 3   | 配線            |    |

| 5 7 1 4   | 配線            |    |

| 5 7 1 5   | 配線            |    |

| 5 7 1 6   | 配線            |    |

| 5 7 1 7   | 配線            |    |

| 5 7 2 1   | 信号            | 30 |

| 5 8 0 3 a | タイミング         |    |

| 5 8 0 3 b | タイミング         |    |

| 5 8 0 3 c | タイミング         |    |

| 5 8 2 1   | 信号            |    |

| 6 4 0 0   | 画素            |    |

| 6 4 0 1   | スイッチング用トランジスタ |    |

| 6 4 0 2   | 駆動用トランジスタ     |    |

| 6 4 0 3   | 容量素子          |    |

| 6 4 0 4   | 発光素子          |    |

| 6 4 0 5   | 信号線           | 40 |

| 6 4 0 6   | 走査線           |    |

| 6 4 0 7   | 電源線           |    |

| 6 4 0 8   | 共通電極          |    |

| 7 0 0 1   | TFT           |    |

| 7 0 0 2   | 発光素子          |    |

| 7 0 0 3   | 陰極            |    |

| 7 0 0 4   | 発光層           |    |

| 7 0 0 5   | 陽極            |    |

| 7 0 1 1   | 駆動用 TFT       |    |

| 7 0 1 2   | 発光素子          | 50 |

|         |             |    |

|---------|-------------|----|

| 7 0 1 3 | 陰極          |    |

| 7 0 1 4 | 発光層         |    |

| 7 0 1 5 | 陽極          |    |

| 7 0 1 6 | 遮蔽膜         |    |

| 7 0 1 7 | 導電膜         |    |

| 7 0 2 1 | 駆動用 TFT     |    |

| 7 0 2 2 | 発光素子        |    |

| 7 0 2 3 | 陰極          |    |

| 7 0 2 4 | 発光層         |    |

| 7 0 2 5 | 陽極          | 10 |

| 7 0 2 7 | 導電膜         |    |

| 9 6 0 0 | テレビジョン装置    |    |

| 9 6 0 1 | 筐体          |    |

| 9 6 0 3 | 表示部         |    |

| 9 6 0 5 | スタンド        |    |

| 9 6 0 7 | 表示部         |    |

| 9 6 0 9 | 操作キー        |    |

| 9 6 1 0 | リモコン操作機     |    |

| 9 7 0 0 | デジタルフォトフレーム |    |

| 9 7 0 1 | 筐体          | 20 |

| 9 7 0 3 | 表示部         |    |

| 9 8 8 1 | 筐体          |    |

| 9 8 8 2 | 表示部         |    |

| 9 8 8 3 | 表示部         |    |

| 9 8 8 4 | スピーカ部       |    |

| 9 8 8 5 | 入力手段（操作キー）  |    |

| 9 8 8 6 | 記録媒体挿入部     |    |

| 9 8 8 7 | 接続端子        |    |

| 9 8 8 8 | センサ         |    |

| 9 8 8 9 | マイクロフォン     | 30 |

| 9 8 9 0 | L EDランプ     |    |

| 9 8 9 1 | 筐体          |    |

| 9 8 9 3 | 連結部         |    |

| 9 9 0 0 | スロットマシン     |    |

| 9 9 0 1 | 筐体          |    |

| 9 9 0 3 | 表示部         |    |

【図1】

【図2】

【図3】

【図4】

(A)

(B)

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 17】

【図 18】

【図 19】

【図 20】

【図 2 1】

【図 2 2】

【図 2 3】

【図 2 4】

【図25】

(B)

【図26】

## フロントページの続き

| (51)Int.Cl.             | F I                  | テーマコード(参考) |

|-------------------------|----------------------|------------|

| H 01 L 21/28 (2006.01)  | H 01 L 21/28 3 0 1 B | 5 F 1 1 0  |

| H 01 L 29/423 (2006.01) | H 01 L 29/58 G       |            |

| H 01 L 29/49 (2006.01)  | H 01 L 29/50 M       |            |

| H 01 L 29/417 (2006.01) | H 01 L 21/28 3 0 1 R |            |

| G 02 F 1/1368 (2006.01) | G 02 F 1/1368        |            |

(72)発明者 二村 智哉

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 笠原 崇廣

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

F ターム(参考) 2H092 JA26 JB79 KA05 KA08 NA14

|                                                         |

|---------------------------------------------------------|

| 4M104 AA03 AA09 BB02 BB04 BB13 BB14 BB16 BB17 BB18 BB29 |

| BB30 BB31 BB32 BB33 BB36 CC01 CC05 DD07 DD15 DD16       |

| DD17 DD18 DD37 DD64 DD65 DD79 FF08 GG09 GG10 GG14       |

| HH13 HH16                                               |

| 5C094 AA15 AA21 AA32 AA37 BA03 BA43 DA13 DA15 DB04 EA10 |

| FB14                                                    |

| 5F033 GG04 HH38 JJ01 JJ09 KK07 KK08 KK11 KK17 KK18 KK19 |

| KK20 KK21 KK32 KK33 KK34 MM05 MM08 PP15 QQ00 QQ08       |

| QQ09 QQ11 QQ14 QQ19 QQ34 QQ37 QQ54 QQ71 QQ98 RR01       |

| RR03 RR04 RR05 RR06 RR08 SS08 SS15 VV06 VV15 XX02       |

| XX10 XX33                                               |

| 5F038 BH07 BH13 EZ01 EZ20                               |

| 5F110 AA22 BB02 CC03 DD02 DD07 EE01 EE03 EE04 EE06 EE14 |

| EE23 FF01 FF02 FF03 FF04 FF09 FF28 FF30 GG01 GG25       |

| GG43 GG58 HK03 HK04 HK06 HK22 HK42 HL01 HL07 HL09       |

| NN02 NN03 NN05 NN22 NN23 NN24 NN25 NN27 NN34 NN40       |

| NN71 NN72 QQ08 QQ09 QQ19                                |