(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-160063

(P2014-160063A)

(43) 公開日 平成26年9月4日(2014.9.4)

| (51) Int.Cl.                  | F 1         |     | テーマコード (参考) |

|-------------------------------|-------------|-----|-------------|

| <b>G01R 31/28 (2006.01)</b>   | GO1R 31/28  | G   | 2G132       |

| <b>H01L 21/8242 (2006.01)</b> | HO1L 27/10  | 321 | 5FO38       |

| <b>H01L 27/108 (2006.01)</b>  | HO1L 27/10  | 441 | 5FO83       |

| <b>H01L 27/105 (2006.01)</b>  | HO3K 3/356  | B   | 5JO34       |

| <b>H03K 3/356 (2006.01)</b>   | HO3K 19/173 | 101 | 5JO42       |

審査請求 未請求 請求項の数 6 O L (全 36 頁) 最終頁に続く

|              |                            |            |                                                                                                 |

|--------------|----------------------------|------------|-------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2014-11105 (P2014-11105) | (71) 出願人   | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地                                                  |

| (22) 出願日     | 平成26年1月24日 (2014.1.24)     | (72) 発明者   | 王丸 拓郎<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                                    |

| (31) 優先権主張番号 | 特願2013-10792 (P2013-10792) | (72) 発明者   | 筒井 直昭<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                                    |

| (32) 優先日     | 平成25年1月24日 (2013.1.24)     | F ターム (参考) | 2G132 AA01 AB01 AK24 AL11<br>5FO38 AC05 DF08 DT06 DT15 EZ01<br>EZ02 EZ13 EZ14 EZ16 EZ17<br>EZ20 |

| (33) 優先権主張国  | 日本国 (JP)                   |            |                                                                                                 |

最終頁に続く

## (54) 【発明の名称】 半導体装置

## (57) 【要約】

【課題】遅延の発生が抑制された信号を記憶回路に供給することができる。論理回路に与える負荷が低減された新規な半導体装置を提供する。

【解決手段】複数のデータ信号と選択信号が供給される記憶回路が、2つの組み合わせ回路を接続する構成を有する。そして、当該記憶回路が選択信号により複数のデータ信号から一を選択する機能を備える構成に想到した。選択回路を記憶回路と組み合わせ回路の間に設ける必要がない。その結果、組み合わせ回路は遅延の発生が抑制された信号を記憶回路に供給することができる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第 1 の組み合わせ回路と、

前記第 1 の組み合わせ回路に、第 1 のデータ信号を供給することができる第 1 の記憶回路と、

前記第 1 の組み合わせ回路に、第 2 のデータ信号を供給することができる第 2 の記憶回路と、

前記第 1 の記憶回路および前記第 2 の記憶回路に選択信号を供給することができる選択信号線と、

前記第 1 の記憶回路に前記第 1 のデータ信号を供給し、前記第 2 の記憶回路に前記第 2 のデータ信号を供給することができる第 2 の組み合わせ回路と、を有し、

前記第 2 の記憶回路は、前記第 2 の組み合わせ回路から供給される信号を選択する第 1 の状態と、前記第 1 の記憶回路から供給される信号を選択する第 2 の状態とを、前記選択信号により選択する機能を備える半導体装置。

**【請求項 2】**

前記第 2 の記憶回路は、

前記第 2 のデータ信号が供給される第 1 の記憶部と、

前記第 1 の記憶部、前記第 1 の記憶回路並びに前記選択信号線からそれぞれ信号が供給される選択部と、

前記選択部に選択された信号が供給され、前記第 1 の組み合わせ回路に信号を供給する第 2 の記憶部と、を有し、

前記選択部が、前記第 1 の状態において、前記第 1 の記憶部から供給される信号を選択し、前記第 2 の状態において、前記第 1 の記憶回路から供給される信号を選択する、請求項 1 記載の半導体装置。

**【請求項 3】**

第 1 の組み合わせ回路と、

前記第 1 の組み合わせ回路に、第 1 のデータ信号を供給することができる第 1 の記憶回路と、

前記第 1 の組み合わせ回路に、第 2 のデータ信号を供給することができる第 2 の記憶回路と、

前記第 1 の記憶回路および前記第 2 の記憶回路に第 1 の選択信号を供給することができる第 1 の選択信号線と、

前記第 2 の記憶回路に供給する信号を選択することができる選択回路と、

前記選択回路に、第 3 のデータ信号を供給することができる副記憶回路と、

前記選択回路を制御する第 2 の選択信号を、供給することができる第 2 の選択信号線と、

前記第 1 の記憶回路に前記第 1 のデータ信号を供給し、前記第 2 の記憶回路に前記第 2 のデータ信号を供給することができる第 2 の組み合わせ回路と、を有し、

前記第 2 の記憶回路は、前記第 2 の組み合わせ回路から供給される信号を選択する第 1 の状態と、前記第 1 の記憶回路から供給される信号を選択する第 2 の状態と、を前記選択信号により選択する機能を備え、

前記選択回路は、前記副記憶回路が供給する信号を供給する状態と、前記第 1 の記憶回路が供給する信号を供給する状態と、を前記第 2 の選択信号により選択する機能を備える半導体装置。

**【請求項 4】**

前記第 2 の記憶回路は、

前記第 2 のデータ信号が供給される第 1 の記憶部と、

前記第 1 の記憶部、前記選択回路並びに前記第 1 の選択信号線からそれぞれ信号が供給される選択部と、

前記選択部に選択された信号が供給され、前記第 1 の組み合わせ回路に信号を供給する

10

20

30

40

50

第2の記憶部と、を有し、

前記選択部が、前記第1の状態において、前記第1の記憶部から供給される信号を選択し、前記第2の状態において、前記選択回路から供給される信号を選択する、請求項3記載の半導体装置。

**【請求項5】**

前記第2の記憶回路は、

第2のデータ信号が供給される第1の記憶部と、

前記第1の記憶部、前記選択回路並びに前記第1の選択信号線からそれぞれ信号が供給される選択部と、

前記選択部に選択された信号が供給され、前記第1の組み合わせ回路に信号を供給する

10 第2の記憶部と、を有し、

前記副記憶回路は、前記第2の記憶回路に供給される信号を記憶する機能を備え、

前記選択部が、前記第1の状態において、前記第1の記憶部から供給される信号を選択し、前記第2の状態において、前記選択回路から供給される信号を選択する、請求項3記載の半導体装置。

**【請求項6】**

前記第2の記憶回路は、

第2のデータ信号が供給される第1の記憶部と、

前記第1の記憶部、前記選択回路並びに前記第1の選択信号線からそれぞれ信号が供給される選択部と、

前記選択部に選択された信号が供給され、前記第1の組み合わせ回路に信号を供給する

20 第2の記憶部と、を有し、

前記副記憶回路は、

第1の制御信号が供給されるゲート電極、前記第2の記憶回路の信号が供給される第1の電極およびチャネルが形成される酸化物半導体層を有する第1のトランジスタと、

前記第1のトランジスタの第2の電極と電気的に接続される第1の電極および低電源電位が供給される第2の電極を有する第1の容量素子と、

前記第1のトランジスタの第2の電極と電気的に接続されるゲート電極および前記第1の容量素子の第2の電極と電気的に接続される第1の電極を有する第2のトランジスタと、

前記第2のトランジスタの第2の電極と電気的に接続される第1の電極および第2の制御信号が供給されるゲート電極を有する第3のトランジスタと、

前記第3のトランジスタの第2の電極と電気的に接続される第1の電極、前記第3のトランジスタのゲート電極と電気的に接続されるゲート電極および高電源電位が供給される第2の電極を有する第4のトランジスタと、

前記第4のトランジスタの第1の電極と電気的に接続される第1の電極および前記第2のトランジスタの第1の電極と電気的に接続される第2の電極を有する第2の容量素子と、

前記第2の容量素子の第1の電極と電気的に接続される信号端子を備え、

前記選択部が、前記第1の状態において、前記第1の記憶部から供給される信号を選択し、前記第2の状態において、前記選択回路から供給される信号を選択する、請求項3記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、物、方法、または、製造方法に関する。または、本発明は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関する。特に、本発明は、例えば、半導体装置、表示装置、発光装置、蓄電装置、それらの駆動方法、または、それらの製造方法に関する。特に、本発明は、半導体装置に関する。特に、スキャンテストが可能な論理回路を備える半導体装置に関する。

10

20

30

40

50

## 【背景技術】

## 【0002】

記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する記憶素子が知られている。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容（データ）を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態（オン状態、またはオフ状態）に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

10

## 【先行技術文献】

## 【特許文献】

## 【0003】

## 【特許文献1】特開2013-9297号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0004】

複数の組み合わせ回路を有する論理回路の検証は、規模が大きいほど困難になる。

## 【0005】

論理回路内の組み合わせ回路の動作を検証する方法の一つにスキャンテストがある。スキャンテストは、組み合わせ回路を接続するフリップフロップ回路（FF回路ともいう）を利用する方法である。

20

## 【0006】

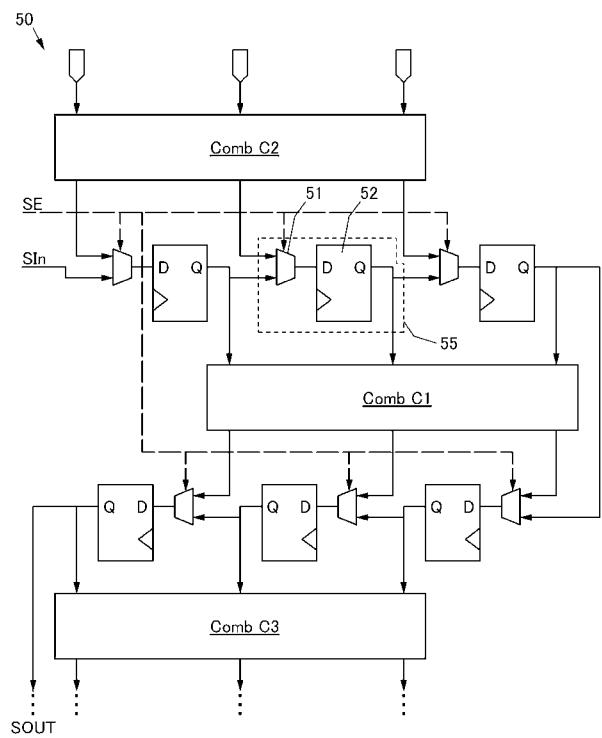

スキャンテストを可能にするには、マルチプレクサ（MUX）を組み合わせ回路とFF回路の間に設ける必要がある。スキャンテストを適用できる論理回路の構成の一例を、図9に示す。

## 【0007】

論理回路50は、マルチプレクサ51を組み合わせ回路CombC2とFF回路52の間に備える。また、マルチプレクサ51は、前段の組み合わせ回路CombC2から供給される信号またはスキャンイン端子から供給される信号（SIn）およびスキャンインエーブル信号（SE）が供給される。

30

## 【0008】

この構成によれば、スキャンインエーブル信号（SE）を用いて、前段の組み合わせ回路から供給される信号またはスキャンイン端子から供給される信号（SIn）のいずれか一方を選択し、FF回路に供給できる。

## 【0009】

また、スキャンインエーブル信号（SE）を用いて、FF回路をマルチプレクサで数珠つなぎにし、シフトレジスタ（スキャンチェーンともいう）を形成できる。スキャンテストの初期値を含むように生成されたシリアルのスキャンイン信号（SIn）を形成されたシフトレジスタにスキャンイン端子から供給すると、各FF回路に当該初期値を設定できる。

40

## 【0010】

なお、スキャンチェーンを構成するマルチプレクサ51とFF回路52を含む回路（図9参照）を、スキャンフリップフロップ55（スキャンFFともいう）という。

## 【0011】

スキャンテストは、各スキャンFFに初期値を設定する第1のステップと、当該初期値を各組み合わせ回路に供給する第2のステップを含む。また、各スキャンFFに各組み合わせ回路の演算結果を供給する第3のステップと、各組み合わせ回路から供給された信号を、スキャンチェーンをシフトすることにより、スキャンチェーンの最終端から回収する第4のステップと、を含む。なお、最終端に供給される信号（SOUT）を解析することで、複数の組み合わせ回路の動作を検証することができる。

50

**【 0 0 1 2 】**

しかし、組み合わせ回路と F F 回路の間に設けられるマルチプレクサが信号の伝達において負荷となり、信号の遅延等が発生する場合がある。これにより、例えば、セットアップ時間違反が発生する場合がある。または、動作周波数を抑制する必要から、論理回路の性能を十分に引き出すことができない場合がある。

**【 0 0 1 3 】**

本発明の一態様は、このような技術的背景のもとでなされたものである。したがって、論理回路に与える負荷が低減された新規な半導体装置を提供することを課題の一とする。または、本発明の一態様は、配線間に大量に電流が流れるのを防ぐことができる半導体装置などの提供を、課題の一つとする。または、本発明の一態様は、破損が引き起こされことを低減することができる半導体装置などの提供を、課題の一つとする。または、本発明の一態様は、貫通電流が流れることを低減することができる半導体装置などの提供を、課題の一つとする。または、本発明の一態様は、オフ電流の低い半導体装置などを提供することを課題とする。または、本発明の一態様は、消費電力の低い半導体装置などを提供することを課題とする。または、本発明の一態様は、目に優しい表示装置などを提供することを課題とする。または、本発明の一態様は、透明な半導体層を用いた半導体装置などを提供することを課題とする。または、本発明の一態様は、信頼性の高い半導体層を用いた半導体装置などを提供することを課題とする。または、本発明の一態様は、新規な半導体装置などを提供することを課題とする。または、本発明の一態様は、良い半導体装置などを提供することを課題とする。

10

20

**【 0 0 1 4 】**

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

30

**【課題を解決するための手段】****【 0 0 1 5 】**

本発明の一態様は、第 1 の組み合わせ回路と、第 1 の組み合わせ回路に第 1 のデータ信号を供給することができる第 1 の記憶回路と、第 1 の組み合わせ回路に第 2 のデータ信号を供給することができる第 2 の記憶回路と、第 1 の記憶回路および第 2 の記憶回路に選択信号を供給することができる選択信号線と、第 1 の記憶回路に第 1 のデータ信号を供給し第 2 の記憶回路に第 2 のデータ信号を供給することができる第 2 の組み合わせ回路と、を有する半導体装置である。そして、第 2 の記憶回路は、第 2 の組み合わせ回路から供給される信号を選択する第 1 の状態と、第 1 の記憶回路から供給される信号を選択する第 2 の状態とを、選択信号により選択する機能を備える。

40

**【 0 0 1 6 】**

また、本発明の一態様は、第 2 の記憶回路が、第 2 のデータ信号が供給される第 1 の記憶部と、第 1 の記憶部、第 1 の記憶回路並びに選択信号線からそれぞれ信号が供給される選択部と、選択部に選択された信号が供給され第 1 の組み合わせ回路に信号を供給する第 2 の記憶部と、を有する上記の半導体装置である。そして、選択部が、第 1 の状態において、第 1 の記憶部から供給される信号を選択し、第 2 の状態において、第 1 の記憶回路から供給される信号を選択する。

**【 0 0 1 7 】**

上記本発明の一態様の半導体装置は、第 2 の組み合わせ回路がデータ信号を、第 1 の記憶回路が信号（例えば、スキャンイン信号）を、それぞれ第 2 の記憶回路に供給することができる構成を有する。第 2 の記憶回路は供給された信号を選択して、後段の回路に供給することができる。これにより、選択回路を第 2 の記憶回路と第 2 の組み合わせ回路に設ける必要がない。その結果、第 2 の組み合わせ回路は遅延の発生が抑制された信号を第 2 の記憶回路に供給することができ、論理回路に与える負荷が低減された新規な半導体装置を提供できる。

50

**【 0 0 1 8 】**

また、本発明の一態様は、第1の組み合わせ回路と、第1の組み合わせ回路に第1のデータ信号を供給することができる第1の記憶回路と、第1の組み合わせ回路に第2のデータ信号を供給することができる第2の記憶回路と、第1の記憶回路および第2の記憶回路に第1の選択信号を供給することができる第1の選択信号線と、第2の記憶回路に供給する信号を選択することができる選択回路と、選択回路に第3のデータ信号を供給することができる副記憶回路と、選択回路を制御する第2の選択信号を供給することができる第2の選択信号線と、第1の記憶回路に第1のデータ信号を供給し第2の記憶回路に第2のデータ信号を供給することができる第2の組み合わせ回路と、を有する半導体装置である。そして、第2の記憶回路は、第2の組み合わせ回路から供給される信号を選択する第1の状態と、第1の記憶回路から供給される信号を選択する第2の状態と、を選択信号により選択する機能を備え、選択回路は、副記憶回路が供給する信号を供給する状態と、第1の記憶回路が供給する信号を供給する状態と、を第2の選択信号により選択する機能を備える。

10

**【 0 0 1 9 】**

また、本発明の一態様は、第2の記憶回路が、第2のデータ信号が供給される第1の記憶部と、第1の記憶部、選択回路並びに第1の選択信号線からそれぞれ信号が供給される選択部と、選択部に選択された信号が供給され、第1の組み合わせ回路に信号を供給する第2の記憶部と、を有する上記の半導体装置である。そして、選択部が第1の状態において第1の記憶部から供給される信号を選択し、第2の状態において選択部が選択回路から供給される信号を選択する。

20

**【 0 0 2 0 】**

上記本発明の一態様の半導体装置は、第2の組み合わせ回路がデータ信号または選択回路に選択される信号（例えば、スキャンイン信号または副記憶回路から供給される信号）を、第2の記憶回路に供給できる構成を有する。第2の記憶回路は供給された信号を選択して、後段の回路に供給することができる。これにより、第2の記憶回路と第2の組み合わせ回路の間に選択回路を設ける必要がない。また、第3のデータを副記憶回路から第2の記憶回路に高速に転送することができる。その結果、第2の組み合わせ回路は遅延の発生が抑制された信号を第2の記憶回路に供給することができ、論理回路に与える負荷が低減された新規な半導体装置を提供できる。

30

**【 0 0 2 1 】**

また、本発明の一態様は、第2の記憶回路が、第2のデータ信号が供給される第1の記憶部と、第1の記憶部、選択回路並びに第1の選択信号線からそれぞれ信号が供給される選択部と、選択部に選択された信号が供給され、第1の組み合わせ回路に信号を供給する第2の記憶部と、を有する上記の半導体装置である。そして、副記憶回路は、第2の記憶回路から供給される信号を記憶する機能を備え、選択部が第1の状態において第1の記憶部から供給される信号を選択し、第2の状態において選択部が選択回路から供給される信号を選択する半導体装置である。

30

**【 0 0 2 2 】**

上記本発明の一態様の半導体装置は、副記憶回路に第2の記憶回路の信号を待避することができる構成を有する。また、副記憶回路に待避した信号を選択回路が選択して第2の記憶回路に供給することができる構成を有する。これにより、半導体装置の第1の動作状態を副記憶回路に記憶させることができる。半導体装置に他の動作させた後に、副記憶回路に第1の動作状態を供給させることで、半導体装置を素早く第1の動作状態に復帰させることができる。また、選択回路を第2の記憶回路と第2の組み合わせ回路の間に設ける必要がない。その結果、第2の組み合わせ回路は遅延の発生が抑制された信号を第2の記憶回路に供給することができ、論理回路に与える負荷が低減された新規な半導体装置を提供できる。

40

**【 0 0 2 3 】**

また、本発明の一態様は、第2の記憶回路が、第2のデータ信号が供給される第1の記憶

50

部と、第1の記憶部、選択回路並びに第1の選択信号線からそれぞれ信号が供給される選択部と、選択部に選択された信号が供給され、第1の組み合わせ回路に信号を供給する第2の記憶部と、を有する半導体装置である。そして、副記憶回路は、第1の制御信号が供給されるゲート電極、第2の記憶回路の信号が供給される第1の電極およびチャネルが形成される酸化物半導体層を有する第1のトランジスタと、第1のトランジスタの第2の電極と電気的に接続される第1の電極および低電源電位が供給される第2の電極を有する第1の容量素子と、第1のトランジスタの第2の電極と電気的に接続される第1の電極を有する第2のトランジスタと、第2のトランジスタの第2の電極と電気的に接続される第1の電極および第2の制御信号が供給されるゲート電極を有する第3のトランジスタと、第3のトランジスタの第2の電極と電気的に接続される第1の電極、第3のトランジスタのゲート電極と電気的に接続されるゲート電極および高電源電位が供給される第2の電極を有する第4のトランジスタと、第4のトランジスタの第1の電極と電気的に接続される第2の電極を有する第2の容量素子と、第2の容量素子の第1の電極と電気的に接続される信号端子を備え、選択部が第1の状態において第1の記憶部から供給される信号を選択し、第2の状態において選択部が選択回路から供給される信号を選択する。

10

## 【0024】

なお、本明細書中において、トランジスタの第1の電極または第2の電極の一方がソース電極を、他方がドレイン電極を指す。

20

## 【発明の効果】

## 【0025】

本発明の一態様によれば、論理回路に与える負荷が低減された新規な半導体装置を提供できる。

## 【図面の簡単な説明】

## 【0026】

【図1】実施の形態に係る半導体装置の構成を説明するブロック図。

【図2】実施の形態に係る記憶回路の構成を説明する回路図および動作を説明するタイミングチャート。

30

## 【図3】実施の形態に係る半導体装置を説明するブロック図。

## 【図4】実施の形態に係る記憶回路を説明するブロック図。

## 【図5】実施の形態に係る副記憶回路を説明するタイミングチャート。

## 【図6】実施の形態に係る記憶回路の構成を説明する回路図。

## 【図7】実施の形態に係る記憶回路の構成を説明する回路図。

## 【図8】実施の形態に係る記憶回路の構成を説明する回路図。

## 【図9】スキャンテストを適用できる論理回路の構成を説明する図。

## 【図10】記憶回路の断面の構造を示す図。

## 【図11】電子機器の図。

## 【発明を実施するための形態】

## 【0027】

そこで、上記課題を解決するために、本発明の一態様は、組み合わせ回路、組み合わせ回路を接続するフリップフロップ回路および組み合わせ回路とフリップフロップ回路の間に設けるマルチプレクサに着眼した。以下に説明する実施の形態には、組み合わせ回路を接続する記憶回路の構成に着眼して創作された本発明の一態様が含まれる。

40

## 【0028】

本発明の一態様の半導体装置は、複数のデータ信号と選択信号が供給される記憶回路が、2つの組み合わせ回路を接続する構成を有する。そして、当該記憶回路が選択信号により複数のデータ信号から一を選択する機能を備える。

## 【0029】

上記本発明の一態様の半導体装置によれば、選択回路を第2の記憶回路と第2の組み合わ

50

せ回路の間に設ける必要がない。その結果、第2の組み合わせ回路は遅延の発生が抑制された信号を第2の記憶回路に供給することができ、論理回路に与える負荷が低減された新規な半導体装置を提供できる。

### 【0030】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更しえることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

10

### 【0031】

#### (実施の形態1)

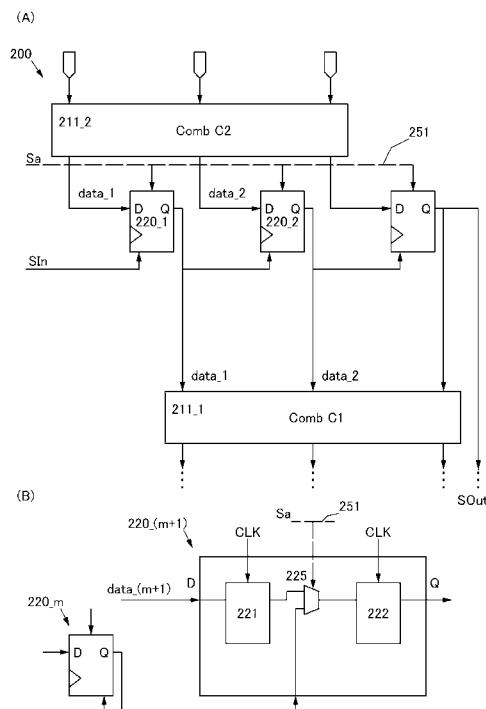

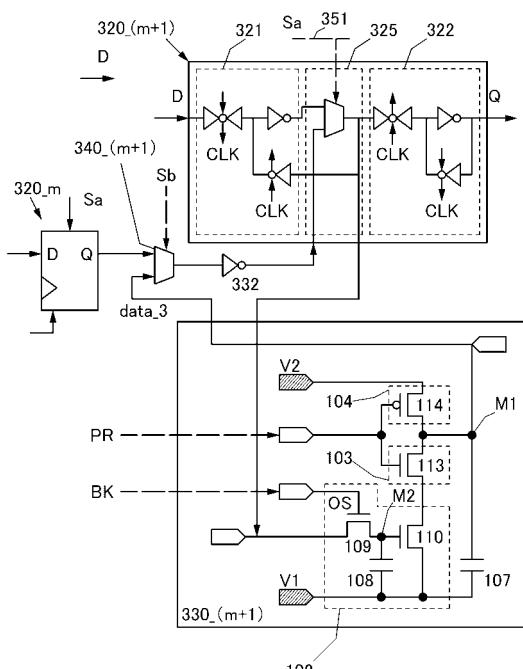

本実施の形態では、本発明の一態様の半導体装置の構成について、図1および図2を参照しながら説明する。

### 【0032】

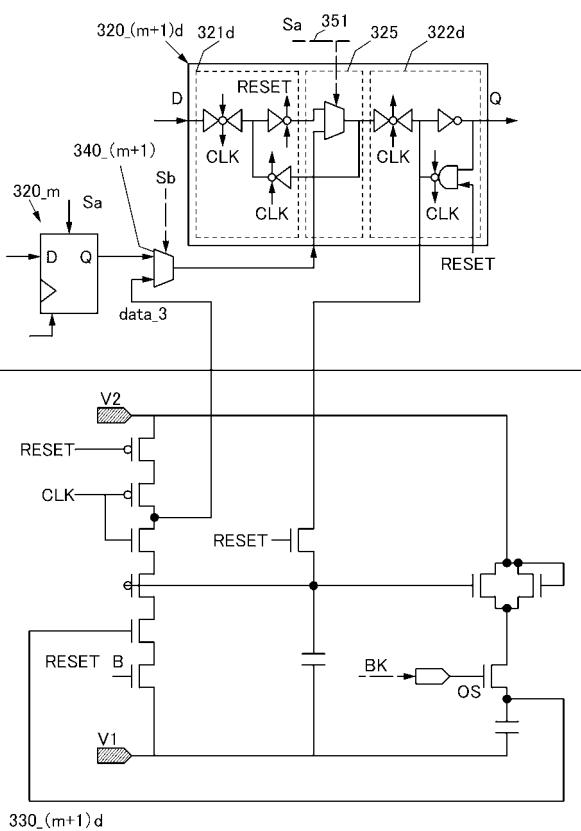

図1(A)は本発明の一態様の半導体装置の構成を説明するブロック図であり、図1(B)は本発明の一態様の半導体装置に含まれる第2の記憶回路の構成を説明するブロック図である。

20

### 【0033】

本実施の形態で例示する半導体装置200は複数の記憶回路を備える。なお、説明の便宜のため、第1の記憶回路220\_1および第2の記憶回路220\_2を符号と共に図1(A)に示し、他の記憶回路は図示しない。

### 【0034】

なお、選択信号Sa、スキャンイン信号SIn、スキャンアウトSOut信号並びにクロック信号CLKを図中に示す。

### 【0035】

本実施の形態で例示して説明する半導体装置200は、第1の組み合わせ回路211\_1と、第1の組み合わせ回路211\_1に第1のデータ信号data\_1を供給することができる第1の記憶回路220\_1と、第1の組み合わせ回路211\_1に、第2のデータ信号data\_2を供給することができる第2の記憶回路220\_2と、を有する(図1(A)参照)。

30

### 【0036】

また、第1の記憶回路220\_1および第2の記憶回路220\_2の状態を第1の状態(S1)または第2の状態(S2)にする選択信号Saを、供給することができる選択信号線251を有する。

### 【0037】

また、第1の状態(S1)の第1の記憶回路220\_1に第1のデータ信号data\_1を供給し、第1の状態(S1)の第2の記憶回路220\_2に第2のデータ信号data\_2を供給することができる第2の組み合わせ回路211\_2と、を有する。

40

### 【0038】

そして、第2の記憶回路220\_2は、第2の組み合わせ回路211\_2から供給される第2のデータ信号data\_2を選択する第1の状態(S1)と、第1の記憶回路220\_1から供給される信号(例えば、第1のデータ信号data\_1)を選択する第2の状態(S2)とを、選択信号Saにより選択する機能を備える。

### 【0039】

記憶回路の詳細な構成のブロック図を図1(B)に示す。説明のため、m(半導体装置200に設けられた接続可能な記憶回路の数をnとするとき、mは1以上(n-1)以下の整数)番目と(m+1)番目の記憶回路のみを示す。

### 【0040】

記憶回路220\_(m+1)は、データ信号data\_(m+1)が供給される第1の記

50

憶部 221 と、第 1 の記憶部 221、記憶回路 220\_m 並びに選択信号線 251 からそれぞれ信号が供給される選択部 225 と、を有する。

【0041】

また、第 2 の記憶部 222 は、選択部 225 に選択された信号が供給され、第 1 の組み合せ回路 211\_1 に信号を供給する。

【0042】

なお、第 1 の状態 (S1) の記憶回路 220\_(m+1) において、選択部 225 が第 1 の記憶部 221 から供給される信号を選択し、第 2 の記憶部 222 に供給する。

【0043】

また、第 2 の状態 (S2) の記憶回路 220\_(m+1) において、選択部 225 が記憶回路 220\_m から供給される信号を選択する。

【0044】

言い換えると、選択部 225 が第 1 の記憶部 221 から供給される信号を第 2 の記憶部 222 に供給する状態が第 1 の状態である。また、選択部 225 が記憶回路 220\_m から供給される信号を第 2 の記憶部 222 に供給する状態が第 2 の状態である。

【0045】

上記本発明の一態様の半導体装置 200 は、第 2 の組み合せ回路 211\_2 がデータ信号（例えば、第 2 のデータ信号 data\_2）を第 2 の記憶回路 220\_2 に供給することができ、第 1 の記憶回路 220\_1 が信号（例えば、スキャンイン信号）を第 2 の記憶回路に供給することができる構成を有する。第 2 の記憶回路 220\_2 は供給された信号のいずれか一方を選択して、後段の回路に供給することができる。

【0046】

これにより、選択回路を記憶回路と組み合せ回路の間（例えば、第 2 の記憶回路 220\_2 と第 2 の組み合せ回路 211\_2 の間）に設ける必要がない。その結果、組み合せ回路は、遅延の発生が抑制されたデータ信号を記憶回路に供給することができ、論理回路に与える負荷が低減された新規な半導体装置 200 を提供できる。

【0047】

また、本実施の形態で例示して説明する半導体装置 200 は、第 2 の状態 (S2) にする選択信号を各記憶回路に供給することにより、m 番目の記憶回路と (m+1) 番目の記憶回路を数珠繋ぎにして、シフトレジスタを形成することができる。これにより、スキャンテストの初期値を含むように生成されたシリアルのスキャンイン信号 SIn を、第 2 の状態 (S2) の第 1 の記憶回路 220\_1 から各記憶回路に供給することができる。

【0048】

そして、第 1 の状態 (S1) にする選択信号を各記憶回路に供給することにより、スキャンイン信号を各記憶回路から組み合せ回路に供給することができる。

【0049】

また、スキャンテストの実行後に、再度第 2 の状態 (S2) にする選択信号を各記憶回路に供給することによりシフトレジスタを形成することができる。これにより、スキャンテストの結果を含むシリアルのスキャンアウト信号 (SOut) を、第 2 の状態 (S2) の第 n の記憶回路から回収できる。

【0050】

<記憶回路の構成例>

以下に、本発明の一態様の半導体装置 200 に適用することができる記憶回路 220\_(m+1) の構成を説明する。

【0051】

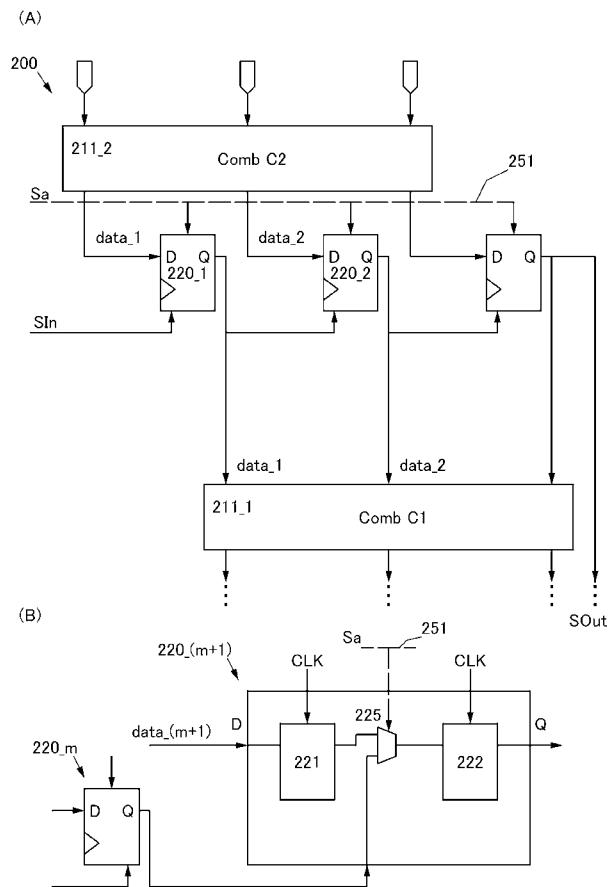

図 2 (A) は、本発明の一態様の半導体装置に適用することができる記憶回路の一例を説明する回路図である。

【0052】

記憶回路 220\_(m+1) は、第 1 の記憶部 221、第 2 の記憶部 222 および選択部 225 を有する。クロック信号により制御されたラッチ回路は、第 1 の記憶部 221 およ

10

20

30

40

50

び第2の記憶部222に適用できる。

【0053】

第1の記憶部221は、トランスマッシュゲート221a、インバータ221bおよびクロックドインバータ221cで構成されている。第2の記憶部222は、トランスマッシュゲート222a、インバータ222bおよびクロックドインバータ222cで構成されている。選択部225は、例えばマルチプレクサを適用できる。

【0054】

なお、第2の状態(S2)にする選択信号を各記憶回路に供給することにより、m番目の記憶回路と(m+1)番目の記憶回路を数珠繋ぎにして、シフトレジスタを形成することができる。図2(A)に例示する構成によれば、m番目の記憶回路220\_mが供給する信号が、(m+1)番目の記憶回路220\_(m+1)の第2の記憶部222に供給される。記憶回路220\_(m+1)の第2の記憶部222は、供給された信号を反転してQ端子に出力する点に留意する必要がある。

10

【0055】

これを避けるため、m番目の記憶回路220\_mが供給する信号をあらかじめ反転するためのインバータを、m番目の記憶回路のQ端子とマルチプレクサとの間(例えば、選択部225)に設けてもよい。

【0056】

<記憶回路の動作例>

以下に、第1の記憶回路220\_1の動作例を、図2(B)を用いて説明する。図2(B)は、第1の記憶回路220\_1の動作を説明するタイミングチャートである。

20

【0057】

図2(B)中、Dは第1の記憶回路220\_1のD端子に供給される第1のデータ信号data\_1であり、Qは第1の記憶回路220\_1のQ端子から供給される信号である。SInは第1の記憶回路220\_1に供給されるスキャンイン信号SInであり、CLKは第1の記憶回路220\_1に供給されるクロック信号CLKである。

30

【0058】

Saは第1の記憶回路220\_1に供給される選択信号Saである。選択信号Saは、第1の期間T1および第3の期間T3においてハイの状態であり、第2の期間T2においてロ-の状態を含む。

30

【0059】

第1の記憶回路220\_1は、選択信号Saがハイである期間(期間T1および期間T3)において第2の状態(S2)となる。その結果、スキャンイン信号SInがQ端子に出力される。

【0060】

第1の記憶回路220\_1は、選択信号Saがロ-である期間T2において第1の状態(S1)となる。その結果、第1のデータ信号data\_1がQ端子に出力される。

40

【0061】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0062】

(実施の形態2)

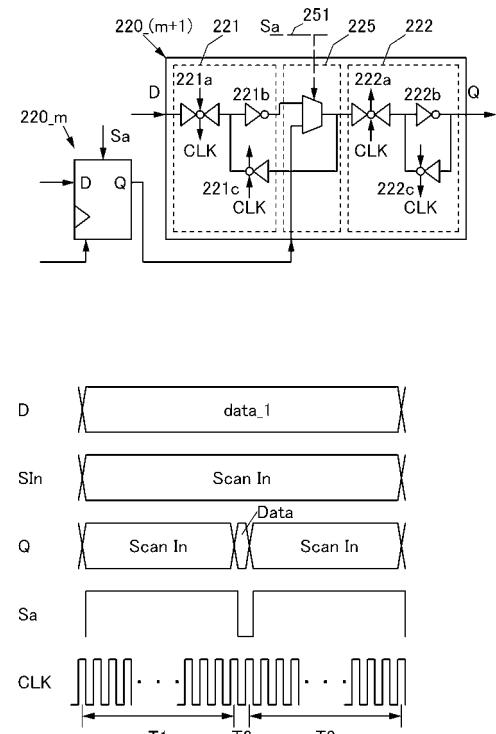

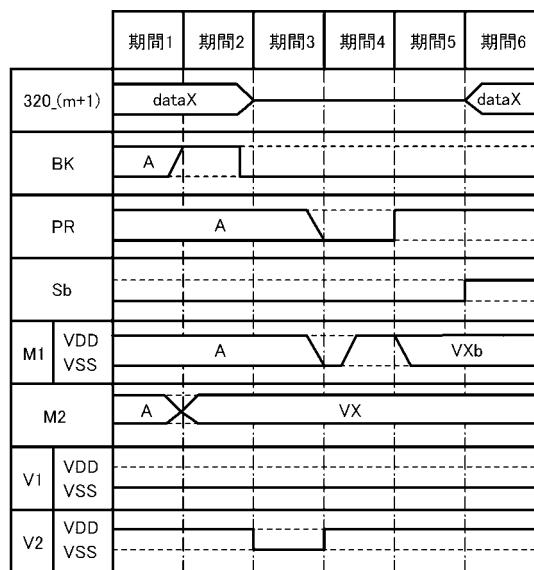

本実施の形態では、本発明の一態様の半導体装置の構成について、図3および図4を参照しながら説明する。

【0063】

図3(A)は本発明の一態様の半導体装置の構成を説明するブロック図であり、図3(B)は本発明の一態様の半導体装置に含まれる第2の記憶回路の構成を説明するブロック図である。

【0064】

本実施の形態で例示する半導体装置300は複数の記憶回路を備える。なお、説明の便宜

50

のため、第1の記憶回路320\_1および第2の記憶回路320\_2を符号と共に図3(A)に示し、他の記憶回路は図示しない。

【0065】

なお、第1の選択信号S<sub>a</sub>、第2の選択信号S<sub>b</sub>、スキャンイン信号S<sub>In</sub>、スキャンアウトS<sub>Out</sub>信号並びにクロック信号C<sub>LK</sub>を図中に示す。また、第1の制御信号B<sub>K</sub>および第2の制御信号P<sub>R</sub>を図中に示す。なお、第2の選択信号S<sub>b</sub>と同じ信号を第2の制御信号P<sub>R</sub>に用いることができる。

【0066】

本実施の形態で例示して説明する半導体装置300は、第1の組み合わせ回路311\_1と、第1の組み合わせ回路311\_1に第1のデータ信号data\_1を供給することができる第1の記憶回路320\_1と、第1の組み合わせ回路311\_1に、第2のデータ信号data\_2を供給することができる第2の記憶回路320\_2と、を有する(図3(A)参照)。

10

【0067】

また、第1の記憶回路320\_1および第2の記憶回路320\_2に第1の選択信号S<sub>a</sub>を供給することができる第1の選択信号線351を有する。

【0068】

そして、第2の記憶回路320\_2に供給する信号を選択することができる選択回路340\_2と、選択回路340\_2に、第3のデータ信号data\_3を供給することができる副記憶回路330\_2と、を有する。

20

【0069】

また、選択回路340\_2を制御する第2の選択信号S<sub>b</sub>を、供給することができる第2の選択信号線352を有する。

【0070】

また、第1の記憶回路320\_1に第1のデータ信号data\_1を供給し、第2の記憶回路320\_2に第2のデータ信号data\_2を供給することができる第2の組み合わせ回路311\_2と、を有する。

30

【0071】

そして、第2の記憶回路320\_2は、第2の組み合わせ回路311\_2から供給される第2のデータ信号data\_2を選択する第1の状態(S1)と、第1の記憶回路320\_1から供給される信号(例えば、第1のデータ信号data\_1)を選択する第2の状態(S2)と、を第1の選択信号S<sub>a</sub>により選択する機能を備える。

【0072】

そして、選択回路340\_2は、副記憶回路330\_2が供給する信号を供給する状態と、第1の記憶回路320\_1が供給する信号を供給する状態と、を第2の選択信号により選択する機能を備える。

40

【0073】

記憶回路の詳細な構成のブロック図を図3(B)に示す。説明のため、m(半導体装置300に設けられた接続可能な記憶回路の数をnとするとき、mは1以上(n-1)以下の整数)番目と(m+1)番目の記憶回路のみを示す。

【0074】

記憶回路320\_(m+1)は、データ信号data\_(m+1)が供給される第1の記憶部321と、第1の記憶部321、選択回路340\_(m+1)並びに第1の選択信号線351からそれぞれ信号が供給される選択部325と、を有する。

【0075】

また、第2の記憶部322は、選択部325に選択された信号が供給され、第1の組み合わせ回路311\_1に信号を供給する。

【0076】

なお、第1の状態(S1)の記憶回路320\_(m+1)において、選択部325が第1の記憶部321から供給される信号を選択し、第2の記憶部322に供給する。

50

## 【0077】

また、第2の状態(S2)の記憶回路320\_\_(m+1)において、選択部325が選択回路340\_\_(m+1)から供給される信号を選択する半導体装置である。

## 【0078】

言い換えると、選択部325が、第1の記憶部321に供給される信号を第2の記憶部322に供給する状態が第1の状態である。また、選択部325が、選択回路340\_\_(m+1)に供給される信号を第2の記憶部322に供給する状態が第2の状態である。

## 【0079】

上記本発明の一態様の半導体装置300は、第2の組み合わせ回路311\_\_2がデータ信号(例えば、第1のデータ信号data\_1および第2のデータ信号data\_2)または選択回路(例えば、選択回路340\_\_2)に選択される信号(例えば、スキャンイン信号SInまたは副記憶回路330に供給される信号)を第2の記憶回路320\_\_2に供給できる構成を有する。第2の記憶回路320\_\_2は供給された信号を選択して、後段の回路に供給することができる。

10

## 【0080】

これにより、選択回路を記憶回路と組み合わせ回路の間(例えば、第2の記憶回路320\_\_2と第2の組み合わせ回路311\_\_2の間)に設ける必要がない。また、第3のデータ信号data\_3を副記憶回路330\_\_2から第2の記憶回路320\_\_2に高速に転送することができる。その結果、第2の組み合わせ回路311\_\_2は遅延の発生が抑制された信号を第2の記憶回路320\_\_2に供給することができ、論理回路に与える負荷が低減された新規な半導体装置300を提供できる。

20

## 【0081】

また、記憶回路320\_\_(m+1)は、データ信号data\_\_(m+1)が供給される第1の記憶部321と、第1の記憶部321、選択回路340\_\_(m+1)並びに第1の選択信号線351からそれぞれ信号が供給される選択部325と、を有する。

## 【0082】

また、第2の記憶部322は、選択部325に選択された信号が供給され、第1の組み合わせ回路311\_\_1に信号を供給する。

## 【0083】

また、副記憶回路330\_\_(m+1)は、第2の記憶回路に供給される信号(例えば、第1の記憶部321に供給される信号)を記憶することができる。

30

## 【0084】

なお、第1の状態(S1)の記憶回路320\_\_(m+1)において、選択部325が第1の記憶部321から供給される信号を選択し、第2の記憶部322に供給する。

## 【0085】

また、第2の状態(S2)の記憶回路320\_\_(m+1)において、選択部325が選択回路340\_\_(m+1)から供給される信号を選択する半導体装置である。

## 【0086】

言い換えると、選択部325が、第1の記憶部321に供給される信号を第2の記憶部322に供給する状態が第1の状態である。また、選択部325が、選択回路340\_\_(m+1)に供給される信号を第2の記憶部322に供給する状態が第2の状態である。

40

## 【0087】

上記本発明の一態様の半導体装置300は、副記憶回路330\_\_2に第2の記憶回路320\_\_2の信号を待避することができる構成を有する。また、副記憶回路330\_\_2に待避した信号を選択回路340\_\_2が選択して第2の記憶回路320\_\_2に供給することができる構成を有する。これにより、半導体装置300の第1の動作状態を副記憶回路に記憶させることができる。半導体装置300に他の動作をさせた後に、副記憶回路に第1の動作状態を供給させることで、半導体装置300を素早く第1の動作状態に復帰(リカバリートもいう)させることができる。また、選択回路を第2の記憶回路と第2の組み合わせ回路311\_\_2の間に設ける必要がない。その結果、第2の組み合わせ回路311\_\_2は

50

遅延の発生が抑制された信号を第2の記憶回路に供給することができ、論理回路に与える負荷が低減された新規な半導体装置を提供できる。

#### 【0088】

また、本発明の一態様の半導体装置300は、第2の組み合わせ回路が第2の記憶回路に信号を供給することができる信号線とは別に、副記憶回路が記憶した第1の動作状態を第2の記憶回路に供給することができる信号線を有する。副記憶回路が記憶した第1の動作状態を第2の記憶回路に供給することができる信号線は、スキャンチェーンを形成する際に利用することができる。これにより、第2の組み合わせ回路が第2の記憶回路に信号を供給することができる信号線にマルチプレクサを設けることなく、スキャンテストを適用することができる半導体装置を提供できる。

10

#### 【0089】

##### <記憶回路の構成例>

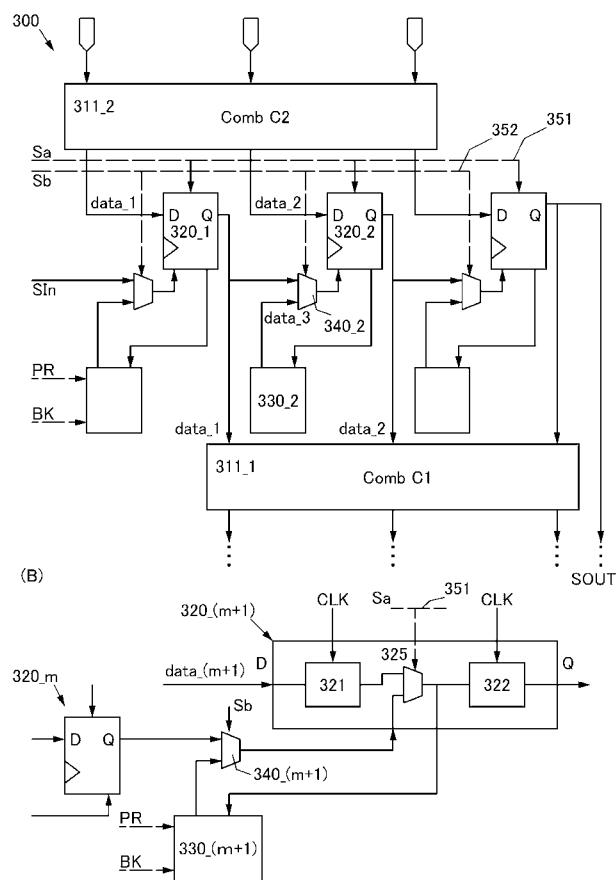

以下に、本発明の一態様の半導体装置300に適用することができる記憶回路320<sub>(m+1)</sub>の構成を説明する。

#### 【0090】

図4は、本発明の一態様の半導体装置に適用することができる記憶回路320<sub>(m+1)</sub>および副記憶回路330<sub>(m+1)</sub>の一例を説明する回路図である。

#### 【0091】

記憶回路320<sub>(m+1)</sub>は、第1の記憶部321、第2の記憶部322および選択部325を有する。クロック信号により制御されたラッチ回路は、第1の記憶部321および第2の記憶部322に適用できる。なお、記憶回路320<sub>(m+1)</sub>の構成は、図2(A)を用いて説明した記憶回路220<sub>(m+1)</sub>と同様であるため、詳細な説明は省略する。

20

#### 【0092】

なお、記憶回路320<sub>(m+1)</sub>の第2の記憶部322は、供給された信号を反転してQ端子に出力するため、インバータ332が選択回路340<sub>(m+1)</sub>の後段に設けられている。

#### 【0093】

##### <副記憶回路の構成例>

以下に、本発明の一態様の半導体装置300に適用することができる副記憶回路330<sub>(m+1)</sub>の構成を説明する。

30

#### 【0094】

副記憶回路330<sub>(m+1)</sub>は、副記憶回路部102と、スイッチ103と、スイッチ104を含んで構成される。また、副記憶回路330<sub>(m+1)</sub>は、第1のトランジスタ109と、第2のトランジスタ110と、第3のトランジスタ113と第4のトランジスタ114とを有する。また、第1の容量素子108と第2の容量素子107を有する。

#### 【0095】

なお、副記憶回路330<sub>(m+1)</sub>は、第1のトランジスタ109の第1の電極に供給された信号を記憶する。そして、副記憶回路330<sub>(m+1)</sub>は、記憶した信号を第3のトランジスタの第2の電極、第4のトランジスタの第1の電極および第2の容量素子の第1の電極と電気的に接続される端子に供給する。

40

#### 【0096】

記憶回路320<sub>(m+1)</sub>の選択部325が選択した信号が第1のトランジスタ109の第1の電極に供給され、副記憶回路330は、記憶した信号を第3のトランジスタの第2の電極、第4のトランジスタの第1の電極および第2の容量素子の第1の電極と電気的に接続される端子から選択回路340<sub>(m+1)</sub>に供給する。

#### 【0097】

第1のトランジスタ109は、第1の制御信号BKが供給されるゲート電極と、第2の記憶回路の信号が供給される第1の電極と、チャネルが形成される酸化物半導体層を有する。

50

## 【0098】

第1の容量素子108は、第1のトランジスタ109の第2の電極と電気的に接続される第1の電極および低電源電位が供給される第2の電極を有する。

## 【0099】

第2のトランジスタ110は、第1のトランジスタ109の第2の電極と電気的に接続されるゲート電極および第1の容量素子108の第2の電極と電気的に接続される第1の電極を有する。

## 【0100】

第3のトランジスタ113は、第2のトランジスタ110の第2の電極と電気的に接続される第1の電極および第2の制御信号PRが供給されるゲート電極を有する。 10

## 【0101】

第4のトランジスタ114は、第3のトランジスタ113の第2の電極と電気的に接続される第1の電極、第3のトランジスタ113のゲート電極と電気的に接続されるゲート電極および高電源電位が供給される第2の電極を有する。

## 【0102】

第2の容量素子107は、第4のトランジスタ114の第1の電極と電気的に接続される第1の電極および第2のトランジスタ110の第1の電極と電気的に接続される第2の電極を有する。

## 【0103】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。 20

## 【0104】

## (実施の形態3)

電源電圧の供給を停止した後も、書き込まれたデータを保持し続ける記憶回路は、本発明の一態様の半導体装置300の副記憶回路に適用することができる。

## 【0105】

電源電圧の供給を停止した後もデータを保持し続ける副記憶回路が適用された本発明の一態様の半導体装置300は、電源電圧の供給の後に電源電圧の供給を停止しても、再び電源電圧を供給することにより、電源電圧の供給を停止する前のデータに基づいて動作を再開できるため、電源電圧の供給を停止するデータの保持時における消費電力を削減された半導体装置を提供することができる。 30

## 【0106】

本実施の形態では、本発明の一態様の半導体装置300に適用することができ、電源電圧の供給を停止した後もデータを保持し続ける副記憶回路330\_(m+1)の駆動方法について、図5に示すタイミングチャートを参照しながら説明する。

## 【0107】

図5のタイミングチャートにおいて、320\_(m+1)は記憶回路320\_(m+1)に保持されているデータを示し、BKは第1の制御信号BKの電位を示し、PRは第2の制御信号PRの電位を示し、Sbは第2の選択信号Sbの電位を示し、V1は電位V1を示し、V2は電位V2を示す。電位V1と電位V2の電位差Vが0のときは、電源電圧が供給されていない場合に相当する。M1はノードM1の電位を示し、M2はノードM2の電位を示す。 40

## 【0108】

なお、以下に示す駆動方法では、図4に示した構成において、スイッチ103をnチャネル型トランジスタとし、スイッチ104をpチャネル型トランジスタとして、第2の制御信号PRがハイレベル電位の場合に、スイッチ103の第1の端子と第2の端子の間が導通状態となり、且つスイッチ104の第1の端子と第2の端子の間が非導通状態となり、第2の制御信号PRがローレベル電位の場合に、スイッチ103の第1の端子と第2の端子の間が非導通状態となり、且つスイッチ104の第1の端子と第2の端子の間が導通状態となる例を示す。 50

## 【0109】

また、選択回路 $340_{(m+1)}$ は、第2の選択信号Sbがハイレベル電位の場合に副記憶回路 $330_{(m+1)}$ に供給される信号が選択され、第2の選択信号Sbがローレベル電位の場合に記憶回路 $320_{(m+1)}$ に供給される信号が選択される例を示す。また、トランジスタ109をnチャネル型トランジスタとして、第1の制御信号BKがハイレベル電位の場合に、トランジスタ109がオン状態となり、第1の制御信号BKがローレベル電位の場合に、トランジスタ109がオフ状態となる例を示す。

## 【0110】

しかしながら、本発明の駆動方法はこれに限定されず、以下の説明における、スイッチ103、スイッチ104、選択回路 $340_{(m+1)}$ 、トランジスタ109の状態が同じとなるように、各制御信号の電位を定めることができる。10

## 【0111】

また、電位V1を低電源電位（以下、VSSと表記）とし、電位V2を高電源電位（以下、VDDと表記）とし、VDDとVSSとで切り替える場合の例を示す。VSSは例えば接地電位とすることができます。なお、本発明の駆動方法はこれに限定されず、電位V2をVSSとし、電位V1をVDDとVSSとで切り替えてよい。

## 【0112】

<通常動作>

図5中、期間1の動作について説明する。期間1では、電源電圧が副記憶回路 $330_{(m+1)}$ に供給されている。ここで、電位V2はVDDである。副記憶回路 $330_{(m+1)}$ へ電源電圧が供給されている間は、記憶回路 $320_{(m+1)}$ がデータ（図5中、dataXと表記）を保持する。この際、第2の選択信号Sbをローレベル電位として、副記憶回路 $330_{(m+1)}$ に供給される信号が選択回路 $340_{(m+1)}$ に選択されない状態とされる。20

## 【0113】

なお、スイッチ103及びスイッチ104の第1の端子と第2の端子の間の状態（導通状態、非導通状態）はどちらの状態であってもよい。即ち、第2の制御信号PRはハイレベル電位であってもローレベル電位であってもよい（図5中、Aと表記）。また、トランジスタ109の状態（オン状態、オフ状態）はどちらの状態であってもよい。即ち、第1の制御信号BKはハイレベル電位であってもローレベル電位であってもよい（図5中、Aと表記）。期間1において、ノードM1にはどのような電位であってもよい（図5中、Aと表記）。期間1において、ノードM2にはどのような電位であってもよい（図5中、Aと表記）。期間1の動作を通常動作と呼ぶ。30

## 【0114】

<電源電圧供給停止前の動作>

図5中、期間2の動作について説明する。副記憶回路 $330_{(m+1)}$ への電源電圧の供給の停止をする前に、第1の制御信号BKをハイレベル電位として、トランジスタ109をオン状態とする。

## 【0115】

こうして、記憶回路 $320_{(m+1)}$ に保持されたデータ（dataX）に対応する信号が、トランジスタ109を介してトランジスタ110のゲートに入力される。トランジスタ110のゲートに入力された信号は、容量素子108によって保持される。こうして、ノードM2の電位は、記憶回路 $320_{(m+1)}$ に保持されたデータに対応する信号電位（図5中、VXと表記）となる。40

## 【0116】

その後、第1の制御信号BKをローレベル電位としてトランジスタ109をオフ状態とする。こうして、 $(m+1)$ 番目の記憶回路 $320_{(m+1)}$ に保持されたデータに対応する信号が副記憶回路部102に保持される。期間2の間も、第2の選択信号Sbによって、副記憶回路 $330_{(m+1)}$ は選択回路 $340_{(m+1)}$ に選択されない状態とされる。スイッチ103及びスイッチ104の第1の端子と第2の端子の間の状態（導通

状態、非導通状態)はどちらの状態であってもよい。即ち、第2の制御信号PRはハイレベル電位であってもローレベル電位であってもよい(図5中、Aと表記)。期間2において、ノードM1にはどのような電位であってもよい(図5中、Aと表記)。期間2の動作を電源電圧供給停止前の動作と呼ぶ。

#### 【0117】

##### <電源電圧供給停止の動作>

図5中、期間3の動作について説明する。電源電圧供給停止前の動作を行った後、期間3のはじめに、副記憶回路330\_\_(m+1)への電源電圧の供給を停止する。電位V2はVSSとなる。電源電圧の供給が停止すると、記憶回路320\_\_(m+1)に保持されていたデータ(dataX)は消える。しかし、副記憶回路330\_\_(m+1)への電源電圧の供給が停止した後においても、容量素子108によって記憶回路320\_\_(m+1)に保持されていたデータ(dataX)に対応する信号電位(VX)がノードM2に保持される。

10

#### 【0118】

ここで、トランジスタ109としてチャネルが酸化物半導体層に形成されるトランジスタを用いている。ここで、トランジスタ109として、リーク電流(オフ電流)が極めて小さい、エンハンスマント型(ノーマリオフ型)のnチャネル型のトランジスタを用い、副記憶回路330\_\_(m+1)への電源電圧の供給が停止した際、トランジスタ109のゲートには接地電位(0V)が入力され続ける構成であるため、副記憶回路330\_\_(m+1)への電源電圧の供給が停止した後も、トランジスタ109のオフ状態を維持することができ、容量素子108によって保持された電位(ノードM2の電位VX)を長期間保つことができる。

20

#### 【0119】

こうして、副記憶回路330\_\_(m+1)は電源電圧の供給が停止した後も、データ(dataX)を保持する。期間3は、副記憶回路330\_\_(m+1)への電源電圧の供給が停止している期間に対応する。

20

#### 【0120】

##### <電源電圧供給再開の動作>

図5中、期間4の動作について説明する。副記憶回路330\_\_(m+1)への電源電圧の供給を再開し、電位V2をVDDにした後、第2の制御信号PRをローレベル電位として、スイッチ104の第1の端子と第2の端子の間を導通状態とし、スイッチ103の第1の端子と第2の端子の間を非導通状態とする。この際、第1の制御信号BKはローレベル電位であり、トランジスタ109はオフ状態のままである。また、第2の選択信号Sbはローレベル電位であり、副記憶回路330\_\_(m+1)が供給する信号は選択回路340\_\_(m+1)に選択されない状態である。

30

#### 【0121】

こうして、スイッチ103の第2の端子及びスイッチ104の第1の端子に、電源電圧供給時における電位V2、即ちVDDが入力される。そのため、スイッチ103の第2の端子及びスイッチ104の第1の端子の電位(ノードM1の電位)を、一定の電位(例えば、VDD)にする(以下、プリチャージ動作と呼ぶ)ことができる。ノードM1の電位は、容量素子107によって保持される。

40

#### 【0122】

上記プリチャージ動作の後、期間5において、第2の制御信号PRをハイレベル電位とすることによって、スイッチ103の第1の端子と第2の端子の間を導通状態とし、スイッチ104の第1の端子と第2の端子の間を非導通状態とする。この際、第1の制御信号BKはローレベル電位のままであり、トランジスタ109はオフ状態のままである。また、第2の選択信号Sbはローレベル電位であり、副記憶回路330\_\_(m+1)が供給する信号は選択回路340\_\_(m+1)に選択されない状態である。

#### 【0123】

容量素子108に保持された信号(ノードM2の電位VX)に応じて、トランジスタ11

50

0 のオン状態またはオフ状態が選択され、スイッチ 103 の第 2 の端子及びスイッチ 104 の第 1 の端子の電位、即ちノード M1 の電位が定まる。トランジスタ 110 がオン状態の場合、ノード M1 には電位 V1 ( 例えれば、VSS ) が入力される。一方、トランジスタ 110 がオフ状態の場合には、ノード M1 の電位は、上記プリチャージ動作によって定められた一定の電位 ( 例えれば、VDD ) のまま維持される。こうして、トランジスタ 110 のオン状態またはオフ状態に対応して、ノード M1 の電位は VDD または VSS となる。

#### 【 0124 】

例えば、記憶回路 320\_ ( m + 1 ) に保持されていた信号が「 1 」であり、ハイレベルの電位 ( VDD ) に対応する場合、ノード M1 の電位は、信号「 0 」に対応するローレベルの電位 ( VSS ) となる。一方、記憶回路 320\_ ( m + 1 ) に保持されていた信号が「 0 」であり、ローレベルの電位 ( VSS ) に対応する場合、ノード M1 の電位は、信号「 1 」に対応するハイレベルの電位 ( VDD ) となる。つまり、記憶回路 320\_ ( m + 1 ) に記憶されていた信号の反転信号がノード M1 に保持されることとなる。

10

#### 【 0125 】

図 5において、この電位を VXB と表記する。つまり、期間 2において記憶回路 320\_ ( m + 1 ) から入力されたデータ ( dataX ) に対応する信号が、ノード M1 の電位 ( VXB ) に変換される。

#### 【 0126 】

その後、期間 6において、第 2 の選択信号 Sb をハイレベル電位として、選択回路 340\_ ( m + 1 ) の第 1 の端子と第 2 の端子の間を導通状態とする。この際、第 2 の制御信号 PR はハイレベル電位のままである。また、第 1 の制御信号 BK はローレベル電位のままであり、トランジスタ 109 はオフ状態のままである。

20

#### 【 0127 】

スイッチ 103 の第 2 の端子及びスイッチ 104 の第 1 の端子の電位 ( ノード M1 の電位 ( VXB ) ) に対応する信号を、インバータ 332 を介して反転信号とし、当該反転信号を記憶回路 320\_ ( m + 1 ) に入力することができる。こうして、記憶回路 320\_ ( m + 1 ) は、副記憶回路 330\_ ( m + 1 ) への電源電圧の供給停止前に保持していたデータ ( dataX ) を再び保持することができる。

#### 【 0128 】

また、ノード M1 の電位は、期間 4におけるプリチャージ動作によって一定の電位 ( 図 5 では、VDD ) にされた後、期間 5において、データ ( dataX ) に対応する電位 VXB となる。プリチャージ動作を行っているため、ノード M1 の電位が所定の電位 VXB に定まるまでの時間を短くすることができる。こうして、電源電圧供給再開後に、記憶回路 320\_ ( m + 1 ) が元のデータを保持しなおすまでの時間を短くすることができる。

30

#### 【 0129 】

以上が、副記憶回路 330\_ ( m + 1 ) の駆動方法の説明である。

#### 【 0130 】

本発明の一態様の半導体装置に適用することができる副記憶回路 330\_ ( m + 1 ) 及びその駆動方法では、副記憶回路 330\_ ( m + 1 ) に電源電圧が供給されない間は、記憶回路 320\_ ( m + 1 ) に記憶されていたデータを、副記憶回路部 102 に設けられた容量素子 108 によって保持することができる。

40

#### 【 0131 】

また、酸化物半導体層にチャネルが形成されるトランジスタはオフ電流が極めて小さい。例えば、酸化物半導体層にチャネルが形成されるトランジスタのオフ電流は、結晶性を有するシリコンにチャネルが形成されるトランジスタのオフ電流に比べて著しく低い。そのため、当該トランジスタをトランジスタ 109 として用いることによって、副記憶回路 330\_ ( m + 1 ) に電源電圧が供給されない間も容量素子 108 に保持された信号は長期間にわたり保たれる。こうして、副記憶回路 330\_ ( m + 1 ) は電源電圧の供給が停止した間も記憶内容 ( データ ) を保持することができる。

#### 【 0132 】

50

また、スイッチ 103 及びスイッチ 104 を設けることによって、上記プリチャージ動作を行うことを特徴とする副記憶回路 330<sub>(m+1)</sub> であるため、電源電圧供給再開後に、記憶回路 320<sub>(m+1)</sub> が元のデータを保持しなおすまでの時間を短くすることができる。

#### 【0133】

また、副記憶回路部 102において、容量素子 108 によって保持された信号はトランジスタ 110 のゲートに入力される。そのため、副記憶回路 330<sub>(m+1)</sub> への電源電圧の供給が再開された後、容量素子 108 によって保持された信号を、トランジスタ 110 の状態（オン状態、またはオフ状態）に変換して、副記憶回路部 102 から読み出すことができる。それ故、容量素子 108 に保持された信号に対応する電位が多少変動しても、元の信号を正確に読み出すことが可能である。10

#### 【0134】

このような副記憶回路 330<sub>(m+1)</sub> を、信号処理回路が有するレジスタやキャッシュメモリなどの記憶装置に用いることで、電源電圧の供給停止による記憶装置内のデータの消失を防ぐことができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰することができる。よって、信号処理回路全体、もしくは信号処理回路を構成する一または複数の論理回路において、短い時間でも電源停止を行うことができため、消費電力を抑えることができる信号処理回路、消費電力を抑えることができる当該信号処理回路の駆動方法を提供することができる。20

#### 【0135】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。20

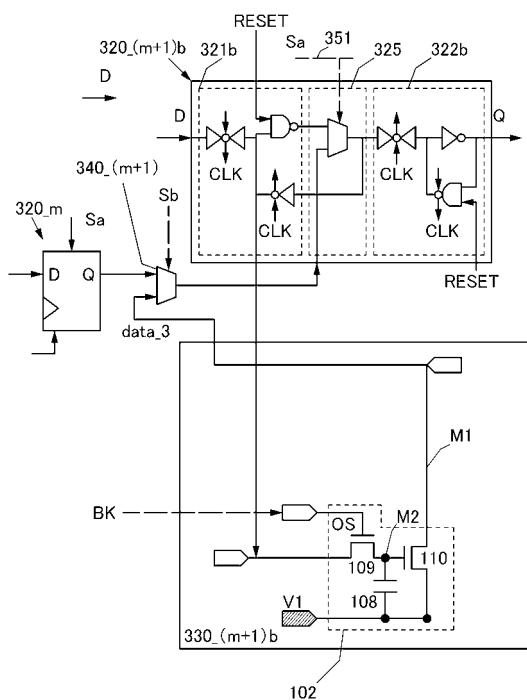

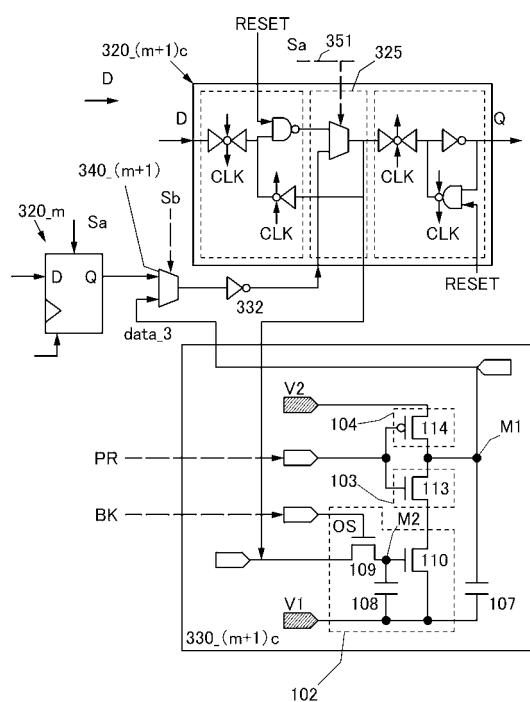

#### 【0136】

##### （実施の形態 4）

本実施の形態では、本発明の一態様の半導体装置に適用することができる記憶回路および副記憶回路の構成について、図 6 乃至図 8 を参照しながら説明する。

#### 【0137】

図 6 乃至図 8 は、本発明の一態様の半導体装置に適用することができる記憶回路 320<sub>(m+1)</sub> および副記憶回路 330<sub>(m+1)</sub> の一例を説明する回路図である。いずれの構成も実施の形態 2 で図 4 に図示した記憶回路および副記憶回路に置換できる。30

#### 【0138】

具体的には、図 6 に示す構成は、記憶回路 320<sub>(m+1)</sub> b は記憶回路 320<sub>(m+1)</sub> の変形例であり、副記憶回路 330<sub>(m+1)</sub> b は副記憶回路 330<sub>(m+1)</sub> の変形例である。

#### 【0139】

図 6 に示す記憶回路 320<sub>(m+1)</sub> b は、第 1 の記憶部 321 のインバータがリセット信号を供給することができる NAND 回路に置換されている点と、第 2 の記憶部 322 のクロックドインバータがリセット信号を供給することができるクロックド NAND 回路に置換されている点が異なる。この構成によれば、リセット信号を記憶回路 320<sub>(m+1)</sub> b 供給すると、記憶回路 320<sub>(m+1)</sub> b をリセットできる。40

#### 【0140】

電源電圧の供給を停止した後に、まずリセット信号を記憶回路 320<sub>(m+1)</sub> b に供給し、その後に、副記憶回路から信号を供給することで、半導体装置を安定に駆動できる。

#### 【0141】

また、記憶回路 320<sub>(m+1)</sub> b は、第 1 の記憶部 321 b から、第 1 の記憶部 321 b に反転される前の信号を副記憶回路 330<sub>(m+1)</sub> b に供給する。また、副記憶回路 330<sub>(m+1)</sub> b は、第 1 の記憶部 321 b から供給された信号の反転信号を、選択回路 340<sub>(m+1)</sub> に供給する。これにより、選択回路 340<sub>(m+1)</sub> と記憶回路 320<sub>(m+1)</sub> b の間にインバータを設ける必要がない。50

**【 0 1 4 2 】**

図7に示す記憶回路 $320_{(m+1)c}$ は、記憶回路 $320_{(m+1)b}$ と同様の構成を備える。

**【 0 1 4 3 】**

記憶回路 $320_{(m+1)c}$ は、第1の記憶部 $321_c$ に反転された後の信号を、副記憶回路 $330_{(m+1)c}$ に供給する。この構成の場合、図4に示す構成と同様に、選択回路 $340_{(m+1)}$ と記憶回路 $320_{(m+1)c}$ の間にインバータを設ける。

**【 0 1 4 4 】**

図8に示す記憶回路 $320_{(m+1)d}$ は、第1の記憶部 $321$ のインバータがリセット信号をゲート信号として供給することができるゲーテッドインバータに置換されている点と、第2の記憶部 $322$ のクロックドインバータがリセット信号を供給することができるクロックド NAND 回路に置換されている点が異なる。この構成によれば、リセット信号を記憶回路 $320_{(m+1)d}$ に供給すると、記憶回路 $320_{(m+1)d}$ をリセットできる。

10

**【 0 1 4 5 】**

また、図8に示す副記憶回路 $330_{(m+1)d}$ は、図4に示す副記憶回路 $330_{(m+1)}$ とは異なる構成を備える。

**【 0 1 4 6 】**

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

20

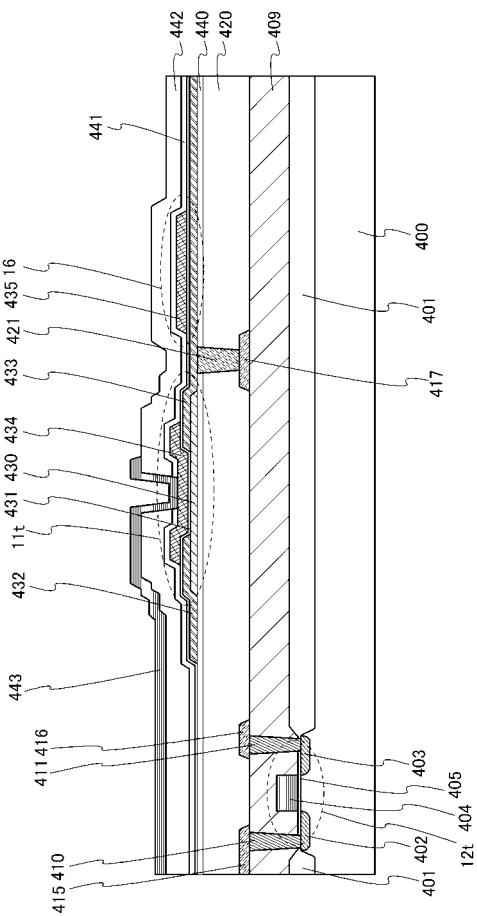

**【 0 1 4 7 】****( 実施の形態 5 )**

本実施の形態では、本発明の一態様の半導体装置に適用することができる記憶回路の構造について、図10を参照しながら説明する。

**【 0 1 4 8 】**

図10は、トランジスタ $11_t$ 、トランジスタ $12_t$ および容量素子 $16$ の断面の構造を示す図である。

**【 0 1 4 9 】**

この構造を図4に示す副記憶回路 $330_{(m+1)}$ に適用する場合、トランジスタ $11_t$ の構造をトランジスタ $10_9$ に適用し、トランジスタ $12_t$ の構造をトランジスタ $11_0$ に適用し、容量素子 $16$ の構造を容量素子 $10_8$ にそれぞれ適用することができる。

30

**【 0 1 5 0 】**

また、本実施の形態では、酸化物半導体膜にチャネル形成領域を有するトランジスタ $11_t$ と、容量素子 $16$ とが、単結晶のシリコン基板にチャネル形成領域を有するトランジスタ $12_t$ 上に形成されている場合を例示している。

**【 0 1 5 1 】**

なお、トランジスタ $12_t$ は、非晶質、微結晶、多結晶または単結晶である、シリコン又はゲルマニウムなどの半導体膜を活性層に用いることもできる。或いは、トランジスタ $12_t$ は、酸化物半導体を活性層に用いていても良い。全てのトランジスタが酸化物半導体を活性層に用いている場合、トランジスタ $11_t$ はトランジスタ $12_t$ 上に積層されなくとも良く、トランジスタ $11_t$ とトランジスタ $12_t$ は、同一の層に形成されていても良い。

40

**【 0 1 5 2 】**

薄膜のシリコンを用いてトランジスタ $12_t$ を形成する場合、プラズマCVD法などの気相成長法若しくはスパッタリング法で作製された非晶質シリコン、非晶質シリコンをレーザーアニールなどの処理により結晶化させた多結晶シリコン、単結晶シリコンウェハに水素イオン等を注入して表層部を剥離した単結晶シリコンなどを用いることができる。

**【 0 1 5 3 】**

トランジスタ $12_t$ が形成される半導体基板 $400$ は、例えは、n型またはp型の導電型を有するシリコン基板、ゲルマニウム基板、シリコンゲルマニウム基板、化合物半導体基

50

板（GaN基板、InP基板、GaN基板、SiC基板、GaP基板、GaInAsP基板、ZnSe基板等）等を用いることができる。図10では、n型の導電性を有する単結晶シリコン基板を用いた場合を例示している。

#### 【0154】

また、トランジスタ12tは、素子分離用絶縁膜401により、他のトランジスタと、電気的に分離されている。素子分離用絶縁膜401の形成には、選択酸化法（LOCOS（Local Oxidation of Silicon）法）またはトレンチ分離法等を用いることができる。

#### 【0155】

具体的に、トランジスタ12tは、半導体基板400に形成された、ソース領域またはドレイン領域として機能する不純物領域402及び不純物領域403と、ゲート電極404と、半導体基板400とゲート電極404の間に設けられたゲート絶縁膜405とを有する。ゲート電極404は、ゲート絶縁膜405を間に挟んで、不純物領域402と不純物領域403の間に形成されるチャネル形成領域と重なる。

#### 【0156】

トランジスタ12t上には、絶縁膜409が設けられている。絶縁膜409には開口部が形成されている。そして、上記開口部には、不純物領域402、不純物領域403にそれぞれ接する配線410と配線411が形成されている。

#### 【0157】

そして、配線410は、絶縁膜409上に形成された配線415に電気的に接続されており、配線411は、絶縁膜409上に形成された配線416に電気的に接続されている。

#### 【0158】

配線415乃至配線417上には、絶縁膜420及び絶縁膜440が順に積層するように形成されている。絶縁膜420及び絶縁膜440には開口部が形成されており、上記開口部に、配線417に電気的に接続された配線421が形成されている。

#### 【0159】

トランジスタ11t及び容量素子16は、絶縁膜440上に形成されている。

#### 【0160】

トランジスタ11tは、絶縁膜440上に、酸化物半導体を含む半導体膜430と、半導体膜430上の、ソース電極またはドレイン電極として機能する導電膜432及び導電膜433と、半導体膜430、導電膜432及び導電膜433上のゲート絶縁膜431と、ゲート絶縁膜431上に位置し、導電膜432と導電膜433の間ににおいて半導体膜430と重なっているゲート電極434と、を有する。なお、導電膜433は、配線421に電気的に接続されている。

#### 【0161】

また、ゲート絶縁膜431において導電膜433と重なる位置に、導電膜435が設けられている。ゲート絶縁膜431を間に挟んで導電膜433及び導電膜435が重なっている部分が、容量素子16として機能する。

#### 【0162】

なお、図10では、容量素子16がトランジスタ11tと共に絶縁膜440の上に設けられている場合を例示しているが、容量素子16は、トランジスタ12tと共に、絶縁膜440の下に設けられていても良い。

#### 【0163】

そして、トランジスタ11t、容量素子16上に、絶縁膜441及び絶縁膜442が順に積層するように設けられている。絶縁膜441及び絶縁膜442には開口部が設けられており、上記開口部においてゲート電極434に接する導電膜443が、絶縁膜441上に設けられている。

#### 【0164】

なお、図10において、トランジスタ11tは、ゲート電極434を半導体膜430の片側において少なくとも有していれば良いが、半導体膜430を間に挟んで存在する一対の

10

20

30

40

50

ゲート電極を有していても良い。

【0165】

トランジスタ $11t$ が、半導体膜 $430$ を間に挟んで存在する一対のゲート電極を有している場合、一方のゲート電極には導通状態または非導通状態を制御するための信号が与えられ、他方のゲート電極は、電位が他から与えられている状態であっても良い。この場合、一対の電極に、同じ高さの電位が与えられていても良いし、他方のゲート電極にのみ接地電位などの固定の電位が与えられていても良い。他方のゲート電極に与える電位の高さを制御することで、トランジスタの閾値電圧を制御することができる。

【0166】

また、図10では、トランジスタ $11t$ が、一のゲート電極 $434$ に対応した一のチャネル形成領域を有する、シングルゲート構造である場合を例示している。しかし、トランジスタ $11t$ は、電気的に接続された複数のゲート電極を有することで、一の活性層にチャネル形成領域を複数有する、マルチゲート構造であっても良い。

10

【0167】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

20

【0168】

(実施の形態6)

本実施の形態では、本発明の一態様の半導体装置に適用することができる酸化物半導体膜について説明する。

20

【0169】

電子供与体(ドナー)となる水分または水素などの不純物が低減され、なおかつ酸素欠損が低減されることにより高純度化された酸化物半導体(purified OS)は、i型(真性半導体)又はi型に限りなく近い。そのため、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタは、オフ電流が著しく小さく、信頼性が高い。

30

【0170】

具体的に、高純度化された酸化物半導体膜にチャネル形成領域を有するトランジスタのオフ電流が小さいことは、いろいろな実験により証明できる。例えば、チャネル幅が $1 \times 10^6 \mu m$ でチャネル長が $10 \mu m$ の素子であっても、ソース電極とドレイン電極間の電圧(ドレイン電圧)が $1V$ から $10V$ の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13} A$ 以下という特性を得ることができる。この場合、トランジスタのチャネル幅で規格化したオフ電流は、 $100 zA / \mu m$ 以下であることが分かる。また、容量素子とトランジスタとを接続して、容量素子に流入または容量素子から流出する電荷を当該トランジスタで制御する回路を用いて、オフ電流の測定を行った。当該測定では、高純度化された酸化物半導体膜を上記トランジスタのチャネル形成領域に用い、容量素子の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流を測定した。その結果、トランジスタのソース電極とドレイン電極間の電圧が $3V$ の場合に、数十 $yA / \mu m$ という、さらに小さいオフ電流が得られることが分かった。従って、高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタは、オフ電流が、結晶性を有するシリコンを用いたトランジスタに比べて著しく小さい。

40

【0171】

なお、特に断りがない限り、本明細書でオフ電流とは、nチャネル型トランジスタにおいては、ドレインをソースとゲートよりも高い電位とした状態において、ソースの電位を基準としたときのゲートの電位が $0$ 以下であるときに、ソースとドレインの間に流れる電流のことを意味する。或いは、本明細書でオフ電流とは、pチャネル型トランジスタにおいては、ドレインをソースとゲートよりも低い電位とした状態において、ソースの電位を基準としたときのゲートの電位が $0$ 以上であるときに、ソースとドレインの間に流れる電流のことを意味する。

【0172】

半導体膜として酸化物半導体膜を用いる場合、酸化物半導体としては、少なくともインジ

50

ウム( In )あるいは亜鉛( Zn )を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気的特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム( Ga )を有することが好ましい。また、スタビライザーとしてスズ( Sn )を有することが好ましい。また、スタビライザーとしてハフニウム( Hf )を有することが好ましい。また、スタビライザーとしてアルミニウム( Al )を有することが好ましい。また、スタビライザーとしてジルコニウム( Zr )を含むことが好ましい。

#### 【 0173 】

酸化物半導体の中でも In - Ga - Zn 系酸化物、 In - Sn - Zn 系酸化物などは、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、スパッタリング法や湿式法により電気的特性の優れたトランジスタを作製することが可能であり、量産性に優れるといった利点がある。また、炭化シリコン、窒化ガリウム、または酸化ガリウムとは異なり、上記 In - Ga - Zn 系酸化物は、ガラス基板上に、電気的特性の優れたトランジスタを作製することが可能である。また、基板の大型化にも対応が可能である。

10

#### 【 0174 】

また、他のスタビライザーとして、ランタノイドである、ランタン( La )、セリウム( Ce )、プラセオジム( Pr )、ネオジム( Nd )、サマリウム( Sm )、ユウロピウム( Eu )、ガドリニウム( Gd )、テルビウム( Tb )、ジスプロシウム( Dy )、ホルミウム( Ho )、エルビウム( Er )、ツリウム( Tm )、イッテルビウム( Yb )、ルテチウム( Lu )のいずれか一種または複数種を含んでいてもよい。

20

#### 【 0175 】

例えば、酸化物半導体として、酸化インジウム、酸化ガリウム、酸化スズ、酸化亜鉛、 In - Zn 系酸化物、 Sn - Zn 系酸化物、 Al - Zn 系酸化物、 Zn - Mg 系酸化物、 Sn - Mg 系酸化物、 In - Mg 系酸化物、 In - Ga 系酸化物、 In - Ga - Zn 系酸化物( IGZO とも表記する)、 In - Al - Zn 系酸化物、 In - Sn - Zn 系酸化物、 Sn - Ga - Zn 系酸化物、 Al - Ga - Zn 系酸化物、 Sn - Al - Zn 系酸化物、 In - Hf - Zn 系酸化物、 In - La - Zn 系酸化物、 In - Pr - Zn 系酸化物、 In - Nd - Zn 系酸化物、 In - Sm - Zn 系酸化物、 In - Eu - Zn 系酸化物、 In - Gd - Zn 系酸化物、 In - Tb - Zn 系酸化物、 In - Dy - Zn 系酸化物、 In - Ho - Zn 系酸化物、 In - Er - Zn 系酸化物、 In - Tm - Zn 系酸化物、 In - Yb - Zn 系酸化物、 In - Lu - Zn 系酸化物、 In - Sn - Ga - Zn 系酸化物、 In - Hf - Ga - Zn 系酸化物、 In - Al - Ga - Zn 系酸化物、 In - Sn - Al - Zn 系酸化物、 In - Sn - Hf - Zn 系酸化物、 In - Hf - Al - Zn 系酸化物を用いることができる。

30

#### 【 0176 】

なお、例えば、 In - Ga - Zn 系酸化物とは、 In と Ga と Zn を含む酸化物という意味であり、 In と Ga と Zn の比率は問わない。また、 In と Ga と Zn 以外の金属元素を含んでいてもよい。 In - Ga - Zn 系酸化物は、無電界時の抵抗が十分に高くオフ電流を十分に小さくすることが可能であり、また、移動度も高い。

#### 【 0177 】

例えば、 In : Ga : Zn = 1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3) あるいは In : Ga : Zn = 2 : 2 : 1 (= 2 / 5 : 2 / 5 : 1 / 5) の原子比の In - Ga - Zn 系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 In : Sn : Zn = 1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3) 、 In : Sn : Zn = 2 : 1 : 3 (= 1 / 3 : 1 / 6 : 1 / 2) あるいは In : Sn : Zn = 2 : 1 : 5 (= 1 / 4 : 1 / 8 : 5 / 8) の原子比の In - Sn - Zn 系酸化物やその組成の近傍の酸化物を用いるとよい。

40

#### 【 0178 】

例えば、 In - Sn - Zn 系酸化物では比較的容易に高い移動度が得られる。しかしながら、 In - Ga - Zn 系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

#### 【 0179 】

50

酸化物半導体膜は、例えば非単結晶を有してもよい。非単結晶は、例えば、 C AAC ( C Axis Aligned Crystal )、多結晶、微結晶、非晶質を有する。非晶質は、微結晶、 C AAC よりも欠陥準位密度が高い。また、微結晶は、 C AAC よりも欠陥準位密度が高い。なお、 C AAC を有する酸化物半導体を、 C AAC - OS ( C Axis Aligned Crystalline Oxide Semiconductor ) と呼ぶ。

#### 【 0180 】

酸化物半導体膜は、例えば C AAC - OS を有してもよい。 C AAC - OS は、例えば、 c 軸配向し、 a 軸または / および b 軸はマクロに揃っていない酸化物半導体を有している。

10

#### 【 0181 】

酸化物半導体膜は、例えば微結晶を有してもよい。なお、微結晶を有する酸化物半導体を、微結晶酸化物半導体と呼ぶ。微結晶酸化物半導体膜は、例えば、 1 nm 以上 10 nm 未満のサイズの微結晶を膜中に含む酸化物半導体を有している。

#### 【 0182 】

酸化物半導体膜は、例えば非晶質を有してもよい。なお、非晶質を有する酸化物半導体を、非晶質酸化物半導体と呼ぶ。非晶質酸化物半導体膜は、例えば、原子配列が無秩序であり、結晶成分のない酸化物半導体を有している。または、非晶質酸化物半導体膜は、例えば、完全な非晶質であり、結晶部を有さない酸化物半導体を有している。

20

#### 【 0183 】

なお、酸化物半導体膜が、 C AAC - OS 、微結晶酸化物半導体、非晶質酸化物半導体の混合膜であってもよい。混合膜は、例えば、非晶質酸化物半導体の領域と、微結晶酸化物半導体の領域と、 C AAC - OS の領域と、を有する。また、混合膜は、例えば、非晶質酸化物半導体の領域と、微結晶酸化物半導体の領域と、 C AAC - OS の領域と、の積層構造を有してもよい。

#### 【 0184 】

なお、酸化物半導体膜は、例えば、単結晶を有してもよい。

#### 【 0185 】

酸化物半導体膜は、複数の結晶部を有し、当該結晶部の c 軸が被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃っていることが好ましい。なお、異なる結晶部間で、それぞれ a 軸および b 軸の向きが異なっていてもよい。そのような酸化物半導体膜の一例としては、 C AAC - OS 膜がある。

30

#### 【 0186 】

C AAC - OS 膜は、完全な単結晶ではなく（非単結晶の一種）、完全な非晶質でもない。なお、当該結晶部は、一辺が 100 nm 未満の立方体内に収まる大きさが多い。また、透過型電子顕微鏡 ( TEM : Transmission Electron Microscope ) による観察像では、 C AAC - OS 膜に含まれる非晶質部と結晶部との境界は明確ではない。また、 TEM によって C AAC - OS 膜には明確な粒界（グレインバウンダリーともいう。）は確認できない。そのため、 C AAC - OS 膜は、粒界に起因する電子移動度の低下が抑制される。

40

#### 【 0187 】

C AAC - OS 膜に含まれる結晶部は、例えば、 c 軸が C AAC - OS 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃い、かつ a b 面に垂直な方向から見て金属原子が三角形状または六角形状に配列し、 c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ a 軸および b 軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、 80 ° 以上 100 ° 以下、好ましくは 85 ° 以上 95 ° 以下の範囲も含まれることとする。また、単に平行と記載する場合、 -10 ° 以上 10 ° 以下、好ましくは -5 ° 以上 5 ° 以下の範囲も含まれることとする。

#### 【 0188 】

50

なお、 C A A C - O S 膜において、結晶部の分布が一様でなくてもよい。例えば、 C A A C - O S 膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、 C A A C - O S 膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

#### 【 0 1 8 9 】

C A A C - O S 膜に含まれる結晶部の c 軸は、 C A A C - O S 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃うため、 C A A C - O S 膜の形状（被形成面の断面形状または表面の断面形状）によっては互いに異なる方向を向くことがある。なお、結晶部の c 軸は、 C A A C - O S 膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃っている。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

10

#### 【 0 1 9 0 】

C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気的特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

#### 【 0 1 9 1 】

C A A C - O S 膜は、例えば、多結晶である金属酸化物ターゲットを用い、スパッタリング法によって成膜する。当該ターゲットにイオンが衝突すると、ターゲットに含まれる結晶領域が a - b 面から劈開し、a - b 面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、 C A A C - O S 膜を成膜することができる。

20

#### 【 0 1 9 2 】

また、 C A A C - O S 膜を成膜するために、以下の条件を適用することが好ましい。

#### 【 0 1 9 3 】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、処理室内に存在する不純物濃度（水素、水、二酸化炭素、及び窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が - 80 以下、好ましくは - 100 以下である成膜ガスを用いる。

30

#### 【 0 1 9 4 】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を 100 以上 740 以下、好ましくは 200 以上 500 以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタリング粒子の平らな面が基板に付着する。

#### 【 0 1 9 5 】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、 30 体積 % 以上、好ましくは 100 体積 % とする。

40

#### 【 0 1 9 6 】

ターゲットの一例として、 I n - G a - Z n 系酸化物ターゲットについて以下に示す。

#### 【 0 1 9 7 】

I n O<sub>x</sub> 粉末、 G a O<sub>y</sub> 粉末及び Z n O<sub>z</sub> 粉末を所定の m o l 数比で混合し、加圧処理後、 1000 以上 1500 以下の温度で加熱処理することで多結晶である I n - G a - Z n 系酸化物ターゲットとする。なお、 X 、 Y 及び Z は任意の正数である。ここで、所定の m o l 数比は、例えば、 I n O<sub>x</sub> 粉末、 G a O<sub>y</sub> 粉末及び Z n O<sub>z</sub> 粉末が、 2 : 2 : 1 、 8 : 4 : 3 、 3 : 1 : 1 、 1 : 1 : 1 、 4 : 2 : 3 または 3 : 1 : 2 である。なお、粉末の種類、及びその混合する m o l 数比は、作製するターゲットによって適宜変更すればよい。

50

## 【0198】

なお、アルカリ金属は酸化物半導体を構成する元素ではないため、不純物である。アルカリ土類金属も、酸化物半導体を構成する元素ではない場合において、不純物となる。特に、アルカリ金属のうちNaは、酸化物半導体膜に接する絶縁膜が酸化物である場合、当該絶縁膜中に拡散してNa<sup>+</sup>となる。また、Naは、酸化物半導体膜内において、酸化物半導体を構成する金属と酸素の結合を分断する、或いは、その結合中に割り込む。その結果、例えば、閾値電圧がマイナス方向にシフトすることによるノーマリオン化、移動度の低下等の、トランジスタの電気的特性の劣化が起こり、加えて、特性のばらつきも生じる。具体的に、二次イオン質量分析法によるNa濃度の測定値は、 $5 \times 10^{-6} / \text{cm}^3$ 以下、好ましくは $1 \times 10^{-6} / \text{cm}^3$ 以下、更に好ましくは $1 \times 10^{-5} / \text{cm}^3$ 以下とするとい。同様に、Li濃度の測定値は、 $5 \times 10^{-5} / \text{cm}^3$ 以下、好ましくは $1 \times 10^{-5} / \text{cm}^3$ 以下とするとい。同様に、K濃度の測定値は、 $5 \times 10^{-5} / \text{cm}^3$ 以下、好ましくは $1 \times 10^{-5} / \text{cm}^3$ 以下とするとい。

10

## 【0199】

また、インジウムを含む金属酸化物が用いられている場合に、酸素との結合エネルギーがインジウムよりも大きいシリコンや炭素が、インジウムと酸素の結合を切断し、酸素欠損を形成することがある。そのため、シリコンや炭素が酸化物半導体膜に混入していると、アルカリ金属やアルカリ土類金属の場合と同様に、トランジスタの電気的特性の劣化が起こりやすい。よって、酸化物半導体膜中におけるシリコンや炭素の濃度は低いことが望ましい。具体的に、二次イオン質量分析法によるC濃度の測定値、またはSi濃度の測定値は、 $1 \times 10^{-8} / \text{cm}^3$ 以下とするとい。上記構成により、トランジスタの電気的特性の劣化を防ぐことができ、PLD(Programmable Logic Device)または半導体装置の信頼性を高めることができる。

20

## 【0200】

また、ソース電極及びドレイン電極に用いられる導電性材料によっては、ソース電極及びドレイン電極中の金属が、酸化物半導体膜から酸素を引き抜くことがある。この場合、酸化物半導体膜のうち、ソース電極及びドレイン電極に接する領域が、酸素欠損の形成によりn型化される。

## 【0201】

n型化された領域は、ソース領域またはドレイン領域として機能するため、酸化物半導体膜とソース電極及びドレイン電極との間におけるコンタクト抵抗を下げることができる。よって、n型化された領域が形成されることで、トランジスタの移動度及びオン電流を高めることができ、それにより、トランジスタを用いたスイッチ回路の高速動作を実現することができる。

30

## 【0202】

なお、ソース電極及びドレイン電極中の金属による酸素の引き抜きは、ソース電極及びドレイン電極をスパッタリング法などにより形成する際に起こりうるし、ソース電極及びドレイン電極を形成した後に行われる加熱処理によっても起こりうる。

## 【0203】

また、n型化される領域は、酸素と結合し易い導電性材料をソース電極及びドレイン電極に用いることで、より形成されやすくなる。上記導電性材料としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wなどが挙げられる。

40

## 【0204】

また、酸化物半導体膜は、単数の金属酸化物膜で構成されているとは限らず、積層された複数の金属酸化物膜で構成されていても良い。例えば、第1乃至第3の金属酸化物膜が順に積層されている半導体膜の場合、第1の金属酸化物膜及び第3の金属酸化物膜は、第2の金属酸化物膜を構成する金属元素の少なくとも1つを、その構成要素に含み、伝導帯下端のエネルギーが第2の金属酸化物膜よりも0.05eV以上、0.07eV以上、0.1eV以上または0.15eV以上、かつ2eV以下、1eV以下、0.5eV以下または0.4eV以下、真空準位に近い酸化物膜である。さらに、第2の金属酸化物膜は、少

50

なくともインジウムを含むと、キャリア移動度が高くなるため好ましい。

#### 【0205】

上記構成の半導体膜をトランジスタが有する場合、ゲート電極に電圧を印加することで、半導体膜に電界が加わると、半導体膜のうち、伝導帯下端のエネルギーが小さい第2の金属酸化物膜にチャネル領域が形成される。即ち、第2の金属酸化物膜とゲート絶縁膜との間に第3の金属酸化物膜が設けられることによって、ゲート絶縁膜と離隔している第2の金属酸化物膜に、チャネル領域を形成することができる。

#### 【0206】

また、第3の金属酸化物膜は、第2の金属酸化物膜を構成する金属元素の少なくとも1つをその構成要素に含むため、第2の金属酸化物膜と第3の金属酸化物膜の界面では、界面散乱が起こりにくい。従って、当該界面においてキャリアの動きが阻害されにくいため、トランジスタの電界効果移動度が高くなる。

10

#### 【0207】

また、第2の金属酸化物膜と第1の金属酸化物膜の界面に界面準位が形成されると、界面近傍の領域にもチャネル領域が形成されるために、トランジスタの閾値電圧が変動してしまう。しかし、第1の金属酸化物膜は、第2の金属酸化物膜を構成する金属元素の少なくとも1つをその構成要素に含むため、第2の金属酸化物膜と第1の金属酸化物膜の界面には、界面準位が形成されにくい。よって、上記構成により、トランジスタの閾値電圧等の電気的特性のばらつきを、低減することができる。

20

#### 【0208】

また、金属酸化物膜間に不純物が存在することによって、各膜の界面にキャリアの流れを阻害する界面準位が形成されることがないよう、複数の酸化物半導体膜を積層させることができ望ましい。積層された金属酸化物膜の膜間に不純物が存在していると、金属酸化物膜間における伝導帯下端のエネルギーの連続性が失われ、界面近傍において、キャリアがトラップされるか、あるいは再結合により消滅してしまうからである。膜間における不純物を低減させることで、主成分である一の金属を少なくとも共に有する複数の金属酸化物膜を、単に積層させるよりも、連続接合（ここでは特に伝導帯下端のエネルギーが各膜の間で連続的に変化するU字型の井戸構造を有している状態）が形成されやすくなる。

30

#### 【0209】

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置（スパッタリング装置）を用いて各膜を大気に触れさせることなく連続して積層することが必要となる。スパッタリング装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $1 \times 10^{-4}$  Pa ~  $5 \times 10^{-7}$  Pa 程度まで）することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体が逆流しないようにしておくことが好ましい。

40

#### 【0210】

高純度の真性な酸化物半導体を得るためにには、各チャンバー内を高真空排気するのみならず、スパッタリングに用いるガスの高純度化も重要である。上記ガスとして用いる酸素ガスやアルゴンガスの露点を、-40以下、好ましくは-80以下、より好ましくは-100以下とし、使用するガスの高純度化を図ることで、酸化物半導体膜に水分等が取り込まれることを可能な限り防ぐことができる。

#### 【0211】

例えば、第1の金属酸化物膜または第3の金属酸化物膜は、アルミニウム、シリコン、チタン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、スズ、ランタン、セリウムまたはハフニウムを、第2の金属酸化物膜よりも高い原子数比で含む酸化物膜であればよい。具体的に、第1の金属酸化物膜または第3の金属酸化物膜として、第2の金属酸化物膜よりも上述の元素を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比で含む酸化物膜を用いると良い。前述の元素は酸素と強く結合するため、酸素欠損が酸化物膜に生じることを抑制する機能を有する。よって、上記構成により、第1

50

の金属酸化物膜または第3の金属酸化物膜を、第2の金属酸化物膜よりも酸素欠損が生じにくい酸化物膜にすることができる。

#### 【0212】

具体的に、第2の金属酸化物膜と、第1の金属酸化物膜または第3の金属酸化物膜とが、共にIn-M-Zn系酸化物である場合、第1の金属酸化物膜または第3の金属酸化物膜の原子数比を $In : M : Zn = x_1 : y_1 : z_1$ 、第2の金属酸化物膜の原子数比を $In : M : Zn = x_2 : y_2 : z_2$ とすると、 $y_1 / x_1$ が $y_2 / x_2$ よりも大きくなるように、その原子数比を設定すれば良い。なお、元素MはInよりも酸素との結合力が強い金属元素であり、例えばAl、Ti、Ga、Y、Zr、Sn、La、Ce、NdまたはHf等が挙げられる。好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも1.5倍以上大きくなるように、その原子数比を設定すれば良い。さらに好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも2倍以上大きくなるように、その原子数比を設定すれば良い。より好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも3倍以上大きくなるように、その原子数比を設定すれば良い。さらに、第2の金属酸化物膜において、 $y_2$ が $x_2$ 以上であると、トランジスタに安定した電気的特性を付与できるため好ましい。ただし、 $y_2$ が $x_2$ の3倍以上になると、トランジスタの電界効果移動度が低下してしまうため、 $y_2$ は、 $x_2$ の3倍未満であると好ましい。

10

#### 【0213】

なお、第1の金属酸化物膜及び第3の金属酸化物膜の厚さは、3nm以上100nm以下、好ましくは3nm以上50nm以下とする。また、第2の金属酸化物膜の厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下であり、さらに好ましくは3nm以上50nm以下である。

20

#### 【0214】

3層構造の半導体膜において、第1の金属酸化物膜乃至第3の金属酸化物膜は、非晶質または結晶質の両方の形態を取りうる。ただし、チャネル領域が形成される第2の金属酸化物膜が結晶質であることにより、トランジスタに安定した電気的特性を付与することができるため、第2の金属酸化物膜は結晶質であることが好ましい。

#### 【0215】

なお、チャネル形成領域とは、トランジスタの半導体膜のうち、ゲート電極と重なり、かつソース電極とドレイン電極に挟まれる領域を意味する。また、チャネル領域とは、チャネル形成領域において、電流が主として流れる領域をいう。

30

#### 【0216】

例えば、第1の金属酸化物膜及び第3の金属酸化物膜として、スパッタリング法により形成したIn-Ga-Zn系酸化物膜を用いる場合、第1の金属酸化物膜及び第3の金属酸化物膜の成膜には、In-Ga-Zn系酸化物( $In : Ga : Zn = 1 : 3 : 2$ [原子数比])であるターゲットを用いることができる。成膜条件は、例えば、成膜ガスとしてアルゴンガスを30sccm、酸素ガスを15sccm用い、圧力0.4Paとし、基板温度を200とし、DC電力0.5kWとすればよい。

#### 【0217】

また、第2の金属酸化物膜をCAC-OS膜とする場合、第2の金属酸化物膜の成膜には、In-Ga-Zn系酸化物( $In : Ga : Zn = 1 : 1 : 1$ [原子数比])であり、多結晶のIn-Ga-Zn系酸化物を含むターゲットを用いることが好ましい。成膜条件は、例えば、成膜ガスとしてアルゴンガスを30sccm、酸素ガスを15sccm用い、圧力を0.4Paとし、基板の温度300とし、DC電力0.5kWとすることができます。

40

#### 【0218】

なお、トランジスタは、半導体膜の端部が傾斜している構造を有していても良いし、半導体膜の端部が丸みを帯びる構造を有していても良い。

#### 【0219】

また、複数の積層された金属酸化物膜を有する半導体膜をトランジスタに用いる場合にお

50

いても、ソース電極及びドレイン電極に接する領域が、n型化されていても良い。上記構成により、トランジスタの移動度及びオン電流を高め、トランジスタを用いたPLDまたは半導体装置の高速動作を実現することができる。さらに、複数の積層された金属酸化物膜を有する半導体膜をトランジスタに用いる場合、n型化される領域は、チャネル領域となる第2の金属酸化物膜にまで達していることが、トランジスタの移動度及びオン電流を高め、PLDまたは半導体装置のさらなる高速動作を実現する上で、より好ましい。

#### 【0220】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

#### 【0221】

##### (実施の形態7)

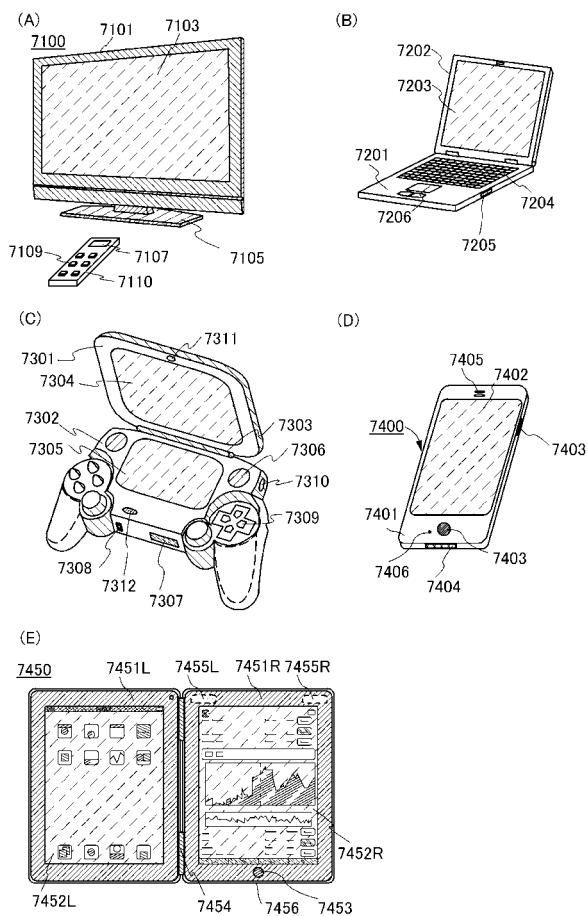

本実施の形態では、本発明の一態様の半導体装置を搭載した電子機器について図11を用いて説明する。

#### 【0222】

本発明の一態様の半導体装置を適用した電子機器として、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。これらの電子機器の具体例を図11に示す。

#### 【0223】

図11(A)は、テレビジョン装置の一例を示している。テレビジョン装置7100は、筐体7101に表示部7103が組み込まれている。表示部7103により、映像を表示することが可能である。また、ここでは、スタンド7105により筐体7101を支持した構成を示している。

#### 【0224】

テレビジョン装置7100の操作は、筐体7101が備える操作スイッチや、別体のリモコン操作機7110により行うことができる。リモコン操作機7110が備える操作キー7109により、チャンネルや音量の操作を行なうことができ、表示部7103に表示される映像を操作することができる。また、リモコン操作機7110に、当該リモコン操作機7110から出力する情報を表示する表示部7107を設ける構成としてもよい。

#### 【0225】

なお、テレビジョン装置7100は、受信機やモデムなどを備えた構成とする。受信機により一般のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向（送信者から受信者）または双方向（送信者と受信者間、あるいは受信者間同士など）の情報通信を行うことも可能である。

#### 【0226】

図11(B)はコンピュータであり、本体7201、筐体7202、表示部7203、キーボード7204、外部接続ポート7205、ポインティングデバイス7206等を含む。

#### 【0227】

図11(C)は携帯型遊技機であり、筐体7301と筐体7302の2つの筐体で構成されており、連結部7303により、開閉可能に連結されている。筐体7301には表示部7304が組み込まれ、筐体7302には表示部7305が組み込まれている。また、図11(C)に示す携帯型遊技機は、その他、スピーカ部7306、記録媒体挿入部7307、LEDランプ7308、入力手段（操作キー7309、接続端子7310、センサ7311（力、変位、位置、速度、加速度、角速度、回転数、距離、光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、においまたは赤外線を測定する機能を含むもの）、マイクロフォン7312）等を備えている。図11(C)に示す携帯型遊技機は、記録媒体に記録されているプログラムまたはデータを読み出して表示部に表示する機能や、他の携帯型遊技機と無線通信を行って

10

20

30

40

50

情報を共有する機能を有する。なお、図 11 (C) に示す携帯型遊技機が有する機能はこれに限定されず、様々な機能を有することができる。

#### 【0228】

図 11 (D) は、携帯電話機の一例を示している。携帯電話機 7400 は、筐体 7401 に組み込まれた表示部 7402 の他、操作ボタン 7403、外部接続ポート 7404、スピーカ 7405、マイク 7406 などを備えている。

#### 【0229】

図 11 (D) に示す携帯電話機 7400 は、表示部 7402 を指などで触ることで、情報を入力することができる。また、電話を掛ける、或いはメールを作成するなどの操作は、表示部 7402 を指などで触ることにより行うことができる。

10

#### 【0230】

表示部 7402 の画面は主として 3 つのモードがある。第 1 は、画像の表示を主とする表示モードであり、第 2 は、文字等の情報の入力を主とする入力モードである。第 3 は表示モードと入力モードの 2 つのモードが混合した表示 + 入力モードである。

#### 【0231】

例えば、電話を掛ける、或いはメールを作成する場合は、表示部 7402 を文字の入力を主とする文字入力モードとし、画面に表示させた文字の入力操作を行えばよい。この場合、表示部 7402 の画面のほとんどにキーボードまたは番号ボタンを表示させることができ。好ましい。

20

#### 【0232】

また、携帯電話機 7400 内部に、ジャイロ、加速度センサ等の傾きを検出するセンサを有する検出装置を設けることで、携帯電話機 7400 の向き（縦か横か）を判断して、表示部 7402 の画面表示を自動的に切り替えるようにすることができる。

#### 【0233】

また、画面モードの切り替えは、表示部 7402 を触れること、または筐体 7401 の操作ボタン 7403 の操作により行われる。また、表示部 7402 に表示される画像の種類によって切り替えるようにすることもできる。例えば、表示部に表示する画像信号が動画のデータであれば表示モード、テキストデータであれば入力モードに切り替える。

#### 【0234】

また、入力モードにおいて、表示部 7402 の光センサで検出される信号を検知し、表示部 7402 のタッチ操作による入力が一定期間ない場合には、画面のモードを入力モードから表示モードに切り替えるように制御してもよい。

30

#### 【0235】

表示部 7402 は、イメージセンサとして機能させることもできる。例えば、表示部 7402 に掌や指で触れ、掌紋、指紋等を撮像することで、本人認証を行うことができる。また、表示部に近赤外光を発光するバックライトまたは近赤外光を発光するセンシング用光源を用いれば、指静脈、掌静脈などを撮像することもできる。

#### 【0236】

図 11 (E) は、折りたたみ式のコンピュータの一例を示している。折りたたみ式のコンピュータ 7450 は、ヒンジ 7454 で接続された筐体 7451L と筐体 7451R を備えている。また、操作ボタン 7453、左側スピーカ 7455L および右側スピーカ 7455R の他、コンピュータ 7450 の側面には図示されていない外部接続ポート 7456 を備える。なお、筐体 7451L に設けられた表示部 7452L と、筐体 7451R に設けられた表示部 7452R が互いに対峙するようにヒンジ 7454 を折り畳むと、表示部を筐体で保護することができる。

40

#### 【0237】

表示部 7452L と表示部 7452R は、画像を表示する他、指などで触ると情報を入力できる。例えば、インストール済みのプログラムを示すアイコンを指でふれて選択し、プログラムを起動できる。または、表示された画像の二箇所に触れた指の間隔を変えて、画像を拡大または縮小できる。または、表示された画像の一箇所に触れた指を移動して画

50

像を移動できる。また、キーボードの画像を表示して、表示された文字や記号を指で触れて選択し、情報を入力することもできる。

#### 【0238】

また、コンピュータ7450に、ジャイロ、加速度センサ、GPS(Gloabal Positioning System)受信機、指紋センサ、ビデオカメラを搭載することができる。例えば、ジャイロ、加速度センサ等の傾きを検出するセンサを有する検出装置を設けることで、コンピュータ7450の向き(縦か横か)を判断して、表示する画面の向きを自動的に切り替えるようにすることができる。

#### 【0239】

また、コンピュータ7450はネットワークに接続できる。コンピュータ7450はインターネット上の情報を表示できる他、ネットワークに接続された他の電子機器を遠隔から操作する端末として用いることができる。

10

#### 【0240】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

#### 【符号の説明】

##### 【0241】

|       |              |

|-------|--------------|

| 11t   | トランジスタ       |

| 12t   | トランジスタ       |

| 16    | 容量素子         |

| 50    | 論理回路         |

| 51    | マルチプレクサ      |

| 52    | FF回路         |

| 55    | スキャンフリップフロップ |

| 102   | 副記憶回路部       |

| 103   | スイッチ         |

| 104   | スイッチ         |

| 107   | 容量素子         |

| 108   | 容量素子         |

| 109   | トランジスタ       |

| 110   | トランジスタ       |

| 113   | トランジスタ       |

| 114   | トランジスタ       |

| 200   | 半導体装置        |

| 200_  | 記憶回路         |

| 200_m | 記憶回路         |

| 200_1 | 記憶回路         |

| 211_1 | 回路           |

| 211_2 | 回路           |

| 220_  | 記憶回路         |

| 220_m | 記憶回路         |

| 220_1 | 記憶回路         |

| 220_2 | 記憶回路         |

| 221   | 第1の記憶部       |

| 221_a | トランスミッショングート |

| 221_b | インバータ        |

| 221_c | クロックドインバータ   |

| 222   | 第2の記憶部       |

| 222_a | トランスミッショングート |

| 222_b | インバータ        |

20

30

40

50

|                   |            |    |

|-------------------|------------|----|

| 2 2 2 c           | クロックドインバータ |    |

| 2 2 5             | 選択部        |    |

| 2 5 1             | 選択信号線      |    |

| 3 0 0             | 半導体装置      |    |

| 3 1 1 _ 1         | 回路         |    |

| 3 1 1 _ 2         | 回路         |    |

| 3 2 0 _ ( m + 1 ) | 記憶回路       |    |

| 3 2 0 _ 1         | 記憶回路       |    |

| 3 2 0 _ 2         | 記憶回路       |    |

| 3 2 1             | 第1の記憶部     | 10 |

| 3 2 1 b           | 第1の記憶部     |    |

| 3 2 1 d           | 第1の記憶部     |    |

| 3 2 2             | 第2の記憶部     |    |

| 3 2 2 b           | 第2の記憶部     |    |

| 3 2 2 d           | 第2の記憶部     |    |

| 3 2 5             | 選択部        |    |

| 3 3 0             | 副記憶回路      |    |

| 3 3 0 _ ( m + 1 ) | 副記憶回路      |    |

| 3 3 0 _ 2         | 副記憶回路      |    |

| 3 3 2             | インバータ      | 20 |

| 3 4 0 _ ( m + 1 ) | 選択回路       |    |

| 3 4 0 _ 2         | 選択回路       |    |

| 3 5 1             | 選択信号線      |    |

| 3 5 2             | 選択信号線      |    |

| 4 0 0             | 半導体基板      |    |

| 4 0 1             | 素子分離用絶縁膜   |    |

| 4 0 2             | 不純物領域      |    |

| 4 0 3             | 不純物領域      |    |

| 4 0 4             | ゲート電極      |    |

| 4 0 5             | ゲート絶縁膜     | 30 |

| 4 0 9             | 絶縁膜        |    |

| 4 1 0             | 配線         |    |

| 4 1 1             | 配線         |    |

| 4 1 5             | 配線         |    |

| 4 1 6             | 配線         |    |

| 4 1 7             | 配線         |    |

| 4 2 0             | 絶縁膜        |    |

| 4 2 1             | 配線         |    |

| 4 3 0             | 半導体膜       |    |

| 4 3 1             | ゲート絶縁膜     | 40 |

| 4 3 2             | 導電膜        |    |

| 4 3 3             | 導電膜        |    |

| 4 3 4             | ゲート電極      |    |

| 4 3 5             | 導電膜        |    |

| 4 4 0             | 絶縁膜        |    |

| 4 4 1             | 絶縁膜        |    |

| 4 4 2             | 絶縁膜        |    |

| 4 4 3             | 導電膜        |    |

| 7 1 0 0           | テレビジョン装置   |    |

| 7 1 0 1           | 筐体         | 50 |

|           |             |    |

|-----------|-------------|----|

| 7 1 0 3   | 表示部         |    |

| 7 1 0 5   | スタンド        |    |

| 7 1 0 7   | 表示部         |    |

| 7 1 0 9   | 操作キー        |    |

| 7 1 1 0   | リモコン操作機     |    |

| 7 2 0 1   | 本体          |    |

| 7 2 0 2   | 筐体          |    |

| 7 2 0 3   | 表示部         |    |

| 7 2 0 4   | キー ボード      |    |

| 7 2 0 5   | 外部接続ポート     | 10 |

| 7 2 0 6   | ポインティングデバイス |    |

| 7 3 0 1   | 筐体          |    |

| 7 3 0 2   | 筐体          |    |

| 7 3 0 3   | 連結部         |    |

| 7 3 0 4   | 表示部         |    |

| 7 3 0 5   | 表示部         |    |

| 7 3 0 6   | スピーカ部       |    |

| 7 3 0 7   | 記録媒体挿入部     |    |

| 7 3 0 8   | L E D ランプ   |    |

| 7 3 0 9   | 操作キー        | 20 |

| 7 3 1 0   | 接続端子        |    |

| 7 3 1 1   | センサ         |    |

| 7 3 1 2   | マイクロフォン     |    |

| 7 4 0 0   | 携帯電話機       |    |

| 7 4 0 1   | 筐体          |    |

| 7 4 0 2   | 表示部         |    |

| 7 4 0 3   | 操作ボタン       |    |

| 7 4 0 4   | 外部接続ポート     |    |

| 7 4 0 5   | スピーカ        |    |

| 7 4 0 6   | マイク         | 30 |

| 7 4 5 0   | コンピュータ      |    |

| 7 4 5 1 L | 筐体          |    |

| 7 4 5 1 R | 筐体          |    |

| 7 4 5 2 L | 表示部         |    |

| 7 4 5 2 R | 表示部         |    |

| 7 4 5 3   | 操作ボタン       |    |

| 7 4 5 4   | ヒンジ         |    |

| 7 4 5 5 L | 左側スピーカ      |    |

| 7 4 5 5 R | 右側スピーカ      |    |

| 7 4 5 6   | 外部接続ポート     | 40 |

【 図 1 】

【 図 2 】

〔 図 3 〕

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

| (51) Int.Cl.           | F I         | テーマコード(参考) |

|------------------------|-------------|------------|

| H 03K 19/173 (2006.01) | G 01R 31/28 | V          |

| H 01L 27/04 (2006.01)  | H 01L 27/04 | T          |

| H 01L 21/822 (2006.01) |             |            |

F ターム(参考) 5F083 AD01 AD02 AD21 AD69 GA06 GA10 HA02 HA06 JA36 JA37

JA39 NA01 PR22

5J034 AB04 CB02

5J042 BA19 CA07 CA15 CA24 CA27 DA03