(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-120943

(P2006-120943A)

(43) 公開日 平成18年5月11日(2006.5.11)

(51) Int.CI.

F 1

テーマコード(参考)

**H01L 23/14 (2006.01)**

**H01L 23/12 (2006.01)**

H01L 23/14 R

H01L 23/12 501W

審査請求 未請求 請求項の数 7 O L (全 15 頁)

|           |                              |          |                                           |

|-----------|------------------------------|----------|-------------------------------------------|

| (21) 出願番号 | 特願2004-308558 (P2004-308558) | (71) 出願人 | 000190688<br>新光電気工業株式会社<br>長野県長野市小島田町80番地 |

| (22) 出願日  | 平成16年10月22日 (2004.10.22)     | (74) 代理人 | 100070150<br>弁理士 伊東 忠彦                    |

|           |                              | (72) 発明者 | 山野 孝治<br>長野県長野市小島田町80番地 新光電氣<br>工業株式会社内   |

|           |                              | (72) 発明者 | 荒井 直<br>長野県長野市小島田町80番地 新光電氣<br>工業株式会社内    |

|           |                              | (72) 発明者 | 町田 洋弘<br>長野県長野市小島田町80番地 新光電氣<br>工業株式会社内   |

(54) 【発明の名称】チップ内蔵基板及びその製造方法

## (57) 【要約】

**【課題】** 本発明は、半導体チップを樹脂基材に内蔵するチップ内蔵基板及びその製造方法に関し、薄型化することができ、他のチップ内蔵基板を搭載すると共に、基板(例えば、マザーボード)に接続することのできるチップ内蔵基板及びその製造方法を提供することを課題とする。

**【解決手段】** 樹脂に球状のフィラーを樹脂基材31全体に対して60~90wt%含有させた樹脂基材31により半導体チップ33を内蔵すると共に、樹脂基材31を貫通する貫通ビア44と、樹脂基材31の上面31aに形成され、貫通ビア44と電気的に接続された第1の外部接続端子53と、樹脂基材31の下面31bに形成され、貫通ビア44と電気的に接続された第2の外部接続端子54とを設けた構成とした。

【選択図】 図2

本発明の実施例によるチップ内蔵基板の断面図

**【特許請求の範囲】****【請求項 1】**

半導体チップと、

該半導体チップを内蔵する樹脂基材と、

外部接続端子とを有するチップ内蔵基板において、

前記樹脂基材は、樹脂からなり、該樹脂に球状のフィラーを前記樹脂基材全体に対して 60 ~ 90 wt % 含有させたことを特徴とするチップ内蔵基板。

**【請求項 2】**

前記樹脂基材は、ガラス転移温度付近の温度での弾性率が 1 GPa ~ 3 GPa であることを特徴とする請求項 1 に記載のチップ内蔵基板。 10

**【請求項 3】**

前記樹脂基材は、ガラス転移温度よりも低い温度での熱膨張係数が 10 ppm ~ 15 ppm であることを特徴とする請求項 1 または 2 に記載のチップ内蔵基板。

**【請求項 4】**

前記樹脂基材の両面に前記外部接続端子を設けたことを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載のチップ内蔵基板。

**【請求項 5】**

前記半導体チップは、前記外部接続端子と接続される電極パッドを有し、

該電極パッドの材料に Al を用いた際、前記電極パッドをジンケート処理し、前記電極パッド上に Ni 層を設けたことを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載のチップ内蔵基板。 20

**【請求項 6】**

半導体チップと、

該半導体チップを内蔵する樹脂基材と、

外部接続端子とを有するチップ内蔵基板の製造方法において、

支持板上に前記半導体チップを配設する半導体チップ配設工程と、

前記半導体チップを覆うよう前記支持板上に前記樹脂基材を配設する樹脂基材配設工程と、

前記支持板を除去する支持板除去工程とを備え、

前記樹脂基材には、樹脂からなり、該樹脂に球状のフィラーを前記樹脂基材全体に対して 60 ~ 90 wt % 含有させることを特徴とするチップ内蔵基板の製造方法。 30

**【請求項 7】**

前記樹脂基材を貫通する貫通ビアを形成する貫通ビア形成工程と、

前記樹脂基材の一方の面に、前記貫通ビアと電気的に接続される第 1 の外部接続端子を形成する第 1 の外部接続端子形成工程と、

前記樹脂基材の他方の面に、前記貫通ビアと電気的に接続される第 2 の外部接続端子を形成する第 2 の外部接続端子形成工程とを設けたことを特徴とする請求項 6 に記載のチップ内蔵基板の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、チップ内蔵基板及びその製造方法に係り、特に半導体チップを樹脂基材に内蔵するチップ内蔵基板及びその製造方法に関する。

**【背景技術】****【0002】**

近年、半導体チップの高密度化が著しく進み、半導体チップのサイズが縮小されている。これに伴い、半導体チップが埋め込まれた基板、いわゆるチップ内蔵基板が提案されている。

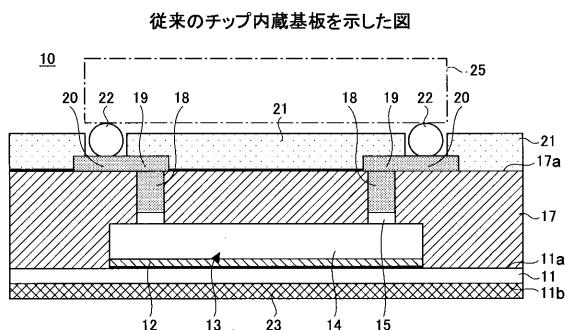

**【0003】**

図 1 は、従来のチップ内蔵基板を示した図である。図 1 に示すように、チップ内蔵基板 50

10は、大略すると支持板11と、半導体チップ13と、樹脂基材17と、ビア18と、配線19と、外部接続端子20と、ソルダーレジスト21と、はんだボール22と、樹脂層23とを有した構成とされている。半導体チップ13は、半導体チップ本体14と、電極パッド15とを有した構成とされている。

#### 【0004】

支持板11は、支持板11の上面11aに設けられた構造体（半導体チップ13や樹脂基材17等）を支持するためのものである。支持板11の上面11aには、電極パッド15が設けられていない側の半導体素子本体14が接着剤12により接着されている。樹脂基材17は、半導体チップ13を覆うよう支持板11上に設けられている。ビア18は、樹脂基材17に設けられており、電極パッド15と接続されると共に、樹脂基材17の面17aから露出されている。配線19は、樹脂基材17の面17a上に形成されており、ビア18と外部接続端子20とに接続されている。

#### 【0005】

外部接続端子20は、はんだボール22を配設するためのものであり、ソルダーレジスト21により露出されている。ソルダーレジスト21は、外部接続端子20を露出させると共に、配線19を覆うよう樹脂基材17上に設けられている。ソルダーレジスト21は、はんだボール22が配線19に接続されないように配線を保護するためのものである。はんだボール22は、外部接続端子20に設けられている。はんだボール22は、他のチップ内蔵基板25等の基板を接続するためのものである。支持板11の下面11bには、樹脂層23が形成されている。この樹脂層23は、支持体11上に支持された構造体（半導体チップ13や樹脂基材17等）が支持板11と共に反ることを防止するためのものである（例えば、特許文献1参照）。

【特許文献1】特開2001-217381号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0006】

しかしながら、従来の樹脂基材17は、ガラス転移温度付近の温度での弾性率が小さく、かつガラス転移温度よりも低い温度での熱膨張係数が大きいため、上記説明したようにチップ内蔵基板10が製造された後も、支持板11上の構造体（半導体チップ13や樹脂基材17等）を支持するために支持板11を残しておく必要があった。また、樹脂基材17の変形によるチップ内蔵基板10の反りを抑制するために、支持板11の下面11bに樹脂層23を設ける必要があった。このように、支持板11や樹脂層23を設ける必要があるため、チップ内蔵基板10を薄型化することが困難であるという問題があった。また、樹脂基材17の一方の面には、支持板11及び樹脂層23が設けられているため、支持板11及び樹脂層23が設けられない側の樹脂基材17にしか外部接続端子20を設けることができないという問題があった。なお、「ガラス転移温度」とは、樹脂の弾性率が急激に低下する温度である。ガラス転移温度で、樹脂の構造は、ガラス構造から、いわばゴム的な構造に転移する。

#### 【0007】

そこで本発明は、上述した問題点に鑑みなされたものであり、薄型化することができると共に、樹脂基材の両面に外部接続端子を設けて、他のチップ内蔵基板を搭載させ、基板へ接続することを可能とするチップ内蔵基板及びその製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

上記課題を解決するために本発明では、次に述べる各手段を講じたことを特徴とするものである。

#### 【0009】

請求項1記載の発明では、半導体チップと、該半導体チップを内蔵する樹脂基材と、外部接続端子とを有するチップ内蔵基板において、前記樹脂基材は、樹脂からなり、該樹脂

10

20

30

40

50

に球状のフィラーを前記樹脂基材全体に対して 60 ~ 90 wt % 含有させたことを特徴とするチップ内蔵基板により、解決できる。

【0010】

上記発明によれば、樹脂からなり、該樹脂に球状のフィラーを樹脂基材全体に対して 60 ~ 90 wt % 含有させた樹脂基材を用いることで、従来の樹脂基材よりもガラス転移温度付近の温度での弾性率が大きく、かつガラス転移温度よりも低い温度での熱膨張係数が小さくなり、樹脂基材の反りの発生が抑制され、従来のチップ内蔵基板のように支持板や樹脂層を設ける必要がなくなるため、チップ内蔵基板を薄型化することができる。なお、「ガラス転移温度」とは、樹脂の弾性率が急激に低下する温度である。

【0011】

請求項 2 記載の発明では、前記樹脂基材は、ガラス転移点付近での弾性率が 1 GPa ~ 3 GPa であることを特徴とする請求項 1 に記載のチップ内蔵基板により、解決できる。

【0012】

上記発明によれば、樹脂基材のガラス転移点付近での弾性率を従来の樹脂基材よりも大きい 1 GPa ~ 3 GPa とすることで、樹脂基材の反りの発生を抑制することができる。

【0013】

請求項 3 記載の発明では、前記樹脂基材は、ガラス転移点よりも低い温度での熱膨張係数が 10 ppm ~ 15 ppm であることを特徴とする請求項 1 または 2 に記載のチップ内蔵基板により、解決できる。

【0014】

上記発明によれば、樹脂基材のガラス転移点よりも低い温度での熱膨張係数を従来の樹脂基材よりも小さい 10 ppm ~ 15 ppm とすることで、熱変形を小さくして、熱を受けた際の反りの発生を抑制することができる。

【0015】

請求項 4 記載の発明では、前記樹脂基材の両面に前記外部接続端子を設けたことを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載のチップ内蔵基板により、解決できる。

【0016】

上記発明によれば、チップ内蔵基板に支持板を設ける必要がないため、樹脂基材の両面に外部接続端子を設けることが可能となり、チップ内蔵基板上に他のチップ内蔵基板を搭載させ、他のチップ内蔵基板を搭載したチップ内蔵基板を基板（例えば、マザーボード）に接続することができる。

【0017】

請求項 5 記載の発明では、前記半導体チップは、前記外部接続端子と接続される電極パッドを有し、該電極パッドの材料に Al を用いた際、前記電極パッドをジンケート処理し、前記電極パッド上に Ni 層を設けたことを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載のチップ内蔵基板により、解決できる。

【0018】

上記発明によれば、電極パッドの材料に Al を用いた際、電極パッドをジンケート処理することで、電極パッドが再酸化されることが防止され、電極パッド上に Ni 層を容易に形成することができる。また、Ni 層を、電極パッド上にビアを配設するための開口部を形成する際のストッパー膜として用いることができると共に、電極パッドが損傷することを防止できる。

【0019】

請求項 6 記載の発明では、半導体チップと、該半導体チップを内蔵する樹脂基材と、外部接続端子とを有するチップ内蔵基板の製造方法において、支持板上に前記半導体チップを配設する半導体チップ配設工程と、前記半導体チップを覆うよう前記支持板上に前記樹脂基材を配設する樹脂基材配設工程と、前記支持板を除去する支持板除去工程とを備え、前記樹脂基材には、樹脂からなり、該樹脂に球状のフィラーを前記樹脂基材全体に対して 60 ~ 90 wt % 含有させることを特徴とするチップ内蔵基板の製造方法により、解決できる。

10

20

30

40

50

## 【0020】

上記発明によれば、樹脂からなり、該樹脂に球状のフィラーを樹脂基材全体に対して 60 ~ 90 wt % 含有させた樹脂基材を用いることで、従来の樹脂基材よりもガラス転移温度付近の温度での弾性率が大きく、かつガラス転移温度よりも低い温度での熱膨張係数が小さくなり、樹脂基材の反りの発生が抑制され、従来のチップ内蔵基板のように支持板や樹脂層を設ける必要がなくなるため、チップ内蔵基板を薄型化することができる。

## 【0021】

請求項 7 記載の発明では、前記樹脂基材を貫通する貫通ビアを形成する貫通ビア形成工程と、前記樹脂基材の一方の面上に、前記貫通ビアと電気的に接続される第 1 の外部接続端子を形成する第 1 の外部接続端子形成工程と、前記樹脂基材の他方の面上に、前記貫通ビアと電気的に接続される第 2 の外部接続端子を形成する第 2 の外部接続端子形成工程とを設けたことを特徴とする請求項 6 に記載のチップ内蔵基板の製造方法により、解決できる。

10

## 【0022】

上記発明によれば、樹脂基材の一方の面上に、貫通ビアと電気的に接続される第 1 の外部接続端子と、樹脂基材の他方の面上に、貫通ビアと電気的に接続される第 2 の外部接続端子とを形成して、他のチップ内蔵基板をチップ内蔵基板に搭載させ、他のチップ内蔵基板を搭載したチップ内蔵基板を基板に接続することができる。

## 【発明の効果】

## 【0023】

本発明によれば、薄型化することができると共に、他のチップ内蔵基板をチップ内蔵基板に搭載させ、他のチップ内蔵基板を搭載したチップ内蔵基板を基板（例えば、マザーボード）に接続することのできるチップ内蔵基板及びその製造方法を提供できる。

20

## 【発明を実施するための最良の形態】

## 【0024】

次に、図面に基づいて本発明の実施例を説明する。

## (実施例)

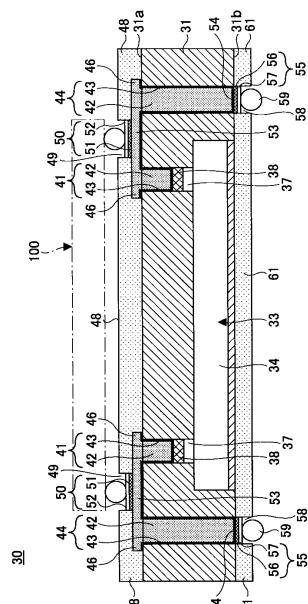

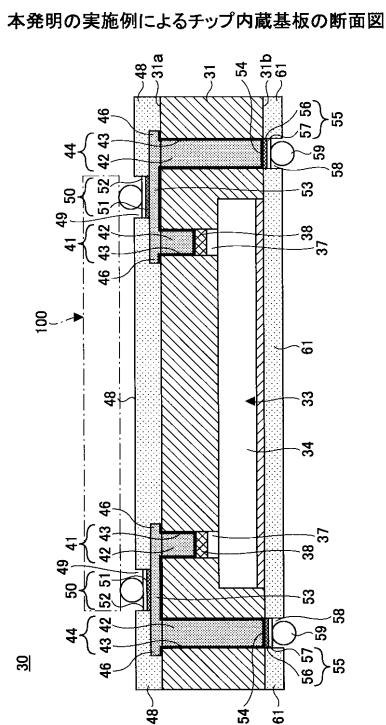

始めに、図 2 を参照して、本発明の実施例によるチップ内蔵基板 30 について説明する。図 2 は、本発明の実施例によるチップ内蔵基板の断面図である。チップ内蔵基板 30 は、大略すると半導体チップ 33 と、樹脂基材 31 と、ビア 41 と、貫通ビア 44 と、配線 46 と、ソルダーレジスト 48, 61 と、Ni / Au 層 50, 55 と、第 1 の外部接続端子 53 と、第 2 の外部接続端子 54 と、はんだボール 59 とを有した構成とされている。

30

## 【0025】

半導体チップ 33 は、半導体チップ本体 34 と、電極パッド 37 を有した構成とされている。電極パッド 37 は、半導体チップ本体 34 の一方の側に複数設けられている。電極パッド 37 の材料には、例えば、Al を用いることができる。電極パッド 37 上には、Ni 層 38 が形成されている。電極パッド 37 の材料として Al を用いた場合には、電極パッド 37 はジンケート処理され、その後、Ni 層 38 が形成される。Ni 層 38 は、電極パッド 37 上にビア 41 を配設するための開口部 71（図 5 参照）を形成する際のストッパー膜である。Ni 層 38 の厚さは、例えば、5 ~ 10 μm とすることができる。また、Ni 層 38 を電極パッド 37 上に設けることで、開口部 71 を形成する際に電極パッド 37 が損傷することを防止できる。

40

## 【0026】

ジンケート処理とは、酸化されやすい Al の表面に亜鉛めっきを行って、Al が再酸化されることを防止するための処理である。このように、Al からなる電極パッド 37 をジンケート処理して、再酸化を防止することで、電極パッド 37 上に形成される金属膜（本実施例の場合は Ni 層 38）との密着性を向上させることができる。

## 【0027】

半導体チップ 33 は、図 2 において、半導体チップ本体 34 の電極パッド 37 が設けられた側が上側となるよう配置されている。また、半導体チップ本体 34 の上面（電極パッド 37 が設けられた側の面）及び側面と電極パッド 37 とは、樹脂基材 31 により覆われ

50

ている。

【0028】

樹脂基材31は、半導体チップ33を内蔵すると共に、チップ内蔵基板30の基材となるものである。樹脂基材31は、樹脂からなり、該樹脂に球状のフィラーを樹脂基材31全体に対して60～90wt%含有させたものである。球状のフィラーの材料としては、例えば、 $\text{SiO}_2$ を用いることができる。球状のフィラーの粒径は、例えば、1～5μm程度とすることができます。なお、球状のフィラーが混合される樹脂には、例えば、エポキシ系樹脂、エポキシ系樹脂とポリアミドイミド(PAI)樹脂とを混合した混合樹脂、ポリアミドイミド(PAI)樹脂等を用いることができる。

【0029】

このように、樹脂に球状のフィラーを樹脂基材31全体に対して60～90wt%含有させた樹脂基材31を用いることで、従来の樹脂基材17よりもガラス転移温度付近の温度での弾性率が大きく、かつガラス転移温度よりも低い温度での熱膨張係数が小さくなり、樹脂基材31に反りが発生することが抑制され、従来のチップ内蔵基板10のように支持板11や樹脂層23を設ける必要がなくなるため、チップ内蔵基板30を薄型化することができる。また、球状のフィラーを樹脂に高充填するため、樹脂基材31の流動性及び硬化後の表面平滑性が向上し、半導体チップ33と樹脂基材31との隙間がなくなり、樹脂基材31により半導体チップ33を精度良く埋め込むことができる。さらに、レーザやエッティング等により、ビア41を形成するための開口部71(図5参照)や貫通ビア44を形成するための貫通孔72(図5参照)を樹脂基材31に形成する際、開口部71及び貫通孔72の加工精度を向上させることができる。

【0030】

樹脂基材31のガラス転移点付近での弾性率を1GPa～3GPa(従来の樹脂基材17のガラス転移点付近での弾性率は、1GPa未満)とすることにより、外力を受けた際、チップ内蔵基板30が変形(反りを含む)することを抑制できる。

【0031】

樹脂基材31のガラス転移温度よりも低い温度での熱膨張係数を10ppm～15ppm(従来の樹脂基材17のガラス転移温度よりも低い温度での熱膨張係数は100ppm程度で、X軸、Y軸、Z軸方向におけるばらつき有り)とすることにより、チップ内蔵基板30の製造工程において、熱処理を受けた際、製造中のチップ内蔵基板30の熱変形(熱による反りも含む)を抑制することができる。また、樹脂基材31は、従来の樹脂基材17と比較して、X軸、Y軸、Z軸方向における熱膨張係数のばらつきを小さくすることができる。なお、ppmは、parts per millionの略である。

【0032】

本実施例では、樹脂としてエポキシ系樹脂、球状のフィラーの材料として $\text{SiO}_2$ を用い、樹脂基材31全体に対して85wt%の $\text{SiO}_2$ の球状のフィラーをエポキシ系樹脂に含有させた樹脂基材31を用いて、弾性率及び熱膨張係数の評価を行った。その結果、弾性率が2GPa(測定時の温度は230)、熱膨張係数が12ppmという結果が得られた。なお、上記弾性率の測定には、動的粘弹性測定装置(DMA)を用い、熱膨張係数の測定(測定時の温度は210)には、熱機械分析装置(TMA)を用いた。また、上記評価に用いた樹脂基材31のガラス転移温度は、215であり、この場合、請求項に記載の「ガラス転移点付近」は、200～215であり、請求項に記載の「ガラス転移点よりも低い温度」は、215以下の温度である。

【0033】

上記評価結果から、本実施例の樹脂基材31を用いることにより、ガラス転移温度付近の温度での弾性率を従来の樹脂基材17よりも大きくでき、かつガラス転移温度よりも低い温度での熱膨張係数を従来の樹脂基材17よりも小さくできることができることが確認できた。

【0034】

ビア41は、樹脂基材31に設けられており、シード層43とC<sub>u</sub>膜42とを有した構成されている。シード層43には、例えば、無電解めっき法又はCVD法により形成され

10

20

30

40

50

たCu膜を用いることができる。また、Cu膜42は、例えば、電解めっき法により形成することができる。ビア41は、一方の端部において、Ni層38を介して、電極パッド37と電気的に接続されており、他方の端部において、配線46と接続されている。

#### 【0035】

貫通ビア44は、樹脂基材31を貫通するよう設けられており、シード層43とCu膜42とを有した構成されている。樹脂基材31の上面31aに露出された貫通ビア44の端部は、配線46と接続されている。

#### 【0036】

配線46は、第1の外部接続端子53を介してビア41と貫通ビア44との間を接続するためのものである。第1の外部接続端子53は、配線46を介して、ビア41及び貫通ビア44と電気的に接続されている。第1の外部接続端子53は、配線46と一緒に形成されており、例えば、Cu膜により構成することができる。

#### 【0037】

ソルダーレジスト48は、第1の外部接続端子53を露出する開口部49を有しており、樹脂基材31の上面31a及び配線46を覆うように設けられている。ソルダーレジスト48は、配線46を保護するためのものである。

#### 【0038】

Ni/Au層50は、第1の外部接続端子53上に設けられており、Ni層51とAu層52とから構成されている。Ni/Au層50は、第1の外部接続端子53に含まれるCuが拡散することを防止すると共に、はんだボール(図示せず)との密着性を向上させるためのものである。Ni/Au層50には、他のチップ内蔵基板100が接続される。Ni層51の厚さは、例えば、3μmとすることができます、Au層52の厚さは、例えば、0.1μmとすることができます。また、Au層52及びNi層51は、例えば、無電解めっき法により形成することができます。

#### 【0039】

先に説明したように、本実施例のチップ内蔵基板30では、樹脂に球状のフィラーを高充填させ、ガラス転移温度付近の温度での弾性率が大きく、かつガラス転移温度よりも低い温度での熱膨張係数が小さい樹脂基材31を用いているため、半導体チップ33を内蔵する樹脂基材31を支持する支持板(図示せず)をチップ内蔵基板30に設ける必要がない。そのため、図2に示すように、樹脂基材31の下面31bに露出された側の貫通ビア44の端部は、はんだボール59が接続可能な状態とされている。この樹脂基材31の下面31bに露出された側の貫通ビア44の端部が、第2の外部接続端子54である。第2の外部接続端子54は、はんだボール59を介して、マザーボード等の基板と接続されるものである。

#### 【0040】

このように、チップ内蔵基板30には、樹脂基材31の上面31a(樹脂基材31の一方の面)に第1の外部接続端子53と、樹脂基材31の下面31b(樹脂基材31の他方の面)に第2の外部接続端子54とが設けられているため、チップ内蔵基板30上に他のチップ内蔵基板100を搭載し、他のチップ内蔵基板100を搭載したチップ内蔵基板30を基板(例えば、マザーボード等の基板)に接続することができます。

#### 【0041】

ソルダーレジスト61は、第2の外部接続端子54を露出する開口部58を有しており、樹脂基材31の下面31b及び半導体チップ33の下端部を覆うように設けられている。Ni/Au層55は、第2の外部接続端子54に設けられており、Ni層56とAu層57とから構成されている。Ni/Au層55は、第2の外部接続端子54に含まれるCuがはんだボール59に拡散することを防止すると共に、はんだボール59との密着性を向上させるためのものである。はんだボール59は、Au層57と接続される。Ni層56の厚さは、例えば、3μmとすることができます、Au層57の厚さは、例えば、0.1μmとすることができます。また、Ni層56及びAu層57は、例えば、無電解めっき法により形成することができます。

## 【0042】

以上、説明したように、樹脂に球状のフィラーを樹脂基材31全体に対して60~90wt%含有させた樹脂基材31を用いることで、従来の樹脂基材17よりもガラス転移温度付近の温度での弾性率を大きく、かつガラス転移温度よりも低い温度での熱膨張係数を小さくして、チップ内蔵基板30を薄型化することができる。また、樹脂基材31の上面31aに第1の外部接続端子53と、樹脂基材31の下面31bに第2の外部接続端子53とを設けて、チップ内蔵基板30上に他のチップ内蔵基板100を搭載し、他のチップ内蔵基板100が搭載されたチップ内蔵基板30を基板（例えば、マザーボード等の基板）に接続することができる。

## 【0043】

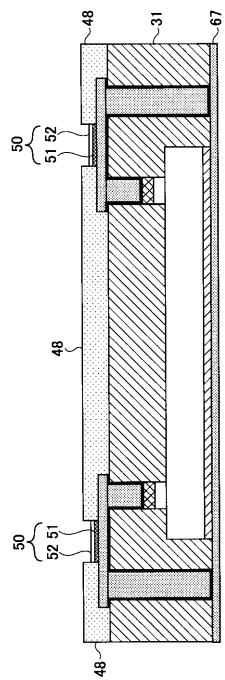

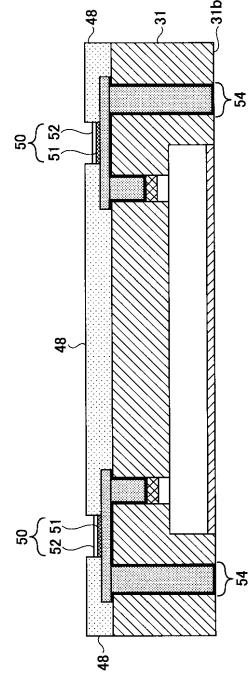

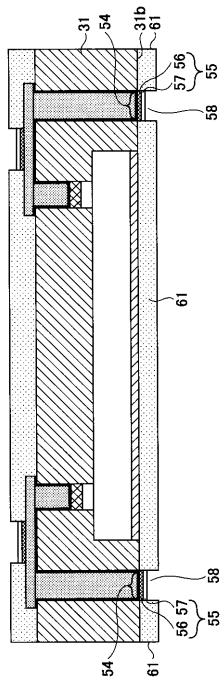

次に、図3乃至図18を参照して、本実施例のチップ内蔵基板30の製造方法について説明する。図3乃至図18は、本実施例のチップ内蔵基板の製造工程を示した図である。

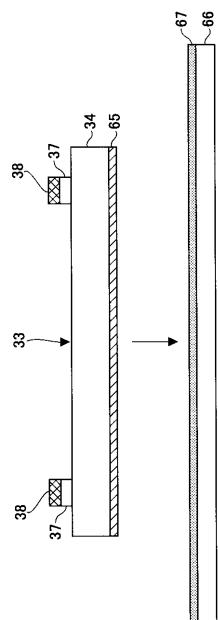

## 【0044】

始めに、図3に示すように、ジンケート法による前処理（ジンケート処理）が行われた電極パッド37（材料はA1）上にNi層38を形成する。このように、A1からなる電極パッド37をジンケート処理して、再酸化を防止することで、電極パッド37上に形成される金属膜（本実施例の場合はNi層38）との密着性を向上させることができる。Ni層38は、レーザ加工によりビア41を配設するための開口部71（図5参照）を樹脂基材31に形成する際のストッパー膜である。

## 【0045】

その後、電極パッド37が設けられていない側の半導体チップ本体34に接着剤65を塗布して、銅箔67が設けられた支持板66上に半導体チップ33を接着させる（半導体チップ配設工程）。銅箔67は、貫通ビア44が配設される貫通孔72（図5参照）を形成する際のストッパー膜である。

## 【0046】

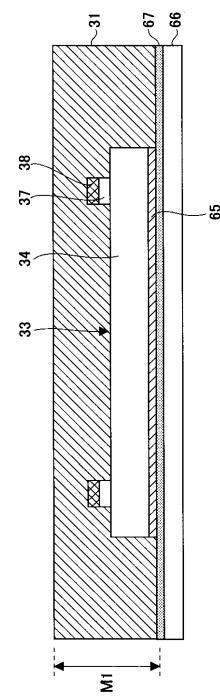

次に、図4に示すように、エポキシ系樹脂にSiO<sub>2</sub>の球状のフィラーを樹脂基材31全体に対して60~90wt%含有させたフィルム状の樹脂基材31により、支持板66上に配設された半導体チップ33と銅箔67とを覆うようラミネートし、必要に応じて、押圧、加熱して、樹脂基材31を硬化させる（樹脂基材配設工程）。樹脂基材31の厚さM1は、例えば、70μmとすることができます。

## 【0047】

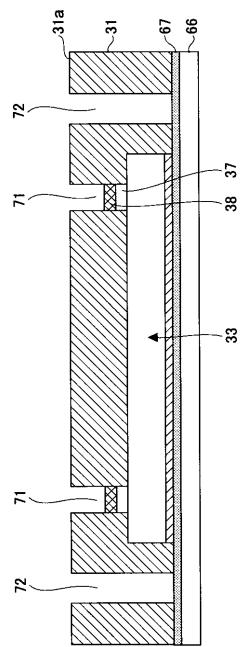

続いて、図5に示すように、レーザ加工により樹脂基材31を貫通する貫通孔72と、Ni層38を露出させる開口部71とを形成する。開口部71は、ビア41を配設するためのものである。貫通孔72は、貫通ビア44を配設するためのものである。開口部71の開口径は、例えば、50μmとすることができます。また、貫通ビア44の直径は、例えば、100μmとすることができます。なお、銅箔67とNi層38とは、レーザ加工により開口部71と貫通孔72とを形成する際のストッパー膜として用いる。

## 【0048】

次に、図6に示すように、開口部71、貫通孔72、及び樹脂基材31の上面31aにシード層43を形成する。シード層43には、例えば、無電解めっき法又はCVD法により形成されたCu膜（厚さは1~2μm程度）を用いることができる。

## 【0049】

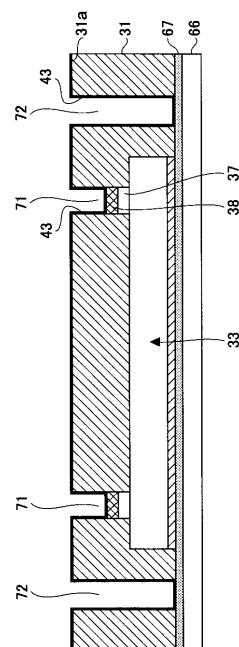

次に、図7に示すように、シード層43を給電層として、電解めっき法により開口部71及び貫通孔72にCu膜42を充填する。この際、電解めっき法を2回に分けて行う。このように、電解めっきを2回に分けて行うことで、開口部71及び貫通孔72に埋め込まれるCu膜42にボイド（埋め込み不良）が発生することを防止することができます。

## 【0050】

続いて、図8に示すように、バフ研磨装置又はCMP装置により樹脂基材31上のCu膜42が平坦になるよう研磨を行う。これにより、開口部71にシード層43とCu膜42からなるビア41と、貫通孔72にシード層43とCu膜42からなる貫通ビア44と

10

20

30

40

50

が形成される（貫通ビア形成工程）。

#### 【0051】

次に、図9に示すように、図8に示した構造体上に、開口部75を有したドライフィルムレジスト74を設ける。開口部75は、配線46が形成される領域46Aと、第1の外部接続端子53が形成される領域53Aとを露出する開口部である。続いて、電解めっき法により開口部75にめっき膜を成長させて、ビア41及び貫通ビア44に接続された配線46と、配線46と一体的に形成された第1の外部接続端子53とを形成する（第1の外部接続端子形成工程）。その後、ドライフィルムレジスト74はレジスト剥離処理により除去される。

#### 【0052】

次に、図10に示すように、第1の外部接続端子53を露出する開口部78を有したドライフィルムレジスト77をシード層43上に配線46を覆うように設ける。続いて、図11に示すように、開口部78に露出された第1の外部接続端子53上に、電解めっき法を用いて、Ni層51と、Au層52とを順次形成して、Ni/Au層50を設ける。ドライフィルムレジスト77は、Ni/Au層50を形成後にレジスト剥離処理により除去される。

#### 【0053】

次に、図12に示すように、配線46及びNi/Au層50を覆うようにドライフィルムレジスト81を設ける。続いて、図13に示すように、樹脂基材31の上面31aに形成されたシード層43をエッティングにより除去して、樹脂基材31の上面31aを露出させる。ドライフィルムレジスト81は、シード層43の除去後にレジスト剥離処理により除去される。

#### 【0054】

次に、図14に示すように、Ni/Au層50を露出させる開口部49を有したソルダーレジスト48を配線46及び樹脂基材31上に形成する。続いて、図15に示すように、支持板66の除去処理を行う（支持板除去工程）。支持板66は、例えば、バフ研磨により除去することができる。次に、図16に示すように、銅箔67の除去処理を行う。これにより、第2の外部接続端子54と樹脂基材31の下面31bとが露出される（第2の外部接続端子形成工程）。銅箔67は、例えば、CMP装置を用いて銅箔67を研磨することで除去することができる。

#### 【0055】

次に、図17に示すように、第2の外部接続端子54を露出する開口部58を有したソルダーレジスト61を形成する。続いて、無電解めっき法を用いて、第2の外部接続端子54にNi層56と、Au層57とを順次積層させて、Ni/Au層55を形成する。

#### 【0056】

その後、図18に示すように、Au層57にはんだボール59を配設することで、チップ内蔵基板30が製造される。なお、本実施例のチップ内蔵基板30においては、はんだボール59及びソルダーレジスト61を設けた構成としたが、はんだボール59及びソルダーレジスト61は必要に応じて設ければ良い。

#### 【0057】

上記説明したように、樹脂に球状のフィラーを樹脂基材31全体に対して60～90wt%含有させた樹脂基材31を用いてチップ内蔵基板30を製造することにより、従来の樹脂基材17よりもガラス転移温度付近の温度での弾性率を大きく、かつガラス転移温度よりも低い温度での熱膨張係数を小さくすることができ、これにより、支持板66を設ける必要や支持板66に樹脂層を設ける必要がなくなるため、支持板66を除去してチップ内蔵基板30を薄型化することができる。また、支持板66を設ける必要がなくなるため、樹脂基材31の両面31a, 31bに外部接続端子（第1及び第2の外部接続端子53, 54）を設けることが可能となり、チップ内蔵基板30上に他のチップ内蔵基板100を搭載して、他のチップ内蔵基板100が搭載されたチップ内蔵基板30を基板（例えば、マザーボード等の基板）へ接続することができる。

10

20

30

40

50

## 【0058】

以上、本発明の好ましい実施例について詳述したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲内に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。なお、開口部71及び貫通孔72は、エッチングにより形成しても良い。

## 【産業上の利用可能性】

## 【0059】

本発明によれば、薄型化することができると共に、樹脂基材の両面に外部接続端子を設けて、従来よりも多くの基板（例えば、マザーボード）を接続することのできるチップ内蔵基板及びその製造方法に適用できる。

10

## 【図面の簡単な説明】

## 【0060】

【図1】従来のチップ内蔵基板を示した図である。

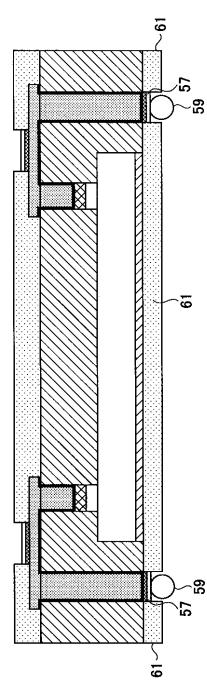

【図2】本発明の実施例によるチップ内蔵基板の断面図である。

【図3】本実施例のチップ内蔵基板の製造工程を示した図（その1）である。

【図4】本実施例のチップ内蔵基板の製造工程を示した図（その2）である。

【図5】本実施例のチップ内蔵基板の製造工程を示した図（その3）である。

【図6】本実施例のチップ内蔵基板の製造工程を示した図（その4）である。

【図7】本実施例のチップ内蔵基板の製造工程を示した図（その5）である。

20

【図8】本実施例のチップ内蔵基板の製造工程を示した図（その6）である。

【図9】本実施例のチップ内蔵基板の製造工程を示した図（その7）である。

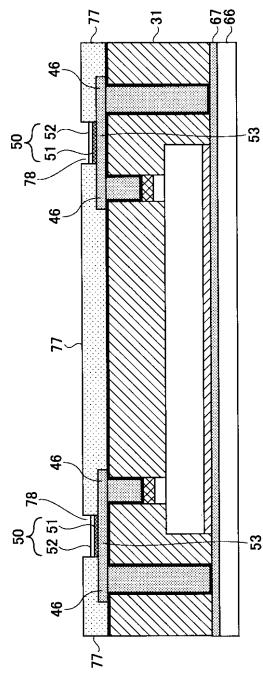

【図10】本実施例のチップ内蔵基板の製造工程を示した図（その8）である。

【図11】本実施例のチップ内蔵基板の製造工程を示した図（その9）である。

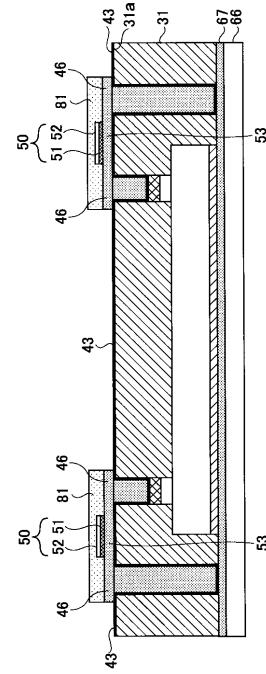

【図12】本実施例のチップ内蔵基板の製造工程を示した図（その10）である。

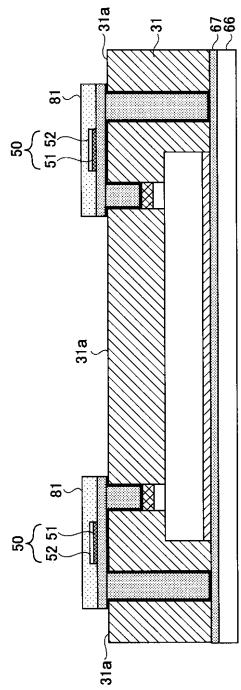

【図13】本実施例のチップ内蔵基板の製造工程を示した図（その11）である。

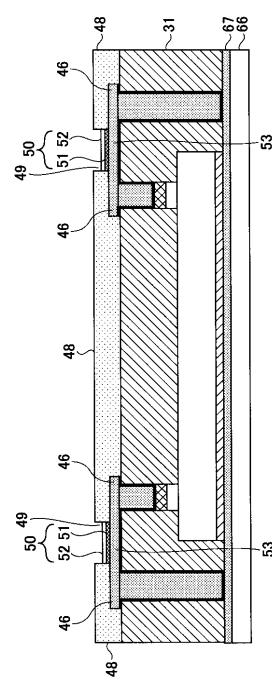

【図14】本実施例のチップ内蔵基板の製造工程を示した図（その12）である。

【図15】本実施例のチップ内蔵基板の製造工程を示した図（その13）である。

【図16】本実施例のチップ内蔵基板の製造工程を示した図（その14）である。

【図17】本実施例のチップ内蔵基板の製造工程を示した図（その15）である。

30

【図18】本実施例のチップ内蔵基板の製造工程を示した図（その16）である。

## 【符号の説明】

## 【0061】

10, 30 チップ内蔵基板

11, 66 支持板

11a, 31a 上面

11b, 31b 下面

12, 65 接着剤

13, 33 半導体チップ

14, 34 半導体チップ本体

15, 37 電極パッド

17, 31 樹脂基材

40

17a 面

18, 41 ピア

19, 46 配線

20 外部接続端子

21, 48, 68 ソルダーレジスト

22, 59 はんだボール

23 樹脂層

25, 100 他のチップ内蔵基板

38 Ni層

50

4 2 Cu 膜

4 3 シード層

4 4 貫通ビア

4 6 A , 5 3 A 領域

4 9 , 5 8 , 7 1 , 7 5 , 7 8 開口部

5 0 , 5 5 Ni / Au 層

5 1 , 5 6 Ni 層

5 2 , 5 7 Au 層

5 3 第 1 の外部接続端子

5 4 第 2 の外部接続端子

6 7 銅箔

7 2 貫通孔

7 4 , 7 7 , 8 1 ドライフィルムレジスト

M 1 厚さ

10

【図 1】

【図 2】

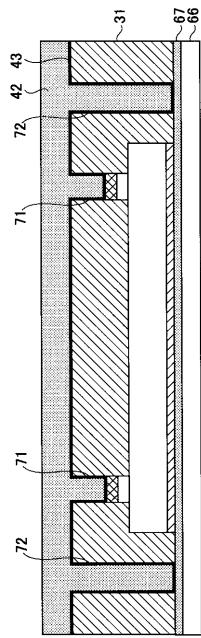

【図3】

本実施例のチップ内蔵基板の製造工程を示した図(その1)

【図4】

本実施例のチップ内蔵基板の製造工程を示した図(その2)

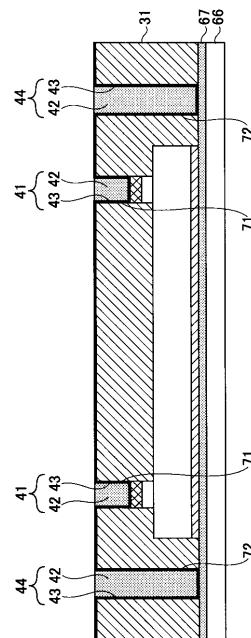

【図5】

本実施例のチップ内蔵基板の製造工程を示した図(その3)

【図6】

本実施例のチップ内蔵基板の製造工程を示した図(その4)

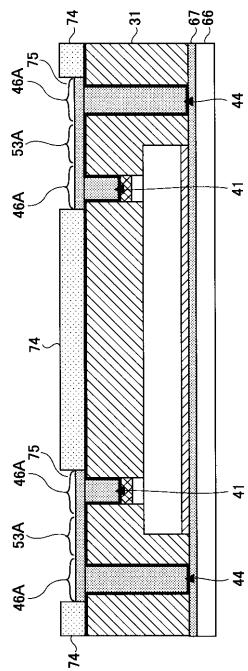

【図7】

本実施例のチップ内蔵基板の製造工程を示した図(その5)

【図8】

本実施例のチップ内蔵基板の製造工程を示した図(その6)

【図9】

本実施例のチップ内蔵基板の製造工程を示した図(その7)

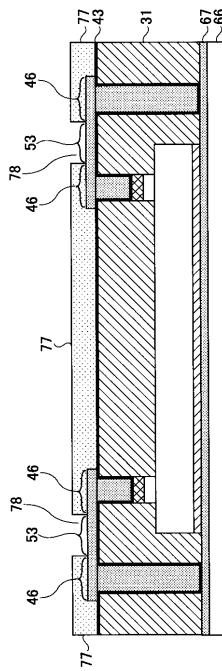

【図10】

本実施例のチップ内蔵基板の製造工程を示した図(その8)

【図11】

本実施例のチップ内蔵基板の製造工程を示した図(その9)

【図12】

本実施例のチップ内蔵基板の製造工程を示した図(その10)

【図13】

本実施例のチップ内蔵基板の製造工程を示した図(その11)

【図14】

本実施例のチップ内蔵基板の製造工程を示した図(その12)

【図15】

本実施例のチップ内蔵基板の製造工程を示した図(その13)

【図16】

本実施例のチップ内蔵基板の製造工程を示した図(その14)

【図17】

本実施例のチップ内蔵基板の製造工程を示した図(その15)

【図18】

本実施例のチップ内蔵基板の製造工程を示した図(その16)