(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294660

(P2005-294660A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

H01L 23/12

H05K 3/46

F 1

H01L 23/12

H05K 3/46

テーマコード(参考)

5E346

N

N

審査請求 未請求 請求項の数 5 O.L. (全 7 頁)

(21) 出願番号

特願2004-109656 (P2004-109656)

(22) 出願日

平成16年4月2日 (2004.4.2)

(71) 出願人 000003193

凸版印刷株式会社

東京都台東区台東1丁目5番1号

(72) 発明者 秋本 聰

東京都台東区台東1丁目5番1号 凸版印

刷株式会社内

(72) 発明者 大房 俊雄

東京都台東区台東1丁目5番1号 凸版印

刷株式会社内F ターム(参考) 5E346 AA01 AA12 AA15 AA35 AA43

BB01 BB11 CC08 CC31 CC54

DD02 DD22 DD33 DD47 EE31

EE39 FF04 FF35 GG17 GG22

GG23 GG28 HH25 HH26

(54) 【発明の名称】半導体装置用基板及びその製造方法

## (57) 【要約】

【課題】レーザー加工装置などのビアを形成するための設備を用いずに、配線パターンの接続部の更なる微細化を可能とした、薄型で高密度な配線パターンを有する半導体装置用基板及び製造方法を提供すること。

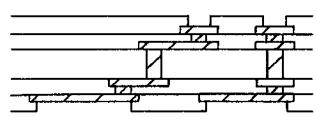

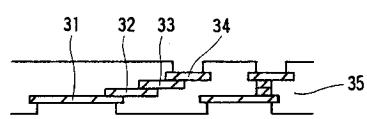

【解決手段】上下に隣接する配線層の上下配線パターン31～34が直接積み重なる構造の接続部と、上下配線パターンが接続部以外では接触、又は必要な絶縁抵抗値以下の間隔に近接しないように配設した複数の配線層を有すること。上下配線パターンは、厚みが3～35μmの金属又は導電性有機材料からなること。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

少なくとも、上下に隣接する配線層の上下配線パターンが直接積み重なる構造の接続部と、該上下配線パターンが接続部以外では接触、又は必要な絶縁抵抗値以下の間隔に近接しないように配設した複数の配線層を有することを特徴とする半導体装置用基板。

**【請求項 2】**

前記上下配線パターンは、厚みが3～35μmの金属又は導電性有機材料からなり、該上下配線パターンと略同一平面上の上下配線パターン周囲が絶縁物で覆われた層を有することを特徴とする請求項1記載の半導体装置用基板。

**【請求項 3】**

(1) 平坦なベース基板上に配線パターン(P1)とその周囲の絶縁物を表面が略同一平面状となるように形成する工程と、

(2) 次の配線パターン(P2)を上記配線パターン(P1)上に直接積み重ねて形成し接続部を設け、該配線パターン(P2)の周囲の絶縁物を表面が略同一平面状となるように形成する工程と、

(3) 上記(2)工程を必要な層数分繰り返す工程、

を少なくとも有することを特徴とする半導体装置用基板の製造方法。

**【請求項 4】**

前記(3)工程後に、平坦なベース基板の少なくとも一部を除去する工程を有することを特徴とする請求項3記載の半導体装置用基板の製造方法。

**【請求項 5】**

前記平坦なベース基板が50～700μmの厚みの金属板、ガラス板、プラスチック板、又はシリコン基板であることを特徴とする請求項3又は4記載の半導体装置用基板の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、複数の配線層からなり、薄型で高密度配線を有する半導体装置用基板に関する。

**【背景技術】****【0002】**

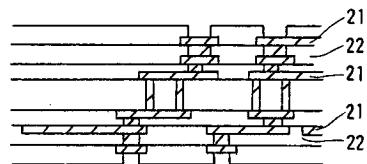

電子技術の進歩に伴い、電子情報端末の小型化、軽量化、高機能化がますます求められており、このため、半導体装置用基板においても、高密度化が強く求められている。従来、半導体装置用基板は、絶縁層と配線パターンが交互に繰り返された構造を有しているが、各層にある配線パターン間の電気的接続方法は、スルーホールもしくはビアホール等を介してなされている。即ち、断面構造は「配線層21(配線パターンとその周囲の絶縁物)」と「絶縁層22(絶縁物とビアホール)」を交互に積み重ねた構造、つまり、配線パターンが形成された配線層と、上下の配線パターンに対応して配置された50～150μm前後の円形パターンのみで構成されるビアホールが形成された絶縁層を交互に積み重ねた構造となっている(図1参照)。

**【0003】**

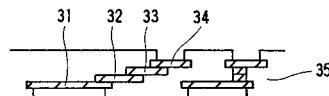

また、通常の多層基板やビルドアップ多層基板以外に、全層IVH構造の基板も知られている。この構造の基板には各種プロセスが提案されており、絶縁層となるプリプレグをレーザーで穿孔し、導電ペーストを充填した後、表裏に導箔を重ねて銅張積層板形成と同様なプロセスで表面が銅箔で覆われた素材を形成し、表面の導箔をエッチングして配線パターンを形成するもの(特許文献1～3)や、銅箔にとげ状の導電ペーストを印刷し、加熱硬化後にプリプレグと通常の銅箔を重ねて銅張積層板形成と同様なプロセスで表面が銅箔で覆われた素材を形成し、表面の導箔をエッチングして配線パターンを形成するもの(特許文献4)や、これと類似の技術が多数知られている(図2参照)。

**【0004】**

10

20

30

40

50

最近では、特殊な網目状の基材に感光剤を塗布し、露光した部位を活性化して無電解銅めっきを行うことで上下が貫通した導電部と非導電部を選択的に形成し、その表面に配線パターンを形成する技術が発表されている（非特許文献1）。

しかし、いずれの技術も導電部（ピアホール）を形成した絶縁層を基本として、その表面に配線パターンを形成し、配線層と絶縁層（+ピアホール）を交互に積み重ねる構造には変わりない。

#### 【0005】

従来技術においては、上下の配線パターン間を接続するためのピアホールを形成する場合、ピアホール径は通常  $100 \sim 200 \mu\text{m}$  程度で、ピアホールを受けるための上下のピアランドはそれより  $50 \sim 100 \mu\text{m}$  大きなサイズが必要だった。例えば、ピアホールが  $150 \mu\text{m}$  とすると、ピアランドの寸法はそれより  $60 \mu\text{m}$  大きな  $210 \mu\text{m}$  になる。

#### 【0006】

これに対し、同じ技術レベルのプロセスを用いても配線パターンは  $100 \mu\text{m}$  前後のピッチでの形成が可能で、配線パターン内にピアランドが存在すると、3本の配線が並んだ部分をピアランドが占めてしまい、配線密度が極端に低下する。また、より高密度を要求する製品にはUVレーザーでピアホールを形成するプロセスが知られており、この場合には  $50 \mu\text{m}$  程度までのピアが形成可能になっている。ピア径が  $50 \mu\text{m}$  の場合、ピアランド寸法は約  $110 \mu\text{m}$  になり、それでも1~2本の配線を阻害することになる。

#### 【0007】

このように、ピアホールが配線パターンの高密度化に大きく影響するため、ピアホールの更なる微細化とピアランド寸法とピア径との差の縮小が望まれている。しかし、 $50 \mu\text{m}$  程度かそれ以下のピア径では安定してピアを穿孔することが難しく、ピアのめっきについては前処理も含めて更に困難な状況となっている。

#### 【0008】

以上については、ピアホールを形成する場合の技術的課題だが、レーザー加工装置などのピアを形成するための設備が配線パターン形成設備以外に必要なことなど、設備的な問題も含んでいる。

#### 【特許文献1】特許第3231537号公報

#### 【特許文献2】特許2991032号公報

#### 【特許文献3】特許3366458号公報

#### 【特許文献4】特許第3251711号公報

【非特許文献1】東芝レビューVOL.57, No.4(2002)：「ナノ多孔質体と選択的めっき技術を組み合わせた新しい高密度配線技術」

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

本発明は、上記問題を解決するためになされたものであり、レーザー加工装置などのピアを形成するための設備を用いずに、配線パターンの接続部の更なる微細化を可能とした、薄型で高密度な配線パターンを有する半導体装置用基板を提供することを課題とするものである。

また、上記半導体装置用基板の製造方法を提供することを課題とする。

#### 【課題を解決するための手段】

#### 【0010】

即ち、請求項1記載の発明においては、少なくとも、上下に隣接する配線層の上下配線パターンが直接積み重なる構造の接続部と、該上下配線パターンが接続部以外では接触、又は必要な絶縁抵抗値以下の間隔に近接しないように配設した複数の配線層を有することを特徴とする半導体装置用基板としたものである。

これは、上述のように配線パターンどうしを直接積み重ねる接続部を設けることと、これによる隣接する配線層の配線パターンの短絡または配線パターンどうしが必要以上に近接

10

20

30

40

50

することによる絶縁性の低下を防ぐように考慮した配線パターンを有する半導体装置用基板としたものである。

#### 【0011】

また、請求項2記載の発明においては、前記上下配線パターンは、厚みが3～35μmの金属又は導電性有機材料からなり、該上下配線パターンと略同一平面上の上下配線パターン周囲が絶縁物で覆われた層を有することを特徴とする半導体装置用基板としたものである。

これは、上記請求項1の発明のうち、半導体装置用基板で使用される市販の銅箔に相当する配線パターン厚みに限定した金属とそれに代わりうる導電性有機材料を用い、配線パターン以外の部分が樹脂で充填されて略同一平面を成す構造の層を少なくとも1層以上含んだ構造としたものである。

#### 【0012】

また、請求項3記載の発明においては、(1)平坦なベース基板上に配線パターン(P1)とその周囲の絶縁物を表面が略同一平面状となるように形成する工程と、(2)次の配線パターン(P2)を上記配線パターン(P1)上に直接積み重ねて形成し接続部を設け、該配線パターン(P2)の周囲の絶縁物を表面が略同一平面状となるように形成する工程と、(3)上記(2)工程を必要な層数分繰り返す工程、を少なくとも有することを特徴とする半導体装置用基板の製造方法としたものである。

これは、平坦なベース基板上に配線パターンとその周囲を充填するような絶縁物をほぼ同じ厚みで形成し、表面が略同一平面となるように形成し、それを必要な層数だけ重ねることによって、所望の半導体装置用基板を得るための製造方法である。

#### 【0013】

また、請求項4記載の発明においては、前記(3)工程後に、平坦なベース基板の少なくとも一部を除去することを特徴とする半導体装置用基板の製造方法としたものである。

#### 【0014】

また、請求項5記載の発明においては、前記平坦なベース基板が50～700μmの厚みの金属板、ガラス板、プラスチック板、又はシリコン基板であることを特徴とする半導体装置用基板の製造方法としたものである。

これは、微細パターン形成に適した平滑で入手が容易な半導体用や表示装置用などに使用されるベース基板材料とその一般的な厚みについて規定したものである。

#### 【発明の効果】

#### 【0015】

本発明の半導体装置用基板は、接続部の構造が上下に隣接する配線層の上下配線パターンが直接積み重なる構造であるので、多層部に従来のビアホール(スルーホールやブラインドホール)を介さないで層間接続が可能なことから、超薄型で高密度配線を有する半導体装置用基板となる。

#### 【発明を実施するための最良の形態】

#### 【0016】

本発明者は、鋭意検討の結果、上記のような従来の問題を解決することができた。図3は、本発明による半導体装置用基板の一例の断面図である。図3に示すように、半導体装置用基板の接続部は、上下に隣接する配線層の上下配線パターン(31～34)が相互に直接積み重なる構造となっている。また、上下配線パターンは接続部以外では接触、又は必要な絶縁抵抗値以下の間隔に近接しないよう配設されている。

すなわち、従来のビアホール(スルーホールやブラインドホール)が必要ないことから、薄型で高密度配線を有する半導体装置用基板となる。

#### 【0017】

以下に、実施例に基づき、本発明をさらに具体的に説明するが、これに限定されるものではない。

#### 【実施例1】

10

20

30

40

50

## 【0018】

## (4層配線基板の作成)

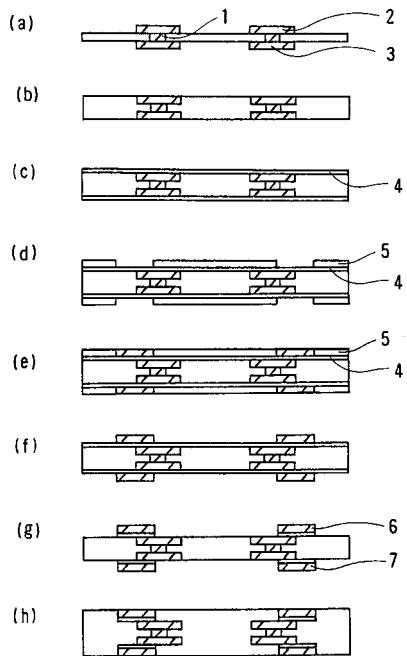

表裏に、第2層の配線パターン2及び第3層の配線パターン3が形成され、かつ、表裏がビアホール1で導通せしめてなる2層配線基板(図4(a))の両面に、絶縁性フィルム(ABF-70H(商品名)、味の素ファインテクノ(株)製)をラミネートし、140で60分間加熱して樹脂を硬化させた。この絶縁性フィルム表面を、両面ともバフによる物理研磨により、第2層、第3層の配線パターンの銅表面が露出するまで研磨を行った(図4(b))。

## 【0019】

次に、過マンガン酸処理を行って、絶縁性フィルム表面を両面とも粗化した後、無電解銅めっきを行いシード層4を形成した(図4(c))。その後、両面に厚みが20μmのドライフィルム(サンフォートAQ-2058(商品名)、旭化成(株)製)をラミネートし、平行光型の露光機で、それぞれ第1層と第4層の配線パターンを焼付け、1%炭酸ナトリウム溶液で現像し、ドライフィルムのパターン5を得た(図4(d))。その後、電解めっきにより配線パターン部をめっきした後(図4(e))、ドライフィルムを剥離し(図4(f))、フラッシュエッチングにより、シード層を除去することで、第1層の配線パターン6及び第4層の配線パターン7を形成した(図4(g))。

## 【0020】

この両面にこれまでと同様にして、絶縁性フィルム(ABF-70H(商品名)、味の素ファインテクノ(株)製)をラミネートし、140で60分間加熱して樹脂を硬化させ、両面とも表面をバフによる物理研磨により、第1層、第4層の配線パターンの銅表面が露出するまで研磨を行い、4層配線を有する多層回路基板を作成した(図4(h))。

## 【実施例2】

## 【0021】

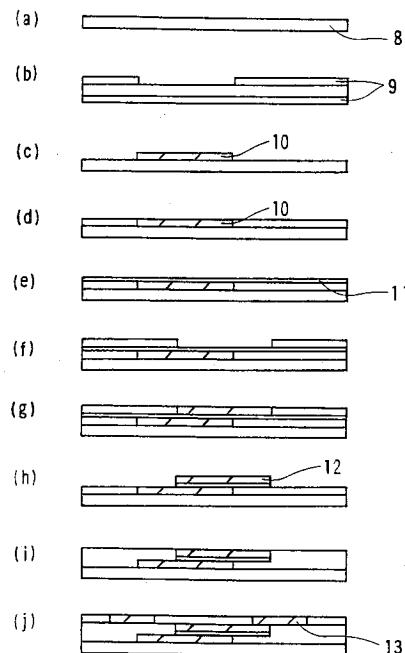

## (放熱板付き3層配線基板の作成)

厚みが100μmのジルコニウム系銅板8(C151(商品名)、三菱伸銅(株)製、CD4合金NO.C15100)(図5(a))の両面に、厚みが20μmのドライフィルム9(サンフォートAQ-2058(商品名)、旭化成(株)製)をラミネートし、平行光型の露光機で一方の面に配線パターンのネガパターンを焼付け、もう片方の面は全面露光を行った後、1%炭酸ナトリウム溶液で現像を行った後(図5(b))、電解めっきを約15μm行い、3%水酸化ナトリウム溶液でドライフィルムを剥離し、第3層の配線パターン10を形成した(図5(c))。

## 【0022】

次に、第3層の配線パターンを形成した側に絶縁性フィルム(ABF-70H(商品名)、味の素ファインテクノ(株)製)をラミネートし、140で60分間加熱して樹脂を硬化させた。この絶縁性フィルム表面をバフによる物理研磨により、第3層の配線パターンの銅表面が露出するまで研磨を行った(図5(d))。

次に、過マンガン酸処理を行って、絶縁性フィルム表面を粗化した後、無電解銅めっきを行いシード層11を形成した(図5(e))。その後、第3層の配線パターンを形成したときと同様に、両面に厚みが20μmのドライフィルム(サンフォートAQ-2058(商品名)、旭化成(株)製)をラミネートし、平行光型の露光機で第3層の配線パターンがある面に第2層の配線パターンのネガパターンを焼付け、もう片方の面は全面露光を行った後、1%炭酸ナトリウム溶液で現像(図5(f))、電解めっき(図5(g))、ドライフィルムを剥離し、第2層の配線パターン12を形成した(図5(h))。この工程を繰り返すことにより第1層の配線パターン13を形成し、放熱板付き3層配線を有する多層回路基板を作成した(図5(j))。

## 【実施例3】

## 【0023】

## (超薄膜3層配線基板の作成)

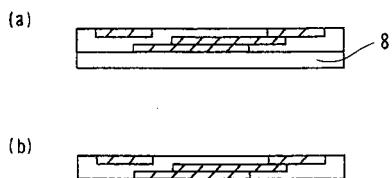

実施例2で作成した放熱板付き3層配線を有する多層回路基板(図6(a))の配線層

10

20

30

40

50

側の面を、厚みが 20 μm のドライフィルム（サンフォート AQ-2058（商品名）、旭化成（株）製）をラミネートすることで保護し、他方面のジルコニウム系銅板 8 をエッチングにより除去することで、超薄膜 3 層配線基板を作成した（図 6（b））。

【0024】

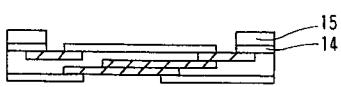

以上、実施例に基づき具体例を述べたが、これに限定されるものではない。また、本発明においては、必要に応じて、既存のソルダーレジスト 14 やカバーレイをコーティングする構成としても良く（図 7）、さらに接続端子に金めっき、錫めっき、耐熱プリフラックス塗布などの防錆用の処理を施しても良い。また、ハンドリング性向上のため、ステイフナー（補強板）15 を搭載してもよい（図 8）。

【図面の簡単な説明】

10

【0025】

【図 1】従来の一般的なビルドアップ技術による半導体装置用基板の構成を示す断面図である。

【図 2】従来の薄型基板技術による半導体装置用基板の構成を示す断面図である。

【図 3】本発明に係わる半導体装置用基板の構成を示す断面図である。

【図 4】実施例 1 の工程説明図である。

【図 5】実施例 2 の工程説明図である。

【図 6】実施例 3 の工程説明図である。

【図 7】スルダーレジストを形成した説明図である。

【図 8】ステイフナーを形成した説明図である。

20

【符号の説明】

【0026】

1 . . . ピアホール

2、12 . . . 第 2 層の配線パターン

3、10 . . . 第 3 層の配線パターン

4、11 . . . シード層

5 . . . ドライフィルムのパターン

6、13 . . . 第 1 層の配線パターン

7 . . . 第 4 層の配線パターン

8 . . . ジルコニウム系銅板

30

9 . . . ドライフィルム

14 . . . ソルダーレジスト

15 . . . ステイフナー

21 . . . 配線層

22 . . . 絶縁層

23 . . . 表面の導箔をエッチングして配線パターンを形成するもの

31、32、33、34 . . . 上下配線パターン

35 . . . 絶縁物

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】