(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 10 2004 049 099 B4 2007.08.09

(12)

## Patentschrift

(21) Aktenzeichen: 10 2004 049 099.6

(51) Int Cl.<sup>8</sup>: G06F 1/32 (2006.01)

(22) Anmelddatum: 08.10.2004

G06F 11/30 (2006.01)

(43) Offenlegungstag: 27.10.2005

(45) Veröffentlichungstag

der Patenterteilung: 09.08.2007

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

(30) Unionspriorität:

2004-095814 29.03.2004 JP

(72) Erfinder:

Sayama, Masahiko, Kobe, Hyogo, JP; Kanzaki, Shouzou, Tokio/Tokyo, JP

(73) Patentinhaber:

Mitsubishi Denki K.K., Tokyo, JP

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

EP 10 83 475 A1

(74) Vertreter:

HOFFMANN & EITLE, 81925 München

### (54) Bezeichnung: Elektronische Steuervorrichtung für ein Fahrzeug

(57) Hauptanspruch: Elektronische Steuervorrichtung für ein Fahrzeug, mit:

– einem Hauptsteuer-Schaltungsabschnitt (110a, 110b) zum Ansteuern von diversen Stromverbrauchern (105) gemäß dem Betriebszustand verschiedener Eingangssensoren (107, 108) und Inhalten eines ersten Programmspeichers (111b, 111e), wobei der Hauptsteuer-Schaltungsabschnitt mittels eines Hauptstromversorgungsschaltkreises (114a) über ein steuerbares Schaltelement (104a, 104b, 141) aus einer Fahrzeughbatterie (101) mit elektrischer Energie versorgt wird; und

– einem Zeitgeberschaltungsabschnitt (120a, 120b), der über einen Unter-Stromversorgungsschaltkreis (124) zu jeder Zeit mit elektrischer Energie von der Fahrzeughbatterie (101) versorgt wird, und eine Zeitspanne einer Unterbrechung der Versorgung des Hauptstromversorgungsschaltkreises (114a) misst, und ein Aufweck-Ausgangssignal (WUP) erzeugt, um den Hauptstromversorgungsschaltkreis (114a) mit der Fahrzeughbatterie (101) zu verbinden, wenn die gemessene Zeitspanne eine bestimmte Aufweck-Sollzeit erreicht hat,

dadurch gekennzeichnet, dass der Zeitgeberschaltungsabschnitt (120a, 120b) umfasst:

– einen Zählzähler (310) zum Zählen eines von einem Zeittaktsignal erzeugungsschaltkreis (301) erzeugten Taktsignals und Messen der verstrichenen Zeitspanne seit der Unterbrechung des Hauptstromversorgungsschaltkreises (114a) als Reaktion...

**Beschreibung****HINTERGRUND DER ERFINDUNG****1. Gebiet der Erfindung**

**[0001]** Die vorliegende Erfindung betrifft eine elektronische Steuervorrichtung für ein Fahrzeug und eine Verbesserung in der Zeitgeber- bzw. Timer-Startsteuerung in einem Automatikzustand in einer Fahrzeugelektroniksteuereinrichtung und insbesondere eine Fahrzeugelektroniksteuereinrichtung, die entworfen ist, um eine höhere Zuverlässigkeit in Bezug auf das Verhindern des durch eine Fehlfunktion bedingten Startens zu erreichen.

**2. Beschreibung des Standes der Technik**

**[0002]** Eine Fahrzeugelektroniksteuereinrichtung, die einen als Haupt-CPU bzw. Hauptzentralverarbeitungseinheit arbeitenden Mikroprozessor enthaltende Hauptsteuerschaltungsabschnitt und einen Zeitgeber- bzw. Timer-Schaltungsabschnitt enthält, ist wohl bekannt.

**[0003]** Beispielsweise schlägt die japanische Patentveröffentlichung (ungeprüft) Nummer 315474/2003 mit dem Titel "Elektroniksteuereinrichtung und integrierte Halbleiterschaltung" ein Konzept vor, in welchem in Bezug auf einen Soak-Timer zum Erfassen einer verbleibenden Zeitdauer für eine Vorheizsteuerung eines Kühlmittels, eine Transpirations erfassung von Kraftstoff oder ähnlichem, ein eine große Vielfalt von Anwendungen abdeckender Soak-Timer offenbart ist zum Messen einer verbleibenden Zeitdauer mit einer Messzeit und einer Messgenauigkeit gemäß der Anwendung.

**[0004]** Als ein für diese Erfindung relevanter Stand der Technik schlägt die japanische Patentveröffentlichung (ungeprüft) Nummer 18315/1993 mit dem Titel "Automobilmotorsteuereinrichtung" ein anderes Konzept vor, in welchem eine Zentralverarbeitungseinheit (CPU), die von einer Bordbatterie mit einer elektrischen Energie über einen Ausgangskontakt und eine Energieversorgungsschaltung eines Energieversorgungsrelais gespeist wird, welches arbeitet, wenn ein Leistungsschalter geschlossen ist, der Betrieb des Energieversorgungsrelais gehalten wird, wenn ein Impulssignal zu generieren ist zur Zeit des Normalbetriebs einer CPU, und die CPU verschiedene Initialisierungsverarbeitungen ausführt, und dann das Erzeugen von Impulsen stoppt, nachdem der Energieversorgungsschalter in eine offene Schaltstellung gebracht wird, hierdurch die Erregung des Energieversorgungsrelais abbauend.

**[0005]** Aus EP 1 083 475 A1 ist ein Multimedia/Personalcomputerbasiertes System zum Betreiben von Informations-, Kommunikations- und Unterhaltungs-

geräten in einem Fahrzeug bekannt, wobei das System ein Power-Management-System verwendet, das eine Leistung einem flüchtigen Speicher während eines Motoranlassens bereitstellt. Während eines Motoranlassens verringert sich die Batteriespannung bis auf einen Punkt, bei dem die meisten elektronischen Geräte nicht mehr funktionieren können. Ein jenseits eines Hauptprozessor-Boards untergebrachter Mikroprozessor schaltet einen Primärspannungsregler, der eine Vielzahl geregelter Spannungen dem Hauptprozessor-Board bereitstellt, ab, um Leistungsanforderungen zu reduzieren. Das Hauptprozessor-Board speichert einen Zustand von vorbestimmten Peripheriegeräten in einem flüchtigen Speicher und schaltet dann die Geräte ab. Der Hauptprozessor geht dann in einen Wartemodus über, wobei er auf ein Aufwecksignal von dem Mikroprozessor wartet. Ein Sekundärspannungsregler schaltet die Energieversorgung für den flüchtigen Speicher an, wenn der Primärspannungsregler abgeschaltet wird.

**[0006]** Die japanische Patentveröffentlichung (ungeprüft) Nummer 19785311992 mit dem Titel "Fahrzeugdiebstahlsicherungseinrichtung" schlägt ein weiteres Konzept vor, in welchem eine Überwachungslichtemissionseinrichtung in einen Blinkzustand versetzt wird und ein Blinkzyklus davon länger gemacht wird, wenn eine ablaufende Zeitdauer zunimmt vom Beginn des Alarmierens.

**[0007]** In der oben erwähnten Elektroniksteuereinheit gemäß der japanischen Patentveröffentlichung (ungeprüft) Nummer 315474/2003 wird ein Energieversorgungsrelais mit einem ODER-Ausgang von Ausgangssignalen des Energieversorgungsschalters und des Soak-Timers erregt zum Speisen einer elektrischen Energie zu der Fahrzeugelektroniksteuereinrichtung. Demgemäß wird in dem Fall, in dem ein Energieversorgungsrelais eingeschaltet bleibt, bedingt durch zum Beispiel eine Fehlfunktion des Soak-Timers, und die Fahrzeugelektroniksteuereinheit mit einer elektrischen Energie über eine lange Zeitdauer in einem Automatikzustand bzw. unbeobachteten Zustand betrieben wird, ein Überentladen einer Bordbatterie hervorgerufen.

**[0008]** Darüber hinaus gibt es ein hohes Risiko des Hervorrufs eines Brandunfalls von Fahrzeugstromverbrauchern, die in ungeeigneter Weise mit einer elektrischen Energie in dem Zustand gespeist werden, dass ein Motor gestoppt ist. Die oben erwähnte Elektroniksteuereinheit ist eine gegen Automatikenenergiezufuhr nicht geschützte Schaltungsanordnung.

**[0009]** Es ist eine Aufgabe der vorliegenden Erfindung eine Fahrzeugelektroniksteuereinrichtung bereitzustellen, die so ausgebildet ist, dass ein unerwünschter automatischer Betrieb der Steuereinrichtung wirksam verhindert werden kann.

## KURZBESCHREIBUNG DER ZEICHNUNGEN

**[0010]** Die Aufgabe wird durch den Gegenstand gemäß dem Anspruch 1 gelöst. Vorteilhafte Ausführungsformen sind in den abhängigen Ansprüchen definiert.

**[0011]** Eine Fahrzeugelektroniksteuereinrichtung wird beispielsweise aus einem Hauptsteuerschaltungsabschnitt gebildet, der mit einem als Haupt-CPU arbeitenden Mikroprozessor versehen ist, und einem Timer-Schaltungsabschnitt, der eine Zeitdauer ansprechend auf einen Zeitperiodenmessstartbefehl des als die erwähnte Haupt-CPU arbeitenden Mikroprozessors misst. Die Fahrzeugelektroniksteuereinrichtung schließt einen Speicher ein, der einen festgelegten Zeitdauerbefehl von der erwähnten Haupt-CPU des Mikroprozessors speichert, der als eine Sub-CPU arbeitet, ausgerüstet mit einem abgelaufenen Zeitdauer von einem Zeitdauer-messstartbefehl des erwähnten, als Haupt-CPU arbeitenden, Mikroprozessors messenden Zeitgeberzähler, und einer ersten und zweiten Rückstellvorrichtung zum Löschen eines gespeicherten Inhaltes dieses Speichers. Die erwähnte erste Rückstellvorrichtung ist eine Zwangsstoppbefehl-Vorrichtung zum Ausführen des Rückstellens mit der erwähnten, durch die erwähnte Sub-CPU gestarteten, Haupt-CPU; und die erwähnte zweite Rückstellvorrichtung ist eine Selbstrückstellvorrichtung, die arbeitet, wenn das Rückstellen der erwähnten ersten Rückstellvorrichtung nicht ausgeführt wird, selbst wenn seit dem Start der erwähnten Haupt-CPU mit Hilfe der erwähnten Sub-CPU eine vorbestimmte Zeitdauer verstrichen ist, und das Speichern des Starts durch die erwähnte Sub-CPU mit einem Rückstellzeitgeber bzw. Rückstell-Timer zurückstellt, der in dem erwähnten Timer-Schaltungsabschnitt vorgesehen ist.

**[0012]** Gemäß der erwähnten Fahrzeugelektroniksteuereinrichtung bestimmt die Haupt-CPU die Schließdauer nach dem Erzeugen einer Schließ-Treiberausgangsgröße, so dass eine lange Zeitdauer der Energieversorgung nicht unnötiger Weise ausgeführt wird, hierdurch einen Vorteil erzielend, dass das Entladen einer Bordbatterie unterdrückt werden kann. Zudem stoppt in dem Fall, in dem die Haupt-CPU das Erzeugen der Schließ-Treiberausgangsgröße nicht stoppt, der Timer-Schaltungsabschnitt selbst die Schließ-Treiberausgangsgröße mit dem Rückstell-Timer, so dass es einen Vorteil der erhöhten Sicherheit gibt.

**[0013]** Die vorangegangenen und andere Ziele, Merkmale, Aspekte und Vorteile der vorliegenden Erfindung werden aus der folgenden detaillierten Beschreibung der vorliegenden Erfindung ersichtlicher, wenn betrachtet im Zusammenhang mit den beiliegenden Zeichnungen.

**[0014]** Es zeigt:

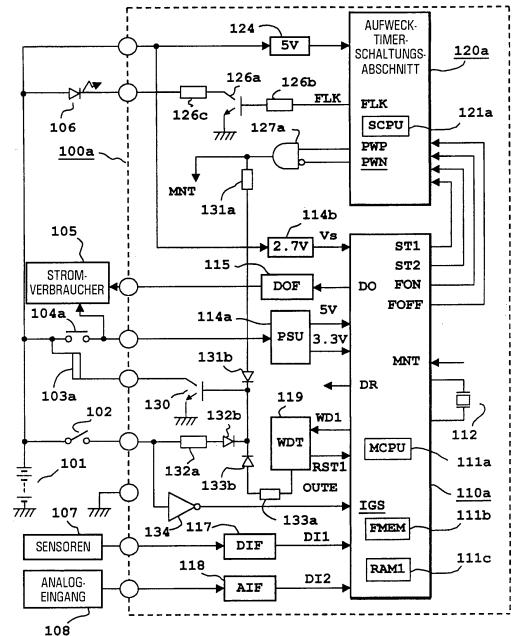

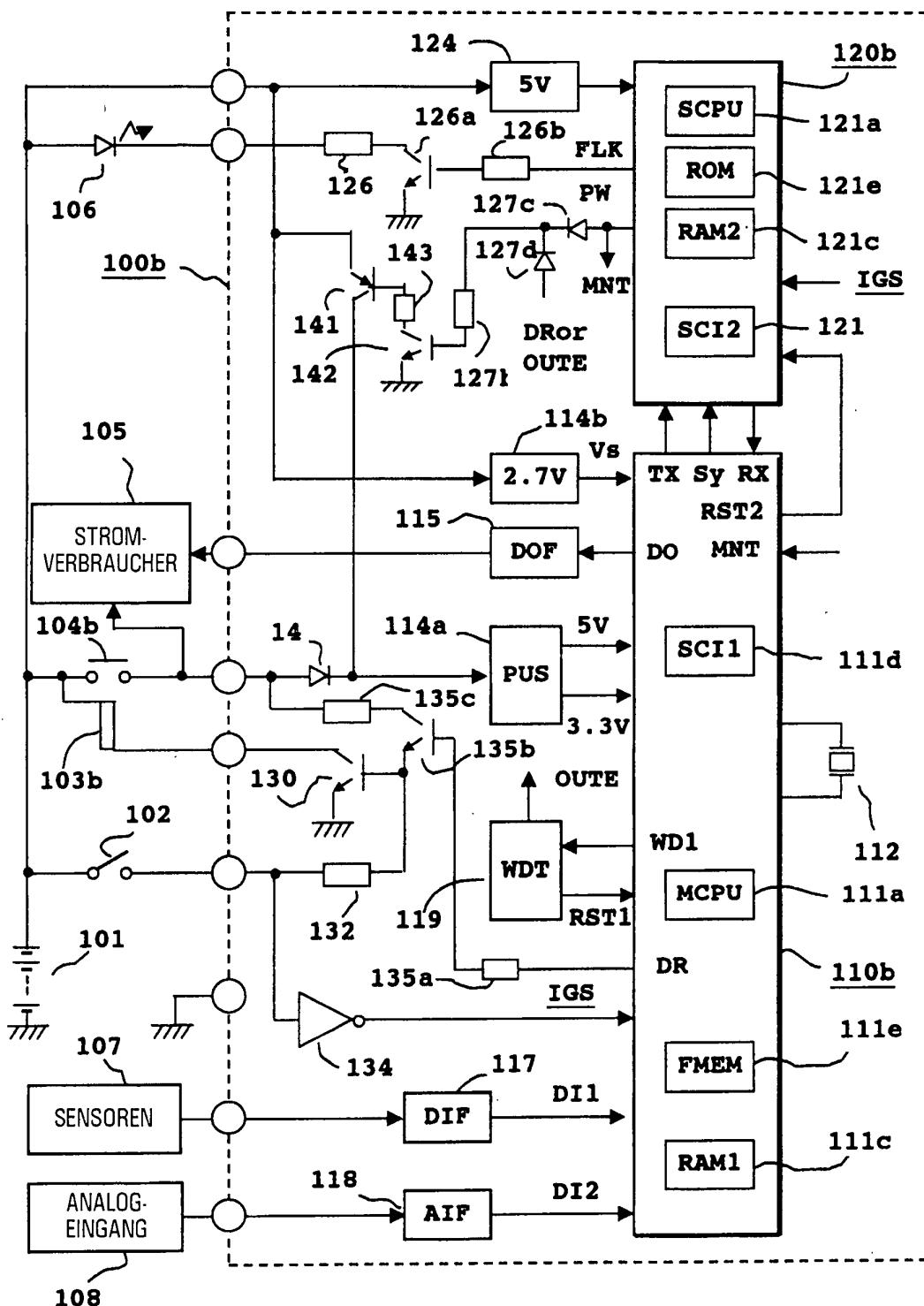

**[0015]** [Fig. 1](#) eine schematische Ansicht einer Gesamtgrundordnung gemäß der ersten bevorzugten Ausführungsform der vorliegenden Erfindung;

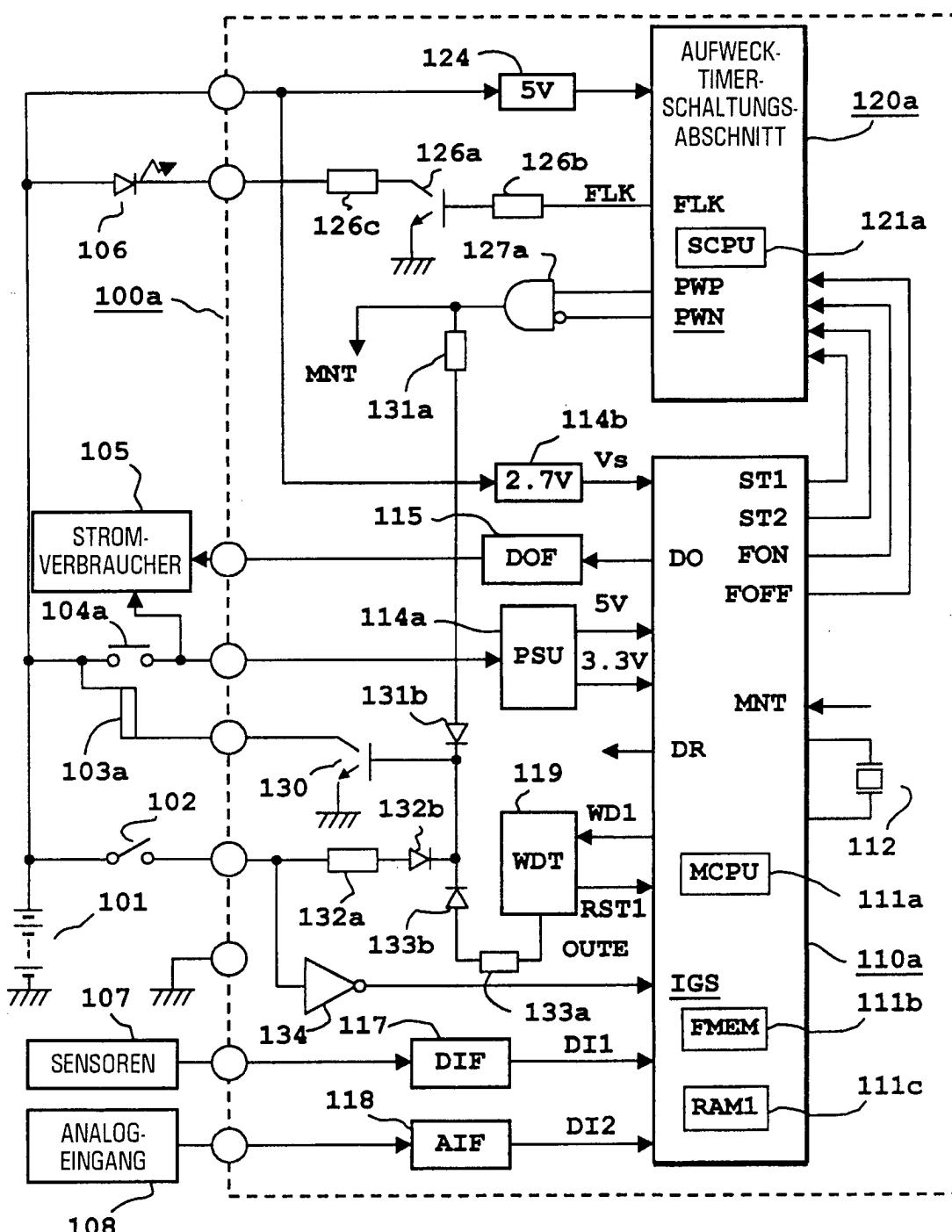

**[0016]** [Fig. 2](#) ein Betriebsablaufzeitdiagramm einer Energieversorgungsschaltung der [Fig. 1](#);

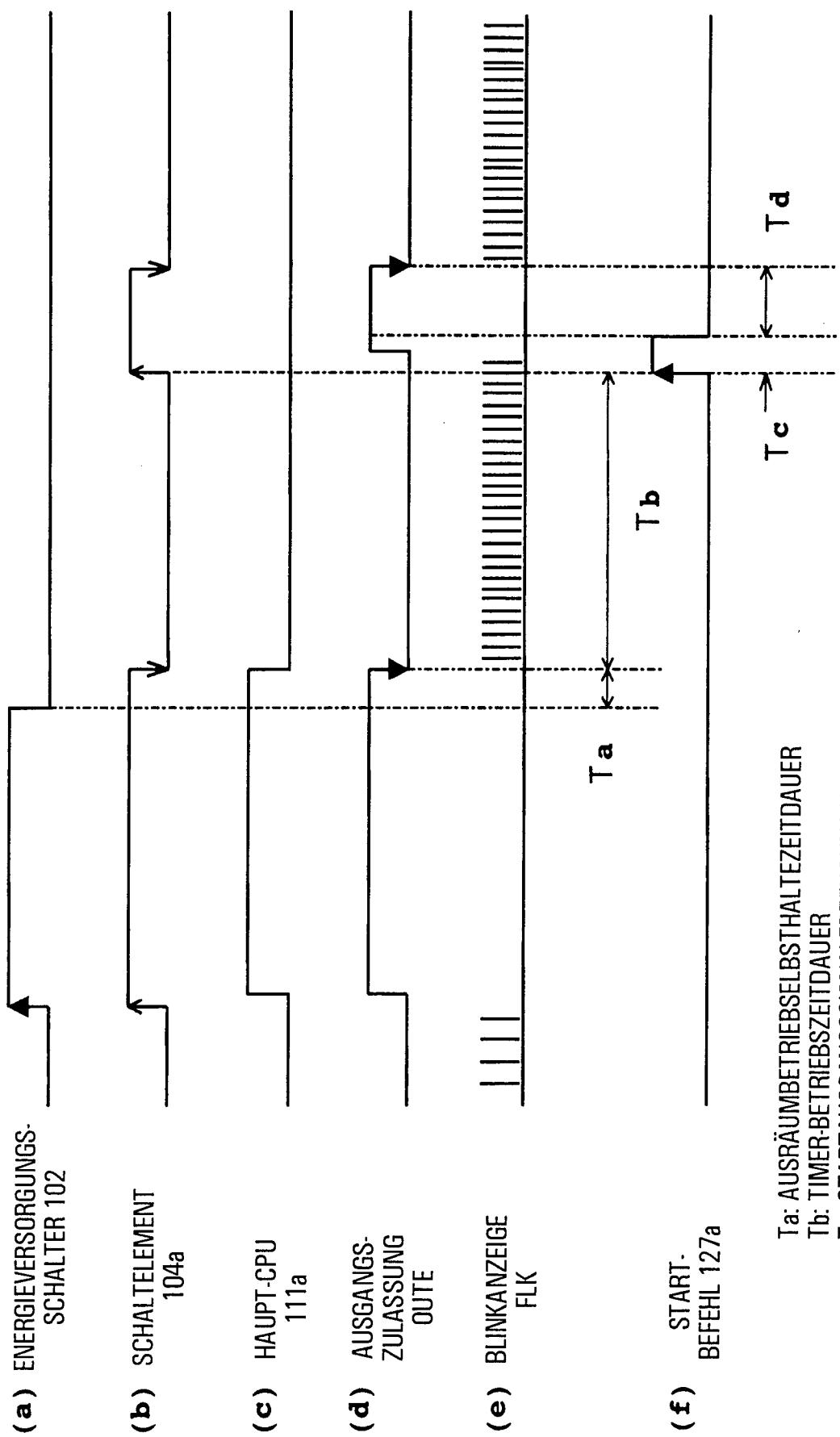

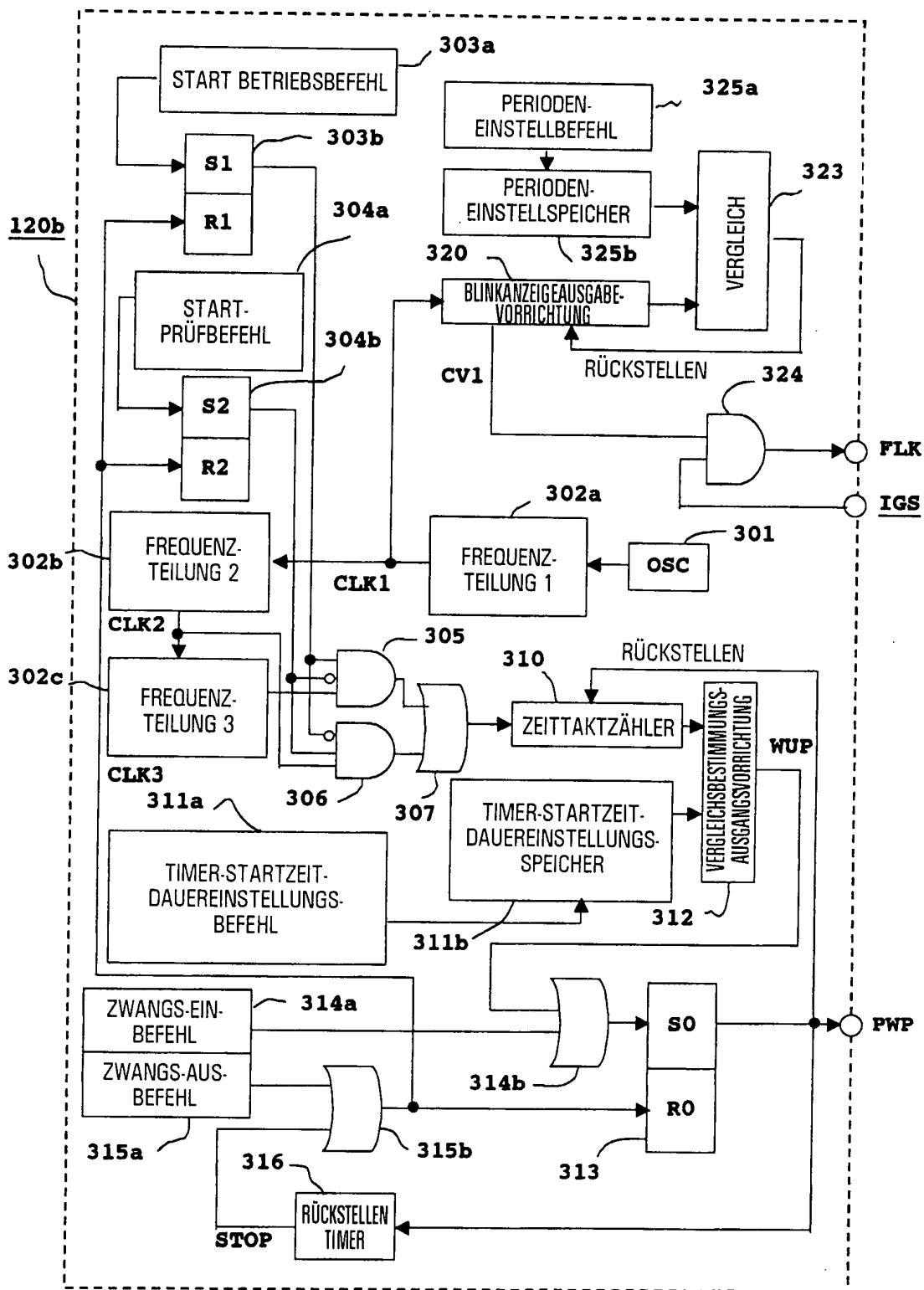

**[0017]** [Fig. 3](#) ein Steuerblockdiagramm eines Timer-Schaltungsabschnittes der [Fig. 1](#);

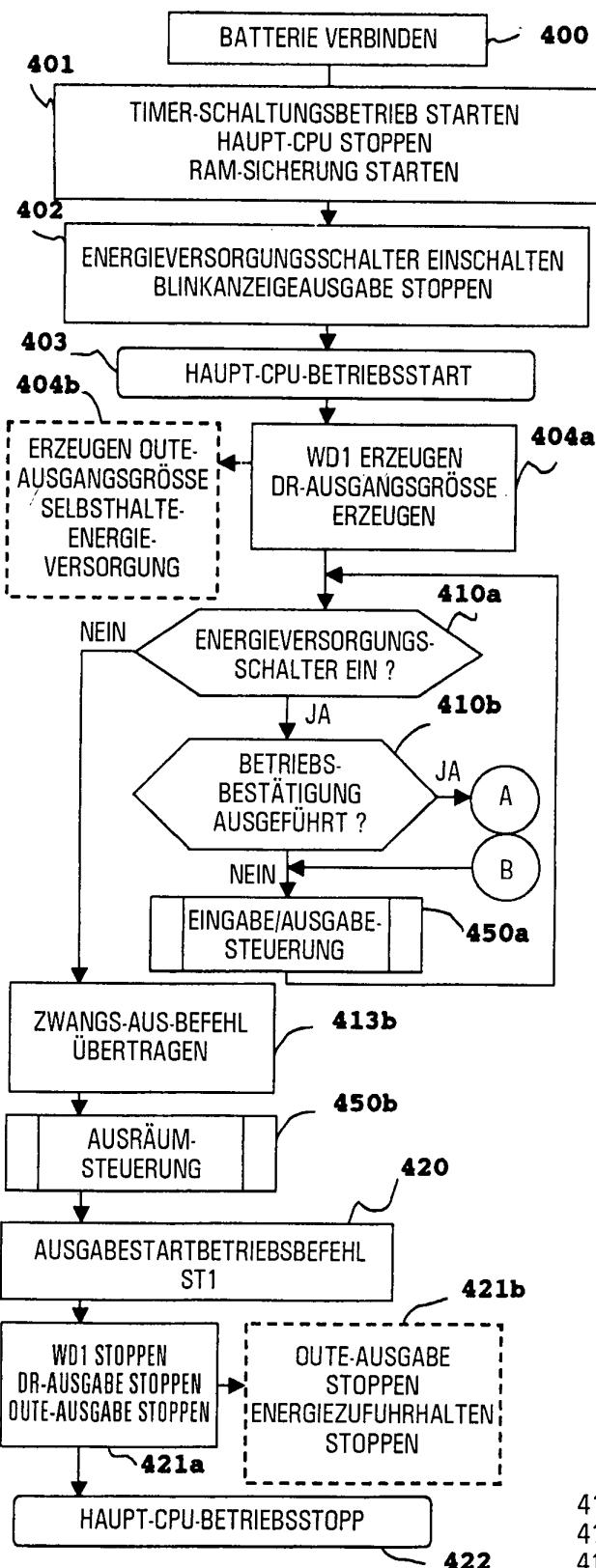

**[0018]** [Fig. 4](#) ein erläuterndes Ablaufdiagramm des ersten Teilarbeitsablaufs der [Fig. 1](#);

**[0019]** [Fig. 5](#) ein erläuterndes Ablaufdiagramm des ersten Teilarbeitsablaufs der [Fig. 1](#);

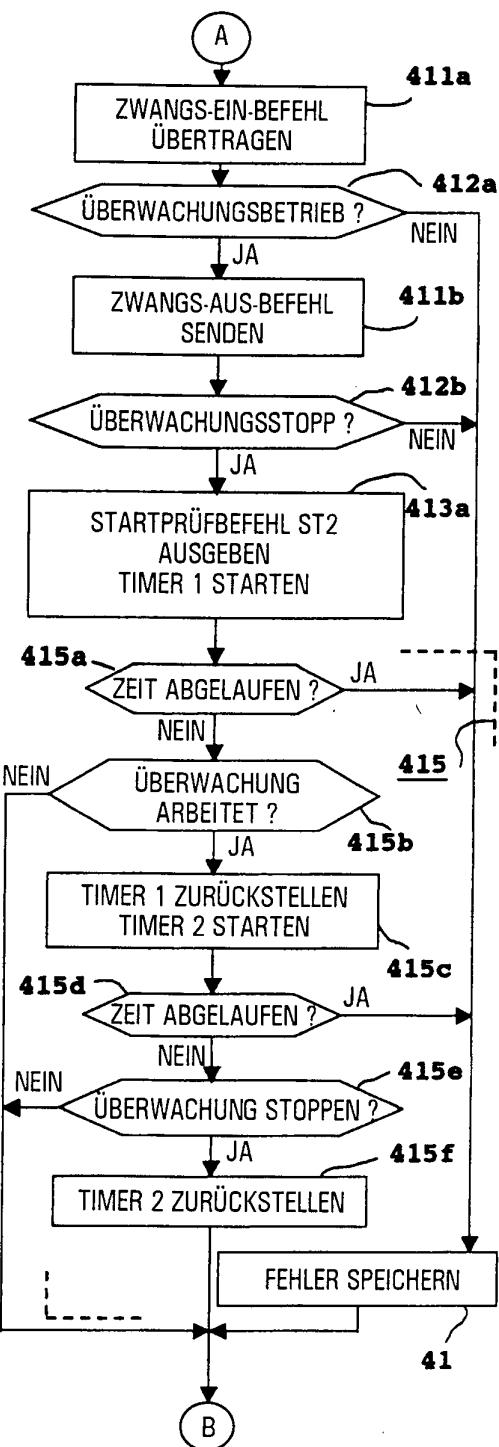

**[0020]** [Fig. 6](#) ein erläuterndes Ablaufdiagramm des zweiten Teilarbeitsablaufs nachfolgend auf [Fig. 4](#) und [Fig. 5](#);

**[0021]** [Fig. 7](#) eine schematische Ansicht der Gesamtzusammensetzung einer zweiten bevorzugten Ausführungsform der Erfindung;

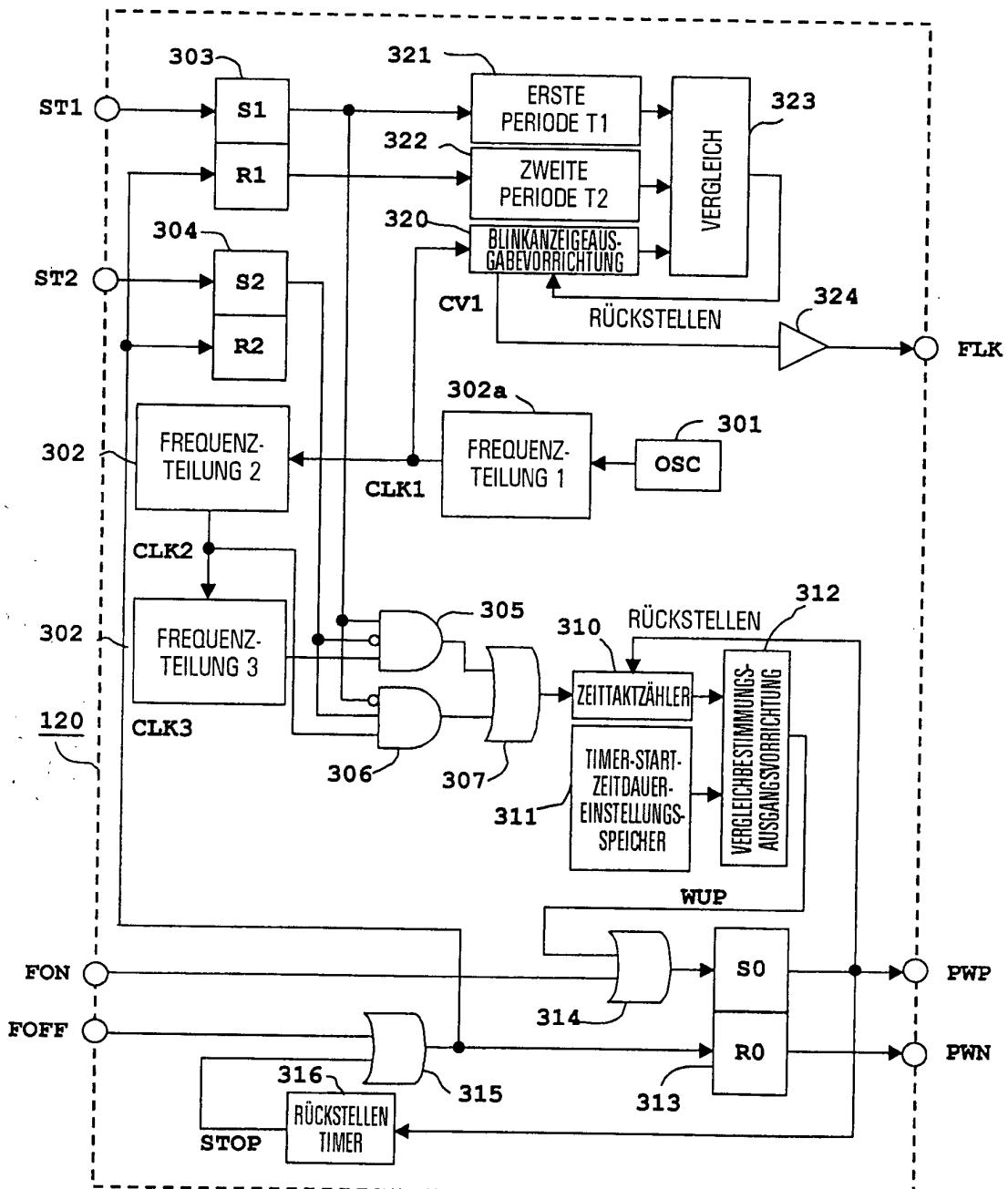

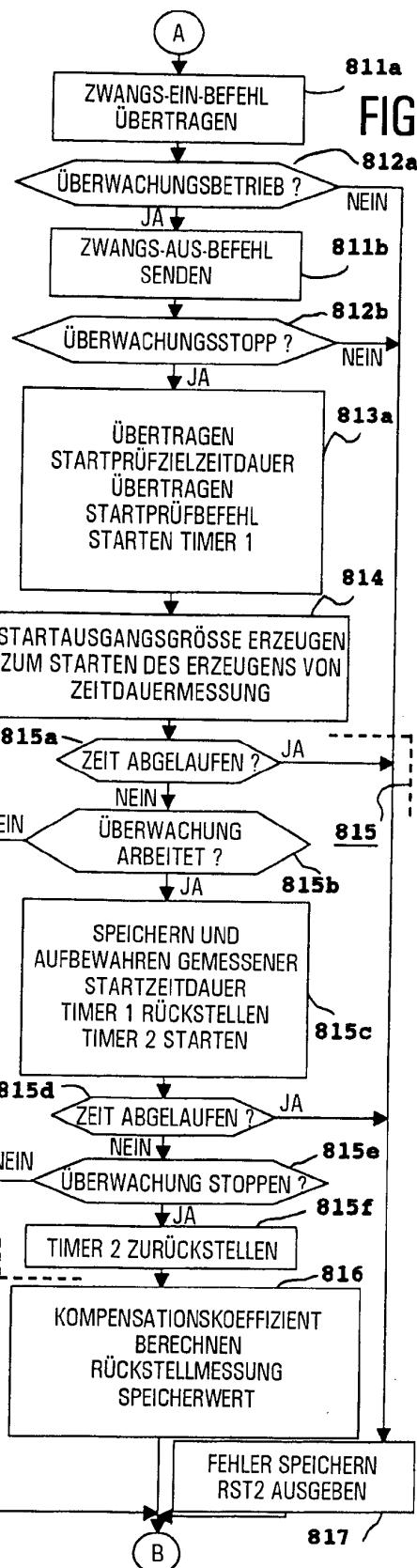

**[0022]** [Fig. 8](#) ein äquivalentes Steuerblockdiagramm eines Timer-Schaltungsabschnittes der [Fig. 7](#);

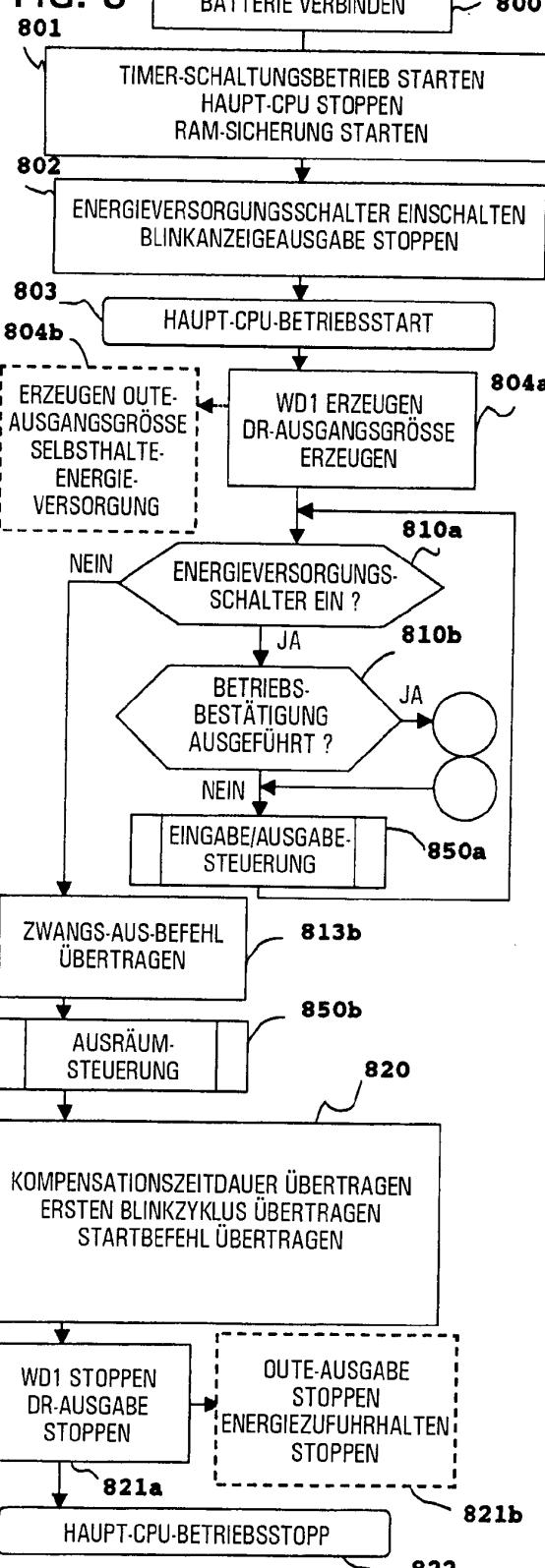

**[0023]** [Fig. 9](#) ein erläuterndes Ablaufdiagramm des ersten Teilarbeitsablaufs der [Fig. 7](#);

**[0024]** [Fig. 10](#) ein erläuterndes Ablaufdiagramm des ersten Teilarbeitsablaufs der [Fig. 7](#);

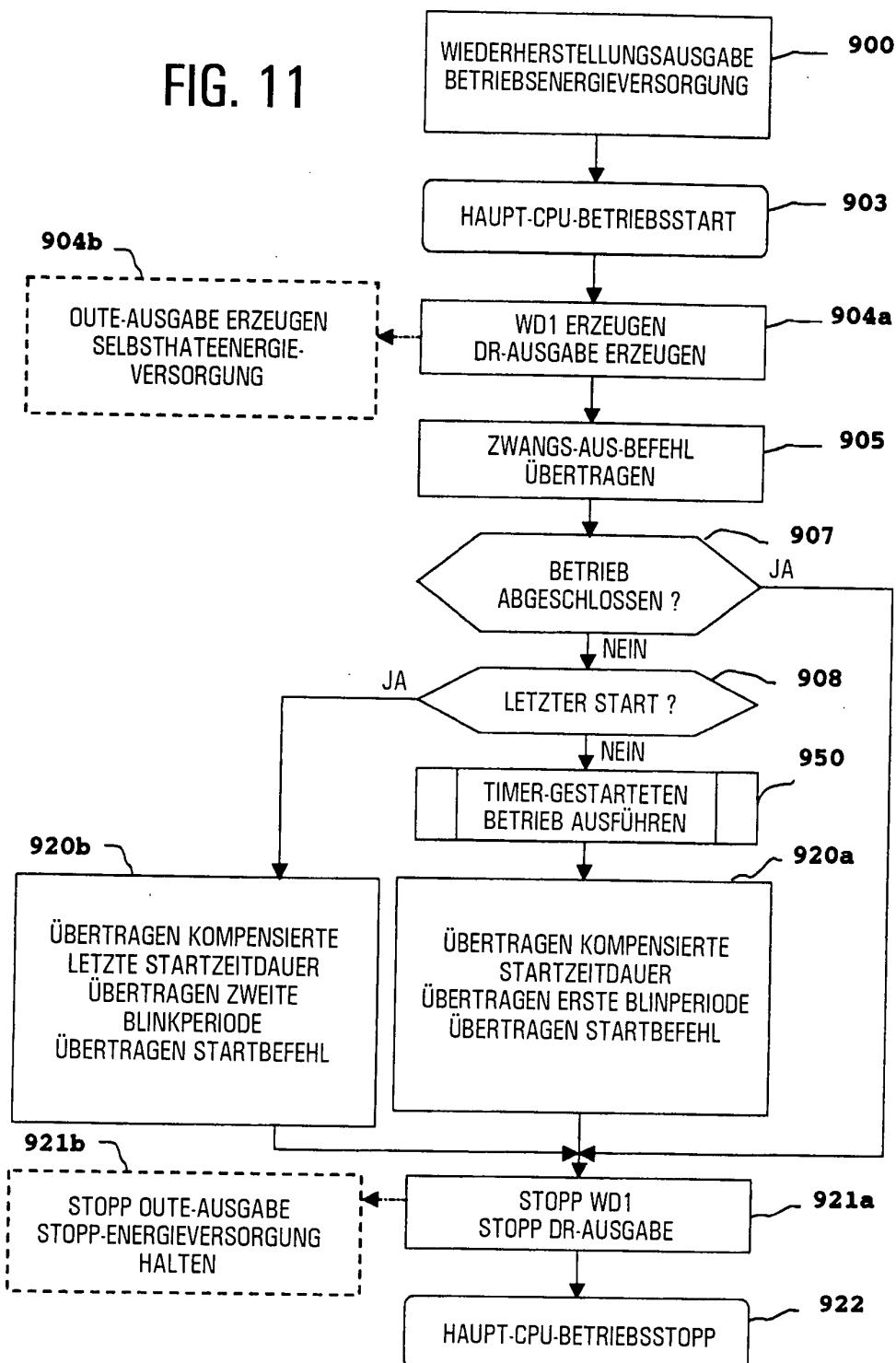

**[0025]** [Fig. 11](#) ein erläuterndes Ablaufdiagramm des zweiten Teilarbeitsablaufs nachfolgend auf [Fig. 9](#) und [Fig. 10](#);

## DETAILLIERTE BESCHREIBUNG DER ERFINDUNG

Ausführungsform 1.

**[0026]** Die den Gesamtaufbau einer ersten bevorzugten Ausführungsform der vorliegenden Erfindung zeigende [Fig. 1](#) wird beschrieben. Unter Bezugnahme auf [Fig. 1](#) setzt sich eine Fahrzeugelektroniksteuereinrichtung **100a** aus einem Hauptsteuerschaltungsabschnitt **110a** und einem Timer-Schaltungsabschnitt **120a** als Hauptkomponenten zusammen. Der Timer-Schaltungsabschnitt **120a** schließt eine Sub-CPU (SCPU) ein, die bei einer niedrigen Geschwindigkeit mit niedrigem Energieverbrauch arbeitet, einen zweiten Programmspeicher, wie zum Beispiel einen ROM-Speicher, einen zweiten RAM-Speicher und einen Seriell-Parallel-Umsetzer.

**[0027]** Erstens gibt es als eine externe Einrichtung, um mit der Fahrzeugelektroniksteuereinrichtung **100a** verbunden zu werden, eine Fahrzeubatterie **101**, einen Energieversorgungsschalter **102**, eine elektromagnetische Spule **103a** eines Energieversorgungsrelais und ein Schaltelement **104a**, das als Ausgangskontakt davon arbeitet, eine Anzeigeeinrichtung oder verschiedene Stromverbraucher **105**, wie zum Beispiel Stellantriebe, verschiedene Eingabesensoren **107** zum Ausführen von EIN-/AUS-Betrieb einschließlich einer Vielzahl von Betriebsschaltern, einen Analogeingabesensor **108** und ein Anzeigeelement (Warnanzeige) **106**, wie zum Beispiel eine lichtemittierende Diode.

**[0028]** Der Hauptsteuerschaltungsabschnitt **110a** schließt eine Haupt-CPU **111a** ein, die ein Mikroprozessor ist, einen ersten Programmspeicher **111b**, wie zum Beispiel einen nichtflüchtigen Flash-Speicher und einen RAM-Speicher **111c** für das Ausführen der Verarbeitung.

**[0029]** Die Haupt-CPU **111a** arbeitet synchron mit einem Referenztaktsignal, das von einem Referenzoszillator **112** unter Verwendung eines Quarzresonators oder eines Keramikresonators übermittelt wird. Eine Hauptenergieversorgungsschaltung **114a** wird mit einer elektrischen Energie von der Fahrzeubatterie **101** über das Schaltelement **104a** versorgt und führt eine stabile Spannung von beispielsweise 5V oder 3,3V Gleichstrom zu dem Hauptsteuerschaltungsabschnitt **110a**. Ferner ist in Bezug auf den Hauptsteuerschaltungsabschnitt **110a** eine Schlummerenergieversorgungsschaltung **114b** vorgesehen, um als Notenergieversorgung für den RAM-Speicher **111c** zu dienen. Obwohl diese Schlummerenergieversorgungsschaltung **114b** unter Umgehung des Schaltelementes **104a** direkt von der Fahrzeubatterie **101** mit Energie versorgt wird, ist deren Energieverbrauch klein. Eine Ausgangs-Schnittstellenschaltung **115** ist zwischen dem Ausgangs-Port DO der Haupt-CPU **111a** und den verschiedenen Stromverbrauchern **105** vorgesehen und bildet eine Schaltung, die einen Ausgangs-Latch bzw. Verrieglungsspeicher einschließt und eine Anzahl von Ausgangstransistoren. Wenn irgend einer der oben erwähnten Ausgangstransistoren in leitenden Zustand versetzt wird, wird einer der mit dem leitenden Transistor verbundenen Stromverbraucher **105** von der Fahrzeubatterie **101** über das Schaltelement **104a** mit elektrischer Energie versorgt und angetrieben.

**[0030]** Eine Eingangs-Schnittstellenschaltung **117** ist zwischen verschiedenen Eingangssensoren **107** und einem Eingangs-Port DI1 der Haupt-CPU **111a** verbunden und bildet eine ein Rauschfilter und einen Datenauswähler einschließende Schaltung. Eine Analogeingangs-Schnittstellenschaltung **118** schließt ein Rauschfilter und einen Mehrkanal-A/D-Umsetzer ein, und ein Digitalumsetzwert einer Vielzahl von

Analogeingangssignalen wird an einen Eingangs-Port DI2 der Haupt-CPU **111a** verbunden. Die Watchdog-Timer-Schaltung **119** überwacht eine Impulsbreite eines Watchdog-Löschsignals WD1, welches eine Impulsfolge ist, die die Haupt-CPU **111a** erzeugt. Wenn diese Impulsbreite kleiner wird als ein vorbestimmter Wert, erzeugt die Watchdog-Timer-Schaltung **119** ein Rückstellimpulssignal RST1 zum Zurückstellen und Neustarten der Haupt-CPU **111a**. Wenn ein Watchdog-Löschsignal WD1 eine normale Impulsfolge ist, verursacht die Watchdog-Timer-Schaltung **119**, dass ein Logikpegel eines Ausgangszulassungssignals OUTE auf hohem Pegel liegt bzw. "H" ist.

**[0031]** Der Timer-Schaltungsabschnitt **120a** wird aus einer bei niedriger Geschwindigkeit mit niedrigem Energieverbrauch arbeitenden Logikschaltung gebildet, wie später detailliert unter Bezugnahme auf [Fig. 3](#) beschrieben. Dieser Timer-Schaltungsabschnitt **120a** arbeitet ansprechend auf einen Startbetriebsbefehl ST1, einen Betriebspüfbefehl ST2, einen Zwangs-EIN-Befehl FON und einen Zwangs-AUS-Befehl FOFF, und erzeugt eine blinkende Anzeigenausgabe FLK oder erste oder zweite Treiberausgänge PWP-PWN. Eine Sub-Energieversorgungsschaltung **124** wird direkt von der Fahrzeubatterie **101** mit Energie versorgt und führt jederzeit eine stabile Spannung, wie zum Beispiel 5V Gleichspannung zu dem Timer-Schaltungsabschnitt **120a**. Ein Transistor **126a** wird von einer Blinkanzeigeausgangsgröße FLK, die der Timer-Schaltungsabschnitt **120a** erzeugt, über einen mit einem Basisanschluss verbundenen Treiberwiderstand **126b** in den leitenden Zustand angetrieben und treibt das Anzeigeelement **106** in blinkender Weise über einen Strombegrenzungswiderstand **126c** an, der mit einem Kollektoranschluss verbunden ist.

**[0032]** Ein Logikelement **127a** erzeugt ein Schließantriebsausgangssignal, das auf einem Logikpegel "H" liegt, nur dann, wenn ein Logikpegel einer ersten Treiberausgangsgröße PWP, die der Timer-Schaltungsabschnitt **120a** erzeugt, "H" ist, und ein Logikpegel einer zweiten Treiberausgangsgröße PWN, die der Treiberschaltungsabschnitt **120a** erzeugt, "L" ist. Dieses Schließ-Treiberausgangssignal wird einem Überwachungseingangsanschluss MNT der Haupt-CPU **111a** zugeführt. Zusätzlich wird auch vorgezogen, dass ein Basiswiderstand einschließender PNP-Transistor als eine Schaltung verwendet wird, die einen äquivalenten Betrieb zu dem des Logikelementes **127a** ausführt, wobei ein Emitter des Transistors mit dem ersten Treiberausgang PWP verbunden ist, ein Basisanschluss mit einem zweiten Treiberausgang PWN verbunden ist und ein Kollektor mit einem Treiberwiderstand **131a** verbunden ist. In dem Fall des Verwendens des einen Basiswiderstand einschließenden PNP-Transistors als eine Schaltung, die einen dem des Logikelementes **127a**

gleichwertigen Betrieb ausführt, wird es eine Stromlogikanordnung. Folglich wird es möglich, die durch den einzelnen Defekt des Logikelementes **127a** bedingte Fehlfunktion und die zur Zeit von Hochimpedanz, wie zum Beispiel, wenn das erste und zweite Treiberausgangssignal PWP·PWN auf einem Logikpegel "X" liegen, zu vermeiden.

**[0033]** Ein Transistor **130** ist mit einem Ende der elektromagnetischen Spule **103a** des Energieversorgungsrelais verbunden, dessen anderes Ende mit einem positivseitigen Anschluss der Fahrzeughartie **101** verbunden ist und über eine Serienschaltung eines Treiberwiderstandes **132a** und einer Diode **132b** in den leitenden Zustand angetrieben wird, wenn ein Energieversorgungsschalter **102** in einen geschlossenen Zustand gebracht wird, um die elektromagnetische Spule **103a** zu erregen und das Schaltelement **104a** zu veranlassen, als ein im leitfähigen Zustand befindlicher Ausgangskontakt zu arbeiten. Ferner wird der Transistor **130** über eine Serienschaltung eines Treiberwiderstandes **133a** und einer Diode **133b** leitend angetrieben mit dem Ausgangszulassungssignal OUTE, das eine Watchdog-Timer-Schaltung **119** gemeinsam mit der Tatsache erzeugt, dass das Schaltelement **104a** leitfähig wird und die Haupt-CPU **111a** den Betrieb startet. Sobald die Haupt-CPU **111a** den Betrieb gestartet hat, führt das Schaltelement **104a** eine Selbsthalteoperation aus, selbst wenn der Energieversorgungsschaltung **102** in einem offenen Zustand ist.

**[0034]** Ein Schnittstellenelement **134** ist verbunden, um ein invertierendes Logiksignal IGS in die Haupt-CPU **111a** ansprechend auf einen Schaltbetrieb des Energieversorgungsschalters **102** einzugeben. Die Haupt-CPU **111a** führt beispielsweise eine Evakuier- bzw. Ausräum-Verarbeitung der Speicherinformation oder eine Initialisierungsverarbeitung aus und stoppt dann das Erzeugen eines Watchdog-Löschsignals WD1, wenn sie erfasst, dass der Energieversorgungsschalter **102** in einen offenen Zustand gebracht worden ist. Als ein Ergebnis wird ein Logikpegel des Ausgangszulassungssignals OUTE der Watchdog-Timer-Schaltung **119** "L" und der Transistor **130** wird nicht-leitend, was zu einer Unterbrechung des Schaltelementes **104a** führt. Ferner ist es auch vorzuziehen, dass ein Selbsthaltetreibersignal DR von der Haupt-CPU **111a** erzeugt wird statt des Ausgangszulassungssignals OUTE, das von einer Watchdog-Timer-Schaltung **119** gesendet wird. Der Transistor **130** wird ferner über eine Serienschaltung eines Treiberwiderstandes **131a** und einer Diode **131b** von einem Ausgang des Logikelementes **127a** in den leitfähigen Zustand angetrieben. Wenn die Timer-Schaltung **102a** die erste Treiberausgangsgröße PWP mit dem Logikpegel "H" erzeugt, und die zweite Treiberausgangsgröße PWN mit dem Logikpegel "L", wird der Transistor **130a** in leitfähigen Zustand gebracht, das Schaltelement **104a** wird in einen ge-

schlossenen Zustand gebracht und die Haupt-CPU **111a** startet den Betrieb.

**[0035]** Wenn der Betrieb der Haupt-CPU **111a** von dem Timer-Schaltungsabschnitt gestartet worden ist, wird das Erzeugen der ersten Treiberausgangsgröße PWP und der zweiten Treiberausgangsgröße PWN, die eine Schließ-Treiberausgangsgröße von dem Timer-Schaltungsabschnitt **120a** sind, gestoppt. Statt dieser Schließ-Treiberausgangsgrößen wird der Betrieb des Energieversorgungsrelais mit dem Ausgangszulassungssignal OUTE aufrecht erhalten, das aktiv wird, wenn ein Erzeugungszyklus eines Watchdog-Löschsignals, das die Haupt-CPU **111a** erzeugt, nicht mehr ist als eine vorbestimmte Zeitdauer, oder mit dem Selbsthaltetreibersignal DR, das die Haupt-CPU **111a** erzeugt.

**[0036]** Es ist auch wünschenswert, dass eine Schließ-Treiberausgangsgröße fortgesetzt erzeugt wird, selbst nach dem Hochfahren der Haupt-CPU **111a** mit Hilfe des Timer-Schaltungsabschnittes, und die Ausgabe einer Schließ-Timer-Ausgangsgröße durch die Haupt-CPU **111a** gemeinsam mit dem Ende des durch den Timer gestarteten Betriebs gestoppt wird.

**[0037]** Es wird Bezug genommen auf **Fig. 2**, ein Betriebszeitdiagramm der Energieversorgungsschaltung der **Fig. 1**; auf das Auftreten eines in **Fig. 2a** gezeigten geschlossenen Schaltungszustandes des Energieversorgungsschalters **102** (bei einem Logikpegel "H"), wird das in **Fig. 2(b)** gezeigte Schaltelement **104a** in einen geschlossenen Schaltungszustand gebracht (bei einem Logikpegel "H"), und die Haupt-CPU **111a** startet den Betrieb, wie in **Fig. 2(b)** gezeigt. Als ein Ergebnis wird ein Watchdog-Löschsignal WD1, das eine von der Haupt-CPU **111a** erzeugte Impulsfolge ist, erzeugt. Die Watchdog-Timer-Schaltung **119** erzeugt das in **Fig. 2(d)** gezeigte Ausgangszulassungssignal OUTE. Während der Zeitdauer, wenn die Haupt-CPU **111a** mit einer elektrischen Energie gespeist wird, wird eine Blinkanzeigeausgabe FLK gestoppt, wie in **Fig. 2(e)** gezeigt.

**[0038]** Ansprechend auf einen offenen Schaltzustand des Energieversorgungsschalters **102** stoppt die Haupt-CPU **111a** den Betrieb, und ein Watchdog-Löschsignal WD1 wird gestoppt, nachdem eine Evakuierungs- bzw. Ausräumbetriebszeitdauer Ta verstrichen ist, wodurch das Erzeugen des Ausgangszulassungssignals OUTE ebenfalls gestoppt wird, das Schaltelement **104a** wird in einen offenen Schaltungszustand gebracht und die Energiezufuhr zu der Haupt-CPU **111a** wird unterbrochen. Jedoch wird der Timer-Schaltungsabschnitt **120a** ständig von der Sub-Energieversorgungsschaltung **124** mit Energie versorgt, um den Betrieb fortzusetzen, und eine Blinkanzeigeausgabe FLK erzeugt eine EIN/AUS-Ausgangsgröße mit einem Befehl der

Haupt-CPU **111a**. Zusätzlich werden während einer Evakuierungsbetriebszeitdauer  $T_a$  eine Vielzahl von Evakuierungsverarbeitungen, die von einer Fahrzeugelektroniksteuereinrichtung zum Dienen benötigt werden, wie zum Beispiel das Speichern in einem nicht-dargestellten nicht-flüchtigen Datenspeicher von verschiedenen Lerninformationen, Fehlerhistorieninformationen oder ähnlichem, die in dem ersten RAM-Speicher **111c** gespeichert worden sind, in Übereinstimmung mit Inhalten des ersten Programmspeichers **111b** ausgeführt. Ferner wird das nächste Startbetriebsbefehlssignal  $ST_1$  dem Timer-Schaltungsabschnitt **120a** zugeführt. Zudem ist es auch vorzuziehen, dass die Haupt-CPU **111a** erfasst, dass das Drehen eines Motors gestoppt wird und die Haupt-CPU **111a** führt dem Timer-Schaltungsabschnitt **120a** ein Startbetriebsbefehlssignal  $ST_1$  zu.

**[0039]** Dann, wie in **Fig. 2(f)** gezeigt, wird, wenn der Timerschaltungsabschnitt **120a** die positiven und negativen Schließ-Treiber-Ausgangsgrößen PWP-PWN erzeugt, ein Ausgangslogikpegel des Logikelements **127a** "H", und der Transistor **130** wird in den leitenden Zustand versetzt, was zu einem Schließen des Schaltelementes **104a** führt. Als Ergebnis wird die Haupt-CPU **111a** durch den Timerschaltungsabschnitt gestartet und erzeugt das Ausgangs-Zulassungssignal OUTE zum Aufrechterhalten des leitenden Zustandes über den Transistor **130**. Ferner wird eine Schließ-Treiber-Ausgangsgröße mit einem Befehl von der Haupt-CPU **111a** gestoppt. Wenn der durch den Timer gestartete Betriebsablauf während einer Zeitdauer  $T_d$  beendet worden ist, wird der Betrieb der Haupt-CPU **111a** gestoppt und das Ausgangs-Zulassungssignal OUTE wird gestoppt, was zu einer Unterbrechung des Schaltelementes **104a** führt. In dem Fall, in dem die Haupt-CPU **111a** den nächsten Startbetriebsbefehl  $ST_1$  während der Zeitdauer  $T_d$  des durch den Timer gestarteten Betriebsablaufs erzeugt, wird derselbe Betriebsablauf im Zeitverlauf ausgeführt. Jedoch, in dem Fall, in dem der nächste Start-Betriebsbefehl nicht ausgegeben wird, wird der Timer den Betrieb nicht wieder starten.

**[0040]** Unter Bezugnahme auf **Fig. 3**, die ein Steuerblockdiagramm des Timerschaltungsabschnittes **120a** der **Fig. 1** ist, wird ein Taktsignal, das eine Zeitabstimmungs-Taktsignalerzeugungsschaltung **301** erzeugt, frequenzaufgeteilt in einer ersten Teilerschaltung **302a** zum Erzeugen eines ersten Taktsignals CLK1 mit einer Periode von z.B. 0,1 Sekunden. Das Taktsignal wird ferner frequenzaufgeteilt in einer zweiten Teilerschaltung **302b** zum Erzeugen eines zweiten Taktsignals CLK2 mit einer Periode von z.B. 1 Sekunde. Das Taktsignal wird ferner frequenzaufgeteilt in einer dritten Teilerschaltung **302c** zum Erzeugen eines dritten Taktsignals CLK3 mit einer Periode von z.B. 1 Minute. Eine Timerstart-Befehlsspeicherschaltung **303** besteht beispielsweise aus einem Flip-Flop mit einem Einstelleingang S1 und einem

Rückstelleingang R1 und speichert das Erzeugen eines von der Haupt-CPU **111a** übertragenen Startbetriebsbefehls  $ST_1$ .

**[0041]** Eine Betriebsprüfbefehls-Speicherschaltung **304** besteht beispielsweise aus einem einen Einstelleingang S2 und einen Rückstelleingang R2 einschließenden Flip-Flop und speichert das Erzeugen eines von der Haupt-CPU **111a** erzeugten Betriebsprüfbefehls  $ST_2$ . Ein UND-Element **305** erzeugt eine UND-Ausgangsgröße von logisch invertierenden Ausgangsgrößen eines Speicherausgangs von der Timerstartbefehls-Speicherschaltung **303** und eines Speicherausgangs von der Betriebsprüfbefehls-Speicherschaltung **304** und eines dritten Taktsignals CLK3. Ferner erzeugt ein UND-Element **306** eine UND-Ausgangsgröße von logisch invertierenden Ausgangsgrößen eines Speicherausgangs von der Betriebsprüfbefehls-Speicherschaltung **304** und eines Speicherausgangs von der Timerstartbefehls-Speicherschaltung **303** und eines zweiten Taktsignals CLK2. Die Ausgänge der UND-Elemente **305** und **306** werden zu einem Eingang eines ODER-Elementes **307** verbunden.

**[0042]** Ein Taktablaufzähler **310** ist zum Zählen eines Ausgangssignals von einem ODER-Element **307** eingerichtet. Dieser Taktablaufzähler **310** führt das Zählen bei einer niedrigen Geschwindigkeit mit einem dritten Taktsignal CLK3 aus, während eine Speicherausgangsgröße von der Timerstartbefehls-Speicherschaltung **303** erzeugt wird; und führt das Zählen bei einer hohen Geschwindigkeit mit einem zweiten Taktsignal CLK2 aus, während eine Speicherausgangsgröße von der Betriebsprüfungsbefehls-Speicherschaltung **304** erzeugt wird.

**[0043]** Eine Konstante, die einem Wert entspricht durch Teilen einer Einstellzeitdauer von der Haupt-CPU durch eine Periodenzeit eines dritten Taktsignals CLK3 erhalten wird, wird in einem Timerstartzeitdauer-Einstellspeicher **311** gespeichert. Eine Vergleichsbestimmungsausgabevorrichtung **312** vergleicht einen momentanen Wert des Zeittaktzählers **310** mit einer Konstanten, die im Timerstartzeitdauer-Einstellspeicher **311** gespeichert ist, und erzeugt ein Weck-Ausgangssignal WUP, wenn beide koinzident sind. Eine Ausgangslogik-Verarbeitungsvorrichtung **313** ist aus einem Flip-Flop aufgebaut, das einen Setz- bzw. Einstelleingang SO und einen Rücksetz- bzw. Rückstelleingang RO hat. Der Einstellausgangswert ist eine erste Ausgangsgröße PWP und der Rückstellausgangswert ist eine zweite Ausgangsgröße PWN.

**[0044]** Ein ODER-Element **314** setzt die Ausgangslogik-Verarbeitungsvorrichtung **313** mit einem ODER-Ausgang eines Weck-Ausgangssignals WUP, das die Vergleichsbestimmungs-Ausgabevorrichtung **312** erzeugt, und einem Zwangs-EIN-Befehl FON,

den die Haupt-CPU **111a** erzeugt. Der Zeittaktzähler **310** wird mit einer Einstellausgangsgröße von der Ausgangslogik-Verarbeitungsvorrichtung **313** zurückgestellt. Ein ODER-Element **315** stellt die Ausgangslogik-Verarbeitungsvorrichtung **313** mit einer ODER-Ausgangsgröße eines Stopsignals zurück, das der zuletzt beschriebene Rückstell-Timer **316** erzeugt, und einem Zwangs-AUS-Befehl FOFF, den die Haupt-CPU **111a** erzeugt; und stellt die Timerstartbefehls-Speicherschaltung **303** zurück und die Betriebsprüfungsbefehls-Speicherschaltung **304**.

**[0045]** Ein Rückstell-Timer **316** startet einen Zeittakt gemeinsam mit dem Erzeugen eines Setzsignals von der Ausgangslogikverarbeitungsvorrichtung **313** und erzeugt ein Stoppsignal STOP nachdem eine vorbestimmte Grenzzeitdauer verstrichen ist zum Zurückstellen der Ausgangslogikverarbeitungsvorrichtung **313**, der Timerstartbefehls-Speicherschaltung **303** und der Betriebsprüfungsbefehls-Speicherschaltung **304**.

**[0046]** Eine Blinkanzeigeausgabevorrichtung **320** besteht aus einem Zähler zum Zählen eines Erzeugungsimpulses eines ersten Taktsignals CLK 1. Eine erste Periodenzeit T1 wird in einem ersten Speicher **321** gespeichert, und dieser erste Speicher **321** wird ausgewählt und verwendet, wenn die Timerstartbefehls-Speicherschaltung **303** eine Einstell-Ausgangsgröße erzeugt. Eine zweite Periodenzeit T2 (> T1) wird in einem zweiten Speicher **322** gespeichert. Dieser zweite Speicher **322** wird ausgewählt und verwendet, wenn die Timerstartbefehls-Speicherschaltung **303** eine Rückstallausgangsgröße erzeugt. Eine Vergleichsschaltung **323** vergleicht einen momentanen Wert des als Blinkanzeige-Ausgabevorrichtung **320** arbeitenden Zählers mit einer ersten Periodenzeit T1 oder einer zweiten Periodenzeit T2 und setzt als ein Ergebnis des Vergleichs einen momentanen Wert des als Blinkanzeigeausgabevorrichtung **320** arbeitenden Zählers auf Null, jedes Mal, wenn sie ko-inzident sind. Ein Gatterelement **324** besteht aus einem UND-Element, von welchem die Eingangsgrößen eine Momentanwert-Ausgangsgröße CV1 sind, die auf einem Logikpegel "H" liegt, wenn ein momentaner Wert des als Blinkanzeigeausgabevorrichtung dienenden Zählers **1** ist, und ein Invertierlogiksignal IGS (s. [Fig. 1](#)), das auf einem Logikpegel "L" liegt, wenn der Energieversorgungsschalter **102** in einen geschlossenen Zustand gebracht wird. Eine UND-Ausgangsgröße davon ist eine Blinkanzeigeausgangsgröße FLK.

**[0047]** Zudem ist eine Periodenzeit eines ersten Taktsignals CLK1 beispielsweise 0,1 Sekunden; während eine erste, in dem ersten Speicher **321** zu speichernde Periodenzeit T1 beispielsweise 20 entsprechend 2 Sekunden ist und eine zweite, in dem zweiten Speicher **322** zu speichernde Periodenzeit T2 beispielsweise 30 entsprechend 3 Sekunden ist.

In diesem Fall, wenn die Timerstartbefehls-Speicherschaltung **303** eingestellt wird, um in dem Wartezustand zu sein für das Hochfahren durch den Timerschaltungsabschnitt, wiederholt eine Blinkanzeigeausgabe FLK den EIN-Betriebszustand für 0,1 Sekunde und den AUS-Betriebszustand für 1,9 Sekunden. Wenn jedoch die Timerstartbefehls-Speicherschaltung **303** nicht zurückgesetzt wird, wiederholt eine Blinkanzeigeausgabe FLK den EIN-Betrieb für 0,1 Sekunde und den AUS-Betrieb für 2,9 Sekunden. Trotzdem wird, wenn der Energieversorgungsschalter **102** sich in einem geschlossenen Zustand befindet, eine Blinkanzeigeausgabe FLK durch die Aktion eines bei einem Logikpegel "L" festzulegenden Gatterelementes **324** gestoppt.

**[0048]** Unter Bezugnahme auf [Fig. 4](#) und [Fig. 5](#), die Ablaufdiagramme zum Erläutern des ersten Teilbetriebs der Haupt-CPU **111a** der [Fig. 1](#) sind, wenn die Fahrzeugelektroniksteuereinrichtung **100a** mit der Fahrzeuggatterelemente **101** in Schritt **400** verbunden wird, startet im darauffolgenden Schritt **401** der Timerschaltungsabschnitt **120a** den Betrieb, und eine Blinkanzeigeausgabe FLK einer zweiten Periodenzeit T2 wird erzeugt. Ferner kommt der Hauptsteuerschaltungsabschnitt **110a** in einen Zustand, dass er imstande ist, die Speicherung des ersten RAM-Speichers **111c** mit Hilfe einer Schlummerenergie-Versorgungsschaltung **114b** zu erhalten. Jedoch befindet sich die Haupt-CPU noch im Stoppzustand. Dann, wenn der Energieversorgungsschalter **102** im Schritt **402** eingeschaltet wird, wird die Blinkanzeigeausgabe FLK durch die Aktion des Gatterelementes **324** der [Fig. 3](#) gestoppt. Jedoch wird der Transistor **130** der [Fig. 1](#) in den leitfähigen Zustand gebracht, die elektromagnetische Spule **103a** wird erregt, der Ausgangskontakt **104a** wird geschlossen und die Energiezufuhr zu dem Hauptsteuerschaltungsabschnitt **110a** wird gestartet. Im nachfolgenden Schritt **403** startet die Haupt-CPU **111a** den Betrieb.

**[0049]** Schritt **404a** wird nachfolgend auf Schritt **403** betrieben und erzeugt ein Watchdog-Löschesignal WD1 oder ein Selbsthalte-Treibersignal DR. Einhergehend mit dem Erzeugen eines Watchdog-Löschesignals WD1, wie im Block **404b** gezeigt, erzeugt die Watchdog-Timerschaltung **119** ein Ausgangszulassungssignal OUTE, und die Leitung durch den Transistor **130** wird aufrechterhalten. Entsprechend wird das Erregtsein der elektromagnetischen Spule **103a** beibehalten, selbst wenn der Energieversorgungsschalter **102** geöffnet wird.

**[0050]** Im Schritt **410a**, der nach Schritt **404a** betrieben wird, wird bestimmt, ob der Energieversorgungsschalter **102** fortgesetzt im geschlossenen Zustand bleibt durch Überwachen eines invertierenden Logiksignals IGS. In dem Fall, in welchem der Energieversorgungsschalter **102** im geschlossenen Zustand ist, geht das Programm weiter zu Schritt **410b**. In dem

Fall, in dem der Energieversorgungsschalter **102** im geöffneten Zustand ist, geht das Programm weiter zu Schritt **413b**. Im Schritt **410b** wird bestimmt, ob ein Betriebsbestätigungstest des Timerschaltungsabschnittes **120b** ausgeführt wird. Wird der Betriebsbestätigungstest ausgeführt, geht das Programm zu Schritt **411a** weiter. Wenn der Betriebsbestätigungstest nicht ausgeführt wird, geht das Programm weiter zu Schritte-Block **450a**.

**[0051]** Zudem wird das Bestimmen in Schritt **410b** im wesentlichen in regelmäßigen Intervallen während einer Periode ausgeführt, wenn eine Motorgeschwindigkeit niedrig ist und die Haupt-CPU **111a** einen Reaktionsspielraum hat, unter der Annahme, dass die Fahrzeugelektroniksteuereinrichtung **100a** eine Motorsteuereinrichtung ist.

**[0052]** Im Schritt **411a** wird ein Zwangs-EIN-Befehl FON erzeugt. In dem darauffolgenden Schritt **412a** wird ein Überwachungseingangsanschluss MNT überwacht, hierdurch bestimend, ob erste und zweite Treiberausgänge normal arbeiten. In dem Fall irgendeines Betriebsfehlers geht das Programm weiter zu Schritt **41**. In dem Fall des Normalbetriebs geht das Programm weiter zu Schritt **411b**.

**[0053]** Im Schritt **411b** wird ein Zwangs-AUS-Befehl FOFF erzeugt. Im nachfolgenden Schritt **412b** wird ein Überwachungseingangsanschluss MNT überwacht, hierdurch bestimend, ob oder nicht erste und zweite Treiberausgänge PWP-PWN den Betrieb normal gestoppt haben. In dem Fall eines Stopp-Fehlers geht das Programm zu Schritt **41**. In dem Fall eines normalen Stoppons geht das Programm zu Schritt **413a**.

**[0054]** Zusätzlich ist der Betrieb des Timerschaltungsabschnittes **120a** ansprechend auf den Zwangs-EIN-Befehl FON oder den Zwangs-AUS-Befehl FOFF wie in [Fig. 3](#) gezeigt. Bei dem Weckbetrieb ist ein erster Treiberausgang PWP auf einem Logikpegel "H", und ein zweiter Treiberausgang PWN ist auf einem Logikpegel "L", wodurch ein Logikpegel eines von dem Logikelement **127a** der [Fig. 1](#) ausgegebenen Überwachungseingangssignals "H" wird.

**[0055]** Im Schritt **413a** wird ein Betriebsüberwachungsbefehl ST2 erzeugt; und ein Timer 1, dessen Zeit in einer Zeitspanne abläuft, die länger ist als eine Betriebsüberwachungszeitdauer, wird gestartet. In dem nachfolgenden Schritt **415a** wird bestimmt, ob die Zeit des Timers 1 abgelaufen ist oder nicht. In dem Fall, in dem die Zeit des Timers 1 abgelaufen ist, geht das Programm zu Schritt **41**. In dem Fall, in dem die Zeit des Timers 1 nicht abgelaufen ist, geht das Programm zu Schritt **415b**.

**[0056]** Im Schritt **415b** wird ein Überwachungseingangsanschluss MNT überwacht, hierdurch bestim-

mend, ob die ersten und zweiten Treiberausgänge PWP-PWN erzeugt worden sind oder nicht. In dem Fall, in dem diese ersten und zweiten Treiberausgangsgrößen PWP-PWN noch nicht erzeugt worden sind, durchläuft das Programm den Schritte-Block **450a** und kehrt zurück zu Schritt **415a**. In dem Fall, in dem ein Aufweck-Ausgangssignal erzeugt wird, geht das Programm zu Schritt **415c**.

**[0057]** Zusätzlich, einhergehend mit dem Erzeugen eines Betriebsprüfbefehls ST2, zählt der in [Fig. 3](#) gezeigte Zeittaktzähler **310** die Anzahl zweiter Taktsignale CLK2, hierdurch mit einer hohen Geschwindigkeit arbeitend, und erreicht eine Zeitspanne, die von der Haupt-CPU festgelegt worden ist in einer kurzen Zeitspanne zum Erzeugen eines Ausgangssignals WUP.

**[0058]** Im Schritt **415c** wird der im Schritt **413a** gestartete Timer 1 zurückgesetzt; und ein Timer 2, dessen Zeitablauf in einer Zeitspanne liegt, die länger ist als eine eingestellte Zeitspanne des Rückstelltimers der [Fig. 2](#) wird gestartet. Im Schritt **415d** wird bestimmt, ob die Zeit des Timers 2 abgelaufen ist oder nicht. In dem Fall, dass die Zeit abgelaufen ist, geht das Programm zu Schritt **41**. In dem Fall, dass kein Zeitablauf vorliegt, geht das Programm zu Schritt **415e**. Im Schritt **415e** wird ein Überwachungseingangsanschluss MNT überwacht und es wird bestimmt, ob erste und zweite Treiberausgangsgröße PWP-PWN gestoppt sind oder nicht. In dem Fall, in dem dieser ersten und zweiten Treiberausgangsgrößen PWP-PWN nicht gestoppt worden sind, durchläuft das Programm den Schritte-Block **450a** und kehrt zurück zum Schritt **415d**. In dem Fall, in dem eine Schließ-Treiber-Ausgangsgröße gestoppt wird, geht das Programm zu Schritt **415f**. Im Schritt **415f** wird der im Schritt **415c** gestartete Timer 2 zurückgesetzt und daraufhin geht das Programm zu dem Schritte-Block **450a**.

**[0059]** Zusätzlich arbeitet der aus den Schritten **415a** bis Schritt **415f** bestehende Schritte-Block **415** als Betriebsprüfüberwachungsvorrichtung.

**[0060]** Im Schritt **41** wird eine Fehlerinformation, wie ein im Schritt **412a** bestimmter Zwangs-EIN-Betriebsdefekt, ein im Schritt **412b** bestimmter Zwangs-AUS-Stoppdefekt, ein im Schritt **415a** bestimmter Zeitspannoverschreitungsdefekt und ein im Schritt **415d** bestimmter Selbstrückstell-Zeitspannaverschreitungsdefekt in dem ersten RAM-Speicher **11c** gespeichert und gesichert; und der Fehler wird mit einer nicht dargestellten Anzeigeeinrichtung bekannt gemacht. Der Schritte-Block **450a** wird abgearbeitet, wenn das Bestimmen des Schrittes **415b** oder Schrittes **425e** NEIN ist oder im Anschluss an Schritt **425f** oder Schritt **41**, und steuert verschiedene Stromverbraucher **105** ansprechend auf den Zustand einer Vielzahl von Eingangssensoren **107** und Ana-

log-Eingangssensoren **108**. Jedoch kehrt in dem Prozess dieser Eingabe-/Ausgabe-Steuerung das Programm in regelmäßigen Intervallen zu Schritt **410a** zurück zum Überwachen, ob der Energieversorgungsschalter **102** offen ist oder nicht.

**[0061]** Schritt **413b** arbeitet, wenn der Energieversorgungsschalter **102** im Schritt **410** als in einem offenen Zustand befindlich bestimmt wird, und erzeugt einen Zwangs-AUS-Befehl FOFF. In dem Fall, in dem der Energieversorgungsschalter **102** im Zuge der Betriebsprüfung mit Hilfe des Schrittes **413a** in einen offenen Zustand gebracht wird, wird die Betriebsprüfung gestoppt. Im Schritt **450b**, der nach Schritt **413a** betrieben wird, wird eine Räumungsverarbeitung, wie Ursprungsrückkehr, betrieben von nicht dargestellten Stellantrieben oder Sichern und Ausräumen gelerner und gespeicherter Information ausgeführt. In den nachfolgenden Schritten **420** wird ein Startbetriebsbefehl ST1 erzeugt. Schritt **421a** arbeitet nachfolgend auf Schritt **420** und stoppt das Erzeugen des Selbsthalte-Antriebssignals DR oder eines Watchdog-Löschsignals WD1, und daraufhin geht das Programm zu einem Betriebsendeschritt **422**. Ferner, wenn ein Watchdog-Löschsignal WD1 im Schritt **421a** gestoppt wird, stoppt die Watchdog-Timerschaltung **119** das Ausgangszulassungssignal OUTE, wie in Block **421b** gezeigt, der Transistor wird in einen nichtleitenden Zustand gebracht und der Ausgangskontakt **104a** wird geöffnet.

**[0062]** Unter Bezugnahme auf [Fig. 6](#), die ein erläuterndes Ablaufdiagramm des zweiten Betriebsablaufs der Haupt-CPU **111a** in [Fig. 1](#) ist, führt im Schritt **500** einhergehend mit dem Erzeugen eines Startbetriebsbefehls ST1 im erwähnten Schritt **420** der Zeitztähler **310** der [Fig. 3](#) die Zähloperation eines dritten Taktsignals CLK 3 aus. Im Laufe der Zeit wird ein Logikpegel des ersten Treiberausgangs PWP "H", und ein Logikpegel des zweiten Treiberausgangs PWN wird "L", und eine Ausgangsgröße des Logikelementes **127a** in [Fig. 1](#) kommt auf einen Logikpegel "H", wodurch der Transistor **130** leitend wird, der Ausgangskontakt **104a** in einen geschlossenen Zustand gebracht wird und die Energiezufluhr zu dem Hauptsteuerschaltungsabschnitt **110a** wiederhergestellt wird. Als ein Ergebnis startet im Schritt **503** der Betrieb der Haupt-CPU **111a**. Im nachfolgenden Schritt **504a** werden ein Watchdog-Löschsignal WD1 oder ein Selbsthalte-Antriebssignal DR erzeugt. Jedoch erzeugt gemeinsam mit dem Erzeugen eines Watchdog-Löschsignals WD1, wie in Block **504b** gezeigt, die Watchdog-Timerschaltung **119** das Ausgangszulassungssignal OUTE und hält die Leitung durch den Transistor **130** aufrecht. Entsprechend wird die Erregung der elektromagnetischen Spule **103a** ausgeführt, selbst wenn eine Schließ-Treiber-Ausgangsgröße gestoppt wird.

**[0063]** Im Schritt **505**, der nach Schritt **504a** betrie-

ben wird, wird ein Zwangs-AUS-Befehl FOFF erzeugt, und die Ausgangslogikverarbeitungsvorrichtung **313** der [Fig. 3](#) wird zurückgesetzt. Ferner kommt der erste Treiberausgang PWP, der als Schließ-Treiber-Ausgang dient, auf einen Logikpegel "L", und der zweite Treiberausgang PWN, der als dasselbe dient, kommt auf den Logikpegel "H", um in den Antriebsstoppzustand zurückzukommen. Im Schritte-Block **550**, der nach Schritt **505** betrieben wird, führt die durch den Timerschaltungsabschnitt gestartete Haupt-CPU **111a** eine Kurzzeitbetriebsdauer aus, gestartet durch einen Timer in Übereinstimmung mit einem im ersten Programmspeicher **111b** gespeicherten Programm, und das Programm geht dann zu Schritt **506**. Zusätzlich ist der durch den im Schritte-Block **550** ausgeführten Timer gestartete Betrieb beispielsweise ein Betrieb, der mit einem Drucksensor einen Innendruck eines dichten und unter Druck befindlichen Kraftstofftankes erfasst und einen erfassten Druck überwacht, um zu bestimmen, ob eine Druckschwankung über die Zeit innerhalb eines normalen Bereichs liegt.

**[0064]** Im Schritt **506** wird bestimmt, ob oder nicht der durch einen Timer gestartete Betrieb wieder erforderlich ist. In dem Fall erforderlichen Wiederaufweckens geht das Programm weiter zu Schritt **520**. In dem Fall, dass kein Wiederaufwecken erforderlich ist, geht das Programm zu Schritt **521a**. In Bezug auf das Bestimmen, ob das Wiederaufwecken erforderlich ist, wird das Wiederaufwecken unnötig, beispielsweise auf das und nach dem Bestimmen, dass eine Schwankung im Kraftstofftankdruck gering ist und keine Transpiration über eine ausreichend verstrichene Zeitspanne auftritt, oder zu und nach der Zeit des Bestimmens, dass eine Schwankung im Kraftstofftankdruck innerhalb des Bereichs eines übermäßig großen Fehlers liegt.

**[0065]** Im Schritt **520** wird ein Startbetriebsbefehl ST1 erzeugt, und daraufhin geht das Programm zu Schritt **521a**. In diesem Schritt **521a** wird das Erzeugen eines Selbsthalte-Treibersignals DR oder eines Watchdog-Löschsignals WD1 gestoppt, und dann geht das Programm zu einem Betriebsende Schritt **522**.

**[0066]** Zudem, wenn das Watchdog-Löschsignal WD1 im Schritt **521a** gestoppt wird, wie durch Block **521b** gezeigt, stoppt die Watchdog-Timerschaltung **119** das Ausgangszulassungssignal OUTE, der Transistor **130** wird in den nichtleitenden Zustand versetzt und der Ausgangskontakt **104a** wird geöffnet.

**[0067]** Die Betriebsabläufe der [Fig. 4](#), [Fig. 5](#) und [Fig. 6](#) werden kurz beschrieben. Schritt **411a** dient als Zwangsbetriebs-Befehlsvorrichtung zum Erzeugen des Zwangs-EIN-Befehls FON.

**[0068]** Schritt **412a** dient als Zwangsbetriebsüber-

wachungsvorrichtung. Schritt **413a** dient als Betriebsprüfungsbefehlsvorrichtung zum Erzeugen des Betriebsprüfungsbefehls ST2. Schritte-Block **415** dient als Betriebsprüfungsüberwachungsvorrichtung bestehend aus Schritten **415a** bis **415f**. Schritt **420** und Schritt **520** dienen als Startbetriebsbefehlsvorrichtung zum Erzeugen des Startbetriebsbefehls ST1. Schritt **411b**, Schritt **413b** und Schritt **505** dienen als Zwangsstoppbefehlsvorrichtung zum Erzeugen des Zwangs-AUS-Befehls FOFF.

**[0069]** Ferner wird auch vorzugsweise auf den Selbstrückstellbetrieb mit Hilfe des Rückstelltimers **316** gewartet statt des Generierens des Zwangs-AUS-Befehls FOFF durch Schritt **411b**. Zusätzlich ist es ferner vorzuziehen, das Warten auf die Zeitdauer mit Schritt **415d** zu beenden, den Zwangs-AUS-Befehl FOFF zu erzeugen und die Ausgangsgröße für den Schließzustand zu stoppen.

**[0070]** Wie aus der vorangehenden Beschreibung ersichtlich, besteht die Fahrzeugelektroniksteuerung **100a** gemäß der ersten Ausführungsform dieser Erfindung aus: einem Hauptsteuerschaltungsausschnitt **110a**, der mit einem als Haupt-CPU **111a** arbeitenden Mikroprozessor versehen ist, welche mit elektrischer Energie über das Schaltelement **104a** gespeist wird, das ansprechend auf den Betrieb eines Energieversorgungsschalters **102** und einer Hauptenergieversorgungsschaltung **114a** von einer Fahrzeubatterie **101** betrieben wird, und treibt verschiedene Stromverbraucher **105** an in Übereinstimmung mit einem Betriebszustand verschiedener Eingangssensoren **107** **108** und Inhalten eines ersten Programmspeichers **111b**; und ein Timerschaltungsausschnitt **102a**, der immer mit elektrischer Energie über eine Sub-Energieversorgungsschaltung **124** von der erwähnten Fahrzeubatterie **101** versorgt wird, erzeugt ein Ausgangssignal WUP und verbindet die erwähnte Hauptenergieversorgungsschaltung **114a** mit der erwähnten Fahrzeubatterie **101**, wenn die erwähnte Zeitdauer, die gemessen worden ist seit dem Erzeugen eines Zeitdauermess-Startbefehls eines als erwähnte Haupt-CPU arbeitenden Mikroprozessors, eine vorbestimmte Zeitdauer erreicht, die durch die erwähnte Haupt-CPU festgelegt ist. Der erwähnte Timerschaltungsausschnitt **120a** schließt ferner ein: einen Zeittaktzähler **310**, der ein Taktsignal zählt, das eine Zeittaktsignalerzeugungsschaltung **301** erzeugt und eine verstrichene Zeitdauer misst seit dem Erzeugen eines Zeitdauermess-Startbefehls eines als erwähnte Haupt-CPU arbeitenden Mikroprozessors; einen Timerstartzeitdauer-Einstellspeicher **311** zum Speichern und Aufbewahren einer von der erwähnten Haupt-CPU eingestellten Zeitdauer; eine Vergleichsbestimmungsausbegovorrichtung **312** zum Erzeugen eines Aufweck-Ausgangssignals WUP, wenn eine einem zeitabgestimmten Momentanwert des erwähnten Zeittaktzählers **310** entsprechende abgelaufene Zeitdauer eine von einer

Haupt-CPU eingestellte Zeitdauer erreicht, die in dem erwähnten Timerstartzeitdauer-Einstellspeicher **311** gespeichert ist; eine Ausgangslogikverarbeitungsvorrichtung **313** zum Speichern des Erzeugens des erwähnten Aufweck-Ausgabesignals WUP und Erzeugen von Schließ-Treiber-Ausgangsgrößen PWP·PWN zum Schließen der Schaltung des Schaltelementes **104a**, das zwischen der erwähnten Haupthaltungseversorgungsschaltung **114a** und der Fahrzeubatterie **101** vorgesehen ist, zur Zeit des erwähnten Speichererzeugens; und erste und zweite Rückstellvorrichtungen zum Löschen eines Speicherinhaltes der erwähnten Ausgangslogikverarbeitungsvorrichtung **313**. Die erwähnte erste Rückstellvorrichtung ist eine Zwangsstoppbefehlsvorrichtung **505** zum Ausführen des Rückstellens mit Hilfe der erwähnten Haupt-CPU **111a**, die von dem Timerschaltungsausschnitt gestartet worden ist; und die erwähnte zweite Rückstellvorrichtung ist eine Selbst-Rückstellvorrichtung, die arbeitet, wenn das Rückstellen durch die erwähnte erste Rückstellvorrichtung nicht ausgeführt wird, selbst wenn eine vorbestimmte Zeitdauer vergangen ist seit dem Erzeugen des Aufweck-Ausgabesignals WUP, und wenn der Rückstelltimer **316** arbeitet, der in dem erwähnten Timerschaltungsausschnitt **120a** vorgesehen ist, setzt er den Speicher der erwähnten Ausgangslogikverarbeitung-Vorrichtung **313** zurück.

**[0071]** Eine (Schaltungs-)Schließ-Treiber-Ausgangsgröße, die die erwähnte Ausgangslogikverarbeitungsvorrichtung **313** erzeugt, schließt erste und zweite Treiberausgangsgrößen PWP·PWN ein. Das erwähnte Schaltelement **104a** wird angetrieben, um in einem geschlossenen Zustand zu sein, wenn die erwähnte erste Treiberausgangsgröße PWP sich auf einem Logikpegel "H" befindet und die erwähnte zweite Treiberausgangsgröße PWN sich auf dem Logikpegel "L" befindet. Wenn das erwähnte Schaltelement **104a** in einen offenen Zustand gebracht wird, wird die Steuerung derart ausgeführt, dass die erwähnte erste Treiberausgangsgröße PWP normalerweise auf einen Logikpegel "H" oder einen Logikpegel "X" kommt und eine zweite Treiberausgangsgröße PWN auf einen Logikpegel "H" oder einen Logikpegel "X" kommt. Als ein Ergebnis wird der Start durch den Timerschaltungsausschnitt nur ausgeführt, wenn zwei Treiberausgangsgrößen beide normal sind, wodurch das Verhindern des Auftretens von unnötigem Aufweckbetrieb, bedingt durch beispielsweise einen kleinen Defekt von Teilen des Ausgangsabschnitts, ermöglicht wird. Im übrigen zeigt ein Logikpegel "X" einen Wert an, dessen Logikpegel weder "H" noch "L" ist.

**[0072]** Die erwähnte Haupt-CPU **111a** ist mit einer Zwangsbetriebs-Befehlsvorrichtung **411a** versehen, die das Erzeugen eines Prüfweckausgangssignals in Bezug auf die erwähnte Ausgangslogikverarbeitungsvorrichtung **313** während der Dauer erzwingt,

wenn die erwähnte Haupt-CPU **111a** mit einer elektrischen Energie von der Hauptenergieversorgungsschaltung **114a** gespeist wird; und die erwähnte Haupt-CPU **111a** ist mit einem Überwachungseingangsanschluss MNT versehen und einer Zwangsbetriebsüberwachungsvorrichtung **412a**-**412b**. Der erwähnte Überwachungseingangsanschluss MNT ist ein Anschluss zum Eingeben eines Zustandes von Schaltungsschließ-Treiberausgangsgrößen PWP-PWN des Schaltelementes **104a**, das die erwähnte Ausgangslogikverarbeitungsvorrichtung **313** erzeugt, zu der Haupt-CPU **111a** als Überwachungsinformation. Die erwähnte Zwangsbetriebsüberwachungsvorrichtung **412a**-**412b** ist eine Vorrichtung zum Ausführen einer Betriebsdiagnose der erwähnten Ausgangslogikverarbeitungsvorrichtung **313** durch Überwachen eines simulierten Startausgangssignals, das von der erwähnten Zwangsbetriebsbefehlsvorrichtung **411a** übertragen wird, und einer Betriebssituation des erwähnten Überwachungseingangsenschlusses MNT, ansprechend auf ein von der erwähnten ersten Vorrichtung übermitteltes Rückstellsignal. Als ein Ergebnis wird eine Betriebsprüfung des Timerschaltungsabschnittes **120a** ausgeführt, wenn der Energieversorgungsschalter **102** in einen geschlossenen Zustand gebracht ist und die Fahrzeugelektroniksteuerereinrichtung betrieben wird, so dass es einen Vorteil dahingehend gibt, dass der Startbetrieb ohne Grund, bedingt durch beispielsweise einen kleinen Ausfall von Teilen, verhindert werden kann.

**[0073]** Die erwähnte Haupt-CPU **111a** ist mit einer Betriebspüfbefehlsvorrichtung **413a** versehen, die den erwähnten Timerschaltungsabschnitt **120a** zwingt, ein Prüfsignal mit einer vorbestimmten simulierten Zielzeitdauer zu erzeugen, während die erwähnte Haupt-CPU **111a** mit einer elektrischen Energie von der Hauptenergieversorgungsschaltung **114a** gespeist und normal betrieben wird; und die erwähnte Haupt-CPU **111a** ist mit dem erwähnten Überwachungseingangsanschluss MNT und der Betriebspüfbefehlsvorrichtung **415** versehen. Der erwähnte Überwachungseingangsanschluss MNT ist ein Anschluss zum Eingeben eines Zustands der Schließ-Treiber-Ausgangsgrößen PWP-PWN des Schaltelementes **104a** in die erwähnte Haupt-CPU **111**, welches die erwähnte Ausgangslogikverarbeitungsvorrichtung **313** basierend auf der erwähnten Betriebspüfbefehlsvorrichtung **313a** als Überwachungsinformation erzeugt. Die erwähnte Betriebspüfbefehlsvorrichtung **415** ist eine Vorrichtung zum Ausführen einer Startbetriebspüfung des erwähnten Timerschaltungsabschnittes **120a** durch Überwachen einer Betriebssituation des erwähnten Überwachungseingangsenschlusses MNT ansprechend auf ein Prüfausgangssignal, das von der erwähnten Betriebspüfbefehlsvorrichtung **413a** gesendet wird, und einem Rückstellsignal, das von der erwähnten zweiten Rückstellvorrichtung gesendet wird.

Als ein Ergebnis führt das Ausführen der Betriebspüfung einschließlich des Betriebsablaufs der Zeitabstimmung einer Startzeitdauer zu einem Vorteil, dass der Startbetrieb ohne Grund, bedingt durch beispielsweise einen Ausfall einer geringen Zahl relevanter Teile, verhindert werden kann.

**[0074]** Zudem besteht die Fahrzeugelektroniksteuerereinrichtung **100a** der ersten Ausführungsform aus: einem Hauptsteuer-Schaltungsabschnitt **110a**, versehen mit einem Mikroprozessor, der als eine mit einer elektrischen Energie über das ansprechend auf den Betrieb eines Energieversorgungsschalters **102** und eine Hauptenergieversorgungsschaltung **114a** von einer Fahrzeuggbatterie **101** mit elektrischer Energie gespeiste Haupt-CPU **111a** arbeitet und verschiedene Stromverbrauchern **105** ansprechend auf einen Betriebszustand verschiedener Eingangssensoren **107**-**108** und Inhalte eines ersten Programmspeichers **111b** antreibt; und einen Timerschaltungsabschnitt **120a**, der immer über eine Sub-Energieversorgungsschaltung **124** von der erwähnten Fahrzeuggbatterie **101** mit elektrischer Energie gespeist wird, misst eine verstrichene Zeitdauer ab der Erzeugung eines Zeitdauermess-Startbefehls von der erwähnten Haupt-CPU und erzeugt ein Ausgangssignal WUP zum Verbinden der erwähnten Hauptenergieversorgungsschaltung **114a** mit der erwähnten Fahrzeuggbatterie **101**, wenn die erwähnte gemessene Zeitdauer eine vorbestimmte Zeitdauer erreicht hat, die von der erwähnten Haupt-CPU festgelegt ist. Der erwähnte Timerschaltungsabschnitt **120a** schließt ein: einen Zeittaktzähler **310** zum Zählen eines Taktsignals, das eine Zeittaktsignalerzeugungsschaltung **301** erzeugt, und Messen einer abgelaufenen Zeitdauer seit dem Erzeugen eines Zeitmess-Startbefehls von der erwähnten Haupt-CPU; einen Timerstartzeitdauer-Festlegungsspeicher **311** zum Speichern und Aufbewahren einer festgelegten Zeitdauer von der erwähnten Haupt-CPU; eine Vergleichsbestimmungsausgangsvorrichtung **312** zum Erzeugen eines Ausgangssignals WUP, wenn eine verstrichene Zeitdauer des erwähnten Zeittaktzählers **310** entsprechend einem momentanen, getakteten Wert eine von einer Haupt-CPU festgelegte Zeitdauer erreicht, die in dem erwähnten Timerstartzeitdauer-Einstellspeicher **311** gespeichert ist; eine Ausgangslogikverarbeitungsvorrichtung **313** zum Erzeugen von Schließ-Treiberausgangsgrößen PWP-PWN zum Schließen der Schaltung des zwischen der erwähnten Hauptenergieversorgungsschaltung **114a** und einer Fahrzeuggbatterie **101** vorgesehenen Schaltelementes **104a**, ansprechend auf das erwähnte Ausgangssignal WUP; und eine Blinkanzeigeausgabevorrichtung **320** zum Antreiben eines Anzeigeelementes **106** zum Blinken in einer ersten Periode während einer Zeitdauer, in der der erwähnte Zeittaktzähler **310** eine verstrichene Zeitdauer von der Unterbrechung der erwähnten Hauptenergieversorgungsschaltung **114a** misst. Das erwähnte Anzeigeelemente

element **106** ist an einer Position montiert, die zumindest für einen Fahrer eines Fahrzeugs sichtbar ist, und meldet, dass der erwähnte Timerschaltungsabschnitt **102a** in einem Betriebszustand ist; und das erwähnte Anzeigeelement **106** ist an einer auch von außerhalb des Fahrzeugs sichtbaren Position angeordnet und funktioniert als Droh-Anzeigevorrichtung zum Zwecke des Verhinderns des Diebstahls eines geparkten Fahrzeugs. Als ein Ergebnis kann ein Fahrer des Fahrzeugs erkennen, dass der Timerschaltungsabschnitt **102a** durch den Timer in den Betriebszustand gestartet worden ist, und ferner zeigt das Anzeigeelement **106** an, dass der Timerschaltungsabschnitt **102a** in einem Betriebsmodus ist, in dem er auch als Droh-Anzeigeelement zum Verhindern des Diebstahls dient, hierdurch zu einem Vorteil führend, dass ein Erhöhen des Energieverbrauchs unterdrückt werden kann.

**[0075]** Die erwähnte Blinkanzeigeausgabevorrichtung **320** schließt eine Dauerantriebsvorrichtung zum kontinuierlichen Antreiben des erwähnten Anzeigeelementes **106** ein, um es in einer zweiten Periode T2 blinken zu lassen, selbst nachdem eine vorbestimmte Zeitdauer seit dem Übertragen eines Zeitdauermess-Startbefehls von der erwähnten Haupt-CPU verstrichen ist und der erwähnte Timerschaltungsabschnitt **120a** das Erzeugen eines Ausgangssignals WUP abgeschlossen hat; und die erwähnte zweite Zeitdauer ist länger als eine erste Periodendauer, und die erwähnte Blinkanzeigeausgabe-Vorrichtung **320** erkennt und meldet, ob der erwähnte Timerschaltungsabschnitt **120a** in einem Betriebszustand ist oder in einem unbetriebenen Zustand. Als ein Ergebnis gibt es einen Vorteil dahingehend, dass es möglich ist, die Droh-Anzeige mit verlängerter Blinkperiode fortzuführen, um einen Energieverbrauch zu reduzieren, selbst in dem Fall des Belassens einer Fahrzeugelektroniksteuereinrichtung für eine lange Zeitdauer nach dem Abschluss des Aufweckvorgangs.

**[0076]** Das Schaltelement **104a**, das zwischen der erwähnten Fahrzeugbatterie **101** und der Hauptenergieversorgungsschaltung **114a** vorgesehen ist, ist ein Ausgangskontakt eines Energieversorgungsrelais, dessen elektromagnetische Spule **103a** angetrieben wird, um in einem geschlossenen Zustand zu sein, ansprechend auf eine ODER-Ausgangsgröße erster, zweiter und dritter Treibersignale. Das erwähnte erste Treibersignal ist ein Treibersignal, das aktiv oder reaktiv wird, ansprechend auf das Einschalten oder Unterbrechen eines beim Fahren eines Fahrzeugs in den geschlossenen Zustand gebrachten Energieversorgungsschalters **102**. Das erwähnte zweite Treibersignal ist ein Ausgangszulassungssignal OUTE, das aktiv wird, wenn eine Erzeugungsperiode eines Watchdog-Löschsignals WD1, das die erwähnte Haupt-CPU **111a** erzeugt, nicht größer ist als eine vorbestimmte Zeitdauer, oder ist ein Selbstthalte-Trei-

bersignal DR, das die erwähnte Haupt-CPU **111a** erzeugt. Das erwähnte dritte Treibersignal ist ein Schließ-Treibersignal PWP-PWN, das der erwähnte Timerschaltungsabschnitt **120a** erzeugt. Ferner werden die erwähnten Schließ-Treiber-Ausgangsgrößen PWP-PWN gestoppt, nachdem die erwähnte Haupt-CPU **111a** mit dem erwähnten dritten Treibersignal gestartet wurde, und ein Schließbetrieb des erwähnten Schaltelementes wird gehalten mit dem zweiten Treibersignal statt des dritten Treibersignals; andernfalls wird das dritte Treibersignal weiterhin erzeugt und die Ausgabe davon wird von der erwähnten Haupt-CPU **111a** gemeinsam mit dem Abschluss des von dem Timer gestarteten Betriebs beendet. Als ein Ergebnis gibt es einen Vorteil dahingehend, dass die Haupt-CPU **111a** weiterhin mit elektrischer Energie gespeist wird mit dem zweiten Treibersignal, um in der Lage zu sein, einen Vorbereitungsbetrieb für die Startsteuerung auszuführen nach der Unterbrechung des Energieversorgungsschalters **102**. Ferner ist es der Haupt-CPU **111a** möglich, die Steuerung in Bezug auf die Zeitspanne des von dem Timer gemeinsam mit dem Erzeugen einer Treiberausgangsgröße gestarteten Betriebs auszuführen; und die Hauptenergieversorgungsschaltung **114a** zu unterbrechen auf den Abschluss der Startvorbereitungsoperation oder den von dem Timer gestarteten Betrieb, was gegebenenfalls im Einsparen einer Elektrizität der Fahrzeugbatterie **101** resultiert.

## Ausführungsform 2.

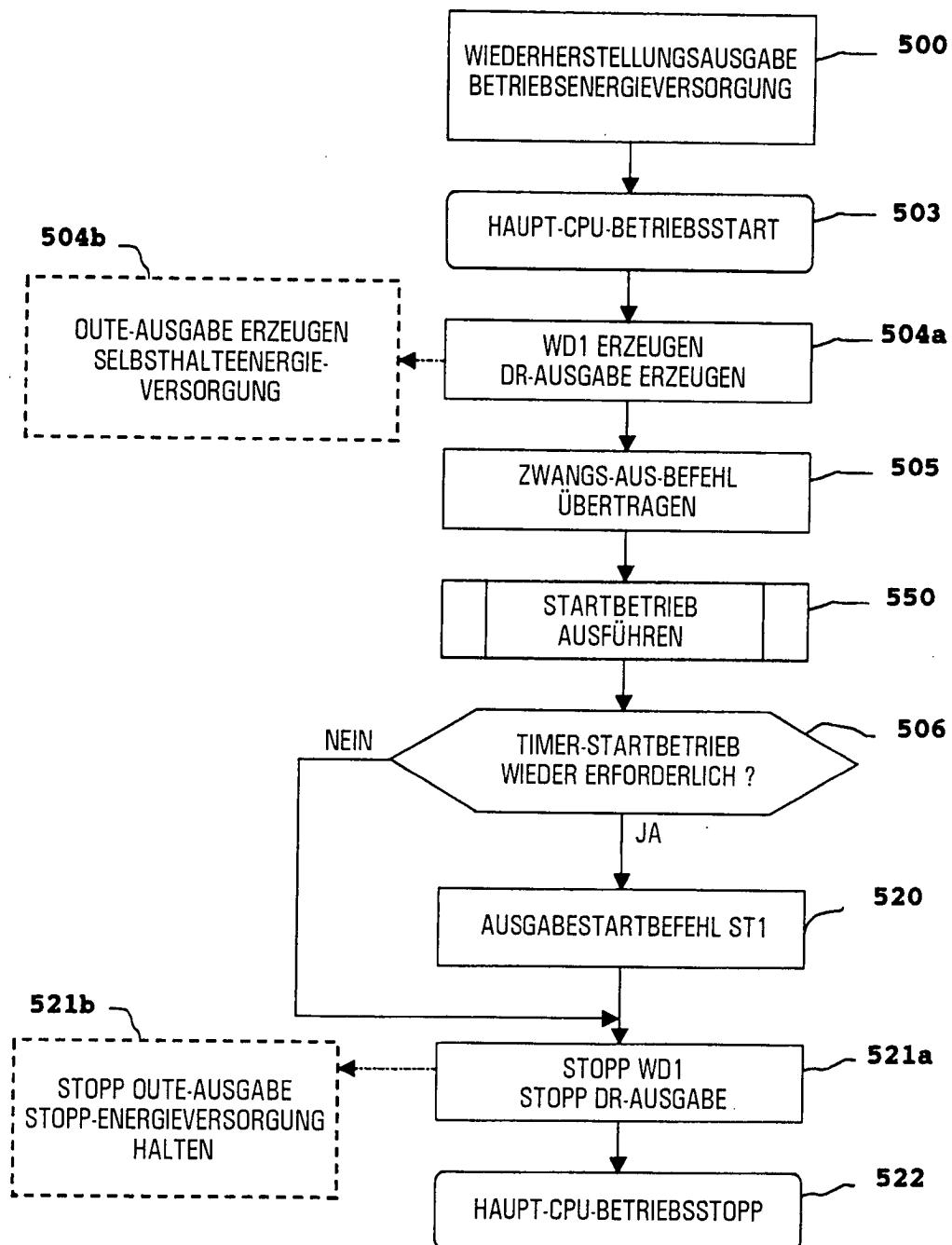

**[0077]** Es wird Bezug genommen auf [Fig. 7](#), die eine schematische Gesamtansicht einer zweiten bevorzugten Ausführungsform dieser Erfindung zeigt, wobei hauptsächlich Punkte beschrieben werden, die sich von denen der [Fig. 1](#) unterscheiden. Unter Bezugnahme auf [Fig. 7](#) wird eine Fahrzeugelektroniksteuereinrichtung **100b** aus einem Hauptsteuerschaltungsabschnitt **110b** und einem Timerschaltungsabschnitt **120b** als Hauptkomponenten gebildet. Zuerst wird ein Ausgangskontakt **104b** eines einer elektromagnetischen Spule **130b** einschließenden Energieversorgungsrelais mit einer Hauptenergieversorgungsschaltung **114a** über eine Rückwärtsstrom-Verhinderungsdiode **14** verbunden, um eine erste Energieversorgungsschaltung von einer Fahrzeugbatterie **101** zu bilden. Der Hauptsteuerschaltungsabschnitt **110b** schließt einen ersten Programmspeicher **111e**, wie zum Beispiel einen nichtflüchtigen Flash-Speicher ein, einen RAM-Speicher **111c** für die Betriebsverarbeitung und einen mit einer Haupt-CPU **111a** kooperierenden Seriell-Parallel-Umsetzer **111d**, und erzeugt ein mit dem Betriebsstart der Haupt-CPU **111a** gemeinsames Selbstthalte-Treibersignal DR. Ein Transistor **130** zum Erregen einer elektromagnetischen Spule **103b** wird über einen Treiberwiderstand **132** ansprechend auf die Tatsache, dass ein Energieversorgungsschalter **102** geschlossen wird, in den leitenden Zustand angetrieben. Ferner wird ein

Transistor **135b**, der über einen Basiswiderstand **135a** von einem Selbsthalte-Treibersignal DR während des Betriebs der Haupt-CPU **111a** in den leitenden Zustand angetrieben, und der Transistor **130** wird durch einen Treiberwiderstand **135c** und den Transistor **135b** im leitenden Zustand gehalten.

**[0078]** Der Timerschaltungsabschnitt **120b** schließt, wie unter Bezugnahme auf [Fig. 7](#) und [Fig. 8](#) detailliert beschrieben, eine Sub-CPU **121a** ein, die bei einer niedrigen Geschwindigkeit arbeitet und mit einem niedrigen Energieverbrauch, einen zweiten Programmspeicher **121**, wie zum Beispiel einen Masken-ROM-Speicher, einen zweiten RAM-Speicher **121c** und einen Seriell-Parallel-Umsetzer **121d**. Nachdem seit dem Auftreten eines offenen Schaltzustandes des oben erwähnten als erstes Schaltelement dienenden Ausgangskontaktes **104b** eine von der Haupt-CPU festgelegte, vorbestimmte Zeitdauer verstrichen ist, erzeugt dieser Timerschaltungsabschnitt **120b** eine Schließ-Treiber-Ausgangsgröße PWP.

**[0079]** Während der Zeit vom Erzeugen des Startbefehls bis zum Erzeugen eines Start-Ausgangssignals führt die Blinkanzeige-Ausgangsgröße FLK einen EIN-/AUS-Betrieb aus. Ferner sind die Haupt-CPU **111a** und die Sub-CPU **121a** derart eingerichtet, dass sie imstande sind, eine serielle Kommunikation miteinander über zwei Seriell-Parallel-Umsetzer **111d** und **121d** auszuführen. Jedoch wird auch ein Invertier-Logiksignal IGS zum Erfassen des Betriebs des Energieversorgungsschalters **102** ebenfalls direkt in die Sub-CPU **121a** eingegeben. Zudem wird eine Schließ-Treiber-Ausgangsgröße PWP ebenfalls direkt in einen Überwachungseingangsanschluss MNT der Haupt-CPU **111a** eingegeben; und zudem ist die Haupt-CPU **111a** eingerichtet, um das später beschriebene Rückstell-Impulssignal RST2 zu generieren, um in der Lage zu sein, die Sub-CPU **121a** zu initialisieren und neu zu starten.

**[0080]** Ein als zweites Schaltelement arbeitender Transistor **141** ist zwischen der Fahrzeubatterie **101** und der Hauptenergieversorgungsschaltung **114a** angeordnet. Dieser Transistor **141** wird über einen Treiberwiderstand **143** in den leitenden Zustand angetrieben, wenn ein in einem Basiskreis vorgesehener Transistor **142** leitend ist.

**[0081]** Der oben erwähnte Transistor **142** wird über eine Serienschaltung einer Diode **127c** und eines Treiberwiderstandes **127b** von dem Schaltungsschließ-Treiberausgang PWP leitend angetrieben. Zudem wird der oben erwähnte Transistor **142** über eine Serienschaltung einer Diode **127d** und eines Treiberwiderstandes **127b** von der Selbsthalte-Treiberausgangsgröße DR leitend gehalten.

**[0082]** Zusätzlich kann statt der zum Halten des

Transistors **135b** und des Transistors **142** im leitfähigen Zustand dienenden Treiberausgangsgröße DR ebenfalls ein Ausgangszulassungssignal OUTE verwendet werden, das die Watchdog-Timerschaltung **119** erzeugt, wenn eine Impulsbreite eines Watchdog-Löschssignals WD1, das eine Impulsfolge ist, die die Haupt-CPU **111a** erzeugt, nicht größer ist als ein vorbestimmter Wert. Zudem, unter der Annahme, dass die Sub-CPU **121a** weiterhin ein Aufweck-Ausgangssignal PWP erzeugt und das Erzeugen dieses Ausgangssignals von der Haupt-CPU **111a** einhergehend mit dem von dem Timer gestarteten Betriebs gestoppt wird, ist es nicht erforderlich, den Transistor **142** mit dem Selbsthalte-Treibersignal DR oder dem Ausgangszulassungssignal OUTE anzutreiben.

**[0083]** [Fig. 8](#) zeigt ein äquivalentes Steuerblockdiagramm von Steuerungsinhalten, die die Sub-CPU **121a** in [Fig. 7](#) in Kooperation mit dem zweiten Programmspeicher **121e** ausführt. Unter Bezugnahme auf [Fig. 8](#) wird ein Taktsignal, das eine Zeittaktsignal-Erzeugungsschaltung **310** erzeugt, frequenzgeteilt von einer ersten Teilerschaltungsvorrichtung **302a** zum Erzeugen eines ersten Taktsignals CLK1 mit einer Periodenzeit von beispielsweise 0,1 Sekunden, wird ferner frequenzgeteilt in einer zweiten Teilerschaltung **302b** zum Erzeugen eines zweiten Taktsignals CLK2 mit einer Periodendauer von beispielsweise 1 Sekunde und wird ferner frequenzgeteilt in einer dritten Teilerschaltung **302c** zum Erzeugen eines dritten Taktsignals CLK3 mit einer Periodenzeit von beispielsweise 1 Minute.

**[0084]** Die Startbefehls-Speichervorrichtung **303b** besteht beispielsweise aus einem einen Einstell- bzw. Setzeingang S1 und einen Rückstelleingang R1 einschließenden Flip-Flop und speichert das Empfangen eines Startbetriebsbefehls **303a**, der von der Haupt-CPU **111a** übertragen worden ist. Die Betriebspüfbefehls-Speichervorrichtung **304b** besteht beispielsweise aus einem einen Einstell- bzw. Setzeingang S2 und einen Rückstell- bzw. Rücksetzeingang R2 enthaltenden Flip-Flop und speichert den Empfang eines Betriebspüfbefehls **304a**, der von der Haupt-CPU **111a** übertragen worden ist.

**[0085]** Ein UND-Element **305** erzeugt eine UND-Ausgangsgröße von logisch invertierten Ausgängen eines Speicherausgangs von der Startbefehls-Speichervorrichtung **303b** und eines Speicher-ausgangs von der Betriebsinspektionsbefehls-Speichervorrichtung **304b** und ein drittes Taktsignal CLK3. Ferner erzeugt ein UND-Element **306** eine UND-Ausgangsgröße logisch invertierender Ausgänge eines Speicherausgangs von der Betriebspüfbefehls-Speichervorrichtung **304** und eines Speicher-ausgangs von der Startbefehls-Speichervorrichtung **303b** und ein zweites Taktsignal CLK2. Ausgangsgrößen von den UND-Elementen **305** und **306** sind mit einem Eingang eines ODER-Elementes **307** ver-

bunden.

**[0086]** Ein Zeittaktzähler **310** ist eingerichtet, um ein Ausgangssignal von dem ODER-Element **307** zu zählen. Dieser Zeittaktzähler **310** führt das Zählen bei einer niedrigen Geschwindigkeit mit einem dritten Taktsignal CLK3 aus, während ein Speicherausgang von der Startbefehls-Speichervorrichtung **303b** erzeugt wird; und führt das Zählen bei einer hohen Geschwindigkeit mit einem zweiten Taktsignal CLK2 aus, während ein Speicherausgang von der Betriebsprüfbefehls-Speichervorrichtung **304b** erzeugt wird.

**[0087]** Eine Konstante, die einem Wert entspricht, der erhalten wird durch Teilen einer festgelegten Zeitdauer von der Haupt-CPU gemeinsam mit einem von der Haupt-CPU **111a** gesendeten Timerstartzeit-einstellbefehl **311a** durch eine Periodenzeit eines dritten Taktsignals CLK3, wird übertragen und gespeichert in einem Timerstartzeitdauer-Einstellspeicher **311b**. Zusätzlich wird ein in Übereinstimmung mit einer Zeitgebereinheit des Zeittaktzählers **310** umgesetzter Zielwert von der Haupt-CPU **111a** übertragen oder diese Umsetzverarbeitung wird auf der Seite der Sub-CPU **111a** ausgeführt.

**[0088]** Eine Vergleichsbestimmungsausgangsvorrichtung **312** vergleicht einen momentanen Wert des Zeittaktzählers **310** mit einer in dem Timerstartzeitdauer-Einstellspeicher **311b** gespeicherten Konstante und erzeugt ein Aufweck-Ausgabesignal WUP, wenn beide koinzidieren. Eine Ausgangslogikverarbeitungsvorrichtung **313** besteht beispielsweise aus einem einen Einstell- bzw. Setzeingang SO und einen Rückstelleingang R0 einschließenden Flip-Flop, und ein Setzausgang davon ist eine Schließ-Treiber-Ausgangsgröße PWP.

**[0089]** Ein ODER-Element **314b** setzt eine Ausgangslogikverarbeitungsvorrichtung **313** mit einer ODER-Ausgangsgröße eines Stoppsignals STOP zurück, das die Vergleichsbestimmungs-Ausgangsvorrichtung **312** erzeugt, und einem Zwangs-EIN-Befehl **314a**, der von der Haupt-CPU **111a** gesendet worden ist; und ein momentaner Wert des Zeittaktzählers **310** wird durch den Setzausgang der Ausgangslogikverarbeitungsvorrichtung **313** auf 0 zurückgesetzt.

**[0090]** Ein ODER-Element **315b** setzt die Ausgangslogikverarbeitungsvorrichtung **313** mit einer ODER-Ausgangsgröße eines Stoppsignals STOP zurück, das der später zu beschreibende Rückstell-timer **316** erzeugt, und einem Zwangs-AUS-Befehl **315a**, der von der Haupt-CPU **111a** gesendet worden ist; und setzt die Startbefehls-Speichervorrichtung **303b** und die Betriebsinspektionsbefehls-Speichervorrichtung **304b** zurück.

**[0091]** Ein Rückstelltimer **316** startet die Zeitabstim-

mung gemeinsam mit dem Erzeugen einer eingestellten Ausgangsgröße der Ausgangslogikverarbeitungsvorrichtung **313** und erzeugt ein Stopp-Signal STOP, nachdem eine vorbestimmte Zeitdauer verstrichen ist, zum Zurücksetzen der Ausgangslogik-Verarbeitungsvorrichtung **313**, der Startbefehls-Speichervorrichtung **303b** und der Betriebsprüfbefehls-Speichervorrichtung **304b**.

**[0092]** Eine Blinkanzeigeausgabevorrichtung **320** besteht aus einem einen erzeugten Impuls eines ersten Taktsignals CLK1 zählenden Zähler. Eine Blink-periodendauer, die gemeinsam mit einem Periodenzeiteinstellbefehl **325a** von der Haupt-CPU **111a** gesendet worden ist, wird in einem Periodeneinstellspeicher **325b** gespeichert. Eine Vergleichsvorrichtung **323** vergleicht einen momentanen Wert des als Blinkanzeigeausgabevorrichtung **320** dienenden Zählers mit einem Inhalt im Periodeneinstellspeicher **325b** und stellt einen momentanen Wert des als Blinkanzeigeausgabevorrichtung **320** dienenden Zählers auf 0 zurück, jedes Mal, wenn sie als Ergebnis des Vergleichs koinzidieren.

**[0093]** Ein Gatterelement **324** besteht aus einem UND-Element, mit einer Momentanwertausgangsgröße CV1, die auf einem Logikpegel "H" liegt, wenn ein Momentanwert des als Blinkanzeigeausgabe-Vorrichtung **320** dienenden Zählers 1 ist, und einem Invertierlogiksignal IGS1, das auf einem Logikpegel "L" liegt, wenn der Energieversorgungsschalter **102** in einen geschlossenen Zustand gebracht wird, als Eingangsgrößen. Die UND-Ausgangsgröße davon ist eine Blinkanzeige-Ausgangsgröße FLK.

**[0094]** Zudem ist eine Periodenzeit eines ersten Taktsignals CLK1 beispielsweise 0,1 Sekunden; während eine in dem Periodeneinstellspeicher **325b** zu speichernde Blinkperiodezeit variable eingestellt wird auf einen Wert von 20 bis 30, was beispielsweise 2 bis 3 Sekunden entspricht.

**[0095]** Trotzdem wird, wenn der Energieversorgungsschalter **102** geschlossen wird, eine Blinkanzeigeausgangsgröße FLK durch die Aktion eines Gatterelementes **324** gestoppt, das auf einen Logikpegel "L" festzulegen ist.

**[0096]** Ferner zeigt [Fig. 8](#) einen äquivalenten Steuerblock in Bezug auf einen Betriebsinhalt der Sub-CPU **121a** in Kooperation mit einem zweiten Programmspeicher **121e**. In Bezug auf die Startbefehls-Speichervorrichtung **313b**, die Betriebsprüfbefehls-Speichervorrichtung **304b**, den Timerstartzeitdauer-Einstellspeicher **311b** und den Periodeneinstellspeicher **325b** wird ein zweiter RAM-Speicher **121c** verwendet, und eine Vielzahl von Logikverarbeitungsvorgängen wird ausgeführt in Übereinstimmung mit einem Steuerprogramm, das in einem zweiten Programmspeicher **121e** gespeichert ist.

**[0097]** Jedoch verwendet eine Zeittaktsignal erzeugungsschaltung **301** einen durch Verbinden von beispielsweise einer ungeraden Zahl von logischen Invertierelementen in einer ringförmig untergeordneten Weise gebildeten Ringzähler. Dieser Ringzähler zeigt eine geringe Periodengenauigkeit im Vergleich zu einem in der Haupt-CPU **111a** verwendeten Referenz-Oszillator **112**. Ferner sind ein Gatterelement **324** oder eine Ausgangslogikverarbeitungslogik **313** ebenfalls aus außerhalb der Sub-CPU **121a** vorgesehener Hardware gebildet.

**[0098]** Unter Bezugnahme auf [Fig. 9](#) und [Fig. 10](#), die ein erläuterndes Ablaufdiagramm des ersten Teilbetriebs der Haupt-CPU **111a** der [Fig. 7](#) sind, wird, wenn in Schritt **800** die Fahrzeugelektroniksteuereinrichtung **100b** mit der Fahrzeughilfsbatterie **101** verbunden wird, im nachfolgenden Schritt **801** der Timerschaltungsabschnitt **120b** mit elektrischer Energie von einer Sub-Energieversorgungsschaltung **124** versorgt, um in einem Zustand zu sein, einen Betrieb ausführen zu können; und der Hauptsteuerschaltungsabschnitt **110b** kommt in den Zustand, in dem er in der Lage ist, den Speicherinhalt des ersten RAM-Speichers **111c** mit Hilfe einer Schlummerenergie-Versorgungsschaltung **114b** zu halten. Jedoch befindet sich die Haupt-CPU noch immer im Stopp-Zustand.

**[0099]** Dann, wenn der Energieversorgungsschalter **102** im Schritt **802** eingeschaltet wird, wird eine Blinkanzeigeausgangsgröße FLK normalerweise durch die Aktion des Gatter-Elementes **324** der [Fig. 8](#) gestoppt. Jedoch wird der Transistor **130** der [Fig. 7](#) in leitfähigen Zustand gebracht, eine elektromagnetische Spule **103b** wird erregt, ein Ausgangskontakt **104b** wird in einen geschlossenen Zustand gebracht und die Energiezufuhr zu dem Hauptsteuerschaltungsabschnitt **110a** wird gestartet. In dem nachfolgenden Schritt **803** startet die Haupt-CPU **111a** den Betrieb.

**[0100]** Schritt **804a** wird nachfolgend auf Schritt **803** betrieben und erzeugt ein Watchdog-Löschesignal WD1 oder ein Selbsthaltetreibersignal DR. Gemeinsam mit dem Erzeugen eines Watchdog-Löschesignals WD1, wie durch den Block **804** gezeigt, erzeugt die Watchdog-Timer-Schaltung **119** ein Ausgangszulassungssignal OUTE. Die Leitung durch den Transistor **130** wird aufrecht erhalten gemeinsam mit dem Erzeugen eines Selbsthaltetreibersignals DR. Demgemäß wird die Erregung der elektromagnetischen Spule **103b** beibehalten, selbst wenn der Energieversorgungsschalter sich in einem offenen Zustand befindet.

**[0101]** Im Schritt **810a**, der nach dem Schritt **804a** betrieben wird, wird bestimmt, ob oder nicht der Energieversorgungsschalter **102** fortgesetzt im geschlossenen Zustand bleibt durch Überwachen eines

invertierenden Logiksignals IGS. In dem Fall, in dem der Energieversorgungsschalter **102** sich im geschlossenen Zustand befindet, geht das Programm zu Schritt **810b**. In dem Fall, in dem der Energieversorgungsschalter **102** sich im offenen Zustand befindet, geht das Programm zu Schritt **813b**.

**[0102]** Im Schritt **810b** wird bestimmt, ob oder nicht ein Betriebsbestätigungstest des Timerschaltungsabschnittes **120b** ausgeführt wird. Wenn der Betriebsbestätigungstest ausgeführt wird, geht das Programm zu Schritt **811a**. Wenn der Betriebsbestätigungstest nicht ausgeführt wird, geht das Programm zum Schrittblock **850a**. Zusätzlich wird das Bestimmen des Schrittes **810b** im wesentlichen in regelmäßigen Intervallen während einer Dauer ausgeführt, wenn eine Motorgeschwindigkeit niedrig ist und die Haupt-CPU **111b** einen Reaktionszeitspielraum hat unter der Annahme, dass die Fahrzeugelektroniksteuereinrichtung **100a** beispielsweise eine Motorsteuereinrichtung ist.

**[0103]** Im Schritt **811a** wird ein in [Fig. 8](#) gezeigter Zwangs-EIN-Befehl **314a** übertragen. Im darauffolgenden Schritt **812a** wird bestimmt, ob eine Schließ-Treiberausgangsgröße PWP normal betrieben wird durch die Überwachung eines Überwachungseingangsanschlusses MNT. In dem Fall des Fehlerbetriebs geht das Programm zu Schritt **817**. In dem Fall des Normalbetriebs geht das Programm zu Schritt **811b**.