(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6247188号

(P6247188)

(45) 発行日 平成29年12月13日(2017.12.13)

(24) 登録日 平成29年11月24日(2017.11.24)

(51) Int.Cl.

F 1

|        |       |           |        |       |         |

|--------|-------|-----------|--------|-------|---------|

| HO 1 G | 4/232 | (2006.01) | HO 1 G | 4/12  | 3 5 2   |

| HO 1 G | 2/06  | (2006.01) | HO 1 G | 1/035 | C       |

| HO 1 G | 4/30  | (2006.01) | HO 1 G | 4/12  | 3 6 1   |

| HO 1 G | 4/35  | (2006.01) | HO 1 G | 4/30  | 3 0 1 C |

|        |       |           | HO 1 G | 4/30  | 3 0 1 B |

請求項の数 16 (全 18 頁) 最終頁に続く

(21) 出願番号

特願2014-203082 (P2014-203082)

(22) 出願日

平成26年10月1日(2014.10.1)

(65) 公開番号

特開2015-88747 (P2015-88747A)

(43) 公開日

平成27年5月7日(2015.5.7)

審査請求日

平成27年1月28日(2015.1.28)

(31) 優先権主張番号

10-2013-0131110

(32) 優先日

平成25年10月31日(2013.10.31)

(33) 優先権主張国

韓国(KR)

(31) 優先権主張番号

10-2014-0084594

(32) 優先日

平成26年7月7日(2014.7.7)

(33) 優先権主張国

韓国(KR)

前置審査

(73) 特許権者 594023722

サムソン エレクトローメカニックス カンパニーリミテッド。

大韓民国、キョンギード、スウォンーシ、ヨントング、(マエタンードン) マエヨンーロ 150

(74) 代理人 110000877

龍華国際特許業務法人

(72) 発明者

リー、キヨ クアン

大韓民国、キョンギード、スウォンーシ、ヨントング、(マエタンードン) マエヨンーロ 150 サムソン エレクトローメカニックス カンパニーリミテッド。内

最終頁に続く

(54) 【発明の名称】積層セラミックキャパシタ

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の誘電体層が積層されるセラミック本体と、

前記複数の誘電体層の各々を介して交互に配置される複数の第1内部電極及び複数の第2内部電極を含む活性層と、

前記複数の第1内部電極において、前記セラミック本体の実装面に露出するように延長されて形成され、前記セラミック本体の長さ方向に沿って離隔されるように配置される第1リード部及び第2リード部と、

前記複数の第2内部電極において、前記セラミック本体の実装面に露出するように延長されて形成され、前記第1リード部及び前記第2リード部の間に配置される第3リード部と、

前記セラミック本体の実装面に前記セラミック本体の長さ方向に沿って離隔されるように配置され、前記第1リード部と接続される第1外部電極及び前記第2リード部と接続される第2外部電極と、

前記セラミック本体の実装面に前記第1外部電極及び前記第2外部電極の間に配置され、前記第3リード部と接続される第3外部電極と、を含み、

前記第1リード部から前記第3リード部は、前記複数の第1内部電極及び前記複数の第2内部電極から傾斜されるように延長された傾斜延長部、及び前記傾斜延長部から前記セラミック本体の実装面に向かって垂直に延長された垂直延長部を含み、

前記第1リード部または前記第2リード部と前記第3リード部の垂直延長部の間に設け

10

20

られる第1スペース部の面積をS<sub>a</sub>、前記第1リード部または前記第2リード部と前記第3リード部の傾斜延長部の間に設けられる第2スペース部の面積をS<sub>b</sub>、S<sub>a</sub>+S<sub>b</sub>をS<sub>t</sub>と規定するとき、0.383 S<sub>a</sub>/S<sub>b</sub> 12、0.277 S<sub>a</sub>/S<sub>t</sub> 0.923であり、

前記第1内部電極の端辺が、前記第1リード部及び前記第2リード部において前記第3リード部と対向しない外側を含んで一直線を成す、積層セラミックキャパシタ。

#### 【請求項2】

前記複数の第1内部電極及び前記複数の第2内部電極は、前記セラミック本体の長さ方向の両面から離隔されるように配置される、請求項1に記載の積層セラミックキャパシタ。10

#### 【請求項3】

前記第1外部電極から前記第3外部電極は、前記セラミック本体の幅方向の両面の一部にそれぞれ延長されるように形成される、請求項1または請求項2に記載の積層セラミックキャパシタ。

#### 【請求項4】

前記第1外部電極から前記第3外部電極は、それぞれに対応するリード部と接触して連結された導電層、及び前記導電層を覆うように形成されためっき層を含む、請求項1から請求項3の何れか1項に記載の積層セラミックキャパシタ。

#### 【請求項5】

前記めっき層は、前記導電層を覆うように形成されたニッケル(Ni)めっき層、及び前記ニッケルめっき層を覆うように形成されたすず(Sn)めっき層を含む、請求項4に記載の積層セラミックキャパシタ。20

#### 【請求項6】

前記複数の第1内部電極において、前記セラミック本体の実装面に対向する面に露出するように延長されて形成され、前記セラミック本体の長さ方向に沿って離隔されるように配置される第4リード部及び第5リード部と、

前記複数の第2内部電極において、前記セラミック本体の実装面に対向する面に露出するように延長されて形成され、前記第4リード部及び前記第5リード部の間に配置される第6リード部と、

前記セラミック本体の実装面に対向する面に配置される絶縁層と、を含む、請求項1から請求項5の何れか1項に記載の積層セラミックキャパシタ。30

#### 【請求項7】

前記複数の第1内部電極は、長さ方向に離隔され、前記セラミック本体の実装面に対向する面に露出する第4リード部及び第5リード部を有し、

前記複数の第2内部電極は、前記セラミック本体の実装面に対向する面に露出し、前記第4リード部及び前記第5リード部の間に前記第4リード部及び前記第5リード部とそれ離隔されて形成された第6リード部を有し、

前記セラミック本体の実装面に対向する面に長さ方向に離隔されて形成され、前記第4リード部と接続された第4外部電極及び前記第5リード部と接続された第5外部電極と、

前記セラミック本体の実装面に対向する面に前記第4外部電極及び前記第5外部電極とそれ離隔されて形成され、前記第6リード部と接続された第6外部電極と、を含む、請求項1から請求項5の何れか1項に記載の積層セラミックキャパシタ。40

#### 【請求項8】

前記第4リード部から前記第6リード部のうち少なくとも一つは、少なくとも片側の一部が傾斜延長部で形成される、請求項7に記載の積層セラミックキャパシタ。

#### 【請求項9】

前記第4リード部から前記第6リード部のうち少なくとも一つは、前記複数の第1内部電極または前記複数の第2内部電極から傾斜されるように延長された傾斜延長部、及び前記傾斜延長部から前記セラミック本体の実装面に対向する面に向かって垂直に延長された垂直延長部を含む、請求項7または請求項8に記載の積層セラミックキャパシタ。50

**【請求項 10】**

前記第4リード部から前記第6リード部は、前記複数の第1内部電極及び前記複数の第2内部電極から傾斜されるように延長された傾斜延長部、及び前記傾斜延長部から前記セラミック本体の実装面に対向する面に向かって垂直に延長された垂直延長部を含み、

前記第4リード部または前記第5リード部と前記第6リード部の垂直延長部の間に設けられる第1スペース部の面積を  $S_a$ 、前記第4リード部または前記第5リード部と前記第6リード部の傾斜延長部の間に設けられる第2スペース部の面積を  $S_b$  と規定するとき、

$0.383 S_a / S_b = 1.2$  である、請求項7または請求項8に記載の積層セラミックキャパシタ。

**【請求項 11】**

10

前記第4リード部から前記第6リード部は、前記複数の第1内部電極及び前記複数の第2内部電極から傾斜されるように延長された傾斜延長部、及び前記傾斜延長部から前記セラミック本体の実装面に対向する面に向かって垂直に延長された垂直延長部を含み、

前記第4リード部または前記第5リード部と前記第6リード部の垂直延長部の間に設けられる第1スペース部の面積を  $S_a$ 、前記第4リード部または前記第5リード部と前記第6リード部の傾斜延長部の間に設けられる第2スペース部の面積を  $S_b$ 、

$S_a + S_b = S_t$  を規定するとき、 $0.277 S_a / S_t = 0.923$  である、請求項7または請求項8に記載の積層セラミックキャパシタ。

**【請求項 12】**

20

前記第4外部電極から前記第6外部電極は、前記セラミック本体の幅方向の両面の一部にそれぞれ延長されるように形成される、請求項7から請求項11の何れか1項に記載の積層セラミックキャパシタ。

**【請求項 13】**

前記第4外部電極から前記第6外部電極は、それぞれに対応するリード部と接触して連結された導電層、及び前記導電層を覆うように形成されためっき層を含む、請求項7から請求項12の何れか1項に記載の積層セラミックキャパシタ。

**【請求項 14】**

前記めっき層は、前記導電層を覆うように形成されたニッケル( $Ni$ )めっき層、及び前記ニッケルめっき層を覆うように形成されたすず( $Sn$ )めっき層を含む、請求項13に記載の積層セラミックキャパシタ。

30

**【請求項 15】**

前記活性層の幅方向の両面に配置されたカバー層をさらに含む、請求項1から請求項14の何れか1項に記載の積層セラミックキャパシタ。

**【請求項 16】**

前記傾斜延長部が曲線からなる、請求項1から請求項15の何れか1項に記載の積層セラミックキャパシタ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、積層セラミックキャパシタ及びその実装基板に関する。

40

**【背景技術】****【0002】**

最近は、電子製品の小型化及び高容量化に伴い、電子製品に用いられる電子部品も小型化及び高容量化が求められている。

**【0003】**

このうち、積層セラミックキャパシタの場合、等価直列インダクタンス(Equivalent Series Inductance、以下「ESL」)が大きくなると、電子製品の性能が低下する可能性があり、適用される電子部品が小型化及び高容量化するほど積層セラミックキャパシタの ESL 増加が電子部品の性能低下に及ぼす影響は相対的に大きくなる。

50

## 【0004】

特に、I Cの高性能化に伴い、デカップリングキャパシタの使用が増加している。これにより、外部端子間の距離を減少させて電流経路を減少させることでキャパシタのインダクタンスを減らすことができる垂直積層型3端子構造のMLCC、いわゆる「LICC(Low Inductance Chip Capacitor)」に対するニーズが高まっている。

## 【先行技術文献】

## 【特許文献】

## 【0005】

【特許文献1】韓国公開特許第2009-0117686号公報

10

【特許文献2】韓国登録特許第0920614号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

本発明の目的は、垂直積層型3端子キャパシタにおいて、低ESLの特性を向上させることができる積層セラミックキャパシタ及びその実装基板を提供することにある。

## 【課題を解決するための手段】

## 【0007】

本発明の一側面は、セラミック本体の実装面に3つの外部電極を離隔されるように配置し、第1及び第2内部電極において、セラミック本体の実装面に露出するように延長されて形成される第1から第3リード部のうち少なくとも一つは、少なくとも片側の一部が傾斜延長部で形成される積層セラミックキャパシタを提供する。

20

## 【発明の効果】

## 【0008】

本発明の一実施形態によると、内部電極のリード部において、少なくとも片側の一部を傾斜延長部で形成することにより、電流経路(current path)を減少させてESLを低減させ、ESL散布を改善させることができる効果がある。

## 【図面の簡単な説明】

## 【0009】

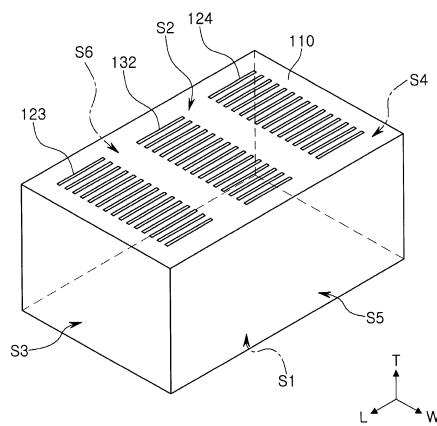

【図1】本発明の一実施形態による積層セラミックキャパシタをひっくり返して概略的に示した斜視図である。

30

【図2】図1の積層セラミックキャパシタにおけるセラミック本体をひっくり返して示した斜視図である。

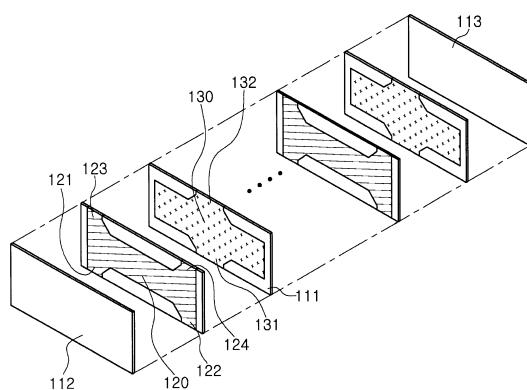

【図3】図1の積層セラミックキャパシタにおける外部電極を省略して示した分解斜視図である。

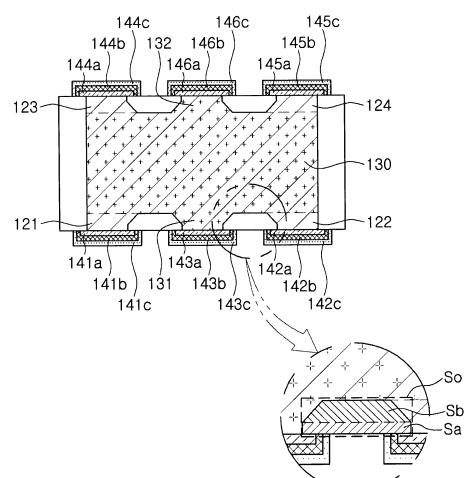

【図4】図1の積層セラミックキャパシタを示した断面図である。

【図5】本発明の他の実施形態による積層セラミックキャパシタを概略的に示した斜視図である。

【図6】図5の積層セラミックキャパシタにおける外部電極を省略して示した分解斜視図である。

40

【図7】図5の積層セラミックキャパシタを示した断面図である。

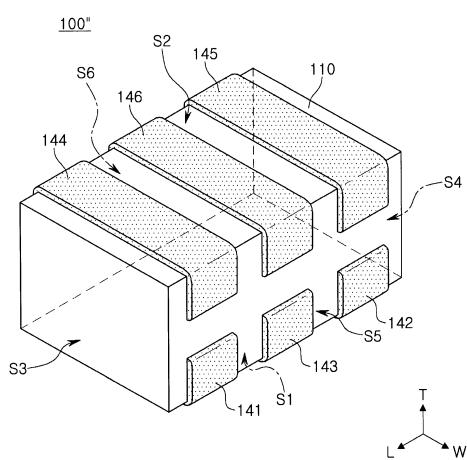

【図8】本発明のさらに他の実施形態による積層セラミックキャパシタを概略的に示した斜視図である。

【図9】図8の積層セラミックキャパシタにおけるセラミック本体を示した斜視図である。

【図10】図8の積層セラミックキャパシタにおける外部電極を省略して示した分解斜視図である。

【図11】図8の積層セラミックキャパシタを示した断面図である。

【図12】本発明の積層セラミックキャパシタにおけるリード部の一形態を示した平面図である。

50

【図13】本発明の積層セラミックキャパシタにおけるリード部の他の一形態を示した平面図である。

【図14】図8の積層セラミックキャパシタが基板に実装された形状を示した斜視図である。

【図15】図8の積層セラミックキャパシタが基板に実装された形状を示した断面図である。

#### 【発明を実施するための形態】

##### 【0010】

以下では、添付の図面を参照し、本発明の好ましい実施形態について説明する。しかし、本発明の実施形態は様々な他の形態に変形されることができ、本発明の範囲は以下で説明する実施形態に限定されない。また、本発明の実施形態は、当該技術分野で平均的な知識を有する者に本発明をより完全に説明するために提供されるものである。したがって、図面における要素の形状及び大きさなどはより明確な説明のために誇張されることがある。

10

##### 【0011】

また、本発明の実施形態を明確に説明するために六面体の方向を定義すると、図面に示されたL、W及びTはそれぞれ長さ方向、幅方向及び厚さ方向を示す。ここで、幅方向は、誘電体層が積層された積層方向と同一の概念で用いられることができる。

##### 【0012】

###### 【積層セラミックキャパシタ】

20

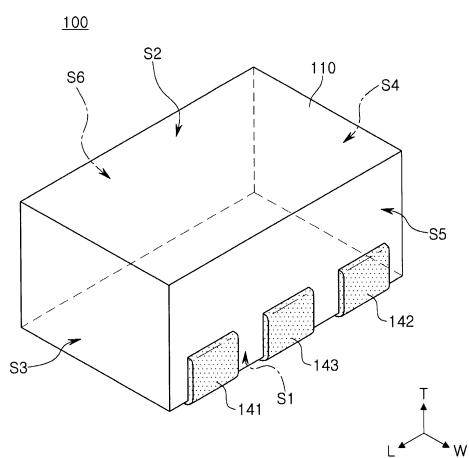

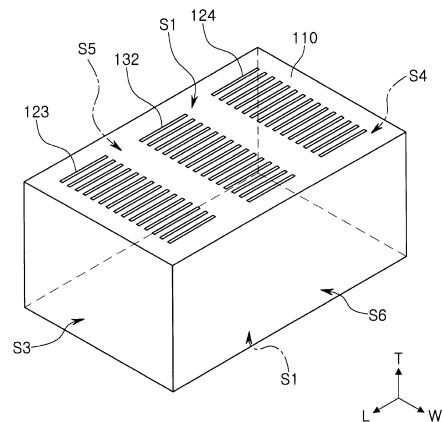

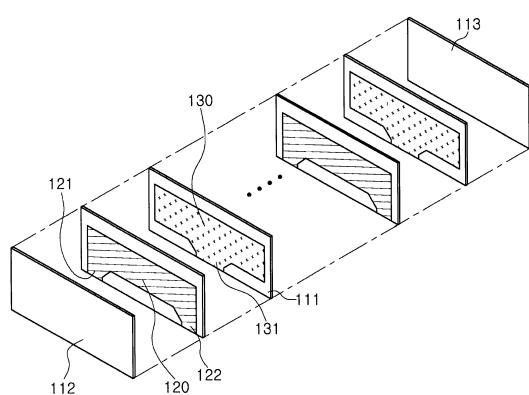

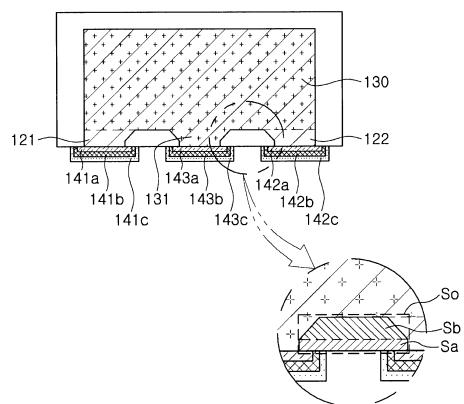

図1は本発明の一実施形態による積層セラミックキャパシタをひっくり返して概略的に示した斜視図であり、図2は図1の積層セラミックキャパシタにおけるセラミック本体をひっくり返して示した斜視図であり、図3は図1の積層セラミックキャパシタにおける外部電極を省略して示した分解斜視図であり、図4は図1の積層セラミックキャパシタを示した断面図である。

##### 【0013】

図1から図4を参照すると、本実施形態による積層セラミックキャパシタ100は、複数の誘電体層111が積層されたセラミック本体110、複数の第1及び第2内部電極120、130を含む活性層、及び第1から第3外部電極141～143を含む。

##### 【0014】

30

本実施形態の積層セラミックキャパシタ100は、総3つの外部端子を有する、いわゆる3端子キャパシタとみなすことができる。

##### 【0015】

セラミック本体110は、相対する厚さ方向の第1面S1及び第2面S2、第1面S1と第2面S2を連結し、相対する幅方向の第5面S5及び第6面S6、及び相対する長さ方向の第3面S3及び第4面S4を有することができる。

##### 【0016】

以下では、本実施形態において、積層セラミックキャパシタ100の実装面は、セラミック本体110の第1面S1と定義して説明する。

##### 【0017】

40

上記セラミック本体110は、複数の誘電体層111を積層してから焼成して形成され、その形状に特に制限されないが、図面に示されているように六面体状を有することができる。

##### 【0018】

ただし、このようなセラミック本体110の形状、寸法及び誘電体層111の積層数は本実施形態に示されるものに限定されない。

##### 【0019】

また、セラミック本体110を形成する複数の誘電体層111は、焼結された状態で、隣接する誘電体層111間の境界が走査電子顕微鏡(SEM、Scanning Electron Microscope)を利用して確認できないほど一体化されている

50

ことができる。

**【0020】**

このようなセラミック本体110は、キャパシタの容量形成に寄与する部分で、複数の内部電極を有する活性層、及びマージン部として上記活性層の幅方向の両面に形成されたカバー層112、113を含むことができる。

**【0021】**

上記活性層は、誘電体層111を介して複数の第1及び第2内部電極120、130を幅方向に交互に積層して形成されることができる。

**【0022】**

このとき、誘電体層111の厚さは、積層セラミックキャパシタ100の容量設計に応じて任意に変更することができ、焼成後の1層の厚さが0.01~1.00μmになるように構成する方が好ましいが、本発明はこれに限定されない。

10

**【0023】**

また、誘電体層111は、高誘電率を有するセラミック粉末、例えば、チタン酸バリウム(BaTiO<sub>3</sub>)系またはチタン酸ストロンチウム(SrTiO<sub>3</sub>)系粉末を含むことができるが、十分な静電容量が得られるものであれば、本発明はこれに限定されない。

**【0024】**

また、誘電体層111には、上記セラミック粉末とともに、必要に応じて、セラミック添加剤や有機溶剤、可塑剤、結合剤、分散剤などがさらに添加されることができる。

**【0025】**

このとき、誘電体層111の形成に用いられるセラミック粉末の平均粒径は、特に制限されないが、本発明の目的を達成するために調節されることがある。例えば、400nm以下に調節されることが可能であるが、本発明はこれに限定されない。

20

**【0026】**

カバー層112、113は、内部電極を含まないことを除いては、誘電体層111と同一材質及び構成を有することができる。

**【0027】**

また、カバー層112、113は、単一誘電体層または2つ以上の誘電体層を上記活性層の幅方向の両面にそれぞれさらに積層して形成されることが可能、基本的に物理的または化学的ストレスによる第1及び第2内部電極120、130の損傷を防止する役割をすることができる。

30

**【0028】**

第1及び第2内部電極120、130は、異なる極性を有する電極であり、セラミック本体110の内部に形成され、誘電体層111を介して対向するように配置される。

**【0029】**

このとき、第1及び第2内部電極120、130は、その間に配置された誘電体層111によって電気的に絶縁されることが可能である。

**【0030】**

このような第1及び第2内部電極120、130は、隣接する内部電極と重畳されて容量形成に寄与する容量部、及び上記容量部の一部が延長されてセラミック本体110の外部に露出するリード部を含む。

40

**【0031】**

上記リード部は、特に制限されないが、例えば、上記容量部を構成する内部電極の長さに比べてさらに短い長さを有することができる。

**【0032】**

また、第1及び第2内部電極120、130の厚さは、用途によって決定されることがある。例えば、セラミック本体110のサイズを考慮して0.2~1.0μmの範囲内にあるように決定することができるが、本発明はこれに限定されない。

**【0033】**

なお、第1及び第2内部電極120、130を形成する材料は、特に制限されない。例

50

えば、パラジウム（Pd）、パラジウム-銀（Pd-Ag）の合金などの貴金属材料、ニッケル（Ni）及び銅（Cu）のうち一つ以上の物質からなる導電性ペーストなどを用いて形成されることができる。

#### 【0034】

さらに、上記導電性ペーストの印刷方法は、スクリーン印刷法やグラビア印刷法などを用いることができるが、本発明はこれに限定されない。

#### 【0035】

本実施形態において、第1内部電極120は、長さ方向に離隔され、セラミック本体110の第1面S1に露出する第1及び第2リード部121、122を有し、第3及び第4面S3、S4から一定距離離隔されて形成されることができる。 10

#### 【0036】

また、第2内部電極130は、セラミック本体110の第1面S1に露出し、第1及び第2リード部121、122の間に第1及び第2リード部121、122とそれぞれ一定距離離隔されて形成された第3リード部131を有し、第3及び第4面S3、S4から一定距離離隔されるように配置されることがある。

#### 【0037】

このとき、第1から第3リード部121、122、131のうち少なくとも一つは、セラミック本体110の第1面S1と連結される部分の少なくとも片側の一部が傾斜延長部で形成されることがある。 20

#### 【0038】

また、上記傾斜延長部は、必要に応じて、直線ではなく曲線からなることもできる。

#### 【0039】

本実施形態において、第1及び第2リード部121、122は、第1内部電極120の容量部とセラミック本体110の第1面S1を連結する内側が、第1内部電極120から傾斜されるように延長された傾斜延長部、及びこの傾斜延長部からセラミック本体110の第1面S1に向かって垂直に延長されるように形成された垂直延長部を含むことができる。

#### 【0040】

このとき、第1及び第2リード部121、122は、必要に応じて、第1内部電極120の容量部とセラミック本体110の第1面S1を連結する外側も同様に、第1内部電極120から傾斜されるように延長された傾斜延長部、及びこの傾斜延長部からセラミック本体110の第1面S1に向かって垂直に延長されるように形成された垂直延長部を含むように構成することができる。 30

#### 【0041】

また、第3リード部131は、第2内部電極130の容量部とセラミック本体110の第1面S1を連結する片側が、第2内部電極130から傾斜されるように延長された傾斜延長部、及びこの傾斜延長部からセラミック本体110の第1面S1に向かって垂直に延長されるように形成された垂直延長部を含むことができる。

#### 【0042】

このとき、第3リード部131は、必要に応じて、第2内部電極130の容量部とセラミック本体110の第1面S1を連結する両側も同様に、第2内部電極130から傾斜されるように延長された傾斜延長部、及びこの傾斜延長部からセラミック本体110の第1面S1に向かって垂直に延長されるように形成された垂直延長部を含むように構成することができる。 40

#### 【0043】

ここで、第1または第2リード部121、122と第3リード部131の垂直延長部の間に設けられる第1スペース部の面積をSa、第1または第2リード部121、122と第3リード部131の傾斜延長部の間に設けられる第2スペース部の面積をSb、上記Sa + SbをStと規定するとき、0.383 Sa / Sb 12及び0.277 Sa / St 0.923であることができる。 50

**【0044】**

一般に、積層セラミック電子部品は、セラミック本体の長さ方向に相対する両面に外部電極が配置されることがある。

**【0045】**

しかし、この場合、外部電極に交流電圧が印加されると、電流経路が長くなつて電流ループがさらに大きく形成される可能性があり、誘導磁場のサイズが大きくなつてインダクタンスが増加するおそれがある。

**【0046】**

上記のような問題を解決すべく、本発明の一実施形態によると、電流経路を減少させるために、セラミック本体110の実装面である第1面S1に第1から第3外部電極141～143を配置することができる。 10

**【0047】**

この場合、第1及び第2外部電極141、142と第3外部電極143の間隔が小さいため、電流ループが減少してインダクタンスを低減させることができる。

**【0048】**

第1及び第2外部電極141、142は、セラミック本体110の面第1面S1に長さ方向に離隔されて形成され、第1及び第2リード部121、122とそれぞれ連結されて接続される。また、第3外部電極143は、セラミック本体110の第1面S1に第1及び第2外部電極141、142の間で第1及び第2外部電極141、142とそれぞれ一定距離離隔されて形成され、第3リード部131と連結されて接続される。 20

**【0049】**

また、第1から第3外部電極141～143は、静電容量を形成するために、第1及び第2内部電極120、130に対応するリード部とそれぞれ電気的に連結され、必要に応じて、セラミック本体110の第5及び第6面S5、S6の一部まで延長されてバンドが形成されることができる。

**【0050】**

このとき、第1から第3リード部121、122、131は、第1から第3外部電極141～143の内側にそれぞれ位置することができます。このため、第1から第3外部電極141～143の幅は、第1から第3リード部121、122、131の長さよりそれぞれ大きく形成されることができる。上記構造によると、第1から第3リード部121、122、131がセラミック本体110の第1面S1に露出しないため、セラミック本体110の第1面S1に別途の絶縁層を形成しなくてもよい。 30

**【0051】**

一方、このような第1から第3外部電極141～143は、3重層構造で形成されることができ、それぞれに対応する内部電極のリード部と接触して連結される第1から第3導電層141a～143a、第1から第3導電層141a～143aをそれぞれ覆うように形成された第1から第3ニッケル(Ni)めっき層141b～143b、及び第1から第3ニッケルめっき層141b～143bをそれぞれ覆うように形成された第1から第3すず(Sn)めっき層141c～143cを含む。

**【0052】**

第1から第3導電層141a～143aは、第1及び第2内部電極120、130と同一材質の導電性物質で形成されることができるが、これに限定されず、例えば、銅(Cu)や銀(Ag)、ニッケル(Ni)などの金属粉末で形成されることができる。また、上記金属粉末にガラスフリットを添加して製造された導電性ペーストを塗布してから焼成することで形成されることができる。 40

**【0053】****[実験例]**

本発明の実施例及び比較例による積層セラミックキャパシタは以下のように製作された。

。

**【0054】**

10

20

30

40

50

まず、チタン酸バリウム(  $BaTiO_3$  )などのパウダーを含んで形成されたスラリーをキャリアフィルム( carrier film )上に塗布及び乾燥して  $1.8 \mu m$  の厚さを有するように製造された複数のセラミックグリーンシートを設ける。

#### 【 0 0 5 5 】

次に、上記セラミックグリーンシート上にスクリーンを用いてニッケル内部電極用導電性ペーストを塗布し、上記セラミックグリーンシートの第1面に露出する第1及び第2リード部を有する第1内部電極、及び上記第1及び第2リード部と離隔されて上記セラミックグリーンシートの第1面に露出する第3リード部を有する第2内部電極を形成する。

#### 【 0 0 5 6 】

このとき、上記第1及び第2内部電極は、上記第1から第3リード部が上記第1及び第2内部電極から傾斜されるように延長された傾斜延長部、及び上記傾斜延長部から上記セラミック本体の実装面に向かって垂直に延長された垂直延長部を含むように形成する。

10

#### 【 0 0 5 7 】

その後、上記セラミックグリーンシートを約200層積層し、第1及び第2内部電極が形成されていないセラミックグリーンシートを幅方向の両面にさらに積層して積層体を製造し、この積層体を85において  $1000 kgf/cm^2$  の圧力条件で等圧圧縮成形(isostatic pressing)した。

#### 【 0 0 5 8 】

続いて、圧着されたセラミック積層体を個別のチップ状に切断し、切断されたチップは大気雰囲気において約230、60時間維持して脱バインダーを行った。

20

#### 【 0 0 5 9 】

次いで、約1,200において内部電極が酸化しないようにNi/NiO平衡酸素分圧より低い  $10^{-11}$  から  $10^{-10}$  atmの酸素分圧下の還元雰囲気で焼成してセラミック本体を設けた。

#### 【 0 0 6 0 】

焼成後の積層チップキャパシタのチップサイズは、長さ×幅( L × W )が約  $1.0 mm \times 0.5 mm$  ( L × W、1005サイズ)であった。ここで、製作公差は、長さ×幅( L × W )が  $\pm 0.1 mm$  内の範囲になるように設定した。

#### 【 0 0 6 1 】

次に、セラミック本体の第1面に第1及び第2内部電極のリード部にそれぞれ対応するように第1から第3外部電極を形成する工程を経て積層セラミックキャパシタを完成させた。その後、デラミネーション( Delamination )不良の発生有無及び等価直列インダクタンス( ESL )を測定するテストを行って表1に示した。各試験は、サンプル試料200個に対して行われた。

30

#### 【 0 0 6 2 】

【表1】

| No | So    | Sa    | Sb   | St    | Sa/St | St/So | Sa/Sb<br>ratio | Delamin<br>ation | ESL<br>[pH] |

|----|-------|-------|------|-------|-------|-------|----------------|------------------|-------------|

| 1  | 15120 | 0     | 7560 | 7560  | 0     | 0.5   | 0              | 50/200           | 37.8        |

| 2  | 15120 | 810   | 7155 | 7965  | 0.102 | 0.527 | 0.113          | 12/200           | 38.2        |

| 3  | 15120 | 1620  | 6750 | 8370  | 0.194 | 0.554 | 0.240          | 5/200            | 38.7        |

| 4  | 15120 | 2430  | 6345 | 8775  | 0.277 | 0.580 | 0.383          | 0/200            | 39.2        |

| 5  | 15120 | 3240  | 5940 | 9180  | 0.353 | 0.607 | 0.545          | 0/200            | 39.9        |

| 6  | 15120 | 4050  | 5535 | 9585  | 0.423 | 0.634 | 0.732          | 0/200            | 40.2        |

| 7  | 15120 | 4860  | 5130 | 9990  | 0.486 | 0.661 | 0.947          | 0/200            | 40.6        |

| 8  | 15120 | 5670  | 4725 | 10395 | 0.545 | 0.688 | 1.200          | 0/200            | 41.3        |

| 9  | 15120 | 6480  | 4320 | 10800 | 0.600 | 0.714 | 1.500          | 0/200            | 41.9        |

| 10 | 15120 | 7290  | 3915 | 11205 | 0.651 | 0.741 | 1.862          | 0/200            | 42.2        |

| 11 | 15120 | 8100  | 3510 | 11610 | 0.698 | 0.768 | 2.308          | 0/200            | 42.5        |

| 12 | 15120 | 8910  | 3105 | 12015 | 0.742 | 0.795 | 2.870          | 0/200            | 42.9        |

| 13 | 15120 | 9720  | 2700 | 12420 | 0.783 | 0.821 | 3.600          | 0/200            | 43.1        |

| 14 | 15120 | 10530 | 2295 | 12825 | 0.821 | 0.848 | 4.588          | 0/200            | 43.5        |

| 15 | 15120 | 11340 | 1890 | 13230 | 0.857 | 0.875 | 6.000          | 0/200            | 44.1        |

| 16 | 15120 | 12150 | 1485 | 13635 | 0.891 | 0.902 | 8.182          | 0/200            | 44.5        |

| 17 | 15120 | 12960 | 1080 | 14040 | 0.923 | 0.929 | 12.000         | 0/200            | 44.9        |

| 18 | 15120 | 13770 | 675  | 14445 | 0.953 | 0.955 | 20.400         | 0/200            | 46          |

| 19 | 15120 | 14580 | 270  | 14850 | 0.982 | 0.982 | 54.000         | 0/200            | 47.5        |

| 20 |       |       |      |       |       |       |                |                  |             |

| 30 |       |       |      |       |       |       |                |                  |             |

## 【0063】

ここで、上記第1または第2リード部と上記第3リード部の垂直延長部の間に設けられる第1スペース部の面積をS<sub>a</sub>、上記第1または第2リード部と上記第3リード部の傾斜延長部の間に設けられる第2スペース部の面積をS<sub>b</sub>、及び上記S<sub>a</sub>+S<sub>b</sub>をS<sub>t</sub>と規定する。

## 【0064】

上記表1を参照すると、全体のスペース部の面積S<sub>t</sub>に対するリード部の垂直延長部の間に設けられる第1スペース部の面積S<sub>a</sub>の比S<sub>a</sub>/S<sub>t</sub>が0.923以下のサンプル1～17の場合、ESLが45pH以下と低く、上記S<sub>a</sub>/S<sub>t</sub>が0.923を超過するサンプル18及び19の場合、ESLが45を超過したことが確認できた。

## 【0065】

したがって、上記S<sub>a</sub>/S<sub>t</sub>は、0.923以下であることが好ましい。

## 【0066】

また、リード部の傾斜延長部の間に設けられて形成される第2スペース部の面積S<sub>b</sub>に対する垂直延長部の間に設けられる第1スペース部の面積S<sub>a</sub>の比S<sub>a</sub>/S<sub>b</sub>が0.383未満のサンプル1～3の場合、デラミネーション不良が発生した。

10

20

30

40

50

## 【0067】

したがって、上記 S<sub>a</sub> / S<sub>b</sub> は、0.383 以上であることが好ましい。

## 【0068】

## [変形例]

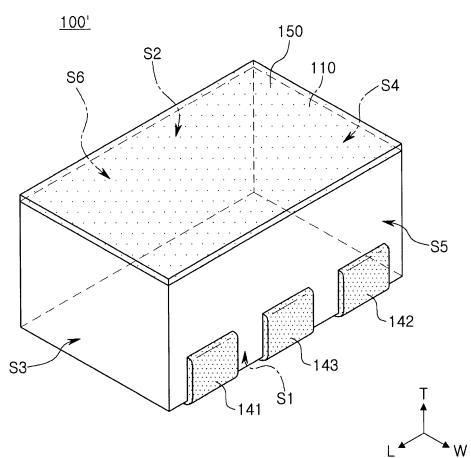

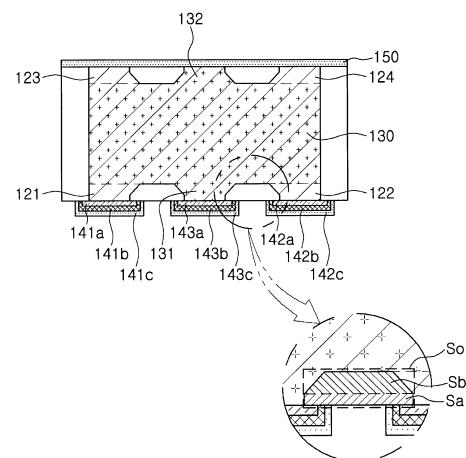

図5は本発明の他の実施形態による積層セラミックキャパシタを概略的に示した斜視図であり、図6は図5の積層セラミックキャパシタにおける外部電極を省略して示した分解斜視図であり、図7は図5の積層セラミックキャパシタを示した断面図である。

## 【0069】

ここで、セラミック本体110の構造は、上述した一実施形態と同一であるため、重複を避けるためにこれに関する具体的な説明を省略し、上述した一実施形態と異なる構造を有する第1及び第2内部電極120、130及び絶縁層150について詳細に説明する。

10

## 【0070】

図5から図7を参照すると、本実施形態の積層セラミックキャパシタ100'は、セラミック本体110の実装面に対向する第2面S2に絶縁層150が配置されることができる。

## 【0071】

第1内部電極120は、セラミック本体110の第2面S2に露出してセラミック本体110の第2面S2に形成された絶縁層150と接触する第4及び第5リード部123、124を有することができる。

## 【0072】

第2内部電極130は、第4及び第5リード部123、124の間に配置され、セラミック本体110の第2面S2に露出して絶縁層150と接触する第6リード部132を有することができる。

20

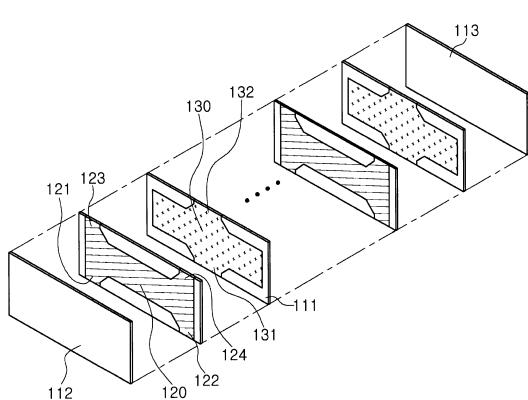

## 【0073】

図8は本発明のさらに他の実施形態による積層セラミックキャパシタを概略的に示した斜視図であり、図9は図8の積層セラミックキャパシタにおけるセラミック本体を示した斜視図であり、図10は図8の積層セラミックキャパシタにおける外部電極を省略して示した分解斜視図であり、図11は図8の積層セラミックキャパシタを示した断面図である。

## 【0074】

30

ここで、セラミック本体110の構造は、上述した一実施形態と同一であるため、重複を避けるためにこれに関する具体的な説明を省略し、上述した一実施形態と異なる構造を有する第4から第6外部電極144～146と第1及び第2内部電極120、130について具体的に説明する。

## 【0075】

図8から図11を参照すると、本実施形態の積層セラミックキャパシタ100"は、第4から第6外部電極144～146がセラミック本体110の第2面S2に第1から第3外部電極141～143と相対するように配置される。

## 【0076】

このとき、第4から第6外部電極144～146は、必要に応じて、セラミック本体110の第5及び第6面S5、S6の一部まで延長されるように形成されることがある。

40

## 【0077】

このような第4から第6外部電極144～146は、3重層構造で形成されることができ、それぞれに対応する内部電極のリード部と接触して連結される第4から第6導電層144a～146a、第4から第6導電層144a～146aを覆うように形成されたニッケル(Ni)めっき層144b～146b、及び第4から第6ニッケルめっき層144b～146bを覆うように形成されたすず(Sn)めっき層144c～146cを含む。

## 【0078】

第1内部電極120は、セラミック本体110の第2面S2に露出してセラミック本体110の第2面S2に形成された第4及び第5外部電極144、145とそれぞれ接続さ

50

れる第4及び第5リード部123、124を有することができる。

**【0079】**

第2内部電極130は、第4及び第5リード部123、124の間に配置され、セラミック本体110の第2面S2に露出して第6外部電極146と接触する第6リード部132を有することができる。

**【0080】**

上記の通り、積層セラミックキャパシタ100"の内部及び外部構造を上下対称構造に形成する場合、キャパシタの方向性を除去することができる。

**【0081】**

即ち、積層セラミックキャパシタ100"が上下対称構造に形成されるため、基板への実装時に実装面が逆になって発生する不良を防止することができる。 10

**【0082】**

したがって、積層セラミックキャパシタ100"の第1及び第2面S1、S2のいかなる面も実装面として提供されることができるため、積層セラミックキャパシタ100"を基板へ実装時に実装面の方向を考慮しなくてもよいという長所がある。

**【0083】**

このとき、第4から第6リード部123、124、132のうち少なくとも一つは、セラミック本体110の第2面S2と連結される部分の少なくとも片側の一部が傾斜延長部で形成されることがある。

**【0084】**

また、上記傾斜延長部は、必要に応じて、直線ではなく曲線からなることもできる。 20

**【0085】**

本実施形態において、第4及び第5リード部123、124は、第1内部電極120の容量部とセラミック本体110の第2面S2を連結する内側が、第1内部電極120から傾斜されるように延長された傾斜延長部、及びこの傾斜延長部からセラミック本体110の第2面S2に向かって垂直に延長されるように形成された垂直延長部を含むことができる。

**【0086】**

このとき、第4及び第5リード部123、124は、必要に応じて、第1内部電極120の容量部とセラミック本体110の第2面S2を連結する外側も同様に、第1内部電極120から傾斜されるように延長された傾斜延長部、及びこの傾斜延長部からセラミック本体110の第2面S2に向かって垂直に延長されるように形成された垂直延長部を含むように構成することができる。 30

**【0087】**

また、第6リード部132は、第2内部電極130の容量部とセラミック本体110の第2面S2を連結する片側が、第2内部電極130から傾斜されるように延長された傾斜延長部、及びこの傾斜延長部からセラミック本体110の第2面S2に向かって垂直に延長されるように形成された垂直延長部を含むことができる。

**【0088】**

このとき、第6リード部132は、必要に応じて、第2内部電極130の容量部とセラミック本体110の第2面S2を連結する両側も同様に、第2内部電極130から傾斜されるように延長された傾斜延長部、及びこの傾斜延長部からセラミック本体110の第2面S2に向かって垂直に延長されるように形成された垂直延長部を含むように構成することができる。 40

**【0089】**

ここで、第4または第5リード部123、124と第6リード部132の垂直延長部の間に設けられる第1スペース部の面積をSa、第4または第5リード部123、124と第6リード部132の傾斜延長部の間に設けられる第2スペース部の面積をSb、上記Sa + SbをStと規定するとき、0.383 Sa / Sb 12及び0.277 Sa / St 0.923であることができる。 50

**【 0 0 9 0 】**

一方、上記表1に示された第1から第3リード部の間に設けられた第1及び第2スペース部の寸法によるデラミネーション不良の発生有無、及びE S L値は、上記第4から第6リード部の間に設けられたスペース部の寸法にも同一に適用されることができる。

**【 0 0 9 1 】**

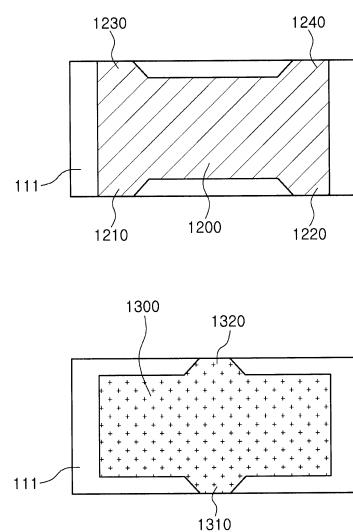

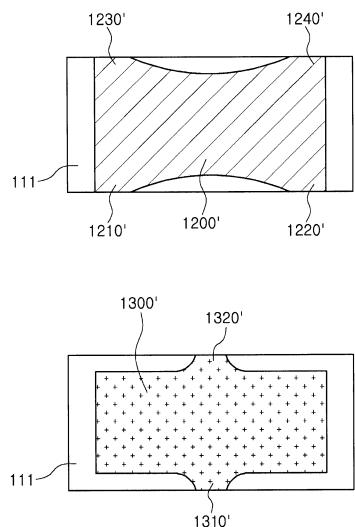

図12は本発明の積層セラミックキャパシタにおけるリード部の一形態を示した平面図である。

**【 0 0 9 2 】**

図12を参照すると、第1及び第2内部電極1200、1300の第1から第6リード部1210～1240、1310、1320とセラミック本体110の第1または第2面が連結される部分の少なくとも片側は、直線からなる傾斜延長部のみで構成されることができる。10

**【 0 0 9 3 】**

ここで、第1及び第2内部電極1200、1300と第1から第6外部電極141～146の他の形成構造は、上述した一実施形態と類似するため、重複を避けるためにこれに関する具体的な説明を省略する。

**【 0 0 9 4 】**

図13は本発明の積層セラミックキャパシタにおけるリード部の他の一形態を示した平面図である。

**【 0 0 9 5 】**

図13を参照すると、第1内部電極1200'の第1及び第2リード部1210'、1220'を互いに連結し、セラミック本体110の第1面S1と連結される片側は一つの曲線からなることができる。同様に、第1内部電極1200'の第4及び第5リード部1230'、1240'を互いに連結し、セラミック本体110の第2面S2と連結される片側は一つの曲線からなることができる。20

**【 0 0 9 6 】**

また、第2内部電極1300'の第3及び第6リード部1310'、1320'は、セラミック本体110の第1または第2面と連結される両側が曲線からなることができる。

**【 0 0 9 7 】**

ここで、第1及び第2内部電極1200'、1300'と第1から第6外部電極141～146の基本的な構造は、上述した一実施形態と類似するため、重複を避けるためにこれに関する具体的な説明を省略する。30

**【 0 0 9 8 】****[ 積層セラミックキャパシタの実装基板 ]**

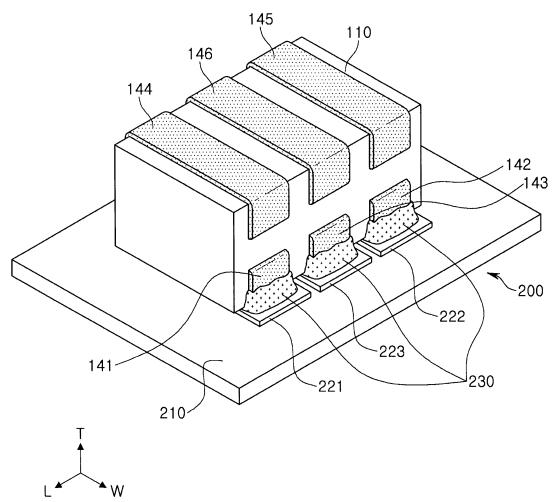

図14は図8の積層セラミックキャパシタが基板に実装された形状を示した斜視図であり、図15は図14の断面図である。

**【 0 0 9 9 】**

図14及び図15を参照すると、本実施形態による積層セラミックキャパシタの実装基板200は、積層セラミックキャパシタが実装される基板210、及び基板210の上面に離隔されるように形成された第1から第3電極パッド221、222、223を含む。40

**【 0 1 0 0 】**

このとき、積層セラミックキャパシタは、第1から第3外部電極141～143がそれぞれ第1から第3電極パッド221、222、223上に接触するように位置した状態で、はんだ230によって基板210と電気的に連結されることができる。

**【 0 1 0 1 】**

一方、図15における図面符号224は接地端子、図面符号225は電源端子を示す。

**【 0 1 0 2 】**

また、本実施形態は図8の積層セラミックキャパシタを実装する形態に図示して説明したが、本発明はこれに限定されず、一例として図1及び図5に示された積層セラミックキャパシタも類似した構造で基板に実装して実装基板を構成することができる。50

## 【0103】

以上、本発明の実施形態について詳細に説明したが、本発明の権利範囲はこれに限定されず、特許請求の範囲に記載された本発明の技術的思想から外れない範囲内で多様な修正及び変形が可能であるということは、当技術分野の通常の知識を有するものには明らかである。

## 【符号の説明】

## 【0104】

100、100'、100" 積層セラミックキャパシタ

110 セラミック本体

111 誘電体層

10

112、113 カバー層

120、1200、1200' 第1内部電極

121～124 第1、第2、第4、第5リード部

130、1300、1300' 第2内部電極

131、132 第3及び第6リード部

141～146 第1から第6外部電極

200 実装基板

210 基板

221、222、223 第1から第3電極パッド

230 はんだ

20

【図1】

【図2】

【図3】

【図5】

【図4】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図13】

【図14】

【図15】

---

フロントページの続き

(51)Int.Cl.

F I

H 01G 4/42 331

(72)発明者 キム、ジン

大韓民国、キョンギ - ド、スウォン - シ、ヨントン - グ、(マエタン - ドン)マエヨン - 口 15

0 サムソン エレクトロ - メカニックス カンパニーリミテッド. 内

(72)発明者 アーン、ヨン ギュ

大韓民国、キョンギ - ド、スウォン - シ、ヨントン - グ、(マエタン - ドン)マエヨン - 口 15

0 サムソン エレクトロ - メカニックス カンパニーリミテッド. 内

(72)発明者 リー、ピヨン ファ

大韓民国、キョンギ - ド、スウォン - シ、ヨントン - グ、(マエタン - ドン)マエヨン - 口 15

0 サムソン エレクトロ - メカニックス カンパニーリミテッド. 内

審査官 馬場 慎

(56)参考文献 実開昭60-048230 (JP, U)

特開2002-203736 (JP, A)

特開2009-021512 (JP, A)

特許第5319007 (JP, B2)

特開2011-091271 (JP, A)

特開2004-140211 (JP, A)

特開2002-299152 (JP, A)

特開2004-140183 (JP, A)

特開2013-106037 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01G 4 / 232

H 01G 2 / 06

H 01G 4 / 30

H 01G 4 / 35