(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-208837

(P2005-208837A)

(43) 公開日 平成17年8月4日(2005.8.4)

(51) Int.C1.<sup>7</sup>G06F 17/50

H01L 21/82

F 1

G06F 17/50 666Z

G06F 17/50 666C

H01L 21/82 C

H01L 21/82 D

H01L 21/82 T

テーマコード(参考)

5B046

5F064

審査請求 未請求 請求項の数 3 O L (全 15 頁)

(21) 出願番号

特願2004-13387 (P2004-13387)

(22) 出願日

平成16年1月21日 (2004.1.21)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 将行

最終頁に続く

(54) 【発明の名称】レイアウト検証装置

## (57) 【要約】

【課題】 半導体集積回路の特定領域が他領域とレイアウト条件が異なる場合においても、正確にレイアウト検証を行なう。

【解決手段】 電位追跡および情報選択手段(40)により、指定端子からグラウンド間の電位を追跡し、この追跡された経路における抵抗インスタンスを選択し、レイアウト上の抵抗の座標およびこの抵抗を含むウェル領域の座標を検出して特定領域を抽出する。この特定領域の抵抗素子およびウェル領域に対し特定用途デザインルール(31)を適用して、ウェル領域の余裕値検証等のレイアウト検証を実行する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

回路図データと前記回路データに基づいて作成されたレイアウトデータとの整合性を検証する整合性検証手段、

前記整合性検証手段からの整合性検証結果データから素子認識情報と素子接続情報とを抽出し、該抽出された情報に従って、指定されたノードから接地ノードの間に接続される素子で構成される対象領域を特定する領域特定手段、および

前記領域特定手段により特定された対象領域の素子に対して、別に設けられた特定領域検証ルールを適用して、前記対象領域の素子のレイアウトを検証する特定領域検証手段を備える、レイアウト検証装置。

**【請求項 2】**

前記領域特定手段は、

前記指定されたノードと接地ノードの間の電位追跡を行ない、該追跡経路における素子群を特定する手段と、

前記特定された素子群から抵抗素子と該抵抗素子が形成されるウェル領域とを選択する手段とを含み、

前記特定領域検証手段は、前記ウェル領域の対応の抵抗素子に対する余裕値を、前記特定領域検証ルールに従って検証する、請求項 1 記載のレイアウト検証装置。

**【請求項 3】**

前記特定領域検証ルールは、前記余裕値が大きい値に設定される、請求項 2 記載のレイアウト検証装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

この発明は、半導体集積回路のレイアウトの検証を行なう装置に関し、特に、多電源構成の半導体集積回路の内部回路の耐圧を検証するための装置に関する。より特定的には、この発明は、高電圧が印加される抵抗素子の耐圧を検証するための装置に関する。

**【背景技術】****【0002】**

I C (集積回路) および L S I (大規模集積回路) のレイアウト設計においては、回路図を参照しながら手作業でレイアウトデータを作成するかまたは C A D (コンピュータ支援設計ツール) を利用する自動配置配線技術を用いてレイアウトデータの作成 (レイアウトの設計) が行なわれる。

**【0003】**

このレイアウトデータの作成においては、適用される半導体プロセスに応じた標準規則 (以下、デザインルールと称す) が存在し、このデザインルールに従ったパターンを描く必要がある。この生成されたレイアウトデータの正当性の確認のためには、一般に、レイアウト検証装置が用いられる。このレイアウト検証装置は、生成されたレイアウトデータとデザインルールとの整合性の検証 (以下、D R C (デザイン・ルール・チェック) ; Design Rule Checking と称す) および回路図データと生成されたレイアウトデータとの整合性の検証 (以下、L V S (レイアウト・バーサス・スケマティック; Layout versus Schematic) と称す) を行なう。

**【0004】**

このようなレイアウト検証装置を用いて、レイアウトパターンの検証を行なう構成は、たとえば特許文献 1 (特許第 2708326 号公報) および特許文献 2 (特開 2003-31664 号公報) に示されている。

**【0005】**

特許文献 1 に示される構成においては、レイアウトデータから入力回路または出力回路領域を抽出し、この抽出された領域に対してサージ耐性検証ルールを適用して、サージ破壊耐性を検証する。

## 【0006】

特許文献2に示されるレイアウト検証装置においては、多電源半導体集積回路において、回路素子の接続を示すネットリストから等電位追跡を行なって、ネットの電位変化範囲を検出する。各ネットの電位差に従って配線間隔が設定され、この配線間隔に基づいて配線レイアウトが決定される。

【特許文献1】特許第2708326号公報

【特許文献2】特開2003-31664号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0007】

半導体集積回路を作成するにあたっては、要求される機能を満たすために、多電源構成が採用されることが多い。この多電源構成においては、複数種類の電源電圧が利用され、内部の回路が実現する機能に応じて電源電圧が振り分けられる。多電源構成の半導体装置においては、一般に、外部電源電圧を変換して必要な電圧レベルの内部電源電圧が生成されることが多い。このような多電源構成においては、製造プロセスについては、各電源ごとにプロセスに対して適用される設計ルールが異なる。したがって、1つのレイアウトデータ（1つの機能ロックに対するレイアウトのデータ）上で、複数のデザインルールを使い分けることが要求される。

## 【0008】

また、アナログ回路を有する半導体集積回路においては、高電圧の電源を使用する回路においても、抵抗の直列接続体により、高電圧を分圧して電源電圧として用いる場合がある。

## 【0009】

前述の特許文献1においては、ネットリストを参照してノード追跡を行うことにより、入出力回路を抽出し、この入出力回路においてサージ耐性が要求される素子（抵抗、ダイオード）および配線に対して、サージ破壊検証用ルールを参照して耐サージ破壊検証を行なう構成が示される。この特許文献1においては、特に絶縁破壊耐性が要求される入出力回路においては、専用の耐サージ破壊検証用ルールを適用することにより、集積回路内の内部回路レイアウトに対し一律にレイアウト検証が行なわれる場合の問題点、すなわち、入出力回路のレイアウトを表示装置上で目視により技術者が検証することによる不完全な検証という問題点、を解決することを図っている。

## 【0010】

しかしながら、この特許文献1においては、サージ破壊が生じる可能性のある入出力回路をパッドからのノード追跡により抽出し、この入出力回路の耐サージ破壊検証を行なっているだけである。電源ごとに適用されるデザインルールが異なる多電源構成において、各電源ごとにデザインルールとの整合性を検証することは行なわれていない。

## 【0011】

また、特許文献2においては、ネットリストと電源ネットとに基づいて等電位追跡を行ない、各ネットの電位を特定し、各電位に対して配線層を割当てた後、ネット間の電位差に基づいて配線間隔を決定する。この特許文献2は、配線材料に銅（Cu）が用いられる場合の高電位の印加による銅の染み出しなどを防止するために、配線間隔を最適化することを図る。

## 【0012】

しかしながら、この特許文献2に示される構成においては、多電源構成は示されているものの、各電源に接続される電位ネットの素子の耐圧特性等を個々に検証する構成については何ら示されていない。

## 【0013】

さらに、高電圧ノードと内部回路の動作電源ノードの間に抵抗素子を直列に接続して高電圧を分圧する構成の場合、レイアウト面積削減から高電圧よりも低い標準電圧用の抵抗素子を利用することが考えられる。このような場合、個々の抵抗素子に印加される電圧は

、高電圧よりも低いため、その耐圧は、標準電圧に対して保証されれば、使用環境下における耐圧が保証される。しかしながら、この抵抗素子が結合される電源ネットは、高電圧が供給されるネットである。たとえ仮に、レイアウト検証時において、対応の電源ネットの電圧レベルに応じてデザインルールを変更してレイアウト検証を行なうことが可能であっても、高電圧ネットに対しては高電圧のデザインルールが適用されることになり、この抵抗素子は、高電圧用ではなく標準電圧用の抵抗素子であるため、そのレイアウトパターン検証は行なうことができない。

#### 【0014】

また、抵抗素子は、面積削減の観点から、拡散抵抗で形成されることが多い。このような場合、抵抗素子を完全に他の素子から分離するためにウェル領域内に拡散抵抗が形成される。ウェル領域は、対応の抵抗素子に印加される電圧レベルにバイアスされる。この結果、ウェル領域と半導体基板との間の電位差は、標準電圧が用いられる場合よりも高くなり、リーク電流が大きくなる可能性がある。したがって、このような抵抗素子に対して、たとえ仮に標準電圧用のデザインルールを適用することが可能であったとしても、リーク電流特性などを保証することができないため、高電圧が印加される標準電圧用抵抗素子のレイアウト検証を行なうことができない。

#### 【0015】

それゆえ、この発明の目的は、回路素子の動作環境に応じたレイアウト検証を確実に行なうことのできるレイアウト検証装置を提供することである。

#### 【0016】

この発明の特定的な目的は、多電源構成の半導体集積回路における高電圧側素子のリーク電流の発生を防止することのできるレイアウト検証装置を提供することである。

#### 【課題を解決するための手段】

#### 【0017】

この発明に係るレイアウト検証装置は、回路図データとこの回路図データに基づいて作成されたレイアウトデータとの整合性を検証する整合性検証手段と、この整合性検証手段による整合性検証結果データから素子認識情報と素子接続情報とを抽出し、この抽出された情報に従って、指定されたノードから接地ノードの間に接続される素子で構成される対象領域を特定する領域特定手段と、この領域特定手段により特定された領域の素子に対して別に設けられた特定領域検証ルールを適用して、この特定領域の素子のレイアウトを検証する特定領域検証手段とを備える。

#### 【発明の効果】

#### 【0018】

指定されたノードから接地ノードへ至る経路の対象領域を電位追跡により特定することにより、特別な検証ルールを適用すべき領域を抽出することができ、この特定された領域の素子に対して、特定領域検証用ルールを適用して素子特性を検証することにより、特定領域の素子の動作環境に応じたレイアウトパターンの検証を自動的に行なうことができる。

#### 【0019】

特に、この高電圧ノードから接地ノードへ至る経路の素子から抵抗素子を抽出し、この抵抗素子のウェル領域の抵抗素子に対する余裕値を検証することにより、例えば、より低い電圧レベルの標準電圧用の抵抗素子を用いて高電圧を分圧して利用する場合においても、確実に、リーク電流を抑制するようにレイアウトパターンの検証を行なうことができる。

#### 【発明を実施するための最良の形態】

#### 【0020】

##### [実施の形態1]

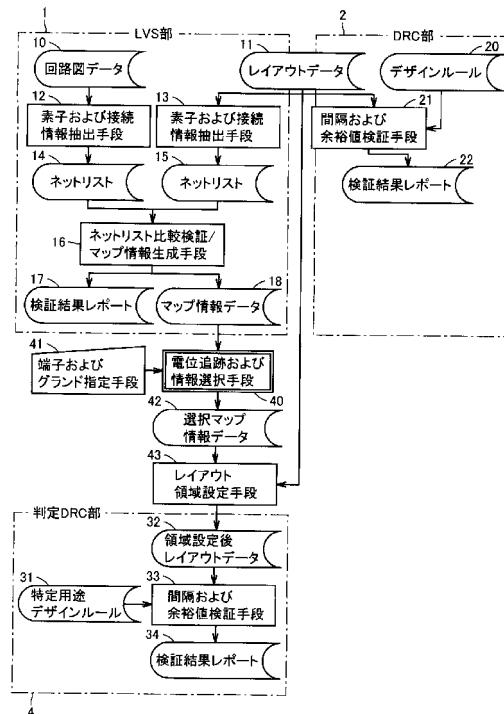

図1は、この発明の実施の形態1に従うレイアウト検証装置の構成を概略的に示す図である。図1において、レイアウト検証装置は、回路図データ10およびレイアウトデータ11に従って、これらの回路図データ10が記載する回路図が、レイアウトデータ11が

記述するレイアウトと整合しているかを判定する L V S 部 1 と、レイアウトデータ 1 1 とデザインルール 2 0 とに従って、この作成されたレイアウトデータ 1 1 が、デザインルール 2 0 が規定するルールに従ってパターンが描かれているかを検証する D R C 部 2 と、回路図データ 1 0 に記載される回路の特定の領域のレイアウトパターンが、この特定領域に對して定められた特定用途デザインルール 3 1 が規定するルールに従ったパターンで描かれているかを検証する特定 D R C 部 4 を含む。

【 0 0 2 1 】

回路図データ 1 0 は、意図する回路を構成するトランジスタ、抵抗素子、電源ノードを特定する情報およびこれらの構成要素の接続配線を示す情報（ネットリスト）を含む。レイアウトデータ 1 1 は、この回路図データ 1 0 に基づいて、たとえば自動配置配線技術に従って生成されたレイアウトについての情報を含む。すなわち、このレイアウトデータ 1 1 は、回路図データ 1 0 により記載される回路の構造を規定するレイアウトパターンデータと、各レイアウトパターンにおいて接続される素子の識別子および接続情報を含む。すなわち、このレイアウトデータ 1 1 は、レイアウトパターンデータと素子情報と回路接続情報とで構成される。

【 0 0 2 2 】

デザインルール 2 0 は、このレイアウトデータ 1 1 が描くレイアウトパターンが従うルールを規定し、配線間隔、エッジの形状などの規則を含む。デザインルール 2 0 は、記述される半導体集積回路が、多電源構成の場合、各電源毎に規定されるデザインルールを含んでもよい。デザインルール 2 0 は、半導体集積回路装置に対して一律に適用される。

【 0 0 2 3 】

L V S 部 1 は、回路図データ 1 0 から素子情報を抽出して、素子の接続情報をネット単位でリストとして表わすネットリスト 1 4 を生成する素子および接続情報抽出手段 1 2 と、レイアウトデータ 1 1 から素子情報を抽出して、このレイアウトにおけるネット情報をリストの形で表わすネットリスト 1 5 を生成する素子および接続情報抽出手段 1 3 と、これらのネットリスト 1 4 および 1 5 を参照して、対応する回路情報および接続情報を検出し、両ネットリスト 1 4 および 1 5 の整合性を判定するとともに、回路図上の素子および接続情報とレイアウト上の素子および接続情報の対応を表わすマップ情報データ 1 8 を生成するネットリスト比較検証 / マップ情報生成手段 1 6 を含む。

【 0 0 2 4 】

ネットリスト比較検証 / マップ情報生成手段 1 6 からは、また、生成されたレイアウトパターンと元の回路図データとの整合性の検証結果を示す検証結果レポート 1 7 が生成されて、たとえば図示しない表示装置上に表示されるかまたはプリンタなどを用いてプリントアウトされる。

【 0 0 2 5 】

D R C 部 2 は、レイアウトデータ 1 1 をデザインルール 2 0 に従って検証する間隔および余裕値検証手段 2 1 を含む。この間隔および余裕値検証手段 2 1 は、レイアウトデータ 1 1 により記述された各レイアウトパターンにおける間隔および余裕値が、デザインルール 2 0 に規定されたルールに従っているかを検証する。具体的に、間隔および余裕値検証手段 2 1 は、配線間の間隔、また拡散領域間の間隔、分離領域（ウェル領域）間の間隔、およびウェル領域端部と拡散領域端部との間の距離（余裕値）などを検証する。この間隔および余裕値検証手段 2 1 の検証結果は、また検証結果レポート 2 2 として出力される。

【 0 0 2 6 】

この検証結果レポート 1 7 および 2 2 に基づいて、レイアウトパターンの不良（エラー）などが存在する場合には、再び手作業または自動配置配線技術に従って回路図データに基づいて、レイアウトの作成が行なわれる。

【 0 0 2 7 】

L V S 部 1 および D R C 部 2 においては、半導体回路の全領域に対し共通に、回路図データとレイアウトデータの整合性および回路レイアウトパターンとデザインルールとの整

10

20

30

40

50

合性の検証が実行される。デザインルール 20 は、レイアウトパターン上における素子の形成幅および素子間隔等の幾何学的な基準値が定義されたルールである。このデザインルール 20 は、多電源構成においては、各電源ごとに異なるものの、電源が共通な回路に対して共通のデザインルールが適用される。

【 0 0 2 8 】

本実施の形態 1 においては、他の回路の使用条件と異なる特定の条件下で使用される特定回路領域（素子）を抽出し、この特定回路領域のレイアウト検証のために、デザインルール 20 と別に設けられた専用の特定用途デザインルール 31 を適用する。特定用途デザインルール 31 は、特定回路領域の素子の間隔および余裕値など、回路特性を保証する上で必要とされる幾何学的形状の基準値を規定する。

10

【 0 0 2 9 】

この特定領域のレイアウト検証を実行するために、特定領域を設定する必要がある。この特定領域設定のために、端子およびグラウンド指定手段 41 より指定された端子とグラウンド（接地ノード）との間の電位を、マップ情報データ 18 に基づいて追跡し、マップ情報データ 18 から、指定された端子およびグラウンド間の素子情報および接続情報を抽出する電位追跡および情報選択手段 40 と、この電位追跡および情報選択手段 40 からの選択マップ情報データとレイアウトデータ 11 とに従って、検証対象のレイアウト領域を設定するレイアウト領域設定手段 43 とが設けられる。

【 0 0 3 0 】

レイアウト領域設定手段 43 により、特定領域のレイアウトデータ（領域設定後レイアウトデータ）32 が生成されて出力される。

20

【 0 0 3 1 】

特定 DRC 部 4 は、このレイアウト領域設定手段 43 により設定された特定領域内のレイアウトデータ（領域設定後レイアウトデータ）32 に対し特定用途デザインルール 31 を適用し、レイアウトパターンの間隔および余裕値を検証する間隔および余裕値検証手段 33 を含む。この間隔および余裕値検証手段 33 から、設定された領域に対して特定用途のデザインルール 31 を適用した検証結果を示す検証結果レポート 34 が出力される。

【 0 0 3 2 】

この特定 DRC 部 4 において特定用途デザインルール 31 に従って特定の領域のレイアウトパターンの整合性を検証することにより、特定領域において他回路の素子と異なるレイアウト条件が課せられる場合においても、正確にレイアウト検証を自動的に行うことができる。たとえば抵抗素子について、電圧レベルの低い標準電圧用の抵抗素子を、高電圧供給ノードに接続される抵抗素子に対して利用する場合においても、その抵抗素子に対するウェル領域の余裕値（抵抗素子からウェル領域端部までの距離）を広く取ることにより、高電圧印加時におけるウェル領域の PN 接合におけるリーク電流を低減することができる。これにより、耐圧特性が保証される場合において、さらにリーク電流の低減が要求され、このため、特定領域のレイアウト条件が他の回路と異なる場合においても、この様な特定領域のレイアウトパターンの自動検証を行なうことができる。

30

【 0 0 3 3 】

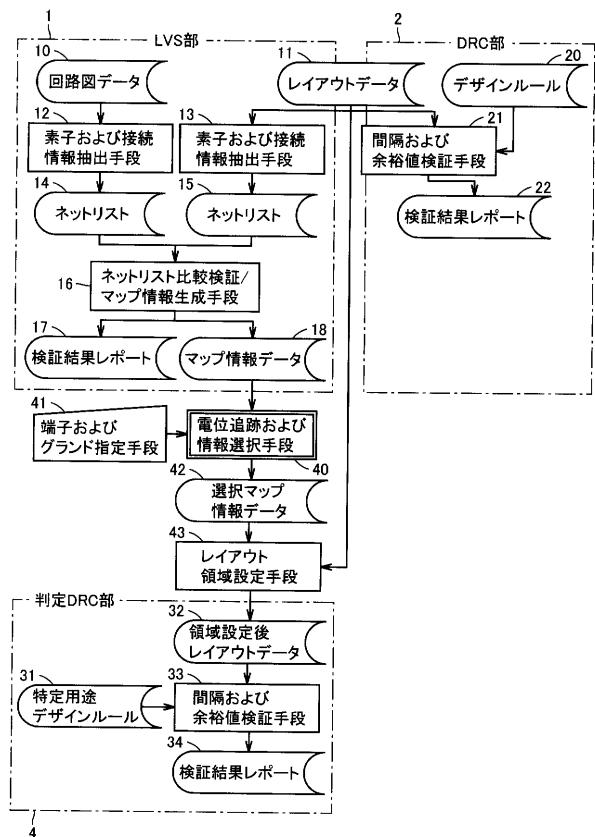

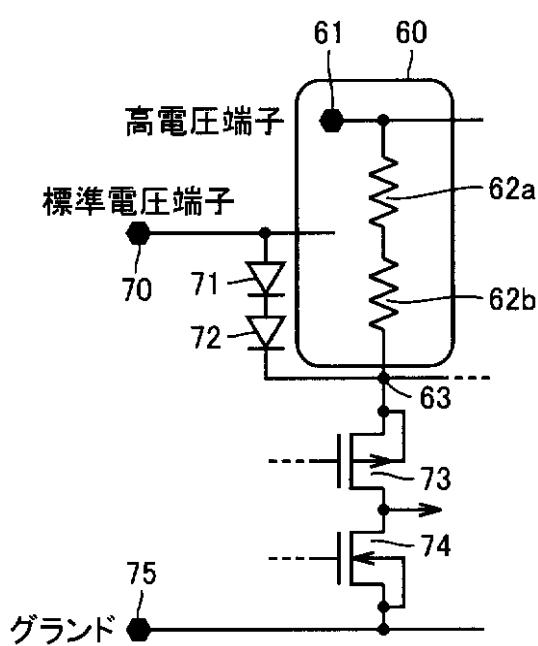

図 2 は、図 1 に示す電位追跡および情報選択手段 40 の構成を概略的に示す図である。図 2 において、電位追跡および情報選択手段 40 は、マップ情報データ 18 から、端子およびグラウンド指定手段 41 により指定された端子およびグラウンド間の電位を追跡して、マップ情報データ 18 から素子の接続情報を選択する指定端子 - グラウンド間電位追跡手段 50 と、この指定端子 - グラウンド間電位追跡手段 50 の追跡中に通過された素子インスタンスから抵抗インスタンスを選択する抵抗インスタンス選択手段 51 と、選択された抵抗インスタンスのレイアウト上の座標を抽出するレイアウト上座標抽出手段 52 と、選択抵抗を包含するウェル領域のレイアウト上の位置を抽出するウェル座標抽出手段 53 を含む。

【 0 0 3 4 】

指定端子 - グラウンド間電位追跡手段 50 は、指定された端子から、順次その電位が低

50

下するようにグラウンドまで接続情報を追跡し、その追跡経路に存在する素子インスタンスを抽出し、その素子の認識および接続ノードを抽出する。追跡経路においてトランジスタ素子が存在するときには、トランジスタの導通時には、そのソース（エミッタ）およびドレイン（コレクタ）が電気的に結合されるため（電流が流れるため）、このトランジスタを通過するように経路の追跡が行われる。

【0035】

抵抗インスタンス選択手段51は、抽出された素子インスタンスから抵抗インスタンスのみを選択する。レイアウト上座標抽出手段52が、選択された抵抗素子の素子情報に従ってマップ情報を参照し、レイアウトデータから対応の素子情報を選択して、その素子情報に付随するレイアウト上の位置情報（座標）を抽出する。

10

【0036】

ウェル座標抽出手段53は、また、選択された抵抗素子の接続情報からマップ情報を参照し、この選択された抵抗素子に接続されるウェル領域をレイアウトデータから抽出して選択抵抗を包含するウェル領域を検索し、検索されたウェル領域情報に含まれる位置情報を抽出して、ウェル座標情報を抽出する。

【0037】

ウェル座標抽出手段53から、対応の抵抗インスタンスの座標およびウェル座標（抵抗接続ノードおよびウェル識別ノード）で構成される選択マップ情報データ42が生成される。この選択マップ情報データ42に基づいて、レイアウト上の領域が設定される。これにより、特定領域の抵抗素子および対応のウェル領域のレイアウトパターンのみを抽出して、レイアウト検証を行なうことができる。以下、具体的なレイアウト検証動作について説明する。

20

【0038】

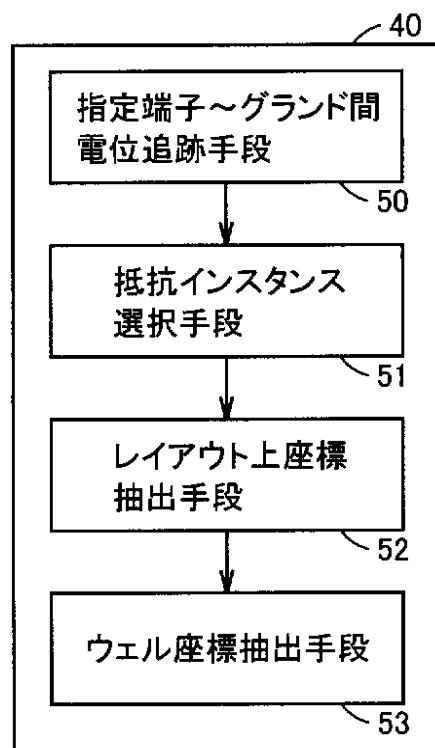

図3は、多電源半導体集積回路の特定領域を含む部分の構成の一例を示す図である。図3において、半導体集積回路は、高電圧を受ける高電圧端子61とノード63の間に直列に接続される抵抗素子62aおよび62bと、高電圧端子61に供給される高電圧よりも低い標準電圧を受ける標準電圧端子70とノード63の間に直列に接続されるダイオード素子71および72と、ノード63と接地（グラウンド）75の間に接続されるPチャネルMOSトランジスタ73およびNチャネルMOSトランジスタ74を含む。

30

【0039】

この高電圧端子61には、最大値がたとえば40Vの高電圧が供給され、標準電圧端子70へは、例えば12Vの電圧が供給される。

【0040】

ダイオード素子71および72が、標準電圧よりもそれぞれの順方向降下電圧 $V_f$ の2倍低い電圧レベルに、ノード63の下限電圧レベルをクランプする。

【0041】

MOSトランジスタ73および74は、図示しないドライブ回路により導通または非導通状態に設定される。ノード63が、これらのMOSトランジスタ73および74で構成される出力ドライブ回路の動作電源ノードとして機能する。MOSトランジスタ73および74は、例えば、コンバータまたはインバータなどの出力ドライブ回路を構成し、MOSトランジスタ73の導通時に、MOSトランジスタ74が非導通状態とされ、それらのMOSトランジスタ73および74の接続ノードから次段に対する信号が出力される。この場合、ノード63の電圧レベルが、MOSトランジスタ73の駆動電流と抵抗素子61および62の抵抗値とにより設定される（ダイオード素子71および72が非導通状態のとき）。

40

【0042】

抵抗素子62aおよび62bとして、標準電圧用の抵抗素子が利用されても、抵抗素子個々の全体には高電圧は印加されないため、その耐圧は十分保証される。MOSトランジスタ73および74には、ソースまたはドレインを構成する不純物領域に高電圧が供給されるため、十分高い耐圧特性を有するようにそのレイアウトパターンが設定される。

50

## 【0043】

この抵抗素子 62a および 62b が、拡散抵抗で構成される場合、抵抗本体部（ボディ部）においては、高電圧は印加されないものの、この拡散抵抗を形成するウェル領域の端部における高電界によりリーク電流が生じる。このウェル領域の P N 接合の逆バイアス電圧によるリーク電流を低減するためには、ウェル領域（分離領域）の P N 接合に印加される電圧を、標準電圧使用時と同程度以下に設定する必要がある。そのため、抵抗素子 62a および 62b に対して標準電圧用抵抗素子を利用する場合に、特別なパターン設計ルール（特定用途デザインルール）を適用して、ウェル領域の接合に印加される電圧を低減して、ウェル領域のリーク電流を低減する。

## 【0044】

10

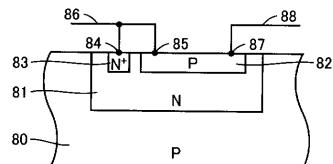

図 4 は、図 3 に示す特定領域 60 に含まれる抵抗素子 62a および 62b に使用される抵抗素子の断面構造を概略的に示す図である。図 4において、抵抗素子は、半導体基板領域 80 の表面に形成されるウェル領域 81 と、このウェル領域 81 の表面に形成される拡散領域（不純物領域）82 と、ウェル領域 81 と同一導電型の不純物領域 83 を含む。図 4 に示す構成においては、半導体基板領域 80 および拡散領域 82 は、P 型を有し、ウェル領域 81 および不純物領域 83 は、N 型を有する。

## 【0045】

20

拡散領域 82 は、その両端のコンタクト 85 および 87 を介して、銅またはアルミニウムの導体配線 86 および 88 にそれぞれ接続される。この導体配線 86 は、またコンタクト 84 を介して N 型不純物領域 83 に接続される。導体配線 86 は、導体配線 88 よりも高電位の電圧を受けるノードに結合される。不純物領域 83 により、ウェル領域 81 の電圧が、この導体配線 86 上の電圧レベルにバイアスされる。ウェル領域 81 により、拡散層 82 で構成される抵抗素子が、他の回路素子から分離され、その設定された抵抗値で、導体配線 86 から導体配線 88 に電圧を伝達する。

## 【0046】

半導体基板領域 80 は、図示しない経路を介して所定電圧レベルにバイアスされる。

## 【0047】

30

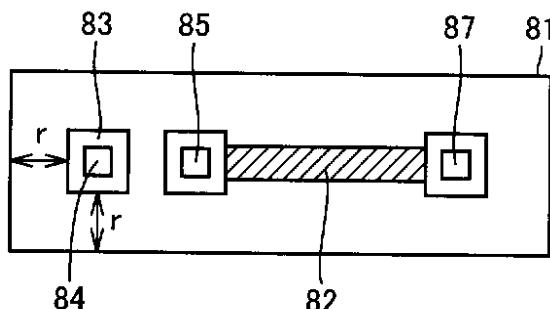

図 5 は、図 4 に示す抵抗素子の平面レイアウトを概略的に示す図である。図 5 に示すように、抵抗ボディ部を構成する拡散領域 82 が、コンタクト 85 および 87 の間に配置される。この抵抗ボディ部を構成する拡散領域 82 は、ウェル領域 81 内に形成される。コンタクト 85 に隣接する領域において、ウェル領域 81 に接続される不純物領域 83 が配置され、この不純物領域 83 はコンタクト 84 により図示しない導体配線に接続される。このコンタクト領域（不純物領域 83）端部とウェル領域 81 の端部との間には距離  $r$  が設けられる。

## 【0048】

40

ウェル領域 81 は、半導体で構成され、ウェル抵抗を有する。この距離  $r$  が大きければ、ウェル領域 81 の端部における P N 接合に印加される電圧が小さくなり、逆方向リーク電流を低減できる。しかしながら、この距離  $r$  が、コンタクト領域（不純物領域 83 およびコンタクト 84）に印加される電圧を十分緩和することができない場合、ウェル領域 81 の P N 接合に大きな逆バイアス電圧が印加され、逆方向リーク電流が増大する。したがってこの場合、距離  $r$  を、印加される電圧に応じて調整し、ウェル領域 81 のリーク電流を低減する。

## 【0049】

50

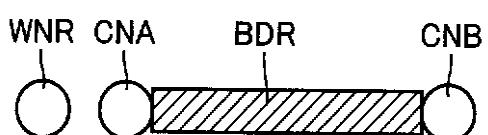

図 6 は、抵抗素子についての情報の構成を示す図である。図 6 において、抵抗素子情報は、抵抗素子の本体（ボディ部）を示す本体情報 BDR と、この抵抗素子の接続ノードを示す接続情報 CNA および CNB と、抵抗素子が形成されるウェル領域への接続を示すウェル接続情報 WNR を含む。この図 6 に示す抵抗素子情報は、それぞれ回路図データおよびレイアウトデータとして生成され、レイアウトデータにおいては、抵抗素子本体情報 BDR は、図形 ID により識別される。本体情報 BDR により拡散領域 82 の位置情報および抵抗素子の認識情報（ID）が規定される。

## 【0050】

接続情報CNAおよびCNBにより、コンタクト85および87の位置情報が規定され、ウェル接続情報WNRにより、抵抗素子がウェル領域に接続する位置が規定される。

## 【0051】

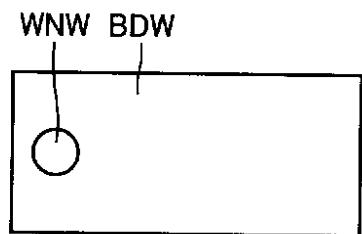

図7は、ウェル情報の構成を概略的に示す図である。図7において、このウェル領域情報は、ウェル領域を示すウェル領域指示情報BDWと、このウェル領域に対するバイアス電圧を供給するコンタクト領域を示すウェルコンタクト情報WNWを含む。このウェル情報において、ウェルコンタクト情報WNWと、抵抗素子のウェルコンタクト情報WNRが、同一ノードを示すときには、この抵抗素子が、対応のウェル領域内に形成されることが示される。

10

## 【0052】

ウェル領域情報は、レイアウトデータにおいては、このウェル領域の四隅の位置を示す情報が含まれる。また、図6に示す抵抗素子の抵抗情報および図7に示すウェル領域情報においては、多電源構成においては、供給される電圧を特定する電位番号情報がそれぞれ含まれる。

## 【0053】

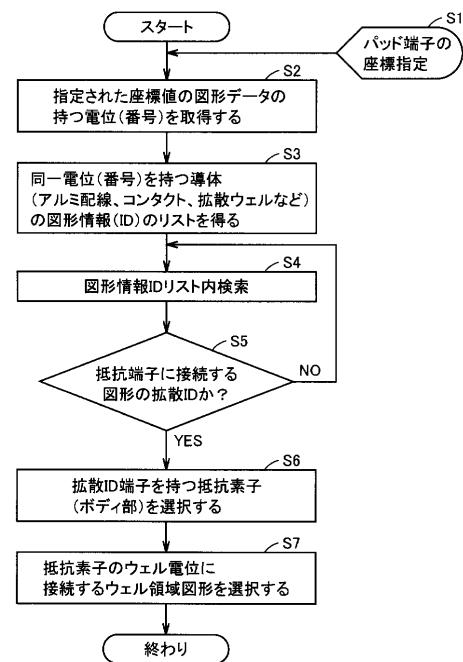

図8は、図3に示す特定領域60を抽出するときの図1に示す電位追跡および情報選択手段40の動作を示すフロー図である。以下、図8を参照して、図1および図2に示す電位追跡および情報選択手段の動作について、図3を併せて参照して説明する。

20

## 【0054】

まず、図1に示す端子およびグラウンド指定手段41から、選択対象のパッド端子の座標情報が入力され、対象パッドが指定される(ステップS1)。この場合、図3に示す高電圧端子61のレイアウト上の座標が指定される。

## 【0055】

このパッドの指定により、図2に示す指定端子-グラウンド間電位追跡手段50は、指定されたパッドの座標位置に配置された図形データを参照し、その図形データが有する電位番号を取得する(ステップS2)。この電位番号の取得により、図3に示す高電圧端子61に供給される高電圧を受ける経路が選択対象として設定される。

## 【0056】

この指定端子-グラウンド間電位追跡手段50は、取得した電位番号に従って、同一電位番号を有する導体の図形情報IDを検索して、その図形情報IDのリストを形成する。同一電位を有する導体は、アルミニウム配線、コンタクト、拡散領域、およびウェル領域であり、これらは、すべて図形IDにより、その種類が特定される。

30

## 【0057】

このステップS3において、指定端子-グラウンド間電位追跡手段50は、図3に示す高電圧端子61から、この高電圧を供給される抵抗素子62aおよび62bと、MOSトランジスタ73および74の経路を、電位番号および接続情報に従って追跡し、接地ノード75で、その追跡を終了する。この追跡の終了は、例えば以下のようにして実行される。対象の導体に対する情報として、高電圧識別番号とともに接地電位を示す電位番号が含まれているときに、この接地電位識別番号の検出により、1つの経路の電位追跡が終了する。

40

## 【0058】

この追跡経路における抵抗素子62aおよび62bとMOSトランジスタ73および74それぞれに付随する配線、コンタクトおよび拡散領域に対するIDおよび接続情報が、レイアウトデータのリストとして生成される。パッド(端子)61から高電圧を受ける経路を、全て追跡し、各経路において、高電圧供給ノードから接地ノードに至る経路におけるインスタンスのリストが作成される。

## 【0059】

次いで、抵抗インスタンス選択手段51は、この生成された図形情報IDリストを検索し、抵抗インスタンスを選択する(ステップS4)。すなわち、この抵抗インスタンス選

50

択手段 5 1 は、生成された図形情報 I D リストを検索し、回路図データ上に記述された抵抗端子（図 6 の端子情報 C N A および C N B ）に接続する図形情報内の拡散 I D を検出する（ステップ S 5）。このステップ S 5 における拡散 I D の検出動作は、図形情報 I D リスト内で、抵抗端子に接続される拡散 I D が全て検索されるまで繰返し実行される。この検索操作により、回路図上で記述された、図 3 に示す抵抗素子 6 2 a および 6 2 b が検出される。

#### 【 0 0 6 0 】

次いで、レイアウト上座標抽出手段 5 2 は、ステップ S 5 において拡散 I D が検出されると、その拡散 I D に付された端子を有する抵抗素子（図 6 のボディ部 B D R ）を、回路図データ上で選択し、またマップ情報データを検索してレイアウトデータから対応の抵抗素子のボディ部情報を抽出して、レイアウト上での抵抗素子の座標を抽出する（ステップ S 6）。

#### 【 0 0 6 1 】

次いで、ウェル座標抽出手段 5 3 は、この選択された抵抗素子に付随するウェルコンタクト情報 W N R を参照し、図形情報の I D リスト内において、このウェルコンタクト情報 W N R と同一コンタクト番号を有するウェルコンタクト番号 W N W を有するウェル領域の図形を選択する（ステップ S 7）。このウェル領域の図形情報には、レイアウトデータにおいて、このウェル領域の四隅の座標情報が含まれ、検索されたウェル領域のレイアウト上での座標が抽出される。

#### 【 0 0 6 2 】

これらの一連の処理動作により、図 3 に示す特定領域 6 0 における選択された素子に対する選択マップ情報データ 4 2 が生成され、図 1 に示すレイアウト領域設定手段 4 3 は、この選択マップ情報データ 4 2 に基づいて、レイアウトデータ 1 1（図 1 参照）から特定領域 6 0 に対応する領域のレイアウトデータ（3 2）を生成する。

#### 【 0 0 6 3 】

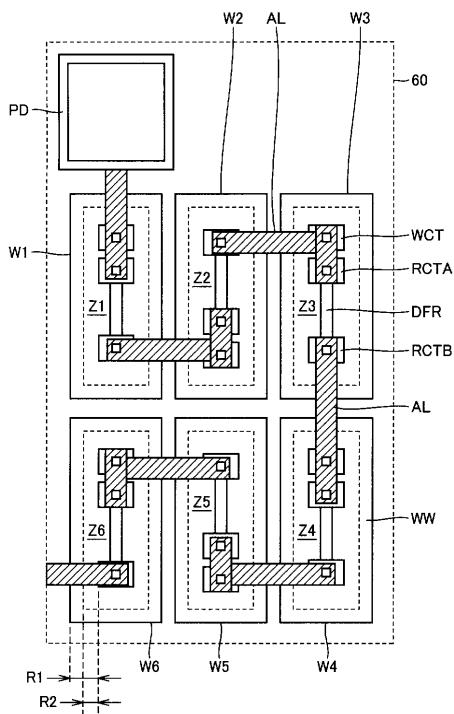

図 9 は、抵抗素子 6 2 a および 6 2 b のレイアウトの一例を示す図である。この図 9 に示すレイアウトにおいては、1 つの抵抗素子 Z 3 に対して形成される領域について参照符号を代表的示す。この領域設定後レイアウトデータ 3 2 により、図 9 に示すように、特定領域 6 0 に含まれる高電圧端子に接続される抵抗素子 6 2 a および 6 2 b のレイアウトパターンについてのデータが抽出される。

#### 【 0 0 6 4 】

図 9においては、高電圧端子 6 1 に対応するパッド P D に直列に、抵抗素子 Z 1 - Z 6 がこの順に接続される。これらの抵抗素子 Z 1 - Z 6 は、同様の構成を有し、高電圧使用時、ウェル領域 W 1 内に形成される抵抗ボディ領域（拡散領域）D F R と、拡散領域 D F R に接続されるコンタクト領域 R C T A および R C T B に接続される配線 A L を含む。また、このコンタクト領域 R C T A に隣接してウェルコンタクト領域 W C T が配置される。配線 A L が、また、ウェルコンタクト領域 W C T に接続され、対応のウェル領域 W に、バイアス電圧を供給する。ウェル領域 W 1 に形成される抵抗素子 Z 1 が、図 3 に示す抵抗素子 6 2 a に対応し、ウェル領域 W 2 - W 6 それぞれに形成される抵抗素子 Z 2 - Z 6 の合成抵抗により抵抗素子 6 2 b が形成される。

#### 【 0 0 6 5 】

抵抗ボディ領域（拡散領域）D F R が、図 6 に示すボディ領域情報 B D R により特定され、また拡散 I D により図形情報として特定される。コンタクト領域 R C T A および R C T B は、不純物領域とコンタクト孔を含むが、同様、図形情報 I D において拡散 I D により識別され、また、抵抗端子情報がその拡散 I D に付されており、これらの拡散 I D および抵抗端子情報により特定される。この抵抗端子情報は、回路図上で抵抗素子 6 2 b を記述するときに、5 個の抵抗素子（Z 2 - Z 6）を記述し、各抵抗素子の端子情報がまた回路図上で記述され、抵抗素子端子に対応する拡散 I D に、この抵抗端子情報がリンクされていてもよい。

#### 【 0 0 6 6 】

10

20

30

40

50

ウェルコンタクト領域 W C T が、図 6 に示すウェルコンタクト情報 W N R および図 7 に示すウェルコンタクト情報 W N W により特定され、拡散 I D により指定される抵抗ボディ領域 D F R の情報に付随するウェル電位情報に基づいて、対応のウェル領域の図形 (W 3) が選択される。このウェル電位情報が、追跡経路における電位を指定しており、この経路において抵抗素子を包含するウェル領域は、標準電圧を受ける場合に較べて、サイズが大きくされている。

#### 【 0 0 6 7 】

上述のように、特定の電圧が供給されるノードを指定し、この特定ノードから接地ノードの間の電位を順次追跡し、その経路における図形情報を検索することにより、拡散抵抗素子および対応のウェル領域の図形情報を得ることができ、レイアウトデータ 1 1 から、図 9 に示すような特定領域 6 0 内のレイアウトデータに基づいてレイアウトパターンデータを表示することができる。

#### 【 0 0 6 8 】

図 1 に示す特定 D R C 部 4 は、この特定領域 6 0 のレイアウトパターンに対し、特定用途デザインルール 3 1 を適用し、ウェル領域 W 1 から W 6 それぞれの間隔または余裕値を検証する。すなわち、図 1 に示す間隔および余裕値検証手段 3 3 は、領域設定後レイアウトデータ 3 2 に従って、この特定領域 6 0 に含まれるウェル領域 W 1 - W 6 それぞれについて、対応の抵抗素子のコンタクト領域 R C T A および R C T B の位置情報を抽出し、このウェル領域の抽出された位置情報と、コンタクト領域 R C T A および R C T B の位置情報とに基づいて、このコンタクト領域 R C T A および R C T B とウェル領域との間隔が、基準値 R 1 以上あるかを検証する。この余裕値の検証時においては、抵抗素子の拡散 I D 端子の位置情報と、ウェル領域の位置情報とに基づいて、水平成分の減算により、その余裕値が基準値 R 1 を満たしているかを検証することができる。

#### 【 0 0 6 9 】

この特定領域において、抵抗素子 Z 1 - Z 6 が、標準電圧を受ける場合、ウェル領域 W 1 - W 6 は、それぞれ、破線で示すウェル領域 W W のサイズに設定され、その余裕値が、間隔 R 2 に設定される。抵抗素子ボディ部 D F R の耐圧特性は、標準電圧に対する耐圧特性を満たす。特定用途デザインルール 3 1 を適用することにより、標準電圧用抵抗素子を用いてその対応のウェル領域 W 1 - W 6 の余裕値を大きくすることができ、ウェル領域端部における電圧を低減することができ、応じて、リーク電流を低減することができる。

#### 【 0 0 7 0 】

ウェル領域 W 1 - W 6 それぞれについて、基準値 R 1 が満たされているかの検証結果が、検証結果レポート 3 4 として出力される。

#### 【 0 0 7 1 】

上述のように、電源電圧の特定情報として、高電圧番号を用いて電位追跡を行なっても、抵抗素子を含む特定領域に対してのみ、特定用途デザインルールを適用し、それ以外の領域に対しては、特定用途のレイアウト検証を実施していない。従って、この特定 D R C 部 4 から出力される検証結果レポート 3 4 には、無用の検証結果は反映されず、必要領域に関する検証結果のみが反映されており、正しい検証を行なうことができる。

#### 【 0 0 7 2 】

なお、この図 1 に示す間隔および余裕値検証手段 3 3 は、ウェル領域のリーク電流を抑制するために、ウェル領域の余裕値を検証している。しかしながら、ウェル領域間の分離を確実にするために、このウェル間の間隔の検証が、併せて行なわれてもよい。

#### 【 0 0 7 3 】

以上のように、この発明の実施の形態 1 に従えば、特定領域を抽出し、この特定領域の素子のレイアウトパターンの検証を、特定領域専用のデザインルールに従って実行しており、確実なレイアウト検証を実現することができる。

#### 【 0 0 7 4 】

特に、この特定領域において、抵抗素子が形成されるウェル領域の余裕値を専用のデザインルールに従って検証することにより、標準電圧用の抵抗素子を高電圧用途に使用して

10

20

30

40

50

も、確実に、リーク電流を抑制するためのレイアウト検証を行なうことができる。

【産業上の利用可能性】

【0075】

この発明は、半導体集積回路のレイアウトを検証する装置に適用することができ、特に、多電源構成の半導体集積回路のレイアウトを検証する装置に適用することができる。

【図面の簡単な説明】

【0076】

【図1】この発明の実施の形態1に従うレイアウト検証装置の全体の構成を概略的に示す図である。

【図2】図1に示す電位追跡および情報選択手段の構成を概略的に示す図である。 10

【図3】検出対象領域を有する半導体集積回路の構成の一例を示す図である。

【図4】図3に示す抵抗素子に使用される抵抗素子の断面構造を概略的に示す図である。

【図5】図4に示す抵抗素子の平面レイアウトを概略的に示す図である。

【図6】抵抗素子情報の構成を概略的に示す図である。

【図7】ウェル領域情報の構成の一例を概略的に示す図である。

【図8】この発明の実施の形態1における電位追跡および情報選択手段の具体的動作を示すフロー図である。

【図9】図3に示す特定領域の平面レイアウトを概略的に示す図である。

【符号の説明】

【0077】

12, 13 素子および接続情報抽出手段、21, 33 間隔および余裕値検証手段、

31 特定用途デザインルール、40 電位追跡および情報選択手段、41 端子および

グラウンド指定手段、43 レイアウト領域設定手段、50 指定端子 - グラウンド間電

位追跡手段、51 抵抗インスタンス選択手段、52 レイアウト上座標抽出手段、53

ウェル座標抽出手段、60 特定領域、62a, 62b, Z1 - Z6 抵抗素子、W1

- W6 ウェル領域、RCTA, RCTB コンタクト領域、DFR 抵抗ボディ部。 20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 佐藤 貴雄

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 金浜 正典

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 村山 哲也

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

F ターム(参考) 5B046 AA08 BA04 JA01

5F064 BB35 CC09 CC22 DD02 DD14 EE52 HH01 HH06 HH09 HH10