(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5495984号

(P5495984)

(45) 発行日 平成26年5月21日(2014.5.21)

(24) 登録日 平成26年3月14日(2014.3.14)

(51) Int.Cl.

F 1

G03G 15/20 (2006.01)

H05B 3/00 (2006.01)G03G 15/20 555

H05B 3/00 335

請求項の数 8 (全 17 頁)

(21) 出願番号 特願2010-151148 (P2010-151148)

(22) 出願日 平成22年7月1日 (2010.7.1)

(65) 公開番号 特開2012-13999 (P2012-13999A)

(43) 公開日 平成24年1月19日 (2012.1.19)

審査請求日 平成25年7月1日 (2013.7.1)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100066061

弁理士 丹羽 宏之

(74) 代理人 100177437

弁理士 中村 英子

(74) 代理人 100143340

弁理士 西尾 美良

(72) 発明者 志村 泰洋

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 八木 智規

最終頁に続く

(54) 【発明の名称】像加熱装置

## (57) 【特許請求の範囲】

## 【請求項 1】

商用電源から電力供給路を通って供給される電力により発熱する第1の発熱体と第2の発熱体と、

メーク接点またはブレーク接点を有する第1のリレーと、トランスファ接点を有する第2のリレーと、を有し、前記第1のリレーと前記第2のリレーにより前記第1の発熱体と前記第2の発熱体を直列接続状態又は並列接続状態に切り替える接続状態切替部と、

前記電力供給路に設けられており、前記第1の発熱体と前記第2の発熱体へ供給する電力を制御するための駆動素子と、

を有する像加熱装置において、

前記第1のリレーよりも前記第1及び前記第2の発熱体側の電力供給路と、前記駆動素子よりも前記商用電源側の電力供給路との間にキャパシタを接続したことを特徴とする像加熱装置。

## 【請求項 2】

前記装置は更に、前記商用電源の電圧を検知する電圧検知部を有し、前記接続状態切替部は前記電圧検知部の検知電圧に応じて前記第1の発熱体と前記第2の発熱体を直列接続状態又は並列接続状態に切り替えることを特徴とする請求項1に記載の像加熱装置。

## 【請求項 3】

前記駆動素子により制御されて前記第1の発熱体と前記第2の発熱体に印加される電圧の波形は交流の半波の途中から電圧を付与する位相制御波形を含んでいることを特徴とす

る請求項 1 又は 2 に記載の像加熱装置。

【請求項 4】

前記装置は更に、エンドレスベルトと、前記第 1 の発熱体と前記第 2 の発熱体を有し前記エンドレスベルトの内面に接触するヒータと、前記エンドレスベルトを介して前記ヒータと共に画像を担持する記録材を挟持搬送しつつ加熱するニップ部を形成するニップ部形成部材と、を有することを特徴とする請求項 1 ないし 3 いずれか 1 項に記載の像加熱装置。

【請求項 5】

商用電源から電力供給路を通って供給される電力により発熱する第 1 の発熱体と第 2 の発熱体と、

10

トランスファ接点を有する第 1 のリレーと、トランスファ接点を有する第 2 のリレーと、を有し、前記第 1 のリレーと前記第 2 のリレーにより前記第 1 の発熱体と前記第 2 の発熱体を直列接続状態又は並列接続状態に切り替える接続状態切替部と、

前記電力供給路に設けられており、前記第 1 の発熱体と前記第 2 の発熱体へ供給する電力を制御するための駆動素子と、

を有する像加熱装置において、

前記第 1 のリレーのコモン電極から前記第 2 の発熱体までの電力供給路と、前記駆動素子よりも前記商用電源側の電力供給路と、の間にキャパシタを接続したことを特徴とする像加熱装置。

【請求項 6】

20

前記装置は更に、前記商用電源の電圧を検知する電圧検知部を有し、前記接続状態切替部は前記電圧検知部の検知電圧に応じて前記第 1 の発熱体と前記第 2 の発熱体を直列接続状態又は並列接続状態に切り替えることを特徴とする請求項 5 に記載の像加熱装置。

【請求項 7】

前記駆動素子により制御されて前記第 1 の発熱体と前記第 2 の発熱体に印加される電圧の波形は交流の半波の途中から電圧を付与する位相制御波形を含んでいることを特徴とする請求項 5 又は 6 に記載の像加熱装置。

【請求項 8】

前記装置は更に、エンドレスベルトと、前記第 1 の発熱体と前記第 2 の発熱体を有し前記エンドレスベルトの内面に接触するヒータと、前記エンドレスベルトを介して前記ヒータと共に画像を担持する記録材を挟持搬送しつつ加熱するニップ部を形成するニップ部形成部材と、を有することを特徴とする請求項 5 ないし 7 いずれか 1 項に記載の像加熱装置。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複写機、レーザービームプリンタ等の画像形成装置に用いる像加熱装置に関する。

【背景技術】

【0002】

画像形成装置の加熱定着等のために用いる像加熱装置では、所定の温度に維持された加熱体と、加熱体に圧接する加圧ローラによって形成されたニップ部に、被加熱材である記録材を導入して、挟持搬送しつつ加熱する方式が用いられる。像加熱装置、特にフィルム加熱方式の像加熱装置の加熱体には、セラミックス等でできた基板上に抵抗発熱体を設けたヒータが一般的に用いられる。

【0003】

像加熱装置において、商用電源電圧が 100V と 200V の地域で、同じ抵抗値のヒータを用いると、ヒータに供給される電力は電圧の二乗に比例するため、商用電源電圧が 200V の場合には、100V に比べて、ヒータに供給可能な最大電力は 4 倍になる。ヒータに供給可能な最大電力が大きくなると、位相制御や波数制御などのヒータの電力制御に

40

50

おける高調波電流やフリッカ等の発生がひどくなる。また、像加熱装置が熱暴走した場合を考慮すると、より応答性の早い安全回路が必要になる。そのため、商用電源電圧が100Vの地域と200V地域では、像加熱装置には異なる抵抗値のヒータを用いる場合が多い。商用電源電圧が100Vの地域と200Vの地域で共用できる像加熱装置を実現する手段としては、リレーなどのスイッチ手段を用いて、ヒータの抵抗値を切り替える方法が提案されている。例えば、特許文献1、特許文献2記載の像加熱装置では、ヒータ長手方向に伸びた第1の導電経路と第2の導電経路を有し、2つの導電経路を直列接続、又は並列接続することにより、ヒータの抵抗値を切り替える方法が提案されている。2つの導電経路の接続を直列と並列に切り替えるために、特許文献1には、メーク接点（常時開路接点）もしくはブレーク接点（常時閉路接点）のリレーと、MBM接点（ブレーク・ビフォア・メーク接点）のリレーを用いる方法が記載されている。また、MBM接点の代わりに、2つのメーク接点又はメーク接点とブレーク接点のリレーを用いても良い。特許文献2には、2つのMBM接点のリレーを用いた切り替え方法が記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平7-199702号公報

【特許文献2】米国特許第5229577号明細書

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、特許文献1や特許文献2に記載されたヒータ抵抗値の切り替え方式を用いた像加熱装置では、ヒータの2つの導電経路を直列接続した状態において、ヒータの電力制御（位相制御）に起因した雑音端子電圧のノイズレベルが上昇する課題があった。

【0006】

本発明はこのような状況のもとでなされたもので、ヒータ抵抗値の切り替え方式を用いた像加熱装置において、ヒータの電力制御による雑音端子電圧のノイズレベルの上昇を抑制することを目的とする。

【課題を解決するための手段】

【0007】

前述した課題を解決するため、本発明では次のとおりに構成する。

【0008】

(1) 商用電源から電力供給路を通って供給される電力により発熱する第1の発熱体と第2の発熱体と、メーク接点またはブレーク接点を有する第1のリレーと、トランスファ接点を有する第2のリレーと、を有し、前記第1のリレーと前記第2のリレーにより前記第1の発熱体と前記第2の発熱体を直列接続状態又は並列接続状態に切り替える接続状態切替部と、前記電力供給路に設けられており、前記第1の発熱体と前記第2の発熱体へ供給する電力を制御するための駆動素子と、を有する像加熱装置において、前記第1のリレーよりも前記第1及び前記第2の発熱体側の電力供給路と、前記駆動素子よりも前記商用電源側の電力供給路と、の間にキャパシタを接続したことを特徴とする像加熱装置。

【0009】

(2) 商用電源から電力供給路を通って供給される電力により発熱する第1の発熱体と第2の発熱体と、トランスファ接点を有する第1のリレーと、トランスファ接点を有する第2のリレーと、を有し、前記第1のリレーと前記第2のリレーにより前記第1の発熱体と前記第2の発熱体を直列接続状態又は並列接続状態に切り替える接続状態切替部と、前記電力供給路に設けられており、前記第1の発熱体と前記第2の発熱体へ供給する電力を制御するための駆動素子と、を有する像加熱装置において、前記第1のリレーのコモン電極から前記第2の発熱体までの電力供給路と、前記駆動素子よりも前記商用電源側の電力供給路と、の間にキャパシタを接続したことを特徴とする像加熱装置。

【発明の効果】

10

20

30

40

50

## 【0010】

本発明によれば、ヒータ抵抗値の切り替え方式を用いた像加熱装置において、ヒータの電力制御による雑音端子電圧のノイズレベルの上昇を抑制することができる。

## 【図面の簡単な説明】

## 【0011】

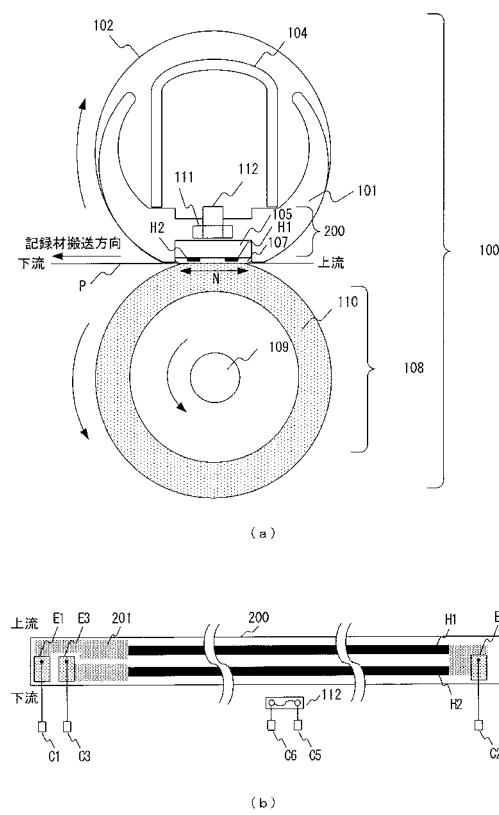

【図1】実施例1の定着装置の断面図、及びヒータ構成図

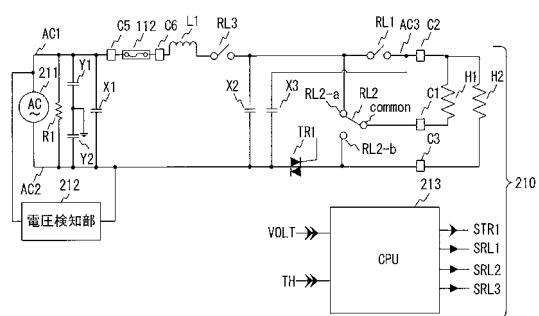

【図2】実施例1のヒータ制御回路の回路構成図

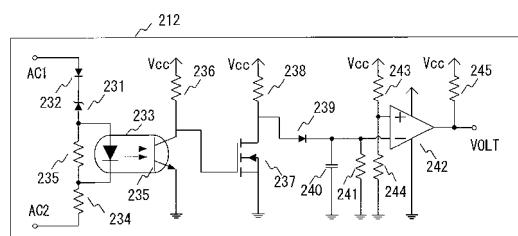

【図3】実施例1の電圧検知部の回路構成図

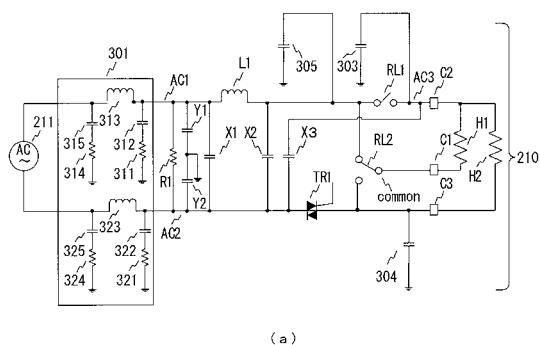

【図4】実施例1の雑音端子電圧測定に使用したヒータ制御回路の回路図

【図5】実施例1のヒータ制御回路の雑音端子電圧の測定波形図

10

【図6】実施例1のヒータ制御回路の雑音端子電圧の測定波形図

【図7】実施例1のリレー制御シーケンスの説明図

【図8】実施例1のリレー制御シーケンスの手順を示すフローチャート

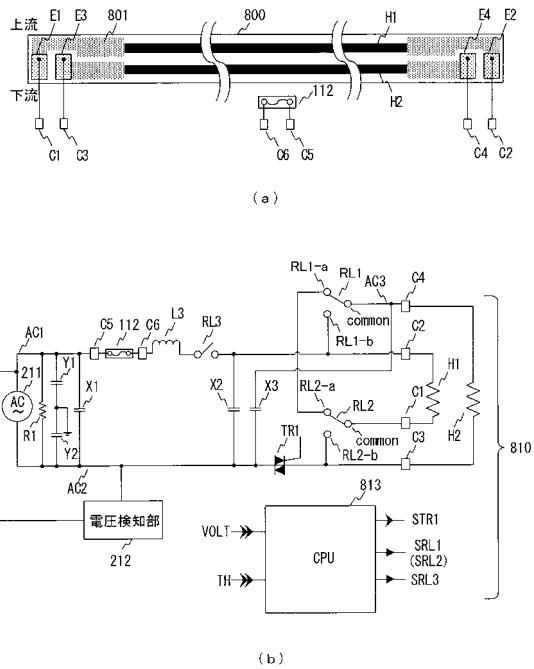

【図9】実施例2のヒータ構成図、及びヒータ制御回路の回路構成図

【図10】実施例3の雑音端子電圧測定に使用したヒータ制御回路の回路図

【図11】実施例3のヒータ制御回路の雑音端子電圧の測定波形図

## 【発明を実施するための形態】

## 【0012】

以下、本発明を実施するための形態について、実施例により詳しく説明する。

## 【実施例1】

20

## 【0013】

## [定着装置の概要について]

図1(a)は、本実施例の像加熱装置の一例としての定着装置100の断面図である。定着装置100は、筒状のフィルム(エンドレスベルト)102と、フィルム102の内面に接触するヒータ200と、フィルム102を介してヒータ200と共に定着ニップ部Nを形成する加圧ローラ(ニップ部形成部材)108を有する。加圧ローラ108は芯金109と弾性層110を有し、不図示のモータから動力を受けて矢印方向に回転する。加圧ローラ108が回転することにより、フィルム102が従動して回転する。ヒータ200は保持部材101に保持され、保持部材101は、フィルム102の回転を案内するガイド機能も有している。ステー104は、保持部材101に不図示のバネの圧力を加えるためのものである。

30

## 【0014】

ヒータ200は、セラミック製のヒータ基板105と、ヒータ基板105上に熱源である抵抗発熱体を用いて形成された導電経路H1及びH2と、導電経路H1及びH2を覆う絶縁性の表面保護層107を有する。ヒータ基板105の裏面側には、搬送方向に直交する方向の長さが画像形成装置で利用可能な最小サイズの記録材(本実施例では封筒DL)の通紙領域に、サーミスタ等を用いた温度検知素子111が当接している。温度検知素子111の検知温度に応じて、商用電源からヒータ200への電力供給が制御される。未定着トナー画像を担持した記録材Pは、記録材搬送方向を上流から下流へ搬送され、定着ニップ部Nで挟持搬送されつつ、加熱されてトナー画像が定着処理される。ヒータ基板105の裏面側には、ヒータ200が異常昇温した時に作動してヒータ200への給電ラインを遮断する、サーモスイッチ等でできた安全素子112も当接している。安全素子112も、温度検知素子111と同様に最小サイズの記録材の通紙領域に当接している。

40

## 【0015】

## [ヒータの概要について]

図1(b)は、本実施例のヒータ200の構成図であり、ヒータ基板105上に形成された発熱パターン、導電パターン、電極、及び、図2の制御回路210に接続するためのコネクタを示す。ヒータ200は、抵抗発熱パターンで形成された第1の発熱体である導電経路H1、及び第2の発熱体である導電経路H2を有する。ヒータ200では、電極と導電経路を接続するために抵抗値の低い導電材料で形成された導電パターン201を用い

50

である。ヒータ200の導電経路H1は、一端を電極E1、他端を電極E2に接続され、電極E1、E2を介して制御回路210から電力が供給され、導電経路H2は、一端を電極E2、他端を電極E3に接続され、電極E2、E3を介して電力が供給される。また、電極E1はコネクタC1と、電極E2はコネクタC2と、電極E3はコネクタC3と、それぞれ接続されている。

#### 【0016】

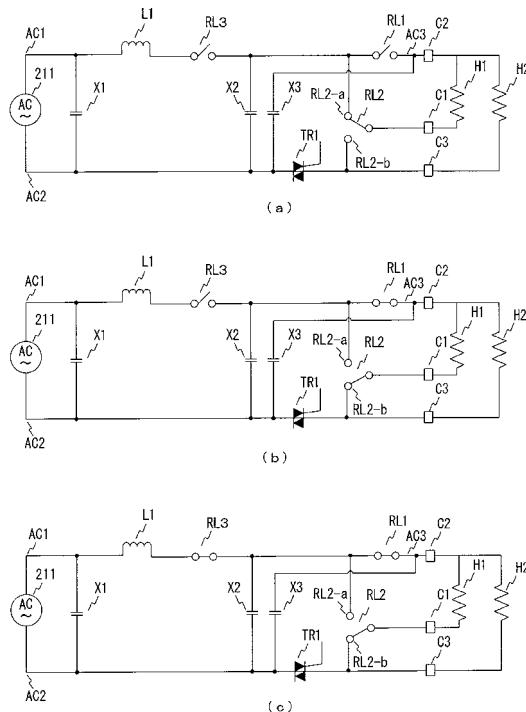

##### [ヒータ制御回路の概要について]

図2は、本実施例のヒータ200の制御回路210の回路構成図である。商用電源211からヒータ200への電力制御は、トライアックTR1の通電／遮断により行われる。

トライアックTR1は、ヒータ駆動を制御するCPU213からのSTR1信号に従って動作する。温度検知素子111によって検知されたヒータ200の温度は、不図示のプルアップ抵抗の分圧として検知され、CPU213にTH信号として入力される。CPU213は、温度検知素子111による検知温度とヒータ200の設定温度に基づき、例えばPI制御(比率積分制御)によりヒータ200への供給電力を算出し、位相角(位相制御)、波数(波数制御)の制御レベルに変換し、トライアックTR1の制御を行う。図1(b)のヒータ200は、コネクタC1、C2、C3を介して制御回路210と接続されている。安全素子112も、コネクタC5、C6を介して制御回路210と接続され、異常昇温時にはヒータ200への電力供給を遮断する。

#### 【0017】

次に、電圧検知部212とリレー制御について説明する。図2において、リレーRL1、RL3は、メーク接点又はブレーキ接点のリレー、リレーRL2は、MBM接点(ブレーキ・ビフォア・メーク接点)のリレーである。また、図2は、電源オフ時における各リレー接点の接続状態(オフ状態)を示しており、リレーRL2においては、コモン接点とRL2-a接点が接続されている状態がオフ状態であり、コモン接点とRL2-b接点が接続されている状態がオン状態である。電圧検知部212は、商用電源211の入力電圧範囲が、例えば100V～127Vの100V系か、あるいは200V～240Vの200V系かを判別し、電圧検知結果をCPU213にVOLT信号として出力する。商用電源211の電圧範囲が200V系の場合には、VOLT信号はロー(Low)レベルとなる。電圧検知部212が商用電源211の電圧が200V系であることを検知した場合には、CPU213は、SRL1信号、SRL2信号によりリレーRL1、RL2をオフ状態に保持する。そして、CPU213がSRL3信号によりリレーRL3をオン状態にすると、ヒータ200に商用電源211を給電可能な状態となる。リレーRL1、RL2がオフ状態であるため、導電経路H1と導電経路H2が直列接続され、ヒータ200は抵抗値の高い状態となる。逆に、電圧検知部212が商用電源211の電圧が100V系であることを検知した場合には、CPU213は、SRL1信号、SRL2信号によりリレーRL1、RL2をオン状態にする。そして、CPU213がSRL3信号によりリレーRL3をオン状態にすると、ヒータ200に商用電源211を給電可能な状態となる。リレーRL1、RL2がオン状態であるため、導電経路H1と導電経路H2が並列接続され、ヒータ200は抵抗値の低い状態となる。

#### 【0018】

##### [ヒータ制御回路のノイズフィルタ構成について]

次に、ヒータ200の電力制御(位相制御)により発生するノイズを低減するノイズフィルタ構成について説明する。図2において、Y1、Y2は商用電源211の電源端子AC1、AC2とグランド間に設けられたキャパシタであり、一般的にYキャパシタ、もしくはYコンデンサと呼ばれる。X1、X2は商用電源211の電源端子AC1、AC2間に設けられたキャパシタであり、一般的にXキャパシタ、もしくはXコンデンサと呼ばれる。キャパシタX1、X2は、インダクタL1と共に、(パイ)型フィルタを形成する。また、図2のキャパシタX3は、トライアックTR1の位相制御に伴い発生する雑音端子電圧のノイズを低減するために設けられている。図2の電源端子AC2とAC3間にキャパシタX3を設けることにより、ヒータ200において導電経路H1とH2を直列接続

10

20

30

40

50

した場合に、ヒータ200の電力制御により生じるノイズが雑音端子電圧のノイズレベルを上昇させることを抑制することができる。

#### 【0019】

##### [電圧検知部の概要について]

図3は、商用電源211の電圧検知手段である電圧検知部212の回路構成図である。電圧検知部212は、電源端子AC1とAC2間に印加された電圧が100V系か、200V系かを判別するための回路である。図3のツェナーダイオード231のツェナー電圧は、商用電源211が200V系の場合に電流が流れるように選択されている。商用電源211が200V系の場合、電源端子AC1とAC2間に印加された電圧はツェナーダイオード231のツェナー電圧よりも高くなり、電源端子AC1とAC2間に電流が流れ。232は電流の逆流防止用ダイオード、234は電流制限抵抗、235はフォトカプラ233の保護抵抗である。フォトカプラ233の発光ダイオードに電流が流れると、フォトトランジスタ235がオンし、抵抗236を介して電源Vccから電流が流れ、FET237のゲート電圧がローレベルとなる。その結果、FET237がオフ状態となるため、抵抗238を介して電源Vccからキャパシタ240に充電電流が流れ。239は電流逆流防止用ダイオードであり、241は放電用抵抗である。電源端子AC1とAC2間に印加された電圧が、ツェナーダイオード231のツェナー電圧よりも高くなる時間の比率が大きくなると、FET237がオフ状態である時間の比率も大きくなる。FET237のオフ時間の比率が大きくなると、キャパシタ240に充電電流が流れる時間が増えるため、キャパシタ240の充電電圧値は高くなる。その結果、キャパシタ240の電圧がコンパレータ242の比較電圧（電圧Vccを抵抗243と抵抗244で分圧した電圧）よりも大きくなると、電源Vccから抵抗245を介してコンパレータ242の出力部に電流が流れ、VOLT信号はローレベルとなる。

#### 【0020】

##### [雑音端子電圧の測定方法について]

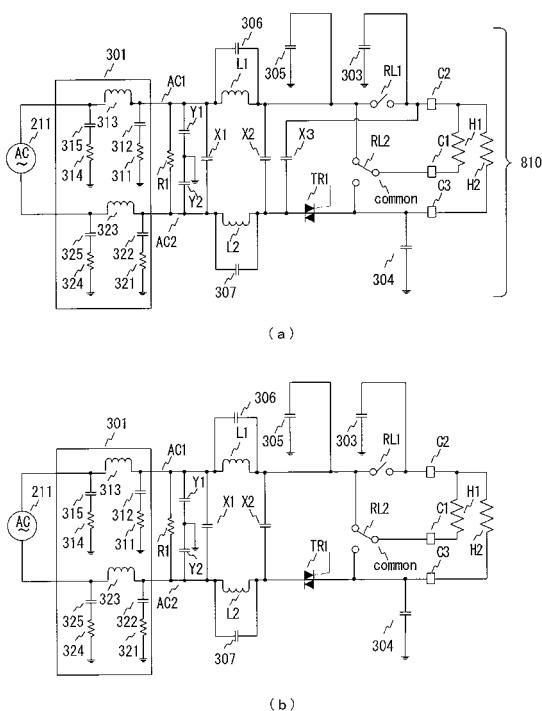

図4(a)は、キャパシタX3による雑音端子電圧ノイズの抑制効果を説明するために、雑音端子電圧のシミュレーション測定に使用した制御回路210の回路図である。図4(b)は、キャパシタX3による効果を比較するために、図4(a)からキャパシタX3を削除した回路図であり、キャパシタX3を削除したため、キャパシタX2の容量値は2倍に設定されている。また、図4(a)、(b)において、リレーRL1、RL2は、導電経路H1、H2が直列接続されるように設定されている。

#### 【0021】

図4(a)において、擬似電源回路網301（以下、「LISN301」という）は、電源ライン上に誘起される雑音電圧を50の電圧値として測定するための回路網である。雑音端子電圧のノイズレベルは、商用電源側のインピーダンスの影響を大きく受け、例えば商用電源211のインピーダンスが大きいほど、ノイズレベルは小さくなる。そのため、雑音端子電圧の測定には、EUT（被試験装置）である制御回路210から商用電源211側を見た場合のインピーダンスを一定に管理する必要がある。図4(a)では、EUTである制御回路210から見たインピーダンスを、50μHのインダクタ313、323と5の抵抗314、324、そして50の測定器の入力インピーダンスである抵抗311、321で規定するために、LISN301を設けている。なお、LISN301において、キャパシタ312、315、322、325はDC成分をカットするために設けている。そして、電源端子AC1に誘起される雑音端子電圧の測定は、LISN301の抵抗311に印加される電圧測定により、電源端子AC2に誘起される雑音端子電圧の測定は、LISN301の抵抗321に印加される電圧測定により行った。

#### 【0022】

また、浮遊容量303～305は、制御回路210の基板、制御回路210の基板ヒータ200を接続するケーブル、ヒータ200の基板に分布する容量成分を、集中定数回路として扱うために示した容量成分である。浮遊容量303～305は同じ容量のキャパシタを用いて、シミュレーションを行った。浮遊容量303～305は、トライアックT

10

20

30

40

50

R 1 がスイッチングした際にコモンモードのノイズを発生させる原因となり、特に、浮遊容量 303 及び 304 がノイズの要因となる。また、浮遊容量 303 によるコモンモードノイズは、抵抗の直列接続 / 並列接続の切り替え機能を持つ定着装置に特有の問題である。トライアック TR 1 がスイッチングした際には、回路の L C 共振によるノーマルモードのノイズと、浮遊容量の充放電によって生じるコモンモードのノイズが発生する。コモンモードのノイズ及びノーマルモードのノイズについては後述する。本実施例では、トライアック TR 1 をスイッチングした際に、浮遊容量 303 の充放電によって生じるサージノイズを抑制するために、キャパシタ X 3 を設けている。キャパシタ X 3 の効果は、キャパシタ X 1 ~ X 3、浮遊容量 303 ~ 305、キャパシタ Y 1、Y 2 のキャパシタンス、インダクタ L 1 のインダクタンス、寄生容量、導電経路 H 1、H 2 の抵抗値、トライアック TR 1 のスイッチング速度などによって異なる。雑音端子電圧の測定で設定した回路定数は、キャパシタ X 3 の効果を説明するための一例である。10

#### 【0023】

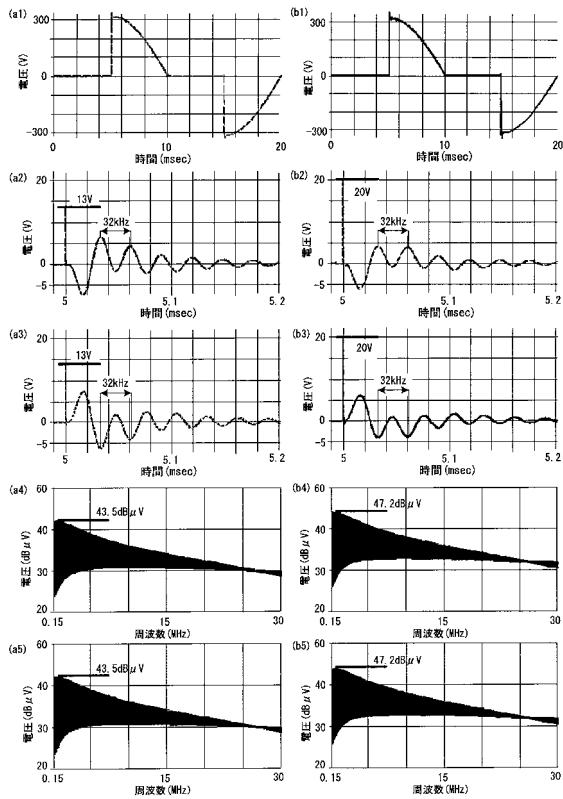

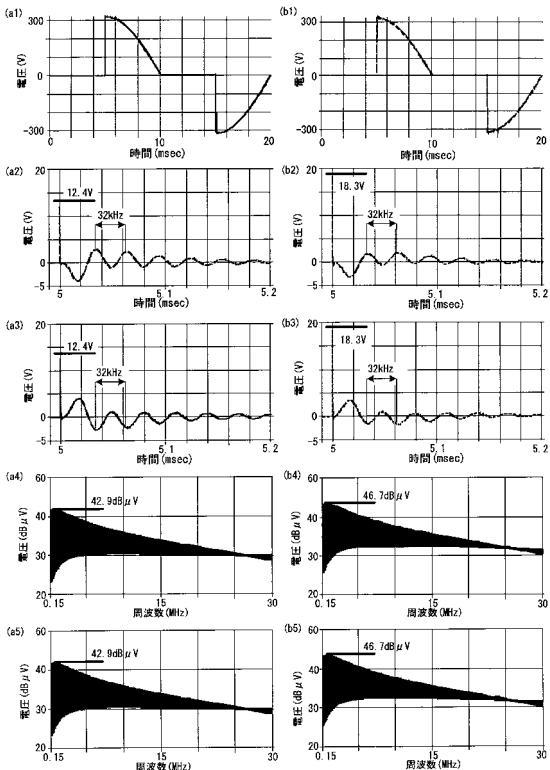

##### [ 雜音端子電圧の測定結果について ]

本実施例の図 5、図 6 は、キャパシタ X 3 の効果を説明するために、図 4 (a)、(b) の回路を用いた雑音端子電圧の測定結果を示したものである。図 5 (a1) ~ (a5) は、図 4 (a) に示す制御回路 210 の端子雑音ノイズの測定結果を示したものであり、図 5 (b1) ~ (b5) は、キャパシタ X 3 による効果を比較するために用いた図 4 (b) の測定結果を示したものである。20

#### 【0024】

図 5 (a1) 及び図 5 (b1) は、商用電源 211 の一周期 (20 msec) における、ヒータ 200 の発熱パターン H 1 及び H 2 に印加される電圧の波形図である。それぞれの波形図は、トライアック TR 1 によって、デューティ 50% に位相制御された状態の波形を示している。以下では、正の位相制御タイミング (5 msec 時点) に発生するノイズについて説明する。負の位相制御タイミング (15 msec 時点) に発生するノイズについては、正の位相制御と同様の結果が得られるため、説明を省略する。なお、詳細については後述するが、サージノイズが発生する要因は浮遊容量 304 及び 303 からの充放電される電流であり、正の位相では浮遊容量からの放電によるサージ電圧が生じ、負の位相では浮遊容量への充電によるサージ電圧が生じる。充電と放電では、サージの位相が 180° 反転する。30

#### 【0025】

図 5 (a2) は、図 4 (a) において、トライアック TR 1 が位相制御されたタイミング (図 5 (a1) の 5 msec 時点) で、LISN 301 の抵抗 311 に印加された電圧 (雑音端子電圧測定で検出されたノイズ成分) の波形を示している。図 5 (a2) より、トライアック TR 1 がオンしたタイミングで、13V の急峻なサージノイズ電圧が発生したのち、約 32kHz の共振ノイズが発生していることが分かる。なお、図 5 (a2) のピーク電圧 13V のサージノイズ波形を拡大したものが図 6 (a1) である。図 5 (a3) は、図 4 (a) において、トライアック TR 1 が位相制御されたタイミング (図 5 (a1) の 5 msec 時点) で、LISN 301 の抵抗 321 に印加された電圧 (雑音端子電圧測定で検出されたノイズ成分) の波形を示している。図 5 (a3) より、トライアック TR 1 がオンしたタイミングで、13V の急峻なサージノイズ電圧が発生したのち、約 32kHz の L C 共振ノイズが発生していることが分かる。なお、図 5 (a3) のピーク電圧 13V のサージノイズ波形を拡大したものが図 6 (a2) である。図 5 (a2)、(a3) より、抵抗 321 に印加されたサージノイズ成分の位相は、抵抗 311 に印加された電圧と位相がほぼ一致しており、電源端子 A C 1、A C 2 の両方に同位相のノイズが発生しているため、コモンモードのノイズ成分であることが分かる。逆に、約 32kHz の L C 共振ノイズ成分の位相は、LISN 301 の抵抗 311 と抵抗 321 で、ほぼ 180° 逆転しており、ノーマルモードのノイズ成分であることが分かる。40

#### 【0026】

図 5 (b2) は、図 4 (b) において、トライアック TR 1 が位相制御されたタイミン50

グ（図5（b1）の5 msec時点）で、LISN301の抵抗311に印加された電圧（雑音端子電圧測定で検出されたノイズ成分）の波形を示している。図5（b2）より、トライアックTR1がオンしたタイミングで、20Vの急峻なサージノイズ電圧が発生したのち、約32kHzの共振ノイズが発生していることが分かる。なお、図5（b2）のピーク電圧20Vのサージノイズ波形を拡大したものが図6（b1）である。図5（b3）は、図4（b）において、トライアックTR1が位相制御されたタイミング（図5（b1）の5 msec時点）で、LISN301の抵抗321に印加された電圧（雑音端子電圧測定で検出されたノイズ成分）の波形を示している。図5（b3）より、トライアックTR1がオンしたタイミングで、20Vの急峻なサージ電圧が発生したのち、約32kHzの共振ノイズが発生していることが分かる。なお、図5（b3）のピーク電圧20Vのサージノイズ波形を拡大したものが図6（b2）である。図5（a2）、（a3）、（b2）、（b3）より、図4のシミュレーション測定結果を比べて、図4（b）では、LISN301の抵抗311、321に印加された雑音端子電圧の測定で検出されたコモンモードのサージノイズ成分が大きいことが分かる。

10

#### 【0027】

図5（a4）は、図4（a）のLISN301の抵抗311に印加された電圧（雑音端子電圧測定で検出されたノイズ成分）を高速フーリエ変換した結果を示したものである。雑音端子電圧の測定では150kHz～30MHzの周波数帯域の測定を行う場合が多いため、図5、及び後述する図11における高速フーリエ変換の図では、150kHz～30MHzの周波数帯域の成分について示している。図5（a4）より、150kHz付近の低周波領域のノイズ成分が最も大きく、約43.5dB $\mu$ Vである。図5（a5）は、図4（a）のLISN301の抵抗321に印加された電圧（雑音端子電圧測定で検出されたノイズ成分）を高速フーリエ変換した結果を示したものである。図5（a5）より、150kHz付近の低周波領域のノイズ成分が最も大きく、約43.5dB $\mu$ Vである。

20

#### 【0028】

図5（b4）は、図4（b）のLISN301の抵抗311に印加された電圧（雑音端子電圧測定で検出されたノイズ成分）を高速フーリエ変換した結果を示したものである。図5（b4）より、150kHz付近の低周波領域のノイズ成分が最も大きく、約47.2dB $\mu$ Vである。図5（b5）は、図4（b）のLISN301の抵抗321に印加された電圧（雑音端子電圧測定で検出されたノイズ成分）を高速フーリエ変換した結果を示したものである。図5（b5）より、150kHz付近の低周波領域のノイズ成分が最も大きく、約47.2dB $\mu$ Vである。

30

#### 【0029】

図4（a）と図4（b）の回路を用いた雑音端子電圧の測定結果を比較すると、図4（a）では、サージノイズのピーク電圧が13Vに抑制されており、図4（b）のピーク電圧20Vより低くなっていることが分かる。パルス幅の短い急峻なサージノイズには高帯域の周波数成分のノイズが含まれており、サージノイズのピーク電圧が高くなると、150kHz～30MHzのノイズ成分も高くなる。図4（a）において発生した約32kHzのLC共振ノイズは、雑音端子電圧の測定下限周波数（150kHz）よりも周波数が低いため、雑音端子電圧のノイズ測定への影響は少ない。

40

#### 【0030】

以上説明したように、制御回路210にキャパシタX3を設けることにより、トライアックTR1がオンする際に生じるサージノイズのピーク電圧を抑えることができ、150kHz～30MHzのノイズ成分を低減させることができる。

#### 【0031】

##### [キャパシタX3によるノイズ低減について]

図5で説明したサージノイズが発生するメカニズムと、本実施例の制御回路210に用いたキャパシタX3のノイズ削減効果について説明する。図6（a1）、（a2）は、時間幅を短くすることにより、図5（a2）、（a3）に示したピーク電圧13Vを発生させたサージノイズ波形を拡大したものである。図6（b1）、（b2）は、時間幅を短く

50

することにより、図5(b2), (b3)に示したピーク電圧20Vを発生させたサージノイズ波形を拡大したものである。次に、キャパシタX3を備えた図4(a)の制御回路210が、キャパシタX3のない図4(b)と比べ、前述したサージノイズ波形を低減できる理由について説明する。

#### 【0032】

図6(a3)は図4(a)における、図6(b3)は図4(b)における、浮遊容量304に充電された電圧波形をそれぞれ示す。これらの電圧波形から、トライアックTR1がオンしたタイミング(5msec時点)で急激な電圧降下が発生し、浮遊容量304に充電された電荷が放電されていることを示している。トライアックTR1がオン状態になると、浮遊容量304に充電された電荷はトライアックTR1を介してLISN301の抵抗321に流れ、正のサージノイズを発生させる。浮遊容量304からの放電で生じた正のサージノイズは、キャパシタX1を介して電源端子AC1にも同様の電圧変動を発生させるため、LISN301の抵抗311にも同様のサージノイズが発生する。

#### 【0033】

図6(a4)は図4(a)における、図6(b4)は図4(b)における、浮遊容量305の容量成分に充電された電圧波形をそれぞれ示す。トライアックTR1がオン状態になつても、電源端子AC1の電位は変化しないため、浮遊容量305からの放電電流によるサージノイズは発生しない。しかし、浮遊容量304、及び後述する浮遊容量303からの放電で生じる正のサージノイズによって、キャパシタX2を介して、浮遊容量305の電圧波形にも同様のサージノイズを発生させている。

#### 【0034】

図6(a5)は図4(a)における、図6(b5)は図4(b)における、浮遊容量303の容量成分に充電された電圧波形をそれぞれ示す。図6(b5)に示す波形から、トライアックTR1がオンしたタイミングで急激な電圧降下が発生していることが分かり、これは浮遊容量303に充電された電荷が放電されていることを示している。トライアックTR1がオン状態になると、浮遊容量303に充電された電荷は、導電経路H2を介してLISN301の抵抗321に流れ、正のサージノイズを発生させる。すなわち、前述した浮遊容量304と同様に、浮遊容量303に充電された電荷の放電も、正のサージノイズを発生させる原因となっている。一方、図6(a5)に示す電圧波形から、キャパシタX3は浮遊容量303に対して十分大きな容量成分を有しているため、電源端子AC2と電源端子AC3間の電圧を保持するように働くのが分かる。そのため、図6(a5)の電圧波形において、トライアックTR1がオンしたタイミングで急激な電圧降下が発生しておらず、これは浮遊容量303に充電された電荷が急激に放電されていないことを示している。浮遊容量303は長い時定数に基づいて放電され、放電周期は150kHzよりも低い周波数となるため、雑音端子電圧への影響を低減することができる。

#### 【0035】

ヒータ抵抗の直列/並列接続の切り替えを行わない定着装置では、導電経路H1及びH2の接続点である中点と、制御回路210とが接続されていないため、浮遊容量303は殆ど無視することができる。ところが、本実施例のように、ヒータ抵抗の直列/並列接続が切り替え可能な定着装置を、リレーRL1をオフ状態にすることによりヒータ抵抗を直列接続して用いた場合には、浮遊容量303に起因するサージノイズが雑音端子電圧を上昇させる要因になる。逆に、ヒータ抵抗を並列接続することにより抵抗値が低くなるリレーRL1のオン状態では、浮遊容量303と浮遊容量305が並列に接続された状態となるため、サージノイズが雑音端子電圧を上昇させる要因とはならない。

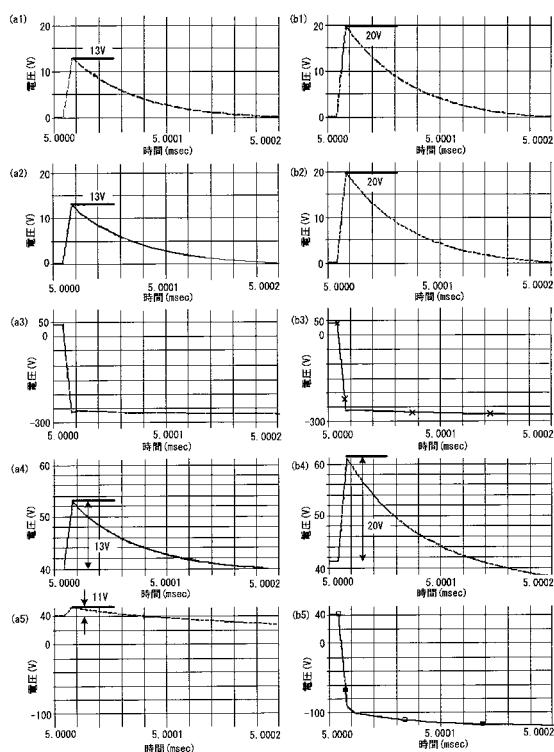

#### 【0036】

##### [リレーの制御シーケンスについて]

図7を用いて、キャパシタX2、X3への突入電流が、リレーRL3、RL1の接点にダメージを与えないように、制御回路210をヒータ200に電力供給が可能な状態に立ち上げる方法について説明する。図7(a)は、制御回路210において、電源オフ時のリレーRL1、RL2、RL3の接続状態を示しており、リレーRL1、RL2はオフ状

10

20

30

40

50

態であり、ヒータ200の導電経路H1、H2が直列接続された状態となっている。図7(b)は、リレーRL1、RL2はオン状態であり、ヒータ200の導電経路H1、H2は並列接続された状態となっている。なお、CPU213がリレーRL1、RL2をオン状態に変化させる時は、リレーRL3はオフ状態で維持されているため、キャパシタX3への突入電流は生じない。図7(c)は、図7(b)の状態でリレーRL3をオンし、ヒータ200に商用電源211から電力を供給可能にした状態を示している。商用電源211及びキャパシタX1からキャパシタX2、X3への突入電流は、リレーRL3、RL1の電気接点にダメージを与える要因になるが、この突入電流はインダクタL1によって抑制することができる。図7(c)の状態において制御回路210の構成では、トライアックTR1がオンしたタイミングで、キャパシタX3から放電される電流は、導電経路H2を介してトライアックTR1に流れ、トライアックに過大な瞬時電流が流れることを防止できる。キャパシタX3に充放電される電流によって、トライアックTR1にダメージを与えることを防止するために、制御回路210では、商用電源のAC1とリレーRL1が接続されており、商用電源のAC2とトライアックTR1が接続されている。

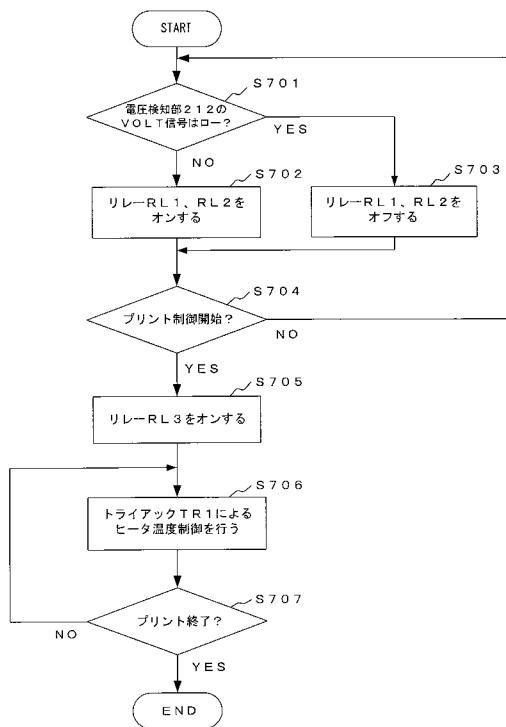

#### 【0037】

図8は、本実施例のリレーの制御シーケンスの手順を示すフローチャートである。本手順は、不図示のROMに格納されたプログラムに基づいてCPU213により実行される。なお、図8のシーケンス手順のスタート時点において、制御回路210はスタンバイ状態であり、リレーRL1～RL3はオフ状態である。

#### 【0038】

CPU213は、電圧検知部212の出力であるVOLT信号に基づき、商用電源211の電源電圧の範囲を判別する(ステップ701(以下、S701のように記す))。CPU213は、電圧検知部202のVOLT信号がローではない、すなわち電源電圧が100V系(例えば100V～127V)であると判断した場合はS702に進む(S701)。逆に、CPU213は、電圧検知部202のVOLT信号がローである、すなわち電源電圧が200V系(例えば200V～240V)であると判断した場合はS703に進む(S701)。S702では、CPU213は、電源電圧が100V系なので、SRL1信号、SRL2信号により、リレーRL1、RL2をオン状態にし、S704に進む。S703では、CPU213は、電源電圧が200V系なので、SRL1信号、SRL2信号により、リレーRL1、RL2をオフ状態にし、S704に進む。S704では、CPU213は、プリント制御開始の判断がされるまで、S701～S703の処理を繰り返す。プリント制御が開始されると、CPU213は、SRL3信号によりリレーRL3をオン状態にし、ヒータ200に電力供給が可能な状態にする(S705)。S706では、CPU213は、温度検知素子111が出力した、ヒータ200の検知温度を示すTH信号に基づき、PI制御を用いてトライアックTR1を制御することにより、ヒータ200に供給する電力制御(位相制御、又は波数制御)を行う。CPU213は、プリント終了と判断するまで、S706の処理を繰り返し、プリント終了と判断すると制御を終了する。

#### 【0039】

本実施例で説明したキャパシタX3の効果は、制御回路210のノイズフィルタ構成(キャパシタX1、X2、インダクタL1、キャパシタY1、Y2)に限定されるものではない。例えば、インダクタL1を電源端子AC2とトライアックTR1間に設置してパイ型フィルタを構成した場合でも、前述の高周波のサーボノイズはキャパシタX2を介してLISN301に同様のノイズを発生させるため、ほぼ同様の測定結果となる。

#### 【0040】

以上説明したように、本実施例によれば、キャパシタX3を制御回路210に設けることにより、抵抗を切り替え可能な像加熱装置において、ヒータ200の電力制御による雑音端子電圧のノイズレベルの上昇を抑制することができる。本実施例では、キャパシタX3を用いることによって、ノイズを低減させている。商用電源のライン間に用いられるXキャパシタは、前述したインダクタと比べて小型で安価なことが多い。また、インダクタ

や、コモンモードチョークコイルと、本提案のキャパシタX3を併用しても良い。

【実施例2】

【0041】

実施例1では、リレーRL1は、メーク接点、又はブレーク接点を有するリレーを用いたのに対して、本実施例では、MBM接点を有するリレーを用いている点が実施例1と異なる。また、本実施例においては、実施例1と同様の構成については、説明を省略する。

【0042】

[ヒータ、ヒータ制御回路の概要]

図9は、本実施例に用いるヒータ800の構成図(図9(a))、及びヒータ800の制御回路810の回路構成図(図9(b))である。図9(a)は、ヒータ800の基板上に形成された発熱パターン、導電パターン、及び電極を示している。ヒータ800は抵抗発熱パターンで形成された導電経路H1、H2を有している。またヒータ800では、電極と導電経路を接続するために抵抗値の低い導電材料で形成された導電パターン801を用いてある。ヒータ800の第1の導電経路H1には、電極E1、E2を介して電力が供給され、第2の導電経路H2は、電極E3、E4を介して電力が供給される。電極E1はコネクタC1と、電極E2はコネクタC2と、電極E3はコネクタC3と、電極E4はコネクタC4と、それぞれ接続されている。

【0043】

図9(b)は、本実施例のヒータ800の制御回路810を示している。図9(b)に示すリレーRL1、RL2、RL3は、電源オフ状態における接点の接続状態を示している。リレーRL1、RL2は、MBM接点のリレー、リレーRL3は、メーク接点又はブレーク接点のリレーを用いている。図9(b)において、リレーRL1は、コモン接点とRL1-a接点が接続されている状態がオフ状態であり、コモン接点とRL1-b接点が接続されている状態がオン状態である。同様に、リレーRL2においては、コモン接点とRL2-a接点が接続されている状態がオフ状態であり、コモン接点とRL2-b接点が接続されている状態がオン状態である。電圧検知部212が商用電源211の電圧範囲が200V系であることを検知した場合、CPU813は、SRL1信号(又はSRL2信号)により、リレーRL1及びRL2をオフ状態にする。リレーRL2は、リレーRL1と連動することを特徴としており、CPU813のSRL1信号がローレベルになると、リレーRL1とリレーRL2はオフ状態になる。そして、CPU813は、SRL3信号によりリレーRL3をオン状態にすることにより、ヒータ800に商用電源211を給電可能な状態となる。また、リレーRL1、RL2はオフ状態であるため、第1の導電経路H1と、第2の導電経路H2が直列接続され、ヒータ800は抵抗値の高い状態になる。逆に、電圧検知部212が100V系を検知した場合、CPU813は、SRL1信号をハイレベルにして、リレーRL1とリレーRL2をオン状態にする。そして、CPU813は、SRL3信号によりリレーRL3をオン状態にすることにより、ヒータ800に商用電源211を給電可能となる。また、RL1、RL2はオン状態であるため、第1の導電経路H1と第2の導電経路H2が並列接続されるため、ヒータ800は抵抗値の低い状態になる。

【0044】

以上説明したように、本実施例では、リレーRL1にMBM接点のリレーを使用しているが、電源端子AC2、AC3間にキャパシタX3を備えることで、ヒータの電力制御のサージノイズによる雑音端子電圧のノイズレベルの上昇を抑制できる。

【実施例3】

【0045】

本実施例の制御回路810は、実施例1の制御回路210のノイズフィルタ構成(キャパシタX1、X2、インダクタL1、キャパシタY1、Y2)にインダクタL2を追加した回路構成である点が、実施例1と相違する点である。本実施例においては、実施例1と同様の構成については説明を省略する。

【0046】

10

20

30

40

50

[ 雑音端子電圧の測定回路について ]

図10は、本実施例の制御回路810に設けたキャパシタX3が雑音端子電圧ノイズを抑制する効果を説明するため、雑音端子電圧のシミュレーション測定に使用した回路図である。キャパシタX3を有する回路図が図10(a)、キャパシタX3がない回路図が図10(b)である。なお、浮遊容量303～305は同じキャパシタンスとし、インダクタL1及びL2の寄生容量306及び307は、浮遊容量303～305の20倍のキャパシタンスを持つものとする。

【 0047 】

[ 雑音端子電圧の測定結果について ]

図11(a1)～(a5)は、図10(a)に示す制御回路810の端子雑音ノイズの測定結果を示したものであり、図11(b1)～(b5)は、図10(b)の測定結果を示したものである。

【 0048 】

図11(a1)、(b1)は、図10(a)、(b)の回路において、商用電源211の一周期(20 msec)におけるヒータ800の発熱パターンH1及びH2に印加される電圧の波形図である。それぞれの波形図は、トライアックTR1によって、デューティ50%に位相制御された状態の波形を示している。以下では、正の位相制御タイミング(5 msec時点)に発生するノイズについて説明する。負の位相制御タイミング(15 msec時点)に発生するノイズについては、位相は180°逆転するが、正の位相制御と同様の結果が得られるため、説明は省略する。

【 0049 】

図11(a2)は、図10(a)において、トライアックTR1が位相制御したタイミング(図11(a1)の5 msec時点)で、LISN301の抵抗311に印加された電圧(雑音端子電圧測定で検出されたノイズ成分)の波形を示している。図11(a2)より、トライアックTR1がオンしたタイミングで、12.4Vの急峻なサージノイズ電圧が発生したのち、約32kHzの共振ノイズが発生していることが分かる。図11(a3)は、図10(a)において、トライアックTR1が位相制御したタイミング(図11(a1)の5 msec時点)で、LISN301の抵抗321に印加された電圧(雑音端子電圧測定で検出するノイズ成分)の波形を示している。図11(a3)より、トライアックTR1がオンしたタイミングで、12.4Vの急峻なサージノイズ電圧が発生したのち、約32kHzのLC共振ノイズが発生していることが分かる。

【 0050 】

図11(b2)は、図10(b)において、トライアックTR1が位相制御したタイミング(図11(b1)の5 msec時点)で、LISN301の抵抗311に印加された電圧(雑音端子電圧測定で検出するノイズ成分)の波形を示している。図11(b2)より、トライアックTR1がオンしたタイミングで、18.3Vの急峻なサージノイズ電圧が発生したのち、約32kHzの共振ノイズが発生していることが分かる。図11(b3)は、図10(b)において、トライアックTR1が位相制御したタイミング(図11(b1)の5 msec時点)で、LISN301の抵抗321に印加された電圧(雑音端子電圧測定で検出するノイズ成分)の波形を示している。図11(b3)より、トライアックTR1がオンしたタイミングで、18.3Vの急峻なサージ電圧が発生したのち、約32kHzの共振ノイズが発生していることが分かる。

【 0051 】

図11(a2)、(a3)、(b2)、(b3)より、図10のシミュレーション測定結果を比べて、図10(b)では、LISN301の抵抗311、321に印加された雑音端子電圧測定で検出されたコモンモードのサージノイズ成分が大きいことが分かる。本実施例の制御回路810では、実施例1の制御回路210にインダクタL2を追加したため、実施例1に比べ、図10(a)及び図10(b)のサージノイズ成分は低減しており、更にキャパシタX3を用いることで、急峻なノイズ成分を低減できることが分かる。

【 0052 】

10

20

30

40

50

図11(a4)は、図10(a)のLISN301の抵抗311に印加された電圧(雑音端子電圧測定で検出されたノイズ成分)を高速フーリエ変換した結果を示したものである。図11(a4)より、150kHz付近の低周波領域のノイズ成分が最も大きく、約42.9dB $\mu$ Vである。図11(a5)は、図10(a)のLISN301の抵抗321に印加された電圧(雑音端子電圧測定で検出されたノイズ成分)を高速フーリエ変換した結果を示したものである。図11(a5)より、150kHz付近の低周波領域のノイズ成分が最も大きく、約42.9dB $\mu$ Vである。

#### 【0053】

図11(b4)は、図10(b)のLISN301の抵抗311に印加された電圧(雑音端子電圧測定で検出されたノイズ成分)を高速フーリエ変換した結果を示したものである。図11(b4)より、150kHz付近の低周波領域のノイズ成分が最も大きく、約46.7dB $\mu$ Vである。図11(b5)は、図10(b)のLISN301の抵抗321に印加された電圧(雑音端子電圧測定で検出されたノイズ成分)を高速フーリエ変換した結果を示したものである。図11(b5)より、150kHz付近の低周波領域のノイズ成分が最も大きく、約46.7dB $\mu$ Vである。

#### 【0054】

図10(a)と図10(b)の回路を用いた雑音端子電圧の測定結果を比較すると、図10(a)のサージノイズのピーク電圧は12.4Vに抑制されており、図10(b)のサージノイズのピーク電圧18.3Vより低くなっていることが分かる。パルス幅の短い急峻なサージノイズは高帯域の周波数成分のノイズを含んでおり、サージノイズのピーク電圧が高くなると、150kHz～30MHzのノイズ成分は高くなる。本実施例の制御回路810において、約32kHzのLC共振ノイズは雑音端子電圧の測定下限周波数(150kHz)よりも周波数が低いため、雑音端子電圧のノイズ測定への影響は少ない。

#### 【0055】

以上説明したように、キャパシタX3を設けた回路では、キャパシタX3のない回路と比べ、トライアックTR1がオンする際に生じるサージノイズの電圧ピークを抑えることができるため、150kHz～30MHzのノイズ成分を低減することができる。

#### 【0056】

ところで、インダクタL1及びL2が、寄生容量成分306及び307のない理想的なコイルであった場合、図10(b)に示したキャパシタX3を用いない構成であっても、図11で説明したサージノイズは殆ど生じなくなる。しかし、実際のコイルでは、浮遊容量に比べて、大きな寄生容量成分を持っている場合が多い。インダクタL1及びL2の寄生容量のキャパシタンスが、基板の浮遊容量のキャパシタンスより大きいほど、インダクタL1及びL2によって、図11で説明したサージノイズを低減する効果は得られなくなる。2つのインダクタL1及びL2を用いた制御回路810の構成においても、キャパシタX3を用いることで、ヒータの電力制御による雑音端子電圧のノイズレベル上昇を抑制することができる。

#### 【0057】

また、ノイズ低減方法としては、本実施例で説明したインダクタL2の他に、コモンモードチョークコイルを設ける方法等がある。しかし、一般的に画像形成装置に用いる像加熱装置には大電流が流れるため、インダクタによる発熱が問題になることが多い。インダクタンス成分が大きく、大電流を流すことができるコイルは、高価で部品サイズが大きくなることが多い。そのため、インダクタを多く用いることは、装置の大型化やコスト増加の要因になる。また、コイルなどのインダクタは、寄生容量成分を持つ場合が多い。本実施例で説明したように、コイルの寄生容量成分のキャパシタンスが、ノイズの要因となる浮遊容量に比べて大きい場合は、図6で説明した高周波のサージノイズを低減する効果は殆ど得られなくなる。

#### 【符号の説明】

#### 【0058】

R L 1 リレー

10

20

30

40

50

|       |         |

|-------|---------|

| R L 2 | リレー     |

| R L 3 | リレー     |

| 2 0 0 | ヒータ     |

| H 1   | 第1の導電経路 |

| H 2   | 第2の導電経路 |

| X 3   | キヤパシタ   |

【 义 1 】

【 図 2 】

【 図 3 】

【図4】

(a)

(b)

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(56)参考文献 特開平7-199702(JP,A)

特開2008-3469(JP,A)

特開2011-215602(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 03 G 15 / 20

H 05 B 3 / 00