(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5693375号

(P5693375)

(45) 発行日 平成27年4月1日(2015.4.1)

(24) 登録日 平成27年2月13日(2015.2.13)

(51) Int.Cl.

F 1

H01L 33/62 (2010.01)

H01L 33/60 (2010.01)H01L 33/00 440

H01L 33/00 432

請求項の数 7 (全 14 頁)

(21) 出願番号 特願2011-114721 (P2011-114721)

(22) 出願日 平成23年5月23日 (2011.5.23)

(65) 公開番号 特開2012-9848 (P2012-9848A)

(43) 公開日 平成24年1月12日 (2012.1.12)

審査請求日 平成26年1月14日 (2014.1.14)

(31) 優先権主張番号 特願2010-122760 (P2010-122760)

(32) 優先日 平成22年5月28日 (2010.5.28)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001960

シチズンホールディングス株式会社

東京都西東京市田無町六丁目1番12号

(73) 特許権者 000131430

シチズン電子株式会社

山梨県富士吉田市上暮地1丁目23番1号

(74) 代理人 100099759

弁理士 青木 篤

(74) 代理人 100092624

弁理士 鶴田 準一

(74) 代理人 100114018

弁理士 南山 知広

(74) 代理人 100151459

弁理士 中村 健一

最終頁に続く

(54) 【発明の名称】半導体発光素子

## (57) 【特許請求の範囲】

## 【請求項 1】

回路基板にフリップチップ実装する半導体発光素子であって、

発光層を含む半導体層と、

前記半導体層を保護するための保護層と、

前記半導体層を回路基板と接続するためのN側バンプ電極と、

前記半導体層を回路基板と接続するためのP側バンプ電極と、を有し、

前記N側バンプ電極及び前記P側バンプ電極のそれぞれが、アンダーバンプメタル層及び電解メッキ法によって形成されたメッキ金属層を含み、

前記アンダーバンプメタル層が、前記電解メッキ法が適用された際に前記メッキ金属層の下に残存したものであって、前記半導体層側に配置された高反射性金属層及び前記半導体層と反対側に配置された金属層を含み、

前記メッキ金属層の厚さが3μm以上、30μm以下であり、

前記発光層と前記保護層との間に配置された材料は透明であり、

前記N側バンプ電極及び前記P側バンプ電極は、前記発光層の上に配置されており、

前記保護層は、前記アンダーバンプメタル層と前記半導体層との間に配置される、

ことを特徴とする半導体発光素子。

## 【請求項 2】

前記メッキ金属層の厚さが10μm以上、30μm以下である、請求項1に記載の半導体発光素子。

**【請求項 3】**

前記高反射性金属層は A 1 層または A g 層である、請求項 1 又は 2 に記載の半導体発光素子。

**【請求項 4】**

前記 P 側バンプ電極及び前記 N 側バンプ電極の平面形状と、前記 P 側バンプ電極及び前記 N 側バンプ電極に含まれるそれぞれの前記アンダーバンプメタル層の平面形状が等しい、請求項 1 ~ 3 の何れか一項に記載の半導体発光素子。

**【請求項 5】**

前記アンダーバンプメタル層は前記メッキ金属層が占める領域よりも広い面積を占める、請求項 1 ~ 3 の何れか一項に記載の半導体発光素子。

10

**【請求項 6】**

前記保護層は開口部を有し、

開口部を有し且つ前記半導体層を被覆するための保護層を更に有し、前記開口部において前記 N 側バンプ電極及び前記 P 側バンプ電極のそれぞれが前記半導体層と電気的に接続される、請求項 1 ~ 5 の何れか一項に記載の半導体発光素子。

**【請求項 7】**

前記 N 側バンプ電極が前記発光層と平面的に重なるように配置されている、請求項 1 ~ 6 の何れか一項に記載の半導体発光素子。

**【発明の詳細な説明】****【技術分野】**

20

**【0001】**

本発明はフリップチップ実装用の半導体発光素子に関する。

**【背景技術】****【0002】**

半導体発光素子（以下特に断らない限り LED 素子と呼ぶ）はパッケージ化に際し半導体発光装置（以下特に断らない限り LED 装置と呼ぶ）の回路基板にフェイスアップ実装又はフェイスダウン実装（フェイスダウンとも呼ばれる）実装されることが多い。フェイスアップ実装は、LED 素子の電極面を上に向け回路基板に LED 素子を配置し、ワイヤーにより LED 素子の電極と回路基板の電極を接続する。これに対しフェイスダウン実装は、LED 素子の電極面を下に向け回路基板に LED 素子を配置し、バンプなどの導電性部材により LED 素子の電極と回路基板の電極を接続する。

30

**【0003】**

フリップチップ実装はバンプ等を介して直接 LED 素子と回路基板が接続するので、放熱効率が高く、またワイヤーが不要なため実装面積が小さくて良いというメリットがある。フリップチップ実装用の LED 素子では、発光効率を改善するため、発光層からみて電極側に反射層を設け、その反射層で発光層から出射し回路基板側に向かう光を反射し LED 装置から出射させる場合がある。

**【0004】**

例えば、結晶基板上に半導体層を積層し、半導体層と Si ダイオード素子とを接続するための n 側電極及び p 側電極を備え、p 側電極に反射層を有する半導体発光素子が知られている（例えば、特許文献 1）。また、n 側電極及び p 側電極は、Si ダイオード素子と接続するためのマイクロバンプを有している。

40

**【0005】**

また、透明基板上に半導体層を積層し、半導体層とパッケージングサブマウントとを接続するための第 1 電極及び第 2 電極を有し、第 1 電極が金属反射層を有するフリップチップ型発光ダイオードが知られている（例えば、特許文献 2）。また、第 1 電極及び第 2 電極は、はんだ付け可能な材料から構成される中間層を介してパッケージングサブマウントと接続される。

**【0006】**

さらに、サファイア基板上に半導体層を積層し、半導体層とサブマウントとを接続する

50

ためのn型電極及びp型電極を有し、n型電極及びp型電極がA1層を有する半導体発光素子が知られている（例えば、特許文献3）。また、n型電極及びp型電極は、サブマウントとの接触性を向上させるためオーバーコート電極となるAu層を有している。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平11-191641号公報（図1）

【特許文献2】特開2006-121084号公報（図3）

【特許文献3】特開2002-26392号公報（図2）

【発明の概要】

【発明が解決しようとする課題】

【0008】

フリップチップ型の半導体発光素子では、発光層側を下にして回路基板に接続されることになるが、実装効率を高めるためには、回路基板と半導体発光素子との間に所定の隙間を形成することが重要である。また、回路基板上に微細なゴミ等が付着している場合にも、回路基板と半導体発光素子との間に所定の隙間を空けて接続することで、ゴミによる影響を軽減することができる。そのために、接続用の電極を厚膜に形成することが考えられる。

【0009】

一般に、スパッター法や真空蒸着法で形成する膜は概ね1μm以下である。スパッター法で厚さが1μm以上の膜を作ろうとすると残留応力が大きくなりすぎるため好ましくない。真空蒸着法で厚さが1μm以上の膜を作ろうとすると、製造時間、材料利用効率及び設備の制約により困難がともなう。

【0010】

しかしながら、従来技術では、簡単且つ容易に、所定の厚さを有し、光利用効率の高い半導体発光素子を提供することは知られていなかった。

【0011】

そこで、本発明は、上記の問題を解決することが可能な半導体発光素子を提供することを目的とする。

【0012】

また、本発明は、メッキ金属層により所定の厚さに形成された電極を有する半導体発光素子を提供することを目的とする。

【課題を解決するための手段】

【0013】

回路基板にフリップチップ実装する半導体発光素子は、発光層を含む半導体層と、半導体層を回路基板と接続するためのN側バンプ電極と、半導体層を回路基板と接続するためのP側バンプ電極と、を有し、N側バンプ電極及びP側バンプ電極のそれぞれがアンダーバンプメタル層及びメッキ金属層を含み、アンダーバンプメタル層が半導体層側に配置された高反射性金属層及び半導体層と反対側に配置された金属層を含み、メッキ金属層の厚さが3μm以上、30μm以下であることを特徴とする。

【0014】

さらに、半導体発光素子では、メッキ金属層の厚さが10μm以上、30μm以下であることが好ましい。

【0015】

さらに、半導体発光素子では、高反射性金属層はA1層またはAg層であることが好ましい。

【0016】

さらに、半導体発光素子では、P側バンプ電極及びN側バンプ電極の平面形状と、P側バンプ電極及び前記N側バンプ電極に含まれるそれぞれのアンダーバンプメタル層の平面形状が等しいことが好ましい。

10

20

30

40

50

## 【0017】

さらに、半導体発光素子では、アンダーバンプメタル層はメッキ金属層が占める領域よりも広い面積を占めることが好ましい。

## 【0018】

さらに、半導体発光素子では、開口部を有し且つ半導体層を被覆するための保護層を更に有し、開口部においてN側バンプ電極及びP側バンプ電極のそれぞれが半導体層と電気的に接続されることが好ましい。

## 【0019】

さらに、半導体発光素子では、N側バンプ電極が発光層と平面的に重なるように配置されていることが好ましい。

10

## 【0020】

さらに、半導体発光素子では、金属層は、原子拡散防止用金属層であることが好ましい。

## 【発明の効果】

## 【0021】

半導体発光素子は、所定の厚さに形成された電極を有するので、ゴミの影響や発光装置に加わる応力の影響を受けにくいという利点がある。

## 【0022】

半導体発光素子では、電解メッキ法を利用しているので、所定の厚さに形成された電極を容易に形成することができる。

20

## 【0023】

半導体発光素子では、P側バンプ電極及びN側バンプ電極においてアンダーバンプメタル層形成時に反射層形成も同時に形成でき、P側バンプ電極及びN側バンプ電極の両方に反射層を有しているので、反射効率を向上させることができる。

## 【0024】

半導体発光素子では、発光層から出射しバンプ電極に向かう光をアンダーバンプメタル層の高反射性金属層において高い効率で反射するのでLED装置の実装効率を高くできる。

## 【0025】

半導体発光素子では、反射層のないウェハーが供与されても電解メッキ工程に不可欠なメッキ電極（共通電極ともいう）の最下層を高反射性金属層とするだけで簡単に反射層を備えたLED素子が得ることができる。

30

## 【図面の簡単な説明】

## 【0026】

【図1】LED装置の斜視図である。

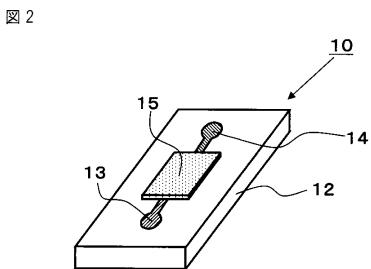

【図2】図1のLED装置から樹脂層11を剥がしとった状態を示す斜視図である。

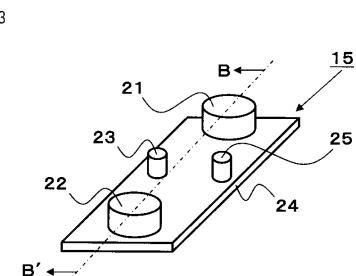

【図3】図2に示すLED素子15をバンプ面から見た斜視図である。

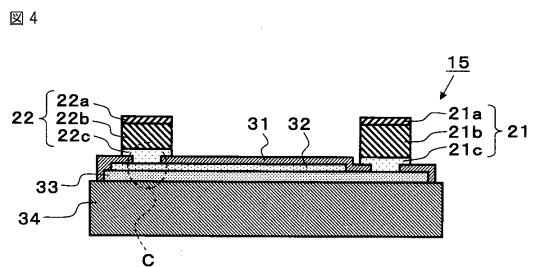

【図4】図3のBB'断面図である。

【図5】図4のC部分の拡大図である。

【図6】放熱用バンプ23の部分断面図である。

40

【図7】保護層31のみをダイ24の上部から見た図である。

【図8】(a)～(i)は、LED素子15のバンプ形成工程を示す図である。

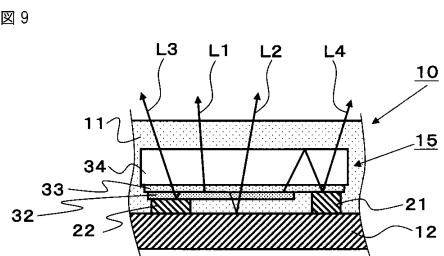

【図9】図1のLED装置のAA'断面図である。

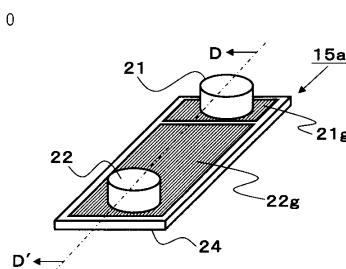

【図10】他のLED素子15aをバンプ面から見た斜視図である。

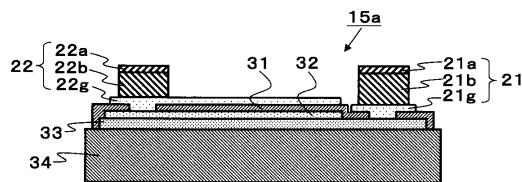

【図11】図10のDD'断面図である。

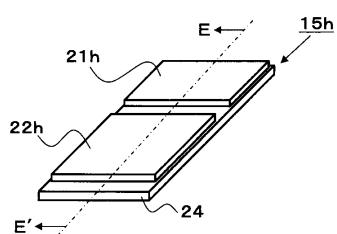

【図12】更に他のLED素子15hをバンプ面から見た斜視図である。

【図13】図12のEE'断面図である。

## 【発明を実施するための形態】

## 【0027】

以下図面を参照して、半導体発光素子について説明する。但し、本発明の技術的範囲は

50

それらの実施の形態に限定されず、特許請求の範囲に記載された発明とその均等物に及ぶ点に留意されたい。なお図面の説明において、同一または相当要素には同一の符号を付し、重複する説明は省略する。また説明のため部材の縮尺は適宜変更している。

【0028】

図1は、LED装置10（半導体発光装置）の外観を示す斜視図である。

【0029】

LED装置10は、図1に示すように、回路基板12の上に樹脂層11が積層している。樹脂層11は、蛍光体を含有し厚さが400μm程度のシリコーン樹脂からなる。

【0030】

図2は、図1のLED装置10から樹脂層11を剥がしとった状態を示す斜視図である。図2を用いて、LED素子15（半導体発光素子）の実装状況を説明する。

【0031】

回路基板12上には、図2に示すように、マイナス電極14とプラス電極13が形成されている。電極上にはLED素子15がフリップチップ実装されている。LED素子15のN側バンプ電極（カソード電極、図示せず）とP側バンプ電極（アノード電極、図示せず）は、それぞれマイナス電極14及びプラス電極13に接続している。回路基板12は、厚さが300μmで、アルミナ面を有するアルミナの板材から構成されている。マイナス電極14及びプラス電極13は、厚さが10～20μm程度でニッケルと金を積層した銅箔である。回路基板12は、下面にマザー基板と接続するための電極（図示せず）を備えており、前記の電極とマイナス電極14及びプラス電極13とはスルーホール（図示せず）で接続している。スルーホールは直径が200μmで銅ペーストが充填されている。

【0032】

図3はLED素子15をバンプ面側から眺めた斜視図である。図3を用いて、LED素子15の電極面（以降バンプ面と呼ぶ）を説明する。

【0033】

LED素子15のダイ24上には、図3に示すように、N側バンプ電極21、P側バンプ電極22、及び放熱用バンプ23及び25が備えられている。N側バンプ電極21とP側バンプ電極22は、ダイ24をフェイスアップ実装するときにワイヤーボンディングのため保護層（図示せず）を開口させた領域に形成されている。放熱用バンプ23及び25はダイ24表面の保護層上に形成され、LED素子15の発する熱を回路基板12（図3には図示せず）に伝えやすくしている。

【0034】

図4は、図3のB-B'断面図である。図4を用いて、LED素子15の断面を説明する。

【0035】

サファイア基板34の上面には、図4に示すように、n型半導体層33があり、n型半導体層33の上面にはp型半導体層32がある。n型半導体層33はp型半導体層32の一部を削って形成した露出部を備えている。n型半導体層33の露出部及びp型半導体層32を覆う保護層31はn型半導体層33の露出部及びp型半導体層32領域に開口部を有し、それぞれの開口部でN側バンプ電極21及びP側バンプ電極22がn型半導体層33及びp型半導体層32に付着している。N側バンプ電極21は、アンダーバンプメタル（以下UBMと呼ぶ）層21c、メッキ金属層21b及び金錫共晶層21aの積層物である。P側バンプ電極22は、UBM層22c、メッキ金属層22b及び金錫共晶層22aの積層物である。なお、本明細書では、保護層31、半導体層（p型半導体層32及びn型半導体層33）、及びサファイア基板34からなるチップをダイ24と称することとする。

【0036】

サファイア基板34の厚さは200～300μm、n型半導体層33の厚さは5μm程度、p型半導体層32の厚さは1μm程度である。N側バンプ電極21及びP側バンプ電極22の厚さは、それぞれ10～30μmである。N側バンプ電極21の上部の金錫共晶

10

20

30

40

50

層 21a 及び P 側バンプ電極 22 の上部の金錫共晶層 22a の厚さは、それぞれ 2 ~ 3  $\mu$  m である。金錫共晶層 21a 及び 22a が溶解することによって、回路基板 12 のマイナス電極 14 及びプラス電極 13 と LED 素子 15 が接合する（金錫共晶接合）。金錫共晶接合では、融点を 300 ~ 420 に設定できるので、250 前後のリフロー温度で LED 装置 10 をマザーボードに実装する場合、共晶接合部は固体のまま維持される。したがって、金錫共晶接合は、有用な接合法である。

#### 【0037】

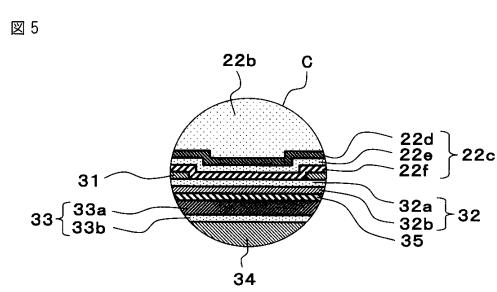

図 5 は、図 4 の C 部分の拡大図である。図 5 を用いて、UBM 層 22c の周辺部の積層構造を詳細に説明する。図 5 は、UBM 層 22c の積層構造について示しているが、UBM 層 21c の積層構造も同様である。

10

#### 【0038】

サファイア基板 34 上には、図 5 に示すように、GaN バッファ層 33b 及び n 型 GaN 層 33a が積層している。なお、GaN バッファ層 33b 及び n 型 GaN 層 33a は、平面形状が等しく隣接しているので、まとめて n 型半導体層 33 として以後の説明を行う。n 型半導体層 33 上には、発光層 35、p 型 GaN 層 32b 及びメタル層 32a が積層している。p 型 GaN 層 32b 及びメタル層 32a も、平面形状が等しく隣接しているため、まとめて p 型半導体層 32 として以後の説明を行う。

#### 【0039】

メタル層は、電流分布の改善やオーミックコンタクト、原子拡散防止などを達成するため多層構造をとることが多い。しかしながら、LED 素子 15 では、ダイ 24 がもともとフェイスアップ実装向けであるので、メタル層 32a は、p 型 GaN 層 32b とオーミックな接続を行い電気抵抗を下げるための透明な ITO 層によって構成されている。なお、ワイヤーボンディング用領域である保護層 31 の開口部において、ITO 層に Ti 等から構成される原子拡散防止層を積層してメタル層としても良い。

20

#### 【0040】

UBM 層 22c は、保護層 31 の上部及び保護層 31 の開口部を覆うように配置されている。UBM 層 22c は、Al 層 22f（高反射性金属層）上に TiW 層 22e と Au 層 22d が積層した積層物である。Al 層 22f、TiW 層 22e、及び Au 層 22d の厚さは、それぞれ 100 nm 程度である。UBM 層 22c 上にはメッキ金属層 22b が積層している。なお、高反射性金属層の材料は Al に限らず Ag や合金であっても良い。高反射性金属層は、広く使われているメッキ電極用金属（TiW）の反射率に比べて高いという意味であり、反射率 90% 以上、好ましくは反射率 95% 以上であることが好ましい。

30

#### 【0041】

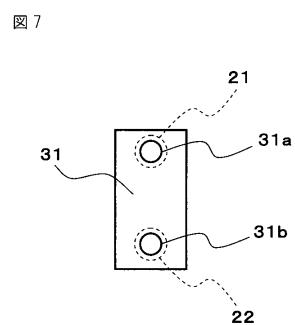

図 6 は、放熱用バンプ 23 の部分断面図である。

#### 【0042】

図 6 に示すように、放熱用バンプ 23 は、保護層 31 の上に形成されており、N 側バンプ 21 及び P 側バンプ 22 と同様に、金錫共晶層 23a、メッキ金属層 23b 及び UBM 層 23c から構成されている。また、UBM 層 23c は、Al 層 23f（高反射性金属層）上に TiW 層 23e と Au 層 23d が積層した積層物である。なお、放熱用バンプ 25 は、放熱用バンプ 23 と同じ構成であるので、その説明を省略する。LED 素子 15 は放熱用バンプ 23 及び 25 を有しているが、必ずしも放熱用バンプを有していないなくても良い。

40

#### 【0043】

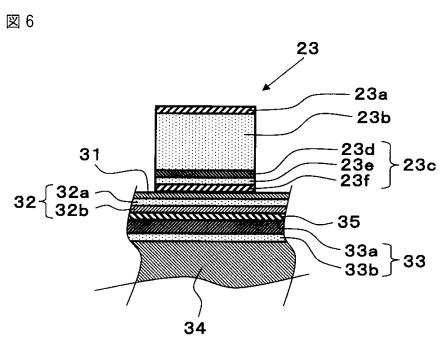

図 7 は、保護層 31 のみをダイ 24 の上部から見た図である。

#### 【0044】

図 7 に示すように、保護層 31 は、N 側バンプ 21 用の開口部 31a 及び P 側バンプ 22 用の開口部 31b を除いてダイ 24 の表面全体を覆っている。また、N 側バンプ 21 用の開口部 31a 及び P 側バンプ 22 用の開口部 31b は、N 側バンプ 21 及び P 側バンプ 22 の直径より若干小さく形成されている。前述したように、放熱用バンプ 23 及び 25

50

は、保護層31上に配置されているため、保護層31は放熱用バンプのための開口部を有していない。

【0045】

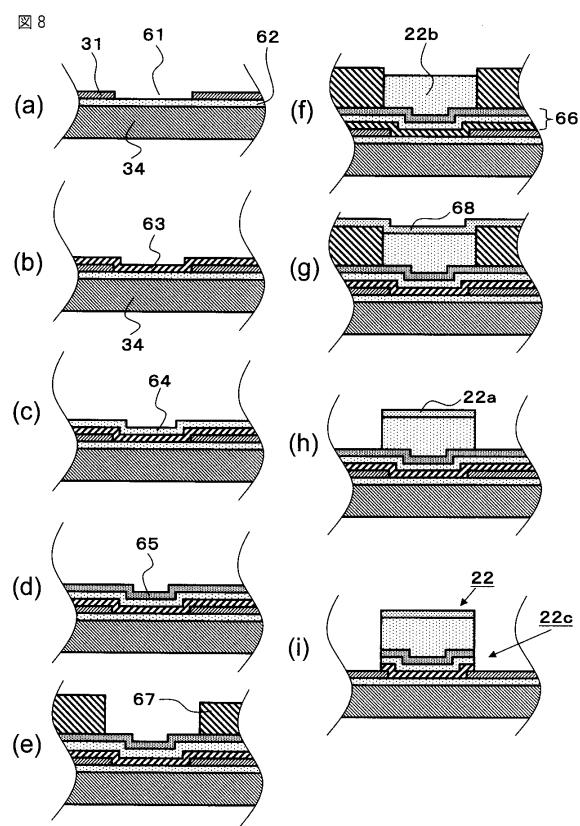

図8はLED素子15のバンプ形成工程を示す図である。

【0046】

各工程図8(a)~(i)では、特徴的な段階におけるバンプ形成領域の周辺部の断面のみを示している。図8を用いて、バンプ形成工程を説明する。なお、図8において、半導体層62の層構造は省略している。半導体層62には、p型半導体層32、発光層35及びn型半導体層33が含まれる。

【0047】

最初に、ウェハー状のサファイアイ基板34を準備し、サファイア基板34上に半導体層62を形成し、さらにその上にバンプ形成領域61が開口した保護層31を形成する(図8(a)参照)。このウェハーは、事前に、洗浄液、純水、ブラシなどで洗われる。

【0048】

次に、保護層31及び開口部61の上部全面に、スパッタリング法によって、Al層63を成膜する(図8(b)参照)。その後、Al層63の上部の全面に、スパッタリング法によって、TiW層64を成膜する(図8(c)参照)。その後、TiW層64の上部の全面に、スパッタリング法によって、Au層65を成膜する(図8(d)参照)。

【0049】

次に、バンプ形成領域61以外の部分にレジスト67を形成する(図8(e)参照)。レジスト材料は、回転塗布法によりAu層65の上部全面に塗布され、その後熱処理が行われる。次に、レジスト材料の上方にバンプ形成領域61部分のみが透明なマスクを配置し、レジスト材料を露光及び現像することにより、レジスト67が形成される。

【0050】

次に、電解メッキ法によりメッキ金属層22bを形成する(図8(f)参照)。サファイア基板34を金メッキ液に浸潤させ、Al層63、TiW層64及びAu層65をマイナス側のメッキ電極66として利用して、メッキ液に電流を流すことにより、メッキ金属層22bを形成する。なお、メッキ金属層22bの厚さはレジスト67の厚さよりも薄くしておく。

【0051】

次に、レジスト67及びメッキ金属層22bの上部の全面に、スパッタリング法によって、厚さが1~2μmの金錫共晶層68を成膜する(図8(g)参照)。

【0052】

次に、レジスト67を除去する(図8(h)参照)。このときバンプ形成領域61以外の金錫共晶層68も除去されるが、メッキ金属層22b上の金錫共晶層22aはそのまま残存する。レジスト67を除去後、アルコールや純水で表面を洗浄しスピンドル乾燥する。

【0053】

次に、メッキ電極66(Al層63、TiW層64及びAu層65)を、エッティングにより除去する(図8(i)参照)。エッティングでは、まず、メッキ金属層22bをマスクとして、ヨウ素系のエッティング液でAu層65を除去する。次に、メッキ金属層22bをマスクとして、過酸化水素水でTiW層64を除去する。最後に、メッキ金属層22bをマスクとして、酢酸系のエッティング液でAl層63を除去する。この結果、メッキ金属層22bの下にのみUBM層22cが残存する。これにより、バンプ形成工程が終了する。

【0054】

図9は、図1のLED装置10のAA'断面図である。図9を用いて、LED装置10の発光効率について説明する。

【0055】

図9に示されるように、光線L1は、p型半導体層32とn型半導体層33の境界部(発光層)で発光した光が、サファイア基板34と樹脂層11を通りLED装置10から出射する様子を示している。光線L2は、発光層で発光した光が、回路基板12に向かって

10

20

30

40

50

出射し、回路基板 12 のアルミナ面で拡散的に反射し LED 装置 10 の外部に出射する様子を示している。

【0056】

光線 L3 は、発光層で発光した光が、P 側バンプ電極 22 に向かって出射し、P 側バンプ電極 22 の上面の A1 層 22f (図 9 には図示せず) で反射し LED 装置 10 から出射する様子を示している。光線 L4 は、発光層で発光した光が、サファイア基板 34 の上面で N 側バンプ電極 21 に向かって反射し、N 側バンプ電極 21 の上面の A1 層 (図示せず) で再度反射し LED 装置 10 から出射する様子を示している。

【0057】

従来の UBM 層の上面は、例えば TiW 層のように反射率の低い金属層であったのに対し、LED 装置 10 の UBM 層 22c の上面は A1 層 22f を備え高い反射率を確保している。このため光線 L3 及び L4 が効率よく LED 装置 10 から出射するようになった。放熱用バンプ 23 (図 3 参照) も、N 側バンプ電極 21 及び P 側バンプ電極 22 と同様に UBM 層上面の A1 層を有しているので、発光層から放熱用バンプ 23 に向かう光線は、UBM 層上面の A1 層で反射して LED 装置 10 の外部に出射する。したがって、LED 装置 10 では、N 側バンプ電極 21、P 側バンプ電極 22 並びに放熱用バンプ 23 及び 25 が占める領域の反射率が向上した分だけ発光効率が改善している。

【0058】

LED 装置 10 において、N 側バンプ電極 21 及び P 側バンプ電極 22 は電解メッキ法によって形成されたメッキ金属層 21b 及び 22b を有しており、メッキ金属層 21b 及び 22b は金バンプであった。バンプ材料 (メッキ金属層) は金に限られず、例えば銅やニッケルなどであっても良い。なお金バンプであれば前述の金錫共晶による接合が適用できるのでリフロー時の安定性が保証されるという利点がある。

【0059】

メッキ金属層 21b 及び 22b は、電解メッキ法によって形成するため、3 μm 未満の厚さであると制御しにくく、厚さがばらつく場合がある。また、10 μm 未満の厚さでは、LED 素子 15 と回路基板 12 との間の隙間が十分ではないので、回路基板 12 上に付着したゴミの影響を受け易くなる。

【0060】

逆に、電解メッキ法によって形成するため、30 μm より厚くする場合には、メッキ金属層 21b 及び 22b の成長させるための製造工程が長時間となる。また、厚くするためには粘性の高いレジスト材料を利用する必要が生じるが、粘性の高いレジスト材料を使うと、取り扱いが面倒になる。

【0061】

そこで、LED 素子 15 では、メッキ金属層 21b 及び 22b の厚さは、3 μm ~ 30 μm であることが好ましく、特に 10 μm ~ 30 μm であることが好ましい。なお、上記の点は、後述する他の LED 素子 15a 及び更に他の LED 素子 15h においても同様である。

【0062】

フェイスアップ用のダイ 24 が配列したウェハーを、バンプ電極を形成するだけでフリップチップ実装向けに転用すると、電極側に反射層がないため LED 発光装置の反射率が低下する。そこで、反射層を備えさせるため、ウェハー製造工程中に反射層を形成する工程を追加しても良い。しかしながら、それではフェイスアップ用のダイ 24 をフリップチップ用 LED 素子 15 に転用する本発明の趣旨に合わない。つまり、専用工程では、ウェハーを準備しておき、フェイスアップ実装に使うか、フリップチップ実装に使うかを状況に応じて使い分けることができなくなる。

【0063】

図 10 は、他の LED 素子 15a をバンプ面から見た斜視図である。図 10 に示す他の LED 素子 15a は、図 3 等に示す LED 素子 15 の代わりに LED 装置 10 に用いることが可能である。図 10 を用いて、他の LED 素子 15a のバンプ面を説明する。

10

20

30

40

50

## 【0064】

他のLED素子15aのダイ24上には、図10に示すように、N側バンプ電極21及びP側バンプ電極22が備えられている。LED素子15(図3参照)と他のLED素子15aとの主たる相違点は、他のLED素子15aのUBM層21g及びUBM層22gがN側バンプ電極21及びP側バンプ電極22の占める領域からはみ出し、広がっていることである。他のLED素子15aの他の構成はLED素子15と同様であるので、それらの説明を省略する。なお、図10では、放熱用バンプ23及び25の記載を便宜上省略している。

## 【0065】

図11は、図10のDD'断面図である。図11を用いて、他のLED素子15aの断面を説明する。

## 【0066】

LED素子15(図4参照)の断面と、他のLED素子15aの断面の主な相違点は、他のLED素子15aのUBM層21g及び22gが広がっている点のみである。他のLED素子15aのUBM層21g及び22gは、LED素子15と同様に、サファイア基板34側から積層されたA1層(図示せず)、TiW層(図示せず)及びAu層(図示せず)による積層物である。

## 【0067】

他のLED素子15aを用いたLED装置10においても、発光層から出射し回路基板12側に向う光線及びLED素子15aの様々な境界面で反射し回路基板12側に向う光線は、UBM層21g及び22gで効率よく反射されLED素子15aから出射する。他のLED素子15aのように、広い反射面(UBM層21g及び22g)を備えると、回路基板12の表面による反射に頼る必要がなくなる。したがって、回路基板12の材料として、反射率は低いが熱伝導率の良い窒化アルミ基板などを用いることが可能となる。

## 【0068】

UBM層21g及び22gは、メッキ電極66を露出させる図8(h)の工程の後、再度ホトリソグラフィ法を適用しメッキ電極66を所望の形状にパターニングすることにより形成される。

## 【0069】

図12は、更に他のLED素子15hをバンプ面から見た斜視図である。図12に示す他のLED素子15hは、図3等に示すLED素子15の代わりにLED装置10に用いることが可能である。図12を用いて、更に他のLED素子15hのバンプ面を説明する。

## 【0070】

更に他のLED素子15hのダイ24上には、図12に示すように、N側バンプ電極21h及びP側バンプ電極22hが備えられており、N側バンプ電極21h及びP側バンプ電極22hによって、ダイ24の上面の大部分が覆われている。LED素子15(図3参照)と更に他のLED素子15hとの主たる相違点は、上述した更に他のLED素子15hの電極形状が異なる点のみである。更に他のLED素子15hの他の構成はLED素子15と同様であるので、それらの説明を省略する。

## 【0071】

図13は、図12のEE'断面図である。図13を用いて、更に他のLED素子15hの断面を説明する。

## 【0072】

LED素子15(図4参照)の断面と、更に他のLED素子15hの断面の主な相違点は、更に他のLED素子15hのN側バンプ電極21h及びP側バンプ電極22hが大きく、更に他のLED発光素子15hの上面をほとんど覆っている点のみである。更に他のLED素子15hのN側バンプ電極21h及びP側バンプ電極22hは、それぞれUBM層21k及び22k、メッキ金属層21j及び22j、金錫共晶層21i及び22iの積層物である。また、N側バンプ電極21hの一部はp型半導体層32と重なっている。更

10

20

30

40

50

に他のLED素子15hのUBM層21k及び22kは、LED素子15と同様に、サファイア基板34側から積層されたAl層(図示せず)、TiW層(図示せず)及びAu層(図示せず)による積層物である。

#### 【0073】

更に他のLED素子15hを用いたLED装置10においても、発光層から出射し回路基板12側に向う光線及び更に他のLED素子15hの様々な境界面で反射し回路基板12側に向う光線は、UBM層21k及び22kで効率よく反射され更に他のLED素子15hから出射する。更に他のLED素子15hのように、広い反射面(UBM層21k及び22k)を備えると、回路基板12の表面による反射に頼る必要がなくなる。したがって、回路基板12の材料として、反射率は低いが熱伝導率の良い窒化アルミ基板などを用いることが可能となる。

10

#### 【0074】

UBM層21k及び22kは、図8の工程でN側バンプ電極21及びP側バンプ電極22を形成する場合のパターンニングを変更することによって、形成することができる。即ち、更に他のLED素子15hでは、電解メッキ法で、N側バンプ電極21h及びP側バンプ電極22hの平面形状を比較的自由に設定できるメリットを活用している。また、更に他のLED素子15hでは、N側バンプ電極21h及びP側バンプ電極22hの形状により、発光層から回路基板12に至る熱抵抗が下がり放熱特性が改善するという更なる利点も有している。その結果、更に他のLED素子15hでは、LED素子15が有する放熱用バンプ23を備える必要が無い。

20

#### 【0075】

反射層を備えていないフリップチップ用LED素子が供与されても電解メッキ工程に不可欠なメッキ電極(共通電極ともいう)の最下層を高反射性金属層とするだけで簡単に反射層を備えたLED素子を得ることができる。したがって、本発明は反射層を備えていないフリップチップ用LED素子に反射層を追加する場合にも有効である。

#### 【符号の説明】

#### 【0076】

|       |              |    |

|-------|--------------|----|

| 10    | LED装置        |    |

| 12    | 回路基板         |    |

| 13    | プラス電極        | 30 |

| 14    | マイナス電極       |    |

| 15    | LED装置        |    |

| 21    | N側バンプ        |    |

| 21a   | 金錫共晶層        |    |

| 21b   | メッキ金属層       |    |

| 21c   | アンダーバンプメタル層  |    |

| 21d   | Au層          |    |

| 21e   | TiW層         |    |

| 21f   | Al層(高反射性金属層) |    |

| 22    | P側バンプ        | 40 |

| 22a   | 金錫共晶層        |    |

| 22b   | メッキ金属層       |    |

| 22c   | アンダーバンプメタル層  |    |

| 22d   | Au層          |    |

| 22e   | TiW層         |    |

| 22f   | Al層(高反射性金属層) |    |

| 23、25 | 放熱バンプ        |    |

| 24    | ダイ           |    |

| 31    | 保護層          |    |

| 32    | p型半導体層       | 50 |

- 3 3 n型半導体層

3 4 サファイア基板

3 5 発光層

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

図11

【図13】

図13

【図12】

図12

---

フロントページの続き

(72)発明者 反町 和昭

山梨県富士吉田市上暮地1丁目23番1号 シチズン電子株式会社内

審査官 北島 拓馬

(56)参考文献 特開2005-093970 (JP, A)

特表2008-543035 (JP, A)

特開2005-045268 (JP, A)

特開2004-356129 (JP, A)

特開2000-114595 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64