# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-191117 (P2006-191117A)

(43) 公開日 平成18年7月20日(2006.7.20)

(51) Int.C1.

$\mathbf{F}$  1

テーマコード (参考)

HO 1 L 25/18 (2006.01) HO 1 L 25/04 (2006.01) HO1L 25/04 Z

審査請求 未請求 請求項の数 10 〇L 外国語出願 (全 37 頁)

(21) 出願番号 特願2006-985 (P2006-985) (22) 出願日 平成18年1月6日 (2006.1.6)

(31) 優先権主張番号 11/030,754

(32) 優先日 平成17年1月6日 (2005.1.6)

(33) 優先権主張国 米国(US)

(71) 出願人 505161208

サイチップ インコーポレーテッド アメリカ合衆国 75093 テキサス, プラノ, ノース ダラス パークウエイ 2805 スイート 400

(74)代理人 100064447

弁理士 岡部 正夫

(74)代理人 100085176

弁理士 加藤 伸晃

(74)代理人 100094112

弁理士 岡部 譲

(74)代理人 100096943

弁理士 臼井 伸一

(74)代理人 100101498

弁理士 越智 隆夫

最終頁に続く

#### (54) 【発明の名称】集積受動デバイス

# (57)【要約】 (修正有)

【課題】集積受動デバイス(IPD)を担体基板(IPD MCM)として含むマルチチップ・モジュール(MCM)を提供する。

【解決手段】寄生電気相互作用は、インタフェースから金属を除去することによって、またはMCMの影響されやすいデバイス構成要素から離れた部分において金属を選択的に使用することによって、IPDの一方または両方のインタフェースで制御される。この影響されやすいデバイス構成要素は、主にアナログ回路構成要素、特にRFインダクタ要素である。IPD配置では、影響されやすい構成要素は、他の構成要素から分離されている。これにより選択性を持つ金属手法の実装が可能になる。さらにIPD基板の上部の上の寄生相互作用を、IC半導体チップおよびICチップの接地平面の選択的な配置によって低減させることも可能にしている。本発明のIPD MCMの好ましい実施形態では、IPD基板は、多結晶である。

【選択図】図6

#### 【特許請求の範囲】

## 【請求項1】

集積受動デバイス・マルチチップ・モジュール(IPD MCM)であって、

a . 基板と、

b.接続層を持つ前記基板に取り付けられているIPDとを含み、前記接続層の少なくとも一部が非導電性であることを特徴とするIPD MCM。

#### 【請求項2】

前記接続層全体が非導電性であることを特徴とする請求項1に記載のIPD MCM。

#### 【請求項3】

前記接続層の第1の部分が非導電性であり、前記接続層の第2の部分が導電性であることを特徴とする請求項1に記載のIPD MCM。

#### 【請求項4】

前記IPDが、少なくとも1つのインダクタ構成要素を含む第1の部分と、少なくとも1つのデジタル構成要素を含む第2の部分とを含み、前記接続層の前記IPDの前記第1の部分の下の部分が非導電性であり、前記接続層の前記デジタル構成要素の下の部分が導電性であることを特徴とする請求項1に記載のIPD MCM。

### 【請求項5】

前記IPD MCMが、前記IPDの上部の上に実装された少なくとも1つの集積回路(IC)チップをさらに含むことを特徴とする請求項4に記載のIPD MCM。

#### 【請求項6】

前記IPDの上部が選択的に接地平面で覆われることを特徴とする請求項4に記載のIPD MCM。

## 【請求項7】

前記接地平面が前記IPDの前記第2の部分上だけに選択的に配置されることを特徴とする請求項6に記載のIPD MCM。

#### 【請求項8】

前記接続層の非導電性部分が電気的絶縁熱伝導ダイ接着材料であることを特徴とする請求項1に記載のIPD MCM。

# 【請求項9】

前記IPDが、多結晶ウェハ上の少なくとも1つの薄膜受動素子を含む多結晶ウェハ基板を含むことを特徴とする請求項1に記載のIPD MCM。

## 【請求項10】

測定された前記IPD MCMの厚さ全体が、前記IPDの厚さ、前記ICチップの厚さ、および前記保護物体の厚さを含めて、1.2mm未満であることを特徴とする請求項1に記載のIPD MCM。

【発明の詳細な説明】

### 【背景技術】

## [0001]

(本項に含まれる技術資料の一部は、従来技術ではない場合がある。)

現況技術の無線周波数(Radio Frequency: RF)電気回路は、多量の受動素子を使用する。これらの回路の多くは、ハンドヘルドの無線製造物内で使用される。したがって、受動素子および受動素子回路の小型化が、RF素子技術では重要な目標となる。

## [0002]

能動シリコン素子の寸法で、受動素子を、集積化し、小型化することは、少なくとも2つの理由で行われなかった。1つは、典型的な受動素子が、今日までさまざまの材料技術を使用していることである。しかし、より根本的には、多くの受動素子の寸法が、デバイスの周波数と相関関係になっており、したがって、本質的に比較的大きいことである。しかし、それでも、よりコンパクトで面積効率が高い集積受動デバイス(Integrated Passive Device: IPD)を製造するための厳しい圧力は存在している。

# [0003]

10

20

30

40

30

40

50

著しい進歩は実現されている。多くの場合において、これらは表面実装技術(Surface Mount Technology: SMT)を含んでいる。多数の受動素子を含む小型の基板は、通常、表面実装技術を使用して、製造される。

[0004]

集積受動素子ネットワークを製造することに関するより最近の進歩には薄膜技術が含まれ、この場合、抵抗器、キャパシタ、およびインダクタが、集積薄膜デバイスとして適切な基板上に作られる。たとえば、米国特許第6、388、290号を参照されたい。この進歩は、受動素子技術における次世代の集積化としての将来性を示している。しかし、基板の材料および特質(純単結晶シリコン)が、能動デバイス技術では、成功への鍵となっていたのと同様に、IPDの集積化が発展するときも、同じことが当てはまるということが明らかとなっている。受動薄膜デバイスは基板上に直接形成されるため、基板と受動素子の間の電気的相互作用が主な問題となる。米国特許出願第10/835338号は、これらの問題を扱っており、所望の誘電特性と結合されたプロセシング利点を提供するIPD基板を説明し、請求している。この基板は、さらに、IPDの外形を小さくするために薄くすることもできる。

[00005]

小型化の観点からの一般的な問題は、デバイスまたは回路のいわゆる「実装面積」であるが、厚さを薄くすることもそれに伴う目標である。ICの実装面積を減らすための一般的な手法は、多重チップモジュール(MultiChip Module: MCM)内で2つもしくはそれ以上のチップを積み重ねることである。MCM技術では、パッケージ化されたチップの厚さが、実装面積と同じくらい重要であることが少なくない。

[0006]

RF回路における小型化のためのMCM手法は、構成要素、特にインダクタ要素間でのRF相互作用に関する問題のために、回避されることが多々ある。RF回路およびIPDに対する通常の手法は、基板上で、デバイスを横方向に広げることである。IPD基板を含むMCMを実装するために、IPD基板が、MCMの担体基板にとってふさわしい候補となるように、通常、IPD基板は、典型的な半導体ICより大きくなり、すなわち、半導体チップはIPD基板の上部の上に実装される。しかし、IPD基板上の積層デバイスは、とりわけ問題となる相互作用をもたらす。このMCM構造内のIPD基板は、RF領域の相互作用に関する2つの問題、1つはIPD基板が実装された基板に関する問題、もう1つはIPD基板の上部の上のICチップに関する問題に直面している。

[0007]

【特許文献1】米国特許第6、388、290号

【特許文献2】米国特許出願第10/835338号

【非特許文献1】Proceedings 1994 IEEE MULTI-CHIP MODULE CONFERENCE MCMC-94、15~19項

【特許文献3】米国特許第6、075、691号

【特許文献4】米国特許第6、005、197号

【発明の開示】

【発明が解決しようとする課題】

[0008]

本発明者らは、IPDを担体基板として含むMCM(IPD MCM)を開発した。

【課題を解決するための手段】

[0009]

寄生電気相互作用 (a parasitic electrical interactions)は、インタフェースから金属を除去することによって、またはMCMの影響されやすいデバイス構成要素から離れた部分において金属を選択的に使用することによって、一方または両方のインタフェースで制御される。影響されやすいデバイス構成要素は、主にアナログ回路構成要素、特にRFインダクタ要素である。IPD配置では、影響されやすい構成要素は、他の構成要素から分離されている。これにより選択性を持つ金属手法の実装が可能となる。さらにIPD基

20

30

40

50

板の上部の上の相互作用を、IC半導体チップの選択的な配置によって低減させることも可能となる。

[0010]

本発明のIPD MCMの好ましい実施形態では、IPD基板は、上記で参照した応用例において説明され、請求された基板である。この基板は、本質的にRF相互作用を低減させ、しかもMCMの外形を最小にするために、薄くすることができる。

【発明を実施するための最良の形態】

[0011]

以下の詳細な説明の最初の部分は、IPD MCM用の好ましい基板を取り扱う。

[0012]

図1は、開始ウェハ11の図である。これは、ブール(boule)から切断された単結晶シリコン・ウェハであり、ICデバイス製造用に世界中で大量に使用されるウェハの一種である。シリコン・ウェハは多くのサイズで製造されるが、通常ウェハの直径が大きくなればなるほど、潜在的なデバイス・コストが低下する。現在、直径が12インチまでのシリコン・ウェハが入手可能である。現況技術を用いた12インチのウェハについては、以下の説明内の実施例として、そのサイズが使用されているが、より小さいウェハ、たとえば6インチまたは8インチのウェハも有効であることが理解される。

[0013]

ウェハ製造施設では、ウェハを鋸引きし、研磨した後、各ウェハは品質管理を受け、そこでウェハが、物理的寸法および電気的性質に関する厳格な標準規格に準拠しての度のか測定される。通常、欠けまたはスクラッチを持つウェハは不合格となったウェハは不合格となったウェハは不合格となったの場合、不合格となったウェハは不力・ウェハ」と呼ばれることもある。この説明では、ならびに以の特許は電気的試験によって呼ばれるブールから切断され、1つまたは複数の物理を持つウェハは、対したために不合格となったウェハは、質素・できる。できる。できる。できる。できる。できる。たとえば、ウェハは、一部は再利用することができる。のでは、ウェハは、ののある構造体を除去するために研究を発してできる。たとえば、ウェハは、欠陥のある構造体を除去するために研究を発している。廃棄ウェハは、許容できるのできる。ののの、より一般的には10%未満の価値を有すると予想することができる。再生されたウェハまたは再利用されるウェハは、のエトのエアD基板の代替的供給源でもある。

[0014]

本発明の一態様によれば、単結晶シリコン・ウェハは、多結晶ウェハを製造するためのハンドル・ウェハとして使用されている。廃棄ウェハが経済的な理由で選択されるウェハとなる可能性があるとき、任意の適切な単結晶シリコン・ウェハを使用することができるということを理解されたい。このプロセスでは、単結晶ウェハは犠牲的なものである。ハンドル・ウェハとして、単結晶ウェハは重要な特性を持つ。たとえ物理的に薄くても(たとえば200~500ミクロン)、比較的物理的に丈夫であり、操作、また処理することができる。単結晶ウェハは、広い面積にわたって非常に平坦である。それは、十分に研磨された均一でなめらかな表面を有する。しかも、シリコン・ウェハ製造プロセスおよびツールに適合する。

[0015]

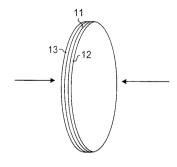

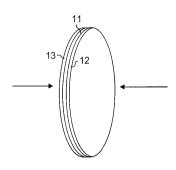

シリコン・ウェハを基板ウェハとして使用して、厚い多結晶層12、13が、図2に示すように、ウェハ11の両側に堆積させられる。あるいは、一方の側面にのみ、多結晶を堆積させることができる。しかし、IPD基板として使用することになっている多結晶層は、比較的厚く、たとえば少なくとも50ミクロン、好ましくは100~300ミクロンである必要がある。本発明者らは、この厚さを持つ層が、単結晶基板上に堆積させられたとき、高い応力を持ち、物理的に歪む傾向があることを発見した。本発明のIPDプロセスでは平面性が望ましいので、基板の著しい歪みを回避することが好ましい。本発明者ら

20

30

40

50

は、単結晶ウェハの両側に多結晶を堆積させることによって、応力が均一化されることを発見した。したがって、好ましくは(しかし必ずしもそうとは限らない)、均一な厚さの層が図 2 に示すように形成される。得られたウェハは、比較的厚く、非常に丈夫である。複合ウェハ内の応力をさらに低減させるために、複合ウェハをアニール (anneal) してもよい。しかし、アニールにより結晶粒の成長が促進されることになり、以下の解説から明らかとなる理由で、微細な結晶粒組織が希望されるため、アニールは慎重に行うべきである

# [0016]

図 2 のサブアセンブリ、すなわち 3 層の複合基板は、基板製造業者によって、単独の製造物として製造することができる。その製造物、ならびに上述のIPD基板の特性は、複合物内の 3 つの層の平面性である。

## [0017]

所望の最終的な基板製造物は、後述するように、単結晶ウェハを持たない多結晶基板である。しかし、たとえ図2に示す複合ウェハが最終的な製造物ではないにしても(すなわち、最終的な製造物内には、単結晶ウェハは存在しない)、複合ウェハ上にプロセシングの少なくとも一部を実施するのには便利である。処理されたウェハは、次いで、多結晶層の1つ、および単結晶層を除去して、最終的なIPD基板としての役割を果たすための多結晶層を残すように、後の工程で薄くすることができる。

#### [ 0 0 1 8 ]

内因性多結晶基板 (an intrinsic polysilicon substrate)の重要な特性は抵抗率が高いことである。多結晶は結晶粒組織を特徴とし、その層または物体は、結晶粒界によって分離されたシリコンの多くの結晶粒で構成されている。この結晶粒界は再結合中心として電気的に作用して、物体内の自由キャリアの寿命を大幅に減少させる。電気的な作用の点から、この特性によって多結晶は単結晶シリコンから分離される。単結晶シリコンが半導体であるとき、多結晶内の多数の結晶粒界は、ドープされないまたは内因性 (intrinsic)の状態では、絶縁体となる。多結晶の抵抗率は、部分的には、結晶粒界の数または結晶粒組織の細かさの作用である。したがって、非常に微細な結晶粒の多結晶は、非常に高い抵抗率を持つことができる。10k0hm・cmを超える抵抗率を持つ多結晶は、簡単に製造することができる。本発明の文脈では、0.1k0hm cmを超える、好ましくは1k0hm cmを超える抵抗値が望ましい。

## [0019]

多結晶層を生成するために使用される方法は、低圧化学的気相成長法(Low-Pressure Chemical Vaper Deposition: LPCVD)が好ましい。この方法およびこの方法を実施するためのCVD装置は、産業界において広く使用されている。簡単に述べると、CVD多結晶に一般に使用される方法は、適度の温度、たとえば550~650°Cでシランを熱分解することを含む。多結晶は、製作されたほとんどすべてのMOSトランジスタ内で使用され、したがって周知の最も一般的な工業用の材料の1つである。多結晶の電気的および物理的性質も周知であることは明白である。先ほど説明したように、多結晶は本質的に抵抗性が高いが、IC用途向けに、抵抗率を低減させるために、一般にイオン注入によって処理される。その内因性の形ではめったに使用されない。厚く広い面積の多結晶層は、太陽電池または光電池内でも使用される。この場合、やはり、多結晶層は、ダイオード構造を形成するために、一般にイオンが注入される。

## [0020]

後述される応用例では、多結晶基板はその内因性の状態で使用され、基板の全体にわたって抵抗率が均一で高いことが望ましい性質である。

# [0021]

CVD多結晶の技術は非常に適切に開発されているので、多結晶層12、13を形成するためには、CVDは好ましい選択肢である。しかし、他の方法も、有効であることが理解できる。たとえば、多結晶の電子ビーム蒸着に関する方法が知られている。厚く、広い面積の、低抵抗率の多結晶基板層を形成するための任意の適切な別の方法も本発明の範囲

内である。

## [0022]

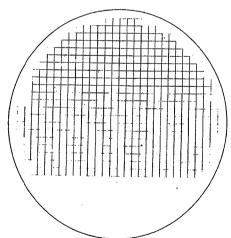

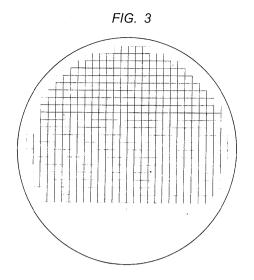

ここで説明するIPD製造手法は、ウェハ寸法によるデバイス製造を目的としている。この手法では、多数の完成した、またはほぼ完成したデバイスが、多結晶ウェハ上に製造される。製造が実質的に完成した後、ウェハは賽の目に切られIPDチップになる。ウェハの寸法が増大し、IPDチップの寸法が縮小するにつれて、ウェハ段階での製造はなお一層魅力的なものとなる。図3は、500個を超えるデバイス・サイト33を提供することができる12インチのウェハ31を示している。(話を簡単にするために、ウェハ平坦部は示していない。)各サイトは、約1平方センチメートルであり、IPDを難なく収容するのには十分に大きい。

[0023]

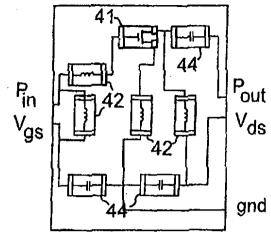

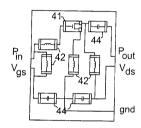

受動素子を形成するために薄膜製造手法を使用すると、ウェハ寸法の製造の有効性を増 大させることができる。一般的な従来技術の手法は、ウェハ段階においてでも、ディスク リートの受動素子をウェハ基板に実装し、取り付けることである。通常、これは表面実装 技術(Surface Mount Technology: SMT)を使用して、実施される。図4は、先に 参照 した 米 国 特 許 第 6 、 3 8 8 、 2 9 0 号 の 図 3 に 示 し た I P D 回 路 に 適 用 し た とき の こ の方法を示している。この回路は、能動素子、すなわちMOSトランジスタ41を含んで いるため厳密にはIPDでない。しかし、以下で明らかとなる理由で、有効な図である。 この回路は、能動部分および受動部分を有するハイブリッド回路とみなすことができる。 ここでは、本発明者らは主に受動部分、すなわち4個のインダクタ42および3個のキャ パシタ44を含む部分に関心がある。選択の問題として、その部分は、IPDとして製造 することができる。図3の回路は、ここでは、および以下では、本発明の技術を示すため の伝達手段として有効であるが、本発明を使用すると多種多様な回路を製作することがで きる。他の実施例、および高Qの観点からより要求の厳しい可能性のある実施例について は、本明細書に参照により組み込まれたProceedings 1994 IEEE MULTI-CHIP MODULE CONFERENCE MCMC-94、15~ 19項を参照されたい。

[0024]

さまざまな薄膜技術によって、薄膜受動素子を形成することができる。これらの技術は十分に開発されており、詳細はここでは繰り返される必要はない。たとえば、2000年6月13日に発行された米国特許第6、075、691号、および1999年12月21日に発行された米国特許第6、005、197号を参照されたい。後者の特許は、ここで説明した応用例に対して簡単に適合することができるPCB用の多層構造を説明している。薄膜受動素子を画定する便利な方法は、受動素子を、基板上に堆積された1つまたは複数の層、一般に複数の層を使用して、基板上に形成することである。

[0025]

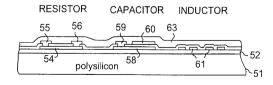

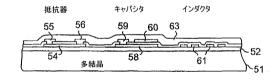

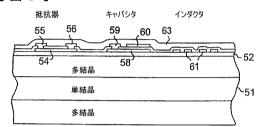

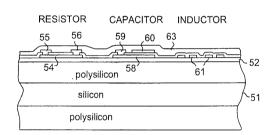

1個の受動素子または相互接続された受動素子の組み合わせを製造するための薄膜方法が、図5によって全体的に表され、そこでは成長させた酸化物層52を有する多結晶基板が51で示されている。第1の層の金属から形成された抵抗体54は接点55、56を有し、下部のキャパシタ・プレート58は接点59を有し、両方とも埋設された層からなる。上部キャパシタ・プレート60およびインダクタ渦巻き61は、図示されない接点と共に最後に形成される。この構造は、ポリイミド層63で保護される。

[0026]

図5の3層の基板構造体51は非常に厚く、それによりプロセシング時の割れおよび他の損傷の危険性が減少する。受動回路素子の製造およびIPDの完成後、基板51は、下部の多結晶層および単結晶シリコン層を除去すると薄くなる。最終的なIPD構造を図6に示す。好ましい薄層工程は、化学的機械研磨法を使用する。この周知のプロセスは、砥粒研磨と化学エッチングを組み合わせている。KOHまたは適切な他のエッチング液は、砥粒スラリーで使用される。複合ウェハは、上部の多結晶層のみ、または上部の多結晶層の一部が残るまでに薄くされる。単結晶層は比較的導電性が高いため、単結晶層全体を除

10

20

30

40

50

去することを強く推奨する。本発明の目標は、IPDにとって好都合なプラットフォームである絶縁性の高い基板を形成することである。

### [0027]

単結晶層(ならびに付加された多結晶層)が、多結晶上部層(IPD層)に対する有効なハンドルを提供するため、IPD層は、最初から比較的薄くすることができる。ウェハ製造が完了した後に、開始ウェハを薄くすることは今日のIC技術では珍しいことではない。これらの多くの場合では、基板は、操作およびプロセシングに耐えるように意図的に厚く製造されて、プロセス内の後半の薄層工程で、デバイスの外形を薄くする。ここで説明した方法では、IPD層の厚さは、最初から最終的な基板の厚さと近似した寸法とすることができる。その厚さは、50~200ミクロンであることが好ましい。

## [0028]

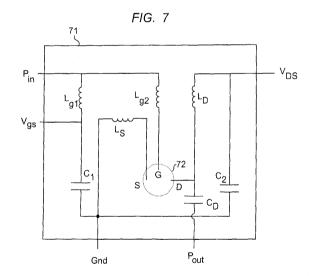

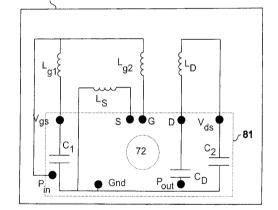

図4のIPDは、図では、図7内の本発明の一実施形態に従って実現される。IPDは、図3に示した1つまたは複数のサイト33の上に形成される。薄膜インダクタLg1、Lg2、Ls、LD、およびキャパシタC1、C2、CDを備える多結晶基板71が示されている。MOSトランジスタ72は、この回路図の段階の時は、IPD内に形成されていないため、想像状態で示されている。図7に関する回路配置は図3のものから意図的に変更されている。この回路およびこの配置は、受動素子を有する典型的な種類の回路を示すためのものである。図7の回路配置は、先に参照した従来技術から採用された回路に関する実施例である。その有効性に関する表示はここでは行わない。

## [0029]

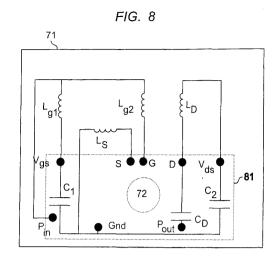

図7内の配置は、すべてのインダクタ素子がグループ化されて設計されている。インダクタ素子は、特に周囲条件、たとえば寄生信号に影響されやすいことが知られている。この認識は、図8に示す能動/受動モジュールの設計の際に用いられる。図7に示したIPDを備える多結晶基板71は、図示のように、能動ICチップ81を、IPDの上部の上にフリップ・チップ実装している。能動ICチップの一部は、トランジスタ72である。この実施形態内の相互接続部は、電気的な相互接続部S、D、G、Vgs、VDSS Pi、P。ut、接地用のはんだバンプとして示されている。基板外部の相互接続箇所(図示せず)は、IPD基板71上に設けることができる。図7に示すようなインダクタ・デバイスのグループ化の目的の1つは、図8において明らかとなる。能動ICチップは、デップは、IPD基板71上に設けることができる。能動ICチップは、ディスのグループ化の目的の1つは、図8において明らかとなる。能動ICチップは、影響されやすいインダクタ素子を覆わないように意図的に配置されている。したがって、積み重ねられた基板配置が、インダクタ素子の性能を損なうことなく、スペースを節約し、コンパクトなデバイス・モジュールを提供するように、有効に実現される。

#### [0030]

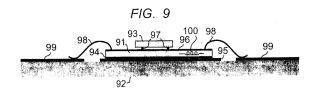

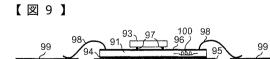

図9は、IPD MCMの別の図であり、この場合、図では、IPD91は、プリント回路基板(PCB)92上に実装されている。ICチップ93は、図では、IPD上に実装されている。話を簡単にするために、1個のICチップのみを示す。通常は、1個より多い。これらのICチップは、アナログ・デバイス、デジタル・デバイス、混成信号デバイス、RFデバイス、および/または微小電気機械システム(Micro-Electro-Mechanical-System: MEMS)によるスイッチまたは発振器とすることができる。

## [0031]

以下の解説から明らかとなるように、たとえ影響されやすいRF構成要素が、上述のようにIPD内で分離されているとしても、別の不都合な問題がまだ取り組まれていないままになっている。それは、IPD内の影響されやすい素子とIPDの付近における外部からの影響、主に金属物体の間の寄生相互作用と関係がある。これらの悪影響は、IPDチップの寸法および主に厚さが減少するにつれて、よりひどくなる。本発明のこの側面は上述の方法と協同しており、IPD MCMの厚さを減らすための本発明全体の目的となっている。

## [0032]

PCBにMCMを実装するための従来の手段は、はんだである。再び図9を参照すると、95におけるPCB接地平面と共に、はんだ結合層が94で示されている。IPDの上

10

20

30

40

50

30

40

50

[0033]

ワイヤ結合部98は、接地平面およびランナを、PCB上の相互接続部99に接続する。ワイヤ結合の他に、ホールをIPD内にエッチングして、IPDの上部と底部の表面上の金属トレースを接続することができる。このエッチング・プロセスは、一般に実行されているMEMS製造プロセスである。スルーホールを備えるIPDが、従来のフリップ・チップ組立てプロセスによって基板に取り付けられる。このスルーホール接続は、さらにIPDと基板の間の相互接続距離を減少させることができる。

[0034]

図9に示す組立て体、ならびに他の図における組立て体は、ポリマー外被でカプセル化されることが当業者によって理解される。プラスチック外被は、ほとんどの従来のデバイスと同様に、プラスチックで被覆成形された物体とすることができ、またはプラスチックのキャビティ・パッケージもしくは他の適切な保護パッケージとすることができる。

[0035]

このMCM構造を持つIPD内の100で概略的に図示されているインダクタなどの影響されやすいRF構成要素は、IPDの両面を覆っている金属のために、漂遊容量に対して弱いことが明らかになっている。

[0036]

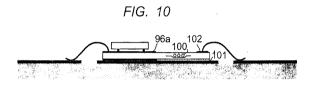

図10は、図9のものと同様のIPD MCMの実施形態を示しているが、インダクタ100の下と上の両方の金属は除去されている。インダクタ100はIPDの一部分であり、この場合、1個または複数個の影響されやすいRF素子が選択的に配置され、他の主にデジタルの回路および回路構成要素から分離されていることが理解される。IPD内のインダクタ構成要素は、RFフィルタ回路と同様に、IPD基板上の他の構成要素と同じ位置内に関連付けることができる。しかし、全体的には、寄生電界の観点から問題となる回路内のインダクタ構成要素である。

[0037]

図 9 内の 9 4 で示した I P D の下の金属は、 I P D のある部分の下に残っているが、 1 0 1 では I P D の影響されやすい素子 1 0 0 を含む部分の下からは除去されている。 I P D のその部分の下の金属は、非導電性の接着性接続層に置き換えられている。非導電性接着剤は、好ましくは、アルミナ充填エポキシなどの電気的絶縁熱伝導ダイ接着材料である

[0038]

また、図9内の96で示したIPDの上部の上の金属は、IPDの影響されやすい素子、たとえば素子100の上にある領域からは除去されている。この金属は、IPD内のデジタル素子上の96aには残っている。ワイヤ結合部は、接点パッド102に作成される。示された実施形態では、金属層96、96aは、接地平面、通常金属からなる連続シートを提供するものとして作成されている。IC上のはんだバンプに接続するために使用されているいくつかの金属ランナは、IPDの影響されやすい素子上で許容することができ

20

30

40

50

る。したがって、より多くのICチップの中の1個をこれらの領域上に実装することができる。しかし、これらの領域における接地平面は、避けるべきである。この配置は、影響されやすい素子の上の表面に沿って延びる金属を使わないで設計されることが好ましい。

[0039]

これらの方法のいずれか、またはその両方が、IPD MCMの電気的性能を改善することになることに注目されたい。

[0040]

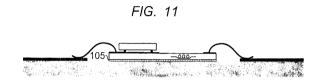

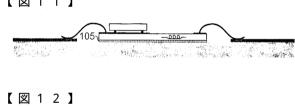

図11は、IPDとPCBの間の金属層全体を除去して、非導電性接着層105に置き換えた、図10の実施形態と同様の実施形態を示している。IPDの下の接地平面はもはや使用されないので、図9内の95で示した金属接地平面層も除去される。得られた構造は、非導電性接続層を有する基板に取り付けたIPDを備える基板であり、IPDは、主にRF構成要素を含む第1の部分、および主に非RF構成要素を含む第2の部分を有し、第1の部分の上には第1の表面、および第1の部分の下には第2の表面を有し、少なくとも1つのデジタルICチップが、IPDの第2の部分上に実装され、IPDの第1および第2表面は金属を持たない。影響されやすいRFデバイスを含まないIPDの部分は、MEMSデバイス、たとえばMEMS発振器またはMEMSスイッチを支持するように適合させることができる。

[0041]

図11の実施形態を綿密に調べてみると、PCBから金属層を除去することにより、IPD MCMの全体的な高さを、その層の厚さだけ減少させることが可能になるということがわかる。それは小さな変更であるように見えるかもしれないが、商業的な観点からは重要である場合がある。商業的なIPD MCMは、図11に示したものと同様の設計で実証されており、PCBの底部からカプセル材料の上部までのパッケージの全体的な高さが1.000mmある。このデバイスは、ある程度外形が小さいために、商業的に競争力があると予想される。

[0042]

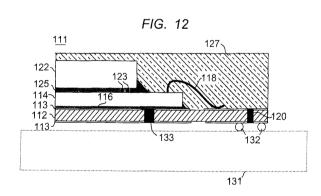

図 1 2 は、全体を 1 1 1 で示した完全に組み立てられたIPD MCM製造物の断面図 を示している。PCB112は、上部と底部の両方の部分上にメタライゼーション113 を備えている。IPDは、114で示され、上述のオプションの中の1つを使用して、ダ イ接着材料 1 1 6 によって P C B に取り付けられている。 I P D は、 P C B に、ワイヤ結 合部(その中の1つを118で示す)で、電気的に相互接続されている。ワイヤは、PC B の上部の層に結合されている。金属バイア 1 2 0 は、 P C B の上部の上の金属を底部上 の金属と貫通接続する。IPD MCMは、その場合、簡単にシステム基板に実装され、 接続することができる。ICチップ122は、図では、IPD114にフリップ・チップ 取り付けされている。はんだバンプ123は、ICチップを、IPD上の金属ランナに取 り付け、接続する。ICチップは、デジタルまたはRF ICチップとすることができる 。ICチップ用の接地平面を備えることは普通である。しかし、前に記載した原理によれ ば、接地平面は、IPDのインダクタ素子の上にある領域からは意図的に欠如されている 。好ましい事例では、ICチップがインダクタ素子の上方に配置されている場合、接地平 面はこの領域から除外される。さらに、そのICチップ用のI/O相互接続部は、必ずし も任意のインダクタ素子の上にはないICチップの縁部の付近には配置されないというこ とが好ましい。

[0043]

能動ICの真下に接地平面を持つPCBの領域では、1個または複数個の熱バイア(the rmal via)を、PCBの上部と底部の金属平面の間に配置して、IPD MCMから動作中に生じた熱を除去することができる。能動ICから生じた熱は、IPD上のICから、アルミナ充填ダイ接着部に、上部の接地平面に、熱バイア(133)に、底部の接地平面に進み、IPD MCMが実装されたシステム基板から放散される。これは従来の手法から発展したものであり、この場合接地平面は連続的な平面であり、ICの下で広がっている。しかし、IPD内にインダクタ素子を収容する必要により、あるRF素子の下には金

20

30

40

50

属平面が存在しない。したがって、この接地平面は、非連続的でよく、小さい部分に分割 することができ、それによって熱が発生するICの下に効果的に配置することができる。

[0044]

あまりに大きすぎてIPD内に実装されることができない受動素子、たとえば、キャパシタ、インダクタ、および抵抗器は、従来の表面実装プロセスを使用して、基板上に実装することができる。

[0045]

組立ての最終段階は、IPD MCM用の保護外被を備えることである。図12は、通常電気組立体上に成形されたポリマーからなる一般的な保護要素である、カプセル材料127を示している。代わりに、この保護外被は、金属缶、プラスチック製キャビティ、または任意の適切な保護外被とすることができる。これらは、当技術分野で周知である。

[0046]

小型化された受動素子を形成する他に、IPDは、IC製造プロセスとPCB製造プロ セスの間の技術上の橋渡しとしての役割も果たす。最先端のICは、ピッチが30マイク ロメートルから300マイクロメートルまでの範囲の接続パッドを使用して、1マイクロ メートルから 0 . 0 6 5 マイクロメートル ( μ m ) までの範囲の形状 ( feature size ) で 製造することができる。IPDは、最新式ではないICツール、たとえば薄膜スパッタリ ングおよびエッチングを使って、1~20ミクロンの特徴寸法で製造される。これらのI PDの特徴は、最小ピッチのIC接続パッドにしっくりと対応することができる。逆に、 P C B 線路およびトレースは、めっきおよびエッチング技術を使用して、ミクロンの 1 0 ( 10 s of μ m ) で製造され、通常 6 0 ~ 3 0 0 ミクロンまでの範囲の大きなピッチの接 続パッドに対応することができる。接続パッドのピッチが大きいICは、表面積の点で、 より小さい接続パッドのピッチを持つICより大きくなる。ICの接続パッドが、ICの 全体的な寸法の決定要因であり、ゲートまたはセルの数がそうなのではないことは非常に 一般的である。したがって、大きな特徴寸法を持つPCB基板に直接接続する場合、表面 積に正比例することになるICのコストは上昇するが、IPDの場合、それはPCBより 特徴寸法がはるかに小さく、そのはるかに簡単な製造工程のため、ICより単位面積当た リのコストが低くなり、ICの微細な特徴機能とPCBの大きな特徴機能を橋渡しするた めの費用効率が高い方法となる。したがって、IPDは、ICと基板の間の費用効率が高 い機械的インタフェースとして作用する。これに関する一態様を図12に概略的に示すこ とができ、この場合、IPD MCMは、図では、システム・レベルの基板131に、は んだボール132で取り付けられている。はんだボール132のピッチをはんだバンプ1 2 3 のピッチと比較すると、先ほど説明した変化が明らかになる。このパッケージの全体 的な高さは、上述のように低く、PCB 112の底部平面から外装または被覆成形物1 27の上部まで、1.2mm未満、好ましくは1.0mm未満、またはそれ以下となる。

[0047]

本発明のさまざまなその他の変更形態が、当業者に見出されるであろう。当技術を進歩させることになった原理およびそれらの等価物に基本的に依存するこの明細書の特定の教示から逸脱したものはすべて、説明し、特許請求したような本発明の範囲内で適切に説明されている。

【図面の簡単な説明】

[0048]

【図1】高抵抗率のIPD基板を作成するための単結晶シリコンの開始ウェハを示す図である。

【図2】多結晶を堆積させた開始ウェハを示す図である。

【図3】薄膜IPDを作るための500個のIPDサイト全体を示した本発明の多結晶ウェハに関する図である。

【図4】従来の基板上に実装した従来のSMT構成要素を示した典型的なIPDに関する 概略断面図である。

【図5】図3の基板のサイトの中の1つにIPDを製造するための薄膜手法に関する概略

図である。

【図6】単結晶シリコン・ハンドルを除去した後の製造済みのIPDに関する図である。

【図7】IPDの実施例を示す概略回路図である。

【図8】IPD上に能動ICチップを備えたIPDを示す図である。

【図9】IPD担体基板および半導体ICチップを備えるMCMの他の図である。

【図10】IPD担体基板、および影響されやすいRF構成要素に対して選択的に配置された半導体ICチップを備えるMCMの実施形態であって、金属が下部のIPDインタフェースから除去された実施形態を示す図である。

【図11】IPD担体基板を備えるMCMのある代替実施形態を示す図である。

【図12】完全に組み立てたIPD MCM製品の断面図である。

【図1】

【図2】

【図3】

10

【図6】 抵抗器

【図7】

P<sub>in</sub>

· V<sub>DS</sub>

インダクタ

$C_{\mathsf{D}}$

$P_{\text{out}}$

キャパシタ

$^{\mathsf{L}}\mathsf{S}$

Gnd

多結晶

60 63

【図4】

【図5】

【図8】

92<sup>J</sup>

111 127 122 125 133 131

【図10】

## フロントページの続き

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 アンソニー エム . チウ

アメリカ合衆国 75082 テキサス,プラノ,バターカップ ドライヴ 2563

(72)発明者 イノン デガニ

アメリカ合衆国 08904 ニュージャージイ, ハイランド パーク, クリーヴランド アヴェニュー 10

(72)発明者 チャーレイ チュンレイ ガオ

アメリカ合衆国 75024 テキサス,プラノ,ホワイト ポーチ ロード 4113

(72)発明者 クンクァン スン

アメリカ合衆国 75093 テキサス,プラノ,グレンホロウ ドライヴ 6405

(72)発明者 リクォ スン

アメリカ合衆国 75093 テキサス,プラノ,ウインドへヴン パークウエイ ナンバー23 27 6201 【外国語明細書】

Title of the Invention

# INTEGRATED PASSIVE DEVICES

# Background of the Invention

(Portions of the technical material contained in this section may not be prior art.)

State of the art radio frequency (RF) electrical circuits use large quantities of passive devices. Many of these circuits are used in hand held wireless products. Accordingly, miniaturization of passive devices and passive device circuits is an important goal in RF device technology.

Integration and miniaturization of passive devices on the scale of active silicon devices has not occurred for at least two reasons. One, typical passive devices to date employ different material technologies. But, more fundamentally, the size of many passive devices is a function of the frequency of the device, and thus is inherently relatively large. However, still, there is unrelenting pressure to produce more compact and area efficient IPDs.

Significant advances have been achieved. In many cases these involve surface mount technology (SMT). Small substrates containing large numbers of passive components are routinely produced using surface mount technology.

More recent advances in producing integrated passive device networks involve thin film technology where resistors capacitors and inductors are built as integrated thin film devices on a suitable substrate. See for example United States Patent No. 6,388,290. This advance shows promise as the next generation of integration in passive device technology. However, just as the substrate material and character (pure single crystal silicon) have been key to the success in active device technology, it is becoming evident that the same is true as IPD integration develops. Because passive thin film devices are formed directly on the substrate, electrical interactions between the substrate and the passive devices are of major concern. United States Patent Application Serial Number 10/835,338 addresses these issues, and describes and claims an IPD substrate that offers processing advantages coupled with the desired dielectric properties. This substrate can also be made thin, to reduce the profile of the IPD.

While a common concern from a miniaturization standpoint is the so-called "footprint" of a device or circuit, reducing thickness is a companion goal. A common approach to reducing the footprint of ICs is to stack two or more chips in an MCM. In MCM technology, the thickness of the packaged chips is often as important as the footprint.

The MCM approach to miniaturization in RF circuits is often avoided due to the problem of RF interactions between components, especially inductor elements. The usual approach for RF circuits and IPDs is to spread the devices

laterally on the substrate. Typically an IPD substrate is larger than a typical semiconductor IC, so to implement an MCM containing an IPD substrate, the IPD substrate is the logical candidate for the carrier substrate of the MCM, i.e. the semiconductor chips would be mounted on top of the IPD substrate. However, stacking devices on an IPD substrate especially invites problematic interactions. An IPD substrate in this MCM configuration faces two issues of RF field interactions, one with the substrate on which the IPD substrate is mounted, and another with the IC chips on the top of the IPD substrate.

# Summary of the Invention

We have developed an MCM that contains an IPD as the carrier substrate (IPD MCM). Parasitic electrical interactions are controlled at one or both interfaces either by eliminating metal from the interfaces, or by selective use of metal in parts of the MCM that are remote from the sensitive device components. The sensitive device components are primarily analog circuit components, especially RF inductor elements. In the IPD layout, the sensitive components are segregated from other components. This allows implementation of the selective metal approach. It also allows interactions on top of the IPD substrate to be reduced by selective placement of the IC semiconductor chips.

In preferred embodiments of the IPD MCM of the invention, the IPD substrate is the substrate described and claimed in the application referenced above. This substrate inherently reduces RF interactions, and can be made thin, to minimize the MCM profile.

# **Detailed Description**

The first part of the detailed description below deals with the preferred substrate for the IPD MCM.

Fig. 1 is a view of a starting wafer 11. This is a single crystal silicon wafer cut from a boule, and is of a type of wafer used in enormous volume for IC device fabrication worldwide. Silicon wafers are produced in many sizes, but typically the larger the diameter of the wafer, the lower the potential device cost. Currently, silicon wafers are available in diameters up to twelve inches. With twelve inch wafers state of the art, that size will be used as the example in the following description, it being understood that smaller wafers, for example 6" or 8", are also useful.

In a wafer production facility, after sawing and polishing the wafers, each wafer is subjected to quality control, where the wafer is measured for conformity to rigid standards for physical size and electrical properties. Typically wafers with chips or scratches will be rejected. Wafers that have excessive or non-uniform conductivity are also rejected. In many cases the rejected wafers are scrapped, and sometimes referred to as "junk wafers". In this description, and in the claims that follow, a "refuse" wafer includes wafers that are cut from a boule, measured by one or more physical or electrical tests, and rejected for failing a test. Refuse wafers have relatively low commercial value. Some may be recycled. Some may be repaired. For example, some wafers are rejected for defects that occur during processing. These wafers have the potential to be polished to remove the defective structure, and used for processing. Such

wafers are also defined as refuse wafers. A refuse wafer may be expected to have a value of less than 50%, and more typically, less than 10%, of the value of an acceptable wafer. A reclaimed wafer or recycled wafer is also an alternative source of low cost IPD substrate.

According to one aspect of the invention, a single crystal silicon wafer is used as a handle wafer to produce a polysilicon wafer. It should be understood that while a refuse wafer may be the wafer of choice for economic reasons, any suitable single crystal silicon wafer may be used. In this process, the single crystal wafer is sacrificial. As a handle wafer, the single crystal wafer has important attributes. Even though physically thin (e.g. 200-500 microns), it is relatively robust physically, and can be handled and processed. It is very flat over a large area. It has a highly polished uniformly smooth surface. And it is compatible with silicon wafer fabrication processes and tools.

Using the silicon wafer as a substrate wafer, thick polysilicon layers 12 and 13 are deposited on both sides of wafer 11 as shown in Fig. 2. Alternatively, polysilicon may be deposited on one side only. However, the polysilicon layer destined for use as an IPD substrate needs to be relatively thick, for example at least 50 microns, and preferably 100-300 microns. We have found that layers with this thickness, when deposited on a single crystal substrate, contain high stress, and tend to physically distort. Since planarity is desirable for the IPD process of the invention, significant distortion of the substrate is preferably avoided. We have found that by depositing polysilicon on both sides of the single crystal wafer, stresses are equalized. Accordingly, layers preferably (but

not necessarily) of equal thickness are formed as shown in Fig. 2. The resulting wafer is relatively thick, and very robust. To further reduce the stress in the composite wafer, the composite wafer may be annealed. However, care in annealing should be exercised, since annealing encourages grain growth, and fine grain structures are desired, for reasons that will become evident from the discussion below.

The subassembly of Fig. 2, i.e. a three-layer composite substrate, may be produced by a substrate manufacturer as a standalone product. A characteristic of that product, as well as the IPD substrates described above, is the planarity of the three layers in the composite.

The final substrate product desired is a polysilicon substrate, without the single crystal wafer, as will be described below. However, even though the composite wafer shown in Fig. 2 is not the final product (i.e., the single crystal wafer will be absent in the final product), it is convenient to perform at least some of the processing on the composite wafer. The processed wafer may then be thinned in a later step to remove one of the polysilicon layers, and the single crystal layer, leaving the polysilicon layer to serve as the final IPD substrate.

An important attribute of an intrinsic polysilicon substrate is high resistivity. Polysilicon is characterized by a grain structure, wherein the layer or body is comprised of many grains of silicon, separated by grain boundaries. The grain boundaries behave electrically as recombination centers, drastically reducing the lifetime of free carriers in the body. In terms of electrical behavior, this characteristic separates polysilicon from single crystal silicon. While single

crystal silicon is a semiconductor, the large number of grain boundaries in polysilicon make it, in an undoped or intrinsic state, an insulator. The resistivity of polysilicon is a partly a function of the number of grain boundaries, or the fineness of the grain structure. Thus very fine grain polysilicon may have very high resistivity. Polysilicon may easily be produced with a resistivity of more than 10 KOhm-cm. In the context of the invention, resistivity values of more than 0.1 KOhm-cm, and preferably more than 1 KOhm-cm are desired.

The method used to produce the polysilicon layers is preferably Low Pressure Chemical Vapor Deposition (LPCVD). This method, and CVD equipment for implementing the method, are widely used in industry. Briefly, the method commonly used for CVD polysilicon involves the pyrolysis of silane at modest temperatures, for example, 550-650 °C. Polysilicon is used in nearly every MOS transistor made, and is thus one of the most common industrial materials known. Obviously, the electrical and physical properties of polysilicon are also well known. Though it is intrinsically highly resistive, as just described, it is typically processed by ion implantation to reduce the resistivity for IC applications. It is rarely used in its intrinsic form. Thick, wide-area, polysilicon layers have also been used in solar cells, or photocells. Here again, the polysilicon layers are typically implanted with ions to form diode structures.

In the application to be described below, the polysilicon substrate is used in its intrinsic state, and uniform high resistivity across the substrate is a desired property.

Since the technology of CVD polysilicon is so well developed, CVD is the

preferred choice for forming the polysilicon layers 12 and 13. However, other methods may be found useful. For example, methods are known for e-beam evaporation of polysilicon. Any suitable alternative for forming a thick, wide area, low resistivity, polysilicon substrate layer is within the scope of the invention.

The IPD production approach described here is aimed at wafer scale device fabrication. In this approach, a large number of finished, or nearly finished, devices are produced on the polysilicon wafer. After fabrication is essentially complete, the wafer is diced into IPD chips. As the size of wafers increases, and IPD chip size shrinks, wafer level fabrication becomes ever more attractive. Fig. 3 shows a twelve inch wafer 31, which is capable of providing more than 500 device sites 33. (For simplicity, the wafer flat is not shown.) Each site is approximately a centimeter square, easily large enough to accommodate an IPD.

The effectiveness of wafer scale fabrication can be multiplied using thin film fabrication approaches for forming the passive devices. A common prior art approach, even at the wafer level, is to mount and attach discrete passive elements to the wafer substrate. Typically this is done using surface mount technology (SMT). Fig. 4 shows this method as applied to the IPD circuit illustrated in Fig. 3 of U.S. Patent No. 6,388,290, referenced earlier. This circuit is not strictly an IPD because it contains an active element, i.e. MOS transistor 41. However, for reasons that will become apparent below, it is a useful illustration. The circuit may be considered a hybrid circuit having an active portion and a passive portion. Here we will be concerned mainly with the

passive portion, i.e. the portion that contains four inductors 42 and three capacitors 44. As a matter of choice, that portion could be produced as an IPD. Although the circuit of Fig. 3 is useful here, and below, as a vehicle to illustrate the technology of the invention, a wide variety of circuits may be made using the invention. For another example, and one that may be more demanding from a high-Q standpoint, see Proceedings 1994 IEEE MULTI-CHIP MODULE CONFERENCE MCMC-94, PAGES 15-19, incorporated herein by reference.

Thin film passive elements may be formed by a variety of thin film techniques. These techniques are well developed and the specifics need not be reiterated here. See for example U.S. Patent 6,075,691, issued June 13, 2000, and U.S. Patent No. 6.005.197, issued December 21, 1999. The latter patent describes a multi-layer structure for PCBs, which could easily be adapted for the application described here. A convenient way of defining a thin film passive device is a passive device that is formed on a substrate using one or more layers, typically a plurality of layers, deposited on the substrate.

Thin film methods for producing single passive elements or combinations of interconnected passive elements are generically represented by Fig. 5, wherein the polysilicon substrate is shown at 51, with a grown oxide layer 52. Resistor body 54, formed from first level metal, has contacts 55 and 56, and lower capacitor plate 58, with contact 59, both comprise buried levels. Upper capacitor plate 60, and inductor spiral 61, are formed last, with contacts not shown. The structure is protected with polyimide layer 63.

The three-layer substrate structure 51 of Fig. 5 is very thick, which

reduces the risk of fracture and other damage during processing. After fabrication of the passive circuit elements, and completion of the IPD, the substrate 51 is thinned to remove the lower polysilicon layer, and the single crystal silicon layer. The final IPD structure is shown in Fig. 6. The preferred thinning step uses chemical mechanical polishing. This well known process combines abrasive polishing with chemical etching. KOH or a suitable alternative etchant is used in the abrasive slurry. The composite wafer is thinned to where only the top polysilicon layer, or a portion of the top polysilicon layer, remains. Removing the entire single crystal layer is highly recommended, since that layer is relatively conductive. A goal of the invention is to provide a highly insulating substrate, which is a favorable platform for IPDs.

Because the single crystal layer (as well as the added polysilicon layer) provides an effective handle for the polysilicon top layer (the IPD layer), the IPD layer may be relatively thin initially. It is not uncommon in IC technology today to thin the starting wafer after wafer fabrication is complete. In many of these cases the substrate is deliberately made thick to survive handling and processing, with a thinning step later in the process to reduce the device profile. In the method described here, the thickness of the IPD layer may be initially the same approximate size as the final substrate thickness. That thickness is preferably 50-200 microns.

The IPD of Fig. 4 is shown implemented according to one embodiment of the invention in Fig. 7. The IPD is formed on one or more of the sites 33 shown in Fig. 3. Polysilicon substrate 71 is shown with thin film inductors  $L_{g1}$ ,  $L_{g2}$ ,  $L_{s}$

and L<sub>D</sub>, and capacitors C<sub>1</sub>, C<sub>2</sub>, and C<sub>D</sub>. MOS transistor 72 is shown in phantom because, while part of the schematic circuit, it is not formed in the IPD. The circuit layout for Fig. 7 is deliberately changed from that of Fig. 3. This circuit and this layout are for the purpose of illustrating a typical type of circuit having passive components. It is an example of a circuit taken from the prior art referenced earlier. No representation as to its effectiveness is made here.

The layout in Fig. 7 is designed with all the inductor elements grouped together. It is known that inductor elements are especially sensitive to ambient conditions, e.g. parasitic signals. This recognition is employed in the design of the active/passive module shown in Fig. 8. The polysilicon substrate 71, with the IPD shown in Fig. 7, has an active IC chip 81 flip-chip mounted over the top of the IPD as shown. Part of the active IC chip is transistor 72. The interconnections in this embodiment are shown as solder bumps for the electrical interconnections S, D, G, V<sub>gs</sub>, V<sub>DS</sub>, P<sub>In</sub>, P<sub>out</sub>, gnd. Off board interconnection sites (not shown) may be provided on the IPD substrate 71. One purpose of the grouping of the inductor devices as shown in Fig. 7 is evident in Fig. 8. The active IC chip is deliberately positioned so as not to overlay the sensitive inductor elements. Thus the stacked substrate arrangement is effectively implemented to save space and provide a compact device module, without compromising the performance of the inductor elements.

Fig. 9 is another view of an IPD MCM, where IPD 91 is shown mounted on a printed circuit board (PCB) 92. An IC chip 93 is shown mounted on the IPD. For simplicity, only one IC chip is shown. Typically there will be more than one.

These IC chips can be an analog device, digital device, mixed signal device, RF device, and/or a micro-electro-mechanical-system (MEMS) based switch or oscillator.

As will be evident from the discussion below, even if the sensitive RF components are segregated in the IPD as described above, other adverse issues remain to be addressed. These have to do with parasitic interactions between the sensitive elements in the IPD and external influences, mainly metal bodies, in the vicinity of the IPD. These adverse influences become more severe as the size, and primarily the thickness, of the IPD chip is reduced. This aspect of the invention cooperates with the expedients described above, it being an objective of the overall invention to shrink the thickness of the IPD MCM.

The conventional means for mounting the MCM to the PCB is solder. Referring again to Fig. 9, a solder bonding layer is shown at 94, with PCB ground plane at 95. The upper surface of the IPD is coated with a ground plane and metal runners for interconnecting the IC chip, typically placed on two levels. These are represented as layer 96 in the figure, and connect to the IC chip through solder bumps 97. The preferred solder connection is different from conventional flip chip connections in which the distance between the flip chip and substrate is kept at a maximum to maintain reliability, i.e. typically 70 to 120 um. The preferred solder connection has a small bump height, under 70 um, to accommodate the flatness variations between the IPD and the IC. Due to the similarity in thermal coefficient of expansion between the active IC and the IPD, there is no concern for solder joint reliability with a shortened distance.

Furthermore, this reduction in distance will also contribute to the reduction of the overall thickness of the module. With this approach that thickness, including the overmolding, made be made small, for example, not exceeding 1.0 mm overall thickness. This reduction in the distance also reduces the parasitic resistance and inductance, to further improve the performance of the RF circuits. Besides solder, other commonly known methods, for example, gold-to-gold, gold-to-aluminum, and conductive adhesives, are also within this scope of this invention.

Wire bonds 98 connect the ground plane and runners to interconnections 99 on the PCB. Beside wire bonding, holes can be etched in the IPD, connecting the metal traces on the top and bottom surfaces of the IPD. This etching process is commonly practiced MEMS manufacturing process. The IPD with through holes is attached to the substrate by conventional flip chip assembly process. This through hole connection can further reduce the interconnect distance between the IPD and the substrate.

It is understood by those in the art that the assembly shown in Fig. 9, as well as that in other figures, is encapsulated in a polymer housing. The plastic housing may be a plastic overmolded body, as in most conventional devices, or may be a plastic cavity package or other suitable protective package.

It is evident that sensitive RF components, such as the inductor indicated schematically at 100, in an IPD with this MCM configuration, are vulnerable to stray capacitances due to the metal covering both surfaces of the IPD.

Fig. 10 shows an IPD MCM embodiment similar to that of Fig. 9 but with the metal both under and over the inductor 100 removed. It is understood that

the inductor 100 represents a section of the IPD where one or more RF sensitive elements are selectively placed, and segregated from other, primarily digital, circuits and circuit components. Inductor components in the IPD may be associated in the same location on the IPD substrate as other components, as in an RF filter circuit. However, it is generally the inductor components in those circuits that are of concern from the standpoint of parasitic electric fields.

The metal underneath the IPD, shown at 94 in Fig. 9, remains under one portion of the IPD, but has been removed at 101 from underneath the portion of the IPD containing sensitive element 100. The metal under that portion of the IPD is replaced with a non-conducting adhesive attachment layer. The non-conducting adhesive is preferably an electrically insulating thermally conducting die attach material such as an alumina filled epoxy.

In addition, the metal on the top of the IPD, shown at 96 in Fig. 9, has been removed from the area overlying the sensitive elements of the IPD, e.g. element 100. The metal remains at 96a, over the digital elements in the IPD. The wire bond is made to contact pad 102. In the embodiment shown the metal layers 96 and 96a are intended as presenting the ground plane, typically a continuous sheet of metal. Some amounts of metal runners used for connecting to solder bumps on the IC may be tolerated over the sensitive elements of the IPD. Accordingly, one of more IC chips may be mounted over these regions. However, a ground plane in these regions is to be avoided. Preferably, the layout is designed with no metal extending along the surface over the sensitive elements.

It should be pointed out that either, or both, of these expedients will improve the electrical performance of the IPD MCM.

Fig. 11 shows an embodiment, similar to that of Fig. 10, with the entire metal layer between the IPD and the PCB removed, and replaced with non-conducting adhesive layer 105. Since the ground plane underneath the IPD is no longer used, the metal ground plane layer, shown at 95 in Fig. 9, is also removed. The resulting structure is a substrate with an IPD attached to the substrate with a non-conducting attachment layer, the IPD having a first portion containing mainly RF components and a second portion containing mainly non-RF components, the IPD having a first surface over the first portion and a second surface under the first portion, at least one digital IC chip mounted on the second portion of the IPD, with the first and second surfaces of the IPD devoid of metal. The portion of the IPD that does not contain RF sensitive devices may also be adapted to support a MEMS device, for example, a MEMS oscillator or a MEMS switch.

Close inspection of the embodiment of Fig. 11 will reveal that the elimination of the metal layer from the PCB allows the overall height of the IPD MCM to be reduced by the thickness of that layer. While that may appear to be a minor change, it can be significant from a commercial standpoint. A commercial IPD MCM has been demonstrated with a design similar to that shown in Fig. 11, having an overall package height from the bottom of the PCB to the top of the encapsulant, of 1.000 mm. This device is expected to be commercially competitive due in part to the small profile.

Fig. 12 shows a section view of a fully assembled IPD MCM product shown generally at 111. PCB 112 is provided with metallization 113 on portions of both the top and bottom. The IPD is shown at 114 and is attached to the PCB by the die attach material 116, using one of the options described above. The IPD is electrically interconnected to the PCB with wire bonds, one of which is shown at 118. The wire is bonded to the top layer of the PCB. Metal via 120 through connects the metal on the top of the PCB with the metal on the bottom. The IPD MCM may then be easily mounted and connected to a system. substrate. An IC chip 122 is shown flip-chip attached to IPD 114. Solder bumps 123 attach and connect the IC chip to metal runners on the IPD. The IC chip may be a digital or RF IC chip. It is usual to provide a ground plane for the IC chips. However, according to the principles set forth above, a ground plane is deliberately absent from the regions of the IPD that overlie inductor elements. In the preferred case, if IC chips are located over the inductor elements, the ground plane is omitted from this region. Also, the I/O interconnections for that IC chip are preferably but not necessarily located near an edge of the IC chip that is not over any inductor elements.

In areas of the PCB with a ground plane directly under an active IC, one or more thermal vias may be placed between the top and bottom metal planes of the PCB to remove heat generated by the IPD MCM during operation. The heat generated by the active IC will pass from the IC onto the IPD, to the alumina filled die attach, to the top ground plane, to the thermal vias (133), to the bottom ground plane, and get dissipated by the system board on which the IPD MCM is

mounted. This is a departure from conventional practice where the ground plane is a continuous plane, spreading out under the IC. However, due to the need to accommodate the inductor elements in the IPD, there is no metal plane under certain RF elements. Therefore, this ground plane may be non-continuous, and can be broken into small pieces that can be strategically placed under the heat generating ICs.

Passive components, for example, capacitors, inductors and resistors, that are too large to be implemented in IPD can be mounted on the substrate using a conventional surface mount process.

The final part of the assembly is the provision of a protective housing for the IPD MCM. Fig. 12 shows an encapsulant 127, a common protective element that consists of a polymer, usually molded over the electrical assembly.

Alternatively, the protective housing may be a metal can, a plastic cavity, or any suitable protective housing. These are well known in the art.

Besides providing miniaturized passive components, the IPD also serves as a technology bridge between IC fabrication process and PCB fabrication process. The leading edge ICs can be fabricated in feature sizes ranging from 1 um to .065 microns (um), using connecting pads ranging in pitch from 30 to 300 um. The IPD is fabricated in less advanced IC tools, for example, thin film sputtering and etch, with feature sizes of 1 to 20 um. These IPD features can seamlessly accommodate the smallest pitch IC connection pads. Conversely, the PCBs lines and traces are fabricated in 10s of um, using plating and etching technology, it can typically accommodate large pitch connection pads, ranging

from 60 to 300 um. An IC, with large connecting pad pitch will be larger in surface area than an IC with smaller connecting pad pitch. It is very common that the connection pads of an IC is the driving factor of the overall size of the IC and not the number of gates or cells. Therefore, the cost of an IC, which is directly proportional to the surface area, will go up if it is to connect directly to a PCB substrate with gross feature sizes, However, with the IPD, which has much finer feature size than the PCB and lower cost per unit area than an IC because of its much simpler fabrication steps, it is a cost effective way to bridge the fine feature capability of the IC and the gross feature capability of the PCBs. Therefore, the IPD acts as a cost effective mechanical interface between the IC and the substrate. One aspect of this can be seen schematically in Fig. 12, where the IPD MCM is shown attached to a system level board 131 with solder balls 132. Comparing the pitch of solder balls 132 with the pitch of solder bumps 123 illustrates the transition just described. The overall height of this package is small, as described above, less than 1.2 mm, and preferably 1.0mm or less, from the bottom plane of PCB 112 to the top of the encasement or overmold 127.

Various additional modifications of this invention will occur to those skilled in the art. All deviations from the specific teachings of this specification that basically rely on the principles and their equivalents through which the art has been advanced are properly considered within the scope of the invention as described and claimed.

# **Brief Description of the Drawing**

- Fig. 1 shows a single crystal silicon starting wafer for preparing a high resistivity IPD substrate;

- Fig. 2 shows the starting wafer with polysilicon deposited;

- Fig. 3 is a view of the polysilicon wafer of the invention showing over 500 IPD sites for building thin film IPDs;

- Fig. 4 is a schematic section view of a typical IPD showing conventional SMT components mounted on a conventional substrate;

- Fig. 5 is a schematic view of a thin film approach to IPD fabrication on one of the sites of the substrate of Fig. 3;

- Fig. 6 is a view of the fabricated IPD after removal of the single crystal silicon handle:

- Fig. 7 is a schematic circuit diagram showing an example of an IPD;

- Fig. 8 shows the IPD with an active IC chip mounted on the IPD:

- Fig. 9 shows another view of an MCM with an IPD carrier substrate and semiconductor IC chip;

- Fig. 10 shows an embodiment of an MCM with an IPD carrier substrate, a semiconductor IC chip selectively placed with respect to sensitive RF components, and metal removed from the lower IPD interface;

- Fig. 11 shows an alternative embodiment of an MCM with an IPD carrier substrate.

- Fig. 12 is a section view of a fully assembled IPD MCM product.

- 1. An integrated passive device multichip module (MCM IPD) comprising:

- a. a substrate,

- b. an IPD attached to the substrate with an attachment layer, wherein at least part of the attachment layer is non-conducting.

- 2. The IPD MCM of claim 1 wherein the entire attachment layer is non-conducting.

- 3. The IPD MCM of claim 1 wherein a first part of the attachment layer is non-conducting and a second part of the attachment layer is conducting.

- 4. The IPD MCM of claim 1 wherein the IPD comprises a first portion containing at least one inductor component and a second portion containing at least one digital component and wherein the part of the attachment layer underneath the first portion of the IPD is non-conducting and the part of the attachment layer underneath the digital components is conducting.

- 5. The IPD MCM of claim 4 wherein the IPD MCM further includes at least one integrated circuit (IC) chip mounted on the top of the IPD.

- 6. The IPD MCM of claim 4 wherein the top of the IPD is selectively covered with a ground plane.

- 7. The IPD MCM of claim 6 wherein the ground plane is selectively placed only on the second portion of the IPD.

- 8. The IPD MCM of claim 1 wherein the non-conducting portion of the attachment layer is electrically insulating thermally conducting die attach material.

- 9. The IPD MCM of claim 1 wherein the IPD comprises a polysilicon wafer substrate with at least one thin film passive device on the polysilicon wafer.

- 10. The IPD MCM of claim 1 wherein the overall thickness of the IPD MCM measured including the thickness of the IPD, the thickness of the IC chip and the thickness of the protective body, is less than 1.2 mm.

# **Abstract of the Disclosure**

The specification describes a multi-chip module (MCM) that contains an integrated passive device (IPD) as the carrier substrate (IPD MCM). Parasitic electrical interactions are controlled at one or both interfaces of the IPD either by eliminating metal from the interfaces, or by selective use of metal in parts of the MCM that are remote from the sensitive device components. The sensitive device components are primarily analog circuit components, especially RF inductor elements. In the IPD layout, the sensitive components are segregated from other components. This allows implementation of the selective metal approach. It also allows parasitic interactions on top of the IPD substrate to be reduced by selective placement of IC semiconductor chips and IC chip ground planes. In preferred embodiments of the IPD MCM of the invention, the IPD substrate is polysilicon, to further minimize RF interactions. The various methods of assembling the module may be adapted to keep the overall thickness within 1.0 mm.

Representative Drawing

Fig. 6

FIG. 2

FIG. 4 (prior art)

FIG. 6