# **PCT**

60/001,279

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

## INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

| (51) International Patent Classification <sup>6</sup> : |    | (11) International Publication Number: | WO 97/04378                |

|---------------------------------------------------------|----|----------------------------------------|----------------------------|

| G06F 1/00, H01L 21/60                                   | A1 | (43) International Publication Date:   | 6 February 1997 (06.02.97) |

US

(21) International Application Number: PCT/US96/11953

(22) International Filing Date: 19 July 1996 (19.07.96)

(30) Priority Data:

60/001,277

20 July 1995 (20.07.95)

60/001,278

20 July 1995 (20.07.95)

US

20 July 1995 (20.07.95)

(71) Applicant: DALLAS SEMICONDUCTOR CORPORATION [US/US]; 4401 South Beltwood Parkway, Dallas, TX 75244-3292 (US).

(72) Inventors: LITTLE, Wendell, L.; 2300 Stonegate Circle, Denton, TX 76205 (US). CURRY, Stephen, M.; 6646 Clearhaven Circle, Dallas, TX 75248 (US). GRIDER, Steven, N.; 2324 Dundee Place, Carrollton, TX 75007 (US). THROWER, Mark, L.; 1415 Pawnee Trail, Carrollton, TX 75007 (US). HASS, Steven, N.; 2514 Bellmeade Drive, Carrollton, TX 75006 (US). BOLAN, Michael, L.; 6241 Misty Trail, Dallas, TX 75248 (US). FIESELER, Ricky, D.; 2764 Salado Trail, Fort Worth, TX 76118 (US). HARRINGTON, Bradley, M.; 2019 Crestover Circle, Carrollton, TX 75007 (US).

(74) Agents: MAXWELL, Roger, L. et al.; Jenkens & Gilchrist, P.C., Suite 3200, 1445 Ross Avenue, Dallas, TX 75202 (US).

(81) Designated States: AL, AM, AT, AU, AZ, BB, BG, BR, BY, CA, CH, CN, CZ, DE, DK, EE, ES, FI, GB, GE, HU, IL, IS, JP, KE, KG, KP, KR, KZ, LK, LR, LS, LT, LU, LV, MD, MG, MK, MN, MW, MX, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, TJ, TM, TR, TT, UA, UG, UZ, VN, ARIPO patent (KE, LS, MW, SD, SZ, UG), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, ML, MR, NE, SN, TD, TG).

#### **Published**

With international search report.

Before the expiration of the time limit for amending the claims and to be republished in the event of the receipt of amendments.

(54) Title: MICROCIRCUIT WITH MEMORY THAT IS PROTECTED BY BOTH HARDWARE AND SOFTWARE

#### (57) Abstract

A secure electronic data module containing a monolithic semiconductor chip of the type having a memory that is protected by a combination of hardware and software mechanisms such that unauthorized access to the data stored in the memory is prevented. The monolithic semiconductor chip comprises a plurality of solder bumps for attaching the chip to a substrate that my be a printed circuit board or another chip; a multi-level interlaced power and ground lines using minimum geometries; and a detection circuit block for detecting an external trip signal that my be produced by a prespecified change in an operating condition brought on by unauthorized accessing, or an internal trip signal that may be produced by shorting of power and ground lines or by a change in an oscillator's frequency, also associated with or appurtenant to unauthorized accessing of the secure memory.

## FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AM | Armenia                  | GB | United Kingdom               | MW | Malawi                   |

|----|--------------------------|----|------------------------------|----|--------------------------|

| AT | Austria                  | GE | Georgia                      | MX | Mexico                   |

| ΑU | Australia                | GN | Guinea                       | NE | Niger                    |

| BB | Barbados                 | GR | Greece                       | NL | Netherlands              |

| BE | Belgium                  | HU | Hungary                      | NO | Norway                   |

| BF | Burkina Faso             | IE | Ireland                      | NZ | New Zealand              |

| BG | Bulgaria                 | IT | Italy                        | PL | Poland                   |

| ВJ | Benin                    | JP | Japan                        | PT | Portugal                 |

| BR | Brazil                   | KE | Kenya                        | RO | Romania                  |

| BY | Belarus                  | KG | Kyrgystan                    | RU | Russian Federation       |

| CA | Canada                   | KP | Democratic People's Republic | SD | Sudan                    |

| CF | Central African Republic |    | of Korea                     | SE | Sweden                   |

| CG | Congo                    | KR | Republic of Korea            | SG | Singapore                |

| CH | Switzerland              | KZ | Kazakhstan                   | SI | Slovenia                 |

| CI | Côte d'Ivoire            | LI | Liechtenstein                | SK | Slovakia                 |

| CM | Cameroon                 | LK | Sri Lanka                    | SN | Senegal                  |

| CN | China                    | LR | Liberia                      | SZ | Swaziland                |

| CS | Czechoslovakia           | LT | Lithuania                    | TD | Chad                     |

| CZ | Czech Republic           | LU | Luxembourg                   | TG | Togo                     |

| DE | Germany                  | LV | Latvia                       | ТJ | Tajikistan               |

| DK | Denmark                  | MC | Monaco                       | TT | Trinidad and Tobago      |

| EE | Estonia                  | MD | Republic of Moldova          | UA | Ukraine                  |

| ES | Spain                    | MG | Madagascar                   | UG | Uganda                   |

| FI | Finland                  | ML | Mali                         | US | United States of America |

| FR | France                   | MN | Mongolia                     | UZ | Uzbekistan               |

| GA | Gabon                    | MR | Mauritania                   | VN | Viet Nam                 |

-1-

# MICROCIRCUIT WITH MEMORY THAT IS PROTECTED BY BOTH HARDWARE AND SOFTWARE

# PRIORITY UNDER 35 U.S.C. §119(e) & 37 C.F.R. §1.78(a)

5 This nonprovisional application claims priority based upon the following prior U.S. Provisional Patent Applications: (i) entitled "Method And Apparatus For Encryption Key Creation," Serial No.: 60/001,277 (Attorney Docket Number 20661/00421), filed July 20, 1995, in the 10 names of Wendell Little and Stephen Curry; (ii) entitled "Microcircuit With Memory That Is Protected by Both Hardware and Software," Serial No.: 60/001,279 (Attorney Docket Number 20661/00420), filed July 20, 1995, in the names of Wendell Little, Rick Fieseler, Steve Hass, and 15 Brad Harrington; (iii) entitled "Single Chip Microprocessor, Math Co-Processor, Random Number Generator, Real-Time Clock, and RAM Having A 1-Wire Interface," Serial No.: 60/001,278 (Attorney Docket Number 20661/00423), filed July 20, 1995, in the names of Wendell 20 Little and Andreas Curiger.

## CROSS-REFERENCE TO RELATED APPLICATIONS

25

This application hereby incorporates by reference the following co-assigned patent applications, concurrently filed herewith, which describe related subject matter:

et al.

Serial No./ <u>Title</u> Inventor(s) Docket No. 20661-00421 Method And Apparatus Schweitzer,

> For Encryption Key Creation

-2-

20661-00423 Single Chip

Little, et al.

Microprocessor, Math Co-Processor, Random Number Generator, Real-Time Clock, and RAM Having A 1-Wire

Interface

20661-00432 Secure Module With Microprocessor And

Little, et al.

Co-Processor

### 5 BACKGROUND OF THE INVENTION

## Technical Field of the Invention

The present invention relates to secure integrated circuits and, in particular, to microcircuits with memory that is protected by both hardware and software.

10

15

20

25

## Description of Related Art

In today's emerging area of electronic commerce, security of data that is stored in a semiconductor memory is a burgeoning issue with which authorized owners of such data must contend. In general, authorized access to electronic data is governed by hardware and software verification schemes involving passwords. personal identification numbers and the like. To further reduce the probability of successful unauthorized access to data, component manufacturers have also resorted to such techniques as data encryption. However, there are many applications wherein security concerns remain high enough that additional security mechanisms may be warranted.

A reliable, efficacious and economical solution to enhanced data security is to provide a combination of physical barriers wherein an intruder must grapple with

-3-

successively overcoming such barriers. Although each physical barrier may itself be rather simple, it can be appreciated that a combination thereof may be a powerful solution wherein an attempt to overcome an outer barrier is designed to thwart successful access to electronic data either by triggering an inner barrier or by destroying the data altogether.

5

10

15

20

25

30

One such physical barrier can be a sealable container within which a semiconductor chip containing memory is disposed. By providing conductive surfaces as part of the container, it is possible in such an arrangement to efficiently integrate both data security and data transmission interfacing. Further, by attaching the semiconductor chip to a substrate disposed within the container using solder bumps, and by encapsulating the chip with a conventional epoxy resin, it can be appreciated that the efficacy of many reverse engineering techniques for determining logic states in the memory cells, for example, backside emission microscopy, is severely curtailed.

Another simple, yet highly effective, physical barrier can be a multi-layered and interlaced conductive grid provided as part of the metallization of the semiconductor chip itself. It can be appreciated that providing an interlaced conductive grid, formed with minimum geometries, can deter effective electron microscopy as well as detect microprobing. Based upon detecting such microprobing of the conductive layers, it would be advantageous to provide a trip circuit that would destroy the data stored in the memory either passively by

-4-

cutting off the internal power supply, or actively by transmitting an erase signal to the memory array.

Furthermore, it would be advantageous to provide a detection/trip circuit as part of the monolithic semiconductor chip, that is capable of detecting a change in any environmental condition associated with an unlawful attempt to gain access. For example, the detection circuit can detect and be tripped by a pre-determined magnitude of change, or by reaching a pre-determined set-point in electromagnetic radiation, chemical composition, ambient pressure, temperature and the like. In addition, by monitoring a real-time oscillator associated with the semiconductor chip, a data erase signal can also be generated should the unlawful entry result in either a change in the frequency of the real-time oscillator.

Although some of the above-mentioned security enhancements have heretofore been extant for sometime, no prior art system is known to have all of the advantages and novel features of the cost-effective combination solution described, and claimed, hereinbelow.

#### SUMMARY OF THE INVENTION

.5

10

15

20

25

30

In one aspect of a presently preferred exemplary embodiment, the present invention includes a housing with a cavity, within which is disposed a substrate with a top surface and a bottom surface; a semiconductor chip of the type having a monolithic integrated microcircuit, the semiconductor chip being affixed to the substrate by a plurality of solder bumps. In another aspect of the present invention, the substrate to which the

semiconductor chip is affixed can be a printed circuit board or another semiconductor chip having additional circuitry.

In a yet another aspect of the present invention, the semiconductor chip comprises a microprocessor with a one-wire interface having a multi-layered interlaced conductive grid, drawn with minimum geometry; and a detection/trip circuit for detecting a change in an environmental condition or in a frequency of a real-time oscillator. The detected change is associated with unauthorized accessing of the electronic data stored in the memory array of the semiconductor chip.

. 5

10

15

20

25

The exemplary embodiments incorporate multiple security techniques to thwart unwanted technical and nontechnical intrusions into the microcircuit and its associated memory. Such security techniques include, but are not limited to a variety and combination of circuit construction techniques, circuit assembly techniques, physical barriers, and circuit software and hardware processes. More specifically, the circuit:

- 1. is hermetically sealed within a stainless steel enclosure. The circuit can also be sealed within a polymer enclosure. If a polymer enclosure is used, a conductive contact surface must be provided for touching the microcircuit to a host circuit.

- 2. contains SRAM memory which is backed by a battery enclosed with the circuitry. Upon tampering with the enclosure around the circuitry, trip circuitry is triggered thereby

-6-

disconnecting the battery's energy with the SRAM. This results in near instantaneous SRAM data destruction.

- 3. can contain a triggerable high/low temperature window circuit. When the temperature is above or below a predetermined temperature the circuit will trigger. Upon the triggering of the temperature circuit, the data in memory will be instantaneously erased.

- 4. can have an interlaced power and ground grid covering the die of the microcircuit. Interlacing the power and ground prohibits 15 probing of the die microcircuitry because power and ground will be shorted by a probe thereby destroying information stored Interlacing power and ground acts as a barrier electron microscope inspection. 20 Furthermore, interlacing is a physical barrier which inhibits effective metal removal with chemical etch techniques because chemical etching of closely interlaced supply and ground lines will short power and ground destroying 25 live SRAM data.

- 5. can have multiple metalized layers over the die circuitry. Each metalized layer can be different metal or non-metal compounds. The compounds can be from the group including polyimide (a nonconductive layer), chromium,

30

-7-

chromium and copper, copper, or solder. Layering of the various compounds will act as a shield to inhibit electron microscope viewing of the die circuitry, will increase the difficulty of circuit dissection and will dissolve at different rates when chemically etched thereby making a controlled etching process extremely difficult.

10

. 5

6. can be encapsulated as a circuit die and printed circuit board. Encapsulation can be with a solid or hollow plastic or polymer barrier. Such a barrier increases the difficulty of penetrating to the microcircuit without destroying data stored in the SRAM memory.

20

7.

15

can have various wrongful entry detection circuits that destroy live SRAM data upon tampering with the sealed enclosure. detection circuits can include, but are not limited to light sensing circuitry, pressure sensitive circuitry, temperature sensitive circuitry, break in internal power sensitive circuitry, gas detection circuitry, electromagnetic wave sensitive circuitry, timed self destruct circuitry and moisture detection circuitry. This detection circuitry may be totally made of hardware so that upon a prescribed detection SRAM memory is destroyed. The detection circuitry can also be partially

30

25

5

software controlled so that a plurality of software selectable detection events must occur prior to destruction of data within SRAM. The exemplary embodiment has a circuit which detects a change in physical environment and destroys the data in SRAM memory based on what is detected.

- 8. can incorporate solder bump technology. Solder

bump technology allows the die circuitry to be

mounted on a circuit card wafer side up instead

of circuit side up with leads from the top of

the die circuitry down to the circuit card.

Inspection of the circuitry and memory data on

the die is made extremely difficult because the

ease of destroying the circuitry and/or the

data within memory.

- 9. can incorporate flip-chip technology. Flip20 chip technology is used with solder bump technology wherein the die circuitry is mounted with the chip flipped such that the die circuitry faces the circuit board it is mounted to and the die wafer faces away from the circuit board.

- 10. can incorporate hardware, software and/or firmware for timed access authorization which makes sure that circuit operations occur within a predetermined amount of time.

WO 97/04378

. 5

11. can incorporate a timing oscillator that must run within a predetermined frequency range or else data within memory will be destroyed. This is useful because the oscillator may speed up or slow down when the circuit is subjected to hot or cold conditions or when the circuitry is being probed or reverse engineered.

Combinations and Permutations of a plurality of the

above mentioned security techniques provide exemplary

microcircuits that can be combined with a memory circuit

and a one-wire circuit so that the memory and the actual

circuitry is protected from unwarranted intrusions.

# 15 BRIEF DESCRIPTION OF THE DRAWINGS

A more complete understanding of the present invention may be had by reference to the following Detailed Description when taken in conjunction with the accompanying Drawings wherein:

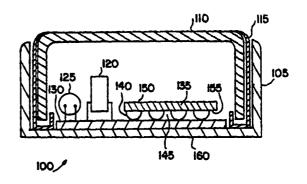

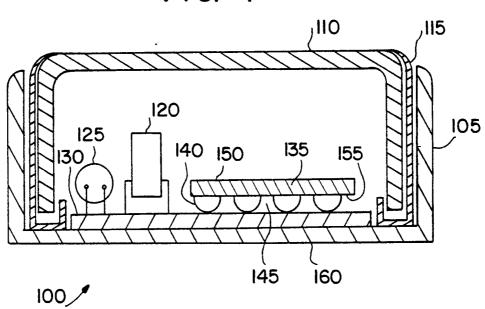

- 20 FIG. 1 is a cross-sectional view of an exemplary embodiment of an electronic data module that may be used for encasing a microcircuit chip with memory that is protected by both hardware and software in accordance with the teachings of the present invention;

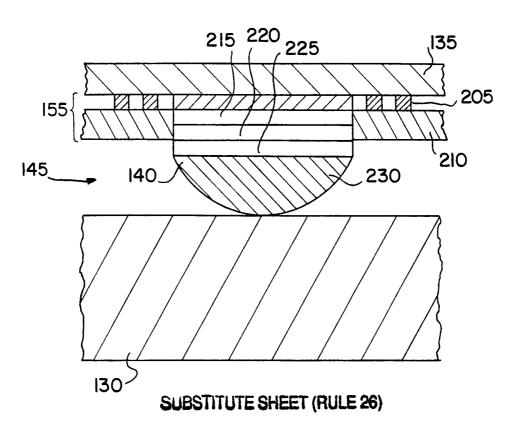

- 25 FIG. 2 is an enlarged cross-sectional view of a presently preferred exemplary embodiment of a solder bump;

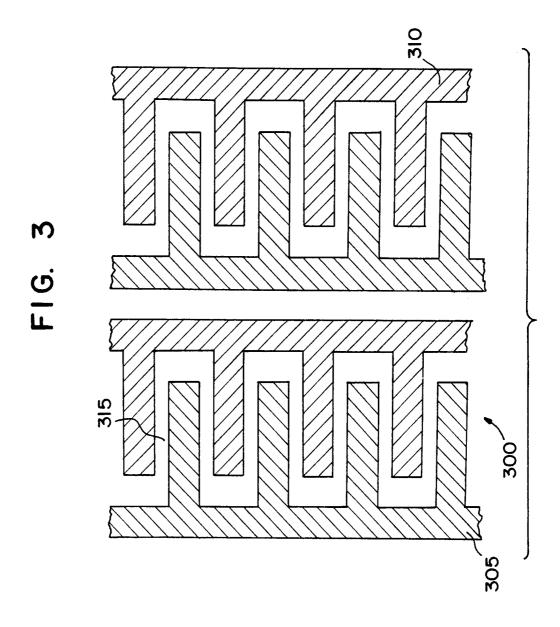

- FIG. 3 is a plan view of a portion of an exemplary interlaced conductive grid;

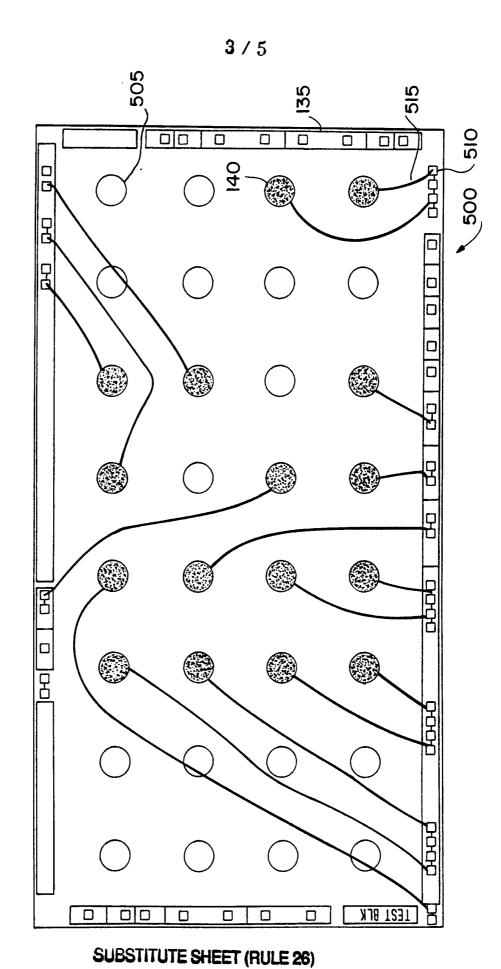

- FIG. 4 is a top plan view of an exemplary monolithic semiconductor chip having a plurality of solder bumps;

-10-

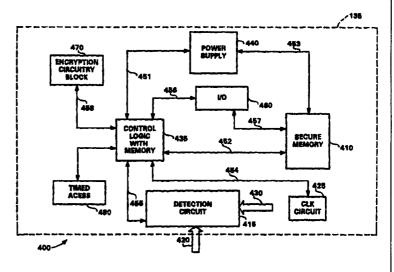

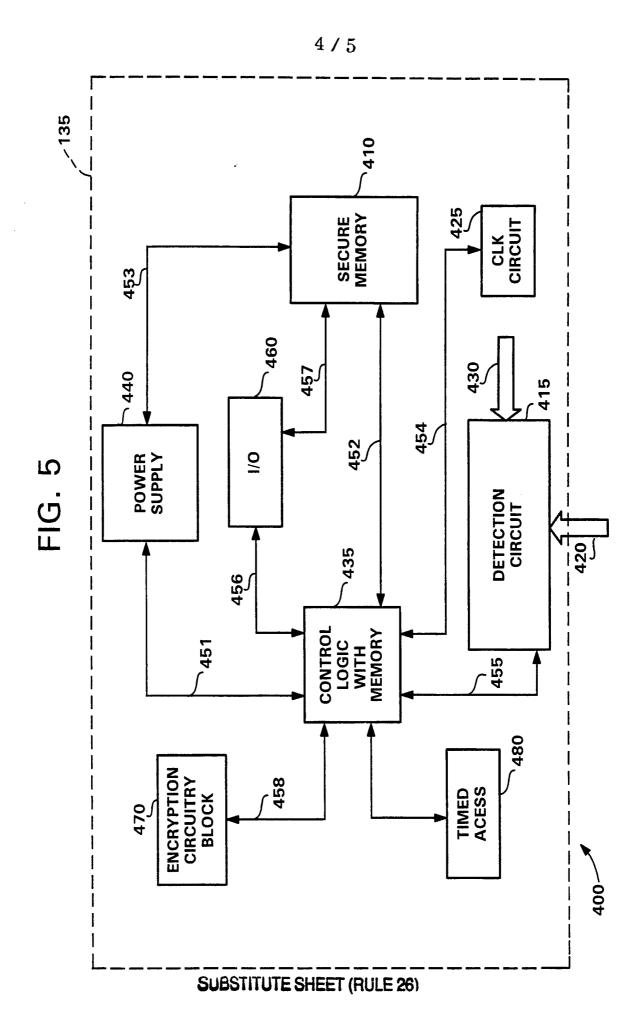

FIG. 5 illustrates a functional block diagram of an exemplary monolithic semiconductor chip; and

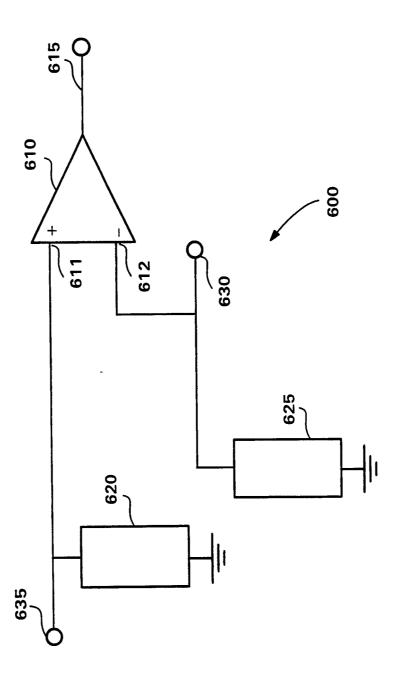

FIG. 6 illustrates a block diagram of a presently preferred exemplary embodiment of a temperature detection circuit used in accordance with the teachings of the present invention.

#### DETAILED DESCRIPTION OF THE DRAWINGS

.5

10

15

20

25

30

Referring now to the Drawings wherein like or similar elements are designated with identical reference numerals throughout the several views, and wherein the various elements depicted are not necessarily drawn to scale, and more particularly to FIG.1, there is shown a crosssectional view of a presently preferred exemplary embodiment of an electronic data module 100 that may be used for encasing a microcircuit chip with memory that is protected by both hardware and software mechanisms according to the teachings of the present invention. The electronic data module 100, which may be substantially token-shaped or button-shaped, is designed to hermetically house a monolithic semiconductor chip 135 that may comprise a host of circuit elements such as memory, microprocessors, multiplexing circuitry and electrostatic discharge protection circuitry. A housing 160 of the electronic data module 100 preferably comprises a male conductive surface 110 and a female conductive surface 105 that are designed so that the male conductive surface 110 is inserted into the female conductive surface 105 which is lined with an insulator 115. In a presently preferred exemplary embodiment, both the female conductive surface

5

10

15

20

25

30

105 and the male conductive surface 110 comprise stainless steel surfaces.

According to the teachings of the present invention, the monolithic semiconductor chip 135 is affixed to a substrate 130 by means of a plurality of solder bumps, for example, solder bump 140, such that a top passivated side 155 of the monolithic semiconductor chip 135 is positioned facing the substrate 130. According to the present invention, a back side or bulk side 150 of the monolithic semiconductor chip 135 is preferably encapsulated with a conventional epoxy resin. Further, the gap 145 between the monolithic semiconductor chip 135 and the substrate 130 is also preferably filled with a conventional resinous filling medium by capillary phenomenon.

Also affixed to the substrate 130 of the presently preferred exemplary electronic data module 100 are a crystal 125 to at least provide a time base, and a battery 120. It can be readily appreciated that the substrate 130 of the present invention may be a conventional printed circuit board or the like. Also, in an additional aspect of the present invention, the substrate 130 may be another semiconductor chip disposed on a printed circuit board that is affixed to the cavity created by the housing 160. In a yet another aspect, the substrate 130 may be a printed circuit board disposed on a top surface of another semiconductor chip, thereby creating a "semiconductor sandwich" in the cavity of the housing 160.

As will be appreciated by those skilled in the art upon reference hereto, in accordance with the teachings of the present invention, enhanced security and integrity of electronic data that may be stored in the memory of the

-12-

monolithic semiconductor chip 135 is realized from innovative aspects pertaining to both the physical barriers and detection circuitry that may be tripped by a change in an environmental condition or in an internal operating condition that may be associated with unauthorized accessing of the stored electronic data. These novel aspects of the present invention will be discussed hereinbelow in reference to the rest of the drawings.

5

10 FIG. 2 depicts an enlarged cross-sectional view of a presently preferred solder bump 140, a plurality of may be used for affixing the semiconductor chip 135 to the substrate 130. It is seen that the top passivated side 155 of the monolithic 15 semiconductor chip 135 comprises an interlaced conductive grid 205 of power and ground lines (shown in FIG. 3) that may preferably be interspersed with a di-electric substance such as Silicon Dioxide  $(SiO_2)$ . Although it is shown in this FIG. that the interlaced conductive grid 205 20 is a single layer, it is contemplated herein that it will be obvious to persons of ordinary skill in the art to fabricate and employ a multi-level interlaced conductive grid to further enhance the security and integrity of stored electronic data according to the teachings of the 25 present invention. In addition, it is envisaged that the interlaced conductive grid 205, which can be either single-level, double-level, or multi-level, may be fabricated according to known processes including but not limited to sputtering of such conventional metals and 30 compositions thereof as Aluminum, Titanium, Tungsten or Titanium-Tungsten.

5

10

15

20

25

30

The interlaced conductive grid 205 is preferably fabricated using minimum design geometries, that is, minimum dimensions for lines and spaces to be used for a specific semiconductor process architecture, so as to specifically minimize at least two things. First, the probability of reaching inner conductive layers of the storage memory for the purpose of reading the logic levels corresponding to the stored data via the various conventional failure analysis techniques such as emission electron microscopy, voltage-contrast or liquid crystal methods, beam-induced current detection et cetera, is minimized because of the physical barrier that is created by the interlaced conductive grid 205. The detector circuits of these conventional techniques are designed to sense such subtle differences as associated with the presence of charge on a programmed memory cell in photon emission, or voltage, or induced current, or visible spectral phase etc. However, the presence of the interlaced conductive grid 205 effectively creates a resistive barrier that will interfere with the detection signal so that reliable reading of the logic levels of the storage memory is impeded.

Furthermore, because of the tight geometries of the interlaced conductive grid 205, the probability of successfully de-layering the monolithic semiconductor chip 135, using conventional chemical etching techniques or focused-ion beam ("FIB") methods is also minimized. It will become obvious to one skilled in the art upon reference hereto that the interlaced conductive grid 205 thereby enhances the security of the data stored in the

memory associated with the exemplary electronic data module 100 (shown in FIG. 1).

Continuing to refer to FIG. 2, therein is shown a polyimide layer 210 covering the interlaced conductive grid 205, in accordance with the teachings of the present invention. The exemplary solder bump 140 is preferably a multi-layer structure having a Chromium layer 215 abutting the interlaced conductive grid layer 205, a Chromium-Copper alloy layer 220 deposited on the Chromium layer 215, and a Copper layer 225 deposited on the Chromium-Copper alloy layer 220. The multi-layer structure is then capped with conventional solder material 230 thereby creating the "bump," with which the semiconductor chip 135 is affixed to the substrate 130.

5

10

15

20

25

30

Using a plurality of solder bumps, for example, the exemplary solder bump 140, for adhesion between the semiconductor chip 135 and the substrate 130 achieves at least two purposes. First, because of direct bonding of the semiconductor chip 135 to the substrate 130, precious board area savings are realized by ultimate reduction in packaged chip foot print. For example, in a presently preferred exemplary embodiment of the present invention, a Silicon-to-board ratio of over 40% is achieved. Second, because the monolithic semiconductor chip 135 is facing down, that is, it is "flipped" on the substrate 130, access to conductive layers of the semiconductor chip 135 by conventional de-layering is severely impeded. Further, any detection of backside emission that may be possible in some sophisticated emission microscopy systems is negated by preferably utilizing epitaxial Silicon

.5

10

15

20

25

30

substrate with suitable modification of dopant characteristics thereof.

Referring now to FIG. 3, therein is shown a plan view, generally at 300, of a portion of an exemplary interlaced conductive grid (reference numeral 205 in FIG. in accordance with the teachings of the present invention. As discussed hereinabove, although a single layer of the interlaced conductive grid 205 is seen, it will be obvious to skilled persons in the art that the grid 205 may in fact be a multi-layer structure, with a suitable di-electric substance in a space 315 between a power line 305 and a ground 310 to prevent electrical shorts in the chip 135. Further, although the power line 305 and the ground 310 are shown as interweaved comb-like structures, it is obvious that virtually any geometric shape, regular or irregular, for example, a serpentine or helical shape, may be used for fabricating the interlaced conductive grid 205 of the present invention.

FIG. 4 depicts a top plan view, generally at 500, of an exemplary monolithic semiconductor chip 135 having a plurality of solder bumps, for example, solder bump 140. The monolithic semiconductor chip 135 preferably has a plurality of bonding pads, for example, bonding pad 510, situated preferably along the outer edges thereof. It is seen that a first sub-plurality of solder bumps, for example, solder bump 140, are electrically connected via connectors, for example, connector 515, to a corresponding first sub-plurality of bonding pads, for example, bonding pad 510. It is also seen that in the exemplary monolithic semiconductor chip 135, a second sub-plurality of solder bumps, for example, solder bump 505, are not electrically

connected to any bonding pads thereof. The second subplurality of solder bumps are thus preferably provided for adding structural stability between the semiconductor chip 135 and the substrate 130 (shown in FIG. 1).

. 5

10

15

20

25

30

Referring now to FIG. 5, therein is illustrated a block diagram, generally at 400, of an exemplary embodiment of a monolithic semiconductor chip 135, in accordance with the teachings of the present invention. Functionally, the semiconductor chip 135 comprises a control logic with memory block 435 capable of processing signals generated by a clock circuit block 425, a detection/trip circuit block 415, an encryption circuitry block 470, an input/output block 460, and a secure memory block 410. As is well known in the art, each of these functional blocks of the monolithic semiconductor chip 135 is powered by a power supply block 440.

The secure memory block 410 can preferably be a static random access memory (SRAM) array that may be backed by the power supply 440 so that SRAM is rendered non-volatile. According to the teachings of the present invention, it is the secure memory block 410 that contains valuable electronic data, wherein unauthorized access thereto is hindered by the novel combination of physical barriers, and hardware and software security systems disclosed herein.

The detection/trip circuit block 415 is preferably provided to process either an internal trip signal 430 or an external trip signal 420. The external trip signal 420 may be produced by a variety of transducers that are capable of converting a pre-specified change in an ambient environmental condition into the trip signal 420. It is

therefore contemplated herein that it is within the scope of the present invention to provide a detection/trip circuit capable of detecting a change in electromagnetic radiation, pressure, temperature, and ambient chemical composition. Further, it is envisaged that contemplated electromagnetic radiation changes detectable over broad ranges of spectra including, for example, visible light, infra-red or ultra-violet waves. In addition, the contemplated chemical composition changes for example, gaseous composition changes, include, moisture content changes, or chemical changes resulting from etching and other de-layering techniques.

5

10

15

20

25

Upon detection of the external trip signal 420 by the detection/trip circuit block 415, and upon communicating such detection over a signal communication path 455 to the control logic/memory block 435, the control logic/memory block 435 produces a block erase signal that transmitted over a signal communication path 452 to the secure memory block 410 in order to erase the electronic data contained therein. The electronic data in the secure memory block 410 may preferably be encrypted application of an encryption circuitry block 470 in response to a logic signal produced by the control logic/memory block 435. The encryption circuitry block 470 may preferably contain such circuits as a random number generator (not shown), a circular redundancy check (CRC) equation generator (not shown) and a data encoder (not shown).

It will be understood upon reference hereto that upon detecting a change in an ambient condition or attainment of an associated set-point by the detection/trip circuit

block 415, it is also possible in another embodiment of the present invention to passively destroy the electronic data contained in the secure memory block 410 by simply cutting off a power line 453 disposed between the power supply 440 and the secure memory block 410.

5

10

15

20

25

30

Continuing to refer to FIG. 5, it may be seen that the detection circuit block 415 is also preferably provided with the capability of processing the internal trip signal 430 that may be produced by a frequency change in an oscillator associated with the clock circuit block 425, or by an elapse of certain time as detected by a timed access block 480, or by a loading on the interlaced power line (reference numeral 305 in FIG. 3) that may be encountered in a reverse-engineering technique, for example, optical beam induced current ("OBIC"), electron beam induced current ("EBIC") or light induced voltage alteration ("LIVA") techniques. Once the internal trip signal 430 is detected by the detection/trip circuit block 415, the control logic/memory block 435 may then apply suitable logic to either actively block erase the secure memory block 410 or passively lose data therein by shutting off power thereto.

As will be appreciated by the persons of ordinary skill in the art, although the detection/trip circuit block 415 is shown as a single functional entity in this FIGURE, it will be obvious upon reference hereto that multiple detection/trip circuits, each circuit being optimized for detecting a pre-determined change in a particular operating condition, may be used in a single embodiment of the present invention.

-19-

FIG. 6 illustrates a functional block diagram of a presently preferred exemplary temperature detection/trip circuit, generally designated by reference numeral 600, used in accordance with the teachings of the present invention. It can be seen that a voltage comparator 610 forms the critical functional block of the temperature sense/trip circuit in this embodiment. The comparator 610 has as its inputs a VPTAT ("Voltage Proportional To Absolute Temperature") signal 635 at its positive terminal 611 and a VBGOUT ("Band-Gap Voltage OUTput") signal 630 at its negative terminal 612.

5

10

15

20

25

30

Continuing to refer to FIG. 6, it can be observed that the VBGOUT signal 630, which functions as a reference voltage for the comparator 610, is produced by a band-gap reference block 625. As is known in the art, the band-gap reference block 625 may be implemented advantageously the voltage-temperature coefficients of bipolar junction transistors (not shown). Moreover, silicon fuses (not shown) are preferably used for providing a trimming function whereby the magnitude of the VBGOUT signal 630 may be altered depending upon the user's need. In the presently preferred exemplary embodiment, the bandgap reference block 625 is designed so that an untrimmed set-point of -55 °C (or, 218 °K) corresponds to a magnitude of 1.25V for the VBGOUT signal 630.

Still continuing to refer to FIG. 6, a temperature sense block 620 produces the VPTAT signal 635. The active devices (not shown) in the block 620 are designed such that a linear relationship between the voltage produced and the temperature of the monolithic semiconductor chip 135 (shown in FIG. 5) is satisfied. In the presently

-20-

preferred exemplary embodiment, it can be seen that the following equation holds:

VPTAT = 1.25(T/218 oK).

5

10

15

20

25

In the general operation, if the magnitude of the VPTAT signal 635 is lower than that of the VBGOUT signal 630 (which remains constant over a range of temperature), an output, DESTRUCT signal 615, of the comparator 610 is set to a logic 0. This logic 0 of the DESTRUCT signal 615 may be interpreted by the control logic/memory block 435 (shown in FIG. 5) as a command to erase the contents of the secure memory 410 (shown in FIG. 5). On the other hand, if the magnitude of the VPTAT signal 635 is greater than that of the VBGOUT signal 630, the DESTRUCT signal 615 is set to a logic 1, which is then interpreted by the control logic/memory block 435 such that no erase signal is produced therefrom.

Furthermore, although not shown in this FIG., it can be readily understood by those skilled in the art that the function of the comparator 610 may be coupled in a conventional manner to a timer arrangement such that the voltage comparison may be done only at certain predetermined intervals. In the presently preferred exemplary embodiment, a 1-second timer and a 16 KHZ clock are operably coupled to the comparator 610 wherein the decision to compare the VPTAT signal 635 with the VBGOUT signal 630 is taken once every second. Obviously, many implementational variations can be had, depending upon particular user needs.

Although a preferred embodiment of the present invention has been illustrated in the accompanying Drawings and described in the foregoing Detailed

5

10

15

20

-21-

Description, it will be understood that the invention is not limited to the embodiment disclosed, but is capable of numerous rearrangements, modifications substitutions without departing from the spirit of the invention as set forth and defined by the following claims. For example, as a further enhancement to the presently preferred exemplary embodiment, it would be advantageous to structure the secure memory 410 (shown in FIG. 5) into a plurality of segments wherein one or more segments are intentionally left vacant when the data is stored in the rest, and further wherein the data periodically migrates to the unoccupied segments. Clearly, when coupled with the combination of hardware and software barriers disclosed hereinabove, the "fluid" data in the secure memory 410 is even more impervious to unauthorized access. Additionally, the substrate 130 (shown in FIG. 1) can be another semiconductor chip to which the monolithic semiconductor chip 135 may be bonded via the solder bumps 140, thereby integrating security with added functionality such as, for example, increased memory capacity. It is therefore envisaged that these and other modifications and enhancements are within the scope of the present invention as set defined hereinbelow.

WO 97/04378

. 5

10

#### WHAT IS CLAIMED IS:

- 1. A secured data module apparatus comprising:

- a housing with a cavity;

- a substrate with a top surface and a bottom surface, said substrate being disposed in said cavity;

- a semiconductor chip comprising a monolithic integrated circuit, said semiconductor chip having a passivated side and a bulk side, wherein said passivated side is affixed to said top surface of said substrate; and

affixing means for affixing said passivated side of said semiconductor chip to said top surface of said substrate.

- 15 2. The secured data module apparatus of claim 1, wherein said housing comprises a metallic container.

- 3. The secured data module apparatus of claim 1, wherein said affixing means comprises a plurality of solder bumps.

- 4. The secured data module apparatus of claim 1, wherein said affixing means further comprises:

a plurality of bonding bumps;

each of said plurality of bonding bumps further comprising at least one of a chromium layer, a combination layer having chromium and copper, and a copper layer; and

wherein each of said plurality of bonding bumps is covered with an amount of bonding material.

-23-

5. The secured data module apparatus of claim 1, wherein said monolithic integrated circuit comprises at least a memory, said at least a memory at least for storing an encryption key, said encryption key for controlling an operation, said operation being at least one of reading a value from said monolithic integrated circuit and writing a value to said monolithic integrated circuit.

10 6. The secured data module apparatus of claim 1, wherein said monolithic integrated circuit further comprises at least a register, said at least a register for storing a value, said at least a register being write-protected after storing a value.

15

20

25

- 5

- 7. The secured data module apparatus of claim 1, wherein said monolithic integrated circuit further comprises a trip circuit, said trip circuit being actuatable upon detection of a change in an operating condition, said trip circuit at least for controlling an operation.

- 8. The secured data module apparatus of claim 7, wherein said change in said operating condition comprises a change in temperature.

- 9. The secured data module apparatus of claim 7, wherein said change in said operating condition comprises a change in humidity.

- 10. The secured data module apparatus of claim 7, wherein said change in said operating condition comprises a change light intensity.

- 5 11. The secured data module apparatus of claim 7, wherein said change in said operating condition comprises a change in pressure.

- 12. The secured data module apparatus of claim 7,

wherein said change in said operating condition comprises

a change in electromagnetic radiation.

- 13. The secured data module apparatus of claim 7, wherein said change in said operating condition comprises a change in ambient gas composition.

15

20

25

- 14. The secured data module apparatus of claim 7, wherein said change in said operating condition comprises a change in a frequency associated with a real-time oscillator, said real-time oscillator forming a portion of said monolithic integrated circuit.

- 15. The secured data module apparatus of claim 1, wherein said monolithic integrated circuit comprises a first metal layer, a second metal layer and a third metal layer, each metal layer being substantially horizontal to the other metal layers.

- 16. The secured data module apparatus of claim 15,30 wherein said first metal layer and said second metal layer

-25-

for providing electrical paths for signals, said third metal layer at least for forming a metallic barrier.

17. The secured data module apparatus of claim 16, wherein said third metal layer comprises a ground line having approximately zero volts and a power line having a voltage level, said ground line and said power line forming an interlaced grid, said interlaced grid at least for detecting probing.

10

5

18. The secured data module apparatus of claim 7, wherein said operation comprises erasing a memory, said memory forming a portion of said monolithic integrated circuit, said memory at least for storing data.

15

19. The secured data module apparatus of claim 14, wherein said operation comprises erasing a memory, said memory forming a portion of said monolithic integrated circuit, said memory at least for storing data.

20

25

- 20. In a secure data access system with a monolithic integrated circuit having a passivated side and a substrate side, the monolithic integrated circuit being operably connectable to an interface unit for transferring data, the monolithic integrated circuit comprising:

- a memory, said memory for storing at least a value;

- a trip circuit operably coupled to said memory, said trip circuit being actuatable upon detecting a change in an operating condition, said trip circuit at least for controlling an operation; and

a plurality of metal layers, said plurality of metal layers at least for providing electrical paths of signals, at least one of said plurality of metal layers being electrically coupled to at least one of said memory and said trip circuit.

- 21. The monolithic integrated circuit of claim 20 being adapted for coupling with a substrate, the monolithic integrated circuit further comprising:

- a microprocessor, said microprocessor operably coupled to said memory;

5

20

25

an input/output bus, said bus at least for providing signals to the interface unit, said bus operably connected to said microprocessor and said memory;

a plurality of bonding bumps disposed on the passivated side, at least one of said plurality of bonding bumps being electrically connected to said input/output bus; and

wherein each of said plurality of bonding bumps is affixed to said substrate.

- 22. The monolithic integrated circuit of claim 20, wherein said change in operating condition comprises a change in temperature.

- 23. The monolithic integrated circuit of claim 20, wherein said change in operating condition comprises a change in humidity.

-27-

- 24. The monolithic integrated circuit of claim 20, wherein said change in operating condition comprises a change in light intensity.

- 5 25. The monolithic integrated circuit of claim 20, wherein said change in operating condition comprises a change in pressure.

- 26. The monolithic integrated circuit of claim 20, wherein said change in operating condition comprises a change in electromagnetic radiation.

- 27. The monolithic integrated circuit of claim 20, wherein said change in operating condition comprises a change in gas composition.

15

20

- 28. The monolithic integrated circuit of claim 20, wherein said plurality of metal layers comprises a first metal layer, a second metal layer and a third metal layer, and further wherein each metal layer is substantially horizontal to the other metal layers.

- 29. The monolithic integrated circuit of claim 28, wherein at least one of said first metal layer, said second metal layer and said third metal layer comprises a ground line and a power line, said ground line having approximately zero volts and said power line having a voltage level, said ground line and said power line forming an interlaced grid, said interlaced grid at least for detecting probing.

-28-

- 30. The monolithic integrated circuit of claim 20, wherein said operation comprises erasing said memory.

- 31. The monolithic integrated circuit of claim 21

5 adapted to be disposed in a container of the type having a first conductive cover and a second conductive cover, wherein said input/output bus further comprises a ground path and a signal path, said ground path being connected to the first conductive cover and said signal path being connected to the second conductive cover.

1/5

FIG. I

FIG. 2

WO 97/04378

FIG. 6

SUBSTITUTE SHEET (RULE 28)

### INTERNATIONAL SEARCH REPORT

Inter. nal Application No PCT/US 96/11953

A. CLASSIFICATION OF SUBJECT MATTER IPC 6 G06F1/00 H01L21/60

According to International Patent Classification (IPC) or to both national classification and IPC

#### **B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols) IPC 6 G06F H04L G06K H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

| ~   | DOCHMENTS | CONCIDEDED | TO BE RELEVANT |

|-----|-----------|------------|----------------|

| · • | DOCUMENTS | CONSIDERED | 10 DE KELEVANI |

| Citation of document, with indication, where appropriate, of the relevant passages                                   | Relevant to claim No.                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EP,A,0 417 447 (IBM) 20 March 1991                                                                                   | 1-3,5-8,<br>12,15,<br>17-19                                                                                                                                                                                                                                              |

| see abstract; figures 1-3                                                                                            | 1, 13                                                                                                                                                                                                                                                                    |

| see column 1, line 1 - column 5, line 52                                                                             | 20,22,<br>26,29,30                                                                                                                                                                                                                                                       |

| EP,A,O 529 503 (HEWLETT PACKARD CO) 3<br>March 1993                                                                  | 1-3,5-8,<br>12,15,<br>17-20,<br>22,25,<br>28-31                                                                                                                                                                                                                          |

| see abstract; figures 1,4,6<br>see column 2, line 1 - column 3, line 41<br>see column 6, line 35 - column 7, line 14 | 20 01                                                                                                                                                                                                                                                                    |

| -/                                                                                                                   |                                                                                                                                                                                                                                                                          |

|                                                                                                                      | EP,A,0 417 447 (IBM) 20 March 1991  see abstract; figures 1-3 see column 1, line 1 - column 5, line 52  EP,A,0 529 503 (HEWLETT PACKARD CO) 3 March 1993  see abstract; figures 1,4,6 see column 2, line 1 - column 3, line 41 see column 6, line 35 - column 7, line 14 |

| X | Further documents are listed in the continuation of box C. |

|---|------------------------------------------------------------|

X Patent family members are listed in annex.

- \* Special categories of cited documents:

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier document but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- document referring to an oral disclosure, use, exhibition or other means

- \*P" document published prior to the international filing date but later than the priority date claimed

- "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- "&" document member of the same patent family

Date of the actual completion of the international search

O Docombon 1006

Date of mailing of the international search report 2 0, 12, 96

9 December 1996

Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Authorized officer

Powell, D

Form PCT/ISA/210 (second sheet) (July 1992)

2

# INTERNATIONAL SEARCH REPORT

Inte onal Application No

PCT/US 96/11953

|             |                                                                                               | PCT/US 96/11953       |

|-------------|-----------------------------------------------------------------------------------------------|-----------------------|

| C.(Continua | ation) DOCUMENTS CONSIDERED TO BE RELEVANT                                                    |                       |

| Category °  | Citation of document, with indication, where appropriate, of the relevant passages            | Relevant to claim No. |

| Y           | GB,A,2 182 467 (NCR CO) 13 May 1987                                                           | 20,22,<br>25,28-31    |

|             | see abstract; figures 3,14 see page 1, line 1 - line 109 see page 6, line 1 - page 7, line 35 |                       |

| A           |                                                                                               | 1,5-8,<br>11,17-19    |

| A           | EP,A,O 256 357 (IBM) 24 February 1988<br>see abstract                                         | 4,21                  |

| A           | US,A,5 053 992 (GILBERG ET AL) 1 October<br>1991<br>see abstract                              | 10,<br>17-20,24       |

| A           | US,A,5 072 331 (THIELE ET AL) 10 December 1991                                                |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

|             |                                                                                               |                       |

2

Form PCT/ISA/218 (continuation of second sheet) (July 1992)

## INTERNATIONAL SEARCH REPORT

information on patent family members

Inte onal Application No

PCT/US 96/11953

| Patent document<br>cited in search report | Publication date | Patent family<br>member(s)                                                                                                                                  | Publication date                                                                                             |

|-------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| EP-A-0417447                              | 20-03-91         | US-A- 502739<br>JP-A- 310553<br>JP-B- 708245<br>US-A- 515962                                                                                                | 8 02-05-91<br>9 06-09-95                                                                                     |

| EP-A-0529503                              | 03-03-93         | JP-A- 525936                                                                                                                                                | 9 08-10-93                                                                                                   |

| GB-A-2182467                              | 13-05-87         | CA-A- 126524<br>DE-A- 363593<br>FR-A- 258960<br>JP-A- 6211704<br>US-A- 469135                                                                               | 8 07-05-87<br>2 07-05-87<br>7 28-05-87                                                                       |

| EP-A-0256357                              | 24-02-88         | DE-D- 378777<br>DE-T- 378777<br>JP-A- 6304582<br>US-A- 513446                                                                                               | 2 05-05-94<br>6 26-02-88                                                                                     |

| US-A-5053992                              | 01-10-91         | AT-T- 13935<br>AU-B- 63544<br>AU-A- 848549<br>CA-A,C 205230<br>DE-D- 6912019<br>DE-T- 6912019<br>EP-A- 047946<br>ES-T- 208797<br>IE-B- 6279<br>JP-A- 425889 | 1 18-03-93<br>1 09-04-92<br>2 05-04-92<br>0 18-07-96<br>0 31-10-96<br>1 08-04-92<br>5 01-08-96<br>9 08-03-95 |

| US-A-5072331                              | 10-12-91         | EP-A- 051043<br>JP-A- 515879                                                                                                                                |                                                                                                              |