(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3896112号

(P3896112)

(45) 発行日 平成19年3月22日(2007.3.22)

(24) 登録日 平成18年12月22日(2006.12.22)

(51) Int.C1.

F 1

|             |           |            |   |

|-------------|-----------|------------|---|

| HO1L 23/14  | (2006.01) | HO1L 23/14 | S |

| HO1L 23/32  | (2006.01) | HO1L 23/32 | D |

| HO1L 25/065 | (2006.01) | HO1L 25/08 | B |

| HO1L 25/07  | (2006.01) |            |   |

| HO1L 25/18  | (2006.01) |            |   |

請求項の数 19 (全 40 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2003-428888 (P2003-428888)  |

| (22) 出願日  | 平成15年12月25日 (2003.12.25)      |

| (65) 公開番号 | 特開2005-191172 (P2005-191172A) |

| (43) 公開日  | 平成17年7月14日 (2005.7.14)        |

| 審査請求日     | 平成16年12月2日 (2004.12.2)        |

|           |                                             |

|-----------|---------------------------------------------|

| (73) 特許権者 | 500174247<br>エルピーダメモリ株式会社<br>東京都中央区八重洲2-2-1 |

| (74) 代理人  | 100077838<br>弁理士 池田 篤保                      |

| (74) 代理人  | 100082924<br>弁理士 福田 修一                      |

| (74) 代理人  | 100129023<br>弁理士 佐々木 敬                      |

| (72) 発明者  | 西尾 洋二<br>東京都中央区八重洲二丁目2番1号 エル<br>ピーダメモリ株式会社内 |

| (72) 発明者  | 船場 誠司<br>東京都中央区八重洲二丁目2番1号 エル<br>ピーダメモリ株式会社内 |

最終頁に続く

(54) 【発明の名称】半導体集積回路装置

## (57) 【特許請求の範囲】

## 【請求項1】

チップセットが搭載されたマザーボードと、当該マザーボードに実装され、かつ前記チップセットに接続されるメモリ部とを備える半導体集積回路装置において、

前記メモリ部として複数のDRAMチップを互いに積層した積層DRAMを用い、

前記積層DRAMを前記マザーボードに実装するためにインタポーラを用い、

当該前記インタポーラは、前記積層DRAMと前記チップセットとを電気的に接続する配線を含むシリコン部と、当該シリコン部の下側に設けられた当該シリコン部と実質上同じサイズの印刷回路基板とを有し、

当該印刷回路基板に前記配線に対して電位基準を与えるレファレンスプレーンが設けられることを特徴とする半導体集積回路装置。

## 【請求項2】

請求項1に記載の半導体集積回路装置において、

前記積層DRAMと前記インタポーラとの間に前記積層DRAMと前記チップセットとの間の信号授受を仲介するインターフェースLSIをさらに備え、

該インターフェースLSIと前記チップセットとが、前記インタポーラ及び前記マザーボードを介してポイント・トゥ・ポイント接続されていることを特徴とする半導体集積回路装置。

## 【請求項3】

請求項2に記載の半導体集積回路装置において、

10

20

前記積層DRAM、前記インターフェースLSI及び前記インターポーラからなる組を複数備え、

互いに隣接する組同士が前記マザーボードを介してポイント・トゥ・ポイント接続されていることを特徴とする半導体集積回路装置。

【請求項4】

請求項1、2または3に記載の半導体集積回路装置において、

前記印刷回路基板と前記マザーボードとが同軸タイプのコネクタで接続されていることを特徴とする半導体集積回路装置。

【請求項5】

請求項2に記載の半導体集積回路装置において、

前記インターフェースLSIが貫通電極を有し、かつフェースアップであることを特徴とする半導体集積回路装置。

【請求項6】

請求項2記載の半導体集積回路装置において、

前記積層DRAMに必要とされる共通論理回路を前記インターフェースLSIに設けたことを特徴とする半導体集積回路装置。

【請求項7】

請求項1に記載の半導体集積回路装置において、

前記積層DRAMと前記インターポーラとの組を複数備え、

これら複数の組が前記チップセットにポイント・トゥ・ポイント接続又は共通接続されていることを特徴とする半導体集積回路装置。

【請求項8】

請求項7に記載の半導体集積回路装置において、

前記積層DRAMと前記チップセットとの間で授受される信号の前記インターポーラが備える入出力端子への割り振りを、同一属性の信号毎に、前記積層DRAMの中心軸を中心とする同心円状に行うようにしたことを特徴とする半導体集積回路装置。

【請求項9】

請求項1に記載の半導体集積回路装置において、

前記積層DRAM及び前記インターポーラからなる組を複数備え、

これら複数の組が前記チップセットにフライ・バイ接続されるように、コマンドアドレス信号用メインバスとデータ信号用メインバスとが、各組の直下で直交するよう前記マザーボードに設けられ、

前記コマンドアドレス信号用メインバス及びデータ信号用メインバスのそれぞれから各組の前記積層DRAMまでのスタブ長が2mm以下にされている、

ことを特徴とする半導体集積回路装置。

【請求項10】

請求項1に記載の半導体集積回路装置において、

前記インターポーラが、前記集積DRAMと前記チップセットとの間の信号の授受を仲介するSiインターポーラ兼インターフェースLSIであることを特徴とする半導体集積回路装置。

【請求項11】

請求項10に記載の半導体集積回路装置において、

前記積層DRAM及び前記Siインターポーラ兼インターフェースLSIからなる組を複数備え、

これら複数の組が行列配置され、前記チップセットにフライ・バイ接続されるように、コマンドアドレス信号用メインバスとデータ信号用メインバスとが、各組が搭載される領域において直交するよう前記マザーボードに格子状に設けられている、

ことを特徴とする半導体集積回路装置。

【請求項12】

請求項10に記載の半導体集積回路装置において、

10

20

30

40

50

前記積層DRAM及び前記Siインターポーラ兼インターフェースLSIからなる組を複数備え、

これら複数の組が行列配置され、前記チップセットにフライ・バイ接続されるように、コマンドアドレス信号用メインバスとデータ信号用メインバスとが、各組の直下で平行となるよう前記マザーボードに平行に設けられている、ことを特徴とする半導体集積回路装置。

【請求項13】

請求項10に記載の半導体集積回路装置において、前記積層DRAM及び前記Siインターポーラ兼インターフェースLSIからなる組を複数備え、

これら複数の組が行列配置され、前記チップセットにもっとも近い行に属する組はそれぞれ前記チップセットにポイント・トゥ・ポイント接続され、

残りの行に属する組は、各列毎に、互いに隣り合う組とポイント・トゥ・ポイント接続されている、

ことを特徴とする半導体集積回路装置。

【請求項14】

請求項10乃至13のいずれか一つに記載の半導体集積回路装置において、積層DRAMとSiインターポーラ兼インターフェースLSIの平面サイズが実質上同一である、

ことを特徴とする半導体集積回路装置。

【請求項15】

請求項10乃至14のいずれか一つに記載の半導体集積回路装置において、Siインターポーラ兼インターフェースLSIが貫通電極を備えていない、

ことを特徴とする半導体集積回路装置。

【請求項16】

請求項15に記載の半導体集積回路装置において、複数のDRAMチップを積層して前記積層DRAMを作成する際に、前記Siインターポーラ兼インターフェースLSIを支持体として利用するようにした、

ことを特徴とする半導体集積回路装置。

【請求項17】

請求項1乃至16のいずれかに記載の半導体集積回路装置において、前記積層DRAMが貫通電極を有し、当該貫通電極が前記複数のDRAMチップにおける周辺回路領域に設けられていることを特徴とする半導体集積回路装置。

【請求項18】

請求項2, 3, 5, 6, 及び10乃至16のいずれかに記載の半導体集積回路装置において、

前記インターフェースLSI又は前記Siインターポーラ兼インターフェースLSIと前記積層DRAMとの間の接続が無終端接続により行われている、

ことを特徴とする半導体集積回路装置。

【請求項19】

請求項1乃至14のいずれか一つに記載の半導体集積回路装置において、前記インターポーラの上面に電源線と接地線との間に接続されたデカップリングコンデンサを備える、

ことを特徴とする半導体集積回路装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体集積回路装置に関し、特に、積層DRAM(または、チップ・オン・チップDRAM(COC DRAM: Chip On Chip Dynamic Random Access Memory)を有する半導体集積回路装置に関する。

【背景技術】

10

20

30

40

50

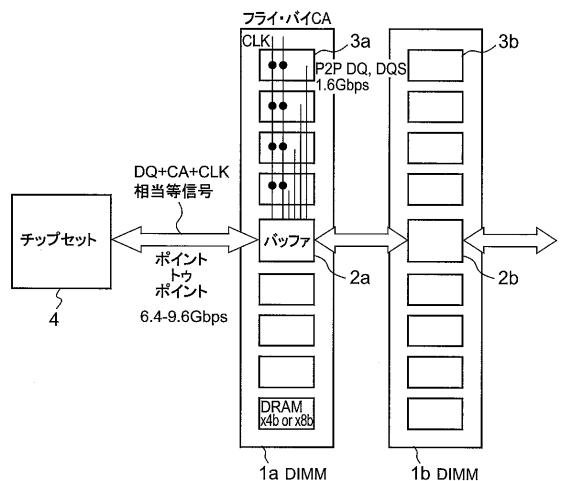

## 【0002】

現在、J E D E C (Joint Electron Device Engineering Council: 電子素子技術連合評議会) 等で検討されているメモリシステムの一例を図27に示す。

## 【0003】

図27のメモリシステムは、図示しないマザーボードに搭載されるチップセット4と、チップセット4との間で信号の授受を行う複数枚(ここでは、2枚のみ示す。)のDIMM (Dual In line Memory Module) 1a, 1bとを備えている。各DIMM 1上には、バッファ2a又は2bと、複数個(ここでは、8個)のDRAMチップ3a又は3bが搭載されている。

## 【0004】

チップセット4とDIMM 1aのバッファ2aとの間、及び互いに隣り合うDIMM 1のバッファ2同士の間は、ポイント・トゥ・ポイント(Point to Point)で信号の授受を行うように接続されている。これらの間のデータレートは6.4Gbps~9.6Gbps程度を想定している。チップセット4と各DIMM 1a, 1bとの間で授受される信号には、DQ(データ)信号やCA(コマンドアドレス)信号が含まれる。これらの信号は、差動伝送信号として伝送される。これらの信号伝送に必要とされる信号線は、150~200本程度である。

## 【0005】

各DIMM 1上では、バッファ2と各DRAM3との間が、信号種別毎に異なる方式で接続される。即ち、DQ系の信号(DQ信号、DQS(ストローブ)信号)に関しては、ポイント・トゥ・ポイント接続が用いられる。そのデータレートは、1.6Gbps程度を想定している。一方、CA信号及びCLK(クロック)信号に関してはフライ・バイ(Fly-by)接続が用いられる。フライ・バイ接続では、モジュール基板に形成されたメインバスの上に、そこに接続されるDRAMが配置される。バッファ2から引き出される信号線は、作動伝送信号用及びシングルエンド伝送信号用を合わせて200~250本程度である。

## 【0006】

バッファ2のパッケージの大きさは、信号ボール、VDDボール、GNDボール、及び無接続(No connection)等を考慮し、ボールピッチを0.8mmとした場合、21mm×21mm~25mm×25mm程度になる。

## 【0007】

なお、図27には示していないが、ポイント・トゥ・ポイント接続では、受信側に終端抵抗が設けられる。また、フライ・バイ接続では、最遠端部に終端抵抗が設けられる。

## 【0008】

また、従来から集積回路の高集積化を目的として、複数のICチップ又はLSIチップを積層する技術が提案されている(例えば、特許文献1乃至3及び非特許文献1参照。)

。

## 【0009】

ここで、特許文献1には、アドレス信号等、同一属性のパッド同士を貫通電極で接続する技術が記載されている。また、特許文献2には、メモリアレー回路とコントローラ回路とを積層する技術が記載されている。また、特表平9-504654号公報には、メモリチップとインターフェースLSIとを積層する技術が記載されている。さらに、非特許文献1には、Siインターポーラで伝送線を構成する技術が記載されている。

## 【0010】

【特許文献1】特開平6-291250号公報

【特許文献2】米国特許第6,133,640号公報(明細書)

【特許文献3】特表平9-504654号公報

【非特許文献1】技術研究組合 超先端電子技術開発機構 H14年度研究成果報告

【発明の開示】

【発明が解決しようとする課題】

10

20

30

40

50

## 【0011】

従来の(図27の)メモリシステムでは、各DIMMにおけるDRAMとバッファとの距離が、DRAM毎に異なっている。それゆえ、このメモリシステムは、バッファが最も遠くに位置するDRAMに合わせて動作せざるを得ず、高速化が困難であるという問題点がある。この問題点は、バッファが同期化処理等を行うことによってある程度解決できるが、システム全体の性能低下及びコスト上昇を招くといった別の問題を引き起こす。

## 【0012】

また、従来のメモリシステムでは、各DIMMにおけるCLK信号等のトポロジー(Topology)とDQ系信号のトポロジーとが異なるので、各DRAMではCLK信号とDQS信号との到着時間(伝播時間)に差が生じる。この差は、システム設計上、例えば1クロック周期の15%以内でなければならず、クロック周波数を上げるとその実現が困難になるという問題点もある。

10

## 【0013】

さらに、従来のメモリシステムでは、全ての伝送線路に終端抵抗が必要なので、終端抵抗で消費される電力が大きいという問題点もある。

## 【0014】

更に、従来のメモリシステムでは、各DRAMとして单一チップ又はスタッキチップ(2チップ)のDRAMが用いられているため、メモリ容量を増加させようとすると占有面積が大きくなるという問題点もある。

## 【0015】

20

なお、上述した特許文献1乃至3及び非特許文献1には、メモリシステム全体の構成について、特に、インタポーラの構成、積層DRAMにおける貫通電極の配置法、あるいは終端抵抗の付け方等について、全く開示されていない。

## 【0016】

また、非特許文献1に記載の技術における絶縁膜の厚みが10μm(LSIに通常用いられる絶縁膜の10倍)もあり、通常のLSI製造工程において作成することが困難である。加えて、非特許文献1に図示されている配線幅12.5μm、配線厚1μmから、配線長10mm長の伝送線のDC抵抗Rdcを計算すると、 $R_{dc} = (1/58e^6) \times (10e^{-3}) / ((1e^{-6}) \times (12.5e^{-6})) = 14\Omega$ となる。この値は50オーム程度を終端抵抗に使う伝送線としては若干高過ぎる値である。

30

## 【0017】

本発明は、上述したような従来の技術が有する問題点に鑑みてなされたものであって、高速化、低消費電力化、大容量化が可能な半導体集積回路装置を提供することを目的とする。

## 【課題を解決するための手段】

## 【0018】

上記目的を達成するために本発明は、積層DRAM構造(COC(Chip on Chip)DRAM構造)を採用する。そして、チップセットとインタフェースLSI(I/F LSI)との間のポイント・トゥ・ポイント接続の信号伝送線において発生する特性インピーダンスの不整合とDC抵抗の増加を、Si(シリコン)部とPCB(Printed Circuit Board)から成るインタポーラを用いて解決する。

40

## 【0019】

I/F LSIをフェース・アップ(Face up)配置とした場合、I/F LSIには400本程度の貫通電極を設ける必要がある。これらの貫通電極を設けることができる場所は限られているため、貫通電極のピッチが40μm程度となる場所も発生する。そのため、I/F LSIと、0.8mmピッチ程度のビア(Via)ピッチを有するPCBとを直接接続するのは困難であるので、インタポーラとしてI/F LSIと同じ物質のSiが必要となる。即ち、信号(電極又は接続端子)のピッチ変換のためにSiインタポーラが必要となる。

## 【0020】

50

また、Siインタポーラの下面の電極端子をフリップチップ接続で、ほぼ同一サイズのPCB基板に接続する。そしてPCB基板の下面に半田ボールを付けて、マザーボード(Mother board)に接続する。このようにすることによって、システムの信頼性が向上する。また、COC DRAM、I/F LSI、Siインタポーラ、及びPCBからなる部分をパッケージとみなせるので取り扱いも容易となる。更に、このPCB部にSiインタポーラの信号配線に対するレファレンスプレーンを設けることによって、Siインタポーラに設けられる配線の特性インピーダンスとDC抵抗とを適切な値に設定することが可能となる。即ち、電気特性、信頼性、取り扱いのし易さからPCBが必須となる。SiインタポーラとPCBとを2層構造から成る単一のインタポーラと見なすことができる。

## 【0021】

10

また、上記目的を達成するために本発明は、I/F LSIと積層DRAM間のDQSとCLK等の各信号の配線トポロジ(Topology)を同一にし、信号遅延差をなくすようにし、また、各信号の終端抵抗を除去した。

## 【0022】

また、DRAMチップの占有面積を低減するように、1チップの厚さが50um程度であるDRAMチップを積層し、貫通電極でチップ間を接続するCOC DRAM構造を採用した。

## 【0023】

20

具体的には、本発明によれば、チップセットが搭載されたマザーボードと、当該マザーボードに実装され、かつ前記チップセットに接続されるメモリ部とを備える半導体集積回路装置において、前記メモリ部として複数のDRAMチップを互いに積層した積層DRAMを用い、前記積層DRAMを前記マザーボードに実装するためにインタポーラを用い、当該前記インタポーラは、前記積層DRAMと前記チップセットとを電気的に接続する配線を含むシリコン部と、当該シリコン部の下側に設けられた当該シリコン部と実質上同じサイズの印刷回路基板とを有し、当該印刷回路基板に前記配線に対して電位基準を与えるレファレンスプレーンが設けられていることを特徴とする半導体集積回路装置が得られる。

## 【0025】

また、本発明によれば、第1の半導体集積回路装置において、前記積層DRAMと前記インタポーラとの間に前記積層DRAMと前記チップセットとの間の信号授受を仲介するインターフェースLSIをさらに備え、該インターフェースLSIと前記チップセットとが、前記インタポーラ及び前記マザーボードを介してポイント・トゥ・ポイント接続されていることを特徴とする第2の半導体集積回路装置が得られる。

30

## 【0027】

また、本発明によれば、第1の半導体集積回路装置において、前記積層DRAMと前記インタポーラとの組を複数備え、これら複数の組が前記チップセットにポイント・トゥ・ポイント接続又は共通接続されていることを特徴とする第3の半導体集積回路装置が得られる。

## 【0028】

40

さらにまた、本発明によれば、第1の半導体集積回路装置において、前記積層DRAM及び前記インタポーラからなる組を複数備え、これら複数の組が前記チップセットにフライ・バイ接続されるように、コマンドアドレス信号用メインバスとデータ信号用メインバスとが、各組の直下で直交するよう前記マザーボードに設けられ、前記コマンドアドレス信号用メインバス及びデータ信号用メインバスのそれぞれから各組の前記積層DRAMまでのスタブ長が2mm以下にされていることを特徴とする第4の半導体集積回路装置が得られる。

## 【0029】

50

また、本発明によれば、第1の半導体集積回路装置において、前記インタポーラが、前記集積DRAMと前記チップセットとの間の信号の授受を仲介するSiインタポーラ兼インターフェースLSIであることを特徴とする第5の半導体集積回路装置が得られる。

## 【0030】

また、本発明によれば、第5の半導体集積回路装置において、前記積層DRAM及び前記Siインターポーラ兼インターフェースLSIからなる組を複数備え、これら複数の組が行列配置され、前記チップセットにフライ・バイ接続されるように、コマンドアドレス信号用メインバスとデータ信号用メインバスとが、各組が搭載される領域において直交するよう前記マザーボードに格子状に設けられていることを特徴とする第6の半導体集積回路装置が得られる。

## 【0031】

さらに、本発明によれば、第5の半導体集積回路装置において、前記積層DRAM及び前記Siインターポーラ兼インターフェースLSIからなる組を複数備え、これら複数の組が行列配置され、前記チップセットにフライ・バイ接続されるように、コマンドアドレス信号用メインバスとデータ信号用メインバスとが、各組の直下で平行となるよう前記マザーボードに平行に設けられていることを特徴とする第7の半導体集積回路装置が得られる。

10

## 【0032】

さらにまた、本発明によれば、第5の半導体集積回路装置において、前記積層DRAM及び前記Siインターポーラ兼インターフェースLSIからなる組を複数備え、これら複数の組が行列配置され、前記チップセットにもっとも近い行に属する組はそれぞれ前記チップセットにポイント・トゥ・ポイント接続され、残りの行に属する組は、各列毎に、互いに隣り合う組とポイント・トゥ・ポイント接続されていることを特徴とする半導体集積回路装置が得られる。

20

## 【発明の効果】

## 【0033】

本発明によれば、積層DRAMを用いたので、各信号のスキューレを小さくすることができる。また、積層DRAMとマザーボードとの間にインターポーラを配したので、各信号線のインピーダンス整合を容易に実現できる。これらにより、本発明は、高速動作が可能な半導体集積回路装置（メモリシステム）を提供することができる。

## 【0034】

また、本発明によれば、積層DRAMが集中定数とみなせるので、各DRAMチップに終端抵抗を設ける必要が無く、従来に比べ終端抵抗の数を減らせるので、終端抵抗による電力消費を削減できる。これにより、本発明は、低消費電力の半導体集積回路装置（メモリシステム）を提供することができる。

30

## 【0035】

さらに、本発明によれば、積層DRAMを用いたので、積層数を増加させることによってメモリ容量の増大を実現できる。これにより、本発明は、占有面積の割に大容量の半導体集積回路装置（メモリシステム）を提供することができる。

## 【発明を実施するための最良の形態】

## 【0036】

以下に、本発明の実施の形態について図面を参照して詳細に説明する。

## 【0037】

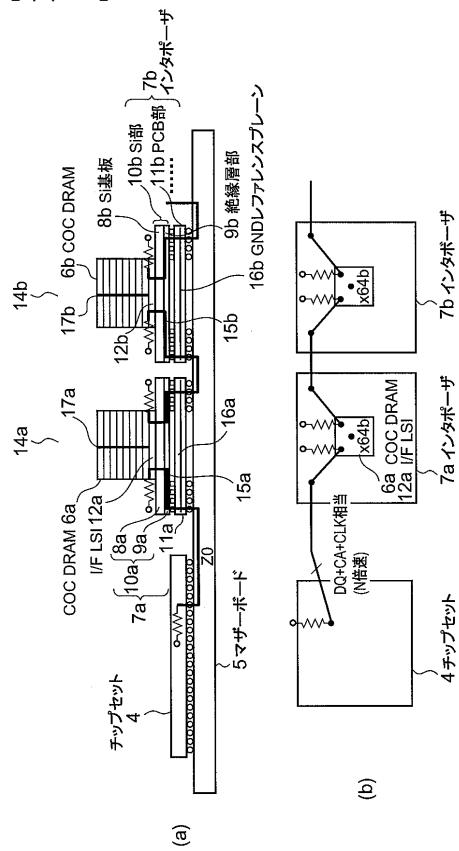

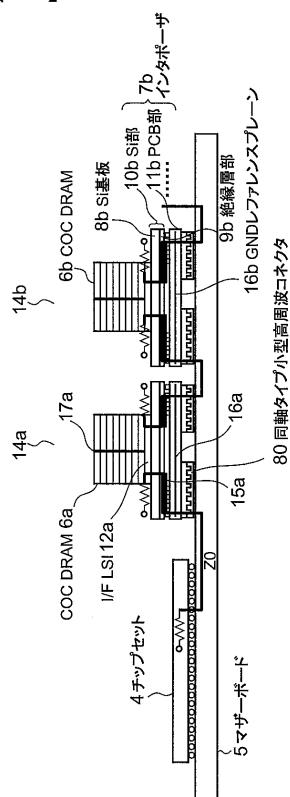

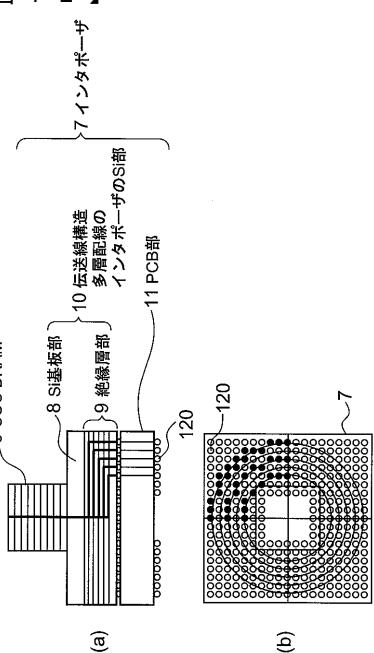

図1は、本発明の第1の実施の形態に係るメモリシステム（半導体集積回路装置）の構成を示す概略図であって、（a）は縦断面構造を示す図、（b）は平面構成を示す図である。

40

## 【0038】

図1のメモリシステムは、マザーボード5上に搭載されたチップセット4と、複数（ここでは2個のみ示す）のDRAM積層体14a, 14bとを有している。各DRAM積層体14は、8~16個のDRAMチップが積層されたチップ・オン・チップDRAM（CO-C DRAM）6と、このCO-C DRAM6が積層されるインターフェースLSI（I/F LSI）12と、このI/F LSI12の下に配設されたSi部10とPCB部11からなるインターポーラ7とを備えている。

## 【0039】

50

各インタポーザ7のSi部10は、Si基板8と絶縁層部9とを含む。インタポーザ7のSi部10とPCB部11とは、フリップチップ接続されている。インタポーザ7のPCB部11とマザーボードとは、半田ボールで接続されている。

#### 【0040】

チップセット4とI/F LSI12aの間の信号伝送は、ポイント・トゥ・ポイント接続により行われる。チップセット4とI/F LSI12aの間の配線は、マザーボード5中では、特性インピーダンスZ0となるように行われる。また、この配線は、インタポーザ7中では、水平方向に關し、絶縁層部9aを通る配線15aとして実現される。

#### 【0041】

I/F LSI12aとI/F LSI12b間の信号伝送も、ポイント・トゥ・ポイント接続により行われる。I/F LSI12aとI/F LSI12b間の信号線も、マザーボード5中では、特性インピーダンスZ0で配線される。また、インタポーザ7b中では、水平方向に關し、絶縁層部9を通る配線15bとして実現される。

#### 【0042】

インタポーザ7a, 7b中の配線15a, 15bに対して電位基準を与えるレファレンスプレーン16a, 16bは、それぞれPCB11a, 11b内に設けられている。このレファレンスプレーン16a, 16bの働きにより、配線15a, 15b夫々の特性インピーダンスをZ0に設定し、DC抵抗を3オーム程度以下にする。インタポーザ7中の配線15とレファレンスプレーン16に関する詳細は後述する。

#### 【0043】

以上のようにして図1のメモリシステムでは、ポイント・トゥ・ポイント接続部の特性インピーダンスが全線に渡りZ0に設定される。また、これらのポイント・トゥ・ポイント接続の受信側は、終端抵抗Z0で終端され、ドライバ側は、ソース抵抗Z0でインピーダンス整合させてある。その結果、ポイント・トゥ・ポイント接続部の信号伝送は、反射が抑えられ、良好な信号インテグリティ(Signal Integrity)が得られる。

#### 【0044】

このポイント・トゥ・ポイント接続部の信号は、DQ信号、CA信号等の情報を含むいわゆるプロトコル信号であり、その信号本数は150~200本である。また、このポイント・トゥ・ポイント接続部の信号は、DRAMのデータレートの4~6倍速で伝送される。例えば、DRAMのデータレートを1.6Gbpsとすると、このポイント・トゥ・ポイント接続部でのデータレートは6.4~9.6Gbpsである。なお、積層されるDRAMは、1チャンネルあたり8バイトとすると、×64ビット構成が望ましい。

#### 【0045】

各DRAM積層体14において、I/F LSI12とCOC DRAM6間の信号伝送は、COC DRAM6を積層方向(垂直方向)に貫いて形成される貫通電極17を介してなされる。図1には貫通電極17を1本のみ示しているが、実際には、DQ、CA、電源等の信号用に必要な本数分設けられる。信号としては、DQ信号、DQS信号、CA信号、CLK等があり、これらは種類毎に区別されて授受されるが、貫通電極17を含む配線は全て同じトポロジー(Topology)である。このため、各信号のスキューリングはほとんど発生しない。また、貫通電極17の長さも、8チップ積層の場合で0.4mm程度と短く、この部分は集中定数とみなせるので、終端抵抗は不要である。従って、I/F LSI12とCOC DRAM6との間の信号伝送を行った場合に、終端抵抗による電力消費がないので、低消費電力動作が可能となる。

#### 【0046】

先にも述べたが、チップセット4とI/F LSI12a間、及び隣り合うI/F LSI12a, 12b間は、ポイント・トゥ・ポイント接続で信号の授受を行う。データレートは6.4~9.6Gbps程度である。信号種は、メモリに必要な、DQ(データ), CA(コマンドアドレス)信号等の情報を含んだ差動伝送プロトコル信号等で、その信号本数は150~200本程度である。これに対応して、PCB部11のボール数は、電源、GND用を含め、300~400個程度となる。そして、総ボール位置数は、ウイン

10

20

30

40

50

ドウ (Window)、及び無接続 (No connection) 等を含めると 500 ~ 600 個となる。ここで、ボールピッチを 0.8 mm と仮定すると、PCB 部 11 の大きさは、20 mm × 20 mm 程度となる。

#### 【0047】

一方、I/F LSI 12 と COC DRAM 6 の間の信号は、DQ, CA, CLK (クロック) 等であり、種類毎に信号の授受が行われる。DQ 系信号のデータレートは 1.6 Gbps 程度である。ここで使用される信号本数は、差動伝送信号、シングルエンド (Single-ended) 伝送信号を含め、200 ~ 250 本程度である。

#### 【0048】

COC DRAM 6 の大きさは、大体 10 mm × 10 mm 程度であり、I/F LSI 10 12 の大きさはそれに合わせてある。I/F LSI 12 をフェースアップ (Face up) 配置とした場合、I/F LSI 12 には、電源、GND 等を含め、400 本程度の貫通電極を設ける必要がある。

#### 【0049】

I/F LSI 12 において、貫通電極を設けることができる場所は限られているので、貫通電極のピッチを 40 μm 程度とせざるを得ない場合も存在する。そのため、I/F LSI 12 と、0.8 mm 程度のビア (Via) ピッチを有する PCB 部 11 とを直接接続するには困難である。そこで、I/F LSI 12 と PCB 部 11 との間に、信号 (配線) のピッチ変換用のインタポーラとして、I/F LSI 12 と同じ物質の Si 部 10 を介在させている。

20

#### 【0050】

Si インタポーラ 10 の下面の電極端子には、フリップチップ接続で、ほぼ同一サイズの PCB 基板 11 が接続される。そして PCB 基板 11 は、その下面に形成された半田ボールを用いてマザーボードに接続される。この構成により、システムの信頼性が向上する。また、COC DRAM 6、I/F LSI 12、Si インタポーラ 10、PCB 11 からなる DRAM 積層体 14 を単一のパッケージとみなせるので、その取扱いが容易である。更に、PCB 部 11 に信号配線に電位基準を与えるレファレンスプレーン 16 を設けているので、Si インタポーラ 10 に設けられる配線 15 の特性インピーダンスと DC 抵抗とをそれぞれ適切な値に設定することができる。このように、PCB 11 は、電気特性、信頼性、及び取り扱いの容易化を実現する。

30

#### 【0051】

インタポーラ 7 中の配線 15 の長さは、10 ~ 15 mm 程度になる場合があるので、インタポーラ 7 の配線に、上記のようにして良好な伝送線特性を持たせておくことは重要である。

#### 【0052】

次に、図 1 のメモリシステムの動作について説明する。

#### 【0053】

まず、チップセット 4 から、COC DRAM 6a にデータを書き込む場合について述べる。チップセット 4 は、DQ 信号、CA 信号等の情報を含むプロトコル信号を I/F LSI 12a へ出力する。I/F LSI 12a は、プロトコルに従ってチップセット 4 からの信号を解読し、COC DRAM 6a へ、CA 信号、DQ 信号、CLK 等を出力する。そして、COC DRAM 6a は、I/F LSI 12a から出力される信号に従い、所定のアドレスにデータを書き込む。

40

#### 【0054】

COC DRAM 6b にデータを書き込む場合は、I/F LSI 12a がプロトコル信号を I/F LSI 12b へ送信し、I/F LSI 12b が、プロトコルに従って信号を解読し、COC DRAM 6b へ、CA 信号、DQ 信号、CLK 等を出力する。その結果、COC DRAM 6b は、COC DRAM 6a と同様に、I/F LSI 12b から出力される信号に従い、所定のアドレスにデータを書き込む。

#### 【0055】

50

次に、COC DRAM 6a からデータを読み出す場合について述べる。

【0056】

チップセット4は、CA信号等の情報を含むプロトコル信号をI/F LSI 12aに供給する。I/F LSI 12aは、プロトコルに従ってチップセット4からの信号を解読し、COC DRAM 6aへ、CA信号、CLK等を出力する。COC DRAM 6aは、I/F LSI 12aからのCA信号等に応答して、所定のアドレスからデータを読み出す。I/F LSI 12aは、読み出されたデータを取り込み、プロトコル信号としてチップセット4へ送出する。

【0057】

COC DRAM 6b からデータを読み出す場合は、チップセット4が、CA信号等の情報を含むプロトコル信号をI/F LSI 12aを介してI/F LSI 12bに供給する。I/F LSI 12bは、プロトコルに従ってチップセット4からの信号を解読し、COC DRAM 6bへ、CA信号、CLK等を出力する。COC DRAM 6bは、I/F LSI 12bからのCA信号等に応答して、所定のアドレスからデータを読み出す。読み出されたデータを、I/F LSI 12bは取り込み、I/F LSI 12aを介して、プロトコル信号としてチップセット4へ出力する。

【0058】

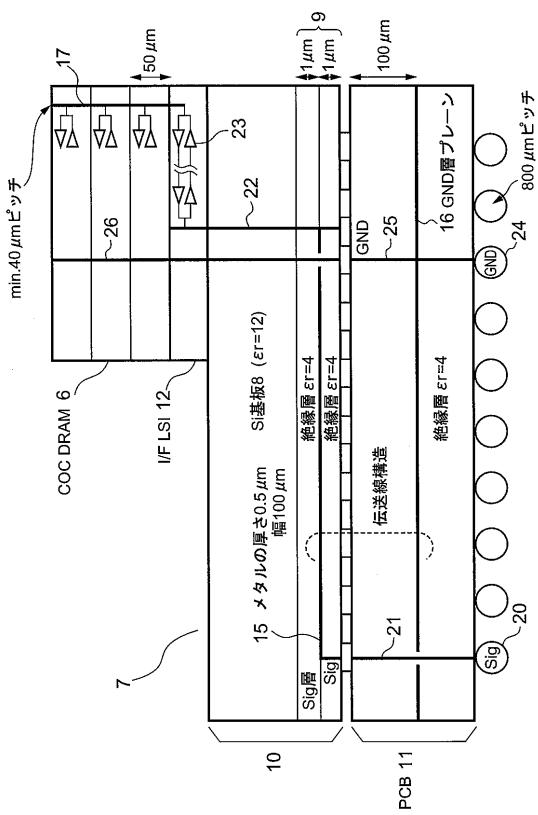

次に、図2を参照して、図1のシステムメモリに使用されるインタポーラ7の原理について説明する。

【0059】

図2は、図1のDRAM積層体14の左半分の断面図を示している。

【0060】

上述のように、インタポーラ7のSi部10は、Si基板部8と絶縁層部9とを含む。絶縁層部9は、厚み1μm程度の複数の絶縁層と、各絶縁層間の配線層とからなる。配線15は、絶縁層部9の配線層をパターニングするなどして形成される。また、配線15は、ブラインドビアにより、Si部10の下面に形成された接続端子に電気的に接続される。配線15は、例えば、幅100μm、厚み0.5μmである。Si部10は、さらに、Si基板部8及び絶縁層部9を貫通し、配線15に接続される貫通電極22を有している。Si部10の絶縁層及び配線15は、通常のLSI製造工程によって製造できるサイズなので工業生産に適している。

【0061】

PCB11のレファレンスプレーン16（即ち、GND層プレーン）は、PCB11の上面から100μm程度離れた位置に形成されている。レファレンスプレーン16は、Si部10の配線15とともに伝送線構造を形成する。レファレンスプレーン16と配線15との距離を100μm以上としたことにより、この伝送線構造の特性インピーダンスは約50オームとなる。また、配線15のDC抵抗Rdcは、その長さを10mmとして、 $R_{dc} = (1/58e^6) \times (10e^{-3}) / ((0.5e^{-6}) \times (100e^{-6})) = 3.4$ オーム、となる。抵抗Rdcは、配線15の厚みと幅を調整することによって、より低い値にすることが可能である。

【0062】

PCB11の下面には、約800μmのピッチで複数の半田ボールが形成されている。半田ボールは、上述したようにマザーボード5に接続固定される。

【0063】

信号用の半田ボール20に入った信号は、PCB11のビア21を通って、Si部10に入る。その後、絶縁層部9を通る配線15によって、I/F LSI 12の下の所定位置までいき、Si部10とI/F LSI 12とを貫通する貫通電極22介してI/F LSI 12に入力される。I/F LSI 12に入った信号は、I/F LSI 12内で論理回路23等を経て、COC DRAM 6の貫通電極17を介して各DRAMに到達する。各DRAMからの信号は、上記経路とは逆の経路を辿り、半田ボール20を介してマザーボードへと到達する。

10

20

30

40

50

## 【0064】

GND電位は、半田ボール24に供給され、PCB11のピア25を介して、Si部10に入り、Si部10、I/F LSI12、COC DRAM6を貫通する貫通電極26によって各DRAMに供給される。また、PCB11内のレファレンスプレーン(GND層プレーン)16にも供給される。

## 【0065】

図3を参照して、インタポーラ7がPCB11を備える必要性について説明する。

## 【0066】

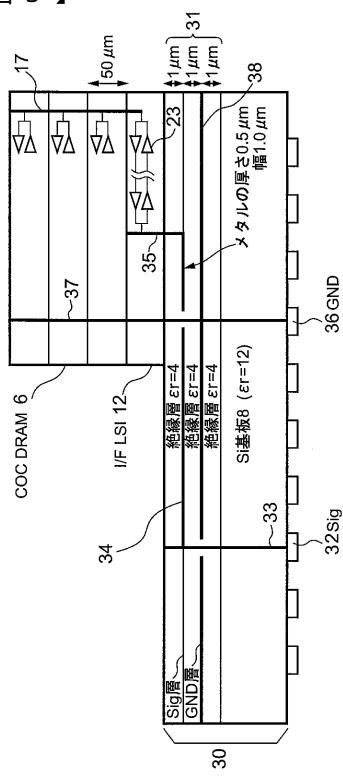

図3は、Si部30のみからなるインタポーラを含むDRAM積層体の左半分断面図である。

10

## 【0067】

Si部30は、Si基板8と絶縁層部31とを有している。絶縁層部31は、厚み1μmの複数の絶縁層を含み、これら絶縁層の間に配線34及びGND層プレーン38が形成されている。配線34とGNDレファレンスプレーン38とは、互いに異なる絶縁層間に配置される。

## 【0068】

また、Si部30は、Si基板8及び絶縁層部31を貫通し、配線34に接続される貫通電極33と、Si基板8及び絶縁層部31を貫通し、さらにCOC DRAM6を貫通するとともにGNDレファレンスプレーン38に接続される貫通電極37と、その下面に形成された複数のフリップチップ電極とを有している。

20

## 【0069】

信号用のフリップチップ電極32からSi部30に入った信号は、Si部30の貫通電極33、絶縁層部31を走る配線34を介してI/F LSI12の貫通電極35に入力される。I/F LSI12に入った信号は、I/F LSI12内の論理回路23等を経て、COC DRAM6の貫通電極17に到達し、各DRAMに入力される。各DRAMからチップセットへ向かう信号は、上記経路と逆の経路を辿り、フリップチップ電極32へ到達する。

## 【0070】

GND電位は、フリップチップ電極36に供給され、Si部30に入り、Si部30、I/F LSI12、COC DRAM6を貫通する貫通電極37に供給され、各DRAM及びGNDレファレンスプレーン38に供給される。

30

## 【0071】

図3のインタポーラにおいて、配線34は、GNDレファレンスプレーン38とともに伝送線構造を形成する。この構成で特性インピーダンスを約50オームにするには、配線34を、幅1μm、厚さ0.5μm程度としなければならない。しかし、この場合、配線34のDC抵抗Rdcは、その長さを10mmとして、 $R_{dc} = (1/58e^6) \times (10e^{-3}) / ((0.5e^{-6}) \times (1e^{-6})) = 340$ オーム、となる。この値は、伝送線としては大き過ぎる値である。つまり、Si部だけでは、工業生産に向いたサイズで、DC抵抗と特性インピーダンスの両方を満たす伝送線構造のインタポーラを作ることは難しい。

40

## 【0072】

なお、図3に示すSi部30のように、絶縁層部がCOC DRAM側に位置し、Si基板がマザーボード側に位置する場合であって、その下にレファレンスプレートを有するPCBを設けることにより、図2のインタポーラ7と同様に、良好な特性を有する伝送線構造を形成することができる。ただし、その場合は、配線とレファレンスプレーンとの間に大きな比誘電率r(=12)を持つSi基板部8が位置するので、図2と同じサイズの場合、特性インピーダンスは小さくなる。

## 【0073】

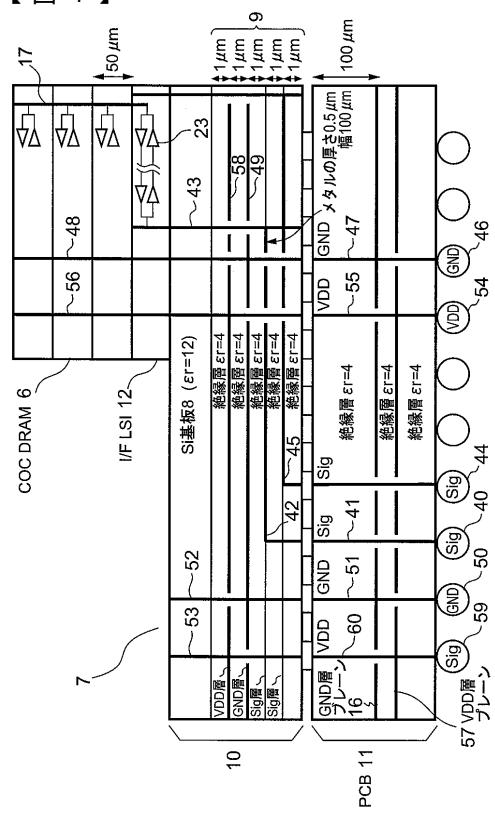

次に、図4を参照して、インタポーラ7についてより詳細に説明する。

## 【0074】

50

図4は、インタポーザ7の詳細構造図であって、図2同様、DRAM積層体14の左半分の断面図を示している。図2と異なる点は、Si部10の絶縁層部9が5層の絶縁層からなり、各絶縁層間にVDD線、GND線、第1及び第2の信号配線が形成されている点、及びこれらに接続される貫通電極あるいはビアを有している点である。

#### 【0075】

図4のインタポーザ7において、半田ボール40に入った信号は、PCB11のビア41を通って、Si部10に入る。Si部10に入った信号は、絶縁層部9を通る配線42によって、I/F LSI12の下の所定位置までいき、Si部10とI/F LSI12を貫通する貫通電極43に到達する。貫通電極43を介してI/F LSI12に入った信号は、I/F LSI12内で論理回路23等を経て、COC DRAM6の貫通電極17を介して各DRAMに到達する。各DRAMからの信号は、上記と逆の経路を辿り、半田ボール40に到達する。

10

#### 【0076】

他の半田ボール44に入った信号も同様にして、COC DRAM6に到達する。ただし、この信号は半田ボール40に入った信号が通る配線42とは、異なる配線層に形成された配線45を通る。配線42と配線45とを異なる配線層に形成することにより、各配線層の配線数を減らすことができ、レイアウトが容易になる。

#### 【0077】

I/F LSI12の下に位置する半田ボールに入る信号も、図示はしないが、上記と同様の経路を辿る。但し、Si部10とI/F LSI12とを貫通する貫通電極の位置によっては、絶縁層部9に設けられる配線は不要である。

20

#### 【0078】

半田ボール46に供給されたGND電位は、PCB11のビア47を介して、Si部10に入り、Si部10、I/F LSI12、COC DRAM6を貫通する貫通電極48を介して各DRAMに供給される。また、PCB11内のGNDレファレンスプレーン16及びSi部10のGNDレファレンス線49にも供給される。

#### 【0079】

I/F LSI12領域の下以外に形成された半田ボール50に供給されたGND電位は、PCB11のビア51を介して、GNDレファレンスプレーン16供給され、また、Si部10の貫通電極52を介してGNDレファレンス線49に供給される。ここで、貫通電極52の代わりにブラインドビアを用いることも可能であるが、貫通電極52を用いた場合は、後述する貫通電極53との間にデカップリングコンデンサを接続することができる。デカップリングコンデンサは、Si部10の上面に形成できる。

30

#### 【0080】

半田ボール54に供給されたVDD電位は、PCB11のビア55を介して、Si部10に入り、Si部10、I/F LSI12、COC DRAM6を貫通する貫通電極56によって各DRAMに供給される。また、PCB11内のVDDプレーン57及びSi部10のVDD線58にも供給される。

#### 【0081】

I/F LSI12領域の下以外に形成された半田ボール59に供給されたVDD電位は、PCB11のビア60を介して、VDDプレーン57に供給され、また、Si部10の貫通電極53を介してVDD線58に供給される。ここで、貫通電極53の代わりにブラインドビアを用いることも可能であるが、貫通電極53を用いることにより、上述した通り、GND電位貫通電極52との間にデカップリングコンデンサを接続することができる。

40

#### 【0082】

PCB11内のGNDレファレンスプレーン16は、PCB11の上面から100um程度の所に設けられている。また、絶縁層9内を通る配線42、45は、夫々幅が100um、厚さが0.5um程度である。絶縁層部9の各絶縁層は、厚み1um程度である。これらの配線や絶縁層は通常のLSIの製造工程で製造できるサイズの範囲内であるので

50

、工業生産に向いている。

【0083】

ここで、配線42、45とGND レファレンスプレーン16で伝送線構造を形成している。この構成の特性インピーダンスは約50オームである。一方、配線42、45の各々のDC抵抗Rdcは、その長さを10mmとして、 $R_{dc} = (1/58e^6) \times (10e^{-3}) / ((0.5e^{-6}) \times (100e^{-6})) = 3.4$ オーム、となる。各配線の厚さと幅を調整することによって、DC抵抗Rdcをより低い値にすることは可能である。

【0084】

図4では、PCB11内のGNDレファレンスプレーン16がVDDプレーンよりもSi部10側に位置する例を示したが、VDDプレーン57が、GNDプレーン16よりもSi部10側に位置する用にしてもよい。この場合、VDDプレーン57が、配線52、54に電位基準を与えるレファレンスプレーンとなる。即ち、配線42、45は、VDDレファレンスプレーン57とともに伝送線構造を形成する。

【0085】

また、図4の例では、Si部10に、VDD線58、GND線49を設けたが、これは電源強化のためであって、必ずしも必要ではない。また、これらVDD線58はGND線49は、絶縁層部9を走る信号配線42、45のレファレンスとならないように布線しなければならない。つまり、VDD線58及びGND線49は、上から見て信号配線52、54と重ならないようにしなければならない。

【0086】

本実施の形態によれば、ポイント・トゥ・ポイント接続されたチップセット4とI/F LSI12間を、上述のように全線伝送線構造にすることができる。よって、終端抵抗やソース抵抗を伝送線の特性インピーダンスと整合させることによって、信号インテグリティ(Signal Integrity)良く、高速伝送をることができる。

【0087】

また、本実施の形態によれば、I/F LSI12とCOC DRAM6との間は、貫通電極を介して短距離で接続される。具体的には、DRAMチップ厚を1個あたり50μmとして、8枚積み重ねた場合でも、その距離は0.4mmである。このため、COC DRAM6において、各信号のスキューレの発生がほとんどなく、高速動作が可能となる。また、I/F LSI12とCOC DRAM6との間の信号伝播時間は、信号の立ち上がり/立ち下がり時間に比べて短いため、COC DRAM6を集中定数回路として扱うことが可能となる。それゆえ、COC DRAM6の各DRAMに終端抵抗を設ける必要が無く、終端抵抗で消費される電力が無いので、低消費電力動作が可能となる。

【0088】

また、本実施の形態によれば、DRAMのメモリ容量を増やす場合、2次元的に平面にDRAMを並べて増やすのではなく、3次元的に積層すればよいので、占有面積を増加させることなくメモリ容量を増加させることができる。この場合、高さの増加も1チップ当たり50μm程度である。

【0089】

なお、上記実施の形態では、PCB10にレファレンスプレーンを設けたが、マザーボードにレファレンスプレーンを設けることとも原理的には可能である。この場合、PCB10は不要となるので、Si部10が直接マザーボードにフリップチップ接続される。

【0090】

次に、図5及び図6を参照して、インタポーラ7のSi部10、I/F LSI12、及びCOC DRAM6を夫々貫通する貫通電極の位置関係について述べる。

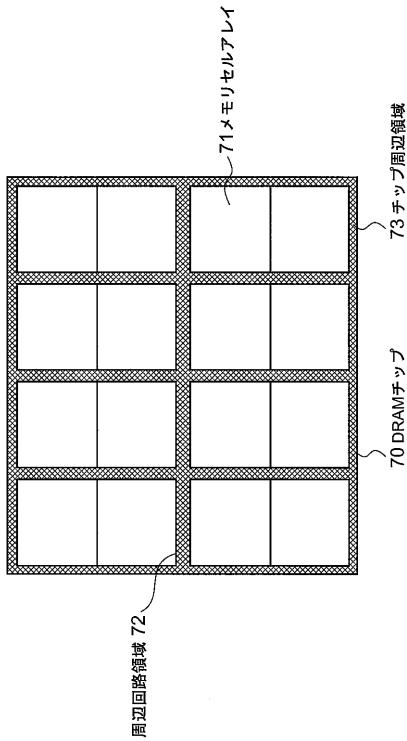

【0091】

図5に示すように、DRAMチップ70の素子形成領域は、その大部分がメモリセルアレイ領域71によって占められる。メモリセルアレイ領域71には、多数のトランジスタが密集して形成されるので、この領域内に貫通電極を形成することはできない。従って、

10

20

30

40

50

貫通電極を設けることができる場所は、メモリセルアレイ領域71同士の間に位置する周辺回路領域72（センターライン領域）、あるいはメモリセルアレイ領域71の外周に位置するチップ周辺領域73に限られる。このような制限下において、インタポーラ7のSi部10、I/F LSI12、及びCOC DRAM6を夫々貫通する貫通電極は、図6に示すような位置関係にある。

#### 【0092】

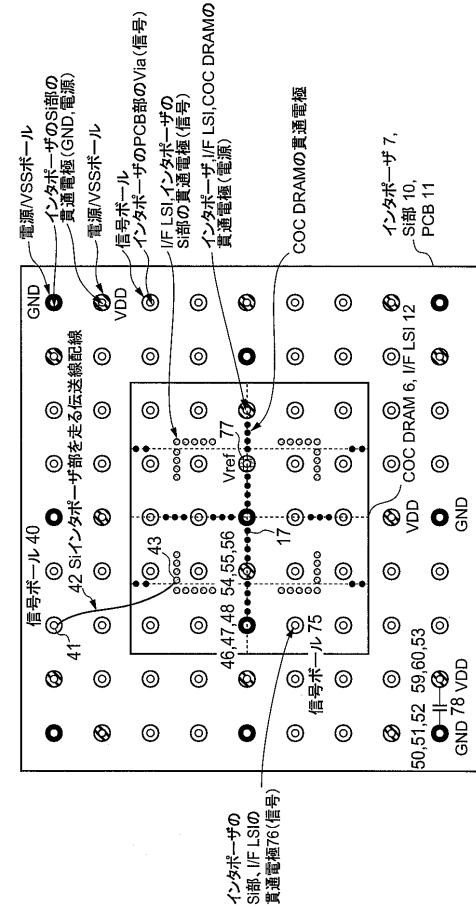

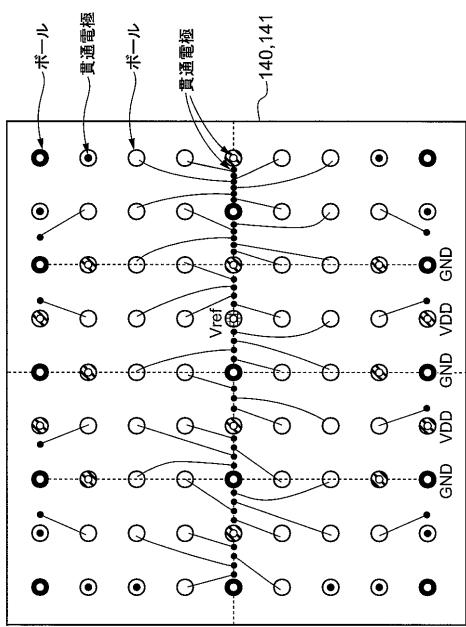

図6は、Si部10、I/F LSI12、及びCOC DRAM6を夫々貫通する貫通電極の位置を示す平面透視図である。なお、貫通電極の数は、実際のインタポーラ7よりも少ない。また、図4と同一のものには、同一の参照符号を付している。

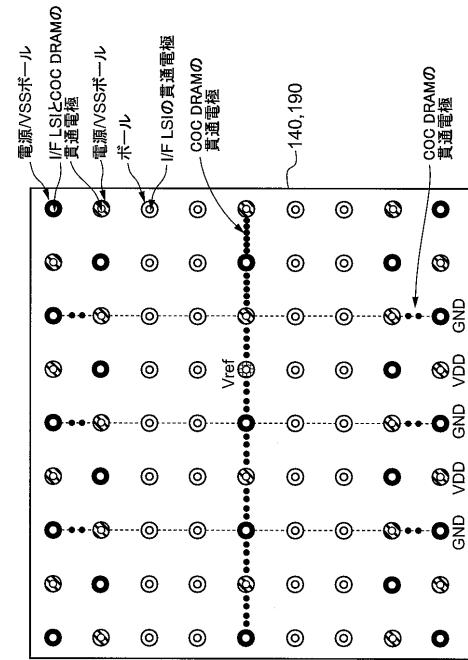

#### 【0093】

図6において、外側の大きい四角形は、インタポーラ7（Si部10及びPCB11）を表し、内側の小さい四角形は、COC DRAM6及びI/F LSI12を表す。

#### 【0094】

マトリクス状に配置された二重丸の外側の丸（大きい丸）は、インタポーラ7の下面に形成される半田ボールを表している。これら大きい丸のうち、白丸は信号用、黒丸はGND用、ハッチングのかかったものはVDD用あるいはVref用の半田ボールを表している。

#### 【0095】

二重丸の内側の丸及びその他の一重丸（小さい丸）は、PCB11に形成されたビアや、Si部10、I/F LSI12及びCOC DRAM6の夫々に形成され、あるいはこれらに共通に形成された貫通電極を示す。小さい丸のうち黒丸は、COC DRAM6の貫通電極である。また、二重丸の内側の丸は、基本的に、ボールの真上に形成されたPCB11のビアである。

#### 【0096】

図5を参照して説明したように、COC DRAM6に形成される貫通電極は、DRAMチップの周辺回路領域及びチップ周辺領域に限定される。インタポーラ7のSi部10及びI/F LSI12を貫通する貫通電極は、互いに対応するCOC DRAM6の貫通電極とPCB11のビアとの接続が容易に行えるように設けられる。

#### 【0097】

小さい四角形の外側に配置された信号用の半田ボール上に形成されたPCB11のビアは、インタポーラ7のSi部10に形成された絶縁層部9を通る配線により、Si部10及びI/F LSI12を貫通する貫通電極に接続される。I/F LSI12は、内部回路23を介して、自身を貫通する貫通電極とCOC DRAM6を貫通する貫通電極とを接続する。例えば、半田ボール40の上に形成されたPCB11のビア41は、配線42によってSi部10及びI/F LSI12を貫通する貫通電極43に接続される。また、貫通電極43は、I/F LSI12の内部回路を介してCOC DRAM6の貫通電極17に接続される。COC DRAM6に形成する貫通電極を、メモリセルアレイ領域以外の周辺回路領域及びチップ周辺領域としたことにより、DRAMチップのレイアウトを効率的に行うことができる。

#### 【0098】

小さい四角形の内側に配置された信号用の半田ボール75上に形成されたPCB11のビアは、その真上にSi部10及びI/F LSI12を貫通する貫通電極76が存在する場合には、絶縁層部9を通る配線を介さずに直接接続される。真上にSi部10が存在しないPCB11のビアは、内側の四角形の外側に配置された半田ボール状に形成されたビアと同様、絶縁層部9を通る配線を介して、Si部10及びI/F LSI12を貫通する貫通電極に接続される。

#### 【0099】

小さい四角形の内側に位置するGND電位用の半田ボール46の上に形成されたPCB11のビア47は、その真上に形成されたSi部10、I/F LSI12及びCOC DRAM6を貫通する貫通電極48に、絶縁層部9の配線を介すことなく接続される。

10

20

30

40

50

## 【0100】

同様に、VDD電位用の半田ボール54上に形成されたPCB11のビア55も、その真上に形成されたSi部10、I/F LSI12及びCOC DRAM6を貫通する貫通電極56に、絶縁層部9の配線を介すことなく接続される。Vref電位用の半田ボール77上に形成されたビアについても同様である。

## 【0101】

小さい四角形の外側に配置されたGND電位用の半田ボール50の上に形成されたPCB11のビア51は、その真上に形成されたSi部10を貫通する貫通電極52に直接接続される。

## 【0102】

同様に、VDD電位用の半田ボール59の上に形成されたPCB11のビア60は、その真上に形成されたSi部10を貫通する貫通電極53に直接接続される。

## 【0103】

以上のように、I/F LSI12の下の領域（小さい四角形の内側）にあるGND用及びVDD用の半田ボールの真上に、PCB11のビアと、Si部10、I/F LSI12及びCOC DRAM6を貫通する貫通電極とを配置するようにしたことで、各DRAMチップに最短距離でGND電位及びVDD電位を供給することができる。また、I/F LSI12の下の領域外（小さい四角の外側）にあるGND用VDD用の半導体ボールの真上に、PCB11のビアとSi10を貫通する貫通電極とを配置し、PCB11内のGNDプレーンやVDDプレーン、及びSi部10のGND線やVDD線を介してCOC DRAM6にGND電位及びVDD電位を供給するようにしたので、各DRAMチップへの安定した電源供給が可能である。

## 【0104】

また、I/F LSI12の下の領域外に、Si部10を貫通するVDD電位貫通電極53とGND電位貫通電極52とを設けることにより、これらの間にデカップリングコンデンサ78を接続することができる。デカップリングコンデンサの存在により、COC DRAM6に対してさらに安定した電源供給が可能である。また、デカップリングコンデンサは、他の同様な箇所にも設置可能である。

## 【0105】

図7は、本発明の第2の実施の形態に係るメモリシステムの構成を示す概略図である。図7において、図1と同一の物には同一の参照符号を付している。

## 【0106】

本実施の形態に係るメモリシステムは、第1の実施の形態に係るメモリシステムと基本構成は同じである。異なる点は、PCB11とマザーボード5との接続に半田ボールではなく、同軸タイプの小型高周波コネクタ80を用いている点である。このコネクタを用いることによって、更に高速性能を向上させることができる。

## 【0107】

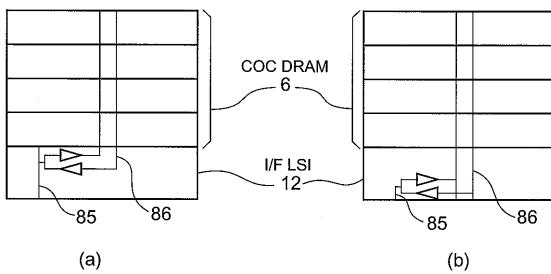

次に、図8を参照して、第1及び第2の実施の形態に係るメモリシステムに共通の、I/F LSI12の配置方法について説明する。

## 【0108】

図8(a)及び(b)から理解されるように、I/F LSI12に下面側から出入りする信号群85の本数（ここでは1本）と、上面側から出入りする信号群86の本数（ここでは2本）とが異なっている場合、I/F LSI12をフェースアップ配置とするか、フェースダウン配置とするかによって、I/F LSI12に形成しなければならない貫通電極の数が異なる。つまり、I/F LSI12に下面側から出入りする信号群85の本数よりも、上面側から出入りする信号群86の本数のほうが多い場合は、図8(a)に示すように、フェースアップ配置したほうが、貫通電極の本数を少なくできる。なお、ここでいうフェースアップ配置とは、I/F LSI12のトランジスタ形成領域が上面(COC DRAM6側)となる配置である。

## 【0109】

第1及び第2の実施の形態に係るメモリシステムでは、I/F LSI12に下面側から出入りする信号よりも、上面側から出入りする信号のほうが数が多いので、フェースアップ配置とすることにより、貫通電極の数を減らすことができ、それによって製造歩留まりの向上を図ることができる。

#### 【0110】

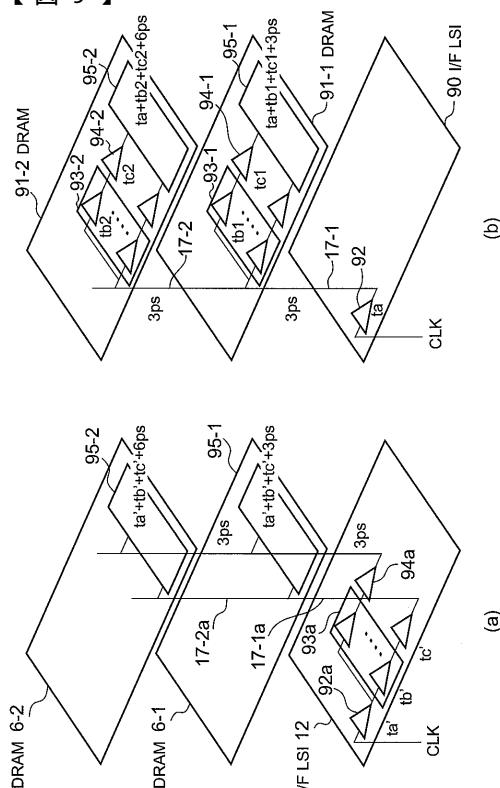

図9(a)は、第1及び第2の実施の形態に係るメモリシステムに用いられるI/F LSI12の構成例を示す図である。図9(b)は、一般的なI/F LSIの構成例である。

#### 【0111】

図9(b)に示す一般的なI/F LSI90は、下側から入力されるCLKをバッファ92で受け、貫通電極17-1及び17-2を介して、DRAM91-1及びDRAM91-2に供給する。

#### 【0112】

DRAM91-1では、CLK分配回路93-1がCLKをチップ内に分配し、バッファ94-1が分配されたCLKをフリップフロップ群95-1に供給する。同様に、DRAM91-2でも、CLK分配回路93-2がCLKをチップ内に分配し、バッファ94-2が分配されたCLKをフリップフロップ群95-2に供給する。

#### 【0113】

ここで、バッファ92の遅延時間をta、CLK分配回路93-1の遅延時間をtb1、バッファ94-1の遅延時間をtc1、CLK分配回路93-2の遅延時間をtb2、バッファ94-2の遅延時間をtc2とする。また、貫通電極1チップ分の遅延時間を3psとする。すると、I/F LSI90にCLKが入ってから、フリップフロップ群95-1に到着するまでの時間は、ta+tb1+tc1+3psで表される。また、I/F LSI90にCLKが入ってから、フリップフロップ群95-2に到着するまでの時間は、ta+tb2+tc2+6psで表される。そして、これらの時間差を求めるとき、(tb2-tb1)+(tc2-tc1)+3psとなる。つまり、この時間差には、DRAMにおけるCLK分配回路93とバッファ94の特性ばらつき分が含まれる。

#### 【0114】

一方、図9(a)に示すI/F LSI12では、バッファ92aが下側から入力されるCLKを受け、CLK分配回路93aがCLKをチップ内に分配し、バッファ94aが分配されたCLKを貫通電極17-1aへ出力する。貫通電極17-1aは、バッファ94aからのCLKをDRAM6-1に供給するとともに貫通電極17-2aに供給し、貫通電極17-2aはDRAM6-2に供給する。DRAM6-1, 6-2に供給されたCLKは、それぞれのフリップフロップ群95-1, 95-2に供給される。

#### 【0115】

このように、図9(a)に示すI/F LSI12は、各DRAMに共通に必要とされるCLK分配回路93やバッファ94を備えており、それによって、各DRAMの構成を簡略化できる。

#### 【0116】

ここで、バッファ92aの遅延時間をta'、CLK分配回路93aの遅延時間をtb'、バッファ94aの遅延時間をtc'をとし、貫通電極1チップ分の遅延時間を3psとする。すると、I/F LSI12にCLKが入ってから、フリップフロップ群95-1に到着するまでの時間は、ta'+tb'+tc'+3psであり、フリップフロップ群95-2に到着するまでの時間は、ta'+tb'+tc'+6psで表される。また、その差は3psで一定である。

#### 【0117】

このように、図9(a)のI/F LSI12を用いると、各DRAMのフリップフロップ群95-1, 95-2に入力されるCLKの時間差は一定となる。つまり、図9(a)に示すI/F LSI12は、DRAM6の特性ばらつきの影響を受けること無く分配できるので、ばらつきの発生が望ましくないCLKのような信号の伝送に有効である。

10

20

30

40

50

## 【0118】

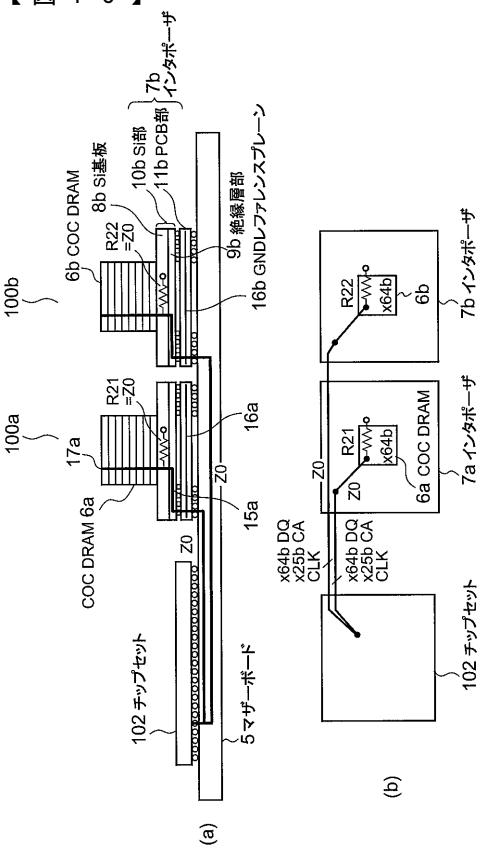

次に、図10(a)及び(b)を参照して、本発明の第3の実施の形態に係るメモリシステムについて説明する。図10において、図1と同一のものには同一の参照符号を付してある。

## 【0119】

図10のメモリシステムが図1のものと異なる点は、DRAM積層体100が、I/F LSI12を有していない点、及び、チップセット102とDRAM積層体との間が一種のポイント・トゥ・ポイント接続(1対多接続)で接続されている点である。つまり、本実施の形態に係るメモリシステムでは、各DRAM積層体100が、COC DRAM 6とインタポーザ7とからなり、チップセット102の各ボールに全DRAM積層体100の対応するボールが接続されている。また、チップセット102とCOC DRAM 6とは、I/F LSI12を介することなく直接信号の授受を行う。10

## 【0120】

チップセット102とDRAM積層体100とを結ぶ信号線は、全線、特性インピーダンスをZ0に設定している。また、これらの信号線には、終端抵抗が接続されている。終端抵抗については、このメモリシステムの動作とともに後述する。

## 【0121】

チップセット102とDRAM積層体100との間で授受される信号には、双方向信号であるDQ, DQSや、単方向信号であるCA, CLK等がある。これら信号は、チップセットとDRAMとの間で直接授受される信号なので、いわゆるプロトコル信号ではない。信号のデータレートは、DRAMのデータレートを1.6Gbpsとすると、1.6Gbpsである。積層するDRAMは、システムとして、1チャネルあたり8バイトとすると、×64ビット構成が望ましい。図10は、1チャネル構成の場合を示している。20

## 【0122】

次に、本実施の形態のメモリシステムの動作と終端抵抗の付け方(終端の方法)について説明する。

## 【0123】

まず、チップセット102から、COC DRAM 6aに書き込む場合について述べる。30

## 【0124】

チップセット102から、64bitのDQ信号、25bit程度のCA信号等が出力されるとする。このとき、チップセット102の一つのボールが、2つのCOC DRAM 6a及び6bにつながっているので、同一の信号が、COC DRAM 6aだけでなく、COC DRAM 6bにも入力される。そこで、チップセット102は、別の互いに独立するボールからCOC DRAM 6a, 6bに対して、制御信号を出力する。その結果、COC DRAM 6aは、チップセットからのDQ信号等を取り込み、COC DRAM 6bは取り込まない。

## 【0125】

各信号線の終端は、DRAM積層体100aと100bの両方に遠端終端を設けることにより行われる。遠端終端を設ける場所としては、COC DRAM 6が考えられる。各DRAMに持たせても良いし、一番上のDRAMに設置しても良い。DRAM内に終端を設けると、終端抵抗のオン/オフ動作が容易に制御できる。40

## 【0126】

遠端終端を設置する別の場所として、インタポーザ7のSi部10が考えられる。この場合、Si部10に若干のMOSトランジスタの作成が必要となる。信号線の遠端終端から先は、COC DRAM 6のみが接続されており、その配線の長さは0.4mm程度なので、信号インテグリティの劣化は実質上無い。また、DRAMに終端抵抗を持たせる必要が無いので、DRAMの負担が小さく、熱発散も容易となる。

## 【0127】

さらに遠端終端の別の設置場所として、インタポーザ7のPCB部11が考えられる。50

信号線の遠端終端から先は、インタポーラ7のSi部10とCOC DRAM6のみが接続されており、その配線長さは0.5mm程度なので、上記と同様信号インテグリティの劣化は実質上無い。また、DRAMに終端抵抗を持たせる必要が無いので、DRAMの負担が小さく、熱発散も容易となる。なお、この場合は、終端抵抗をオフできるようにすることは難しいが、読み出し時に、COC DRAM6の出力ドライバとしてオープンドレイン型のドライバを用いれば特に問題はない。

【0128】

チップセット102から、COC DRAM6bに書き込む場合も上記同様に行われる。

【0129】

次に、COC DRAM6aからデータを読み出す場合について述べる。

【0130】

チップセット102から、CA信号等がCOC DRAM6aに供給される。このCA信号等は、書き込みの場合と同様にCOC DRAM6bにも供給されるが、制御信号により取り込みが阻止される。COC DRAM6aは、チップセット102から供給された信号を解読し、対応するアドレスからデータを読み出す。COC DRAM6aから読み出されたデータは、チップセット102へ送られ、取り込まれる。また、チップセット102へ送られたデータは、チップセット102のポートを介してCOC DRAM6b側へ伝送される。そのため、COC DRAM6b側での終端が必須である。また、望ましくは、COC DRAM6aのドライバのオン抵抗をZ0に合わせておくとよい。また、COC DRAM6aのドライバがプッシュプル型の場合は、図10に示したCOC DRAM6a側の終端は不要である。

【0131】

COC DRAM6bからデータを読み出す場合も、上記と同様にして行われる。

【0132】

本実施の形態に係るメモリシステムによれば、図1のメモリシステムと同様の効果が得られる。さらに、本実施の形態のメモリシステムは、I/F LSIを持たないので、図1のメモリシステムに比べ低消費電力化と低成本化が可能となる。また、チップセット102のポート数を削減できる。

【0133】

次に、図11を参照して、本発明の第4の実施の形態に係るメモリシステムに説明する。

【0134】

図11のメモリシステムは、図10のメモリシステムと基本的に同じであるが、チップセット103と各COC DRAM6とが1対1で信号の授受を行う点で異なっている。つまり、チップセット103が、COC DRAM6a用の端子とCOC DRAM6b用の端子とを別々に備えている。

【0135】

チップセット103の一つのポートから、COC DRAM6aとインタポーラ7aからなるDRAM群100aのみに信号線が接続され、別のポートから、COC DRAM6bとインタポーラ7bからなるDRAM群100bのみに信号線が接続されている。信号としては、双方向信号であるDQ, DQSや、単方向信号であるCA, CLK等がある。これらは、チップセットとDRAMとの間で直接授受される信号であるので、いわゆるプロトコル信号ではない。

【0136】

チップセット103とDRAM群100a, 100bの間は、ポイント・トゥ・ポイント接続であり、全線の特性インピーダンスをZ0に設定している。信号のデータレートは、DRAMのデータレートを1.6Gbpsとすると、1.6Gbpsである。積層するDRAMは、1チャネルあたり8バイトとすると、×64bit構成が望ましい。図11のメモリシステムは、2チャネル構成である。

10

20

30

40

50

## 【0137】

次に図11のメモリシステムの動作と終端抵抗の付け方について説明する。

## 【0138】

まず、チップセット103から、COC DRAM6aに書き込む場合について述べる。チップセット103から、64bitのDQ信号、25bit程度のCA信号等が出力される。

## 【0139】

終端法は、DRAM群100aに遠端終端を設ける。遠端終端を設ける場所としては、図10の説明で述べたように3通りが考えられる。また、望ましくは、チップセット103のドライバのON抵抗を伝送線の特性インピーダンスに合わせておくのが良い。

10

## 【0140】

チップセット103から、COC DRAM6bに書き込む場合も同様である。

## 【0141】

この場合、COC DRAM6a及び6bは互いに独立に動作できる。即ち、2チャネル動作が可能である。

## 【0142】

次に、COC DRAM6aからデータを読み出す場合について述べる。チップセット103から、CA信号等がCOC DRAM6aに供給される。COC DRAM6aでは信号を解読し、対応するアドレスからデータを読み出す。読み出されたデータは、チップセット103へ伝送され、取り込まれる。そのため、チップセット103に終端抵抗を設ける。また、望ましくは、COC DRAM6aのドライバのオン抵抗をZ0に合わせておくとよい。また、COC DRAM6aのドライバがプッシュプル型のドライバの場合は、図11に示したCOC DRAM6a側の終端は不要である。

20

## 【0143】

COC DRAM6bからデータを読み出す場合も、上記と同様にして行われる。

## 【0144】

本実施の形態のメモリシステムによれば、図10のメモリシステムと同様の効果が得られる。さらに、2チャネル動作が可能なので、システム性能をさらに向上できる。

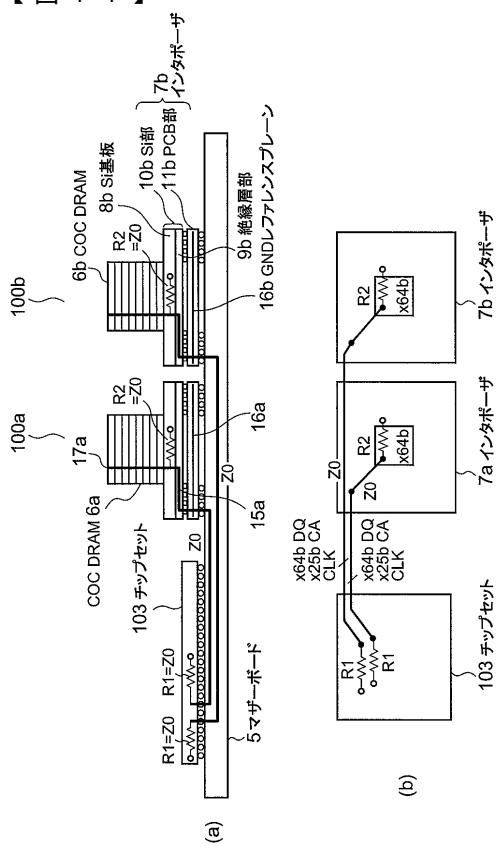

## 【0145】

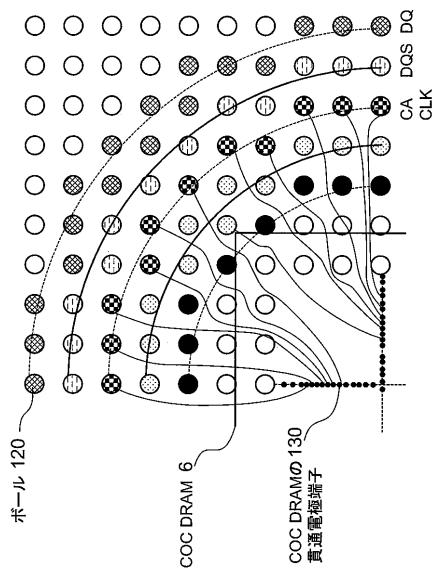

図12(a)及び(b)は、図10及び図11に示すメモリシステムにおけるインタポーラー7の半田ボール120への信号の割り振り例を説明するための図である。図12(a)はDRAM積層体100の縦断面図、図12(b)は平面透視図である。なお、インタポーラーの配線層数は、配線の混雑度等を考慮して決定される。

30

## 【0146】

図10や図11のシステム構成の場合、DQやCA等の信号種別毎に、チップセットとCOC DRAM6との間で信号の授受が行われるので、それらの信号のスキューが小さいことが望ましい。そのため、インタポーラー7に信号が入ってから、COC DRAM6に信号が到達するまでの時間を信号種別毎に一致させることは高速化に有利である。従って、同一属性の信号を、インタポーラー7の中心を中心とする同心円上にある(又は近い)ボールに割り当てる。例えば、図12(b)の例では、一番半径の大きい円に沿って黒丸印で示すボールにDQを割り当て、その内側の円に沿って白丸印で示すボールに、DQを捕まえるためのDQS信号を割り当てる。また、CA信号と、CA信号を捕まえるためのCLK信号とは、DQS信号用の円の一つ内側の円に沿って黒丸印のボールに割り当てる等である。このようにインタポーラー7のボールに信号を割り当てるにより、チップセット102又は103からの信号がインタポーラー7のボールに入るまでの遅延時間を信号種別毎に揃えることができ、小さなスキューで、チップセット102又は103とCOC DRAM6との間の信号の授受が可能となる。

40

## 【0147】

図13は、図12(b)の右上部の拡大図である。図13には、ボールの割り振りと、CA信号及びCLK信号用のボールと、COC DRAM6の貫通電極17の端子130

50

との配線接続例とを示している。図13からの理解されるように、CA信号及びCLK信号用のボールと端子130とは、全て略等しい長さで結線されている。他の信号線の配線も同様に、略等しい長さにすることができる。

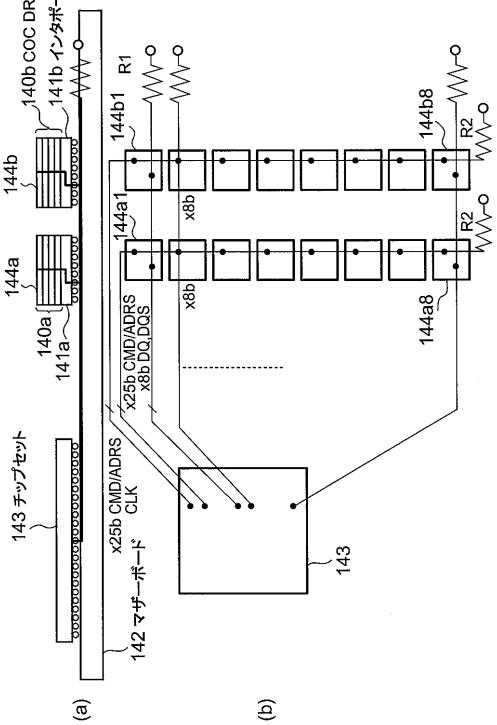

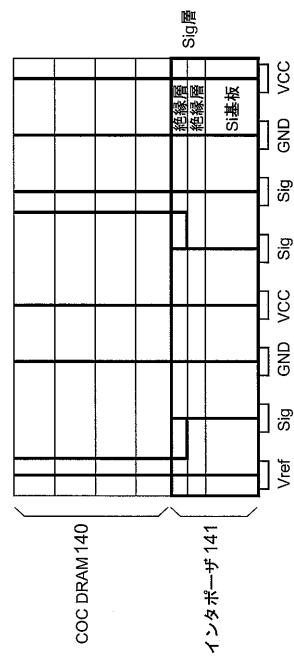

#### 【0148】

次に、図14(a)及び(b)を参照して、第5の実施の形態に係るメモリシステムについて説明する。第1乃至4に係るメモリシステムは、インタポーラ7の平面サイズがCOC DRAM6のそれより大きいものであったが、本実施の形態に係るメモリシステムは、インタポーラの平面サイズがCOC DRAMのそれと同程度のものである。これは、COC DRAMの構成が、 $\times 8$ ビット程度の場合等、信号数が少ない場合に適している。

10

#### 【0149】

図14のメモリシステムは、マザーボード142と、マザーボード142上に搭載されたチップセット143及び複数のDRAM積層体144とを有している。

#### 【0150】

各DRAM積層体144は、4チップのDRAMが積層されたCOC DRAM140と、インタポーラ141とが積層されている。

#### 【0151】

各COC DRAM140が $\times 8$ ビット構成で、1チャンネルが64ビットの場合、8個のDRAM積層体144を一組として使用する。図14は、2チャンネル構成の例を示しており、8個 $\times 2$ 列のDRAM積層体144を有している。DRAM積層体の列は、チップセット143から一方向に遠ざかるように並べられる。

20

#### 【0152】

インタポーラ141としては、Siインタポーラ又はPCBインタポーラが利用できる。COC DRAMの貫通電極のピッチを最小 $40\mu m$ 程度にする場合は、Siインタポーラを用いる。その場合、Siインタポーラは、マザーボード142にフリップチップ接続されるか、同じ大きさのPCB(図示せず)にフリップチップ接続され、PCBの半田ボールを用いてマザーボードに接続される。SiインタポーラとPCBの組み合わせを用いる場合は、その組み合わせ全体をインタポーラとみなせる。

#### 【0153】

一方、COC DRAMの貫通電極のピッチが $0.8mm$ 程度の場合は、PCPインタポーラが利用できる。この場合、COC DRAMとPCBインタポーラ141をフリップチップ接続し、PCBインタポーラ141とマザーボードを半田ボールで接続する。あるいは、COC DRAMをマザーボードにフリップチップ接続してもよい。

30

#### 【0154】

チップセット143とCOC DRAM140との間のDQ, DQS信号伝送は、図示したようなフライ・バイ方式で接続された信号線を用いて行われる。即ち、チップセット143とDRAM積層体144との間で送受される64ビットのDQ, DQS信号のうち、最初の8ビット分が、DRAM積層体144a1, 144b1とやり取りされ、次に8ビット分が、DRAM積層体144a2, 144b2とやり取りされ、最終の8ビット分が、DRAM積層体144a8, 144b8とやり取りされる。これらの信号線は、マザーボード142の特性インピーダンスがZ0の場合、遠端にZ0より低い値の終端抵抗R1で終端される。終端抵抗R1は、伝送線に負荷が接続されるため、容量が増え、実効特性インピーダンスが下るので、その実効特性インピーダンスに合わせればよい。

40

#### 【0155】

チップセット143とCOC DRAM140間のCA信号伝送は、図示したようなフライ・バイ方式で接続され、DQ, DQS信号と直交する信号線を用いて行われる。1コピーパーのCA信号が、DRAM積層体144a1, 144a2, ..., 144a8とやり取りし、別の1コピーパーが、DRAM積層体144b1, 144b2, ..., 144b8とやり取りする。CA信号を捕まえるためのCLKも同様の信号線により伝送される。これらの信号線は、マザーボード142の特性インピーダンスがZ0の場合は、遠端に

50

$Z_0$  より低い値の終端抵抗  $R_2$  で終端する。

【0156】

ここで、DQ信号及びCA信号のいずれも、マザーボード142を走るメインバスからCOCDRAMへと分岐される。そのスタブ長が長いと、そこで反射が大きくなり、信号のインテグリティが悪化する、従って、いずれの信号線とも、スタブ長は2mm程度以下が望ましい。

【0157】

次に、図14のメモリシステムの動作について説明する。

【0158】

まず、チップセット143から、COCDRAM140aに書き込む場合について述べる。

【0159】

チップセット143から、DQ信号、CA信号出力される。ここで、チップセット143のドライバのON抵抗は、それぞれのメインバスの実効特性インピーダンス  $R_1, R_2$  に合わせておくことが望ましい。

【0160】

COCDRAM140aは、チップセット143からのコマンド信号を解読し、対応するアドレスにデータを書き込む。

【0161】

COCDRAM140bへの書き込みも、上記と同様に行われる。

20

【0162】

次に、COCDRAM140aからデータを読み出す場合について述べる。

【0163】

チップセット143から、CA信号が出力される。COCDRAM140aは、チップセット143からのコマンド信号を解読し、対応するアドレスからデータを読み出す。読み出されたデータは、チップセット143へ伝送され、取り込まれる。読み出し時には、チップセット143に終端抵抗を持たせることが望ましい。その値は、 $R_1$  である。

【0164】

COCDRAM140bからデータを読み出す場合も上記と同様である。

【0165】

本実施の形態に係るメモリシステムによれば、I/F LSIも不要で、インタポーラに伝送線構造を持たせる必要もなく、信号のデータレートもDRAMのスピードと同じで、N倍化された高速部分がないので、実装設計が安価にできる。

30

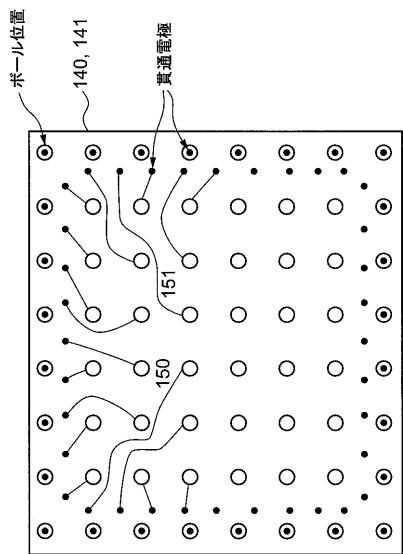

【0166】

図15は、図14のメモリシステムのCOCDRAM140の貫通電極の配置について検討するための図である。図15において、大きい丸は、インタポーラ141のボールの位置を示し、小さい黒丸は、COCDRAM140の貫通電極の位置を示す。COCDRAM140の貫通電極を設置できる位置は、図5を参照して説明したような制限があり、ここでは、チップ周辺部に形成されている。

【0167】

マザーボード142からインタポーラ141のボールに入った信号は、COCDRAM140の貫通電極位置まで、横方向に走らなければならない。そのための配線がスタブとなる。図15に示す例では、配線150や151の長さが3mm以上に長くなっている。高速伝送向きではない。

40

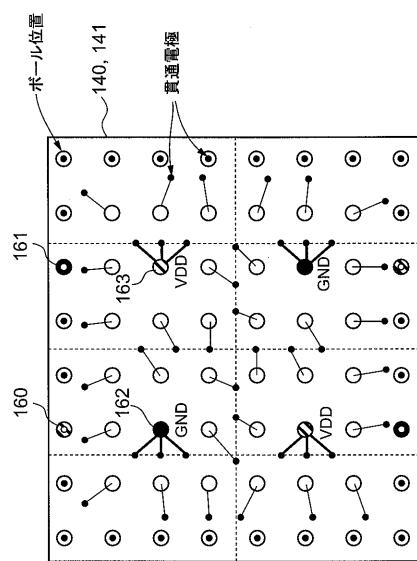

【0168】

そこで、図14のメモリシステムでは、図16に示すように、COCDRAM140の貫通電極を配置する。即ち、チップ周辺部のみならず、チップのセンターライン等の周辺回路領域にも設置するようにする。このように、COCDRAM140の貫通電極を配置することにより、各貫通電極が接続されるインタポーラ141のボールまでの距離、即ちスタブ長を短くしている。また、VDDやGNDに接続される貫通電極は、それらが割

50

り当り当たる半田ボール 160 や 161 の真上に貫通電極を設ける。あるいは、VDD や GND に割り当たる半田ボール 162 や 163 のできるだけ近くに貫通電極を設けて太い配線で接続する。この場合、貫通電極同士を接続してもよい。

【0169】

図 16 の例では、貫通電極のピッチが 0.8 mm 程度と大きいので、インタポーザ 141 として、PCB を用いることが可能で、コスト低減が可能となる。

【0170】

図 17 は、図 14 のメモリシステムに適用可能な COC DRAM140 の貫通電極配置の他の例である。図 16 の例と異なる点は、COC DRAM140 の貫通電極を極力センターラインに設置した点である。現在の DRAM は、パッドの大部分がセンターラインに設置されている場合が多いため、そのレイアウト構成を活用でき、設計期間の短縮が可能となる。もちろん、スタブ長が短くできていることは言うまでもない。

10

【0171】

この場合には、貫通電極のピッチが最小 40 μm 程度と小さいので、インタポーザ 141 として、Si インタポーザを用いることが必要である。

【0172】

図 18 は、図 17 に示す貫通電極配置を持つ COC DRAM140 と、それが積層された Si インターポーザ 141 の構造を示す縦断面図である。図 18 において、電源関係の貫通電極は、インタポーザ 141 と COC DRAM140 とを貫通している。また、信号用の貫通電極は、インタポーザ 141 の貫通電極と COC DRAM140 の貫通電極の位置は必ずしも一致していない。

20

【0173】

PCB インタポーザを用いた場合も、図 18 と同様な構成となる。

【0174】

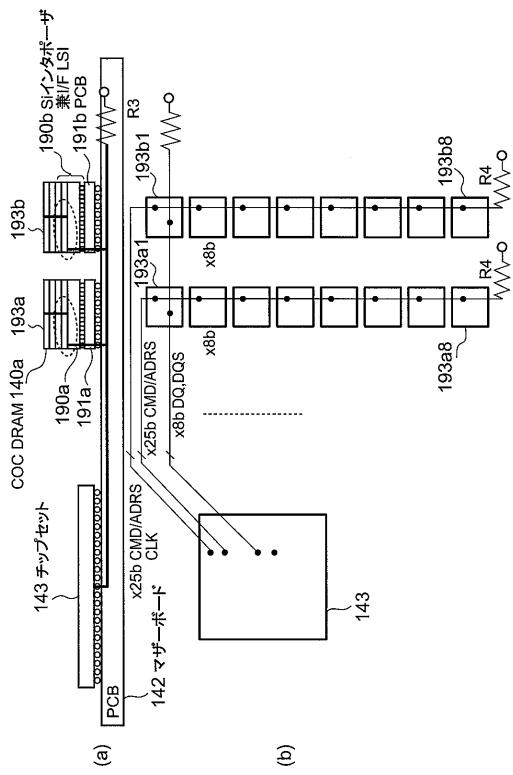

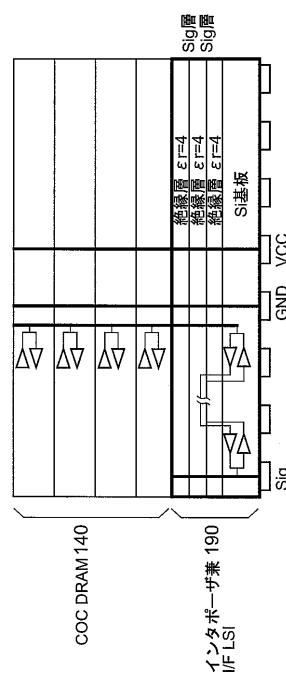

次に、図 19 (a) 及び (b) を参照して、本発明の第 6 の実施の形態に係るメモリシステムについて説明する。

【0175】

本実施の形態に係るメモリシステムが、図 14 のメモリシステムと異なっている点は、インタポーザ 141 に代えて Si インタポーザ兼 I/F LSI190 を備えている点である。即ち、4 チップの DRAM が積層された COC DRAM140 と、Si インタポーザ兼 I/F LSI190 とが積層されて、DRAM 積層体 193 が構成されている。

30

【0176】

図 19 には、PCB 191 が示されているが、これは信頼性確保のために設けられたものであって、特性上は特に必要ではない。

【0177】

マザーボード 142 上に、チップセット 143 と、複数の DRAM 積層体が、図 14 と同様の配列及び接続で並べられている。チップセット 143 と COC DRAM140 の間の DQ, DQS 信号伝送は、最初の 8 ビット分が、DRAM 積層体 193a1, 193b1 と行われ、次の 8 ビット分が、DRAM 積層体 193a2, 193b2 と行われ、最終の 8 ビット分が、DRAM 積層体 193a8, 193b8 と行われる。接続方法は、図示したようなフライ・バイ方式であり、チップセット 143 と COC DRAM140 との間に、Si インタポーザ兼 I/F LSI190 が介在する。各信号線は、マザーボード 142 の特性インピーダンスが Z0 の場合は、DQ 系メインバスの遠端に Z0 より低い値の終端抵抗 R3 を接続して終端すればよい。この終端抵抗 R3 の値は、伝送線に負荷 (Si インタポーザ兼 I/F LSI190) が接続されるため、容量が増え、実効特性インピーダンスが下がるので、その実効特性インピーダンスに合わせればよい。

40

【0178】

チップセット 143 と COC DRAM140 との間の CA 信号伝送は、1 コピー分が、DRAM 積層体 193a1, 193a2, ..., 193a8 と行われ、別の 1 コピー分が、DRAM 群 193b1, 193b2, ..., 193b8 と行われる。CA 信号を

50

捕まえるための C L K も同様である。接続方法は、図示したようなフライ・バイ方式で、D Q , D Q S 信号用の信号線と直交している。これらの信号の場合も、チップセット 143 と C O C D R A M 1 4 0 の間に、S i インタポーラ兼 I / F L S I 1 9 0 が介在する。マザーボード 142 の特性インピーダンスが Z 0 の場合は、C A 系メインバスの遠端に Z 0 より低い値の終端抵抗 R 4 で終端すればよい。

#### 【 0 1 7 9 】

本実施の形態に係るメモリシステムでは、D Q 、C A 信号用のいずれの配線も、マザーボード 142 を走るメインバスから S i インタポーラ兼 I / F L S I 1 9 0 へ分岐され、図 14 のように、C O C D R A M まで直接配線されないので、そのスタブ長が短い。従って、このメモリシステムは、高速化が可能である。

10

#### 【 0 1 8 0 】

次に図 19 のメモリシステムの動作について説明する。

#### 【 0 1 8 1 】

まず、チップセット 143 から、C O C D R A M 1 4 0 a に書き込む場合について述べる。

#### 【 0 1 8 2 】

チップセット 143 から、D Q 信号、C A 信号等が出力される。ここで、チップセット 143 のドライバのオン抵抗は、それぞれのメインバスの実効特性インピーダンスに合わせておくことが望ましい。

#### 【 0 1 8 3 】

S i インタポーラ兼 I / F L S I 1 9 0 a は、チップセット 143 から入力される信号をバッファリングし、C O C D R A M 1 4 0 a へ出力する。C O C D R A M 1 4 0 a は、S i インタポーラ兼 I / F L S I 1 9 0 a からのコマンド信号を解読し、対応するアドレスにデータを書き込む。ここで、S i インタポーラ兼 I / F L S I 1 9 0 a と C O C D R A M 1 4 0 a との間は、終端は不要である。

20

#### 【 0 1 8 4 】

C O C D R A M 1 4 0 b への書き込みも、上記と同様に行われる。

#### 【 0 1 8 5 】

次に、C O C D R A M 1 4 0 a からデータを読み出す場合について述べる。

#### 【 0 1 8 6 】

チップセット 143 から、C A 信号等が出力される。チップセット 143 から出力された C A 信号等は、S i インタポーラ兼 I / F L S I 1 9 0 a を経て、C O C D R A M 1 4 0 a に供給される。C O C D R A M 1 4 0 a は、コマンド信号を解読し、対応するアドレスからデータを読み出す。読み出されたデータは、S i インタポーラ兼 I / F L S I 1 9 0 a を経て、チップセット 143 送られ、取り込まれる。従って、読み出し時には、チップセット 143 に終端抵抗 R 3 を持たせることが望ましい。読み出し時も、S i インタポーラ兼 I / F L S I 1 9 0 a と C O C D R A M 1 4 0 a 間は、終端は不要である。

30

#### 【 0 1 8 7 】

C O C D R A M 1 4 0 b からデータを読み出す場合も同様である。

40

#### 【 0 1 8 8 】

本実施の形態に係るメモリシステムによれば、S i インタポーラ兼 I / F L S I 1 9 0 で、一旦信号を切るので、スタブ長が短くなり、高速動作が可能になる。また、C O C D R A M 1 4 0 の積層数 ( D R A M チップ数 ) が増えても、メインバスの負荷は、S i インタポーラ兼 I / F L S I 1 9 0 のみで変わらないので、大容量化と高速化を両立できる。さらに、S i インタポーラ兼 I / F L S I 1 9 0 のサイズが大きい場合でも、スタブ長を短くできる。

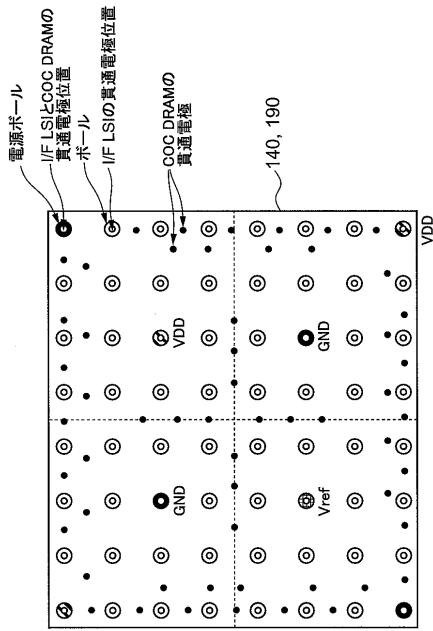

#### 【 0 1 8 9 】

図 20 は、図 19 のメモリシステムの D R A M 積層体における、C O C D R A M の貫通電極と、S i インタポーラ兼 I / F L S I の貫通電極及びボールとの位置関係の一例

50

を示す図である。

【0190】

図20において、大きい丸はSiインタポーザ兼I/F LSIのボール、小さい白丸は、Siインタポーザ兼I/F LSIの貫通電極、小さい黒丸は、COC DRAMの貫通電極である。

【0191】

COC DRAMの貫通電極は、図5を参照して説明したように、チップ周辺や、チップのセンターライン等の周辺回路領域にも設置できるので、それらの領域に設置している。また、VDDやGNDに割り当てるボールの真上に、I/F LSIとCOC DRAMの貫通電極が設けられている。信号に割り当てるボールの真上にはI/F LSIの貫通電極が設置されている。 10

【0192】

以上のように貫通電極を設けることによって、電源、GND電位は、最短の直線で、Siインタポーザ兼I/F LSI 190とCOC DRAM 140に供給されるので安定な電源供給が可能になる。

【0193】

図21は、図19のメモリシステムのDRAM積層体における、COC DRAMの貫通電極と、Siインタポーザ兼I/F LSIの貫通電極及びボールとの位置関係の他の例を示す図である。図20と大きく異なる点は、COC DRAM 140の貫通電極を極力センターラインに設置した点である。現在のDRAMは、パッドの大部分がセンターラインに設置されている場合が多いので、現在のDRAMチップのレイアウト構成を活用でき、設計期間の短縮が可能となる。 20

【0194】

図22は、図19、図20又は図21のDRAM積層体の縦断面構造を示す図である。図22において、電源関係の貫通電極は、Siインタポーザ兼I/F LSI 190とCOC DRAM 140を貫通している。また、信号の貫通電極は、Siインタポーザ兼I/F LSI 190とCOC DRAM 140とで独立して設けられ、Siインタポーザ兼I/F LSI 190の中で論理回路等を介して互いに接続されている。なお、Siインタポーザ兼I/F LSI 190の中での接続は、DQ等については双方向信号であるので双方向に行われている。 30

【0195】

以上の説明で判るように、マザーボード142から分岐して、Siインタポーザ兼I/F LSI 190に入るスタブ長は短い。

【0196】

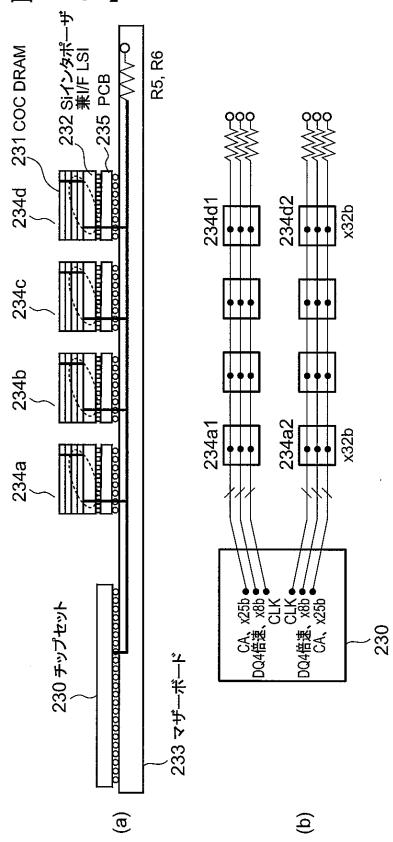

次に、図23(a)及び(b)を参照して本発明の第7の実施の形態に係るメモリシステムについて説明する。

【0197】

図23のメモリシステムは、メインバスのスピードをN倍速、例えば4倍速にしたメモリシステムである。このメモリシステムは、4~8個のDRAMチップが積層されたCOC DRAM 231と、それと同様の平面サイズを持つインタポーザ(Siインタポーザ兼I/F LSI 232及びPCB 235)とが積層されたDRAM積層体234を複数備える。また、このメモリシステムは、これらDRAM積層体234を搭載するマザーボード233と、マザーボード上に搭載されたチップセット230とを備える。 40

【0198】

COC DRAMは×32ビット構成であり、1チャンネルが64ビットの場合は、図(b)に示すようにDRAM積層体234(234a1, 234a2)を2個一組として並置する。複数組のDRAM積層体234は、チップセット230から遠ざかるように一方向に沿って並べられる。図23(b)は、4組のDRAM積層体234の例を示している。

【0199】

Siインターポーラ兼I/F LSI232は、図23(a)に示すように、同じ平面サイズのPCB235とフリップチップ接続され、PCB235の半田ボールを用いてマザーボード233に接続される。この場合、Siインターポーラ232とPCB235との組み合わせをインターポーラと見なせる。あるいは、Siインターポーラ兼I/F LSI232は、マザーボード233に直接フリップチップ接続で搭載されてもよい。

#### 【0200】

チップセット230とCOC DRAM231との間のDQ, DQS信号伝送は、フライ・バイ方式で接続された信号線を用いて行われる。即ち、チップセット230は、DQ, DQS信号のうち8ビット分を4倍速で、DRAM積層体234a1-234d1とやり取りし、残りの8ビット分を同じく4倍速で、DRAM積層体234a2-234d2とやり取りする。

10

#### 【0201】

DQ, DQS信号用の信号線は、マザーボード233の配線の特性インピーダンスがZ0の場合、メインバスの遠端にZ0より低い値の終端抵抗R5を接続することにより終端される。この終端抵抗R5の値は、伝送線に負荷が接続されるため、容量が増え、実効特性インピーダンスが下がるので、その実効特性インピーダンスに合わせればよい。

#### 【0202】

チップセット230とCOC DRAM231との間のCA信号伝送は、DQ, DQS信号用の信号線と同じくフライ・バイ方式の信号線により行われる。また、この信号線は、DQ, DQS信号用の信号線と平行に設けられる。チップセット230は、CA信号の1コピー分を、DRAM群234a1-234d1とやり取りし、別の1コピー分を、DRAM群234a2-234d2とやり取りする。CA信号を捕まえるためのCLKも同様である。

20

#### 【0203】

CA信号用の信号線は、マザーボード233の特性インピーダンスがZ0の場合、遠端にZ0より低い値の終端抵抗R6を接続することにより終端される。

#### 【0204】

DQ信号用及びCA信号用のいずれの信号線も、マザーボード233を走るメインバスから各COC DRAM231に向かい分岐される。その分岐によるスタブ長が長いとそこでの信号反射が大きくなり、信号インテグリティが悪くなる。本実施の形態に係るメモリシステムでは、Siインターポーラ兼I/F LSI232がCOC DRAM231とメインバスとの間に挿入されているので、スタブ長が短く、高い信号インテグリティを実現できる。

30

#### 【0205】

次に図23のメモリシステムの動作について説明する。

#### 【0206】

まず、チップセット230から、COC DRAM231aに書き込む場合について述べる。

#### 【0207】

チップセット230から、DQ信号、CA信号等が出力される。ここで、チップセット230のドライバのオン抵抗は、それぞれのメインバスの実効特性インピーダンスに合わせておくことが望ましい。

40

#### 【0208】

Siインターポーラ兼I/F LSI232aは、チップセット230からの入力信号をバッファリング、あるいは、スピード変換等を実施して、COC DRAM231aへ出力する。ここで、Siインターポーラ兼I/F LSI232aとCOC DRAM231a間は、終端は不要である。

#### 【0209】

COC DRAM231aは、入力されたコマンド信号を解読し、対応するアドレスにデータを書き込む。

50

## 【0210】

他のCOC DRAM231b等に書き込む場合も、上記と同様である。

## 【0211】

次に、COC DRAM231aからデータを読み出す場合について述べる。

## 【0212】

チップセット230から、CA信号等が出力される。Siインターポーラ兼I/F LSI232aは、チップセット230からのCA信号等をCOC DRAM231aへ出力する。COC DRAM231aは、入力されたコマンド信号を解読し、対応するアドレスからデータを読み出す。読み出されたデータは、Siインターポーラ兼I/F LSI232aを経て、チップセット230へ送られ、取り込まれる。従って、読み出し時には、チップセット230に終端抵抗を持たせることが望ましい。その値は、メインバスの実効特性インピーダンスに等しい値(R5又はR6)である。読み出し時も、Siインターポーラ兼I/F LSI232aとCOC DRAM231aとの間は、終端は不要である。10

## 【0213】

他のCOC DRAM231b等からデータを読み出す場合も、上記と同様である。

## 【0214】

本実施の形態に係るメモリシステムによれば、Siインターポーラ兼I/F LSI232で、一度信号を切るので、スタブ長が短くなり、高速動作が可能である。また、COC DRAMのDRAMチップ数を増加させても、メインバスの負荷は、Siインターポーラ兼I/F LSI232のみで変わらないので、大容量化と高速化の両立を図ることができる。さらに、DRAMのビット構成が大きくなつて、Siインターポーラ兼I/F LSI232のサイズが大きくなつた場合でも、スタブ長を短くできる。20

## 【0215】

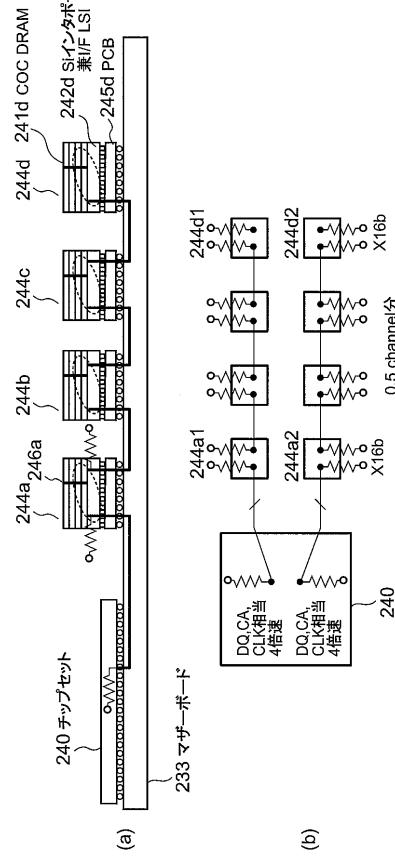

図24(a)、(b)に、本発明の第8の実施の形態に係るメモリシステムを示す。このメモリシステムは、×16ビット構成のCOC DRAM241を複数備えている点で図23のメモリシステムと異なつてゐる。

## 【0216】

詳述すると、このメモリシステムは、マザーボード233と、マザーボード上に搭載されたチップセット240と、複数のDRAM積層体244とからなる。

## 【0217】

各DRAM積層体244は、積層された8~16個のDRAMチップと、Siインターポーラ兼I/F LSI242と、PCB245とを含む。Siインターポーラ兼I/F LSI242はPCB245にフリップチップ接続され、PCB245はマザーボードに半田ボールで接続される。PCB245は、必ずしも必要ではなく、Siインターポーラ兼I/F LSI242を直接マザーボードにフリップチップ接続するようにしてもよい。30

## 【0218】

DRAM積層体244は、1チャンネルが64ビットであるとすると、4個一組(図では、0.5チャンネル分の2個のみ示す。)で用いられ、記憶容量に応じて複数組のDRAM積層体がCOCチップセット240から遠ざかるように一方向に並べて配置される。各組の4個のDRAM積層体244は、チップセット240に対して、実質的に等距離にある。40

## 【0219】

チップセット240とSiインターポーラ兼I/F LSI242との間の信号伝送線は、ポイント・トゥ・ポイント接続である。マザーボード233中の配線は、特性インピーダンスZ0で行う。隣り合うSiインターポーラ兼I/F LSI242間の信号伝送線も、ポイント・トゥ・ポイント接続である。これらの間でもマザーボード233中では、特性インピーダンスZ0で配線を行う。各ポイント・トゥ・ポイント接続の伝送線の受信側は、終端抵抗Z0で終端し、ドライバ側は、ソース抵抗Z0で整合させる。こうして、ポイント・トゥ・ポイント接続部の伝送信号は反射を抑えられ、良好な信号インテグリティが得られる。50

## 【0220】

Siインターポーラ兼I/F LSI242とCOC DRAM241との間の信号伝送は、COC DRAM241に形成された貫通電極246を介してなされる。図24(a)には、各COC DRAM241について貫通電極が1本しか示されていないが、DQ、電源等ように必要な本数分だけ設けられる。信号として、DQ信号、DQS信号、CA信号、CLK等があり、種類毎に信号の授受を行われる。これらの信号用の配線は、全て同じトポロジーでなされている。このため、各信号のスキューはほとんど発生しない。また、COC DRAM241の貫通電極の長さも、8チップ積層の場合で0.4mm程度と短いので、この部分の伝送部は、集中定数とみなせ、終端抵抗は不要である。従って、Siインターポーラ兼I/F LSI242とCOC DRAM241間の信号伝送線に波10終端抵抗が不要であるので、低消費電力動作が可能となる。

## 【0221】

次に、本実施の形態に係るメモリシステムの動作について説明する。

## 【0222】

まず、チップセット240から、COC DRAM241aに書き込む場合について述べる。

## 【0223】

チップセット240から、DQ信号、CA信号等の情報を含むプロトコル信号がSiインターポーラ兼I/F LSI242aに供給される。Siインターポーラ兼I/F LSI242aは、プロトコルに従ってチップセット240からの信号を解読し、COC DRAM241aへ、CA信号、DQ信号、CLK等を出力する。COC DRAM241aは、入力されたCA信号等に従い、対応するアドレスにデータを書き込む。20

## 【0224】

COC DRAM241bに書き込む際は、チップセット240から出力されたプロトコル信号が、Siインターポーラ兼I/F LSI242aを介して、Siインターポーラ兼I/F LSI242bに伝送される。Siインターポーラ兼I/F LSI242bは、プロトコルに従って入力された信号を解読し、COC DRAM241bへ、CA信号、DQ信号、CLK等を出力する。COC DRAM241bは、Siインターポーラ兼I/F LSI242bからの信号に従い、対応するアドレスにデータを書き込む。

## 【0225】

他のCOC DRAM241c等への書き込みも上記と同様にして行われる。30

## 【0226】

次に、COC DRAM241aからデータを読み出す場合について述べる。

## 【0227】

チップセット240から、CA信号等の情報を含むプロトコル信号がSiインターポーラ兼I/F LSI242aに供給される。Siインターポーラ兼I/F LSI242aは、プロトコルに従って入力される信号を解読し、COC DRAM241aへ、CA信号、CLK等を出力する。COC DRAM241aは、Siインターポーラ兼I/F LSI242aからの信号に従い、対応するアドレスからデータを読み出す。読み出されたデータは、Siインターポーラ兼I/F LSI242aに取り込まれ、Siインターポーラ兼I/F LSI242aから、プロトコル信号としてチップセット240へ伝送される。40

## 【0228】

COC DRAM241bからデータを読み出す場合は、チップセット240からのCA信号等の情報を含むプロトコル信号がSiインターポーラ兼I/F LSI242aを介してSiインターポーラ兼I/F LSI242bに供給される。Siインターポーラ兼I/F LSI242bは、プロトコルに従って入力された信号を解読し、COC DRAM241bへ、CA信号、CLK等を出力する。COC DRAM241bは、入力された信号に従い、所定のアドレスからデータを読み出す。読み出されたデータは、Siインターポーラ兼I/F LSI242bに取り込まれ、Siインターポーラ兼I/F LSI242bからSiインターポーラ兼I/F LSI242aを介して、プロトコル信号としてチ50

ップセット240に伝送される。

【0229】

他のCOC DRAM241c等からデータを読み出す場合も、上記と同様にして行われる。

【0230】

本実施の形態に係るメモリシステムによれば、COC DRAM241のピット構成を小さくし、かつプロトコル信号のデータレートが高くしたので、Siインターポーラ兼I/F LSI242のサイズを、COC DRAM241と同等にでき、伝送線構造のインターポーラが不要となる。また、各接続がポイント・トゥ・ポイント接続であるので、高速動作が可能である。

10

【0231】

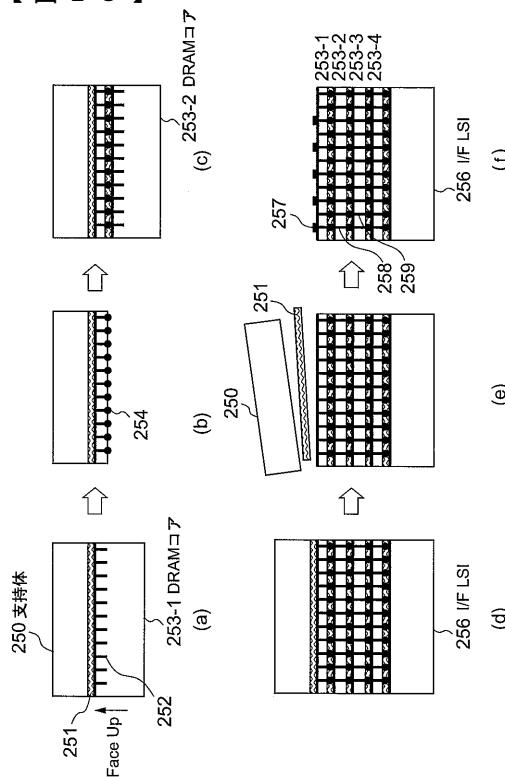

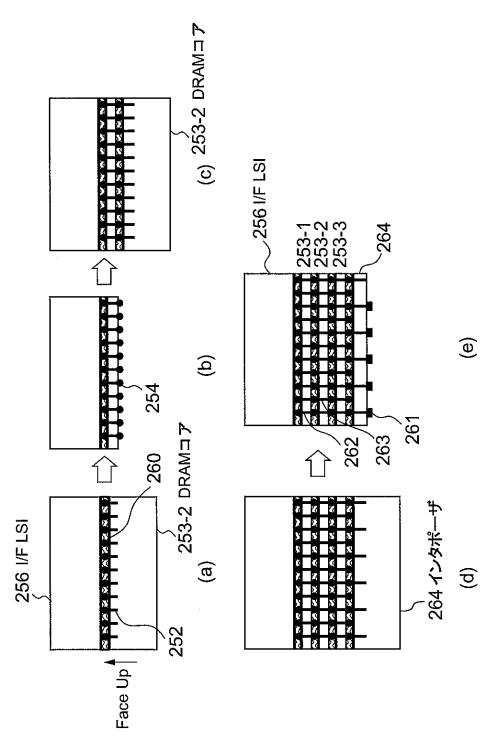

次に、図25を参照して、上述した第5乃至第8の実施の形態に係るメモリシステムに適用可能なCOC DRAM及びI/F LSIの積層方法について説明する。ただし、上述したメモリシステムのI/F LSIは、貫通電極を有するものであったが、ここで説明するのは、貫通電極を持たない（持たせるのが難しい）I/F LSIを含む積層体の積層方法である。

【0232】

まず、図25(a)に示すように、表面側に貫通電極252が設けられたDRAMコア253-1を、接着物251を用いて支持体250に接続固定する。

【0233】

次に、DRAMコア253-1を裏面側から研削し、貫通電極が露出するまで薄くする。それから、露出した貫通電極に貫通電極端子254を付け、図25(b)に示す状態とする。これで一層のDRAMチップが形成された状態である。

20

【0234】

その後、DRAMコア235-1と同様の別のDRAMコア253-2を貫通電極端子254が形成されたDRAMコア235-1に積層し、図25(c)のようとする。その後、DRAMコア235-2の裏面を貫通電極が露出するまで削り、貫通電極端子を付ける。

【0235】

以後、DRAMコアの積層、研削、及び貫通電極端子形成の各工程を繰り返し、所望の層数だけDRAMチップを形成する。

30

【0236】

その後、図25(d)に示すように、貫通電極を設けていないI/F LSI256をフェースアップの状態で、最後に形成されたDRAMの貫通電極端子と接続、積層する。

【0237】

それから、図25(e)に示すように支持体250を取り去り、接着物251を剥離する。

【0238】

最後に、積層体の上面側の貫通電極にフリップチップ接続端子257等を設ける。

【0239】

40

図25の積層方法により製造された積層体における信号の流れについて説明する。

【0240】

フリップチップ接続端子257に入った信号は、貫通電極258を介して、一端I/F LSI256に入る。I/F LSI256に入った信号は、I/F LSI256の中で論理演算処理等され、貫通電極259に出力され、貫通電極259を介して各DRAM253に供給される。

【0241】

COC DRAM253から出力される信号は、上記と逆の経路を辿る。

【0242】

このように、図25の積層方法により製造された積層体では、COC DRAMの上面

50

側から入力された信号が、一旦、その裏面側の I / F L S I に導かれるため、信号の伝送距離が長くなる。しかし、C O C D R A M の厚さは 1 枚 5 0  $\mu$ m 程度であるので、遅延、反射等が特に問題となることはない。従って、このような積層方法を利用することにより、I / F L S I に貫通電極を設けるのが、難しい場合であっても、C O C D R A M を用いたメモリシステムを構築することができる。

【 0 2 4 3 】

次に、図 2 6 を参照して、C O C D R A M 、I / F L S I 及びインタポーザを積層する方法について説明する。なお、この方法は、図 2 5 で説明した方法のように支持体は使用しない。

【 0 2 4 4 】

まず、図 2 6 ( a ) に示すように、支持体の役目を果たす I / F L S I 2 5 6 に、その表面側に貫通電極 2 5 2 とそれに接続された貫通電極端子 2 6 0 を設けた D R A M コア 2 5 3 - 1 を接続固定する。

【 0 2 4 5 】

続いて、D R A M コア 2 5 3 - 1 を裏面側から研削し、貫通電極が露出するまで薄くする。そして、露出した貫通電極に貫通電極端子 2 5 4 を付け、図 2 6 ( b ) の状態とする。

【 0 2 4 6 】

その後、貫通電極端子 2 5 4 が形成された D R A M コア 2 5 3 - 1 の下面に、D R A M コア 2 5 3 - 1 と同様の D R A M コア 2 5 3 - 2 を積層し、図 2 6 ( c ) の状態とする。それから、D R A M コア 2 5 3 - 2 を裏面側から研削し、貫通電極が露出するまで薄くする。そして、露出した貫通電極に貫通電極端子を付ける。

【 0 2 4 7 】

以降、所望の総数の D R A M チップを積層するまで上記工程を繰り返す。

【 0 2 4 8 】

その後、図 2 6 ( d ) に示すように、表面側に貫通電極を設けたインタポーザ 2 6 4 を、最下層の D R A M チップに積層し、D R A M チップ側に形成された貫通電極端子とインタポーザ 2 6 4 の貫通電極とを接続する。

【 0 2 4 9 】

最後に、インタポーザ 2 6 4 を裏面側から研削し、貫通電極が露出するまで薄くし、露出した貫通電極にフリップチップ接続端子 2 6 1 を設け、図 2 6 ( e ) に示す状態とする。なお、インタポーザ 2 6 4 が不要の場合には、最下層の D R A M チップ 2 5 3 - 3 の露出した貫通電極にフリップチップ接続端子を設ける用にもできる。

【 0 2 5 0 】

次に、図 2 6 の積層方法により製造された積層体における信号の流れについて説明する。

【 0 2 5 1 】

フリップチップ接続端子 2 6 1 に入った信号は、貫通電極 2 6 2 を介して、I / F L S I 2 5 6 に入る。I / F L S I 2 5 6 に入った信号は、I / F L S I 2 5 6 の中で、論理信号処理されるなどして、貫通電極 2 6 3 に出力される。貫通電極 2 6 3 に出力された信号は、各 D R A M チップに供給される。

【 0 2 5 2 】

C O C D R A M 2 5 3 から出力される信号は、上記の経路とは逆の経路を辿る。

【 0 2 5 3 】

図 2 6 の方法によれば、図 2 5 の方法に比べて支持体の剥離工程が省けるので、剥離工程においてチップに割れが生じる恐れを低減することができる。

【 0 2 5 4 】

図 2 5 の方法により製造した積層体の場合と同様、図 2 6 の方法により製造された積層体のC O C D R A M の厚さは 1 枚 5 0  $\mu$ m 程度なので、下面側に入力された信号を上面側の I / F L S I を介して各 D R A M チップに供給するようにしても、遅延、反射等が

特に問題となることない。従って、このような積層方法を利用することにより、I/F LSIに貫通電極を設けるのが、難しい場合であっても、インタポーラ及びCOC DRAMを用いたメモリシステムを構築することができる。

【図面の簡単な説明】

【0255】

【図1】本発明の第1の実施の形態に係るメモリシステムの構成を示す図であって、(a)は縦断面構成図、(b)は平面構成図である。

【図2】図1のメモリシステムに用いられるDRAM積層体の左半分を示す図である。

【図3】図1のメモリシステムにおいてインタポーラがPCBを必要とする理由を説明するための図である。

【図4】図1のメモリシステムに用いられるインタポーラの詳細な構成を説明するための図である。

【図5】図1のメモリシステムに含まれるCOC DRAMにおいて貫通電極を設置できる場所を説明するための図である。

【図6】図1のメモリシステムにおける、Siインタポーラ、I/F LSI及びCOC DRAMにそれぞれ形成された貫通電極の位置関係を説明するための図である。

【図7】本発明の第2の実施の形態に係るメモリシステムの構成を示す図である。

【図8】図1及び図7のメモリシステムに共通の、I/F LSIの配置方法について説明するための図であって、(a)はフェースアップ、(b)はフェースダウンの場合を示す図である。

【図9】図1及び図7のメモリシステムに用いられるI/F LSIの構成を説明するための図であって、(a)はその回路構成図、(b)は比較のための一般的な回路構成図である。

【図10】本発明の第3の実施の形態に係るメモリシステムの構成を示す図であって、(a)は縦断面構成図、(b)は平面構成図である。

【図11】本発明の第4の実施の形態に係るメモリシステムの構成を示す図であって、(a)は縦断面構成図、(b)は平面構成図である。

【図12】図10及び図11に示すメモリシステムにおけるインタポーラのボールへの信号の割り振りを説明するための図であって、(a)は縦断面構成図、(b)は平面構成図である。

【図13】図12(b)の右上部分における、インタポーラのボールへの信号の割り振り、及びボールとCOC DRAMの貫通電極端子との接続の詳細例を示す図である。

【図14】本発明の第5の実施の形態に係るメモリシステムの構成を示す図であって、(a)は縦断面構成図、(b)は平面構成図である。

【図15】図14のCOC DRAMの貫通電極の配置に関する検討を行うための図である。

【図16】図14のCOC DRAMの貫通電極の配置、及びそれら貫通電極とボールとの接続を説明するための図である。

【図17】図14のCOC DRAMの貫通電極の他の配置、及びそれら貫通電極とボールとの接続を説明するための図である。

【図18】図17の貫通電極配置のCOC DRAMとそれが積層されるSiインタポーラとの構造を示す縦断面構成図である。

【図19】本発明の第6の実施の形態に係るメモリシステムの構成を示す図であって、(a)は縦断面構成図、(b)は平面構成図である。

【図20】図19のメモリシステムにおけるCOC DRAM及びI/F LSIそれぞれ設けられた貫通電極とI/F LSIのボールとの位置関係を示す図である。

【図21】図19のメモリシステムにおけるCOC DRAM及びI/F LSIそれぞれ設けられた貫通電極とI/F LSIのボールとの位置関係の他の例を示す図である。

【図22】図19、図20あるいは図21のDRAM積層体の構成を示す縦断面構成図である。

10

20

30

40

50

【図23】本発明の第7の実施の形態に係るメモリシステムの構成を示す図であって、(a)は縦断面構成図、(b)は平面構成図である。

【図24】本発明の第8の実施の形態に係るメモリシステムの構成を示す図であって、(a)は縦断面構成図、(b)は平面構成図である。

【図25】(a)乃至(f)は、図14、図19、図23及び図24に示すメモリシステムに適用可能なCOC DRAM及びI/F LSIの積層方法を説明するための図である。

【図26】(a)乃至(e)は、図14、図19、図23及び図24に示すメモリシステムに適用可能なCOC DRAM、I/F LSI及びインタポーラの積層方法を説明するための図である。

【図27】従来のメモリシステム構成を示す概略図。

【符号の説明】

【0256】

|                                                                                                                                                                                                                                                                                                                                                           |                  |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----|

| 1 a , 1 b                                                                                                                                                                                                                                                                                                                                                 | D I M M          |    |

| 2 a , 2 b , 9 2 , 9 4 - 1 , 9 4 - 2                                                                                                                                                                                                                                                                                                                       | バッファ             |    |

| 3 a , 3 b , 6 - 1 , 6 - 2 , 7 0 , 9 1 - 1 , 9 1 - 2                                                                                                                                                                                                                                                                                                       | D R A M チップ      | 10 |

| 4 , 1 0 2 , 1 0 3 , 1 4 3 , 2 3 0 , 2 4 0                                                                                                                                                                                                                                                                                                                 | チップセット           |    |

| 5 , 1 4 2 , 2 3 3                                                                                                                                                                                                                                                                                                                                         | マザーボード           |    |

| 6 , 6 a , 6 b , 1 4 0 , 1 4 0 a , 1 4 0 b , 2 3 1 , 2 4 1 d                                                                                                                                                                                                                                                                                               | C O C D R A      |    |

| M                                                                                                                                                                                                                                                                                                                                                         |                  | 20 |

| 7 a , 7 b , 1 4 1 , 1 4 1 a , 1 4 1 b , 2 6 4                                                                                                                                                                                                                                                                                                             | インタポーラ           |    |

| 8 , 8 a , 8 b                                                                                                                                                                                                                                                                                                                                             | S i 基板部          |    |

| 9 , 9 a , 9 b , 3 1                                                                                                                                                                                                                                                                                                                                       | 絶縁層部             |    |

| 1 0 , 1 0 a , 1 0 b 、 3 0                                                                                                                                                                                                                                                                                                                                 | S i (シリコン)部      |    |

| 1 1 , 1 1 a , 1 1 b , 1 9 1 a , 1 9 1 b                                                                                                                                                                                                                                                                                                                   | P C B 部          |    |

| 1 2 , 1 2 a , 1 2 b , 9 0 , 2 5 6                                                                                                                                                                                                                                                                                                                         | I / F L S I      |    |

| 1 4 a , 1 4 b , 1 0 0 a , 1 0 0 b , 1 4 4 a , 1 4 4 a 1 , 1 4 4 a 8 , 1 4 4 b , 1 4 4 b 1 , 1 4 4 b 8 , 1 9 3 a , 1 9 3 a 1 , 1 9 3 a 8 , 1 9 3 b , 1 9 3 b 1 , 1 9 3 b 8 , 2 3 4 a , 2 3 4 a 1 , 2 3 4 a 2 , 2 3 4 b , 2 3 4 c , 2 3 4 d , 2 3 4 d 1 , 2 3 4 d 2 , 2 4 4 a , 2 4 4 a 1 , 2 4 4 a 2 , 2 4 4 b , 2 4 4 c , 2 4 4 d , 2 4 4 d 1 , 2 4 4 d 2 | D R A M 積層体      | 30 |

| 1 5 a , 1 5 b , 3 4 , 4 2 , 4 5 , 1 5 0 , 1 5 1                                                                                                                                                                                                                                                                                                           | 配線               |    |

| 1 6 , 1 6 a , 1 6 b , 3 8                                                                                                                                                                                                                                                                                                                                 | G N D レファレンスプレーン |    |

| 1 7 , 1 7 a , 1 7 b , 1 7 - 1 , 1 7 - 1 a , 1 7 - 2 , 1 7 - 2 a , 2 2 , 2 6 , 3 3 , 3 5 , 3 7 , 4 3 , 4 8 , 5 2 , 5 3 , 5 6 , 7 6 , 8 5 , 8 6 , 2 4 6 a , 2 5 2 , 2 5 8 , 2 5 9 , 2 6 2 , 2 6 3                                                                                                                                                           | 貫通電極             |    |

| 2 0 , 2 4 , 4 0 , 4 4 , 4 6 , 5 0 , 5 4 , 5 9 , 7 5 , 7 7 , 1 6 0 , 1 6 1 , 1 6 2 , 1 6 3                                                                                                                                                                                                                                                                 | 半田ボール            |    |

| 2 1 , 2 5 , 4 1 , 4 7 , 5 1 , 5 5 , 6 0                                                                                                                                                                                                                                                                                                                   | ピア               |    |

| 2 3                                                                                                                                                                                                                                                                                                                                                       | 論理回路             | 40 |

| 3 2 , 3 6                                                                                                                                                                                                                                                                                                                                                 | フリップチップ電極        |    |

| 4 9                                                                                                                                                                                                                                                                                                                                                       | G N D レファレンス線    |    |

| 5 7                                                                                                                                                                                                                                                                                                                                                       | V D D プレーン       |    |

| 5 8                                                                                                                                                                                                                                                                                                                                                       | V D D 線          |    |

| 7 1                                                                                                                                                                                                                                                                                                                                                       | メモリセルアレイ         |    |

| 7 2                                                                                                                                                                                                                                                                                                                                                       | 周辺回路領域           |    |

| 7 3                                                                                                                                                                                                                                                                                                                                                       | チップ周辺領域          |    |

| 7 8                                                                                                                                                                                                                                                                                                                                                       | カッピングコンデンサ       |    |

| 8 0                                                                                                                                                                                                                                                                                                                                                       | 小型高周波コネクタ        |    |

| 8 5 、 8 6                                                                                                                                                                                                                                                                                                                                                 | 信号群              | 50 |

9 3 - 1 , 9 3 - 2 C L K 分配回路

9 5 - 1 , 9 5 - 2 フリップフロップ群

1 3 0 端子

1 9 0 , 1 9 0 a , 1 9 0 b , 2 3 2 , 2 4 2 S i インタポーザ兼 I / F L S I

2 5 0 支持体

2 5 1 接着物

2 5 3 - 1 , 2 5 3 - 2 , 2 5 3 - 3 , 2 5 3 - 4 D R A M コア

2 5 4 貫通電極端子

2 5 7 フリップチップ接続端子

2 6 0 貫通電極端子

10

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【 义 8 】

【図9】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

【 図 1 4 】

【図15】

【図16】

【図17】

【図18】

【図 19】

【図 20】

【図 21】

【図 22】

【図 2 3】

【図 2 5】

【図 2 4】

【図 2 6】

【図27】

---

フロントページの続き

審査官 坂本 薫昭

(56)参考文献 特開平06-177318(JP,A)

特開平09-232503(JP,A)

特開平11-317494(JP,A)

特開2000-215956(JP,A)

特開2001-102479(JP,A)

特開2001-326305(JP,A)

特開2002-110865(JP,A)

特開2003-347502(JP,A)

特開2004-327474(JP,A)

特表2004-502174(JP,A)

特表2005-521178(JP,A)

特表2005-524239(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/14

H01L 23/32

H01L 25/065

H01L 25/07

H01L 25/18