(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4401776号

(P4401776)

(45) 発行日 平成22年1月20日(2010.1.20)

(24) 登録日 平成21年11月6日(2009.11.6)

(51) Int.Cl.

H03F 3/195 (2006.01)

H03G 3/10 (2006.01)

F 1

H03F 3/195

H03G 3/10

A

請求項の数 4 (全 7 頁)

(21) 出願番号 特願2003-539161 (P2003-539161)

(86) (22) 出願日 平成14年10月4日 (2002.10.4)

(65) 公表番号 特表2005-507202 (P2005-507202A)

(43) 公表日 平成17年3月10日 (2005.3.10)

(86) 國際出願番号 PCT/US2002/031859

(87) 國際公開番号 WO2003/036790

(87) 國際公開日 平成15年5月1日 (2003.5.1)

審査請求日 平成17年10月3日 (2005.10.3)

(31) 優先権主張番号 10/001,388

(32) 優先日 平成13年10月25日 (2001.10.25)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78735 テキサス州

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100116322

弁理士 桑垣 衡

(72) 発明者 コネル、ローレンス イー。

アメリカ合衆国 60565 イリノイ州

ネイバービル リオ グランデ サーク

ル 2464

最終頁に続く

(54) 【発明の名称】自動バイアス供給源調節機構を有する可変利得増幅器

## (57) 【特許請求の範囲】

## 【請求項 1】

入力で入力信号を受け、出力で出力信号を与える高利得増幅器と、

前記出力に接続され、かつ前記出力に負荷をかけ、前記出力信号に応答して前記出力負荷を調整する自動バイアス供給源と、

からなり、同自動バイアス供給源は、

正の入力で基準電圧によってバイアスをかけられる差動増幅器と、

前記出力と前記差動増幅器の出力との間に接続された負荷抵抗器と、

前記差動増幅器の前記出力と負の入力との間に接続された積分抵抗器と、

からなり、

前記高利得増幅器は、

差動トランジスタ対のそれぞれの第1の導電端末が共通接続点に接続され、該差動トランジスタ対の第1のトランジスタの第2の導電端末が供給電圧に接続され、該差動トランジスタの他方のトランジスタの第2の導電端末が前記出力である、差動トランジスタ対と前記共通接続点と前記入力との間に接続され、前記第3のトランジスタの第1の導電端末が、前記入力に接続され、第2の導電端末が前記共通接続点に接続されている、入力トランジスタと、前記入力トランジスタの制御端末に接続された第1のバイアス電圧と、前記差動トランジスタ対の1対の制御端末間に差動接続された第2のバイアス電圧と、

10

20

からなる、

広帯域高周波数増幅器。

【請求項 2】

前記積分抵抗器は、キャパシタと直列の抵抗器からなる請求項 1 に記載の広帯域高周波数増幅器。

【請求項 3】

広帯域高周波数線形増幅器を含み、同広帯域高周波数線形増幅器は、

入力で入力信号を受け、出力で出力信号を与える非反転高利得増幅器と、

前記出力に接続され、かつ前記出力に負荷をかけ、前記出力信号に応答して前記出力負荷を調整する自動バイアス供給源と、からなり、

10

前記非反転高利得増幅器は、

共通ソース接続を有し、差動電界効果トランジスタ対の第 1 の電界効果トランジスタのドレーンが供給電圧に接続され、前記差動電界効果トランジスタ対の他方の電界効果トランジスタのドレーンが前記出力である、差動電界効果トランジスタ (FET) 対と、

前記差動 FET 対の前記共通ソース接続と前記入力との間にドレーン・ソース接続された入力 FET と、

前記入力 FET のゲートに接続された第 1 のバイアス電圧と、

前記差動 FET 対のそれぞれのゲートに差動接続された自動利得制御電圧と、からなり

、

前記自動バイアス供給源は、

20

正の入力で基準電圧によってバイアスをかけられる差動増幅器と、

前記出力と前記差動増幅器の出力との間に接続された負荷抵抗器と、

同差動増幅器の出力と負の入力との間に接続された低域通過フィルタと、からなる集積回路チップ。

【請求項 4】

前記低域通過フィルタは、前記差動増幅器の出力と負の入力との間に接続された抵抗器と、前記負の入力とグランドとの間に接続されたキャパシタとである請求項 3 に記載の集積回路チップ。

【発明の詳細な説明】

【技術分野】

30

【0001】

本発明は、広帯域線形増幅器に関し、特に、抵抗負荷をかけられる広帯域高周波数線形増幅器に関する。

【背景技術】

【0002】

広帯域マルチチャネル通信システムには、搬送波の相互作用が起こる頻度が高いために起こる 2 次的および 3 次的な影響を回避するために高度の線形性を有する広帯域増幅器が必要である。したがって、増幅器の線形性を最大にするには 2 次的および 3 次的な影響を最小限に抑えなければならない。通常、大きな入力信号を補償するために、利得を少なくし、均一な利得を犠牲にして信号の線形性を拡張するある形の自動利得制御が含まれる。

40

【0003】

残念なことに、代表的な集積回路増幅器では、出力電流は一方向に流れ、すなわち、電源から電源リターンまたはグランドに流れるので、このような従来技術の増幅器は通常、電流を抵抗負荷まで / 抵抗負荷から離れる、方向に流し、したがって増幅器の DC 動作点が著しく変化する。このように動作点が変動すると、増幅器の線形性が不十分になり、増幅器の利得範囲が制限される。抵抗負荷に向かう電流が大きすぎる場合、出力電圧が著しく低下する可能性があり、増幅器が飽和し、線形性が不十分になるとと共に、増幅器信号応答および帯域幅が劣化する恐れがある。出力抵抗負荷に向かう電流が小さすぎる場合、出力電圧が著しく上昇し、デバイスの破滅的な故障が起こる可能性がある。

【0004】

50

したがって、広帯域マルチチャネル増幅器の負荷バイアスを安定させ、増幅器を所望の動作バイアス点に維持する必要がある。

前記およびその他の目的、態様、および利点は、図面を参照することによって、好ましい実施形態についての以下の詳細な説明からよりよく理解されよう。

#### 【発明を実施するための最良の形態】

##### 【0005】

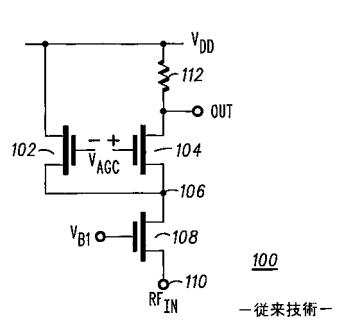

次に、図面、特に図1を参照すると、負荷抵抗器( $R_L$ )112によって受動負荷がかけられた代表的なこのようないくつかの従来技術の広帯域増幅器100が示されている。差動電界効果トランジスタ(FET)対102、104は、共通ソース接続106を有している。FET108は、入力110と共通ソース接続106との間にソース・ドレーン接合されている。FET102、104のゲート間に差動利得制御電圧( $V_{AGC}$ )が印加される。

FET108のゲートにバイアス電圧 $V_{B1}$ が印加される。FET102のドレーンは供給電圧( $V_{dd}$ )に直接接合され、FET104のドレーンは増幅器出力(OUT)に接合されている。負荷抵抗器 $R_L$ 112は、 $V_{dd}$ と増幅器出力との間に接続されている。

10

##### 【0006】

増幅器の線形性は、増幅器デバイス・バイアス状態、特に各増幅器デバイスのデバイス・ドレーン・ソース間電圧( $V_{ds}$ )の関数である。寄生デバイス・キャパシタンス、固有抵抗、および増幅器の過励振によって非線形性が導入されることがある。増幅器の過励振が起こるのは、増幅器デバイスのドレーン・ソース電圧が非常に低くなり、デバイスが飽和状態でなくなり、増幅器の線形性および/または帯域幅が劣化したときである。

20

##### 【0007】

理想的には、増幅器の動作範囲全体にわたって、すべての3つのFET102、104、および108に、飽和領域で動作するようにバイアスをかける。飽和時には、各デバイスのドレーン・ソース電圧( $V_{ds}$ )は、そのゲート・ソース間電圧( $V_{gs}$ )から特定のデバイスのしきい値電圧( $V_T$ )を引いた電圧よりも高くなる。すなわち、次式が成立する。

##### 【0008】

$$V_{ds} > V_{gs} - V_T$$

定常状態では、次式が成立する。

$$V_{out} = V_{dd} - I_{ds} * R_L$$

飽和状態のFETは、電圧制御電流源として働き、デバイス・ドレーン・ソース電流( $I_{ds}$ )は( $V_{gs} - V_T$ )<sup>2</sup>にほぼ正比例し、 $V_{ds}$ に依存しない。小信号用途(すなわち、信号の範囲が信号応答範囲の小さな一部である用途)の場合、FETドレーン電流の変化(=  $I_{ds}$ )は次式によって近似し得る。

30

##### 【0009】

$\frac{I_{ds}}{V_{gs}} = \frac{V_{gs}}{V_{T}}$

したがって、出力電圧 $V_{out}$ の変動、すなわち $V_{out}$ である出力信号は、 $-V_{gs}$ に比例し、ここで $V_{gs}$ はデバイス・トランスコンダクタンスである。 $V_{gs}$ はゲート・バイアス電圧 $V_{B1}$ 、各FETのソース電圧、および入力信号 $V_{RFIN}$ の関数である。

FET108のソースを駆動するあらゆる入力信号は実際上、FET108のゲートで反転され、したがって、次式が成立する。

40

##### 【0010】

$$V_{gs} = -V_{RFIN}$$

および

$$V_{out} = V_{RFIN} R_L$$

しかし、 $V_T$ は部分的に、ソース基板間バイアスの関数である。 $V_{gs}$ はゲート・バイアス電圧(FET108では $V_{B1}$ 、FET102、104では利得制御電圧 $V_{AGC}$ )および特定の各FETのソース電圧の関数である。 $V_{AGC}$ は、電流をFET104またはFET102を通して出力負荷抵抗器112に向ける利得・バイアス点をFET102、104に設定する。したがって、FET108では、次式が成立し、

50

【0011】

【数1】

$$\Delta I_{ds108} \cong -\Gamma_{108} V_{RFIN}$$

上式で、 $\Gamma_{108}$  は FET108 のトランスクンダクタンスであり、FET104 では、次式が成立し、

【0012】

【数2】

$$\Delta I_{ds104} = -\frac{\Gamma_{104}}{\Gamma_{104} + \Gamma_{102}} [\Gamma_{108} V_{RFIN}]$$

上式で、 $\Gamma_{102}$  および  $\Gamma_{104}$  はそれぞれ、FET102 および 104 のトランスクンダクタンスであり、さらに  $V_{AGC}$  に比例する。この場合、増幅器出力  $V_{out}$  は次式に等しい。

【0013】

【数3】

$$V_{out} = \frac{-\Gamma_{104}}{\Gamma_{104} + \Gamma_{102}} [\Gamma_{108} \cdot V_{RFIN}] \cdot R_L$$

上式は小さな信号には成立するが、より大きな信号では線形性問題が生じ、小信号近似が無効になり、 $I_{ds}$  を  $(V_{GS} - V_T)^2$  に比例するとみなさなければならない。したがって、この上記の関係は、出力がその線形動作範囲内であり、すなわち  $V_{AGC} + V_T < V_{out} < V_{dd}$  であり、かつ平均信号成分が零であり、すなわち  $V_{RFIN} = 0$  であるかぎり成立する。

【0014】

利得は、 $V_{AGC}$  またはバイアス電圧  $V_{B1}$  ( $V_{ds108}$  を変化させる) を変化させることによって変化させることができる。これらの基準電圧のいずれかの変化は、出力動作点に反映され、増幅器の線形性に影響を与える可能性がある。 $V_{B1}$  または  $V_{AGC}$  を高くすると、FET102、104、および 108 の 1 つまたはすべてについて  $V_{ds}$  が低くなり、したがって、十分な入力信号によって、影響を受けるデバイスは飽和状態でなくなり、デバイス・キャパシタンスが増し、増幅器線形性が不十分になる。さらに、平均信号成分が零でないとき動作点はシフトする。あらうる非零平均信号成分は DC 動作点シフトとして反映される。

【0015】

したがって、上記に指摘したように、FET104 は、増幅器が過励振されるように最初のバイアス点を設定したことによるか、それとも出力信号によって起こるバイアス点シフトによるものかにかかわらず、出力信号が  $V_{AGC} + V_T$  よりも低くなるような動作点の場合に飽和状態でなくなる。さらに、前述のように、バイアス点は、デバイス 102 または 104 がオフになり、潜在的な出力電圧 ( $V_{dd}$ ) のすべてまたはほぼすべてがオフ・デバイス全体にわたって検知されるようにシフトする可能性がある。したがって、オフ・デバイスについては、 $V_{ds}$  がデバイス破壊電圧を超える、FET104 および 102 のいずれかまたは両方を破壊する恐れがある。

10

20

30

40

50

## 【0016】

簡単に言えば、上述のように、増幅器100には、一定の電流がFET108を通って流れ、RFINにおけるあらゆる信号変動によって、デバイス104を通る電流の線形変動が生じるように、バイアスがかけられる。デバイス104を通る電流の線形変動は、負荷抵抗器112の両端間の電圧降下に反映され、その結果、出力電圧、すなわち $V_{dd} - I_{ds104} R_L$ に反映される。 $V_{AGC}$ は、デバイス104のゲート電圧を高くすると、デバイス102のゲート電圧が低くなり、したがって、デバイス108を通る電流が一定になり、106における電圧が一定になるように印加される差動電圧である。したがって、デバイス104および102は電流を出力と電源のいずれかに向ける。 $V_{AGC}$ を高くし、すなわち、 $V_{dd}$ に近い値に設定すると、FET104において $V_{ds}$ の出力電圧スイングが小さくなり、それによって増幅器の線形範囲が狭くなり、その結果、増幅器線形性が得られる。これに対して、小信号用途で $V_{AGC}$ を低くすると、増幅器の動作点が高くなり、 $V_{out}$ が $V_{dd}$ に近い値にバイアスされ、FET102および104のゲート・ドレーン電位が高くなる。 $V_{dd}$ が十分に高い場合、ゲート・ドレーン電位は、デバイスの破滅的な故障が起こるほど高くなる可能性がある。

10

## 【0017】

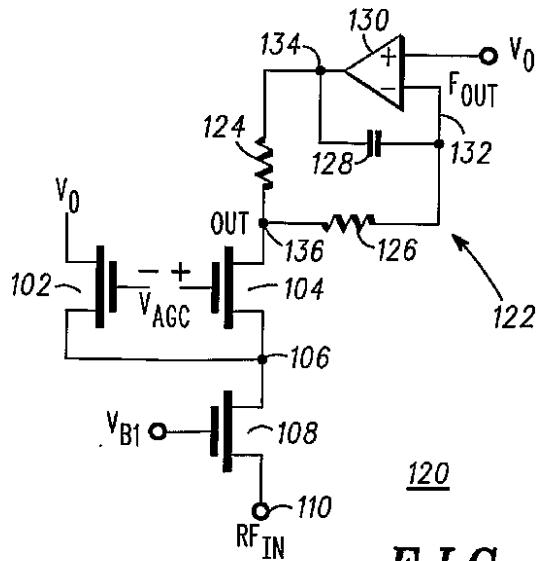

図2は、自動バイアス供給源調節機構を有する高利得広帯域幅増幅器120の好ましい実施形態の概略図である。能動負荷122は、増幅器出力のDCバイアス・シフトに応答して能動的に調整される負荷供給を与える。増幅器120は、共通ソース接続106に接続され、かつ増幅器FET108のドレーンに接続された一対の差動電界トランジスタ(FET)102、104を含んでいる。共通ソース接続106と増幅器信号入力RFINとの間に増幅器FET108が接続されている。バイアス・デバイス108のゲートにバイアス電圧( $V_{B1}$ )が印加され、差動FET対102、104のゲートに自動利得制御電圧( $V_{AGC}$ )が差動的に印加される。

20

## 【0018】

能動負荷122は、抵抗器124、126、キャパシタ128、および差動増幅器130を含み、自動バイアス供給源を形成する。キャパシタ128は、差動増幅器130の負入力132と差動増幅器130の出力134との間に接続されている。正入力に負荷基準電圧VOが与えられる。差動増幅器130の出力134とFET104のドレーンの所の高利得広帯域増幅器出力136との間に抵抗器124が接続されている。出力136におけるFET104のドレーンの所の出力と差動増幅器130の負入力132との間に抵抗器126が接続されており、増幅器負荷フィードバックを与える。

30

## 【0019】

差動増幅器130は、出力136の所のバイアス・シフトに応答して抵抗器124に負荷電流を供給し、差動増幅器120の出力136の所のDC電圧を基準電圧VOに等しいレベルに維持し、すなわち、 $V_{FOUT} = VO$ にする。抵抗器126とキャパシタ128は、FOUTの所の無線周波数(RF)信号( $V_{FOUT}$ )を補償し、補償されたDCバイアス成分を出力136に送る積分抵抗器を形成している。入力信号がないとき、 $V_{out}$ はVOであり、すなわち、 $V_{out} = V_{FOUT} = VO$ であり、したがって、出力DC成分はVOである。入力RFINに信号が印加されると、DC成分は、たとえば信号デューティ・サイクルによってシフトする可能性がある。増幅器130は、負荷抵抗器124の駆動を増大/低下させるあらゆるそのようなシフトを補償し、DC出力成分をVOに維持する。したがって、能動負荷122は、信号によって起こるあらゆるそのようなシフトを補償するように増幅器120バイアス点を自動で調整する。

40

## 【0020】

有利なことに、無線周波数(RF)集積回路チップ上の能動負荷122の自動バイアス供給源調節機構を有する高利得広帯域幅増幅器120を含めることにより、能動負荷は、RF増幅器のオンチップ電圧を調節することによって増幅器出力DC動作点を調整する。増幅器出力の静止電圧成分またはDC電圧成分は、高利得広帯域増幅器120の利得設定にかかわらずVOに維持される。したがって、出力信号範囲全体にわたって増幅器線形性

50

を維持しつつ増幅器の動作範囲および利得を増大させることができる。

**【0021】**

したがって、本発明の高利得広帯域増幅器120は、予想される動作範囲にわたって帯域幅および線形性を最大にする。さらに、能動負荷122は、集積回路チップ上のRF増幅器用の負荷として用いられる際に、追加的なチップ面積をほとんど使用せず、したがって、RF増幅器回路のコストを上げることはない。したがって、本発明の広帯域RF増幅器は、高周波数、すなわちRFで利得が低くなるというすでに経験されている問題の低コスト解決策である。

**【0022】**

本発明を好ましい実施形態について説明したが、当業者には、本発明を添付の特許請求の範囲の趣旨および範囲内で修正して実施し得ることが認識されよう。 10

**【図面の簡単な説明】**

**【0023】**

【図1】負荷抵抗器による受動負荷を有する代表的な従来技術の広帯域増幅器を示す図。

【図2】自動バイアス供給源調節機構を有する高利得広帯域幅増幅器の好ましい実施形態の概略図。

**【図1】**

**【図2】**

**FIG. 2**

---

フロントページの続き

(72)発明者 ホーレンベック、ニール ダブリュ .

アメリカ合衆国 60067 イリノイ州 パラタイン エッジウォーター レーン 1606

審査官 儀同 孝信

(56)参考文献 特開平09-064651(JP,A)

特開平08-065056(JP,A)

実用新案登録第2542311(JP,Y2)

特開平07-022858(JP,A)

特開平04-278611(JP,A)

実開平03-053020(JP,U)

実開平05-065112(JP,U)

特表平08-501197(JP,A)

特開平11-195937(JP,A)

国際公開第00/070756(WO,A1)

特開平09-284062(JP,A)

特開平04-120906(JP,A)

特開昭55-133115(JP,A)

米国特許第06316996(US,B1)

(58)調査した分野(Int.Cl., DB名)

H03F 1/00- 3/45、 3/50- 3/52、

3/62- 3/64、 3/68- 3/72、

H03G 1/00- 3/34