(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6237570号

(P6237570)

(45) 発行日 平成29年11月29日(2017.11.29)

(24) 登録日 平成29年11月10日(2017.11.10)

(51) Int.Cl.

F 1

|      |        |           |

|------|--------|-----------|

| HO2M | 1/08   | (2006.01) |

| HO3K | 17/04  | (2006.01) |

| HO1L | 21/336 | (2006.01) |

| HO1L | 29/78  | (2006.01) |

|      |       |      |

|------|-------|------|

| HO2M | 1/08  | A    |

| HO3K | 17/04 | Z    |

| HO1L | 29/78 | 301D |

| HO1L | 29/78 | 652F |

| HO1L | 29/78 | 657F |

請求項の数 6 (全 16 頁) 最終頁に続く

(21) 出願番号

特願2014-219348 (P2014-219348)

(22) 出願日

平成26年10月28日 (2014.10.28)

(65) 公開番号

特開2015-195700 (P2015-195700A)

(43) 公開日

平成27年11月5日 (2015.11.5)

審査請求日 平成29年2月23日 (2017.2.23)

(31) 優先権主張番号

特願2014-66595 (P2014-66595)

(32) 優先日

平成26年3月27日 (2014.3.27)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 100106149

弁理士 矢作 和行

(74) 代理人 100121991

弁理士 野々部 泰平

(74) 代理人 100145595

弁理士 久保 貴則

(72) 発明者 赤間 貞洋

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

(72) 発明者 山本 聖

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

最終頁に続く

(54) 【発明の名称】 駆動装置

## (57) 【特許請求の範囲】

## 【請求項 1】

パワースイッチング素子(200)のオンオフを制御する駆動装置であって、前記パワースイッチング素子のオン動作を行うオン側回路(110)と、前記パワースイッチング素子のオフ動作を行うオフ側回路(120)と、を備え、前記オン側回路および前記オフ側回路の少なくとも一方の回路は、出力トランジスタとしての複数のメインMOSトランジスタ(Tr10～Tr15, Tr50～Tr55)と、

複数の前記メインMOSトランジスタとゲートが共通し、複数の前記メインMOSトランジスタに対してカレントミラーを構成することによって、前記メインMOSトランジスタのドレイン電流を規定するセンスMOSトランジスタ(Tr20, Tr60)と、

前記センスMOSトランジスタのドレイン電流を一定に制御するセンス電流制御回路(SC)と、を有し、

さらに、前記オン側回路および前記オフ側回路の少なくとも一方の回路は、

前記メインMOSトランジスタのゲートに接続され、前記メインMOSトランジスタのオンオフを制御することにより前記パワースイッチング素子におけるゲート電流を切り替える複数のスイッチ回路(SW)を有し、

前記スイッチ回路のそれぞれは、対応する前記メインMOSトランジスタのゲートに接続されることを特徴とする駆動装置。

## 【請求項 2】

10

20

前記センス電流制御回路は、

参照電位 ( $V_{ref}$ ) を発生させる参照電源 (113, 123) と、

前記センスMOSトランジスタに直列接続された基準抵抗 (112, 122) と、

前記基準抵抗と前記センスMOSトランジスタとの間の電位が前記参照電位に近づくように前記センスMOSトランジスタのゲートに出力を発生させるオペアンプ (111, 121) と、を有して、

前記センスMOSトランジスタのドレイン電流として前記基準抵抗の抵抗値と前記参照電位とによって決まる電流を流すように構成されることを特徴とする請求項1に記載の駆動装置。

#### 【請求項3】

10

前記センス電流制御回路は、

前記センスMOSトランジスタのゲートに出力を発生させるオペアンプ (161) と、

所定の電流を前記オペアンプの一方の入力端子に供給する電流源 (P2) と、

前記オペアンプに対して前記電流源と感温素子 (164) とが並列に接続され、

温度に依存する前記感温素子の電圧降下に基づいて、前記センスMOSトランジスタのドレイン電流を変化させるように構成されることを特徴とする請求項1に記載の駆動装置。

#### 【請求項4】

20

前記メインMOSトランジスタおよび前記センスMOSトランジスタを構成する単位MOSトランジスタ (Tr16) は、チャネル長 (L) およびチャネル幅 (W) がすべて同一に構成されることを特徴とする請求項1～3のいずれか1項に記載の駆動装置。

#### 【請求項5】

前記メインMOSトランジスタおよび前記センスMOSトランジスタを構成する単位MOSトランジスタは、隣接する素子との間にトレンチ (400) を有して素子分離されるLDMOSにより構成され、

前記トレンチは、隣り合う素子において互いに共有されるように形成されることを特徴とする請求項4に記載の駆動装置。

#### 【請求項6】

30

前記パワースイッチング素子のコレクタ電流を検出する電流検出部 (150) を備え、

前記電流検出部は、前記パワースイッチング素子のコレクタ電流が所定の閾値を超える場合において、前記パワースイッチング素子のコレクタ電流が所定の閾値を超えない場合に較べて前記センスMOSトランジスタのゲート電圧を小さく設定することを特徴とする請求項1～5のいずれか1項に記載の駆動装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、パワースイッチング素子のオンオフ動作を行う駆動装置に関する。

##### 【背景技術】

##### 【0002】

インバータやコンバータ等の半導体電力変換装置を構成するパワースイッチング素子について、スイッチング動作時のサージ電圧とスイッチング損失とのトレードオフを解消する技術として、ゲート電圧あるいはゲート電流を動的に制御するアクティブゲートコントロール (AGC) が用いられている。

##### 【0003】

例えば、パワースイッチング素子として絶縁ゲートバイポーラトランジスタ (IGBT) を用いる場合、ターンオフ時のコレクタ - エミッタ間電圧 (以降、コレクタ電圧  $V_{ce}$  という) の時間変化  $dV/dt$  をフィードバックして、IGBTのゲート電荷の放電速度を制御する。具体的には、特許文献1において、IGBTのゲートに注入するゲート電流の電流量を切り替えることによって、ゲート電荷の放電速度を、放電の途中で切り替える技術が提案されている。しかしながら、特許文献1の技術は、切り替え段数に対応する数

40

50

のゲートオフ回路が必要となるため、回路規模、すなわちレイアウト面積が大きくなってしまう。

#### 【0004】

一方、特許文献2では、広い出力電流を有する、換言すれば、出力電流を幅広く切り替えることのできる半導体装置において、レイアウト面積を抑えることのできる回路が提案されている。具体的には、この半導体装置は、出力電流をリファレンス電流のカレントミラーによって生成する。そして、カレントミラーを多段とすることによって、出力電流の広いダイナミックレンジを実現している。

#### 【先行技術文献】

##### 【特許文献】

10

##### 【0005】

##### 【特許文献1】特許第3885563号公報

##### 【特許文献2】特開2006-20098号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0006】

しかしながら、特許文献2の技術は、出力トランジスタをオンするためのゲートへの電流供給をリファレンス電流によって行うため、カレントミラーを構成する出力トランジスタの段数が増加するほどリファレンス電流が変化してしまう。すなわち、出力トランジスタをオンするごとに出力電流が変動してしまう。

20

##### 【0007】

また、特許文献2のような回路構成では、一般に、リファレンス電流をできるだけ小さくすることが望ましいが、カレントミラーを構成する出力トランジスタのゲートへの電荷の注入速度がリファレンス電流に依存するため、リファレンス電流が小さいと出力トランジスタがオンするまでの時間が長くなってしまう。つまり、特許文献2の技術をパワースイッチング素子のオフ用回路に適用する場合、パワースイッチング素子をオフする旨の指示を受けてから出力トランジスタがオンするまでの応答速度が確保できない虞がある。

20

##### 【0008】

本発明は、上記問題点を鑑みてなされたものであり、ゲート電流を高精度で制御しつつ、ゲート電流の切り替え速度の高速化することを目的とする。

30

#### 【課題を解決するための手段】

##### 【0009】

ここに開示される発明は、上記目的を達成するために以下の技術的手段を採用する。なお、特許請求の範囲およびこの項に記載した括弧内の符号は、ひとつの態様として後述する実施形態に記載の具体的手段との対応関係を示すものであって、発明の技術的範囲を限定するものではない。

##### 【0010】

上記目的を達成するために、本発明は、パワースイッチング素子(200)のオンオフを制御する駆動装置であって、パワースイッチング素子のオン動作を行うオン側回路(110)と、パワースイッチング素子のオフ動作を行うオフ側回路(120)と、を備え、オン側回路およびオフ側回路の少なくとも一方の回路は、出力トランジスタとしての複数のメインMOSトランジスタ( $T_{r10} \sim T_{r15}$ ,  $T_{r50} \sim T_{r55}$ )と、複数のメインMOSトランジスタとゲートが共通し、複数のメインMOSトランジスタに対してカレントミラーを構成することによって、メインMOSトランジスタのドレイン電流を規定するセンスMOSトランジスタ( $T_{r20}$ ,  $T_{r60}$ )と、センスMOSトランジスタのドレイン電流を一定に制御するセンス電流制御回路(SC)と、を有し、さらに、オン側回路およびオフ側回路の少なくとも一方の回路は、メインMOSトランジスタのゲートに接続され、メインMOSトランジスタのオンオフを制御することによりパワースイッチング素子におけるゲート電流を切り替える複数のスイッチ回路(SW)を有し、各々のスイッチ回路は、それぞれが対応するメインMOSトランジスタのゲートに接続されることを

40

50

特徴としている。

**【0011】**

これによれば、センスMOSトランジスタとカレントミラーを構成するメインMOSトランジスタが複数形成され、これらの有効／無効がスイッチ回路のオンオフ制御によって制御されている。このため、有効とされるメインMOSトランジスタの数を切り替えることによって、出力電流を切り替えることができる。

**【0012】**

また、カレントミラーによってメインMOSトランジスタのドレン電流を規定するセンスMOSトランジスタのドレン電流が、参照電位と基準抵抗の抵抗値によって規定される。このため、本発明に係る駆動装置に電力を供給する電源電圧や、オフ側回路の出力電流の電流値に依らず、出力電流を高精度に制御することができる。さらに、センスMOSトランジスタのドレン電流はスイッチ回路のオンオフに依らず一定であるから、有効とされるメインMOSトランジスタの数に依らず、出力電流を高精度に制御することができる。

10

**【0013】**

また、出力トランジスタとしてのメインMOSトランジスタを駆動させるためのゲートへの電圧印加がオペアンプの出力によって制御されるため、リファレンス電流によって制御される場合に較べて、スイッチング速度を高速化することができる。

**【図面の簡単な説明】**

**【0014】**

20

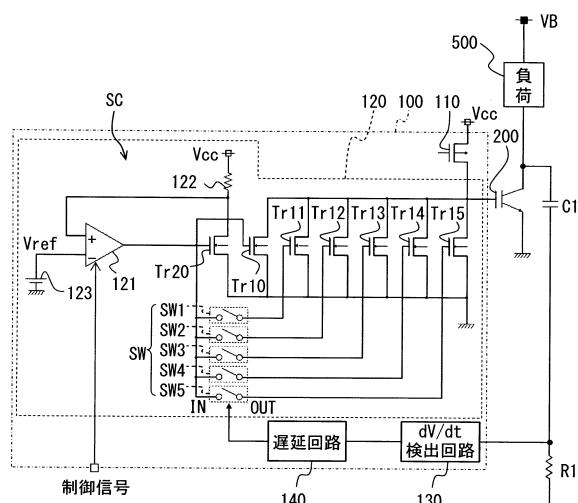

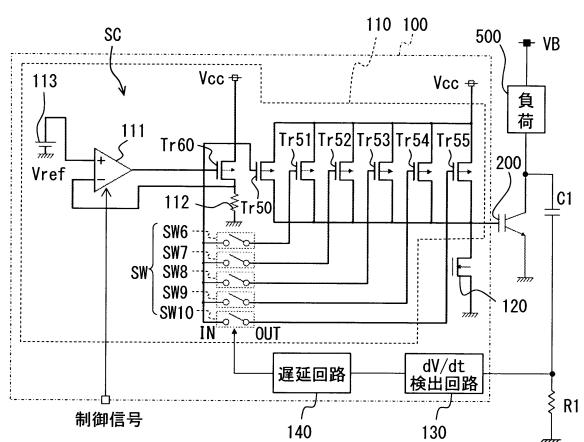

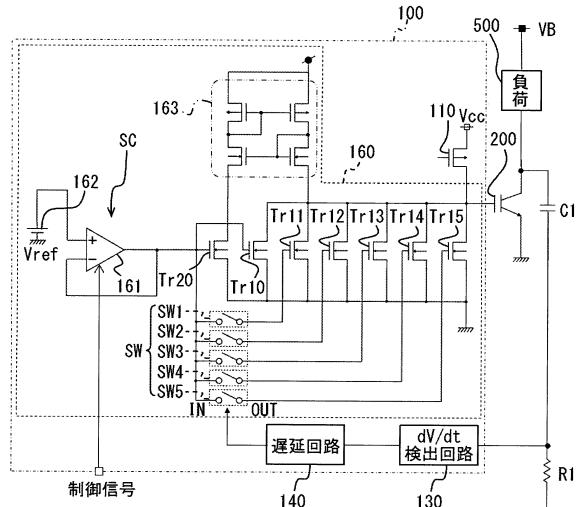

【図1】第1実施形態に係る駆動装置の概略構成を示す回路図である。

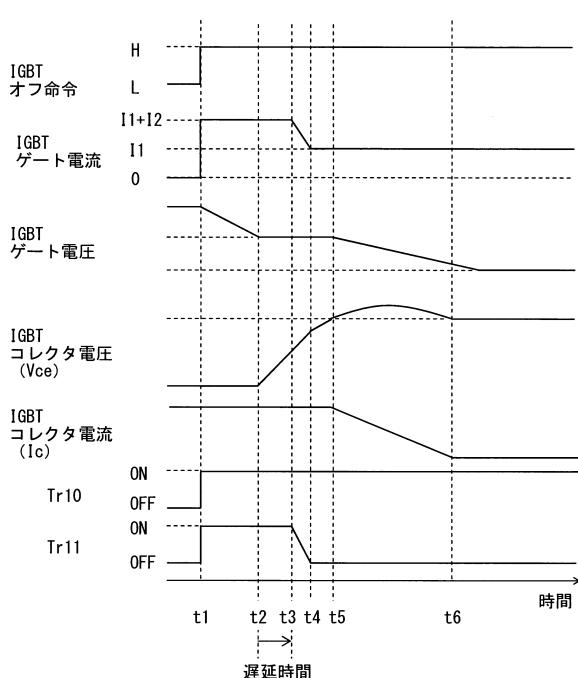

【図2】駆動装置による駆動を示すタイミングチャートである。

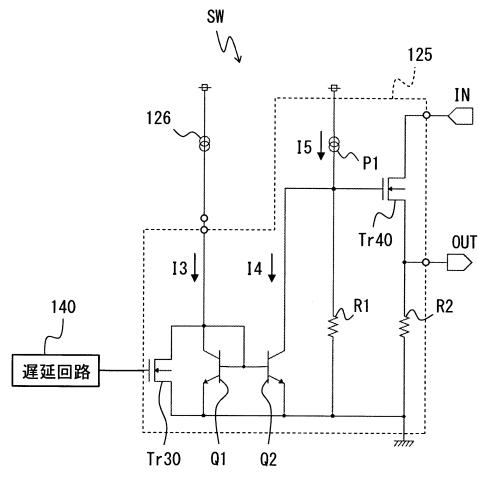

【図3】スイッチ回路の詳細な構成を示す回路図である。

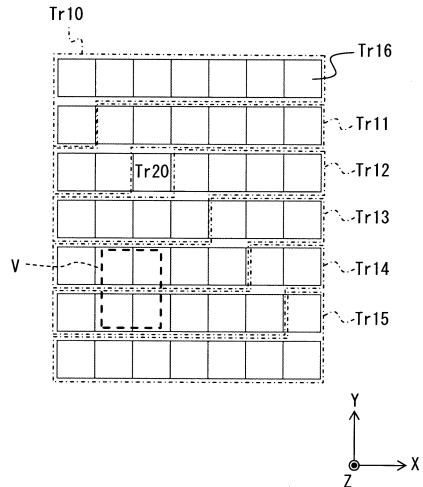

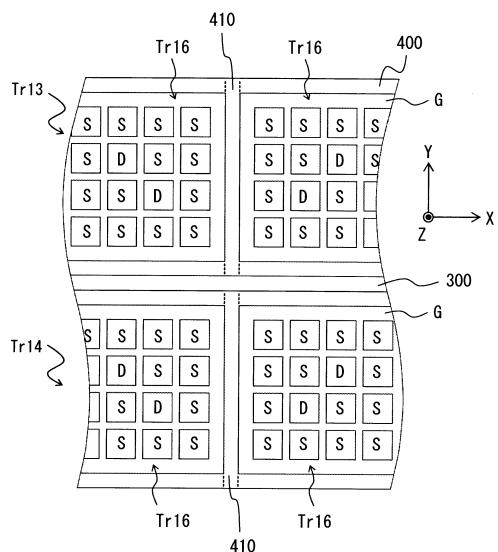

【図4】NMOSトランジスタのレイアウトを示す上面図である。

【図5】図4に示す領域Vの拡大図である。

【図6】変形例1に係る駆動装置の概略構成を示す回路図である。

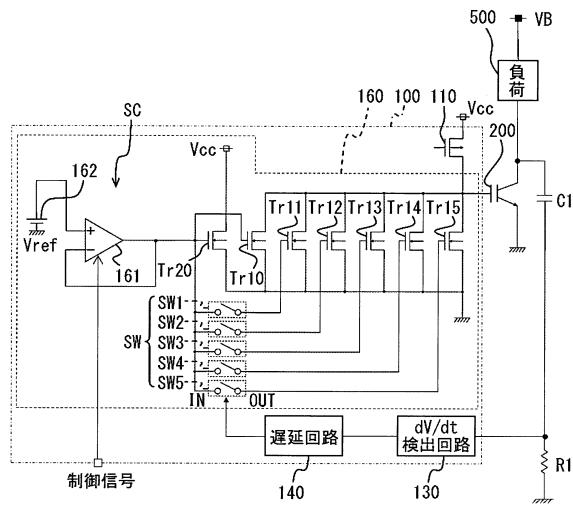

【図7】第2実施形態に係る駆動装置の概略構成を示す回路図である。

【図8】第3実施形態に係る駆動装置の概略構成を示す回路図である。

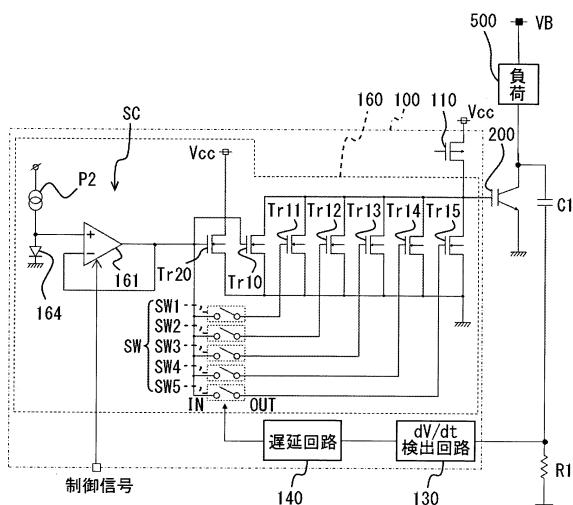

【図9】変形例2に係る駆動装置の概略構成を示す回路図である。

【図10】変形例3に係る駆動装置の概略構成を示す回路図である。

30

**【発明を実施するための形態】**

**【0015】**

以下、本発明の実施の形態を図面に基づいて説明する。なお、以下の各図相互において、互いに同一もしくは均等である部分に、同一符号を付与する。

**【0016】**

(第1実施形態)

最初に、図1を参照して、本実施形態に係る駆動装置について説明する。

**【0017】**

図1に示すように、この駆動装置100は、負荷500を駆動するパワースイッティング素子としての絶縁ゲートバイポーラトランジスタ(IGBT)200の駆動を制御するものである。

40

**【0018】**

この駆動装置100は、オン側回路110と、オフ側回路120と、dV/dt検出回路130と、遅延回路140と、を備えている。

**【0019】**

オン側回路110およびオフ側回路120は電源とGNDとの間で直列に接続され、その中間点にIGBT200のゲートが接続されている。オン側回路110は、PMOSトランジスタにより構成され、このPMOSトランジスタがオン状態のときにはIGBT200のゲートに電源電圧Vccが印加される。これによりIGBT200がオン状態になり、IGBT200のコレクタ-エミッタ間に電流が流れ、負荷500に電力が供給され

50

る。

#### 【0020】

オフ側回路120は、複数のNMOSトランジスタ( $T_{r10} \sim T_{r15}, T_{r20}$ )を有している。これらNMOSトランジスタは、出力トランジスタとしてのメインMOSトランジスタ( $T_{r10} \sim T_{r15}$ )と、メインMOSトランジスタのドレイン電流を規定するセンスMOSトランジスタ $T_{r20}$ とから構成されている。本実施形態では、6つのメインMOSトランジスタ( $T_{r10} \sim T_{r15}$ )が、センスMOSトランジスタ $T_{r20}$ のゲートに対してカレントミラーを構成するようになっている。具体的には、各メインMOSトランジスタ( $T_{r10} \sim T_{r15}$ )のゲートはセンスMOSトランジスタ $T_{r20}$ のゲートと共に接続され、ソースが共通してGNDに接続されている。各メインMOSトランジスタ( $T_{r10} \sim T_{r15}$ )のドレインはIGBT200のゲート接続されている。10

#### 【0021】

このような構成では、各メインMOSトランジスタ( $T_{r10} \sim T_{r15}$ )には、それぞれ、センスMOSトランジスタ $T_{r20}$ のサイズ比と同一の電流比でドレイン電流が流れる。つまり、本実施形態では、IGBT200のゲートに注入する電流の電流経路が6つ存在している。なお、サイズとはMOSトランジスタにおけるチャネル幅Wとチャネル長Lのアスペクト比(W/L)である。

#### 【0022】

また、オフ側回路120は、センスMOSトランジスタ $T_{r20}$ のドレイン電流を制御するためのオペアンプ121と、該オペアンプ121の出力を規定するための基準抵抗122と、該オペアンプ121の一つの入力端子に参照電位 $V_{ref}$ を与える参照電源123と、を有している。オペアンプ121は、図示しないマイコンなどからIGBT200をオフさせることを示す制御信号が入力されると、センスMOSトランジスタ $T_{r20}$ のゲートに電圧を印加することで、IGBT200のゲートに定電流が注入されるようとする。20

#### 【0023】

基準抵抗122は、シャント抵抗であり、センスMOSトランジスタ $T_{r20}$ のドレイン電流の電流値を規定する。ひいては、IGBT200のゲートに注入される電流の電流値を規定する。IGBT200のゲートに注入される電流は、メインMOSトランジスタ( $T_{r10} \sim T_{r15}$ )に流れるドレイン電流の合計である。そして、メインMOSトランジスタ( $T_{r10} \sim T_{r15}$ )はセンスMOSトランジスタ $T_{r20}$ とともにカレントミラーを構成しているので、IGBT200のゲートに注入される電流はセンスMOSトランジスタ $T_{r20}$ のドレイン電流に依存する。30

#### 【0024】

このような構成では、IGBT200をオフさせることを示す信号が入力されると、オペアンプ121が駆動されてセンスMOSトランジスタ $T_{r20}$ にゲート電圧が印加される。このときのドレイン電流は基準抵抗122の抵抗値Rにより規定される。そして、その電流値は、基準抵抗122とセンスMOSトランジスタ $T_{r20}$ との間の中間電位が、参照電位 $V_{ref}$ に近づくように、オペアンプ121の出力が調整されることによりフィードバック制御される。これにより、センスMOSトランジスタ $T_{r20}$ のドレイン電流が高精度に一定の値( $= (V_{cc} - V_{ref}) / R$ )に制御される。よって、IGBT200のゲートに注入される電流も、高精度に一定電流とされる。なお、本実施形態において、特許請求の範囲に記載のセンス電流制御回路SCは、オペアンプ121と基準抵抗122および参照電源123とにより構成される回路に相当する。40

#### 【0025】

さらに、オフ側回路120は、IGBT200のゲートに注入される電流の電流値、すなわちドライブ能力を切り替えるためのスイッチ回路(SW1～SW5)を有している。このスイッチ回路(SW1～SW5)は、6つのメインMOSトランジスタ( $T_{r10} \sim T_{r15}$ )のうち5つのメインMOSトランジスタ( $T_{r11} \sim T_{r15}$ )のゲートにそれぞれ接続されている。例えば、スイッチ回路SW1が有効とされ、その他のスイッチ回50

路 ( SW2 ~ SW5 ) が無効の状態であれば、IGBT200のゲート電荷は、メインMOSトランジスタTr10およびTr11により規定される電流により引き抜かれる。つまり、スイッチ回路 ( SW1 ~ SW5 ) のうち、どのスイッチ回路が有効となっているかによってオフ側回路120のドライブ能力を制御することができる。なお、5つのスイッチ回路 ( SW1 ~ SW5 ) は互いに等価であり、以降、個々のスイッチ回路について述べる場合を除き、符号SWと総称する。本実施形態におけるスイッチ回路SWの詳しい回路構成は追って説明する。

#### 【0026】

駆動装置100におけるdV/dt検出回路130は、IGBT200のコレクタ電圧Vceの時間変化dV/dtを検出する回路である。具体的には、dV/dt検出回路130は、IGBT200のコレクタとGNDとの間に直列接続されて微分器を構成するコンデンサC1と抵抗器R1の中間点に接続されている。オペアンプ121にIGBT200をオフさせることを示す信号が入力されると、IGBT200のゲート電荷が引き抜かれてコレクタ電圧Vceが上昇するため、dV/dtがゼロでない値をとる。dV/dt検出回路130はこれを検出し、その旨を遅延回路140に出力する。

#### 【0027】

遅延回路140は、dV/dtが上昇を開始した時点から所定の遅延時間だけ遅れてスイッチ回路SWを動作させる回路である。5つのスイッチ回路 ( SW1 ~ SW5 ) のうち、どのスイッチ回路SWを動作させるかについては、予め決めておくこともできるし、dV/dtの値等に応じて決定されてもよい。

#### 【0028】

次に、本実施形態に係る駆動装置100における、IGBT200のゲート電荷の放電期間中の放電速度を切り替える駆動について、図2を参照して説明する。

#### 【0029】

時刻t1において、オペアンプ121にIGBT200をオフさせることを示す制御信号が入力される。これにより、図2に示すように、オペアンプ121が駆動してIGBT200のゲートに電流が注入される。この説明において、時刻t1におけるスイッチ回路SWは、SW1が有効(オン)とされ、SW2 ~ SW5は無効(オフ)であるとする。つまり、ゲートに注入される電流は、メインMOSトランジスタTr10のドレイン電流I1と、メインMOSトランジスタTr11のドレイン電流I2との合計値I1 + I2である。

#### 【0030】

IGBT200のゲートに電流が注入されて電荷の引き抜きが行われ始めると、ゲート電圧は低下していく。そして、時刻t2において、ゲート電圧が所定の電位(ミラー電圧)まで低下し一定時間が経過すると、コレクタ電圧Vceが上昇を始める。すなわち、時刻t2の時点で、dV/dtがほぼゼロの状態から、dV/dtが正の値をとる。dV/dt検出回路130はこれを検出して、その旨を遅延回路140に対して出力する。

#### 【0031】

そして、遅延回路140により予め規定された遅延時間後の時刻t3において、スイッチ回路SW1がオフされることによって、メインMOSトランジスタTr11のオフ動作が開始される。メインMOSトランジスタTr11は瞬時にオフされるのではなく、素子に規定された立ち下がり時間を要してオフ(時刻t4)に至る。このため、ゲートに注入される電流は、時刻t3から時刻t4に至る間に、I1 + I2からI1へ変化する。そして、この期間において、IGBT200のコレクタ電圧Vceの変化dV/dtは、徐々に小さくなっていく。時刻t4に至ると、メインMOSトランジスタTr11はオフ状態となり、IGBT200のゲート電流は、I1 + I2からI1に切り替わる。

#### 【0032】

このため、オフ側回路120のドライブ能力、換言すればゲート電荷の放電速度、は、時刻t3の時点に較べて時刻t4の時点のほうが小さくなる。したがって、時刻t3直前のdV/dtに比べて、時刻t4直後のdV/dtは小さくなる。その結果、コレクタ電

10

20

30

40

50

圧  $V_{ce}$  のオーバーシュートが抑制され、サージ電圧を低減する効果を発揮することができる。その後、時刻  $t_6$ において、コレクタ電圧  $V_{ce}$  が定常値に収束して IGBT200 のオフ動作は終了する。

#### 【0033】

なお、メインMOSトランジスタTr11のオフ開始のタイミング（時刻  $t_3$ ）は、メインMOSトランジスタTr11が完全にオフになる時刻  $t_4$  が、想定されるコレクタ電圧  $V_{ce}$  の定常値に至る時刻  $t_5$  よりも早い時期に設定されることが好ましい。

#### 【0034】

また、時刻  $t_6$  以降において、再びメインMOSトランジスタTr11をオンしてオフ側回路120のドライブ能力を向上させることによって、IGBT200の確実なオフを保証するように構成しても良い。10

#### 【0035】

次に、図3を参照して、本実施形態におけるスイッチ回路SWの具体的な構成について説明する。なお、図3に示す回路は、各スイッチ回路（SW1～SW5）いずれも同一の構成である。

#### 【0036】

スイッチ回路SWは、主回路125と、主回路125に一定の電流  $I_3$  を供給する定電流回路126とを有している。

#### 【0037】

主回路125は、遅延回路140からの信号に基づいて入力端子INと出力端子OUTの間ににおける電流の通電および遮断を担っている。主回路125は、図3に示すように、遅延回路140からの信号によりオンオフ動作するMOSトランジスタTr30を有している。また、定電流回路126に対して、MOSトランジスタTr30と並列に接続され、定電流回路126から入力される電流  $I_3$  をミラーするようにカレントミラーを構成する2つのNPNトランジスタQ1, Q2を有している。また、ゲートに注入される電流に基づいて入力端子INと出力端子OUTの間ににおける電流の通電および遮断を行うMOSトランジスタTr40を有している。さらに、スイッチ回路SWをオン状態とする場合にMOSトランジスタTr40のゲートに電流を注入する電流源P1を有している。なお、本実施形態では、図3に示す入力端子INがオペアンプ121の出力端子に接続されており、出力端子OUTがメインMOSトランジスタ（Tr11～Tr15）のゲートに接続されている。2030

#### 【0038】

主回路125の動作について説明する。スイッチ回路SWをオン状態とする場合、遅延回路からMOSトランジスタTr30をオン状態とする旨の信号が入力される。この状態では、定電流回路126から供給される電流  $I_3$  は、MOSトランジスタTr30のドレンイン電流として流れ、カレントミラーを成すNPNトランジスタQ1, Q2に電流が流れない。すなわち、図3に示す電流  $I_4$  は流れない。このため、電流源P1からの電流  $I_5$  がMOSトランジスタTr40のゲートに注入されてオンとなり、入力端子INと出力端子OUTの間が通電される。すなわち、スイッチ回路SWがオン状態となる。なお、電流源P1とGNDとの間に挿入された抵抗器R1は、MOSトランジスタTr40の定常状態におけるゲート電圧を規定するための抵抗である。40

#### 【0039】

一方、スイッチ回路SWをオフ状態とする場合、遅延回路からMOSトランジスタTr30をオフ状態とする旨の信号が入力される。この状態では、MOSトランジスタTr30のドレンイン電流は流れず、定電流回路126から主回路125に入力される電流  $I_3$  は、NPNトランジスタQ1, Q2によりミラーされて図3に示す電流  $I_4$  が流れる。この電流  $I_4$  は、電流源P1による電流  $I_5$  およびMOSトランジスタTr40のゲート電荷を引き抜くように流れるため、MOSトランジスタTr40がオフする。よって、入力端子INと出力端子OUTの間の電流が遮断されてスイッチ回路SWがオフ状態となる。なお、スイッチ回路SWがオフすると、対応するメインMOSトランジスタのゲートがハイ50

インピーダンスとなる。本実施形態におけるスイッチ回路SWは、スイッチ回路SWのオフ動作を確実にするため、出力端子OUTとGNDとの間にプルダウン抵抗器R2が挿入されている。

#### 【0040】

前述の定電流回路126は、主回路125に一定の電流I3を供給するための回路である。この定電流回路126は、一定の電流を与えるため的一般的に知られた回路を採用することができるため、回路の詳細な説明を割愛する。

#### 【0041】

次に、図4および図5を参照して、センスMOSトランジスタTr20およびメインMOSトランジスタ(Tr10～Tr15)のレイアウトについて説明する。便宜上、図4に示すように、X方向と、X方向に直交するY方向と、X方向とY方向により規定されるXY平面に直交するZ方向を定義する。これらNMOSトランジスタは半導体基板300の表層において、XY平面に沿って形成されている。10

#### 【0042】

図4に示すように、メインMOSトランジスタTr10～Tr15およびセンスMOSトランジスタTr20を構成するNMOSトランジスタは、X方向およびY方向に沿って、単位MOSトランジスタTr16が $7 \times 7$ の格子状に並んで形成されたLD MOS(横方向拡散MOS)である。本実施形態では、49個の単位MOSトランジスタTr16のうち、1個がセンスMOSトランジスタTr20に相当し、残りの48個がメインMOSトランジスタ(Tr10～Tr15)に相当する。なお、図4に示すように、メインMOSトランジスタ(Tr10～Tr15)は、それぞれ8個の単位MOSトランジスタTr16から構成されている。20

#### 【0043】

これらNMOSトランジスタのレイアウトについてより詳しく説明する。図5は図4に示す領域Vを拡大した図である。図5に示すように、各単位MOSトランジスタTr16には、それぞれ複数のソース領域Sとドレイン領域Dが格子状に形成されている。本実施形態では、 $4 \times 4$ で1つのセルを形成している。そして、1つのセルを形成するソース領域Sおよびドレイン領域Dを取り囲むように、ゲート領域Gが形成されている。このゲート領域Gと、 $4 \times 4$ の格子を成すソース領域Sおよびドレイン領域Dと、により一つの単位MOSトランジスタTr16を構成している。なお、センスMOSトランジスタTr20、メインMOSトランジスタ(Tr10～Tr15)は、すべて同一の単位MOSトランジスタTr16から構成されている。30

#### 【0044】

さらに、図5に示すように、単位MOSトランジスタTr16は、互いに電気的に素子分離するためのトレチ400を有している。トレチ400は、半導体基板300の表層からZ方向に沿って形成されるとともに、各単位MOSトランジスタTr16をそれぞれ取り囲んで形成されている。換言すれば、トレチ400は、各単位MOSトランジスタTr16におけるゲート領域Gを取り囲むように、枠状に形成されている。そして、本実施形態では、隣り合うNMOSトランジスタ、例えば、X方向において隣り合う単位MOSトランジスタTr16の間に形成されたトレチ400の一辺410が、双方のトレチ400を共有している。なお、本実施形態では、Y方向において隣り合う単位MOSトランジスタTr16の間のトレチ400の一辺は共有されていない。40

#### 【0045】

また、図5に示すように、本実施形態における各単位MOSトランジスタTr16は、ソース領域Sやドレイン領域Dの一部配置を除き、ソース領域Sの形状および面積、ドレイン領域Dの形状および面積、ゲート領域Gの形状および面積が、互いに等価に形成されている。すなわち、メインMOSトランジスタ(Tr10～Tr15)およびセンスMOSトランジスタTr20を構成する単位MOSトランジスタTr16は、チャネル長Lとチャネル幅Wがすべて同一に形成されている。

#### 【0046】

50

次に、本実施形態に係る駆動装置100の作用効果について説明する。

#### 【0047】

図1に示すように、センスMOSトランジスタTr20とカレントミラーを構成するメインMOSトランジスタ(Tr10～Tr15)が複数形成され、これらの有効／無効がスイッチ回路SWのオンオフ制御によって制御されている。このため、有効とされるメインMOSトランジスタ(Tr10～Tr15)の数を切り替えることによって、出力電流を切り替えることができる。

#### 【0048】

また、カレントミラーによってメインMOSトランジスタ(Tr10～Tr15)のドレイン電流を規定するセンスMOSトランジスタTr20のドレイン電流が、参照電位V<sub>ref</sub>と基準抵抗122の抵抗値Rによって規定される。このため、本発明に係る駆動装置100に電力を供給する電源電圧V<sub>cc</sub>や、オフ側回路120の出力電流の電流値に依らず、出力電流を高精度に制御することができる。さらに、センスMOSトランジスタTr20のドレイン電流は、スイッチ回路SWのオンオフに依らず一定であるから、有効とされるメインMOSトランジスタ(Tr10～Tr15)の数に依らず、出力電流を高精度に制御することができる。

#### 【0049】

また、出力トランジスタとしてのメインMOSトランジスタ(Tr10～Tr15)を駆動させるためのゲートへの電圧印加がオペアンプ121の出力によって制御されるため、リファレンス電流によって制御される場合に較べて、スイッチング速度を高速化することができる。

#### 【0050】

さらには、センスMOSトランジスタTr20のドレイン電流が、参照電位V<sub>ref</sub>と基準抵抗122の抵抗値Rによって規定されるため、センスMOSトランジスタTr20のドレイン-ソース間電圧V<sub>ds</sub>を閾値電圧(いわゆるV<sub>th</sub>)よりも十分大きく保つことができる。これにより、基準抵抗122の抵抗値Rを小さくできるから、基準抵抗122となる抵抗器をディスクリート部品として別途用意することなく、メインMOSトランジスタ(Tr10～Tr15)やセンスMOSトランジスタTr20と同一の半導体基板300上に集積化することができる。

#### 【0051】

さらに、図5に示すように、各NMOSトランジスタ(Tr20, Tr10～Tr15)を構成する単位MOSトランジスタTr16を互いに素子分離するトレンチ400が、隣り合う単位MOSトランジスタTr16の間で一部共有化されている。本実施形態においては、X方向に隣り合う単位MOSトランジスタTr16において、柵状のトレンチ400の一辺410が共有化されている。したがって、トレンチ400が共有化されない構成に較べて、X方向のレイアウト面積を小さくすることができる。

#### 【0052】

また、図5に示すように、メインMOSトランジスタ(Tr10～Tr15)およびセンスMOSトランジスタTr20は、それらを構成する単位MOSトランジスタTr16チャネル長Lとチャネル幅Wがすべて同一に形成されている。各単位MOSトランジスタTr16がすべて等価に形成されているから、駆動装置100の製造が容易になり、ゲートに印加される電圧に対するドレイン電流の特性も均一化することができる。また、図4に示すように、単位MOSトランジスタTr16を格子状に配置することができるため、半導体基板300の表層面積に対するNMOSトランジスタの占める割合を小さくすることができる。すなわち、レイアウト面積を小さくすることができる。

#### 【0053】

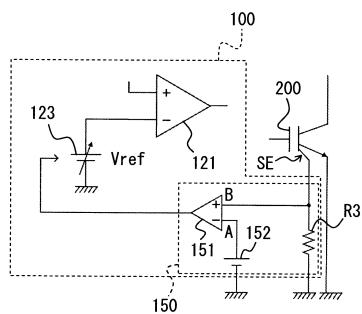

##### (変形例1)

上記した実施形態における構成に加えて、本変形例では、図6に示すように、駆動装置100が電流検出部150を備えている。また、参照電源123は参照電位V<sub>ref</sub>が可変になっている。なお、図6では、オン側回路110、各NMOSトランジスタ(Tr1

10

20

30

40

50

0 ~ Tr15, Tr20)、スイッチ回路SW、基準抵抗122、dV/dt検出回路130および遅延回路140の図示を省略している。

#### 【0054】

電流検出部150はIGBT200のコレクタ電流を検出して、過電流から保護する回路である。この電流検出部150は、コンパレータ151と、コンパレータ151の一方の入力端子に閾値となる電圧を与える電圧源152と、IGBT200のコレクタ電流を電圧に変換するための抵抗器R3とを有している。

#### 【0055】

前述のように、コンパレータ151の一方の入力端子Aには電圧源152が接続されている。そして、他方の入力端子Bは、IGBT200のセンスエミッタ端子SEとGNDとの間に接続された抵抗器R3との中間点に接続されている。すなわち、コンパレータ151における入力端子Bには、IGBT200のセンスエミッタ端子SEからGNDに向かって流れる電流と抵抗器R3の抵抗値に対応した電圧が印加されている。入力端子Bに印加される電圧は、センスエミッタ端子SEからGNDに向かって流れる電流に比例する。つまり、この電圧はIGBT200のコレクタ電流が大きくなるほど高電圧となる。

#### 【0056】

コンパレータ151は、センスエミッタ端子SEを流れる電流に対応した電圧が、電圧源152の電圧を超えた場合、すなわち、コレクタ電流が所定の閾値を超えた場合に、参照電源123に対して、参照電位Vrefを大きくするように制御する。

#### 【0057】

これによれば、IGBT200に過度のコレクタ電流(過電流)が流れている場合に、参照電位Vrefが大きくされることによって、センスMOSトランジスタTr20のドレイン電流が小さくなる。このため、オフ側回路120のドライブ能力が抑制され、IGBT200を緩やかにオフすることができる。したがって、過電流発生時において、サーボ電圧を抑制することができ、IGBT200を保護することができる。

#### 【0058】

##### (第2実施形態)

上記した実施形態では、オフ側回路120において、IGBT200の温度に基づく制御を可能にした例について示したが、これはオン側回路110についても適用することができる。

#### 【0059】

具体的には、図7に示すように、オン側回路110は、複数のPMOSトランジスタ(Tr50 ~ Tr55, Tr60)を有している。これらPMOSトランジスタは、出力トランジスタとしてのメインMOSトランジスタ(Tr50 ~ Tr55)と、メインMOSトランジスタのドレイン電流を規定するセンスMOSトランジスタTr60とから構成されている。本実施形態では、6つのメインMOSトランジスタ(Tr50 ~ Tr55)が、センスMOSトランジスタTr60に対してカレントミラーを構成するようになっている。具体的には、各メインMOSトランジスタ(Tr50 ~ Tr55)のゲートはセンスMOSトランジスタTr60のゲートと共に接続され、ドレインが共通して電源Vccに接続されている。各メインMOSトランジスタ(Tr50 ~ Tr55)のソースはIGBT200のゲート接続されている。

#### 【0060】

また、オン側回路110は、センスMOSトランジスタTr60のドレイン電流を制御するためのオペアンプ111と、該オペアンプ111の出力を規定するための基準抵抗112と、該オペアンプ111の一つの入力端子に参照電位Vrefを与える参照電源113と、を有している。オペアンプ111は、図示しないマイコンなどからIGBT200をオンさせることを示す制御信号が入力されると、センスMOSトランジスタTr60のゲートに電圧を印加することで、IGBT200のゲートへ定電流が供給されるようになる。

#### 【0061】

10

20

30

40

50

さらに、オン側回路 110 は、IGBT 200 のゲートへ供給される電流の電流値、すなわちドライブ能力を切り替えるためのスイッチ回路 (SW6～SW10) を有している。このスイッチ回路 (SW6～SW10) は、6 つのメインMOSトランジスタ (Tr50～Tr55) のうち 5 つのメインMOSトランジスタ (Tr51～Tr55) のゲートにそれぞれ接続されている。これらスイッチ回路 (SW6～SW10) は、第 1 実施形態に記載のスイッチ回路 SW と等価であり、その回路構成は、図 3 に示す回路構成を採用することができる。

#### 【0062】

本実施形態における構成要素である、メインMOSトランジスタ (Tr50～Tr55) 、センスMOSトランジスタ Tr60 、オペアンプ 111 、基準抵抗 112 、参照電源 113 、およびスイッチ回路 (SW6～SW10) は、それぞれ、第 1 実施形態におけるメインMOSトランジスタ (Tr10～Tr15) 、センスMOSトランジスタ Tr20 、オペアンプ 121 、基準抵抗 122 、参照電源 123 、およびスイッチ回路 (SW1～SW5) に相当する要素である。よって、各構成要素の動作および作用効果は、第 1 実施形態およびその変形例に準じるものである。すなわち、オン側回路 110 の出力電流を高精度に制御することができ、また、リファレンス電流によって制御される場合に較べて、スイッチング速度を高速化することができる。

#### 【0063】

なお、本実施形態における参照電位 Vref は、第 1 実施形態における参照電位 Vref と必ずしも一致している必要はない。

#### 【0064】

##### (第 3 実施形態)

センス電流制御回路 SC は、オペアンプ 111, 121 と基準抵抗 112, 122 および参照電源 113, 123 とにより構成される回路に限定されない。

#### 【0065】

上記した各実施形態におけるセンス電流制御回路 SC では、基準抵抗 112, 122 の抵抗値 R と参照電源 113, 123 の参照電位 Vref とによって規定される電流値になるようにフィードバック制御されるよう構成されていた。これに対して、本実施形態におけるセンス電流制御回路 SC は、フィードバック制御を行わない構成となっている。

#### 【0066】

具体的には、本実施形態におけるオフ側回路 160 のセンス電流制御回路 SC は、図 8 に示すように、センスMOSトランジスタ Tr20 のゲートに出力端子が接続されたオペアンプ 161 と、オペアンプ 161 の一方の入力端子に所定の電圧を印加する参照電源 162 と、を有している。他方の入力端子には、オペアンプ 161 の出力が負帰還されており、参照電源 162 により規定される電圧がセンスMOSトランジスタ Tr20 に印加されるようになっている。このような構成であっても、有効とされるメインMOSトランジスタ (Tr10～Tr15) の数を切り替えることによって、出力電流を切り替えることができる。なお、本実施形態に較べて第 1 および第 2 実施形態のようなセンス電流制御回路 SC を採用したほうが、センスMOSトランジスタ Tr20 のドレイン電流を高精度に維持できるが、高精度を要しない負荷 500 を駆動する場合には本実施形態に係るセンス電流制御回路 SC を採用することによって部品点数や製造コストを低減することができる。

#### 【0067】

##### (変形例 2 )

第 3 実施形態におけるセンス電流制御回路 SC の、センスMOSトランジスタ Tr20 およびメインMOSトランジスタ (Tr10～Tr15) へ供給するゲート電流を高精度に制御するために、図 9 に示すように、Vds 調整回路 163 を採用することができる。

#### 【0068】

本変形例における Vds 調整回路 163 は、例えばウィルソン型のカレントミラー回路であり、2 つの電流経路がセンスMOSトランジスタ Tr20 およびメインMOSトラン

10

20

30

40

50

ジスタ (Tr10 ~ Tr15) のドレインにそれぞれ接続されている。これにより、各N MOSトランジスタのドレイン - ソース間電圧Vdsが一定に調整されるため、より精度良く各N MOSトランジスタのドレイン電流を制御することができる。

#### 【0069】

(変形例3)

センスMOSトランジスタTr20およびメインMOSトランジスタ(Tr10 ~ Tr15)の閾値電圧や電荷の移動度は一般に温度特性を有しているので、温度の変化とともにIGBT200のゲート電圧が変化する虞がある。本変形例では、これを抑制するため、センス電流制御回路SCとして、第3実施形態および変形例2に示した参照電源162に適切な温度特性を持たせた構成を採用している。

10

#### 【0070】

具体的には、本実施形態におけるオフ側回路160のセンス電流制御回路SCは、図10に示すように、オペアンプ161と、所定の電流をオペアンプ161の一方の入力端子に供給する電流源P2と、オペアンプ161に対して電流源P2と並列接続された感温素子164と、を有している。本変形例における感温素子164は、例えば感温ダイオードである。各N MOSトランジスタの閾値電圧や電荷の移動度は一般に負の温度特性を有し、また、感温ダイオードの電圧降下量(Vf)も負の温度特性を有する。このため、図10に示すように、オペアンプ161の非反転入力端子に電流源P2および感温ダイオードを接続し、反転入力端子にオペアンプ161の出力を負帰還させる。これによって、駆動装置100の温度上昇に合わせて、センスMOSトランジスタTr20およびメインMOSトランジスタ(Tr10 ~ Tr15)のゲート電圧を低下させることができる。すなわち、温度によるIGBT200のゲート電圧の変化を抑制することができる。なお、感温素子164としては、感温ダイオードに限定されるものではない。

20

#### 【0071】

(その他の実施形態)

以上、本発明の好ましい実施形態について説明したが、本発明は上記した実施形態になんら制限されることなく、本発明の主旨を逸脱しない範囲において、種々変形して実施することが可能である。

#### 【0072】

上記した実施形態および変形例では、パワースイッチング素子としてIGBT200を例示したが、この例に限定されない。例えば、パワースイッチング素子として、パワーMOSトランジスタ等についても本発明を適用することができる。

30

#### 【0073】

また、スイッチ回路SWとして、図3に示すような回路構成を例示したが、これに限定されない。すなわち、遅延回路140の出力に基づいて、入力端子INと出力端子OUT間ににおける電流の通電および遮断を制御できればよい。

#### 【0074】

また、上記した実施形態および変形例では、駆動装置100が、一つのセンスMOSトランジスタTr20を有する例について示したが、センスMOSトランジスタTr20は複数形成されてもよい。この場合、各センスMOSトランジスタそれぞれに対応したメインMOSトランジスタが複数形成される。また、メインMOSトランジスタの数についても上記例に限定されない。

40

#### 【0075】

さらに、上記した実施形態および変形例では、センスMOSトランジスタTr20を構成する単位MOSトランジスタTr16が1個である例を示したがこの数についても限定されない。また、メインMOSトランジスタ(Tr10 ~ Tr15)を構成する単位MOSトランジスタTr16が8個である例を示したが、この数についても限定されるものではない。

#### 【0076】

上記した第3実施形態、変形例2および変形例3の説明は、オフ側回路に対してセンス

50

電流制御回路SCのバリエーションを記載したものであるが、オン側回路110に適用することができる。

【符号の説明】

【0077】

- 100 . . . 駆動装置

- 110 . . . オン側回路

- 120 . . . オフ側回路

- 130 . . . dV/dt検出回路

- 140 . . . 遅延回路

- 200 . . . パワースイッチング素子(IGBT)

- Tr10 ~ Tr15, Tr50 ~ Tr55 . . . メインMOSトランジスタ

- Tr20, Tr60 . . . センスMOSトランジスタ

- SW (SW1 ~ SW5, SW6 ~ SW10) . . . スイッチ回路

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 29/78 6 5 6 C

(72)発明者 小林 敦

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 金森 淳

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

審査官 小林 秀和

(56)参考文献 米国特許出願公開第2013/0169322(US, A1)

特開2012-098220(JP, A)

特開2012-249357(JP, A)

特開2014-054019(JP, A)

特開2010-283973(JP, A)

特許第4954290(JP, B2)

特開平11-299221(JP, A)

国際公開第2007/138929(WO, A1)

(58)調査した分野(Int.Cl., DB名)

H 0 2 M 1 / 0 8

H 0 1 L 2 1 / 3 3 6

H 0 1 L 2 9 / 7 8

H 0 3 K 1 7 / 0 4