**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) . Int. Cl.<sup>7</sup>

H01L 21/304

(45) 공고일자 2005년08월31일

(11) 등록번호 10-0511381

(24) 등록일자 2005년08월23일

|           |                 |           |                 |

|-----------|-----------------|-----------|-----------------|

| (21) 출원번호 | 10-2002-0050844 | (65) 공개번호 | 10-2003-0019144 |

| (22) 출원일자 | 2002년08월27일     | (43) 공개일자 | 2003년03월06일     |

|            |            |             |        |

|------------|------------|-------------|--------|

| (30) 우선권주장 | 10142400.0 | 2001년08월30일 | 독일(DE) |

|------------|------------|-------------|--------|

|           |                                          |

|-----------|------------------------------------------|

| (73) 특허권자 | 실트로닉 아케<br>독일연방공화국 81737 뮌헨 한스-사이델-플라츠 4 |

|-----------|------------------------------------------|

|          |                                             |

|----------|---------------------------------------------|

| (72) 발명자 | 조지제이피츠<br>독일연방공화국 데-84489부르그하우센, 도르프너 베그18A |

|----------|---------------------------------------------|

|                                           |

|-------------------------------------------|

| 미켈케르스탄<br>독일연방공화국 데-84489부르그하우센, 바하스트라세44 |

|-------------------------------------------|

|                                           |

|-------------------------------------------|

| 안톤후버<br>독일연방공화국 데-84489부르그하우센, 아우겐탈러 베그26 |

|-------------------------------------------|

|          |        |

|----------|--------|

| (74) 대리인 | 유미특허법인 |

|----------|--------|

**심사관 : 김갑병**

**(54) 국부평탄도를 향상시킨 반도체 웨이퍼 및 그 제조방법**

**요약**

본 발명은 반도체 웨이퍼의 표면을 가공하는 기계적 가공에 의한 유일한 재질제거 연마를 특징으로 하며 단일공정(1S-DDG)으로 반도체 웨이퍼의 양면을 동시 연마하는 반도체 웨이퍼의 제조방법에 관한 것이다.

또, 본 발명은 향상시킨 기하학적 구조 및 나노토폴로지(nanotopology)에 관한 것이다.

**대표도**

도 1a

**색인어**

국부평탄도, 나노토폴로지(nanotopology), 재질제거 기계적 가공, 기하학적 형상, 사진평판(photolithography).

**명세서**

## 도면의 간단한 설명

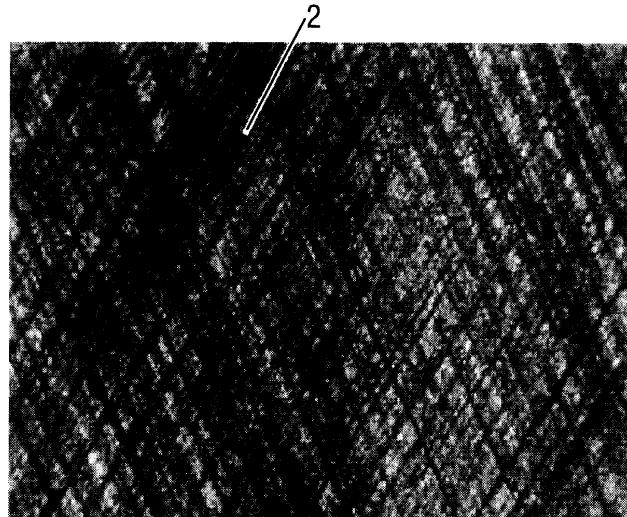

도 1a 및 1b는 기계적 가공 종료후, 본 발명에 의해 제조된 각 1실리콘 웨이퍼의 웨이퍼면의 미시적 영상도, 도 1a는 양면 연마를 실시한 도, 도 1b는 종래 기술에서 따라 제조된 실리콘 웨이퍼를 나타낸 도이다.

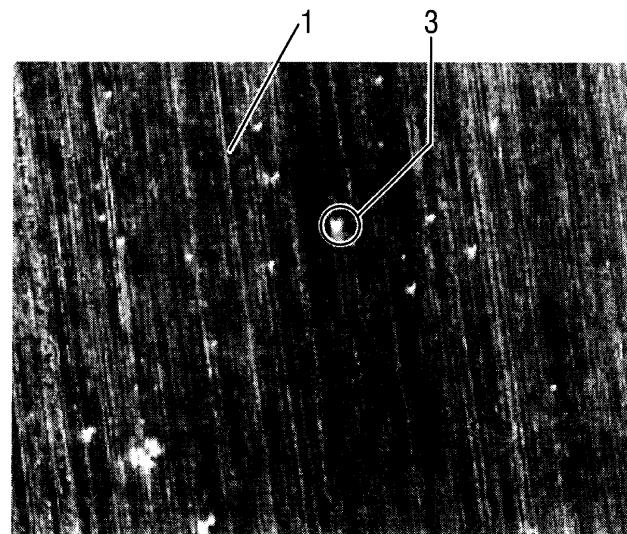

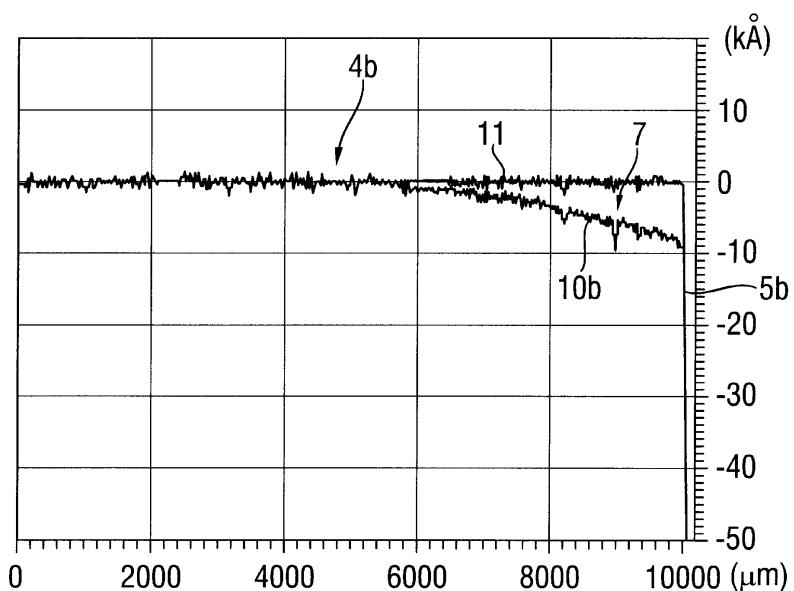

도 2a 및 2b는 각각 기계적 가공 종료후, 본 발명에 의해 제조된 실리콘 웨이퍼의 에지영역의 표면 프로파일도, 도 2a는 양면 연마를 실시한 도, 도 2b는 종래 기술에 따라 제조된 실리콘 웨이퍼를 나타낸 도이다.

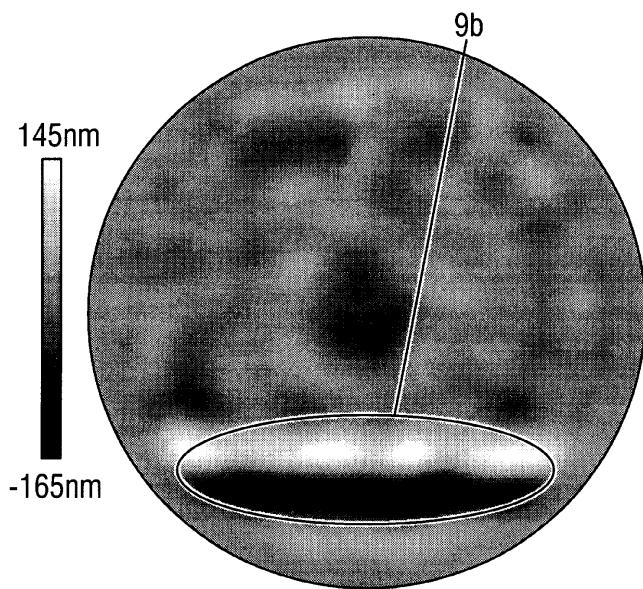

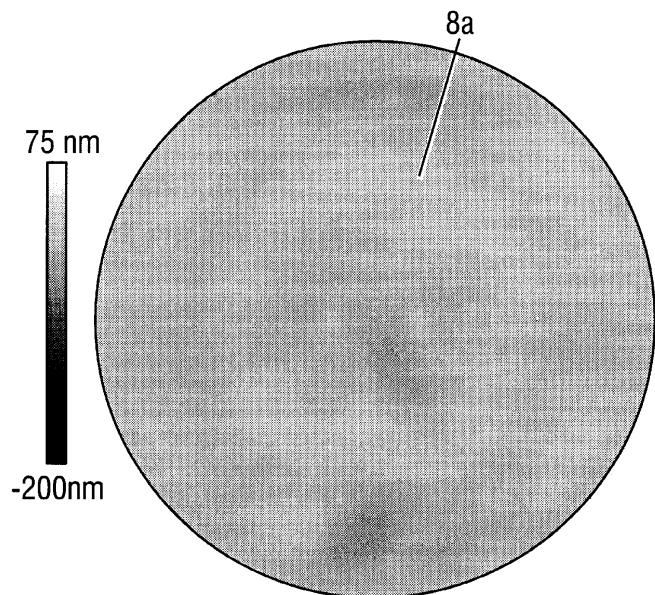

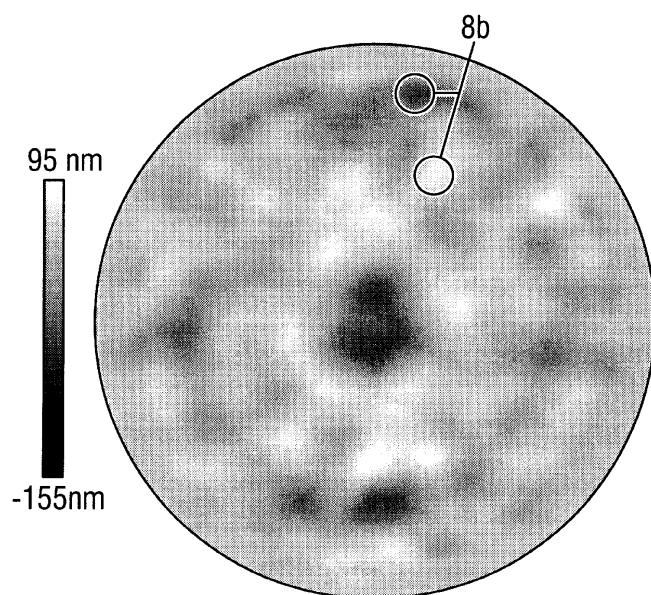

도 3a는 연마 종료후의 본 발명에 의해 제조된 실리콘 웨이퍼의 나노토플로지를 나타내며, 도 3b는 마찬가지로 연마 종료후의 종래 기술에 따라 제조된 실리콘 웨이퍼이다.

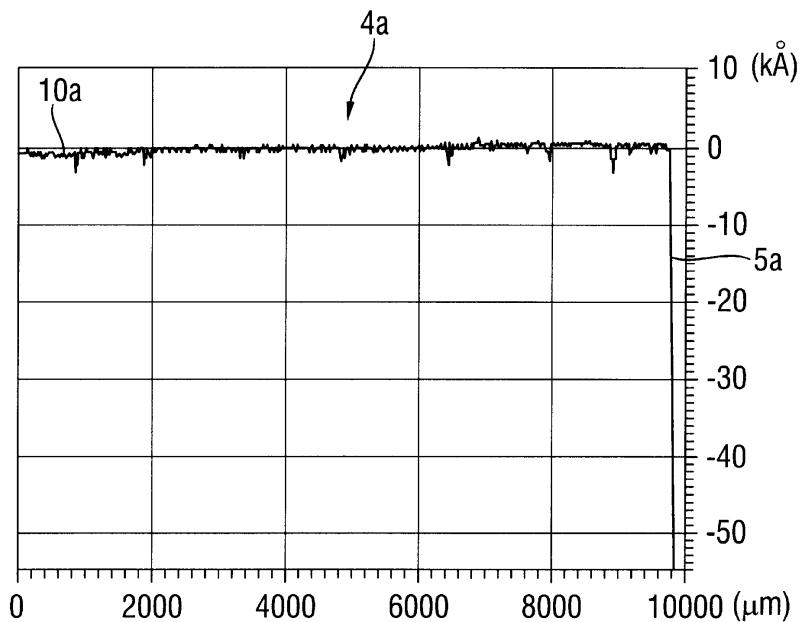

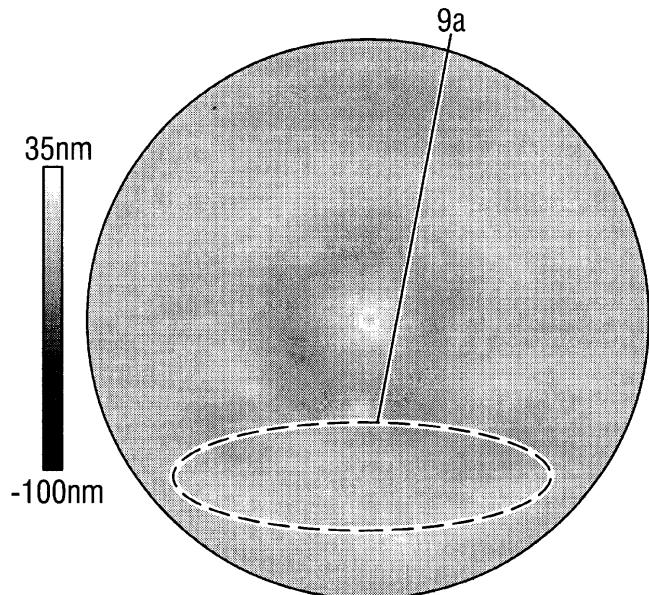

도 4a 및 4b는 실리콘 웨이퍼가 와이어톱(MWS)으로 절삭시 톱와이어가 쪼갠 잉곳 조각으로부터 생긴 것 이외에는 도 3a 및 3b와 동일한 비교를 나타낸 도이다.

### <도면의 주요부분에 대한 부호의 설명>

1,2 : 연삭 마크, 3 : 마모조각,

4a : 웨이퍼 표면, 5a : 웨이퍼 에지,

7 : 에지 강하, 8b : 국부높이 편차,

10a : 우수평면도, 10b :프로필로그램(profilogram),

11 : 거칠기 커브.

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 국부평탄도(나노토플로지)를 향상시킨 반도체 웨이퍼 및 그와 같은 형의 반도체 웨이퍼를 제조하는 방법에 관한 것이다.

전자공학, 마이크로 전자공학 및 마이크로 전자기계공학의 산업은 실리콘 및 게르마늄 또는 갈륨비소화물등의 기타 몇개의 반도체 웨이퍼를 점점 정밀하고, 복잡하며 재생가능한 규모로 기계적 및 화학적 정형화, 가공화 및 구조화에 크게 기여를 두고 있다.

이와 같은 기술의 구동력은 특히 구성부품 집적밀도가 높아짐에 따라 사실상 원자규모로 화학적으로 또 구조적으로 잘 구성되는 구조를 필요로 하는 것이 시발점인 실리콘 마이크로전자공학이다. 특히, 필요 구성부품은, 예로써 마이크로 프로세서는 전형정으로 서로 전선으로 접속되고 절연 중간층에 의해 서로 분리된 다층구조의 구성부품 레벨로 이루어지고 있다. 이와 같은 형의 다층 구성부품제조의 중간 공정은 중간층을 평탄화하는데 사용하는 사실상 화학적 기계적 연마(CMP)뿐이다. 이들 중간층의 고평탄도는 다음 구성부품 레벨의 사진평판구조화에 대한 최대 조건이다. 최근  $0.18\mu\text{m}$  또는  $0.13\mu\text{m}$ 의 측면구조 분해능 및  $200\text{nm}$ 이하의 노출파장이 요구됨으로 석판인쇄는 매우 낮은 노출초점 깊이를 가짐으로 다만 특히 평탄한 노출표면에만 작용한다.

CMP방법이 절연층을 관통하지 않으며 또 그 밑에 배치된 구성부품을 상하지 않게 하며, 크기가 불균일하게 생성된 구조물을 얹게 않는 것을 보증하기 위하여 개시표면까지도 즉, 실리콘기판 베이스의 표면은 가능한한 완전하게 평탄하게 되어야 한다.

수년전까지도, 기판웨이퍼에 필요한 평탄도는 모든 기판에 대해 다만 포괄적이거나, 또는 각각의 구성부품에 의해 점유된 표면적에 대해 정의되고 명세화하였다.

예를 들면, 특성가변 TTV(total thickness variation, 전두께 변화)는 웨이퍼의 전영역을 통하여 웨이퍼 두께의 편차를 나타낸다.

다른 편으로는, 특성가변 SFQR(site focal-plane least-square deviation range(peak to valley), 사이트 초점면 최소 자승 편차범위(피크 벨리)는 각각 구성부품 조립의 범위에 관계한다(사이트; 노출점; 즉 예로써 25mm × 25mm의 면을 가진 마이크로 프로세서).

이들 장기특성 변수이외에 개시면의 잔류거칠기는 개시면에 구성되어 그로부터 형성된 각개구성 부품의 작용에 직접 영향을 미치므로, 각각 구성부품의 길이 규모에 단기(원자)거칠기에 대해 규정이 되어 왔으며, 아직도 되고 있다. 큰규모 다층 구성부품의 구성부품 중간층을 평탄화하는 CMP방법의 출현으로 이들 전통적, 특히 단기 및 장기 약정영역 이외에 밀리미터(millimeter)규모 및 약간 그 이상의 최대 잔류 얼룩의 명세사 추가된다. 이 범위내의 구조를 나노토풀로지(nanotopology)라고 칭한다.

"나노토풀로지" 또는 "나노토포그래피"(nanotopography)의 용어는 약 0.2 ~ 20mm(측면 상관관계 길이)의 3차원 과장 및 품질지역(QFA, "고정품질영역"; 제품명세서에 요구된 웨이퍼 특성이 만족되어야 할 표면영역)내의 영역에서 모든 웨이퍼 앞면의 평탄성의 관찰로서 SEMI(Semiconductor Equipment and Materials Inter national)에 의해 보다 정확하게 규정된다.

그러므로, 특히 나노토풀로지에 속하는 것으로써 분류될 수 있는 웨이퍼의 특징은 그의 특징적 측면 크기(상관관계 길이 또는 장소진동수)에 의해 비교가능한 크기 서열 높이변화를 가진 다른 특징과는 구별된다. 예를 들면, 단지 20nm의 높이(피크 벨리)를 가진 나노토풀로지 특징도 반도체 웨이퍼에 적용된 필름구조 두께에 구성부품의 기능상의 역효과를 가져오며, 또 제조시 필름의 불균일한 착색(퇴색화)으로 나타나는 변화를 가져온다.

우수한 나노토풀로지는 예로써 이와 같은 형의 레벨층에 사용된 CMP방법의 성공적 처리를 위하여 특히 중요하다. CMP처리시 사용되는 연마포의 강성 및 CMP의 기타 처리파라미터에 의해 나노토풀로지 영역에서 바람직한 평활화가 이루어진다. 그와 같은 것은 CMP처리시 나쁜 나노토풀로지와 연관된 반도체 웨이퍼상의 구성부품 구조물의 불균일한 속음 때문이다. 결과적으로, 구성부품 특징은 중간층(유전체)을 관통할 때 발생할 수 있는 달락회로의 범위까지 악화된다.

나노토풀로지는 서로 다른 크기의 측정칸을 가진 모든 웨이퍼 표면이 완전히 그리고 중첩되게 스캔닝되어 측정되며, 각 측정칸에서 측정된 표면높이(피크 벨리)중의 하나도 모든 웨이퍼의 필요 최대치를 초과하지 않는다. 측정칸의 크기는 명세서에 좌우되며, 예로써 2mm × 2mm, (5mm × 5mm) 및 10mm × 10mm로 기재된다. 그 측정칸에 대하여는, 예로써 구성부품의 0.13μm 최소 측면크기의 경우에는 < 20nm, (<30nm) 및 <50nm의 최대 높이 편차가 허용된다. 거의 독점적으로 CMP방법을 사용하여 제조되는 수준 높은 요구사항이 적용된다. CMP방법의 특수성 때문에, 그 요구사항은 전반적인 사이트(site) 관계된, 그리고 미시적 잔류얼룩치 보다 매우 엄격하며, 반도체 웨이퍼 제조의 통상적 가공절차로는 달성될 수 없으며, 또는 통상적 가공절차로는 비경제적 수율만은 달성할 수 있다.

그러므로, 특히 단층제조 기술에서, 또 CMP방법으로 0.13μm와 그 이하의 측면 구성부품 크기 및 200mm와 그 이상의 웨이퍼 직경으로, 특히 마이크로 전자부품을 요구하는 제조에 의해 가지게 되는 개시 평탄도에 대한 요구사항을 만족하는 그러한 나노토풀로지를 가진 반도체 웨이퍼를 제조하는 것이 필요하다.

종래 방법에 의해, 반도체 웨이퍼 특히 실리콘 웨이퍼는 다음의 여러 공정 그룹으로 이루어진 가공절차에 의해 저결합 일체식 단결정으로부터 개시하여 제조된다 :

- (a) 단결정을 웨이퍼로 분리하는 작업(톱질),

- (b) 기계적 가공,

- (c) 화학적 가공,

- (d) 화학 · 기계적 가공.

또한, 세정, 분류, 측정 및 포장등의 광범위한 기타공정이 실시된다. 그러나, 이것들은 웨이퍼 표면의 평탄도에는 영향을 미치지 않으므로, 다음 본문에서는 상세하게 설명되지 않는다.

종래 기술에 따라, 분리작업(a)는 내부 직경톱(ID), 와이어톱(멀티와이어톱, MWS)에 의해 분리/평탄화 연마(그라인드-슬라이싱, GS)에 의해 밴드톱(단일절삭, 다중절삭) 또는 웨브톱(다중절삭)에 의해 일반적으로 달성된다.

기계적 연마(b)는 기계적 연마 재질제거 공정에 의한 웨이퍼 에지의 원형화 및 웨이퍼 표면의 평탄화로 이루어지며, 에지 원형화(에지/노치 원형화, ENR)는 등근 스트립형 공구 또는 유사공구를 사용하여 연삭 또는 연마에 의해 실행되며, 웨이퍼 표면의 평탄화는 래핑 혼탁액을 사용한 비결합입자 래핑에 의해 배치로 즉 다수의 웨이퍼에 대해, 동시에 또는 비결합입자 연삭에 의한 단일 웨이퍼 방법으로 실시된다. 연삭의 경우, 반도체 웨이퍼의 한측은 진공으로 척(chuck)에 고정되며, 다른측은 연마제 입자로 덮인 연삭 디스크에 의해 가공된다. 반도체 웨이퍼의 양측의 가공은 순차로 이루어진다.

일반적으로, 래핑운동학을 가진 배치양면 연삭방법이 사용되며, 거기에는 준고정상태로 자리잡고 있는 덮개(천)에 사용된 결합 연마제, 또는 연마제가 반도체 웨이퍼를 반자유상태에서 연마한 2개의 큰 대향한 디스크에 배치됨으로, 반도체 웨이퍼는 래핑시와 마찬가지로 가이드 케이지에서 양측으로 운동할 수 있다. 또한, 작업 디스크를 경질재로 덮힌 펠렛(pellet)과 맞물려 있는 "플랫 혼닝(flat honing)" 같은 방법도 있다.

화학적 가공(c)은 1개 이상의 세정공정 및 에칭공정으로 이루어진다. 에칭시(배치로 또는 각 단일 웨이퍼당), "깊은 세정", 파손결정성을 가진 표면지역의 제거 및 기계적 가공후의 기계적 표면응력 감소의 목적으로 반도체 웨이퍼의 양측에서 재질이 제거된다.

에칭에 의해 제거된 재질량은 재질의 부가적 소모이며, 또 반도체 웨이퍼 제조에 포함된 전반적 가공경비를 증가시키며, 또 더욱이 가공시 이전에 달성한 웨이퍼의 기하학적 구조(평탄도, 치수정확도)의 열화와 일반적으로 관련됨으로 에칭을 배제하는 수많은 선형순서가 알려져 있다.

화학·기계적 가공(d)은 복수의 연마공정으로 이루어진다. 종래 기술에 따라 이를 공정은 임의 선택 다단예비연마공정 및 일반적 다단정밀연마공정을 함유한다. 예비연마(스톡-제거연마, 1차 연마) 및 정밀연마(무연마염마, 2차 연마)는 이 경우 중간세정, 분류, 측정 및 기타 스텝을 가진 여러 다른 마신으로 복수의 피가공물 클램프의 형태로 실시되며, 또는 매번 예비연마 및 정밀연마를 위해 특성이 최적화되는 여러 다른 연마포를 가진 다양한 연마판에 직접 반도체 웨이퍼를 이송하는 종합 기계공구로 실시된다.

일반적으로 연마공정은 콜로이드분산성 화학적변성실리카용액(현탄액)이 반도체 웨이퍼와 연마포간의 상대운동의 결과로 기계적 마모에 의해 부분적으로, 그러나 화학적 공정에 의해 탁월하게 재질을 제거하는 화학·기계적 공정이다. 이와 같은 제거에 의해 결정결함(기하학적 구조)을 적게 하고, 또 표면을 미시적으로 평탄(거칠기)하게 하도록 웨이퍼의 평면화를 다듬질한다.

예비연마 및 정밀연마에는 단면연마 방법이 사용되며, 예비연마에는 양면연마 방법이 사용된다. 단면 연마의 경우에는 반도체 웨이퍼는 뒷면에서 지지판(시멘트 연마)에 결합되어 진공으로 지탕되며, 또는 후면 바침패드(주고 정밀연마의 경우)로 알려진 마찰에 의해 접착된다. 단면연마에는 개별 웨이퍼 연마방법과 배치 연마방법의 양방법이 있다. 정밀연마는 차후에 반도체 웨이퍼의 앞면이 될 연마에만 적용된다.

차후에 웨이퍼 뒷면이 될 소정의 다듬질에 따라, 앞면만이 예비연마시 처리되며, 결과로 뒷면은 사전 처리에 의해 결정된 거칠기를 유지하며, 또는 양면은 그후의 단면연마에 의해, 또는 동시 양면연마에 의해 처리된다. 양면연마는 다만 예비연마 방법에 사용된다. 또한, 종래 기술은 웨이퍼가 반자유롭게 이동하여 래핑운동학을 사용하여 연마포를 구비한 2개 판간에 양면에서 동시에 연마될 수 있도록 반도체 웨이퍼를 얇은 가이드 케이지에 삽입하는 배치(batch)방법을 포함한다.

또한, 일반적으로 웨이퍼의 에지는 예비연마전에 다듬질 가공(연마)되며, 통합 예비원형화(챔퍼링) 및 단일공정에서 정밀원형화(에지연마)를 제공하는 절차를 포함한 그외의 절차도 알려져 있다. 가공웨이퍼의 특히 우량한 기하학적 구조는 기계적 가공(b)시 동시 양면 연삭방법(양면 디스크 연삭, DDG)을 사용하여 달성되는 것이 공지되어 있다. 그러나, 지금까지 발표되고 동시 양면 연삭공정을 포함한 모든 기계적 절차의 공통 특징은 복수의 기계적 가공공정을 포함하고 있는 것이다.

지금까지 원측적으로 DDG방법을 거친 예비연삭 스텝으로, 또는 2단 방법에 예비연삭으로 또 다듬질 연삭스텝으로 사용하는 DDG스텝을 가진 가공절차는 다만 가능한 것으로 또 달성 가능한 것을 고려되어 왔다.

특허문헌(EP 1 049 145 A1)에서는, 1개 또는 다수의(차례로)단면 다듬질스텝 (다듬질)전에 DDG 예비연삭 스텝(거칠게 하는)을 포함한 가공절차를 발표하였다.

대조적으로, 특허문헌(US 6,066,565)에서는, 양면 예비연삭 및 양면 다듬질연삭을 가진 2단 방법의 DDG공정의 사용에 대하여 발표하였다. 이것에는 2개의 머신이 필요하며, 또 여러번 크램핑될 공작부품이 필요하다.

종래 방법에 의한 상기의 가공절차는 DDG가공의 일반적 장점은 DDG를 사용시 항상 필요한 것으로 사료되는 복수의 스텝에서 기계적 가공의 결점을 회생시켜서 얻는 것을 특징으로 한다. 1개 이상의 DDG스텝을 함유한 종래 방법에 의한 부분적 다단기계적가공절차는 모든 가공절차에 대하여 다음의 현저한 결점을 가진다.

재질의 소모는 가공스텝의 수에 따라 증가한다. 양단 또는 다단가공의 경우에는 열적평형이 성립될때까지의 연삭 및 가열연삭은 여러회 발생함으로 단일 스텝가공을 할때보다 전체적으로 더 많은 재질이 피가공물에서 제거된다. 또한, 각 개개의 스텝의 품질목표를 초기품질이 변동하는 피가공물을 가지고도 확실하게 달성될 수 있도록 최소한의 재질제거를 할 수 있는 재질 제거재가 여러번 재질제거에 사용되어야 한다.

제거 재질량 이외에 각 개개 스텝의 수율은 100% 이하임으로 스크랩 비율은 가공스텝의 수에 따라 증가한다.

또한, 다수의 가공스텝을 가진 긴 처리절차는 저유연성, 전체적 가공절차 및 긴 드로우푸트시간의 불충분한 가용성을 특징으로 하며, 일반적으로 가공절차의 전체적 가용성은 각개 스텝수가 증가할수록 떨어진다. 그러므로, 생산손실을 제거하기 위하여는 버퍼저장 및 예비머신을 유지하는 것이 필요하다.

그러므로, 전체적으로 반도체 웨이퍼의 생산비용은 가공 스텝수에 따라 상승하며, 이와 같은 현상은 그밖에 유리한 DDG 스텝을 함유한 종래 방법에 의한 다단 기계적 가공절차에도 적용된다.

따라서, 본 발명이 기저로한 목적은 계속되는 부품제조의 증가하는 품질 요구를 만족하는 특히 나노토폴로지에 관한 반도체 웨이퍼, 동시에 가능한 한 저가이며, 재질절약형이고, 또 고속이며, 유연성의 반도체 웨이퍼의 제조방법을 제공하는 것이다.

### 발명이 이루고자 하는 기술적 과제

본 발명의 목적은 단일스텝(1S-DDG)에서 반도체 웨이퍼 양면의 동시 연삭을 포함한 반도체 웨이퍼의 제조방법에 의해 달성되며, 여기서 그 연삭공정은 다만 반도체 웨이퍼의 표면을 가공하기 위해 사용되는 재질제거 기계적 가공스텝이다.

### 발명의 구성 및 작용

반도체 웨이퍼를 제조하는 본 발명의 방법에 있어서, 반도체 웨이퍼면의 기계적 성형가공은 "1-스텝 동시 양면연마"에 의해 바로 한번에 실시된다("1-스텝 동시 양디스크 연삭", "단일-페스 동시 양디스크 연삭", 1S-DDG, "양디스크 연삭" 및 "양면연삭"은 기재된 동시 연삭방법의 관계에서 같은 의미에서 사용된다). 이것은 동시 양면연삭기로 시행되는 방법을 의미하는 것으로 이해되며, 다만 1개의 피가공물 클램프를 가진 단일 가공작업으로 이루어지는 것을 특징으로 한다. 이것은 일반적으로 필요한 예비가공 및 정밀가공("거칠기" 및 "다듬질")이 통합된 단일 가공스텝에서 실시되는 것을 의미한다.

그러나, 만족스러운 개시 표면에 관하여는 한정되지 않으며, 모든 실질적 거칠기를 가진 표면 및 이전 방법에서의 구조물, 특히 MWS(단방향 및 양방향), ID, GS 또는 웨브톱(web saw)에 의해 톱질하여 얻은 표면을 가공하는 것이 가능하다.

그러나, 또한 이미 연삭된 또는 이미 연마된 표면을 처리하는 것이 가능하다. 특히, 1S-DDG는 특히 그후의 다듬질 스텝에 대해 성공한 이전의 분리공정(정밀공정)에서 얻은 평활한 표면에 "진입거칠기"(engagement roughness)를 생성하기 위해, 즉 정밀 연삭스텝의 가는 마모제 입자가 진입할 수 있는 거칠기를 생성하기 위해 거치름 스텝에서 종래 방법의 공정에서 항상 필요한 것으로 고려된 표면의 거칠기를 제거한다.

1S-DDG방법은 재질량의 추가 제거의 필요없이 거칠기, 두께 또는 기하학적 형상에 대한 개시 웨이퍼 품질의 변동을 크게 견디어 낸다. 일반적으로 1S-DDG스텝은 종래 방법의 다단기계적가공공정의 상기 결점을 제거함으로, 작업시 상당량의 재질이 절약된다.

동시에, 양면 연삭공정에서 2개의 스픬들축의 공선배열에 의해 양면 연마후 반도체 웨이퍼의 최종 두께의 치수정확도를 고도로 달성하는 것이 가능하다.

본 발명에 있어서는 종래의 방법에서 요구되는 것 같은 예비가공, 또는 래핑에 의한 재가공의 단면가공(SSG), 웨이퍼 양면의 연속 단면연삭(2×SSG), 또는 주로 기계적 대패질 제거에 의한 형태 형성시키는 어떠한 기계적 공정도 없다. 이것은 이들 공정에 의해 반도체 웨이퍼의 표면, 더욱이 그 에지를 가공하지 않음으로, 연삭 전후에 실시되는 에지 원형화 또는 에지 연마를 배제하지 않는다.

본 발명의 방법에 의해 반도체 웨이퍼는 특히 소수의 각개의 가공스텝을 사용하여 제조된다. 소수의 각개의 가공스텝은 제조(광범위한 고객 명세서에 대한 신속반응), 물류관리(생산라인에서의 소량의 재질; 보다 신속한 가용성)등의 융통성에 상당한 이점을 가져온다. 또한, 특히 반도체 웨이퍼는 재질면에서 경제적으로 제조되며, 단결정 반도체 잉곳의 제조는 반도체 웨이퍼의 전체적 제조비용의 상당한 비율이 된다. 그러므로, 반도체 웨이퍼의 다듬질전의 여러 스텝에서 단결정 잉곳의 계속 가공시 재질손실의 감소는 상당한 비용절약을 가져온다.

종래 방법에 있어서, 양면 연삭스텝(양디스크 연삭, DDG)은 래핑, 단면연삭 또는 연속적 단면연삭에 의한 반도체 웨이퍼의 기타 기계적 예비가공 및 재재공을 포함하지 않으면 안되는 기계적 절차에 대한 사용만을 항상 고려하고 있다. 지금까지 기계적 중앙 평탄화 방법으로써, DDG를 사용하도록 시도하고 있다. 그러나, 기대이상으로 필요한 특성을 단일 스텝의 동시에 양면연삭으로 달성할 수 있는 것이 알려지고 있다. 그러므로, 본 발명의 방법에 의해 고수율로 품질 손실없는 반도체 웨이퍼의 제조가 이루어진다.

또한, 본 발명에 의한 방법은 복수스텝의 조합결과로 종전 방법의 처리절차에서는 가지지 않은, 또는 상실한 이점을 제공한다.

본 발명에 의한 특별한 이점은 반도체 웨이퍼를 1S-DDG방법에서 교차 연삭으로 가공하는 것이며, 이것은 연삭시 서로 교차하는 각개의 연삭체가 궤도연삭과 다르게, 예로써 다만 평행 연삭마크가 형성되는 SSG공정에서 형성되는 것을 의미한다. 교차연삭 및 그 특징은 에칭 또는 화학기계적 연마에 의해 그후의 화학적 가공에 대하여 반도체 웨이퍼의 개시형태학을 결정한다. 복수의 결정적 특징이 교차 연삭에 의해 이루어진다.

교차연삭 운동학에 의한 재질제거는, 예로써 SSG, 2×SSG 또는 DDG 및 SSG 또는 2×SSG의 조합에 의한 종래 방법에 의한 가공의 경우에는, 궤도연삭에 의한 것보다 신속하여 경제적이다.

교차연삭은 궤도연삭보다 결정학제으로 더욱 동방성이며, 단결정의 양방향 특성(결정학적 비등방성)때문에 보다 가공하기 용이하고, 또 보다 가공하기 어려운 독특한 경향이 있다. 교차연삭의 경우에는 방향이 다른 연삭마크는 가공웨이퍼면의 어느 지점에서나 항상 서로 교차함으로, 더욱 가공하기 어려운 결정학적 방향에서 보다 가공하기 용이한 결정학적 방향에서는 더이상 재질이 제거되지 않는다. 그러므로, 결정향위에 좌우되는 각개의 절삭속도는 평준화 된다.

서로 교차하는 통로를 갖지 않은 궤도연삭의 경우에는, 결정학적 가공각은 반도체 웨이퍼의 위치에 좌우된다. 그러므로, 다른 재지량이 다른 위치로부터 제거된다. 이와 같은 현상은 반도체 웨이퍼의 과도한 비균질 박막화를 보호하는 연삭디스크의 강성에 의해서만 제한된다.

궤도연삭의 경우, 결정대칭성을 반사하는 바람직한 방향의 매우 긴 패턴이 형성된다.

결정면 <100> (si <100>)에 평행인 실리콘면의 경우에는, 예를 들면 교차점이 형성되며, 한편 si<111>의 경우에는 6개 점의 별이 형성된다. 이와 같은 장파의 기하학적 방해는 다음 가공스텝에서 제거되거나, 또는 현저한 재질제거로만 제거된다. 특히, 소위 매직거울 측정법을 사용하며 질적으로 또 예로써 간섭측정법 또는 레이저 삼각측량에 의해 양적으로 주목 할만한 불필요한 연삭교차자 다듬질가공된 반도체 웨이퍼에 남게 된다.

종래 방법에 의한 DDG와 SSG 또는 2×SSG의 가공결합에서, 제 2의 SSG스텝은 웨이퍼의 표면형태학을 결정한다. 그러므로, DDG에 의해 제조한 유리한 교차연삭은 종래 방법의 가공절차에서 선택적으로 작용하는 화학적 또는 그후의 화학기계적 가공에는 더이상 사용되지 않는다. 사실상 그후의 가공공정에 의해 기계적 가공에 의해 약화된 결정격자 영역을 바람직하게 진입하여 연삭교차를 전개한다.

본 발명의 테두리 내에서 강제 유도없이(자유부동법, FFP) 실제로 반도체 웨이퍼를 지탕하고 이동하는 피가공물 마운트를 이용하는 동시 양면연삭 방법을 사용하는 것이 바람직하다. 일반적으로 그 자체가 결점이 있는 비강제적 또는 강제적

잠금 마운트를 통하여 제한적 강제상태를 제거한 FFP가공의 일반적 장점은 예로써(양면) 래핑 및 양면연마(DSP)에서 공지되어 있으며, 제이 하이스마(J.Haisma)씨 등(응용광학 33(34)(1994)7945)에 의해 DSP의 특징인 성질에 대한 전형적 응용의 예로써 기재되었다.

또한, 경질의 세라믹 결합의 연삭휠의 사용은 본 발명의 테두리 내에서 바람직하며, 그 강성 때문에 그 훈은 반도체 웨이퍼의 특히 최종 두께 치수정확도를 높게 한다.

또, 1S-DDG의 세라믹결합 연삭디스크에 의해 마모된 플라스틱 형태의 표면오염 및 예로써 금속에 의한 표면 또는 부피 오염이 방지된다. 예로써 수지결합한 연삭디스크를 사용할때 발생하는 마모 플라스틱의 부재는, 예로써 재질제거 에칭에 의해 그후의 "깊은 세정스텝"을 없게 할 수가 있다.

또한, 에칭은 기계적 가공에 의한 결정파손의 원인이 되는 표면응력을 감소시킬 수 있으므로, 에칭스텝을 생략하는 예비 조건은 연삭후 평활한 다듬질을 충분히 하는 것이다.

결정응력 및 결합의 밀도가 너무 클때에는 특히 자유로히 이동하는 반도체 웨이퍼를 가진 "자유부동" DSP의 경우에 연마시 기계적 하중은 그 결합을 번식시키며, 또 최종 생성품에서도 지속한다.

그러므로, 본 발명의 방법에 대하여 1S-DDG 공정후 웨이퍼 표면의 낮은 거칠기를 확보하는, 특히 미세 마모제 입자를 사용하는 것이 바람직하다. 그러나, 입자의 분말도는, 1S-DDG에 의한 반도체 웨이퍼의 개시표면의 직접 가공이(예로써 MWS에 의한 단결정 잉곳의 절삭후), 사용된 마모제 입자가 거칠면 거칠수록 더욱 용이하게 아직 가능함으로, 일정한계에 설정된다. 그 정반대의 요구사항은 본 발명의 방법의 테두리 내에서 사용하는 것이 바람직한 특정한 세라믹 결합 연삭디스크를 통하여 만족된다. 미국 메시(US mesh) 또는 JIS메시 #2000(및 FEPA표준; 약 4~6 $\mu\text{m}$  평균입자 크기에 대응한)에 대응한 또한 더욱 미세한 마모제 입자를 가진 연삭디스크가 특히 바람직하게 사용된다. 또한, 결합경도 및 다공성, 마모제 입자농도 및 분포곡선 및 스핀들 전진운동, 스핀들 전략 및 제거율등의 기타 몇개의 재질 파리미터 및 처리 파라미터가 가공된 재질에 배합되는 것이 특히 바람직하다.

1S-DDG의 가공 서브스텝후, 본 발명에 의해 제조된 반도체 웨이퍼는 잔존결정격자결함(파속)의 낮은 표면거칠기, 조도 및 깊이를 가지며, 예로써 본 발명의 실시예에서는 약 400Å RMS의 조도를 #2000 마모제입자 체(sieve)(4~6 $\mu\text{m}$  입자크기)를 가진 세라믹 결합 절삭휠에 의해 달성하였으며, 약 100Å RMS의 조도를 1.5 $\mu\text{m}$  입자크기의 체로 달성하였다.

또한, 약 50Å RMS의 조도는 본 발명에 의한 단일 1S-DDG 가공작업에서 연삭휠 원형을 사용하여 달성되었다. 이것은 단면연삭(궤도연삭)에 의해 아직도 경제적으로 존속할 수 있는 가능한 가장 미세한 재질제거율을 제공하며, 종래 방법에 따라 자체예리화(self-sharpening)(블록킹 않됨)하는 수지결합 연삭휠로 작업할때에도 500Å RMS 이하의 조도를 달성할 수 없는 것과 비교될 수 있다(<80 $\mu\text{m}$  높은 페스에서 1 $\mu\text{m}$  다이아몬드 탐침을 가진 조도계의 측정치). 특히, 조도는 재질 절약 후속 연마제거로도 소정의 최종 다듬질을 제공할 수 있을 정도로 낮다. 또한, 연마시 기계적 하중 때문에 결합변식이 없으므로, 잔류하는 결정결함은 최종 생성품에 이르는 모든 곳에 존속하지 않는다. 원칙적으로 본 발명의 1S-DDG 공정은 최종 생성품 상당한 정밀가공을 가능하게 한다. 칙(chuck)이 없다는 것은 접촉을 지탱함으로 야기되는 연삭 반도체 웨이퍼의 파손이 없으며, 따라서 재질집중식으로 제거 또는 수리되어야 할 굵힌 자국이 없다는 것을 의미한다.

1S-DDG 가공서브스텝후, 반도체 웨이퍼는 처리목표치에 가까운 매우 낮은 두께편차를 가진다. 그러므로, 본 발명은 한 스텝에서 반도체 웨이퍼의 동시양면 연삭후 즉시  $\Delta\text{THK} \leq 0.75\mu\text{m}$ ( $\Delta\text{THK}$  = 시험배치에서 평균웨이퍼 두께<THK>의 표준편차)의 소정평균 목표두께(두께, <THK>와 TTV≤1 $\mu\text{m}$ 의 전두께 변화(TTV)에서의 편차를 가지는 반도체 웨이퍼에 관한 것이다.

또, 1S-DDG 가공서브스텝후, 반도체 웨이퍼는 현저하게 회전대칭적이다. 즉, 반도체 웨이퍼내에서 잔존 TTV치를 나타내는 두께분포는 반사상으로 대칭(1-파라미터)횡단면 프로파일에 의해 거의 완전하게 결정된다. 그러므로, 본 발명은 또한 한 스텝에서 반도체 웨이퍼의 동시양면 연삭후, 즉시 회전대칭  $\Delta\text{ROT} \leq 0.5\mu\text{m}$ 를 가지는 반도체 웨이퍼에 관한 것이다.

정의에 의해, 두께분포의 잔여각 종속성으로 인한 회전비대칭  $\Delta\text{ROT}$ 는 항상 전두께 변화 TTV보다 작거나, 동일하여야 한다. 가장 최근의 종래 기술에 의한 연삭방법에 있어서, 전 두께변화(TTV)에의 큰 기여는

$$\text{TTV} = \max_{\phi, r} \{ \text{THK}(\phi_1, r_1) - \text{THK}(\phi_2, r_2) \}$$

실제로 예로써 반도체 웨이퍼의 에지형성, 예로써 단면연삭의 경우는 텁블링Chuck(tumbling chuck)(수직운동)에 의해 회전비대칭  $\Delta ROT$ 는

$$\Delta ROT = \max_r [\max_{\Phi} \{ THK_r(\Phi_1) - THK_r(\Phi_2) \}]$$

와 같이 정의되며, 여기서  $\max_{\Phi, r}$ 는 각( $\Phi$ ) 및 반경( $r$ )이 변화될 때 얻은 최대높이차  $THK(\Phi_1, r_1) - THK(\Phi_2, r_2)$ 이며, 또  $\max_{\Phi}$ 는  $\Phi$ 가 변화되고,  $r$ 이 고정될 때 얻은 최대치이며, 또  $\max_r$ 는  $r$ 이 변화되고,  $\Phi$ 가 고정될 때 얻은 최대치이며,  $THK_r(\Phi)$ 는 고정된  $r$ 을 가진  $\Phi$ 의 함수로서 국부두께(THK)를 나타낸다.

좋은 목표두께 치수정확성으로, 본 발명에 의한 반도체 웨이퍼는 연마에 의한 직접 다른 가공에 특히 적합하며, 무엇보다 예비연마는 다수의 웨이퍼가 하나의 가공작업에서 연마판에 동시에 평행으로 가공되는 다수웨이퍼 공정이다. 이와같은, 다수 웨이퍼 연마공정에 도달하는 반도체 웨이퍼의 매우 균일한 개시두께는 연마배치에 모든 웨이퍼에 대해 재질의 균일제거 및 일정하고 우수한 기하학적 형상 및 나노톤플로지를 특징으로 하는 성공적 엔마방법에 대한 긴요한 조건이다. 이 조건은 모드웨이퍼의 개개의 연마운동학이 연마작업에서 동일할때에만 충족된다. 특히, 웨이퍼가 2개연마판간에 자유로히 부동하는 것 같이, 웨이퍼가 얇은 가이드 케이지에 느슨하게 배치되어 연마되는 양면연마의 경우에는 개시두께의 모든 산란은 각각 웨이퍼에 불균일한 하중분포를 하게 된다. 가장 두꺼운 웨이퍼는 연마처리 개시에 연마판에서 대부분이 하중을 흡수함으로, 위와 같은 현상은 파쇄의 위험성을 증가시킨다. 또한, 개시두께의 큰 산란은 웨이퍼에서 웨이퍼로 여러 다른 운동학, 즉 개개의 운동을 하게 한다 : 두꺼운 웨이퍼는 빠르게 회전하며, 얇은 웨이퍼는 느리게 회전한다.

개개의 웨이퍼에 있어서, 이것은 다른편으로는 양면연마후 여러 다른 기하학적 형상을 유도한다.

또, 개시두께의 변동은 만족스러운 기하학적 형상 및 기타 웨이퍼 특성을 가진 균질한 개시두께를 달성하기 위해 다수 웨이퍼 연마시 제거가 필요한 소량의 재질을 증가시킨다.

연마에 의한 재질제거는 매우 비용이 많이 드름으로, 가능한 얇은 연마공정이 바람직하다. 따라서, 1S-DDG방법에 의해 제공되는 것 같은 매우 균질개시두께가 요구된다.

예를들면, DDG거치론 연마 및 SSG 또는 2×SSG 다듬질로 이루어진 결합방법에 있어서, 주로 동일한 웨이퍼개시두께를 제공하는 DDG방법의 고유장점은 SSG가 비교적 나쁜 최종두께 안정성만을 고유하게 제공함으로, SSG 또는 2×SSG에 의한 재가공을 통하여 무효로 된다.

이것은 SSG에 의한 척과 연삭스핀들간의 축옵셋(axes-offset)에 비교한 DDG에 의한 연삭스핀들 축의 공선성(collinearity) 때문이다. DDG에 의한 공선성은 연삭휠의 순간적 절삭속도의 변동에 대한 공정을 면하게 만들며, 고유하게 뱃뺏하고, 비틀림에 대한 저항성이 있다.

절삭휠의 절삭속도가 자연적으로 변화하는 경우에는 축옵셋은 연삭스핀들 송달의 결과로 형성하는 압력의 반대압력을 보상하면서, 서로간에 또 머신의 탄성비틀림에 대해 축을 경사되게 한다.

또, 처리시 순간적 피가공물 두께의 정밀측정은 이 경우, 웨이퍼의 양면이 가공시 자유로히 접근함으로 DDG에 의해서만 가능하다. SSG의 경우, 척(chuck)에 일반적으로 파동반도체 웨이퍼의 편면성 부족으로 척의 상면과 피가공물 저면간의 소정위치에 남아있는 공간은 알 수 없으며, 또 잔류수직운동 및 척자체의 불균일성의 두께측정을 찌그러지게 함으로, 순간적 두께의 정확한 측정을 방해하는 척위에 웨이퍼의 한면이 지탕된다. 최근의 웨이퍼두께의 측정은 2×SSG방법에서 연질척과 경질척이 전형적으로 교대로 사용되고, 또 연질척의 두께측정은 일반적으로 고도의 정확성이 불가한 사실 때문에 부가적으로 더욱 어렵게 된다.

1S-DDG가공서브스텝후에, 반도체 웨이퍼는 높은 목표치 정확성을 가지며, 이것은 1S-DDG가공후의 반도체 웨이퍼의 실제형상이 연마 또는 선택적 에칭의 다음 가공스텝에 대한 개시형상을 형성하는 목표한 형상으로부터 다만 약간 벗어난 것을 의미한다. 또한, 1S-DDG가공후 아직 잔류한 잔류형상편자는 항상 그후의 공정에 대하여 특히 위태롭지 않은 형이다.

예를들면, 양면연마(DSP)는 그 DSP자체는 회전대칭 웨이퍼구조를 생성하며, 도 유사한 회전비대칭(예로써 웨지형상)은 다른 재질의 제거를 포함한 추가연마에 의해 다만 효율적으로 제거됨으로, 임의로 분포된 국부두께  $THK = THK(\Phi, r)$ (각 경우  $\triangle ROT$  및 TTV의 비교치에 대해)에서 얻은 그 전체두께변화 TTV에 보다 웨이퍼두께 THK의 잔류회전 비대칭  $\triangle ROT$ 에 더욱 위태롭게 반응한다.

일반적으로, 후속가공의 최적개시형상도 특히 후속방법의 소정특징이 그 형상에서 목표편차에 의해 사전에 보상되는 경우에는 이상적인 평면웨이퍼의 형상으로부터 때때로 벗어난다. 한 예로, 여기서 다시 DSP를 언급할 수 있으며, 그것은 소정의 조건하에 평면-평행면의 소망한(그리고, 달성가능한) 이상(ideal)에서 벗어나 회전대칭면, 그러나 볼록하게 만곡된다(양면 볼록렌즈)을 형성하기 쉬워, 그러므로 1S-DDG처리후 1 양면 오목렌즈 임의로 오목하게 만곡된 면(및 마찬가지로 필요한 회전대칭면)으로 이익을 가져온 DSP이다.

1S-DDG방법의 사용을 통한 전체적 처리절차의 단축은 연삭웨이퍼는 완전가공된 웨이퍼의 다듬질에 접근한 것을 의미함으로, 좋은 기하학적 형상의 문제점은 기계적 형상가공후에도 상당히 중요하다. 본 발명의 방법절차의 후속방법은 웨이퍼 형상의 어떠한 중요한 변화를 더이상 야기하지 않음으로, 특히 연마시 제거된 상당량 감소된 재질을 가진 단기 처리절차의 경우에는 1S-DDG방법에 의해 제공된 것 같이, 기계적 가공스텝후의 특히 평면웨이퍼가 일반적으로 유리하다.

반도체 웨이퍼 제조에 대한 본 발명에 의한 바람직한 방법절차는 다음 서브스텝을 포함한다.

- (a) 다수의 반도체 웨이퍼로 반도체 잉곳의 분리화.

- (b) 반도체 웨이퍼의 에지의 원형화.

- (c) 반도체 웨이퍼 양면의 동시연삭, 1S-DDG.

- (d) 반도체 웨이퍼의 연마.

여기서, 스텝(c)은 반도체 웨이퍼 면을 가공하는데 사용되는 유일한 재질제거 기계적가공스텝이다.

스텝(a)는 웨이퍼형태의 단위를 정확한 치수로 된 견인단결정에서 분리하는 분리스텝이다. 그 분리스텝은 종래방법에 따라 시행되며, 순차적 분리방법(한 웨이퍼후 다음 웨이퍼로), 또는 동시분리방법(동시에 한벌의 절삭으로 모든 웨이퍼)이 될 수 있다. 순차적 분리방법은 예를들면 내공톱(ID) 또는 띠탱(band saw)을 사용하여, 시행된다. 웨이퍼의 동시톱질 및 잉곳의 단부면의 연삭, 즉 형성된 반도체 웨이퍼면의 톱질(연삭슬라이싱, GS)이 또한 가능하다.

그러나, 본 발명의 방법절차의 테두리내에서 임의로 절삭현탄액(현탄액 절삭래핑, S-MWS) 또는 결합마모제 입자를 와이어(즉, 다이아몬드 와이어 절삭-래핑, D-MWS)를 사용한 와이어톱에 의한 동시분리방법(다수와이어 슬라이싱, MWS)이 바람직하다. MWS방법의 장점은 낮은 비용, 높은 배출 및 비교적 큰 잉곳직경에 대해서도 유용성이 있는 것이다. 예로써, 톱질과동같은 MWS의 전형적 단점은 본 발명에 의한 후속양면 연삭스텝에 의해 제거된다.

스텝(b)에서, 웨이퍼에지를 프로파일한다(에지/노치원형화, 챕퍼링). 이 스텝은 종래기술의 방법에서 임의로 선택될 수 있으며, 프로파일된 마모체를 사용한 연삭, 마모체 또는 롤러에서 반도체 웨이퍼의 윤곽의 운동에 의한 연삭, 벨트 또는 천연삭을 고려하는 것이 가능하다.

특히, 또한 에지정밀원형화 또는 에지챔퍼링 및 에지연마를 포함한 통합처리를 사용하는 것이 가능하다.

통상적인 거친원형화의 경우에는 에지/노치연마스텝이 다른 가공절차시 적절한 위치에 포함되어야 한다.

또, 에지원형화는 1S-DDG스텝후에 실행되며, 이 대안의 단점은 아직 정확하지 않은 치수 및 웨이퍼의 예리한 에지, 또 후속에지원형화 재클램핑되어야 할 웨이퍼의 결과로서 1S-DDG스텝에 의해 시행되는 반도체 웨이퍼의 표면다듬질에 대한 위험때문에, 1S-DDG가공시 피가공물 취급의 어려움이 증가하는 것이다. 다른 편으로는 에지원형화시, 예로써 특허문헌(JP 08090401A)에 기재된 것 같이 통합챔퍼링 및 정밀원형화 방법(연삭 및 연마)의 사용이 가능한 이점이 있다.

스텝(c)는 앞에서 광범위하게 설명한 1S-DDG공정이다.

스텝(d)는 종래기술에 의한 연마방법이며, 다음에 별도로 설명되는 예비연마 및 최종연마로 일반적으로 이루어진다. 예비연마는 다수웨이퍼 또는 단일웨이퍼 연마방법이고, 또 단면 또는 양면연마방법이다. 양면연마방법은 순차적 단면연마방법(먼저 뒷면, 다음에 앞면) 또는 동시양면 연마방법(DSP)이다. 단일 웨이퍼 및 다수 웨이퍼, 단면 및 양면연마방법의 모든 조합이 가능하다. 지금까지는 다만 다수웨이퍼 DSP에 의해 DSP와 관련한 종래기술의 일부분을 형성하였다. 최종연마는 일반적으로 단면연마로서 시행된다.

스텝(d)에서 여러 다른 연마방법을 사용한 본 발명에 의한 다음의 가공절차가 바람직하다: 연마는 양면 예비연마웨이퍼 앞면의 단면최종연마 절차로 이루어진다. 또, 반도체 웨이퍼의 양면연마가 단면연마를 순차적으로 실행하며, 그 다음 반도체 웨이퍼의 앞면이 최종연마를 실시하는 가공절차를 사용하는 것이 가능하다.

단면 예비연마와 단면 최종연마는 서로 분리되어 일어날 수 있으며, 또는 결합될 수 있다. 예를들면, 뒷면 및 앞면의 예비연마를 하나의 머신으로 또는 하나의 공정으로 실시하는 것이 가능하다. 양자 택일로 하나의 머신 또는 하나의 공정으로 앞면 예비연마와 앞면 최종연마의 조합을 사용하는 것이 가능하다. 다만, 반도체 웨이퍼의 앞면이 예비연마되고, 다음 최종연마되는 가공절차가 또한 가능하다. 단면 예비연마와 단면 최종연마가 분리형태에서(즉, 분리된 머신으로) 또는 통합형태에서 일어난다(즉, 처리중단없이 또는 아무로딩 및 언로딩 작업없이 필요할 경우, 그간에 실시된 세정스텝을 통하여 반도체 웨이퍼가 직접 이송된 다른 연마판을 가진 1개의 머신으로).

양면에 동시에 또는 순차적으로 한면에 또는 다만 한면에(즉, 스픬 · 에칭방법을 사용하여), 화학적 수단에 의해 웨이퍼면에서 재질을 제거하는 에칭 또는 (깊은)세정스텝은 임의로 양면연삭(c)과 연마(d)간에 부가될 수 있다.

필요한 경우, 이와같은 방법으로 경정격자파손 및 표면응력을 감소시키며 또 오염을 제거시킨다. 그러나, 에징스텝 없는 가공절차가 바람직하며, 이것에 의해 재질, 시간 및 비용이 절약되며, 처리절차가 단순화된다. 또한, 기계적 가공시 달성되는 웨이퍼 형상에서 에칭의 결과로서 항상 발생하는 열화를 기피할 수가 있다.

또한, 세정, 분류, 측정 및 포장스텝등의 광범위의 기타스텝을 시행할 수 있으나, 이것은 웨이퍼면의 평면도에 영향을 주지 않는다. 또, 웨이퍼면은 예로써 에피택시(epitaxy)에 의해 최종연마후 코팅될 수 있다.

본 발명에 의한 다듬질 가공 반도체웨이퍼는, 예로써 정밀연마후, 우수한 국부평면도(나노토플로지)를 가진다. 그러므로, 본 발명은 크기  $2\text{mm} \times 2\text{mm}$ 의 임의의 측정영역에서  $20\text{nm}$ 이하 및 크기  $10\text{mm} \times 10\text{mm}$ 의 임의의 측정영역에서  $50\text{nm}$ 이하인 웨이퍼 앞면에 있는 최대의 울퉁불퉁을 가진 반도체 웨이퍼에 관한 것이다.

그 결과로, 웨이퍼는 고수율을 가진 기타 추후가공에 특히 적합함으로 CMP방법을 사용하여 생성된 특히 고품질 부품을 형성할 수가 있다. 그 CMP방법은 상기의 짧은 영역에서 잔류 울퉁불퉁에 특히 위태롭게 반응한다.

본 발명에 의한 방법은 특히 스텝(a)에서 와이어톱을 사용하여 반도체잉곳을 절삭시 톱와이어가 파열되어 새와이어로 교체될 경우에는 우수한 나노토플로지를 가지게 된다. 절삭후, 그와 같은 것은 웨이퍼의 두께프로파일에서 독특한 스텝이다. 종래 방법에 의한 이와같은 "파열-와이어"는 톱질배치에서 모드웨이퍼에, 즉 동시에 약  $200 \sim 300\text{nm}$  영향을 미치므로, 고품위 응용에는 사용할 수 없으며, 또 전체적 생산비용에 대해 대응되게 심각한 결과로 일반적으로 폐물로 된다. 본 발명에 의한 방법은 이와같은 웨이퍼도 고품질의 최종생성품으로 가공할 수가 있다.

본 발명에 따라 생성된 반도체 웨이퍼의 다른 특위한 유효특징은 가장 외부의 에지에 까지 도중내내 높은 평면성이다. 특히, 그 웨이퍼는 웨이퍼면을 평가할때(에지 제외, EE) 지금까지 배제되었던 에지영역에 대해서도 전형적으로  $3\text{mm}$ 이다.

본 발명에 의해 생성된 반도체 웨이퍼에 있어서, 품질은 소정의 표면영역의 크기가, 예로써 에지배제  $2\text{mm}$ (기대표준),  $1\text{mm}$ (미래) 및  $0.5\text{mm}$ 만큼 증가할때, 다만 약간 악화한다.

특히, 본 발명에 따라 제조된 웨이퍼는 어떤 "에지드롭"을 갖지 않는다. 즉, 웨이퍼의 에지방향으로 어떤 궁용부(convexity) 또는 두께의 폭줄임을 가지지 않는다.

SSG 또는  $2 \times SSG$ 의 경우, 그들 가공에 필요한 큰 연삭디스크 직경에 의해, 그와 같은 에지드롭을 발생시킬수 있다. SSG에서 사용되는 연삭디스크의 직경은 전형적으로 가공되는 반도체 웨이퍼의 직경보다 크다. 이것은 웨이퍼의 직경위에 가능한한 일직선으로 뻗는 이상적인 절삭경로를 형성하기 위해 필요하며, 이것은 척(chuck) 및 연삭스핀들의 축의 옵셋(offset) 때문에 연삭시 불균일한 힘의 유입으로 야기된 불안정을 깨트린다. 따라서, SSG에 필요한 큰 연삭 디스크는 웨이

폐의 에지를 웨이퍼면만으로 거의 수직으로 연삭한다. 웨이퍼면에 수직으로 신속한 연삭진입에 의해 구조적으로 약한 에지에 미세한 에지플레이킹(edge flaking)이 발생한다. 또한, 궤도연삭(서로 교차하지 않는 평행연삭마크)로서 알려진 연마운동학을 통하여, SSG는 웨이퍼에지에서 결정양화를 일으키며, 그와 같은약화는 그후 가공시, 예로써 화학적에칭 또는 화학기계적연마에 의해 웨이퍼에지에서 제거된 재질량을 증가시킨다.

SSG의 경우, 비교차방사상궤도연삭은 보편적으로 피가공물의 오목클램핑에 의해, 작은 볼록체 또 척축 또는 스판들축의 적절한 작은 경사를 서로 형성시킨다. 원칙적으로, 교차연삭은 SSG에 의해 가능하다. 그러나, 그것은 분리하다. 그 이유는 척/스핀들축의 옵셋 및 그 결과로 생긴 불안정성에 대한 고유의 성향때문에, 진동 및 스틱·슬립(stick and slip)등을 가진 고르지 못한 진입도 고의로 사전강요된 축의 방향설정에 의한 작업시에 발생할 수 있기 때문이다.

그러나, DDG의 경우 가공한 반도체 웨이퍼의 반의 직경범위의 직경을 가진 작은 연삭디스크를 사용하는 것이 유리하다. 그것은 양 연삭휠스핀들이 서로 정밀하게 배열되고, SSG에서와 다르게, 모든 힘이 DDG에서는 정확하게 보상되기 때문이다. 이것에 의해 마모체는 웨이퍼에지에 거의 평행으로, 그에 따라 작은 연삭각으로 부드럽게 웨이퍼면을 연삭시키며, 또 에지에서 미소박편의 가능성을 감소시킨다. 또한, DDG의 교차연삭은 차기공정에서 에지영역에 불균질한 재질제거를 가진 경정학적상의 결정격자 과손이 없는 것을 의미한다.

본 발명의 이점을 도면 및 실시예에 따라 더욱 상세히 설명한다.

#### 실시예 1.

본 발명에 의한 실리콘 웨이퍼는 와이어톱에 의해 공칭직경 300㎚의 정확한 크기로 된 단결정에서 절삭하여, 크기 #2000(약 4 ~ 6μm)의 세라믹 결합마모제 입자를 가진 연삭휠을 사용하여 에지원형화(1S-DDG)를 하며, 웨이퍼면위에 에칭혼합물의 층흐름을 가진 에칭장비에 있는 불화수소산 및 질산의 적절한 혼합물을 사용하여 에칭을 하고, 본 발명의 양면 예비연마 및 단면 최종연마를 하여 제조되었다.

도 1은 1S-DDG 가공서브스텝후의 실리콘 웨이퍼면의 확대도(현미경에 의한)를 나타낸다. 서로 교차한 1S-DDG강공에 의한 연삭마크(2)가 분명하게 나타나 있다.

표면에는 마모물질 또는 오염물이 없으며, 그것은 작은 거칠기와 깊은 손상과 함께 추후에칭 또는 추후세정에 대한 필요성을 제거하였기 때문이다. 그 표면은 청결하고 등군질이였다.

도 2는 스캔닝프로브로 기록된 흐로필로그램(profilogram)의 형태에서 1S-DDG 가공서브스텝후의 실리콘 웨이퍼의 에지영역의 양적표시를 나타낸 도이다. 웨이퍼에지를 이르는 도중내내 좋은 평면도(10a)가 고의로 이미 원형화된 웨이퍼면(4a)과 웨이퍼에지(5a)간의 가파른 전이를 통하여 명확하게 인정된다.

에지원형화시 생성된 챔퍼(chamfer)가 민감한 높이금(단위 : 10KÅ = 1μm) 때문에 거의 하방으로 향한 수직선으로 보인다.

충분히 가공되고 연마된 실리콘 웨이퍼의 앞면이 도 3에 나타내었으며, 국부높이 편차(-200nm ~ 75nm)의 그레이스케일(gray scale) 표시가 간접측정시험법에 의해 얻어졌다.

특히, 전체면을 통한 2mm×2mm 및 10mm×10mm의 소정의 측정영역에서 모든 국부높이 편차는 각각 20nm 또는 50nm 이하였다. 그레이스케일은 회귀표면에 대응한 영(zero)높이로 표면의 절대높이를 나타낸다.

#### 비교 실시예 1.

기계적 가공스텝시 1S-DDG 공정이 2회 실시는 연속적 단면연삭(2×SSG)으로 대치되는 것 이외에는, 실시예 1과 동일 방법으로 실리콘 웨이퍼를 제조한다.

2×SSG 공정은 제 2의 경질철(hard-chuck) 연삭스텝으로 뒤따르는 제 1의 연질척(soft-chuck) 연삭스텝으로 이루어진다(실리콘 웨이퍼의 디크킹, 턴닝 및 중간세정후). 크기 15μm(약 #1200)의 마모제 입자를 가진 수지결합 연삭휠을 사용한다. 또한, 전체재질 20μm를 제거한 산성층 흐름에 에칭스텝을 기계적 가공과 연마스텝간에 실시하였다.

도 1B는 기계적 가공후의 실리콘 웨이퍼의 확대도(현미경하 예)를 나타낸다. 대략 평행이고, 서로 교차않는 개개의 연삭마크(1)가 뚜렷하게 분명히 보인다. 연삭휠의 수지결합 마모조각(3)은 추후재질제거세정 또는 에칭스텝을 필요로 한다.

이들 추가스텝시, 높은 지역의 재질은 마모된 위치에서 마스킹의 결과로 그 자리에 남아 있게 되며, 이것은 거칠기에 역효과를 가지게 되어 대응한 다향의 재질제거가 필요하게 된다.

기계가공후의 웨이퍼표면 에지영역의 프로필로그램(10b)을 도 2B에 나타내었다. 시행된 연삭공정은 사전에 고의로 등글게 된 에지영역(5b)에 향한 웨이퍼맨 (4b)에 조기강하(7)가 존재하는 것을 의미한다. 일반적으로 관례적인 3mm의 에지배제(본 도에서는 약  $x = 7000\mu\text{m}$ )에 의해 약  $3\text{K}\text{\AA} = 0.3\mu\text{m}$ 의 편차를 가진 불원의 에지강하(7)는 실리콘 웨이퍼의 전체적 평면도에 결정적 차이를 아직 만들지 않고 있다. 미래의 감소된 에지배제 대역 2mm(이경우,  $x = 8000\mu\text{m}$ 에서 약  $4\text{K}\text{\AA} = 0.4\mu\text{m}$ 인 편차  $\Delta y$ ,  $1\text{mm}(x \sim 9000\mu\text{m}, \Delta y \sim 6\text{K}\text{\AA} = 0.6\mu\text{m})$  또는  $0.5\text{mm}(x \sim 9500\mu\text{m}, \Delta y \sim 8\text{K}\text{\AA} = 0.8\mu\text{m})$  및 웨이퍼의 전체표면상의 높아진 평면도 요구에 의해, 이와같은 에지강하는 분명히 품질 및 수율의 감소면에서 영향을 끼친다. 여과않던 프로필로그램(10b) 및 고역 여과된 거칠기커브(11)를 나타내었다.

도 3B에는 완전가공된 실리콘 웨이퍼의 나노토플로지를 나타내었다. 그레이스케일 표시(-155nm ~ +95nm)는 또다시 간접측정시험법에 의한 것이다. 분명하게 공헌한 단거리 국부높이 편차(8b)가 보이며,  $2\text{mm} \times 2\text{mm}$  또는  $10\text{mm} \times 10\text{mm}$ 의 선택측정 분야내에서는 이들의 크기는 때때로 20nm 또는 50nm 이상이다. 종래 방법에 따라 제조된 그와 같은반도체 웨이퍼는 그외의 처리에 대하여는 요구하는 바가 많으며, 또 대규모의 집적마이크로 전자다층부품 및 특히 그와 같은부품을 사용하는 화학기계적 연마(CMP)방법에 대하여는 적합하지 않다.

## 실시예 2.

실리콘 웨이퍼는 본 발명에 의해 실시예 1에 기재된 방법과 동일하게 제조되었다. 실시예 1과 다만 다른 차이는 톱와이어가 MWS에 의해 실리콘 단결정의 절삭시 파열되었으며, 또 절삭작업이 새와이어를 결합후에 계속 된 것이다. 그것은 열적 표류 및 다수의 기타이유 때문에 처리중단에 의해 그와같이 절삭된 웨이퍼의 두께프로파일에서 항상 명백하게 형성된 스텝으로 이르게 된다. 그러나, 그후 가공은 도 4A에 표시된 간섭그램(interferogram)에 의해 나타낸 것 같이 거의 완전히 이 스텝을 제거하였으며, 최종제품의 표면(9a)은 거의 완전하게 평탄하게 되었다.

## 비교 실시예 2.

와이어 파열이 발생한 실시예 2의 톱질배치(sawn batch)에서 얻은 실리콘 웨이퍼는 비교 실시예와 동일방법으로 종래방법에 의해 가공되었다. 도 4B는 완전가공된 실리콘 웨이퍼의 간섭그램(interferogram)을 나타낸다. 도 4A에 비교하여 상당히 큰 높은 치수를 사용하여도(도 4A의 -100nm ~ +35nm에 비교하여 -165nm ~ +145nm), 와이어 파열시 형성된 표면(9b)의 스텝은 완전히 가공된 웨이퍼 높이의 중대한 국부편차로서, 즉 연마후에 분명하게 볼 수 있다. 종래 방법에 따라 제조된 그와 같은웨이퍼, 그러므로 와이어 파열이 발생한 전체 톱질배치는 그외의 가공에 대해 요구하는 바가 너무 많아서, 특히 화학적 기계적 평탄화(CMP)방법을 이와같은 부품의 제조에 사용할 경우에는 대규모의 집적 마이크로전자 다층부품에 적합하지 않다.

## 발명의 효과

본 발명에 있어서, 반도체 웨이퍼면을 가공연마시 재질제거 가공방법의 단일 스텝가공(1S-DDG)을 이용한 반도체 웨이퍼의 양면의 동시연마로 우수한 평면도를 가진 제품의 제조는 물론, 동시에 저비용, 소량의 재질제거등 여러 장점을 가진다.

## (57) 청구의 범위

### 청구항 1.

반도체 웨이퍼의 제조방법으로서,

(a) 반도체 잉곳(ingot)을 복수의 반도체 웨이퍼로 분리하는 스텝과,

(b) 반도체 웨이퍼의 에지를 원형화하는 스텝과,

(c) JIS/US 메시(mesh) #2000 또는 더 미세한 연마제 입자크기를 가진 세라믹 결합 연삭휠을 이용하여, 상기 반도체 웨이퍼의 양면을 동시연삭(1S-DDG)하는 스텝과,

(d) 반도체 웨이퍼를 연마(polish)하는 스텝

을 순차적으로 구비하고,

상기 반도체 웨이퍼의 양면을 동시연삭하는 (c) 스텝은 상기 반도체 웨이퍼면을 가공하기 위해 사용되는 유일한 기계적 재질 제거 가공 스텝인 것을 특징으로 하는 반도체 웨이퍼의 제조방법.

## 청구항 2.

삭제

## 청구항 3.

제 1항에 있어서, 상기 반도체 웨이퍼를 연마하기 전에 웨이퍼 표면의 한면 또는 양면을 에칭매질로 처리하는 것을 특징으로 하는 반도체 웨이퍼의 제조방법.

## 청구항 4.

삭제

## 청구항 5.

삭제

## 청구항 6.

삭제

## 청구항 7.

단일스텝으로 반도체 웨이퍼의 양면을 동시연삭(1S-DDG)한 직후에, 목표두께(THK)의 편차  $\triangle$ THK가  $0.75\mu\text{m}$  이하이고, 기하학적 형상치 TTV가  $1\mu\text{m}$  이하이며, 회전대칭치  $\triangle$ ROT가  $0.5\mu\text{m}$  이하이고, 앞면의 표면 비평탄도(파크-밸리의 편차)의 최대치가, 모든 측정 영역에서  $2\text{mm} \times 2\text{mm}$ 의 크기 내에서는  $20\text{nm}$  이하이고, 모든 측정 영역에서  $10\text{mm} \times 10\text{mm}$ 의 크기 내에서는  $50\text{nm}$  이하인 것을 특징으로 하는 반도체 웨이퍼.

## 청구항 8.

삭제

## 청구항 9.

제 7항에 있어서, 상기 표면 비평탄도의 최대치는 상기 반도체 웨이퍼의 에지로부터  $0.5\text{mm}$ 를 배제한 모든 영역에 대해 만족하는 것을 특징으로 하는 반도체 웨이퍼.

**도면**

도면1a

도면1b

도면2a

도면2b

도면3a

도면3b

도면4a

도면4b