(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5376706号

(P5376706)

(45) 発行日 平成25年12月25日(2013.12.25)

(24) 登録日 平成25年10月4日(2013.10.4)

|               |                      |

|---------------|----------------------|

| (51) Int.Cl.  | F 1                  |

| H 01 L 27/10  | (2006.01)            |

| G 06 K 19/07  | (2006.01)            |

| G 06 K 19/077 | (2006.01)            |

| H 01 L 29/786 | (2006.01)            |

|               | HO 1 L 27/10 4 6 1   |

|               | HO 1 L 27/10 4 3 1   |

|               | G 06 K 19/00 H       |

|               | G 06 K 19/00 K       |

|               | HO 1 L 29/78 6 1 3 B |

請求項の数 6 (全 24 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2007-294261 (P2007-294261)  |

| (22) 出願日     | 平成19年11月13日 (2007.11.13)      |

| (65) 公開番号    | 特開2008-147640 (P2008-147640A) |

| (43) 公開日     | 平成20年6月26日 (2008.6.26)        |

| 審査請求日        | 平成22年11月4日 (2010.11.4)        |

| (31) 優先権主張番号 | 特願2006-310883 (P2006-310883)  |

| (32) 優先日     | 平成18年11月17日 (2006.11.17)      |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (74) 代理人  | 100099173<br>弁理士 濵谷 孝                          |

| (72) 発明者  | 徳永 肇<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

|           | 審査官 外山 毅                                       |

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

同一基板上に複数の薄膜トランジスタと、複数のメモリ素子とを有する半導体装置の作製方法であって、

絶縁表面を有する基板上に第1の半導体層及び第2の半導体層を形成し、

前記第1の半導体層及び前記第2の半導体層上に第1の絶縁膜を形成し、

前記第1の半導体層上に前記第1の絶縁膜を介して第1の導電層を形成し、

前記第2の半導体層上に前記第1の絶縁膜を介して第2の導電層を形成し、

前記第2の導電層の側壁部に第1の絶縁層を形成し、

前記第1の導電層、前記第2の導電層、及び前記第1の絶縁層を覆う第2の絶縁膜を形成し、 10

前記第2の絶縁膜をエッチングして、前記第2の導電層、前記第1の絶縁層及び前記第2の半導体層を露出する第1の開口を形成し、

前記第2の導電層上及び前記第1の絶縁層を覆って第3の半導体層を形成し、

前記第2の絶縁膜をエッチングして前記第1の半導体層の一部を露出する第2の開口を形成し、

前記第3の半導体層上に第3の導電層を形成し、

前記第1の半導体層上に第4の導電層を形成し、

前記第2の導電層又は前記第3の導電層を、前記第3の半導体層と合金化する材料で形成し、

前記第1の導電層及び前記第2の導電層を同一工程で形成し、

前記第3の導電層及び前記第4の導電層を同一工程で形成することを特徴とする半導体装置の作製方法。

**【請求項2】**

請求項1において、

前記第1の絶縁層を、湾曲している面を有するように形成し、

前記第3の半導体層を、前記第1の絶縁層の湾曲している面で接するように形成することを特徴とする半導体装置の作製方法。

**【請求項3】**

請求項1又は請求項2において、

前記第1の導電層の側壁部に第2の絶縁層を、前記第1の絶縁層と同一工程で作製することを特徴とする半導体装置の作製方法。

**【請求項4】**

請求項1乃至請求項3のいずれか一項において、

前記第3の導電層及び前記第4の導電層の形成と同じ工程で前記第2の絶縁膜上に第5の導電層を形成し、

前記第5の導電層上に前記第5の導電層と電気的に接続するアンテナを形成することを特徴とする半導体装置の作製方法。

**【請求項5】**

請求項1乃至4のいずれか一項において、

前記第2の導電層又は前記第3の導電層のうち少なくともどちらか一方は、Ti、W、Ni、Cr、Mo、Ta、Co、Zr、V、Pd、Hf、Pt、Feから選ばれた少なくとも一の元素を含む材料からなることを特徴とする半導体装置の作製方法。

**【請求項6】**

請求項1乃至請求項5のいずれか一項において、

前記絶縁表面を有する基板は、ガラス基板、プラスチック基板、半導体基板、又は紙であることを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、シリサイド反応を利用したメモリ素子を有する半導体装置及びその作製方法に関する。

**【背景技術】**

**【0002】**

従来、様々なタイプのメモリが提案されている。代表的なメモリとしては、磁気テープや磁気ディスクを含むメモリや、書き込み読み出しが可能なRAMや、読み出しを専用とするROM(Read Only Memory)などが挙げられる。

**【0003】**

従来のROMとしては、IC製造工程におけるマスクで情報を記憶するマスクROM、ICチップ製造後に電流によりヒューズ素子を溶断して情報を記憶するヒューズROM、ICチップ製造後に電流によって絶縁体を短絡させて情報を記憶するアンチヒューズROMなどが挙げられる。

**【0004】**

マスクROMは、IC製造プロセス中のマスクで情報を記憶させるため、書き込む情報に応じたマスクを用意しなければならず、そのために製造コストが増加していた。また、ヒューズROMは、ヒューズ素子を溶断する際にゴミが発生して誤動作を引き起こす恐れがあった。

**【0005】**

また、アンチヒューズROMは、製造時に書き込む情報に応じたマスクも不要であり、メモリに情報を書き込む際にゴミも発生しない点で他のROMに比べ有利である。近年、シ

10

20

30

40

50

リコン基板上にシリサイド反応を利用したアンチヒューズROMを形成する技術が提案されている（例えば、特許文献1）。

#### 【0006】

特許文献1に開示されているアンチヒューズROMは、陰極・陽極として機能する一対の導電膜と、該導電膜間に設けられたアモルファスシリコン膜とからなるメモリ素子を複数有している。該メモリ素子は、陽極・陰極間に電圧を印加することにより、陽極又は陰極として機能する導電膜とアモルファスシリコン膜とがシリサイド反応して素子の抵抗が変化することを利用した素子である。

#### 【0007】

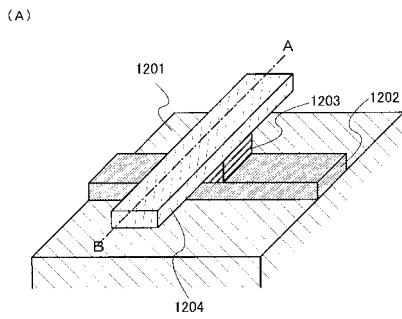

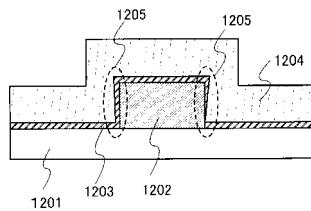

アンチヒューズROMは、例えば図12(A)に示すように半導体基板1201上に形成されたワード線となる配線1202、ワード線となる配線1202上に形成されたアモルファスシリコン膜1203、アモルファスシリコン膜1203上に形成されたビット線となる配線1204とを有している。アモルファスシリコン膜1203がワード線となる配線1202とビット線となる配線1204とに挟まれた構造となっている。このように、ワード線とビット線との交点にアモルファスシリコン膜を形成することは、メモリ素子を小型化する上で有効である。

#### 【0008】

また、近年、無線通信機能を有する半導体装置、具体的には無線チップは、大きな市場が見込まれているため、注目されている。このような無線チップは、その用途によりIDタグ、ICタグ、ICチップ、RF(Radio Frequency)タグ、無線タグ、電子タグ、RFID(Radio Frequency Identification)と呼ばれることがある。

#### 【0009】

無線チップの構成は、インターフェース、メモリ、制御部等を有する。メモリは、書き込み読み出しが可能なRAM、読み出しを専用とするROMが使用され、目的に応じて使い分けられている。具体的には、特定のアプリケーション毎にメモリ領域が割り当てられており、アプリケーション毎、並びにディレクトリ毎にアクセス権が管理されている。アクセス権を管理するため、無線チップはアプリケーションの暗証コードと比較照合する照合手段を有し、照合手段による比較照合の結果、暗証コードが一致するアプリケーションに関するアクセス権をユーザに与える制御手段を有する。このような無線チップは、シリコンウェハから形成され、半導体基板にメモリ回路、演算回路等の集積回路が集積されている。

#### 【0010】

このような無線チップが搭載されたカード（所謂ICカード）と、磁気カードとを比較すると、ICカードはメモリ容量が大きく、演算機能を備えることができ、認証性が高く、改ざんすることが極めて困難である、といったメリットを有する。そのため、ICカードは個人情報の管理に好適である。ICカードに搭載するメモリとしては、改ざんできないように、読み出しを専用とするROMが多く用いられている。

#### 【特許文献1】特許3501416号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0011】

しかしながら、図12(A)に示したメモリ素子は、半導体基板1201とビット線となる配線1202との端部に段差が生じるため、図12(B)に示す領域1205のような段差部分において、ビット線となる配線1202の側壁部にアモルファスシリコン膜1203又はワード線となる配線1204の被覆が十分に行われないことによる問題が生じる。ここで、図12(B)は図12(A)の点Aと点Bとを結ぶ破線における断面の模式図である。

#### 【0012】

例えば、ビット線となる配線1202の側壁部においてアモルファスシリコン膜1203

10

20

30

40

50

の被覆が十分に行われないことにより、ピット線となる配線 1202 とワード線となる配線 1204 とが部分的に接触しショートが生じる場合がある。また、ピット線となる配線 1202 の側壁部においてアモルファスシリコン膜 1203 が部分的に薄くなり、アモルファスシリコン膜 1203 の膜厚がばらつくことにより、メモリ素子への書き込み特性のばらつきが大きくなってしまう。

#### 【0013】

本発明は上記問題を鑑み、基板表面と基板上に形成された配線とで形成される段差部分にシリコン膜を形成した場合においても、メモリ素子の書き込み特性を低下させない半導体装置および当該半導体装置の作製方法の提供を課題とする。

#### 【課題を解決するための手段】

10

#### 【0014】

本発明は、絶縁表面を有する基板上に形成された第1の電極と、第1の電極の側壁部に形成されたサイドウォール絶縁層と、第1の電極上及びサイドウォール絶縁層を覆って形成された半導体層と、半導体層上に形成された第2の電極と、を有し、第1の電極又は第2の電極は、半導体層と合金化する材料で形成されているメモリ素子を複数有する半導体装置及び半導体装置の作製方法に関する。なお、半導体装置はメモリ素子に加えてトランジスタを有していてもよい。トランジスタのゲート電極の側壁部にサイドウォール絶縁層が設けられたものを用いる場合、トランジスタのゲート電極とメモリ素子の第1の電極とを同一工程で形成して、ゲート電極の側壁部に形成されるサイドウォール絶縁層と第1の電極の側壁部に形成されるサイドウォール絶縁層とを同時に形成することができる。

20

#### 【0015】

本発明の半導体装置は、絶縁表面を有する基板上に形成された第1の電極と、第1の電極の側壁部に形成されたサイドウォール絶縁層と、第1の電極上及びサイドウォール絶縁層を覆って形成された半導体層と、半導体層上に形成された第2の電極と、を有し、第1の電極又は第2の電極は、半導体層と合金化する材料で形成されている。

#### 【0016】

本発明の半導体装置は、絶縁表面を有する基板上に形成された複数の薄膜トランジスタ、及び複数のメモリ素子を有し、メモリ素子は、絶縁表面を有する基板上に形成された第1の電極と、第1の電極の側壁部に形成された第1のサイドウォール絶縁層と、第1の電極上及び第1のサイドウォール絶縁層を覆って形成された半導体層と、半導体層上に形成された第2の電極と、を有し、薄膜トランジスタのゲート電極は、メモリ素子の第1の電極と同じ材料であり、薄膜トランジスタのソース電極またはドレイン電極は、メモリ素子の第2の電極と同じ材料であり、メモリ素子の第1の電極又はメモリ素子の第2の電極は、半導体層と合金化する材料で形成されている。

30

#### 【0017】

本発明の半導体装置は、絶縁表面を有する基板上に形成された複数の薄膜トランジスタ、複数のメモリ素子、及びアンテナを有し、メモリ素子は、絶縁表面を有する基板上に形成された第1の電極と、第1の電極の側壁部に形成された第1のサイドウォール絶縁層と、第1の電極上及び第1のサイドウォール絶縁層を覆って形成された半導体層と、半導体層上に形成された第2の電極と、を有し、薄膜トランジスタのゲート電極は、メモリ素子の第1の電極と同じ材料であり、アンテナは、該アンテナの下方に位置する接続電極と電気的に接続し、接続電極は、薄膜トランジスタと電気的に接続し、薄膜トランジスタのソース電極またはドレイン電極と同じ材料であり、且つ、メモリ素子の第2の電極と同じ材料であり、メモリ素子の第1の電極又はメモリ素子の第2の電極は、半導体層と合金化する材料で形成されている。

40

#### 【0018】

本発明の半導体装置において、第1のサイドウォール絶縁層は、湾曲している面を有し、該湾曲している面で半導体層と接している。さらに、ゲート電極の側壁部に第2のサイドウォール絶縁層が形成されることが好ましい。また、第1の電極又は第2の電極は、Ti、W、Ni、Cr、Mo、Ta、Co、Zr、V、Pd、Hf、Pt、Feから選ばれる

50

少なくとも一の元素を含む材料からなることが好ましい。また、絶縁表面を有する基板は、ガラス基板、プラスチック基板、半導体基板、又は紙であることが好ましい。また、半導体層として、アモルファスシリコン膜、微結晶シリコン膜、又は多結晶シリコン膜を用いることが好ましい。

#### 【0019】

本発明の半導体装置の作製方法は、絶縁表面を有する基板上に第1の電極を形成し、第1の電極の側壁部にサイドウォール絶縁層を形成し、第1の電極上及びサイドウォール絶縁層を覆って半導体層を形成し、半導体層上に第2の電極を形成し、第1の電極又は第2の電極を、半導体層と合金化する材料で形成することを特徴とする。なお、サイドウォール絶縁層は、湾曲している面を有し、該湾曲している面で半導体層と接していることが好ましい。また、半導体層として、アモルファスシリコン膜、微結晶シリコン膜、または多結晶シリコン膜を用いることが好ましい。10

#### 【0020】

本発明の半導体装置の作製方法は、同一基板上に複数の薄膜トランジスタと、複数のメモリ素子とを有する半導体装置の作製方法であり、絶縁表面を有する基板上に第1の半導体層及び第2の半導体層を形成し、第1の半導体層及び第2の半導体層上に第1の絶縁膜を形成し、第1の半導体層上に第1の絶縁膜を介して第1の電極を形成し、第2の半導体層上に第1の絶縁膜を介して第2の電極を形成し、第2の電極の側壁部に第1のサイドウォール絶縁層を形成し、第1の電極及び第2の電極、及び第1のサイドウォール絶縁層を覆う第2の絶縁膜を形成し、第2の絶縁膜をエッチングして、第2の電極、第1のサイドウォール絶縁層及び第2の半導体層を露出する第1の開口を形成し、第2の電極上及び第1のサイドウォール絶縁層上に第3の半導体層を形成し、第2の絶縁膜をエッチングして第1の半導体層の一部を露出する第2の開口を形成し、第2の半導体層上に第3の電極を形成し、第1の半導体層上に第4の電極を形成し、第2の電極又は第3の電極を、第3の半導体層と合金化する材料で形成することを特徴とする。20

#### 【0021】

なお、第1のサイドウォール絶縁層は、湾曲している面を有し、該湾曲している面で第3の半導体層と接していることが好ましい。また、第3の半導体層として、アモルファスシリコン膜、微結晶シリコン膜、または多結晶シリコン膜を用いることが好ましい。また、絶縁表面を有する基板は、ガラス基板、プラスチック基板、半導体基板、又は紙であることが好ましい。また、第1の電極及び第2の電極は、同一工程で形成することが好ましい。また、第3の電極及び第4の電極は、同一工程で作製することが好ましい。また、第3の電極及び第4の電極の形成と同じ工程で第2の絶縁膜上に第5の電極を形成し、さらに、第5の電極上に第5の電極と電気的に接続するアンテナを形成することが好ましい。また、第1の電極の側壁部に第2のサイドウォール絶縁層を、第1のサイドウォール絶縁層と同一工程で作製することが好ましい。また、メモリ素子は、第2の電極と、第3の半導体層と、第3の電極とを有する。また、薄膜トランジスタは、第1の半導体層と、第1の電極と、第4の電極とを有する。また、第1の電極は、薄膜トランジスタのゲート電極であり、第1の絶縁膜は、ゲート絶縁膜であり、第4の電極はソース電極又はドレイン電極である。30

#### 【0022】

本発明の半導体装置の駆動方法は、絶縁表面を有する基板上に形成された第1の電極と、第1の電極の側壁部に形成されたサイドウォール絶縁層と、第1の電極上及びサイドウォール絶縁層を覆って形成された半導体層と、半導体層上に形成された第2の電極と、を有し、第1の電極と第2の電極との間に電圧を印加し、第1の電極又は第2の電極と、半導体層とを合金化することを特徴とする。40

#### 【0023】

なお、本発明の半導体装置の駆動方法において、サイドウォール絶縁層は、湾曲している面を有し、該湾曲している面で半導体層と接しているのが好ましい。また、第1の電極又は第2の電極は、Ti、W、Ni、Cr、Mo、Ta、Co、Zr、V、Pd、Hf、P50

t、Feから選ばれる少なくとも一の元素を含む材料からなるのが好ましい。また、絶縁表面を有する基板は、ガラス基板、プラスチック基板、半導体基板、又は紙であるのが好ましい。

**【発明の効果】**

**【0024】**

本発明の半導体装置は、メモリ素子部において基板と第1の電極との段差部分に半導体層及び第2の電極を形成した場合でも、段差部分において第1の電極と半導体層とが接触せず、第1の電極の上面部分だけがメモリ素子として機能する。第1の電極の上面に形成される半導体層の膜厚は均一であるため、メモリ素子の書き込み特性のばらつきを低減することができる。

10

**【0025】**

また、トランジスタのゲート電極とメモリ素子の第1の電極とを同一工程で形成することで、ゲート電極の側壁部に形成されるサイドウォール絶縁層と第1の電極の側壁部に形成されるサイドウォール絶縁層とを同時に形成することができる、従って、工程数を増加させることなく、メモリ素子の書き込み特性が安定した半導体装置を作製することが可能である。

**【発明を実施するための最良の形態】**

**【0026】**

本発明の実施形態について、以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

20

**【0027】**

(実施の形態1)

本実施の形態において、陽極又は陰極として機能する導電層の側壁部にサイドウォール絶縁層を有するメモリ素子の構成について説明する。

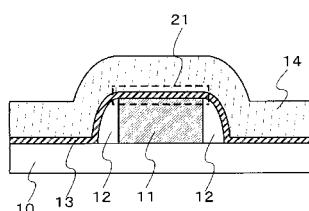

**【0028】**

本実施の形態のメモリ素子は図1に示すように、絶縁表面を有する基板10上に形成された第1の電極11、第1の電極11の側壁部に形成されたサイドウォール絶縁層12、第1の電極11及びサイドウォール絶縁層12を覆って形成されたシリコン膜13、及びシリコン膜13上に形成された第2の電極14を有する。なお、基板10と第1の電極11とで段差部が形成されており、シリコン膜13と第2の電極14とは、該段差部分を覆うように形成されている。また、サイドウォール絶縁層12は、第1の電極11の側面とシリコン膜13とが直接接するのを防いでいる。また、サイドウォール絶縁層12のシリコン膜13と接する面は湾曲していてもよい。なお、第1の電極11と第2の電極14との間に電圧を印加することにより、第1の電極11又は第2の電極14とシリコン膜13とが合金化し、領域21の状態が変化してメモリ素子の抵抗が変化する。よって、図1に示したメモリ素子を複数設けた半導体装置において、合金化したメモリ素子と合金化していないメモリ素子とを作り分けることにより、半導体装置にデータを書き込むことが可能であり、また、それぞれのメモリ素子の抵抗を読み取ることで半導体装置に書き込まれたデータを読み取ることが可能である。

30

**【0029】**

ここで、図1に示すメモリ素子の作製方法について説明する。まず、絶縁表面を有する基板10(例えば、ガラス基板)上に、プラズマCVD法やスパッタリング法等を用いてチタン(Ti)膜を形成し、エッチングすることにより第1の電極11を形成する。続いて、絶縁表面を有する基板10上に熱CVD法等を用いて珪素膜等の絶縁膜を形成し、エッチングして第1の電極11の側壁部に部分的に珪素等の絶縁膜を残存させてサイドウォール絶縁層12を形成する。このときエッチング条件によっては、サイドウォール絶縁層12の膜厚が第1の電極11の膜厚より薄くなることもある。続いて、第1の電極11上及

40

50

びサイドウォール絶縁層12を覆ってプラズマCVD法等を用いてシリコン膜13を形成する。続いて、プラズマCVD法やスパッタリング法等を用いてシリコン膜13上にチタン膜からなる第2の電極14を形成する。以上により、図1に示すメモリ素子を作製することができる。

#### 【0030】

ここで、基板10としては、ガラス基板、石英基板等を用いることができる。他にもプラスチック基板として、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PEES)、アクリルなどの基板を選択することもできる。また、基板として紙等を用いてもよい。

#### 【0031】

また、シリコン膜13として、アモルファスシリコン膜、微結晶シリコン膜、または多結晶シリコン膜を用いることができる。また、第1の電極11及びサイドウォール絶縁層12を覆って形成する膜はシリコン膜に限定されず、第1の電極11又は第2の電極14の少なくとも一方と合金化する材料からなる半導体層であればよい。例えば、シリコン(Si)、ゲルマニウム(Ge)などの単体の半導体のほかGaAs、InP、SiC、ZnSe、GaN、SiGeなどのような化合物半導体、又は酸化亜鉛(ZnO)、酸化スズ(SnO<sub>2</sub>)などの酸化物半導体等を用いることができる。

#### 【0032】

また、第1の電極11又は第2の電極14のうち、少なくとも一方はシリコン膜13と合金化する材料を用いて形成する。シリコン膜と合金化する材料を用いた膜として、チタン(Ti)、タンクステン(W)、ニッケル(Ni)、クロム(Cr)、モリブデン(Mo)、タンタル(Ta)、コバルト(Co)、ジルコニウム(Zr)、バナジウム(V)、パラジウム(Pd)、ハフニウム(Hf)、白金(Plt)、鉄(Fe)から選ばれた元素からなる金属材料、または前記元素を主成分とする合金材料若しくは化合物材料の单層膜、またはこれらの積層膜を用いることができる。

#### 【0033】

なお、第1の電極11と第2の電極14の一方をシリコン膜13と合金化する材料で形成した場合、もう一方の電極の材料は特に限定されない。例えば、タンタル(Ta)、タンクステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、等から選択された元素又はこれらの元素を主成分とする合金材料若しくは化合物材料で形成することができる。または、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成してもよい。また、第1の電極11又は第2の電極14を導電性材料を積層した膜で形成する場合、シリコン膜13と接する側がシリコン膜13と合金化する材料で形成されていればよい。なお、半導体層は、スパッタ法、LPCVD法、またはプラズマCVD法等を用いて形成することができる。

#### 【0034】

また、サイドウォール絶縁層12は、熱CVD法、プラズマCVD法、スパッタリング法等により絶縁表面を有する基板10上に形成された、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む材料からなる膜や、有機樹脂などの有機材料を含む材料からなる膜を单層又は積層した絶縁膜をエッチングすることにより形成することができる。

#### 【0035】

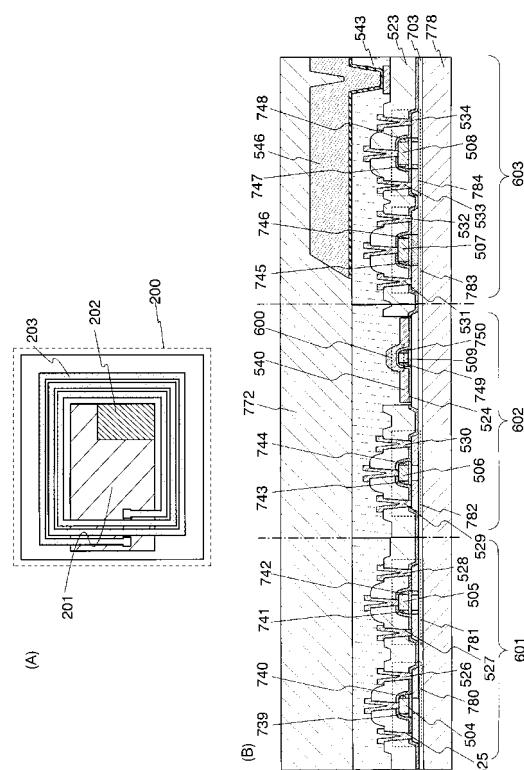

図1に示したメモリ素子は、例えば図2に示すような外部と無線通信が可能な無線チップのメモリ部に用いることができる。

#### 【0036】

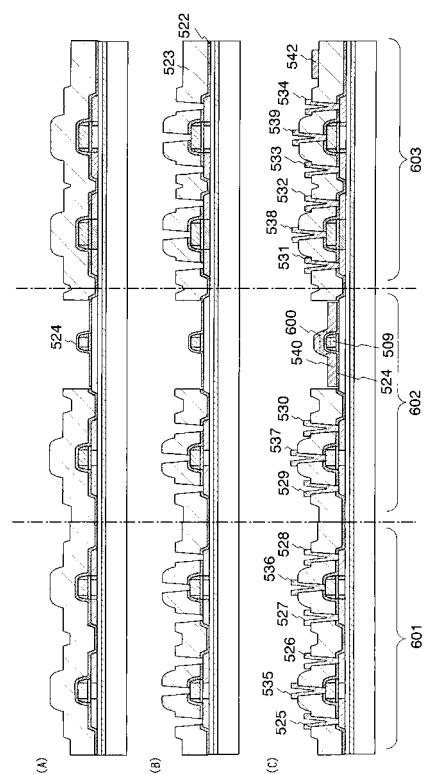

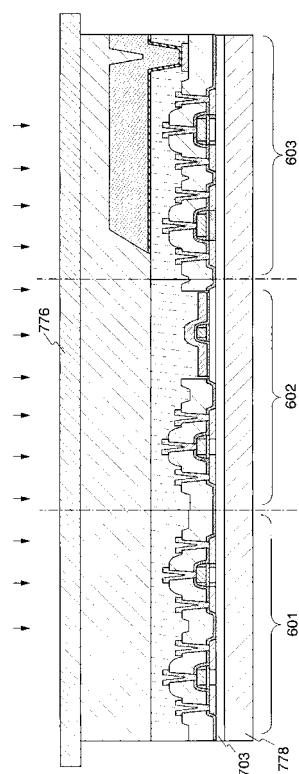

無線チップ200は、駆動回路部201、複数のメモリ素子を有するメモリ部202、アンテナ部及び電源回路部203を有している(図2(A))。なお、図2(B)において、駆動回路部601は図2(A)の駆動回路部201の断面構造の一部に対応し、メモリ部602は図2(A)のメモリ部202の断面構造の一部に対応し、アンテナ部及び電源回路部603は図2(A)のアンテナ部及び電源回路部203の断面構造の一部に対応している。なお、図2においてメモリ部はメモリ素子を複数有し、またメモリ部および駆動

10

20

30

40

50

回路部は薄膜トランジスタ（TFT）やコンデンサ等の素子を複数有することはいうまでもない。

#### 【0037】

本実施の形態に示す無線チップは、メモリ部602において絶縁表面を有する基板778上に形成された第1の電極509と、第1の電極509の側壁部に形成されたサイドウォール絶縁層749、750と、第1の電極509上及びサイドウォール絶縁層749、750上に形成されたシリコン膜524と、シリコン膜524上に形成された第2の電極540と、を有するメモリ素子600を複数有する（図2（B））。また、基板778上に絶縁層703を介して設けられた薄膜トランジスタ（TFT）780～784と、薄膜トランジスタ（TFT）780～784の側壁に設けられたサイドウォール絶縁層739～748と、薄膜トランジスタ780～784上に設けられた絶縁膜523と、当該絶縁膜523上に設けられたソース電極又はドレイン電極525～534とを有する。

10

#### 【0038】

なお、本実施の形態において、薄膜トランジスタ（TFT）780～784のゲート電極504～508と第1の電極509とは、同一工程で作製されており、ソース電極又はドレイン電極525～534と第2の電極540とは、同一工程で作製されている。つまり、ゲート電極504～508と第1の電極509とは、同じ材料で形成されており、ソース電極又はドレイン電極525～534と第2の電極540とは、同じ材料で形成されている。また、薄膜トランジスタ（TFT）780～784の側壁部に設けられたサイドウォール絶縁層739～748と、第1の電極509の側壁に形成されたサイドウォール絶縁層749、750とは、同一工程で形成されている。

20

#### 【0039】

このように、トランジスタのゲート電極とメモリ素子の第1の電極とを同一工程で形成することで、ゲート電極の側壁部に形成されるサイドウォール絶縁層と第1の電極の側壁部に形成されるサイドウォール絶縁層とを工程数を増加させることなく同時に形成することができる。

#### 【0040】

また、本実施の形態に示す無線チップは、ソース電極又はドレイン電極525～534及び第2の電極540上に形成された絶縁膜543と、絶縁膜543上に形成されたアンテナ546と、絶縁膜543及びアンテナ546を覆うように設けられた絶縁層772とを有している。なお、本実施の形態において、第1の電極509又は第2の電極540の少なくとも一方は、シリコン膜524と合金化する材料で形成されている。

30

#### 【0041】

本実施の形態に示すメモリ素子は、第1の電極の側壁部にサイドウォール絶縁層が設けられているため、第1の電極とシリコン膜とが直接接しない構造とすることができる。それにより、基板と第1の電極との段差部分にシリコン膜及び第2の電極を形成した場合でも、段差部分において第1の電極とシリコン膜とが接触せず、第1の電極の上面部分だけがメモリ素子として機能する。第1の電極の上面に形成されるシリコン膜の膜厚は均一であるため、メモリ素子の書き込み特性のばらつきを低減することができる。

#### 【0042】

また、トランジスタのゲート電極とメモリ素子の第1の電極とを同一工程で形成することで、ゲート電極の側壁部に形成されるサイドウォール絶縁層と第1の電極の側壁部に形成されるサイドウォール絶縁層とを同時に形成することができる。従って、工程数を増加させることなく、メモリ素子の書き込み特性が安定した半導体装置を作製することが可能である。また、ワード線やビット線となる配線の交点部分にメモリ素子を作製しても書き込み特性のばらつきを抑えることができるため、半導体装置の小型化が可能である。

40

#### 【0043】

##### （実施の形態2）

本実施の形態において、実施の形態1で示したメモリ素子を有する半導体装置の作製工程について図面を用いて説明する。本実施の形態では、メモリ素子を有する半導体装置の例

50

として外部と無線通信が可能な無線チップについて説明する。

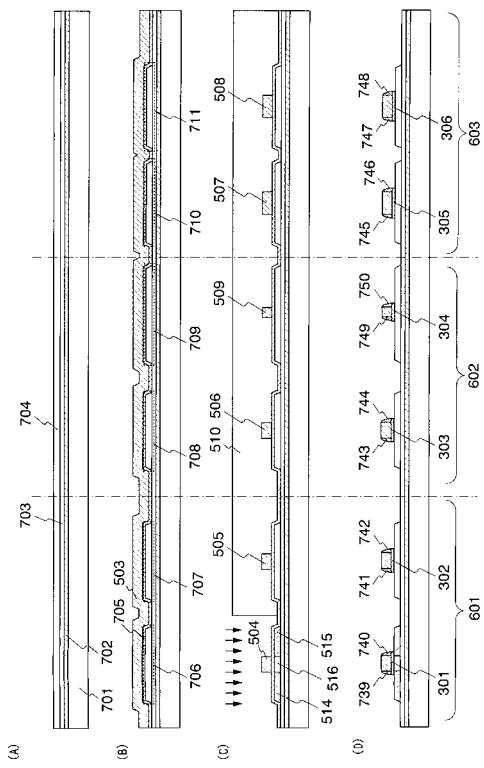

#### 【0044】

まず、第1の基板701の一表面に剥離層702を形成する(図3(A))。第1の基板701は、絶縁表面を有するものであれば特に限定されない。例えば、石英基板、ガラス基板、プラスチック基板等を用いることができる。第1の基板701がガラスからなる場合は、その面積や形状に大きな制限はない。そのため、第1の基板701として、例えば、1辺が1メートル以上あって、矩形状のものを用いれば、生産性を格段に向上させることができる。このような利点は、円形の単結晶シリコン基板を用いる場合と比較すると、大きな優位点である。また、基板701がプラスチックからなる場合、作製工程の処理温度に耐えうる耐熱性のプラスチックを用いる必要がある。なお、後述するが、好適には、ガラスからなる第1の基板701上に薄膜トランジスタを設けた後、当該薄膜トランジスタを剥離して、プラスチックからなる基板上に設けてよい。10

#### 【0045】

なお、本工程では、剥離層702は、第1の基板701の全面に設けているが、必要に応じて、基板701の全面に剥離層を設けた後に、フォトリソグラフィ法を用いて剥離層をエッチングして選択的に設けてよい。また、第1の基板701に接するように剥離層702を形成しているが、必要に応じて、第1の基板701に接するように下地となる絶縁層を形成し、当該絶縁層に接するように剥離層702を形成してもよい。

#### 【0046】

剥離層702は、スペッタリング法やプラズマCVD法等により、タンゲステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(Nb)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、珪素(Si)等から選択された元素または前記元素を主成分とする合金材料若しくは化合物材料からなる層を、単層又は積層して形成する。20

#### 【0047】

次いで、剥離層702の表面を酸化させて酸化金属層を形成してもよい。酸化金属層の形成方法は、純水やオゾン水を用いて表面を酸化して形成してもよいし、酸素プラズマで酸化して形成してもよい。また、酸素を含む雰囲気で加熱を行って酸化金属層を形成してもよい。また、後の絶縁膜の形成工程で形成してもよい。この場合、絶縁膜として酸化珪素膜や酸化窒化珪素膜をプラズマCVD法で形成する際に、剥離層702表面が酸化されて酸化金属層を形成することができる。30

#### 【0048】

次に、剥離層702を覆うように、下地となる絶縁層703を形成する。絶縁層703は、スペッタリング法やプラズマCVD法等により、珪素の酸化物又は珪素の窒化物を含む材料からなる膜を、単層又は積層で形成する。珪素の酸化物材料とは、珪素(Si)と酸素(O)を含む物質であり、酸化珪素、窒素を含む酸化珪素等が該当する。珪素の窒化物材料とは、珪素と窒素(N)を含む物質であり、窒化珪素、酸素を含む窒化珪素等が該当する。下地となる絶縁層は、第1の基板701からの不純物の侵入を防止するプロッキング膜として機能する。代表的な一例は2層構造から成り、PCVD法によりSiH<sub>4</sub>、NH<sub>3</sub>、及びN<sub>2</sub>Oを反応ガスとして成膜される窒化酸化珪素膜を50~100nm、SiH<sub>4</sub>、及びN<sub>2</sub>Oを反応ガスとして成膜される酸化窒化珪素膜を100~150nmの厚さに積層形成する構造が採用される。なお、絶縁層703の一層として膜厚100nm以下の窒化シリコン膜(SiN膜)、或いは窒化酸化珪素膜(SiN<sub>x</sub>O<sub>y</sub>膜(X>Y))を用いることが好ましい。また、窒化酸化珪素膜と、酸化窒化珪素膜と、窒化シリコン膜とを順次積層した3層構造を用いてもよい。なお、特に必要でなければ絶縁層703は設ける必要はない。40

#### 【0049】

次に、絶縁層703上に、非晶質半導体層704を形成する。非晶質半導体層704は、スペッタリング法、LPCVD法、プラズマCVD法等により形成する。なお、プラズマ50

CVD法を用いれば、絶縁層703と、非晶質半導体層704とを大気に触れることなく連続的に積層することができる。非晶質半導体層の厚さは25~80nm（好ましくは30~70nm）の厚さで形成するとよい。続いて、非晶質半導体層704を結晶化法（レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法とレーザ結晶化法を組み合わせた方法等）により結晶化して、結晶質半導体層を形成する。その後、得られた結晶質半導体層を所望の形状にエッチングして、結晶質半導体層706~711を形成する（図3（B））。

#### 【0050】

ここで、結晶質半導体層706~711の作成工程の一例について以下に説明する。まず

10

、プラズマCVD法を用いて、絶縁層703上に非晶質半導体層704を形成する。次に、結晶化を助長する金属元素であるニッケルを含む溶液を非晶質半導体層上に保持させた後、非晶質半導体層に脱水素化の処理（500、1時間）と、熱結晶化の処理（550

、4時間）を行って結晶質半導体層を形成する。非晶質半導体層を結晶化して得られた結晶質半導体層上に第1のフォトマスクを用いてレジストマスクを形成した後、結晶質半導体層を所望の形状にエッチングすることにより結晶質半導体層706~711を形成することができる。

#### 【0051】

レーザ結晶化法で結晶質半導体層を形成する場合、気体レーザ又は固体レーザを用いることができる。気体レーザと固体レーザは、連続発振又はパルス発振のどちらでもよい。例えば、Arレーザ、Krレーザ、エキシマレーザなどの気体レーザ、単結晶のYAG、YVO<sub>4</sub>、フォルステライト（Mg<sub>2</sub>SiO<sub>4</sub>）、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶（セラミック）のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、銅蒸気レーザまたは金蒸気レーザのうち一種または複数種から発振されたレーザビームを用いることができる。このようなレーザビームの基本波、及びこれらの基本波の第2高調波から第4高調波のレーザビームを照射することで、大粒径の結晶を得ることができる。

#### 【0052】

なお、単結晶のYAG、YVO<sub>4</sub>、フォルステライト（Mg<sub>2</sub>SiO<sub>4</sub>）、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶（セラミック）のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザ、Arイオンレーザ、またはTi:サファイアレーザは、連続発振をさせることができ可能であり、Qスイッチ動作やモード同期などを行うことによって10MHz以上の発振周波数でパルス発振をさせることも可能である。連続発振レーザ若しくは10MHz以上の周波数で発振するレーザビームを照射することで、結晶化された半導体膜の表面を平坦なものとすることができます。それにより、後の工程で形成するゲート絶縁膜を薄膜化することが可能であり、より薄型の半導体装置を作製することができる。また、ゲート絶縁膜の耐圧を向上させることに寄与することができる。

#### 【0053】

なお、結晶化を助長する金属元素を用いて非晶質半導体層の結晶化を行うと、低温で短時間の結晶化が可能となるうえ、結晶の方向が揃うという利点がある一方、金属元素が結晶質半導体層に残存するためにオフ電流が上昇し、特性が安定しないという欠点がある。そこで、結晶質半導体層上に、ゲッタリングサイトとして機能する非晶質半導体層を形成するとよい。ゲッタリングサイトとなる非晶質半導体層には、リンやアルゴンの不純物元素を含有させる必要があるため、好適には、アルゴンを高濃度に含有させることができ可能なスパッタリング法で形成するとよい。その後、加熱処理（RTA法やファーネスアニール炉を用いた熱アニール等）を行って、非晶質半導体層中に金属元素を拡散させ、続いて、当

10

20

30

40

50

該金属元素を含む非晶質半導体層を除去する。そうすると、結晶質半導体層中の金属元素の含有量を低減又は除去することができる。

#### 【0054】

次いで、レジストマスクを除去する。次いで、必要があればTFTのしきい値を制御するために、微量な不純物元素（ボロンまたはリン）のドーピングを半導体層に対して行う。ここでは、ジボラン（B<sub>2</sub>H<sub>6</sub>）を質量分離しないでプラズマ励起したイオンドープ法を用いる。そして、フッ酸を含むエッチャントで半導体層表面の酸化膜を除去すると同時に半導体層の表面を洗浄するとよい。

#### 【0055】

次に、結晶質半導体層706～710を覆うゲート絶縁層705を形成する（図3（B））。ゲート絶縁層705は、プラズマCVD法やスパッタリング法により、珪素の酸化物又は珪素の窒化物を含む材料からなる膜を、単層又は積層して形成する。なお、ゲート絶縁層は、結晶質半導体層706～710に対し高密度プラズマ処理を行い、表面を酸化又は窒化することで形成しても良い。例えば、He、Ar、Kr、Xeなどの希ガスと、酸素、酸化窒素（NO<sub>2</sub>）、アンモニア、窒素、水素などの混合ガスを導入したプラズマ処理で形成する。この場合のプラズマの励起は、マイクロ波の導入により行うと、低電子温度で高密度のプラズマを生成することができる。この高密度プラズマで生成された酸素ラジカル（OHラジカルを含む場合もある）や窒素ラジカル（NHラジカルを含む場合もある）によって、半導体膜の表面を酸化又は窒化することができる。

#### 【0056】

このような高密度プラズマを用いた処理により、1～20nm、代表的には5～10nmの絶縁膜が半導体膜に形成される。この場合の反応は、固相反応であるため、当該絶縁膜と半導体膜との界面準位密度はきわめて低くすることができる。このような、高密度プラズマ処理は、半導体膜（結晶性シリコン、或いは多結晶シリコン）を直接酸化（若しくは窒化）するため、形成される絶縁膜の厚さは理想的には、ばらつきをきわめて小さくすることができる。加えて、結晶性シリコンの結晶粒界でも酸化が強くされることはないと、非常に好ましい状態となる。すなわち、ここで示す高密度プラズマ処理で半導体膜の表面を固相酸化することにより、結晶粒界において異常に酸化反応をさせることなく、均一性が良く、界面準位密度が低い絶縁膜を形成することができる。よって、より薄く特性のよい半導体装置を作製することが可能である。

#### 【0057】

ゲート絶縁層は、高密度プラズマ処理によって形成される絶縁膜のみを用いても良いし、それにプラズマや熱反応を利用したCVD法で酸化シリコン、酸窒化シリコン、窒化シリコンなどの絶縁膜を堆積し、積層させても良い。いずれにしても、高密度プラズマで形成した絶縁膜をゲート絶縁層の一部又は全部に含んで形成されるトランジスタは、特性のばらつきを小さくすることができる。よって、より薄く特性のよい半導体装置を作製することが可能である。

#### 【0058】

また、半導体膜の結晶化の際に半導体膜に対し、連続発振レーザ若しくは10MHz以上の周波数で発振するレーザビームを照射しながら一方向に走査して結晶化させて得られた結晶質半導体層706～711は、そのビームの走査方向に結晶が成長する特性がある。その走査方向をチャネル長方向（チャネル形成領域が形成されたときにキャリアが流れる方向）に合わせてトランジスタを配置し、上記ゲート絶縁層を組み合わせることで、特性ばらつきが小さく、しかも電界効果移動度が高いトランジスタ（TFT）を得ることができる。

#### 【0059】

次に、ゲート絶縁層705上に、プラズマCVD法やスパッタリング法により導電層503を形成する。次に、フォトリソグラフィ法により、第2のフォトマスクを用いてレジストマスクを形成し、ゲート電極とゲート線を形成するためのエッチング処理を行って、ゲート電極504～508、及びメモリ素子の下部電極となる第1の電極509を形成する

10

20

30

40

50

(図3(C))。

#### 【0060】

ゲート電極504～508、及び第1の電極509の上層側の材料としては、シリコンと合金化する材料を用いることが好ましく、Ti、W、Ni、Cr、Mo、Ta、Co、Zr、V、Pd、Hf、Pt、Feから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料の単層、またはこれらの積層で形成することができる。ただし、薄膜トランジスタ(TFT)のゲート電極としては高融点金属が好ましいため、WまたはMoを用いるのが好ましい。ゲート電極504～508、及び第1の電極509を積層とする場合には、上層となる材料層が上述した材料であれば、下層となる材料層は特に限定されず、リン等の不純物元素をドーピングした多結晶シリコン層としてもよい。

10

#### 【0061】

なお、後に形成されるメモリ素子の第2の電極(上部電極)をシリコンと合金化する材料を用いて形成する場合、ゲート電極504～508、及び第1の電極509の材料は特に限定されない。例えば、ゲート電極504～508、及び第1の電極509は、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、等から選択された元素又はこれらの元素を主成分とする合金材料若しくは化合物材料で形成することができる。または、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成することができる。第1の導電層と第2の導電層の組み合わせの例を挙げると、窒化タンタルからなる層とタンゲステンからなる層、窒化タンゲステンからなる層とタンゲステンからなる層、窒化モリブデンからなる層とモリブデンからなる層等が挙げられる。タンゲステンや窒化タンタルは、耐熱性が高いため、第1の導電層と第2の導電層を形成した後に、熱活性化を目的とした加熱処理を行うことができる。また、2層構造ではなく、3層構造の場合は、モリブデンからなる層とアルミニウムからなる層とモリブデンからなる層の積層構造を採用するといい。

20

#### 【0062】

次いで、nチャネル型TFTとする結晶質半導体層707～711を覆うように第3のフォトマスクを用いてレジストマスク510を形成し、pチャネル型TFTとする領域の半導体層にゲート電極504をマスクとして不純物元素を導入することによりp型を示す不純物領域を形成する(図3(C))。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。ここでは、pチャネル型TFTとする領域の半導体層にボロン(B)を $1 \times 10^{19} \sim 1 \times 10^{20} / \text{cm}^3$ の濃度で含まれるように導入することによって、p型を示す不純物領域を形成することができる。その結果、pチャネル型TFTとする領域の半導体層に、ソース領域又はドレイン領域514、515、及びチャネル形成領域516が形成される。

30

#### 【0063】

次に、ゲート絶縁層705、ゲート電極504～508、及び第1の電極509を覆うように絶縁層を形成する。絶縁層は、プラズマCVD法やスパッタリング法により、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む材料からなる膜や、有機樹脂などの有機材料を含む材料からなる膜を、単層又は積層して形成する。

40

#### 【0064】

次に、絶縁層を垂直方向を主体とした異方性エッチングにより選択的にエッチングして、ゲート電極504～508の側面に接するサイドウォール絶縁層739～748、及び第1の電極509の側面に接するサイドウォール絶縁層749～750を形成する(図3(D))。なお、サイドウォール絶縁層739～750は、ゲート電極504～508又は第1の電極509と接しない面において湾曲している。また、サイドウォール絶縁層739～751の作成と同時に、ゲート絶縁層705をエッチングして絶縁層301～306を形成する。サイドウォール絶縁層739～748は、後にLDD(Lightly Doped drain)領域を形成する際のドーピング用のマスクとして用いる。

#### 【0065】

50

次いで、pチャネル型TFTとする結晶質半導体層706及びメモリ素子の下側に形成された結晶質半導体層709を覆うように第4のフォトマスク511を用いてレジストマスクを形成し、nチャネル型TFTとする領域の結晶質半導体層707、708、710、711にゲート電極505～508及びサイドウォール絶縁層741～744、745～748をマスクとして不純物元素を導入することにより、第1の不純物領域（LDD領域ともよぶ）727、729、731、733と、第2の不純物領域726、728、730、732とを形成する（図4（A））。ここで、第1の不純物領域727、729、731、733の不純物元素の濃度は、第2の不純物領域726、728、730、732の不純物元素の濃度よりも低い。ここでは、nチャネル型TFTとする領域の半導体層にリン（P）を $1 \times 10^{19} \sim 1 \times 10^{20} / \text{cm}^3$ の濃度で含まれるように導入することによって、n型を示す高濃度不純物領域を形成することができる。その結果、nチャネル型TFTとする領域の半導体層に、ソース領域又はドレイン領域として機能する第2の不純物領域726、728、730、732、LDD領域として機能する第1の不純物領域727、729、731、733、及びチャネル形成領域401～404が形成される。なお、サイドウォール絶縁層の下方にLDD領域が形成されている。

10

#### 【0066】

なお、本実施の形態では、nチャネル型TFTに含まれる半導体層にLDD領域を形成し、pチャネル型TFTに含まれる半導体層にLDD領域を設けない構造を示したが、もちろんこれに限られず、nチャネル型TFT及びpチャネル型TFTの両方の半導体層にLDD領域を形成してもよいし、両方の半導体層にLDDを設けない構成としてもよい。

20

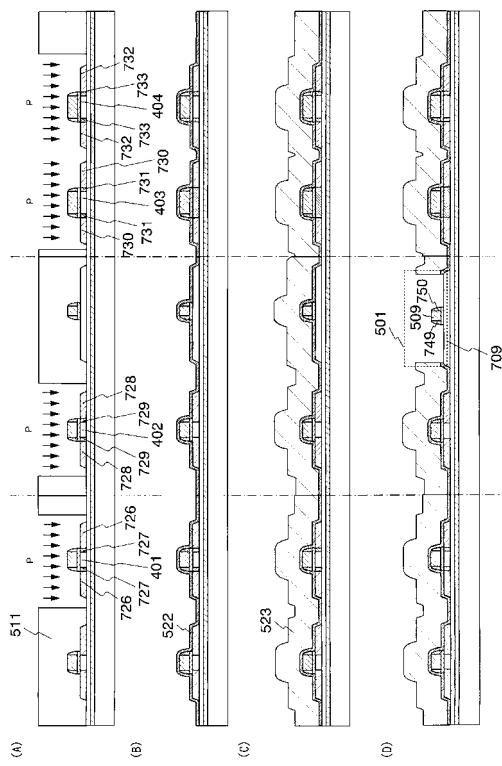

#### 【0067】

次いで、レジストマスクを除去し、ゲート電極及び半導体層上に絶縁膜522を形成する（図4（B））。絶縁膜522としては、SOG法、液滴吐出法等により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ、シロキサン等の有機材料等により、単層又は積層で形成する。シロキサンとは、Si-O-Si結合を含む樹脂に相当する。シロキサンは、シリコン（Si）と酸素（O）との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基（例えばアルキル基、芳香族炭化水素）が用いられる。また、置換基として、フルオロ基を用いてもよい。また、絶縁膜522を形成した後、半導体層に添加された不純物元素の活性化処理および水素化処理を行ってもよい。不純物元素の活性化処理および水素化処理は、炉での熱処理（300～550で1～12時間の熱処理）または、ランプ光源を用いたラピッドサーマルアニール法（RTA法）を用いる。例えば、絶縁膜522は、PCVD法により得られる膜厚は50nm～200nmの窒化酸化珪素膜（SiNO膜）を用いることができる。加えて、結晶化を助長する金属元素、代表的にはニッケルを用いて半導体膜を結晶化させている場合、活性化と同時にチャネル形成領域におけるニッケルの低減を行うゲッタリングを行なうことができる。なお、絶縁膜522は層間絶縁膜の1層目である。

30

#### 【0068】

次いで、スパッタ法、LPCVD法、またはプラズマCVD法等を用いて層間絶縁膜の2層目となる絶縁膜523を形成する（図4（C））。絶縁膜523としては、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜の単層または積層を用いる。ここでは絶縁膜523の膜厚は300nm～800nmとする。

40

#### 【0069】

次いで、絶縁膜523上に第5のフォトマスクを用いてレジストマスクを形成し、選択的に絶縁膜522及び絶縁膜523をエッチングして、第1の電極509、サイドウォール絶縁層749～750、及び結晶質半導体層709の一部を露出する第1の開口501を形成する（図4（D））。第1の開口501形成後にレジストマスクは除去する。

#### 【0070】

次いで、スパッタ法、LPCVD法、またはプラズマCVD法等を用いて、第1の電極509、サイドウォール絶縁層749～750、及び結晶質半導体層709上にシリコン膜

50

を形成する。シリコン膜は、アモルファスシリコン膜、微結晶シリコン膜、または多結晶シリコン膜のいずれか一を用いて膜厚10nm～200nm程度で形成する。本実施の形態では、プラズマCVD法を用いて100nmの膜厚を有するアモルファスシリコン膜を成膜する。次いで、アモルファスシリコン膜上に第6のフォトマスクを用いてレジストマスクを形成し、選択的にアモルファスシリコン膜をエッチングし、シリコン膜524を形成する(図5(A))。エッチング後にレジストマスクは除去する。なお、第1の電極509、サイドウォール絶縁層749～750、及び結晶質半導体層709上に形成する膜はシリコン膜に限定されず、第1の電極509又は第2の電極540の少なくとも一方と合金化する材料からなる半導体層であればよい。例えば、シリコン(Si)、ゲルマニウム(Ge)などの単体の半導体のほかGaAs、InP、SiC、ZnSe、GaN、SiGeなどのような化合物半導体、又は酸化亜鉛(ZnO)、酸化スズ(SnO<sub>2</sub>)などの酸化物半導体等を用いることができる。

10

#### 【0071】

次いで、絶縁膜523上に第7のフォトマスクを用いてレジストマスクを形成し、選択的に絶縁膜522及び絶縁膜523をエッチングして、半導体層に達するコンタクトホール、ゲート電極に達するコンタクトホールをそれぞれ形成する(図5(B))。そして、エッチング後にレジストマスクは除去する。

#### 【0072】

次いで、フッ酸を含むエッチャントで露呈している半導体層表面及び露呈しているゲート電極表面の酸化膜を除去すると同時に露呈している半導体層の表面及び露呈している第1の電極表面を洗浄するとよい。

20

#### 【0073】

次いで、絶縁膜523上にスパッタ法を用いて導電膜を形成する。この導電膜は、後工程でエッチングすることにより、メモリ素子の第2の電極540、駆動回路部601のTFTの配線、メモリ部602のTFTの配線、又はアンテナ部及び電源回路部603のTFTの配線となる。導電膜として、例えばTi、W、Ni、Cr、Mo、Ta、Co、Zr、V、Pd、Hf、Pt、Fe、Al、Cuから選ばれた元素からなる金属材料、または前記元素を主成分とする合金材料若しくは化合物材料の単層膜、またはこれらの積層膜で形成することができる。ただし、メモリ素子の下部電極となる第1の電極509をシリコン膜524と合金化する材料で形成した場合、該導電膜の材料は特に限定されない。

30

#### 【0074】

また、導電膜を積層する場合は、少なくともシリコン膜524と接する一層は、シリコンと合金化する材料を用いる。例えば、Ti膜と、Siを微量に含むAl膜と、Ti膜との3層構造、或いはTi膜と、NiとCを含むAl合金膜と、Ti膜との3層構造を用いる。本実施の形態では、膜厚100nmのTi膜と、膜厚350nmの純Al膜と、膜厚100nmのTi膜との3層積層とする。

#### 【0075】

次いで、導電層上に第8のフォトマスクを用いてレジストマスクを形成し、選択的に導電膜をエッチングして、ソース電極またはドレイン電極525～534、ゲート引出配線535～539、メモリ素子の第2の電極540、アンテナ部の接続電極542を形成する(図5(C))。第2の電極540はシリコン膜524と重なりメモリ素子の上部電極となる。なお、ここでは図示しないが、接続電極542は、アンテナ部及び電源回路部のTFTと電気的に接続している。そして、エッチング後にレジストマスクを除去する。これにより、第1の電極509上に形成されたシリコン膜524、シリコン膜524上に形成された第2の電極540を有するメモリ素子600を得ることができる。

40

#### 【0076】

なお、ここで結晶質半導体層709は、シリコン膜524及び第2の電極540をエッチングする際に、下地層までエッチングされるのを防ぐためのエッチングストッパーである。また、本実施の形態においては、シリコン膜524をエッチングしてから第2の電極540を形成しているが、シリコン膜及び導電層を連続して形成した後で、エッチングする

50

ことにより同時にシリコン膜 524 及び第 2 の電極 540 を形成してもよい。これにより、フォトマスクを 1 枚減らすことができ、工程を削減することができる。

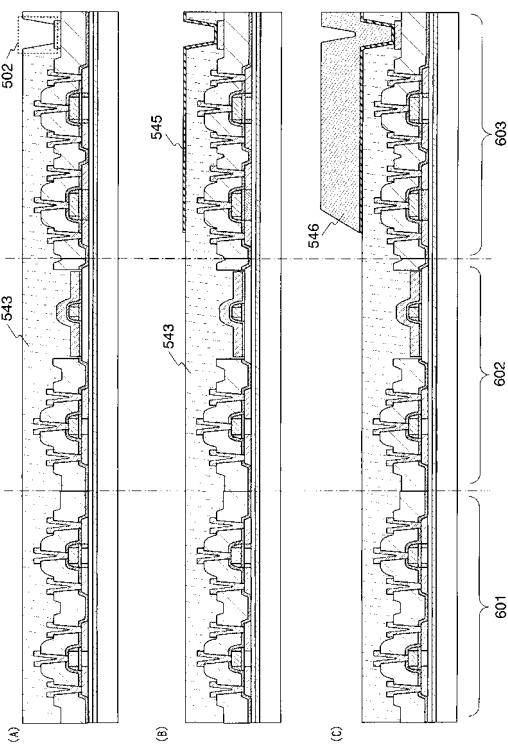

#### 【0077】

次いで、駆動回路部 601 の TFT と、メモリ部 602 の TFT 及びメモリ素子と、アンテナ部及び電源回路部 603 の TFT を覆う絶縁膜 543 を形成する。絶縁膜 543 は、酸化シリコンを含む絶縁膜または有機樹脂膜を用いる。無線チップの信頼性を向上させる上では酸化シリコンを含む絶縁膜を用いることが好ましい。また、後に形成するアンテナをスクリーン印刷法で形成する場合には平坦面を有していることが望ましいため、塗布法を用いる有機樹脂膜を用いることが好ましい。絶縁膜 543 は、実施者が適宜、選択すればよい。また、本実施例では後に形成するアンテナが駆動回路及びメモリ部と重なる例を示しているため、絶縁膜 543 は、アンテナとの絶縁を図る層間絶縁膜として機能している。輪状(例えば、ループアンテナ)又はらせん状のアンテナとする場合には、アンテナの両端のうち一方を下層の配線で引き回すため、絶縁膜 543 を設けることが好ましい。ただし、マイクロ波方式を適用し、線状(例えば、ダイポールアンテナ)、平坦な形状(例えば、パッチアンテナ)等のアンテナとする場合には、後に形成するアンテナが駆動回路及びメモリ部と重ならないように配置できるため、絶縁膜 543 は特に設けなくともよい。

10

#### 【0078】

次いで、絶縁膜 543 上に第 9 のフォトマスクを用いてレジストマスクを形成し、選択的に絶縁膜 543 をエッティングして、接続電極 542 に達する第 2 の開口 502 を形成する(図 6(A))。そして、エッティング後にレジストマスクは除去する。

20

#### 【0079】

次いで、絶縁膜 543 上にアンテナの下地膜 545 を形成する(図 6(B))。絶縁膜 543 上に、Ti、Ni、Au から選ばれる単層またはそれらの積層の金属膜を形成し、該金属膜上に第 10 のフォトマスクを用いてレジストマスクを形成して、選択的に金属膜をエッティングすることにより、アンテナの下地膜 545 を形成することができる。なお、ここでの下地膜 545 は、レジストマスクを用いることなく、メタルマスクを用いたスパッタ法で選択的に形成することもできる。アンテナの下地膜 545 は必ずしも設ける必要はないが、下地膜 545 を設けることでアンテナとの接触面積を広く確保することができる。

30

#### 【0080】

次いで、下地膜 545 上にアンテナ 546 を形成する。アンテナ 546 はスパッタ法を用いて Al または Ag など金属膜を形成した後、フォトマスクを用いてエッティングする方法、或いはスクリーン印刷法を用いることができる。フォトマスク数を削減することを優先するのであれば、スクリーン印刷法を用いてアンテナを形成すればよい。スクリーン印刷法とは、金属あるいは高分子化合物纖維のメッシュによりなるベースに所定のパターンが感光性樹脂にて形成されたスクリーン版上にのせたインキもしくはペーストをスキージと呼ばれるゴム、プラスチック、或いは金属のブレードを用いてスクリーン版の反対側に置かれたワークに転写する方法である。スクリーン印刷法は、比較的大面積でのパターン形成が低コストで実現することができるメリットを有している。

40

#### 【0081】

以上の工程により、同一基板上に駆動回路部 601 の TFT と、メモリ部 602 の TFT 及びメモリ素子 600 と、アンテナ部及び電源回路部 603 の TFT 及びアンテナとを形成することができる。

#### 【0082】

なお、本実施の形態では、フォトマスクを用いてレジストマスクを形成する例を示したが、特に限定されず、フォトマスクを用いることなくレジスト材料を液滴吐出法で選択的に形成してレジストマスクを形成してもよい。

#### 【0083】

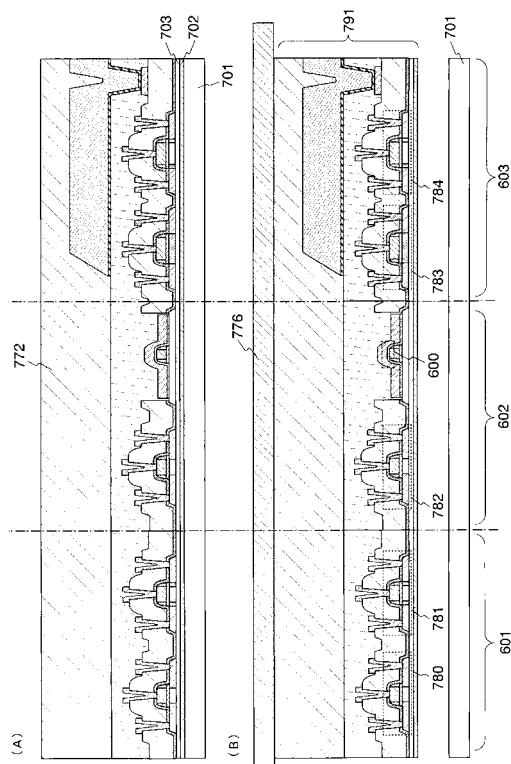

次に、駆動回路部 601 の TFT と、メモリ部 602 の TFT 及びメモリ素子 600 と、

50

アンテナ部及び電源回路部 603 の TFT 及びアンテナとを覆うように絶縁層 772 を形成する(図 7(A))。絶縁層 772 は、後に記載する剥離工程において TFT を含む素子形成層への損傷を抑える機能を有する材料であれば特に制限されるものではないが、好ましくは樹脂(より好ましくはエポキシ樹脂)により形成する。絶縁層 772 としてエポキシ樹脂を用いることにより、絶縁層 772 表面の平坦性が向上し、後の剥離工程において TFT を含む素子形成層への損傷を低減し、かつ絶縁層 772 の下層の記憶素子部や素子形成層をほこり等から保護し、半導体装置の機械的強度を保つことが可能である。

#### 【0084】

なお、本実施の形態では、薄膜トランジスタ 780 ~ 784、メモリ素子 600 を含む層を素子形成層 791 とよぶ。また、アンテナ 546 の下方に位置する層(基板 701 を除く)の厚さは、5 μm 以下、好ましくは 0.1 μm ~ 3 μm の厚さを有するように形成するとよい。なお、ここでは図示しないが、素子形成層 791 には、ダイオード、TFT、コンデンサ、抵抗素子などが形成されていてもよい。

10

#### 【0085】

なお、図 7 は 1 つの無線チップの一部分であり、ここでは図示していないが、無数の無線チップが基板 701 に形成されている。そこで、それぞれの無線チップを切り分けるために、剥離層 702 の表面の一部が露出するように、ダイサー、レーザー、ワイヤソーなどにより開口部を形成する。次に、剥離層 702 の表面の一部が露出した開口部にエッチング剤を導入して、剥離層 702 を除去する。エッチング剤は、フッ化ハロゲンを含む気体又は液体を使用することができる。例えば、三フッ化塩素(CF<sub>3</sub>)、三フッ化窒素(NF<sub>3</sub>)、三フッ化臭素(BrF<sub>3</sub>)、フッ化水素(HF)がある。なお、エッチング剤として、フッ化水素を使用する場合は、剥離層 702 として、酸化珪素からなる層を用いる。

20

#### 【0086】

また、絶縁層 772 は、剥離層 702 を除去した後に、薄膜トランジスタ 780 ~ 784 を含む素子形成層 791 が分離しないように設けたものである。薄膜トランジスタ 780 ~ 784 を含む素子形成層 791 の開口部で分断された各無線チップは小さく薄く軽いために、剥離層 702 をエッチングした後は、第 1 の基板 701 との密着性が低下するために飛散しやすい。しかしながら、薄膜トランジスタ 780 ~ 784 を含む素子形成層 791 上に絶縁層 772 を形成することで、薄膜トランジスタ 780 ~ 784 を含む素子形成層 791 に重みが付き、基板 701 から素子形成層 791 の開口部で分断された各無線チップ部分の飛散を防止することができる。また、薄膜トランジスタ 780 ~ 784 を含む素子形成層 791 単体では薄くて軽いが、絶縁層 772 を形成することで、素子形成層 791 が巻かれた形状になることがなく、ある程度の強度を確保することができる。

30

#### 【0087】

次に、絶縁層 772 をシート材 776 に接着させて、第 1 の基板 701 から薄膜トランジスタ 780 ~ 784 を含む素子形成層 791 を完全に剥離する(図 7(B))。ここで、シート材 776 は、通常の状態ではその接着力が強く、熱を加えたり、光を照射することによりその接着力が弱くなる性質を有するものを用いるとよい。例えば、加熱することにより接着力が弱くなる熱剥離テープや、紫外光を照射することにより接着力が弱くなる UV 剥離テープ等を用いるとよい。また、通常の状態で接着力が弱い弱粘性テープ等を用いてもよい。なお、薄膜トランジスタ 780 ~ 784 を含む素子形成層 791 が剥離された後の基板 701 は、コストの削減のために、再利用するとよい。

40

#### 【0088】

次に、絶縁層 703 と基板 778 とを固定する。ここで、基板 778 は、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなるフィルム、繊維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム、紙類等)と接着性合成樹脂フィルム(アクリル系合成樹脂、エポキシ系合成樹脂等)との積層フィルムなどを用いることができる。基板 778 がプラスチックからなる場合、薄型、軽量で、曲げることが可能であるためデザイン性に優れ、フレキシブルな形状を有する装置

50

への加工が容易である。また、耐衝撃性に優れ、様々な物品に貼り付けたり、埋め込んだりすることが容易であり、多種多様な分野で活用することができる。

#### 【0089】

また、本実施の形態において、基板778の絶縁層703側の表面には接着層が設けられている。接着層は、熱硬化樹脂、紫外線硬化樹脂、酢酸ビニル樹脂系接着剤、ビニル共重合樹脂系接着剤、エポキシ樹脂系接着剤、ウレタン樹脂系接着剤、ゴム系接着剤、アクリル樹脂系接着剤等の接着剤を含む層に相当する。

#### 【0090】

なお、基板778の表面は、二酸化珪素(シリカ)の粉末により、コーティングされていてよい。コーティングにより、高温で高湿度の環境下においても防水性を保つことができる。また、その表面は、インジウム錫酸化物等の導電性材料によりコーティングされていてよい。コーティングした材料が静電気をチャージし、薄膜集積回路を静電気から保護することができる。また、その表面は、炭素を主成分とする材料(例えば、ダイヤモンドライクカーボン)によりコーティングされていてよい。コーティングにより強度が増し、半導体装置の劣化や破壊を抑制することができる。

#### 【0091】

次に、薄膜トランジスタ780～784を含む素子形成層791を有する基板778とシート材776とを分離する。ここでは、シート材776としてUV剥離テープを用いる場合を説明する。まず、シート材776と絶縁層772との接着力を弱めるためにシート材776に紫外光を照射する(図8)。次に、シート材776を絶縁層772から分離する。

#### 【0092】

以上の工程により、図2(B)に示すような半導体装置を作製することができる。

#### 【0093】

次いで、無線チップをシート状の基体に固定する。シート状の基体としては、プラスチック、紙、プリプレグ、セラミックシートなどを用いることができる。2枚のシート状の基体に無線チップを挟むように固定してもよいし、1枚のシート状の基体に接着層で固定してもよい。接着層としては、反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。また、紙の形成途中に無線チップを配置して、1枚の紙の内部に無線チップを設けることもできる。

#### 【0094】

以上の工程を経た無線チップは、無線チップ製造後に書き込みをいつでも行える追記型のメモリを実現できる。例えば、フレキシブルなシート状の基体に固定した無線チップを曲面を有する物品に貼り付けた後、その無線チップに含まれるアンチヒューズROMに対してデータの書き込みを行うことができる。

#### 【0095】

本実施の形態に示す半導体装置は、メモリ素子部の第1の電極の側壁部にサイドウォール絶縁層が設けられているため、基板と第1の電極との段差部分において第1の電極とシリコン膜とが直接接しない構造とすることができる。それにより、基板と第1の電極との段差部分にシリコン膜及び第2の電極を形成した場合でも、段差部分において第1の電極とシリコン膜とが接触せず、第1の電極の上面部分だけがメモリ素子として機能する。第1の電極の上面に形成されるシリコン膜の膜厚は均一であるため、メモリ素子の書き込み特性のばらつきを低減することができる。

#### 【0096】

また、トランジスタのゲート電極とメモリ素子の第1の電極とを同一工程で形成することで、ゲート電極の側壁部に形成されるサイドウォール絶縁層と第1の電極の側壁部に形成されるサイドウォール絶縁層とを同時に形成することができる。従って、工程数を増加させることなく、メモリ素子の書き込み特性が安定した半導体装置を作製することが可能である。また、ワード線やビット線となる配線の交点部分にメモリ素子を作製しても書き込

10

20

30

40

50

み特性のばらつきを抑えることができるため、半導体装置の小型化が可能である。

【0097】

(実施の形態3)

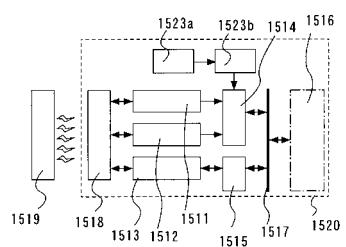

本発明を用いた半導体装置の構成例について、図9を参照して説明する。図9に示すように、本発明の半導体装置1520は、非接触でデータを交信する機能を有し、電源回路1511、クロック発生回路1512、データ復調/変調回路1513、他の回路を制御する制御回路1514、インターフェイス回路1515、記憶回路1516、データバス1517、アンテナ1518、センサ1523a、センサ回路1523bを有する。図9において、駆動回路とは、電源回路1511、クロック発生回路1512、データ復調/変調回路1513、他の回路を制御する制御回路1514、及びインターフェイス回路1515を指している。

10

【0098】

電源回路1511は、アンテナ1518から入力された交流信号を基に、半導体装置1520の内部の各回路に供給する各種電源を生成する回路である。クロック発生回路1512は、アンテナ1518から入力された交流信号を基に、半導体装置1520の内部の各回路に供給する各種クロック信号を生成する回路である。データ復調/変調回路1513は、リーダライタ1519と交信するデータを復調/変調する機能を有する。制御回路1514は、記憶回路1516を制御する機能を有する。アンテナ1518は、電波の送受信を行う機能を有する。リーダライタ1519は、半導体装置との交信、制御及びそのデータに関する処理を制御する。なお、半導体装置は上記構成に制約されず、例えば、電源電圧のリミッタ回路や暗号処理専用ハードウェアといった他の要素を追加した構成であつてもよい。

20

【0099】

記憶回路1516は、実施の形態1に示すようなメモリ部、即ち外部からの電気的作用により合金化するシリコン膜が、側壁部にサイドウォール絶縁層が形成された第1の電極と、第2の電極との間に挟まれた記憶素子を複数有する。なお、記憶回路1516は、側壁部にサイドウォール絶縁層が形成された第1の電極と、第2の電極との間にシリコン膜が挟まれた記憶素子のみを有していてもよいし、他の構成の記憶回路を有していてもよい。他の構成の記憶回路とは、例えば、DRAM、SRAM、FeRAM、マスクROM、PROM、EPROM、EEPROM及びフラッシュメモリから選択される1つ又は複数に相当する。

30

【0100】

センサ1523aは抵抗素子、容量結合素子、誘導結合素子、光起電力素子、光電変換素子、熱起電力素子、トランジスタ、サーミスタ、ダイオードなどの半導体素子で形成される。センサ回路1523bはインピーダンス、リアクタンス、インダクタンス、電圧又は電流の変化を検出し、アナログ/デジタル変換(A/D変換)して制御回路1514に信号を出力する。

【0101】

(実施の形態4)

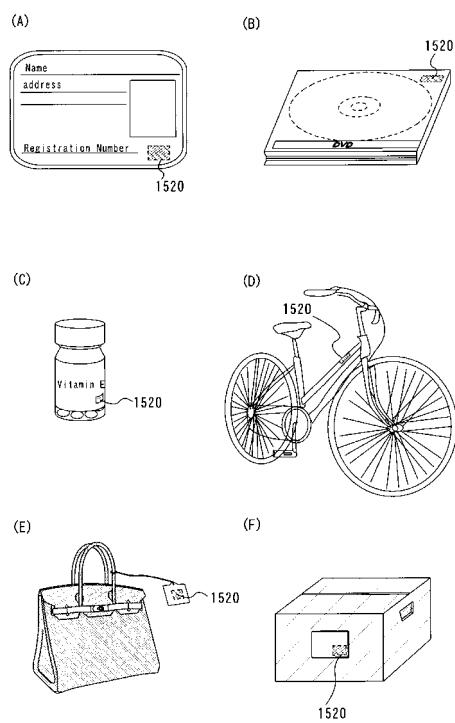

本発明により無線チップとして機能する半導体装置1520を形成することができる。無線チップの用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類(運転免許証や住民票等、図10(A))、包装用容器類(包装紙やボトル等、図10(C))、記録媒体(DVDソフトやビデオテープ等、図10(B))、乗物類(自転車等、図10(D))、身の回り品(鞄や眼鏡等)、食品類、植物類、動物類、衣類、生活用品類、電子機器等の商品や荷物の荷札(図10(E)、図10(F))等の物品に設けて使用することができる。電子機器とは、液晶表示装置、EL表示装置、テレビジョン装置(単にテレビ、テレビ受像機、テレビジョン受像機とも呼ぶ)及び携帯電話等を指す。

40

【0102】

本発明の半導体装置1520は、プリント基板に実装し、物品表面に貼着、物品に埋め込

50

む等して、物品に固定される。例えば、本なら紙に埋め込む、有機樹脂からなるパッケージなら当該有機樹脂に埋め込む等して、各物品に固定される。本発明の半導体装置1520は、小型、薄型、軽量を実現するため、物品に固定した後も、その物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、証書類等に本発明の半導体装置1520を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に本発明の半導体装置を設けることにより、検品システム等のシステムの効率化を図ることができる。

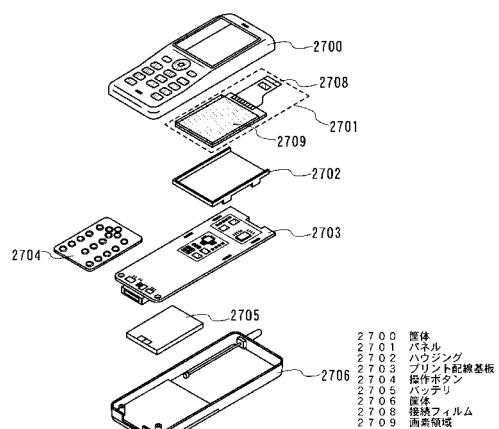

#### 【0103】

次に、本発明の半導体装置を実装した電子機器の一態様について図面を参照して説明する。

10 ここで例示する電子機器は携帯電話機であり、筐体2700、2706、パネル2701、ハウジング2702、プリント配線基板2703、操作ボタン2704、バッテリ2705を有する(図11)。パネル2701はハウジング2702に脱着自在に組み込まれ、ハウジング2702はプリント配線基板2703に嵌着される。ハウジング2702はパネル2701が組み込まれる電子機器に合わせて、形状や寸法が適宜変更される。プリント配線基板2703には、パッケージングされた複数の半導体装置、例えば、コントローラ、中央処理ユニット(CPU、Central Processing Unit)、メモリ、電源回路、音声処理回路、送受信回路等のいずれかの機能を有する半導体装置が実装されている。このうちのメモリとして、本発明の半導体装置を用いることができる。

20

#### 【0104】

パネル2701は、接続フィルム2708を介して、プリント配線基板2703と接着される。上記のパネル2701、ハウジング2702、プリント配線基板2703は、操作ボタン2704やバッテリ2705と共に、筐体2700、2706の内部に収納される。パネル2701が含む画素領域2709は、筐体2700に設けられた開口窓から視認できるように配置されている。

#### 【0105】

上記の通り、本発明の半導体装置は、小型、薄型、軽量であることを特徴としており、上記特徴により、電子機器の筐体2700、2706内部の限られた空間を有効に利用することができる。

30

#### 【0106】

また、本発明の半導体装置は、外部からの電気的作用により合金化するシリコン膜が一対の導電層に挟まれた単純な構造の記憶素子を有するため、安価な半導体装置を用いた電子機器を提供することができる。また、本発明の半導体装置は安定した書き込み特性を有するため、信頼性の高い電子機器を提供することができる。

また、本発明の半導体装置はワード線やビット線となる配線の交点部分にメモリ素子を作製しても書き込み特性のばらつきを抑えることができるため、小型化、高集積化が容易である。それによって、大容量の記憶回路を有する半導体装置を用いた電子機器を提供することができる。

#### 【0107】

また、本発明の半導体装置が有する記憶装置は、外部からの電気的作用によりデータの書き込みを行うものであり、不揮発性であって、データの消去は不可能であるが、データの追記は可能であることを特徴とする。上記特徴により、書き換えによる偽造を防止することができ、新たなデータを追加して書き込むことができる。従って、高機能化と高付加価値化を実現した半導体装置を用いた電子機器を提供することができる。

40

#### 【0108】

なお、筐体2700、2706は、携帯電話機の外観形状を一例として示したものであり、本実施例に係る電子機器は、その機能や用途に応じて様々な態様に変容しうる。

#### 【図面の簡単な説明】

#### 【0109】

10

20

30

40

50

【図1】本発明のメモリ素子の断面を説明する図。

【図2】本発明のメモリ素子を用いた半導体装置の構成例を説明する図。

【図3】本発明のメモリ素子を用いた半導体装置の作製工程の一例を説明する図。

【図4】本発明のメモリ素子を用いた半導体装置の作製工程の一例を説明する図。

【図5】本発明のメモリ素子を用いた半導体装置の作製工程の一例を説明する図。

【図6】本発明のメモリ素子を用いた半導体装置の作製工程の一例を説明する図。

【図7】本発明のメモリ素子を用いた半導体装置の作製工程の一例を説明する図。

【図 8】本発明のメモリ素子を用いた半導体装置の作製工程の一例を説明する図。

【図9】本発明のメモリ素子を用いた半導体装置のブロック図を示す図。

【図10】電子機器の一例を示す図。

10

【図11】電子機器の一例を示す図。

【図12】従来のメモリ素子の断面を説明する図。

### 【符号の説明】

【0110】

10 基板

1 1 電極

12 サイドウォ

13 シリ

1 4 電極

30

【 四 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

(B)

---

フロントページの続き

(56)参考文献 米国特許第05576576(US,A)

特開平06-216254(JP,A)

特開2006-270059(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/10

G06K 19/07

G06K 19/077

H01L 29/786