(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5272265号

(P5272265)

(45) 発行日 平成25年8月28日(2013.8.28)

(24) 登録日 平成25年5月24日(2013.5.24)

(51) Int.Cl.

G06F 13/10 (2006.01)

F 1

G06F 13/10 330C

請求項の数 13 (全 30 頁)

(21) 出願番号 特願2008-250208 (P2008-250208)

(22) 出願日 平成20年9月29日 (2008.9.29)

(65) 公開番号 特開2010-79816 (P2010-79816A)

(43) 公開日 平成22年4月8日 (2010.4.8)

審査請求日 平成23年6月16日 (2011.6.16)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 100114236

弁理士 藤井 正弘

(74) 代理人 100075513

弁理士 後藤 政喜

(74) 代理人 100120260

弁理士 飯田 雅昭

(72) 発明者 馬場 貴成

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所 中央研究所内

(72) 発明者 森木 俊臣

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所 中央研究所内

最終頁に続く

(54) 【発明の名称】 P C I デバイス共有方法

## (57) 【特許請求の範囲】

## 【請求項 1】

仮想化部を備えて 1 以上の仮想サーバを提供する複数の物理サーバと、前記複数の物理サーバで共有される I / O デバイスと、前記複数の物理サーバと前記 I / O デバイスを接続するスイッチと、前記スイッチを初期化する管理部とを有するサーバシステムであって、

前記 I / O デバイスが、

仮想的な機能である Virtual Function (VF) を有し、

前記スイッチが、

前記物理サーバが認識する識別子である第 1 の識別子と、前記管理部が管理する識別子である第 2 の識別子と、の間の対応関係を示す識別子対応情報を保持し、 10

前記物理サーバからパケットを受信した場合に、

送信元の物理サーバを識別するサーバ識別子を含む前記パケットを前記スイッチ内で変換し、

前記パケットを前記 I / O デバイスに送信する際には、前記識別子対応情報に基づいて、前記パケットに含まれる前記第 1 の識別子を、当該第 1 の識別子に前記対応付けられた前記第 2 の識別子に変換し、かつ、前記サーバ識別子を削除した前記パケットを、前記 I / O デバイスに送信する、ことを特徴とするサーバシステム。

## 【請求項 2】

請求項 1 記載のサーバシステムであって、

前記物理サーバは、前記第1の識別子に基づいて、前記仮想サーバから前記VFへのアクセスを管理し、

前記I/Oデバイスは、前記第2の識別子に基づいて、前記仮想サーバから前記VFへのアクセスを管理する、ことを特徴とするサーバシステム。

【請求項3】

請求項1記載のサーバシステムであって、

前記スイッチは、

更に前記物理サーバが認識する前記VFのMMIOアドレス領域情報と、前記管理部が管理する前記VFのMMIOアドレス領域情報との間の対応関係を示すMMIOアドレス対応情報を保持し、

前記物理サーバからパケットを受信した場合に、更に、前記MMIOアドレス対応情報に従って前記パケットの宛先アドレスを変換する処理を行う、ことを特徴とするサーバシステム。

【請求項4】

請求項1記載のサーバシステムであって、

前記I/Oデバイスは、PCI sig規定のSingle Root I/O Virtualization and Sharing Specification (SR-IoV)に準拠、もしくはSR-IoVの上位互換のI/Oデバイスであることを特徴とするサーバシステム。

【請求項5】

仮想化部を備えて1以上の仮想サーバを提供する複数の物理サーバと、仮想的な機能であるVirtual Function (VF)を有して前記複数の物理サーバで共有されるI/Oデバイスと、を接続するスイッチング装置であって、

前記物理サーバと接続する第1のポートと、

前記I/Oデバイスと接続する第2のポートと、

前記物理サーバが認識する識別子である第1の識別子と、前記スイッチを初期化する管理部が管理する識別子である第2の識別子と、の間の対応関係を管理する識別子管理部と、

前記物理サーバにより送信された前記I/Oデバイス宛のパケットの前記I/Oデバイスへの転送を制御する転送制御部と、を備え、

前記第1のポートが前記物理サーバから前記I/Oデバイス宛のパケットを受信した場合に、

前記転送制御部は、送信元の物理サーバを識別するサーバ識別子を含む前記パケットを前記スイッチ内で変換し、

前記パケットを前記第2のポートから前記I/Oデバイスに送信する際には、前記識別子管理部が管理する前記対応関係に基づいて、前記パケットに含まれる前記第1の識別子を、当該第1の識別子に前記対応付けられた前記第2の識別子に変換し、かつ、前記サーバ識別子を削除した前記パケットを、前記I/Oデバイスに送信する、ことを特徴とするスイッチング装置。

【請求項6】

請求項5記載のスイッチング装置であって、

前記第1の識別子は、前記仮想サーバから前記VFへのアクセスの管理のために前記物理サーバが用いる識別子であり、

前記第2の識別子は、前記仮想サーバから前記VFへのアクセスの管理のために前記I/Oデバイスが用いる識別子である、ことを特徴とするスイッチング装置。

【請求項7】

請求項5記載のスイッチング装置であって、

前記物理サーバが認識する前記VFのMMIOアドレス領域情報と、前記管理部が管理する前記VFのMMIOアドレス領域情報との間の対応関係を管理するMMIOアドレス対応関係管理部を、更に有し、

10

20

30

40

50

前記第1のポートが前記物理サーバから前記I/Oデバイス宛のパケットを受信した場合に、

前記転送制御部は、更に、前記MMIOアドレス対応管理部に従って前記パケットの宛先アドレスを変換する処理を行う、ことを特徴とするスイッチング装置。

【請求項8】

仮想化部を備えて1以上の仮想サーバを提供する複数の物理サーバと、I/Oデバイスと、前記複数の物理サーバと前記I/Oデバイスとを接続するスイッチと、前記スイッチを初期化する管理部と、を有するサーバシステムにおいて、前記I/Oデバイスを前記複数の物理サーバ間で共有するI/Oデバイス管理方法であって、

前記I/Oデバイスによって、仮想的な機能であるVirtual Function (VF)を複数生成し、

前記スイッチによって、

前記物理サーバが認識する前記VFの識別子である第1の識別子と、前記管理部が管理する前記VFの識別子である第2の識別子と、の間の対応関係を示す識別子対応情報を管理し、

前記スイッチが前記物理サーバからパケットを受信した場合に、送信元の物理サーバを識別するサーバ識別子(=VHN)を含む前記パケットを前記スイッチ内で変換し、

前記パケットを前記I/Oデバイスに送信する際には、前記識別子対応情報を基づいて、前記パケットに含まれる前記第1の識別子を、当該第1の識別子に前記対応付けられた前記第2の識別子に変換し、かつ、前記サーバ識別子を削除した前記パケットを、前記I/Oデバイスに送信する、ことを特徴とするI/Oデバイス管理方法。

【請求項9】

請求項8記載のI/Oデバイス管理方法であって、

前記第1の識別子に基づいて、前記仮想サーバから前記VFへのアクセスに関して前記物理サーバによる管理を行い、

前記第2の識別子に基づいて、前記仮想サーバから前記VFへのアクセスに関して前記I/Oデバイスによる管理を行う、ことを特徴とするI/Oデバイス管理方法。

【請求項10】

請求項8記載のI/Oデバイス管理方法であって、

前記スイッチによって、

更に前記物理サーバが認識する前記VFのMMIOアドレス領域情報と、前記管理部が管理する前記VFのMMIOアドレス領域情報と、の間の対応関係を示すMMIOアドレス対応情報を管理し、

前記物理サーバからパケットを受信した場合に、更に、前記MMIOアドレス対応情報を従って前記パケットの宛先アドレスを変換する処理を行う、ことを特徴とした、I/Oデバイス管理方法。

【請求項11】

請求項3記載のサーバシステムであって、

前記物理サーバが認識する前記VFのMMIOアドレス領域情報は、前記仮想サーバがアクセスする前記VFのMMIO空間のアドレスのオフセットであって、

前記管理部が管理する前記VFのMMIOアドレス領域情報は、前記管理部がアクセスする前記VFのMMIO空間のアドレスのオフセットであって、

前記サーバ識別子は、送信元の物理サーバを識別する仮想階層ナンバーであることを特徴とするサーバシステム。

【請求項12】

請求項7記載のスイッチング装置であって、

前記物理サーバが認識する前記VFのMMIOアドレス領域情報は、前記仮想サーバがアクセスする前記VFのMMIO空間のアドレスのオフセットであって、

前記管理部が管理する前記VFのMMIOアドレス領域情報は、前記管理部がアクセスする前記VFのMMIO空間のアドレスのオフセットであって、

10

20

30

40

50

前記サーバ識別子は、送信元の物理サーバを識別する仮想階層ナンバーであることを特徴とするスイッチング装置。

#### 【請求項 13】

請求項 10 記載の I / O デバイス管理方法であって、

前記物理サーバが認識する前記 VF の MMIO アドレス領域情報は、前記仮想サーバがアクセスする前記 VF の MMIO 空間のアドレスのオフセットであって、

前記管理部が管理する前記 VF の MMIO アドレス領域情報は、前記管理部がアクセスする前記 VF の MMIO 空間のアドレスのオフセットであって、

前記サーバ識別子は、送信元の物理サーバを識別する仮想階層ナンバーであることを特徴とする I / O デバイス管理方法。

10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、複数の計算機を備えたブレードサーバに關し、特に、ひとつの I / O デバイスを複数の計算機で共有する技術に關する。

##### 【背景技術】

##### 【0002】

情報セキュリティやコンプライアンスへの意識の高まりから、サーバサイドでのウィルスチェックやメールフィルタなど、企業の情報システムに求められる処理要求が増大している。これらの処理要求の増大に対し、従来は処理内容ごとに個別にサーバを導入して対応してきた。しかし、サーバ台数の増大は運用コストの増大を招き、企業の IT 予算を圧迫して問題化している。

20

##### 【0003】

この問題に対し、複数のサーバで実行されていた処理を 1 台の高性能サーバに集約して、情報システムを構成するサーバ台数を削減するサーバ統合が注目されている。サーバ統合ではサーバの台数に比例して継続して発生する消費電力やスペース(占有床面積)、ハードウェア障害時のメンテナンスコスト等を削減できる。

##### 【0004】

サーバ統合を実現する手段として、CPU を高密度に集積したブレードサーバが台頭している(例えば、特許文献 1)。典型的なブレードサーバは、CPU(プロセッサ)、メモリ及び NIC (Network Interface Card) を搭載した複数のブレードと、ネットワークスイッチ、および拡張用 I / O スロットを搭載した I / O ドロワーが 1 つの筐体に格納された構成をとる。ブレードサーバを用いると、ネットワーク経由で処理を行うサーバに対して効果的にサーバ統合を実現できる。

30

##### 【0005】

一方、ブレードサーバは I / O ドロワーの拡張用 I / O スロットは、ブレードと I / O スロットとの対応が固定的であった。このため、NIC 以外の I / O カードを稀にしか使用しない、もしくは全く使用しないブレードに対しても I / O スロットが予約されており、スペースに無駄が生じるという問題があった。また、ブレードの用途によっては多数の I / O カードを必要とする場合(例; 複数ブレード間での Hot - Standby 構成等)に、I / O ドロワー内の I / O スロットの数を超えて I / O スロットを割り当てることができない、という問題があった。

40

##### 【0006】

ブレードサーバのように多数のブレードで限られた数の I / O スロット(または I / O デバイス)を利用する技術として、ひとつの I / O デバイスを複数のホストで利用する技術が提案されている。

##### 【0007】

このような技術としては、PCI - Sig で標準化が行われているシングルルート I / O 仮想化技術(SR - IOV: Single Root IO Virtualization) やマルチルート I / O 仮想化技術(MR - IOV: Multi Root IO Virtualization) が知られている(例えば、

50

特許文献2、非特許文献1等)。

【0008】

この他、任意のサーバ間でストレージ装置を共有する技術としては、iSCSIが広く知られている。iSCSIは、サーバとストレージ装置のアクセスに使用されるSCSIコマンドを、ネットワーク通信のプロトコルであるTCP/IPパケットにカプセル化する技術である。これにより任意のサーバ間でiSCSI対応ターゲットデバイスを共有できる。

【特許文献1】特開特開2002-32153号

【特許文献2】米国特許第7058738号

【非特許文献1】「Single-Root I/O Virtualization and Sharing Specification, Revision 1.0, Section 1 - Architectural」、2008年発行、著者PCI-SIG、第15～34頁

10

【発明の開示】

【発明が解決しようとする課題】

【0009】

上記従来例のシングルルートI/O仮想化技術(以下、SR-IOV)では、1つのI/Oデバイスの物理機能(PF; Physical Function)が複数の仮想機能(VF; Virtual Function)を提供することができる。同一ブレード内の複数のOSインスタンス間で、複数の仮想機能をそれぞれ占有することでひとつのSR-IOV対応のI/Oデバイスを共有することができる。

【0010】

20

一方、上記従来例のマルチルートI/O仮想化技術(以下、MR-IOV)では、1つのI/Oデバイスに複数の物理機能(PF; Physical Function)を搭載し、各物理機能上で複数の仮想機能(VF; Virtual Function)を提供することができる。MR-IOV対応のI/Oデバイスを利用し、仮想化ソフトウェアを導入することで、異なる物理サーバ上で動作する仮想計算機(VM; Virtual Machine)間で1つのI/Oデバイスを共有することができる。すなわち、MR-IOVでは、特定のブレード(物理計算機)に対して1つのPFを占有させ、各VMはPFが提供する複数のVFを占有する。

【0011】

30

ここで、SR-IOVに対応するI/Oデバイスでは、一つの物理機能を備えればよいので、MR-IOVに対応するI/Oデバイスに低コストで調達することができる。

【0012】

上記従来例のブレードサーバにおいて複数のブレードでI/Oデバイスを共有する場合、上記SR-IOVに対応するI/Oデバイスを用いれば、I/Oデバイスの調達コストを抑制できるものの、ひとつのブレードに対してひとつのI/Oデバイスを割り当てることになり、複数のブレード間でひとつのI/Oデバイスを共有できない、という問題があった。

【0013】

一方、従来例のブレードサーバにおいて複数のブレードでI/Oデバイスを共有する場合、上記MR-IOVに対応するI/Oデバイスを用いれば、複数のブレード間でひとつのI/Oデバイスを共有することができる。しかしながら、MR-IOVに対応するI/OデバイスはSR-IOVに対応するI/Oデバイスに対して調達コストが高いため導入コストが増大する、という問題がある。

40

【0014】

なお、上記iSCSIをブレードサーバで利用した場合、ストレージ装置の共有は可能であるが、I/OデバイスがNIC等の場合は利用することができない。

【0015】

そこで本発明は、上記問題点に鑑みてなされたもので、複数のブレードを備えたブレードサーバにおいて、複数のブレード間で、I/Oドロワーに装着されるI/Oデバイスを安価に共有することを目的とする。

50

## 【課題を解決するための手段】

## 【0016】

本発明は、仮想化部を備えて1以上の仮想サーバを提供する複数の物理サーバと、前記複数の物理サーバで共有されるI/Oデバイスと、前記複数の物理サーバと前記I/Oデバイスを接続するスイッチと、前記スイッチを初期化する管理部とを有するサーバシステムであって、前記I/Oデバイスが、仮想的な機能であるVirtual Function (VF) を有し、前記スイッチが、前記仮想サーバが認識する識別子である第1の識別子と、前記管理部が管理する識別子である第2の識別子と、の間の対応関係を示す識別子対応情報を保持し、前記仮想サーバからパケットを受信した場合に、送信元の物理サーバを識別するサーバ識別子を含む前記パケットを前記スイッチ内で変換し、前記パケットを前記I/Oデバイスに送信する際には、前記識別子対応情報に基づいて、前記パケットに含まれる前記第1の識別子を、当該第1の識別子に前記対応付けられた前記第2の識別子に変換し、かつ、前記サーバ識別子を削除した前記パケットを、前記I/Oデバイスに送信する、ことを特徴とするサーバシステム。

## 【発明の効果】

## 【0017】

したがって、本発明は、ひとつのI/Oデバイス、特にSR-IOV対応のI/Oデバイスを複数のサーバで共有することが可能となる。

## 【発明を実施するための最良の形態】

## 【0018】

以下、本発明の一実施形態を添付図面に基づいて説明する。

## 【0019】

図1は、第1の実施形態を示し、本発明を適用したブレードサーバ（複合型計算機システム）のブロック図を示す。図1において、ブレードサーバ1は、物理計算機として機能するn台のブレード10-1～10-nと、シングルルートI/O仮想化技術（以下、SR-IOV）に対応したI/Oデバイス50と、マルチルートI/O仮想化技術（以下、MR-IOV）でトランザクション（パケット）を処理するブレード10-1～10-nとI/Oデバイス50を接続するPCI-eスイッチ40と、I/Oデバイス50のブレード10-1～10-nへの割当てを管理するPCI管理サーバ（PCI管理計算機）20と、ユーザや管理者がブレードサーバ1を制御するための管理用端末30と、ブレードサーバ1の各部に電力を供給する電源供給装置60から構成されている。なお、PCI-eスイッチ40、I/Oデバイス50は、上記PCI-SIG (<http://www.pcisig.com/>) が策定したPCI-expressの規格に準拠したインターフェースで接続される。なお、図1においては、PCI-eスイッチ40が1つ、I/Oデバイス50が1つの例を示したが、複数のPCI-eスイッチ40と複数のI/Oデバイス50を備えることができる。

## 【0020】

ブレード10-1は1以上のCPU（プロセッサ）11-1, 11-2と、1以上のメモリ12-1と、1以上のチップセット13-1と、を含むハードウェアで構成される。なお、ブレード10-nとPCI管理サーバ20もブレード10-1と同一のハードウェアで構成される。

## 【0021】

また、ブレード10-1～10-nとPCI管理サーバ20の間はネットワーク70を介して接続される。ネットワークとしては、LAN (Local Area Network) やI<sup>2</sup>C (Inter-Integrated Circuit) を用いることができる。各ブレード10-1～10-nにはBMC (Baseboard Management Controller) を搭載してもよく、BMCによって各ブレード10-1～10-nの構成情報（コンフィギュレーション）や電源状態を収集し、PCI管理サーバ20に通知することができる。

## 【0022】

なお、各ブレード10-1～10-n及びPCI管理サーバ20のチップセット13-

10

20

30

40

50

1 ~ 1 3 - n は、それぞれ PCI - express に準拠した I / O ポート 1 3 1 - 1 ~ 1 3 1 - n と、イーサネット（登録商標）等の LAN の規格に準拠したネットワークインターフェース 1 3 2 - 1 ~ 1 3 2 - n を備え、チップセット 1 3 - 1 ~ 1 3 - n のネットワークインターフェース 1 3 2 - 1 ~ 1 3 2 - n がネットワーク 7 0 に接続され、チップセット 1 3 - 1 ~ 1 3 - n の I / O ポート 1 3 1 - 1 ~ 1 3 1 - n が PCI - e スイッチ 4 0 に接続される。

【 0 0 2 3 】

PCI - e スイッチ 4 0 は、ブレード 1 0 - 1 ~ 1 0 - n 及び PCI 管理サーバ 2 0 のチップセット 1 3 と接続されるアップストリームポート 4 1 - 0 ~ 4 1 - n と、I / O デバイス 5 0 が接続されるダウンストリームポート 4 2 - 1 ~ 4 2 - n を備える。 10

【 0 0 2 4 】

図 1 の例では、ブレード 1 0 - 1 のチップセット 1 3 - 1 の I / O ポート 1 3 1 - 1 が PCI - e スイッチ 4 0 のアップストリームポート 4 1 - 1 に接続され、ブレード 1 0 - n のチップセット 1 3 - n の I / O ポート 1 3 1 - n が PCI - e スイッチ 4 0 のアップストリームポート 4 1 - n に接続され、PCI 管理サーバ 2 0 のチップセット 1 3 - M の I / O ポート 1 3 1 - M が PCI - e スイッチ 4 0 のアップストリームポート 4 1 - 0 に接続され、ダウンストリームポート 4 2 - 1 に I / O デバイス 5 0 が接続された例を示す。

【 0 0 2 5 】

なお、ブレード 1 0 - 1 ~ 1 0 - n と PCI - e スイッチ 4 0 の接続及び I / O デバイス 5 0 と PCI - e スイッチ 4 0 の接続は、ブレードサーバ 1 のバックプレーなどを利用することができる。 20

【 0 0 2 6 】

PCI - e スイッチ 4 0 は、アップストリームポート 4 1 - 1 ~ 4 1 - n が M R - I O V に対応しており、ダウンストリームポート 4 2 - 1 ~ 4 2 - n が S R - I O V に対応し、アップストリームポート 4 1 - 1 ~ 4 1 - n はブレード 1 0 - 1 ~ 1 0 - n との間でマルチルート I / O 仮想化技術のトランザクション（パケット）を送受信し、ダウンストリームポート 4 2 - 1 ~ 4 2 - n と I / O デバイス 5 0 の間ではシングルルート I / O 仮想化技術のパケットを送受信する。このため、PCI - e スイッチ 4 0 は、マルチルート I / O 仮想化技術のパケットとシングルルート I / O 仮想化技術のパケットを相互に変換する処理を行う。 30

【 0 0 2 7 】

PCI 管理サーバ 2 0 には、入出力装置（図示省略）を備えた管理端末 3 0 が接続され、管理者などの操作により後述する PCI マネージャ 2 0 2 に指令を行うことができる。

【 0 0 2 8 】

図 2 は、ブレードサーバ 1 の機能要素を示すブロック図である。ブレード 1 0 - 1 ~ 1 0 - n 上ではソフトウェア構成要素である仮想マシンモニタ（VMM ; Virtual Machine Monitor）1 0 0 - 1 ~ 1 0 0 - n が稼動し、各仮想マシンモニタ 1 0 0 - 1 ~ 1 0 0 - n 上では複数の仮想計算機 1 0 1 - 0 ~ 1 0 1 - k - 1 が提供される。ブレード 1 0 - 1 では、仮想マシンモニタ 1 0 0 - 1 上に 2 つの仮想計算機 1 0 1 - 0 、 1 0 1 - 1 が生成され、各各仮想計算機 1 0 1 - 0 、 1 0 1 - 1 では OS 1 0 2 - 0 と OS - 1 0 2 - 1 がそれぞれ実行される。仮想計算機 1 0 1 - 0 、 1 0 1 - 1 の OS 1 0 2 - 0 と OS - 1 0 2 - 1 には I / O デバイス 5 0 の仮想機能（VF ; Virtual Function）を利用するための VF ドライバ 1 0 3 がそれぞれロードされている。他のブレード 1 0 - n もブレード 1 0 - 1 と同様に構成され、それぞれ複数の仮想計算機 1 0 1 - k - 1 で OS 1 0 2 を実行し、VF ドライバ 1 0 3 によって I / O デバイス 5 0 の仮想機能を利用することができる。また、各仮想計算機 1 0 1 - 1 ~ 1 0 1 - k - 1 の OS 1 0 2 - 0 ~ 1 0 2 - k - 1 では、任意のアプリケーションまたはサービスが実行される。 40

【 0 0 2 9 】

一方、PCI 管理サーバ 2 0 では、OS 2 0 1 上で各ブレード 1 0 - 1 ~ 1 0 - n と P

50

PCI-eスイッチ40及びI/Oデバイス50を管理するPCIマネージャ202が動作する。PCI管理サーバ20のOS201にはI/Oデバイス50の物理機能(PF; Physical Function)を利用するためのPFドライバ203がロードされている。

【0030】

ブレード10-1~10-nの各仮想計算機101-1~101-k-1と、PCI管理サーバ20からアクセスされるI/Oデバイス50は、ひとつの物理機能(PF)501と複数の仮想機能(VF)502を提供するSR-IoVに準拠したPCI-expressのI/Oデバイスである。物理機能501と仮想機能502は、I/Oデバイス50の制御部510が提供する機能であり、仮想機能502の数等はPCI管理サーバ20からの要求によって決定される。なお、図2では、I/Oデバイス50が仮想機能502としてVF1~VFkまでのk個の仮想機能502を提供する例を示す。10

【0031】

ここで、ブレード10-1~10-nチップセット13-1~13-nと各仮想計算機101-1~101-k-1のVFドライバ103は、MR-IoVに対応したPCI-expressのパケットを送受信する。一方、I/Oデバイス50はSR-IoVに対応したPCI-expressのパケットを送受信する。

【0032】

本発明の特徴部であるPCI-eスイッチ40は、後述するように、MR-IoVのアップストリームポート41-1~41-nとSR-IoVのダウンストリームポート42-1~42-nとの間で、パケットの変換を行って、複数のブレード10-1~10-nでSR-IoVのI/Oデバイス50を共有する。20

【0033】

各ブレード10-1~10-n及びPCI管理サーバ20を構成するチップセット13-1~n、13-Mは、PCI-Expressのプロトコル階層としてルートコンプレックス(RC; Root Complex)を含み、ルートコンプレックスはエンドポイントとしてのI/Oデバイス50までのローカルPCIツリーを管理する。

【0034】

PCI管理サーバ20のPCIマネージャ202は、後述するように、ブレード10-1~10-nに割当てるPCIツリーの初期化と、PCI-eスイッチ40からI/Oデバイス50のトポロジーと、ブレード10-1~10-nへ割当てるPCIツリーの対応関係を管理し、各ブレード10-1~10-nとPCI-eスイッチ40間のMR-IoVの設定を行う。30

【0035】

また、PCIマネージャ202は、ブレード10-1~10-nの管理部としても機能し、各ブレード10-1~10-nの仮想マシンモニタ100-1~100-nが生成する仮想計算機101-1~101-k-1や起動するOS102-0~102-k-1を管理する。

【0036】

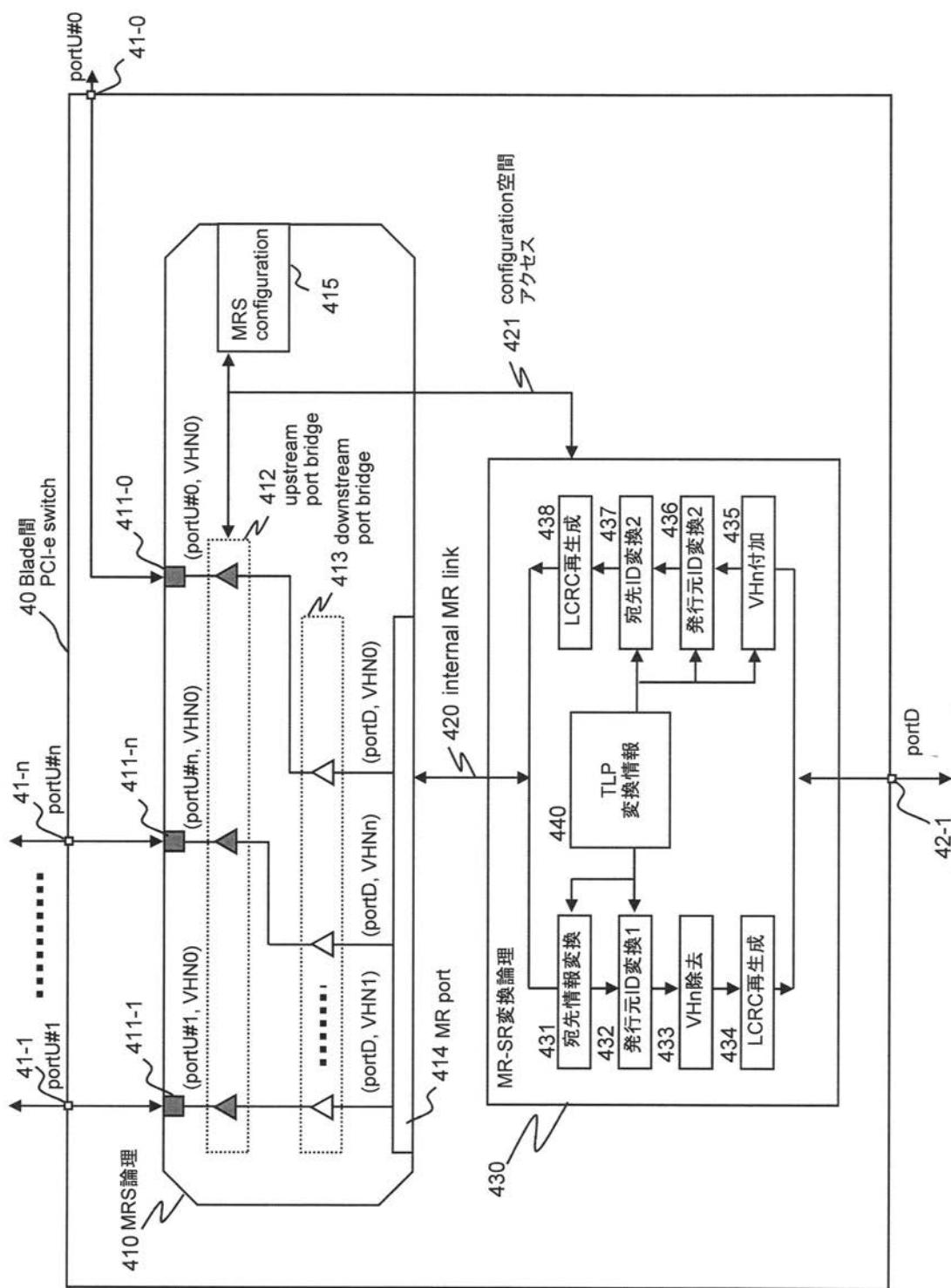

図3は、PCI-eスイッチ40の構成を示すブロック図である。PCI-eスイッチ40は、各ブレード10-1~10-nに接続されてMR-IoVのパケットを送受信するアップストリームポート41-1~41-nがマルチルートスイッチ(以下、MRS)論理410に接続され、I/Oデバイス50に接続されるダウンストリームポート42-1~42-nは、SR-IoVのパケットとMR-IoVのパケットを相互に変換するマルチルート-シングルルート(以下、MR-SR)変換論理430に接続される。なお、MR-SR変換論理430は、ダウンストリームポート42-1に対応するものだけを図示したが、実際には、各ダウンストリームポート42-1~42-n毎にMR-SR変換論理430が設けられる。40

【0037】

MRS(マルチルートスイッチ)論理410は、アップストリームポート41-1~450

1 - n に接続されるポート 4 1 1 - 0 ~ 4 1 1 - n と、ポート 4 1 1 - 0 ~ 4 1 1 - n にそれぞれ接続されたアップストリームポートブリッジ 4 1 2 と、アップストリームポートブリッジ 4 1 2 に接続されたダウンストリームポートブリッジ 4 1 3 と、ダウンストリームポートブリッジ 4 1 2 に接続されたマルチルートポート 4 1 4 と、ポート 4 1 1 - 0 ~ 4 1 1 - n とマルチルートポート 4 1 4 と、ポート 4 1 1 - 0 ~ 4 1 1 - n とマルチルートポート 4 1 4 の接続関係等の M R S (マルチルートスイッチ) 構成情報 (コンフィギュレーション) 4 1 5 とを備える。M R S 構成情報 4 1 5 は、ポート 4 1 1 - 0 ~ 4 1 1 - n とマルチルートポート 4 1 4 のルーティングを管理する。この M R S 構成情報 4 1 5 は、コンフィギュレーション空間アクセスパス 4 2 1 によりアップストリームポートブリッジ 4 1 2 に接続されてアップストリームポート 4 1 - 1 ~ 4 1 - n からアクセス可能となっており、例えば、アップストリームポート 4 1 - 0 に接続された P C I 管理サーバ 2 0 からアクセスすることができる。さらに、コンフィギュレーション空間アクセスパス 4 2 1 は、M R - S R 変換論理 4 3 0 にも接続され、P C I 管理サーバ 2 0 は M R S 論理 4 1 0 からコンフィギュレーション空間アクセスパス 4 2 1 を介して M R - S R 変換論理 4 3 0 にもアクセス可能となっている。

【 0 0 3 8 】

M R S 論理 4 1 0 のマルチルートポート 4 1 4 は、内部マルチルートリンク 4 2 0 を介して M R - S R 変換論理 4 3 0 に接続される。

【 0 0 3 9 】

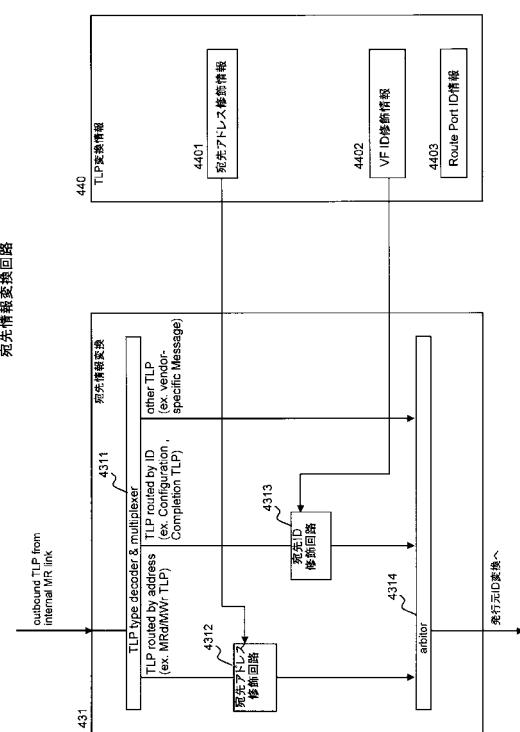

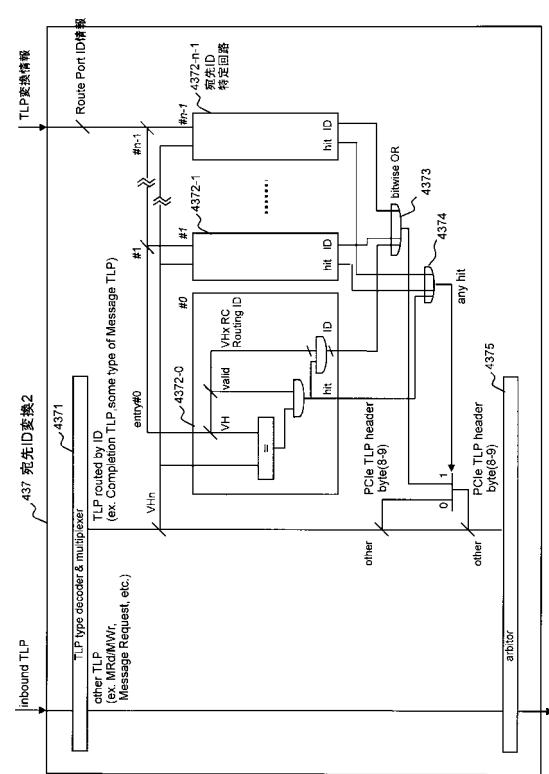

M R - S R 変換論理 4 3 0 は、内部マルチルートリンク 4 2 0 から受信した M R - I O V のパケットを S R - I O V のパケットに変換し、ダウンストリームポート 4 2 - 1 から I / O デバイス 5 0 へ送信するユニット 4 3 1 ~ 4 3 4 と、ダウンストリームポート 4 2 - 1 から受信した I / O デバイス 5 0 からの S R - I O V のパケットを M R - I O V のパケットに変換して、内部マルチルートリンク 4 2 0 に送信するユニット 4 3 5 ~ 4 3 8 と、M R - I O V のパケットと S R - I O V のパケットの変換を行うための情報を格納する T L P (Transaction Layer Packet) 変換情報 4 4 0 を主体に構成される。

【 0 0 4 0 】

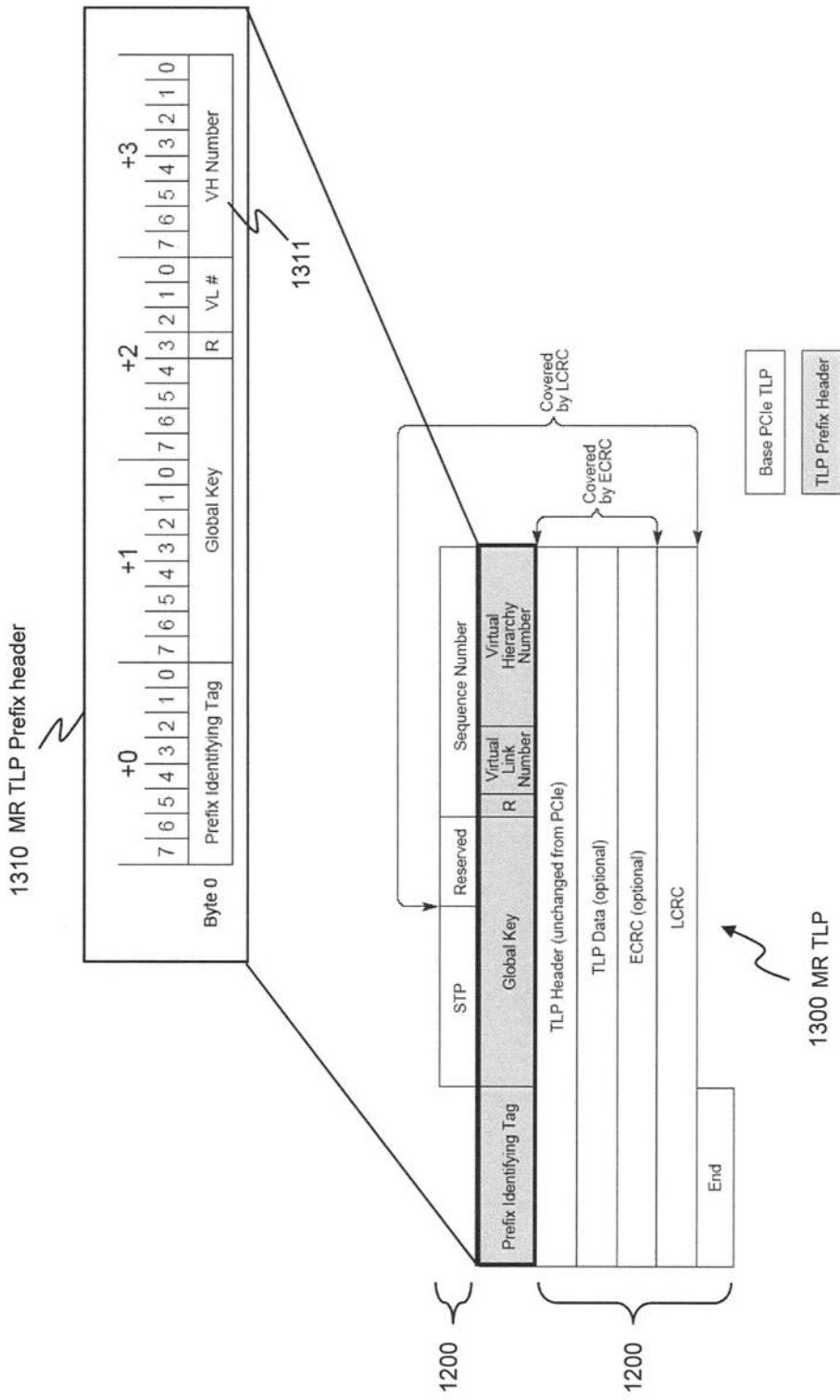

ここで、本発明のパケットの構成について説明する。図 1 4 は、マルチルート T L P 及び P C I e ( P C I - e x p r e s s ) ベース T L P のフォーマットを示す説明図である。

【 0 0 4 1 】

マルチルート T L P (図中 M R T L P ) 1 3 0 0 は、P C I - e x p r e s s のパケットである P C I e ベース T L P 1 2 0 0 のヘッダーの前に、マルチルート T L P プリフィックスヘッダー 1 3 1 0 を附加したものである。

【 0 0 4 2 】

P C I e ベース T L P 1 2 0 0 は、スタートフレーム (図中 S T P ) と、シーケンス番号と、T L P ヘッダーと、E C R C (End to End Cyclic Redundancy Check) と、L C R C (Link Cyclic Redundancy Check) と、エンドフレームから構成される。

【 0 0 4 3 】

マルチルート T L P 1 3 0 0 は、P C I e ベース T L P 1 2 0 のシーケンス番号と T L P ヘッダーの間に、マルチルート T L P プリフィックスヘッダ 1 3 1 0 を挿入したものである。

【 0 0 4 4 】

マルチルート T L P プリフィックスヘッダ 1 3 1 0 は、M R - I O V において P C I e パケットの発行元のブレード 1 0 - 1 ~ 1 0 - n を特定するための仮想階層ナンバー ( V H n ; Virtual Hierarchy Number ) 1 3 1 1 を含む。なお、本実施例における仮想階層ナンバー 1 3 1 1 は P C I e スイッチ 4 0 の内部で付与される識別番号であり、M R S 構成情報 4 1 5 に格納されている。

【 0 0 4 5 】

本発明のブレードサーバ 1 では、仮想計算機 1 0 1 - 1 ~ 1 0 1 - k - 1 、仮想マシン

10

20

30

40

50

モニタ 100 - 1 ~ 100 - n、チップセット 13 - 1 ~ 13 - n 及びアップストリームポート 41 - 1 ~ 41 - n 間では、MR - IOV のパケットであるマルチルート TLP 1300 で送受信を行い、ダウンストリームポート 42 - 1 と I/O デバイス 50 の間では、マルチルート TLP 1300 からマルチルート TLP プリフィックスヘッダ 1310 を削除して、PCIe ベース TLP 1200 で送受信を行う。

#### 【0046】

ここで、本発明のブレードサーバ 1 では、ブレード 10 - 1 ~ 10 - n から I/O デバイス 50 への下り方向 (Outbound) のパケットではマルチルート TLP 1300 は、PCI - e スイッチ 40 の MR - SR 変換論理 430 が、マルチルート TLP プリフィックスヘッダ 1310 を削除して、送信元を PCIe 管理サーバ 20 とした PCIe ベース TLP 1200 に変換して I/O デバイス 50 に送信する。 10

#### 【0047】

逆に、I/O デバイス 50 からブレード 10 - 1 ~ 10 - n への上り方向 (Inbound) のパケットでは、PCI - e スイッチ 40 の MR - SR 変換論理 430 が、I/O デバイス 50 から受信した PCIe ベース TLP 1200 に、下り方向のパケットに付与されていた仮想階層ナンバー 1311 を含むマルチルート TLP プリフィックスヘッダ 1310 を付加してブレード 10 - 1 ~ 10 - n に送信する。

#### 【0048】

以上のような構成により、PCI - e スイッチ 40 のブレード 10 - 1 ~ 10 - n 側では MR - IOV のパケットで通信を行い、PCI - e スイッチ 40 の I/O デバイス 50 側では SR - IOV のパケットで通信を行うことで、複数のブレード 10 - 1 ~ 10 - n でひとつの SR - IOV に準拠した I/O デバイス 50 を共有できる。 20

#### 【0049】

また、PCI - e スイッチ 40 は、発行元のブレード 10 - 1 ~ 10 - n を I/O デバイス 50 に対して隠蔽するのに加え、各ブレード 10 - 1 ~ 10 - n 間で異なる MMIO (Memory-mapped I/O) 空間を吸収する。

#### 【0050】

このため、PCI 管理サーバ 20 は、仮想マシンモニタ 100 - 1 ~ 100 - n の起動時に、各仮想計算機 101 - 1 ~ 101 - k - 1 の MMIO 空間のアドレスと、I/O デバイス 50 への PCIe ベース TLP 1200 の発行元となる PCI 管理サーバ 20 の MMIO 空間の差分 (オフセット) を、PCI - e スイッチ 40 の TLP 変換情報 440 に格納しておき、上り方向のマルチルート TLP 1300 の宛先アドレスを、実際の宛先となる仮想マシンモニタ 100 - 1 ~ 100 - n の MMIO 空間に変換する。 30

#### 【0051】

以下に、PCI - e スイッチ 40 が行う仮想階層ナンバー 1311 の削除及び付加と宛先アドレスの変換について詳述する。

#### 【0052】

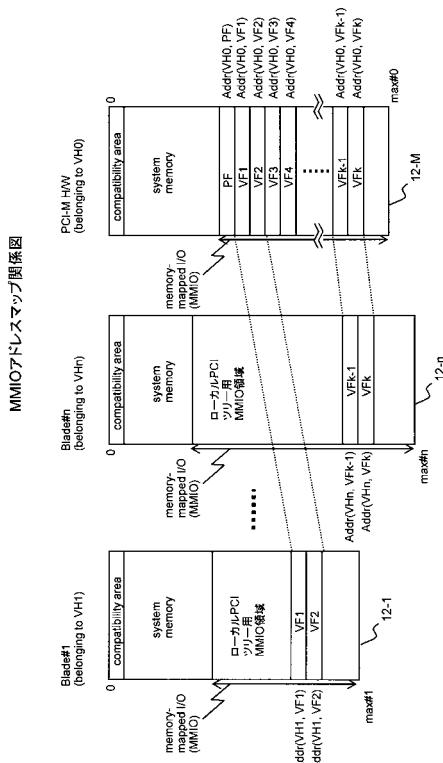

図 4 は、ブレード 10 - 1 (Blade #1) ~ 10 - n (Blade #n) 及び PCIe 管理サーバ 20 (PCI - M) が管理するメモリ 12 - 1 ~ n、12 - M 上に設定した MMIO 空間を示す。例えば、図示の例では、ブレード 10 - 1 に 2 つの仮想機能 502 = VF1、VF2 を割り当て、ブレード 10 - n にも 2 つの仮想機能 502 = VFk - 1、VF2k 割り当てた例を示す。 40

#### 【0053】

ブレード 10 - 1 ~ 10 - n の仮想マシンモニタ 100 - 1 ~ n はローカル PCIe ツリーの後に I/O デバイス 50 の仮想機能 502 (VF) へアクセスするための MMIO 空間を設定する。各ブレードの MMIO 空間は、搭載しているメモリ 12 - 1 ~ n の容量等の違いにより、アドレスは相違する。各ブレードの MMIO 空間は、各ブレード 10 - 1 ~ 10 - n が使用する仮想機能 502 (VF) 毎に PCIe 管理サーバ 20 が設定するメモリ 12 - M 上の MMIO 空間に割り当てられる。

#### 【0054】

各ブレード 10 - 1 ~ 10 - n が使用する MMIO 空間のアドレスの違いは、PCI マネージャ 202 が設定する宛先アドレス修飾情報 4401 の「Off f set」にその差分が設定されることで、PCI - e スイッチ 40 は、I/O デバイス 50 とブレード 10 - 1 ~ 10 - n 間のパケットの宛先アドレスを変更することができる。

#### 【0055】

つまり、ブレード 10 - 1 ~ 10 - n から I/O デバイス 50 に対する読み込み要求等では、各ブレードが送信するパケットの発行元アドレスは、PCI - e スイッチ 40 が、宛先アドレス修飾情報 4401 の「Off f set」によって、PCI 管理サーバ 20 の MMIO 空間が発行元アドレスのパケットに書き換えて I/O デバイス 50 に送信する。

#### 【0056】

逆に、I/O デバイス 50 からブレード 10 - 1 ~ 10 - n に対する読み込み要求等への応答では、I/O デバイス 50 が送信するパケットの宛先アドレスは、PCI 管理サーバ 20 の MMIO 空間となっているので、PCI - e スイッチ 40 は宛先アドレス修飾情報 4401 の「Off f set」によって、PCI 管理サーバ 20 の MMIO 空間をブレード 10 - 1 ~ 10 - n 毎の MMIO 空間に書き換えて返信することができる。

#### 【0057】

以上の処理により、PCI - e スイッチ 40 は、MMIO 空間のアドレスを差し替えることで、複数のブレード 10 - 1 ~ 10 - n で SR - I/OV に対応する I/O デバイス 50 の共有を実現する。

#### 【0058】

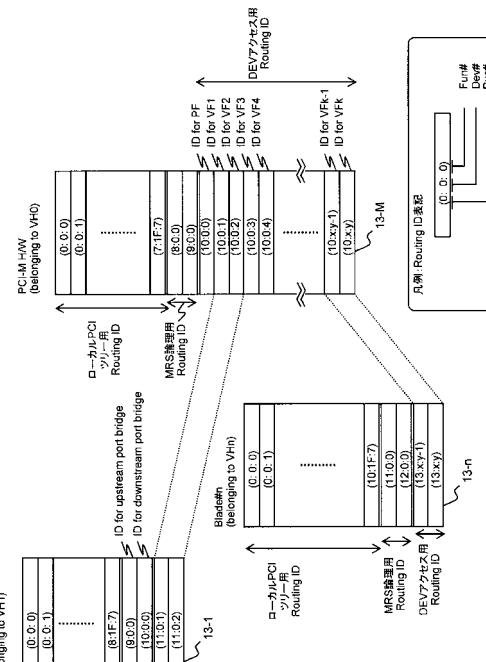

図 5 は、ブレード 10 - 1 (Blade #1) ~ 10 - n (Blade #n) 及び PCI 管理サーバ 20 (PCI - M) のチップセット 13 - 1 ~ n、M が管理するルーティング ID の関係を示す。各チップセット 13 - 1 ~ n、M は、それぞれ、各計算機内のデバイスについて認識したローカル PCI ツリー用のルーティング ID と、PCI - e スイッチ 40 の MRS 論理 410 から取得した MRS 論理用ルーティング ID と、各チップセット 13 - 1 ~ n、M からの I/O デバイス 50 のアクセス用ルーティング ID とを備える。

#### 【0059】

ブレード 10 - 1 ~ 10 - n のチップセット 13 - 1 ~ n では、接続している PCI - e スイッチ 40 のアップストリームポート 41 - 1 ~ n が異なるため、チップセット 13 - 1 ~ n が認識する I/O デバイス 50 のバス番号は異なる。例えば、図示の例では、ブレード 10 - 1 に 2 つの仮想機能 502 = VF1、VF2 を割り当て、ブレード 10 - n にも 2 つの仮想機能 502 = VFk - 1、VF2k 割り当てた例を示す。

#### 【0060】

チップセット 13 - 1 から I/O デバイス 50 の仮想機能 502 = VF1 へのルーティング ID は、11 : 0 : 1 であり、バス番号は 11 であるのに対し、チップセット 13 - n から I/O デバイス 50 の仮想機能 502 = VFk - 1 へのルーティング ID は、13 : x : y - 1 でありバス番号は 13 である。MRS 論理用ルーティング ID も同様であり、ブレード 10 - 1 ~ 10 - n 毎に異なる。なお、ルーティング ID は、バス番号 (Bus #) : デバイス番号 (Dev #) : ファンクション番号 (Fun #) の順に設定される。

#### 【0061】

一方、I/O デバイス 50 の物理機能 501 にアクセス可能な PCI マネージャ 202 は、起動時に物理機能 501 と仮想機能 502 のルーティング ID を初期化してチップセット 13 - M で管理しており、図示の例ではルーティング ID = 10 : 0 : 0 ~ 10 : x : y - 1 を I/O デバイス 50 のアクセス用ルーティング ID に設定する。

#### 【0062】

そして、PCI マネージャ 202 は、各ブレード 10 - 1 ~ 10 - n が起動する度に、図 7 に示す TLP 変換情報 440 の仮想機能 ID 修飾情報 4402 に、各ブレード 10 - 1 ~ 10 - n のチップセット 13 - 1 ~ n から I/O デバイス 50 の仮想機能 502 まで

10

20

30

40

50

のルーティングIDと、PCI管理サーバ20のチップセット13-Mが管理するI/Oデバイス50のルーティングIDを、各ブレード10-1~10-n毎の仮想階層ナンバー1311と共に設定する。

【0063】

ルーティングIDで各ブレード10-1~10-nとI/Oデバイス50がアクセスを行う場合には、PCI-eスイッチ40が仮想機能ID修飾情報4402を参照し、パケット中のルーティングIDを付け替えて通信を行う。

【0064】

すなわち、PCI-eスイッチ40は、ブレード10-1~10-nからI/Oデバイス50へのパケットがルーティングIDでアクセスする場合、各ブレード10-1~10-nのルーティングIDをPCI管理サーバ20のルーティングIDに差し替えてI/Oデバイス50に送信する。

10

【0065】

逆に、I/Oデバイス50からブレード10-1~10-nへのパケットがルーティングIDでアクセスする場合、PCI-eスイッチ40は、PCI管理サーバ20のルーティングIDを各ブレード10-1~10-nのルーティングID差し替えてI/Oデバイス50に送信する。

【0066】

以上の処理により、PCI-eスイッチ40は、ルーティングIDを差し替えることで、複数のブレード10-1~10-nでSR-IOVに対応するI/Oデバイス50の共有を実現する。

20

【0067】

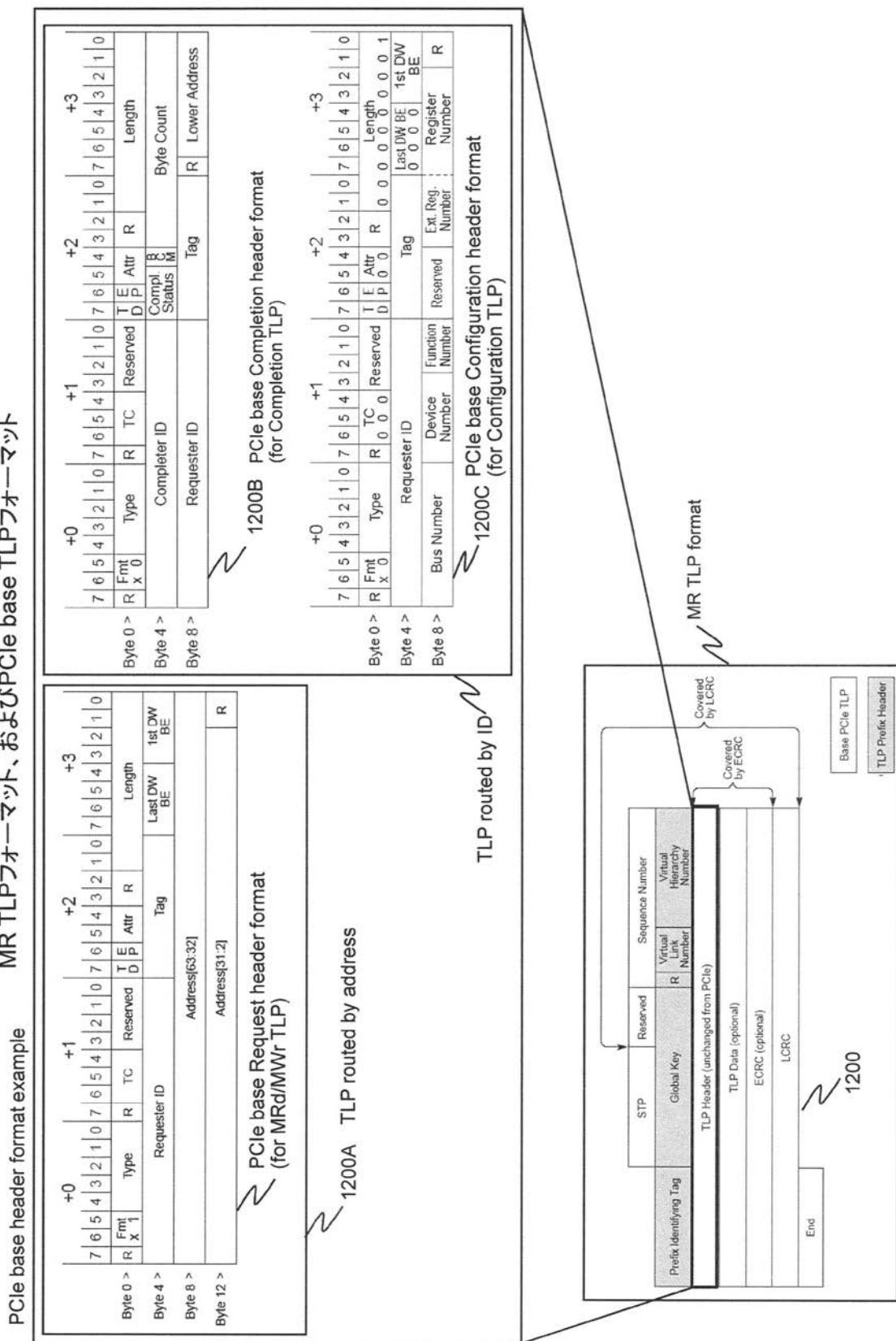

ここで、ブレードサーバ1で使用されるPCI-expressのパケットのフォーマットを図15に示す。図15はPCI-eスイッチ40で転送されるPCIeベースTL\_P1200のうちTL\_Pヘッダをアクセス形態毎に示す説明図である。

【0068】

図15は、PCIeベースTL\_P1200のTL\_Pヘッダの詳細を示し、TL\_Pヘッダ1200Aは、MMIO空間のアドレスでブレード10-1~10-nとI/Oデバイス50のアクセスを行うパケットを示し、TL\_Pヘッダ1200B、1200CはルーティングIDでアクセスを行うパケットを示しており、TL\_Pヘッダ1200Bは要求（書き込み要求など）に対する完了通知を通知するパケットの例を示し、TL\_Pヘッダ1200Cは対象のデバイスの構成情報（コンフィギュレーション）の設定するパケットを示す。

30

【0069】

各TL\_Pヘッダ1200A~Cは、バイト0~15の16バイトで構成される。

【0070】

MMIO空間のアドレスでアクセスするTL\_Pヘッダ1200Aは、メモリリード要求やメモリライト要求の際に使用される。

【0071】

TL\_Pヘッダ1200Aは、バイト4、5にパケットの発行元（リクエスタ）IDに要求元のルーティングIDを格納し、バイト8~15に読み込む対象のMMIO空間のアドレスを格納し、バイト0の0~4ビットに要求の種別を格納する。

40

【0072】

PCI-eスイッチ40は、ブレード10-1~10-nからI/Oデバイス50へ向かう下りパケットの時には、リクエスタIDに格納されたブレードのルーティングIDをPCI管理サーバ20のルーティングIDに書き換えて、要求元がPCI管理サーバ20であることを設定する。つまり、SR-IOVのI/Oデバイス50は、ひとつの計算機のみと接続されるため、I/Oデバイス50へのパケットはPCI管理サーバ20発に差し替える。

【0073】

50

そして、PCI-eスイッチ40は、ブレードのMMIO空間のアドレスを宛先アドレス修飾情報4401の「off set」でPCI管理サーバ20(PCIマネージャ202)のMMIO空間のアドレスに変更し、I/Oデバイス50が認識可能なアドレス空間に変更する。

【0074】

ルーティングIDでアクセスする場合の、TLPhedda1200Bは、要求(書き込み要求等)に対する完了通知の際に使用される。TLPhedda1200Bは、バイト4,5のコンプリータIDに完了通知(コンプリーション)を発行するデバイスのルーティングIDを格納し、バイト8,9のリクエスタIDに要求元(リクエスタ)のルーティングIDを格納し、バイト0の0~4ビットにコンプリーションを示す値を格納する。

10

【0075】

PCI-eスイッチ40は、仮想機能ID修飾情報4402を参照して、I/Oデバイス50へ向かう上りパケットの時には、リクエスタIDに格納されたPCI管理サーバ20のルーティングIDをPCI管理サーバ20のルーティングIDから送信先のブレードのルーティングIDに差し替えて送信する。

【0076】

ルーティングIDでアクセスするTLPhedda1200Cは、デバイスに対する構成情報の設定を要求するパケットで使用される。TLPhedda1200Cは、バイト4,5のリクエスタIDに構成情報の設定を要求するデバイスのルーティングIDを格納し、バイト8,9には構成情報の設定対象のバス番号とデバイス番号とファンクション番号からなるルーティングIDを格納し、バイト0の0~4ビットに構成情報の設定要求(コンフィギュレーション)を示す値を格納する。

20

【0077】

PCI-eスイッチ40は、ブレード10-1~10-nからI/Oデバイス50へ向かう下りパケットの時には、リクエスタIDに格納されたブレードのルーティングIDをPCI管理サーバ20のルーティングIDに書き換えて、要求元がPCI管理サーバ20であることを設定する。また、PCI-eスイッチ40は、仮想機能ID修飾情報4402を参照して、ブレードが設定したI/Oデバイス50のルーティングID(バス番号、デバイス番号、ファンクション番号を、)PCI管理サーバ20が認識するルーティングIDに差し替えて、I/Oデバイス50にはPCI管理サーバ20からの要求であることに変更する。

30

【0078】

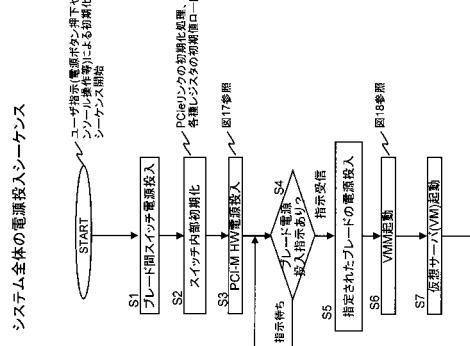

図16は、ブレードサーバ1の起動手順を示すフローチャートである。この処理は、ブレードサーバ1の管理者またはユーザのスイッチ操作に基づいて開始される。

【0079】

ステップS1では、管理者(またはユーザ)がPCI-eスイッチ40の電源を投入する。PCI-eスイッチ40は、起動するとPCI-eリンクの初期化処理と各種レジスタの初期化処理を実行する(S2)。すなわち、図3のMRS構成情報415及びTLPhedda1200B変換情報440の初期化が行われる。また、管理者などによりI/Oデバイス50の電源が投入される。なお、I/Oデバイス50の電源は、PCI-eスイッチ40と連動していても良い。

40

【0080】

ステップS3では、管理者(またはユーザ)が、PCI管理サーバ20の電源を投入する。PCI管理サーバ20では、後述する図17のように各種初期化が行われる。PCI管理サーバ20の起動が完了すると、ステップS4ではPCIマネージャ202が管理端末30からのブレードに対する起動の指示を待ち受ける。

【0081】

PCIマネージャ202は管理端末30から起動するブレード10-1~10-nに対する指令を受け付けると、ステップS5に進んで指令を受け付けたブレード10-1~10-nの電源を投入し、その後、ステップS6では、PCIマネージャ202が、起動が

50

完了したブレードに対して仮想マシンモニタ 100-1~100-n を起動する。仮想マシンモニタ 100-1~100-n の起動については後述の図 18 にて詳述する。ステップ S7 では、仮想マシンモニタの起動が完了した後に、受け付けた指令に基づいて仮想計算機 101-1~101-k-1 を生成し、各仮想計算機 101-1~101-k-1 で OS 102-0~102-K-1 を起動させる。仮想計算機の起動が完了すると再びステップ S4 に戻って次のブレード 10-1~10-n の起動の指令を待つ。

#### 【0082】

上記処理により、PCI-e スイッチ 40、PCI 管理サーバ 20、I/O デバイス 50 の順で電源が投入されて初期化が行われた後、管理端末 30 から指令されたブレード 10-1~10-n が起動される。

10

#### 【0083】

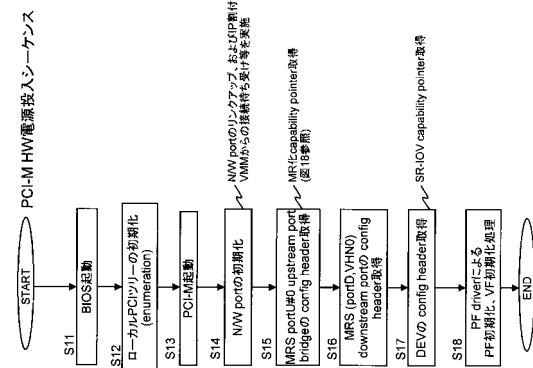

図 17 は、図 16 に示したステップ S3 の PCI 管理サーバ 20 の起動の際に行われる処理の一例を示すフロー チャートである。

#### 【0084】

PCI 管理サーバ 20 は、電源を投入されるとステップ S11 で BIOS (Basic I/o System) または EFI (Extensible Firmware Interface) が起動する。BIOS (または EFI) の起動時には、ステップ S12 でチップセット 13-M が PCI 管理サーバ 20 内のデバイスについて、ルートコンプレックスの下にローカル PCI ツリーを構成し、PCI ローカルツリーの初期化を行う。すなわち、チップセット 13-M は、図 5 で示したような、ローカル PCI ツリーのルーティング ID をチップセット 13-M のレジスタ等の所定の領域に設定する。この例では、PCI 管理サーバ 20 内のローカルルーティング ID として、0:0:0~7:1F:7 が各エントリに設定される。

20

#### 【0085】

ステップ S13 では、BIOS (または EFI) の起動が完了すると OS 201 が起動し、その後に、PCI マネージャ 202 (PCI-M) が起動する。このとき、OS 201 は PF ドライバ 203 を読み込んで、PCI マネージャ 202 が I/O デバイス 50 の物理機能 PF 501 を利用する準備を行う。なお、I/O デバイス 50 の物理機能を使用するのは PCI-e スイッチ 40 及び I/O デバイス 50 を管理する PCI マネージャ 202 のみであり、他のブレード 10-1~10-n は仮想機能を利用する。

#### 【0086】

30

ステップ S14 では、OS 201 がネットワークインターフェース 132-M の初期化を実施する。ネットワークインターフェース 132-M の初期化は、ネットワーク 70 への接続と IP アドレスの付与及びブレード 10-1~10-n の仮想計算機からの接続要求に対する待ち受けの開始が含まれる。

#### 【0087】

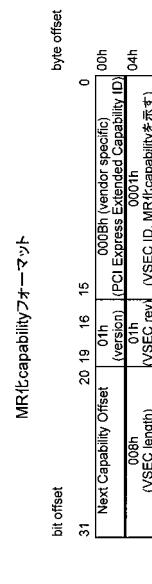

次に、ステップ S15 では、PCI マネージャ 202 が I/O ポート 131-M から PCI-e スイッチ 40 にアクセスして、マルチルートスイッチ論理 410 のアップストリームポートブリッジ 412 からアップストリームポート 41-0 に接続されたポート 411-0 に設定された構成情報 (例えば、マルチルート化可能ポインタ : Capability pointer) を取得し、当該ポート 411-0 のバス番号 (例えば、9) を取得する。ここで、構成情報としてのマルチルート化可能ポインタは、図 19 で示すように、4 バイト目の 0~15 ビットの VSEC\_ID がマルチルート化可能ポインタを示す。PCI マネージャ 202 は、PCI-e スイッチ 40 から仮想階層ナンバー 1311 を取得する。図 4 の例では、PCI 管理サーバ 20 の仮想階層ナンバー 1311 (VH) は「0」となる。

40

#### 【0088】

ステップ S16 では、PCI マネージャ 202 が、I/O ポート 131-M から PCI-e スイッチ 40 にアクセスして、MRS 論理 410 のダウンストリームポートブリッジ 413 の構成情報 (例えば、コンフィギュレーションヘッダ) を取得する。

#### 【0089】

次に、ステップ S17 では、PCI マネージャ 202 は、I/O ポート 131-M 及び

50

アップストリームポート 41 - 0 から I/O デバイス 50 にアクセスし、I/O デバイス 50 の SR - IOV に関する構成情報（例えば、コンフィギュレーションヘッダ）を取得する。PCI マネージャ 202 は、I/O デバイス 50 の構成情報から仮想機能（VF）の個数や MMIO 空間などを取得する。また、PCI マネージャ 202 は I/O デバイス 50 からバス番号及びデバイス番号を取得する。例えば、PCI 管理サーバ 20 のチップセット 13 - M のルートコンプレックスから見た I/O デバイス 50 のアクセス用ルーティング ID は 0 : 2 : 0 となる。

#### 【0090】

ステップ S18 では、上記ステップ S15 ~ S17 で取得したマルチルートスイッチ論理 410 のアップストリームポートブリッジ 412 とダウンストリームポートブリッジ 413 の構成情報と、I/O デバイス 50 の構成情報から、図 5 で示すように、MRS 論理用ルーティング ID と、I/O デバイス 50 をアクセスするためのルーティング ID (DEV アクセス用 Routing ID) をチップセット 13 - M のレジスタ等の所定の領域に設定する。また、PCI マネージャ 202 は、めもり 12 - M の所定の領域に物理機能 501 にアクセスするための MMIO と、仮想機能 501 にアクセスするための MMIO を k 個設定する。

#### 【0091】

図 5 の例では、PCI マネージャ 202 が PCI 管理サーバ 20 の I/O ポート 131 - M から PCI - e スイッチ 40 のアップストリームポート 41 - 0 からダウンストリームポートブリッジ 413 までの MR - IOV のルーティング ID として、ポート 411 - 0 がバス番号 = 9、MRS 構成情報 415 がバス番号 = 8、I/O デバイス 50 のバス番号 = 10 となり、MRS 論理 410 用のルーティング ID は、8 : 0 : 0、9 : 0 : 0 となる。また、I/O デバイス 50 のデバイスアクセス用ルーティング ID は、10 : 0 : 0 が I/O デバイス 50 の物理機能にアクセスするためのルーティング ID に設定され、10 : 0 : 1 ~ 10 : 0 : VF k までの k 個のルーティング ID が I/O デバイス 50 のアクセス用に設定される。そして、PCI マネージャ 202 が PF ドライバ 203 で I/O デバイス 50 の物理機能 PF501 と仮想機能 502 を初期化する。

#### 【0092】

上記処理によって、I/O デバイス 50 の物理機能 PF501 と仮想機能 502 を初期化が PCI マネージャ 202 によって行われる。

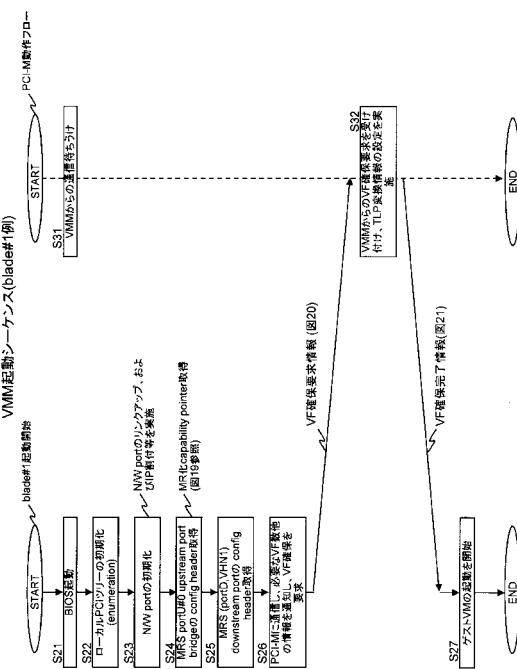

#### 【0093】

図 18 は、図 16 のステップ S6、S7 で行われるブレード 10 - 1 ~ 10 - n の起動と仮想計算機（ゲスト VM）の起動処理の一例を示すフローチャートである。この例では、管理端末 30 から図 1 のブレード 10 - 1 (BLADE #1) を起動し、ブレード 10 - 1 の仮想マシンモニタ 100 - 1 上で仮想計算機 101 - 1 (VM #0)、101 - 2 (VM #1) を生成する指令があった例を示す。

#### 【0094】

PCI マネージャ 202 は、既に起動してステップ S31 にて仮想マシンモニタ 100 - 1 ~ 100 - n からの通信を待ち受ける状態となっている（図 17 の S14）。

#### 【0095】

PCI 管理サーバ 20 は管理端末 30 から指令を受けたブレード 10 - 1 (BLADE #1) に起動の指令を出力し、ブレード 10 - 1 を起動する。この処理は、例えば、ブレード 10 - 1 ~ 10 - n が BMC を備えている場合には、該当するブレードの BMC に対して起動を指令し、ネットワークインターフェース 132 - 1 ~ n へ起動を指令する場合にはマジックパケットを送信することで行われる。

#### 【0096】

PCI 管理サーバ 20 からの指令で起動したブレード 10 - 1 は、電源を投入されるとステップ S21 で BIOS または EFI が起動する。BIOS (または EFI) の起動時には、ステップ S22 でチップセット 13 - 1 がブレード 10 - 1 内のデバイスについてルートコンプレックスの下にローカル PCI ツリーを構成し、PCI ローカルツリーの初

10

20

30

40

50

期化を行う。すなわち、チップセット 13-1 は、図 5 で示した `Bla de #1` のように、ローカル PCI ツリーのルーティング ID をチップセット 13-1 のレジスタ等の所定の領域に設定する。この例では、ブレード 10-1 内のローカルルーティング ID として、`0:0:0~8:1F:7` が各エントリに設定される。

#### 【0097】

ステップ S23 では、BIOS ( または EFI ) の起動が完了すると仮想マシンモニタ 100-1 が起動する。仮想マシンモニタ 100-1 がネットワークインターフェース 132-1 の初期化を実施する。ネットワークインターフェース 132-1 の初期化は、ネットワーク 70 への接続と IP アドレスの付与が含まれる。

#### 【0098】

次に、ステップ S24 では、仮想マシンモニタ 100-1 が I/O ポート 131-1 から PCI-e スイッチ 40 にアクセスして、マルチルートスイッチ論理 410 のアップストリームポートブリッジ 412 からアップストリームポート 41-0 に接続されたポート 411-1 に設定された構成情報 ( 例えば、マルチルート化可能ポインタ : Capability pointer ) を取得し、当該ポート 411-1 のバス番号 ( 例えば、9 ) を取得する。構成情報としてのマルチルート化可能ポインタは、図 19 で示したように、4 バイト目の 0~15 ビットの `VSEC_ID` がマルチルート化可能ポインタを示す。仮想マシンモニタ 100-1 は、PCI-e スイッチ 40 から仮想階層ナンバー 1311 を取得する。図 5 の例では、ブレード 10-1 の仮想階層ナンバー 1311 ( VH ) は「 1 」となる。

#### 【0099】

ステップ S25 では、仮想マシンモニタ 100-1 が、I/O ポート 131-1 から PCI-e スイッチ 40 にアクセスして、MRS 論理 410 のダウンストリームポートブリッジ 413 の構成情報 ( 例えば、コンフィギュレーションヘッダ ) を取得する。仮想マシンモニタ 100-1 は、ルートコンプレックスから見た I/O デバイス 50 のルーティング ID のデバイス番号として、MRS 論理 410 のダウンストリームポートブリッジ 413 のデバイスを割り当てる。この例では、ルートコンプレックスから見た I/O デバイス 50 のルーティング ID は、`0:6:0` となる。

#### 【0100】

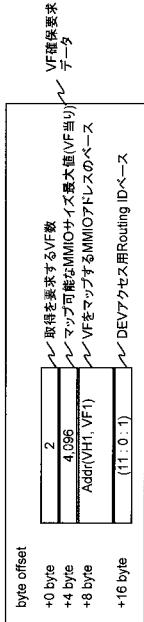

次に、ステップ S26 では、仮想マシンモニタ 100-1 が必要とする仮想機能 502 の数を含む確保要求を PCI マネージャ 202 に VF 確保要求データとしてネットワーク 70 から送信する。この確保要求は、図 20 で示すように、仮想マシンモニタ 100-1 が必要とする仮想機能 ( VF ) 502 の数 ( = 2 ) と、仮想マシンモニタ 100-1 がひとつずつ仮想機能 502 に対してメモリ 12-1 に設定可能な MMIO のサイズの最大値と、仮想機能 502 を設定する MMIO のベースアドレス及び仮想階層ナンバー 1311 ( VH = 1 ) と、I/O デバイス 50 からアクセスするためのルーティング ID ( 11:0 : 1 及び 11:0 : 2 ) を含む。なお、ブレード 10-1 から見た I/O デバイス 50 のバス番号は 11 となり、PCI 管理サーバ 20 から見たバス番号とは異なる。また、ブレード 10-1 は、確保要求にルートコンプレックスが取得した I/O デバイス 50 のアクセス用ルーティング ID ( 0:6:0 ) も通知する。なお、I/O デバイス 50 からアクセスするためのルーティング ID は、各ブレード 10-1 ~ 10-n の起動時に BIOS が決定した値を用いることができる。

#### 【0101】

仮想機能 502 を確保する要求を受け付けた PCI マネージャ 202 は、ブレード 10-1 から見た PCI-e スイッチ 40 の MRS 論理 410 及び I/O デバイス 50 のルーティング ID と、ブレード 10-1 の MMIO 空間を認識する。

#### 【0102】

PCI マネージャ 202 は、ブレード 10-1 から要求された仮想機能 502 に対する I/O デバイス 50 のアクセス用ルーティング ID から図 5 に示した VF1 及び VF2 をブレード 10-1 に割り当てる、図 4 に示した MMIO 空間に確保した VF1, VF2 の MMIO をブレード 10-1 に割り当てる。

10

20

30

40

50

## 【0103】

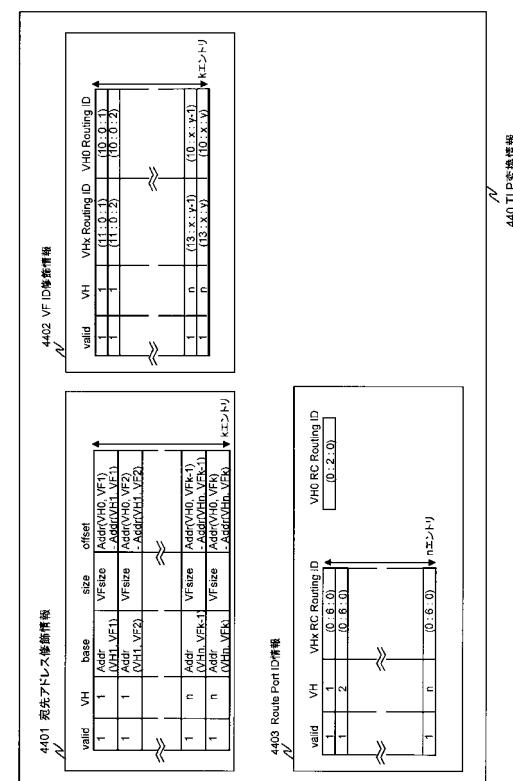

そして、PCIマネージャ202は、ブレード10-1から受信した確保要求に含まれるブレード10-1のI/Oデバイス50のアクセス用ルーティングIDと、仮想階層ナンバー1311と、MMIOのベースアドレスと、仮想階層ナンバー1311を、MR-SR変換論理530のTLR変換情報440に書き込む。このとき、PCIマネージャ202は、確保要求で要求された仮想機能502の数に応じてPCIマネージャ202が管理する仮想機能502のMMIOとブレード10-1が管理するMMIOのオフセットを求める。

## 【0104】

PCIマネージャ202は、MR-SR変換論理530のTLR変換情報440(図7)を構成する宛先アドレス変換論理4401へ、仮想機能502毎に仮想階層ナンバー1311、ブレード10-1のMMIOのベースアドレスと、MMIOのサイズと、PCIマネージャ202が管理する仮想機能502のMMIOとブレード10-1が管理するMMIOのオフセットを書き込む。PCIマネージャ202は、書き込みを行ったエントリのValidに有効であることを示す「1」をセットする。

## 【0105】

次に、PCIマネージャ202は、図5のルーティングIDからブレード10-1に割り当てた仮想機能502(VF1とVF2)のルーティングID(10:0:1と10:0:2)と、ブレード10-1から通知を受けたルーティングID(11:0:1と11:0:2)を対応づける。

## 【0106】

そして、PCIマネージャ202は、MR-SR変換論理530のTLR変換情報を構成する仮想機能ID修飾情報4402(図7)へ、各ブレードからI/Oデバイス50のアクセス用ルーティングID毎に、ブレード10-1~10-nの仮想階層ナンバー1311(VH)をVHに書き込み、I/Oデバイス50のアクセス用ルーティングIDをVH\_x\_RoutingIDに書き込み、ブレードのルーティングIDに対応するPCIマネージャ202が対応付けたルーティングIDをVH0\_RoutingIDに書き込む。PCIマネージャ202は、書き込みを行ったエントリのValidに有効であることを示す「1」をセットする。

## 【0107】

次に、PCIマネージャ202は、図7のルートポートID情報4403に、ブレード10-1のルートコンプレックスが認識したI/Oデバイス50のルーティングID(0:6:0)を仮想階層ナンバー1311毎に書き込む。PCIマネージャ202は、書き込みを行ったエントリのValidに有効であることを示す「1」をセットする。

## 【0108】

以上により、MR-SR変換論理430のTLR変換情報440にブレード10-1から受信したVF確保要求データの値を設定し、ブレード10-1がI/Oデバイス50を共有することを設定する。

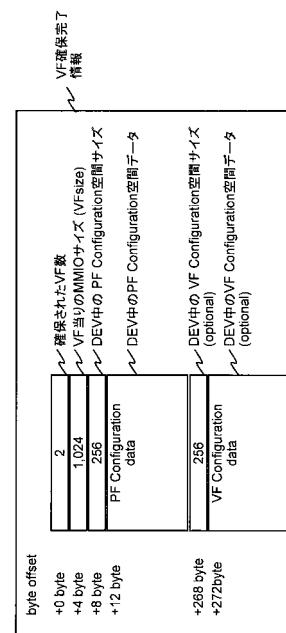

## 【0109】

PCIマネージャ202は、MR-SR変換論理430のTLR変換情報440にブレード10-1から受信したVF確保要求データの設定が完了すると、TLR変換情報440に設定した情報をVF確保完了データとしてネットワーク70からブレード10-1に送信する。VF確保完了データの一例としては図21のようになる。図21において、VF確保完了データは、PCIマネージャ202がTLR変換情報440に確保した仮想機能502の数(=2)と、仮想機能502当たりのMMIOのサイズと、I/Oデバイス50の物理機能PF501の構成情報の空間サイズと、I/Oデバイス50の物理機能501の構成空間データと、I/Oデバイス50の仮想機能502の構成空間サイズと、I/Oデバイス50の仮想機能502の構成空間データが含まれる。

## 【0110】

VF確保完了データを受信した仮想マシンモニタ100-1は、ステップS27で管理

10

20

30

40

50

端末 30 から指令された仮想計算機 101-1、101-2（ゲスト VM）を起動し、PCI マネージャ 202 から受信した I/O デバイス 50 の仮想機能 502（VF1, VF2）をそれぞれ割り当てる。

【0111】

上記の処理により、仮想マシンモニタ 100-1 が必要とする I/O デバイス 50 の仮想機能 502 を PCI マネージャ 202 が確保し、仮想マシンモニタ 100-1 は PCI マネージャ 202 が確保した仮想機能 502 を起動する仮想計算機 101-1、101-2 に割り当てることができる。

【0112】

なお、上記の処理は他のブレード 10-2 ~ 10-n を起動するときにも同様に実行され、TLR 変換情報 440 には I/O デバイス 50 を共有するブレード 10-1 ~ 10-n の情報が加えられることになる。

【0113】

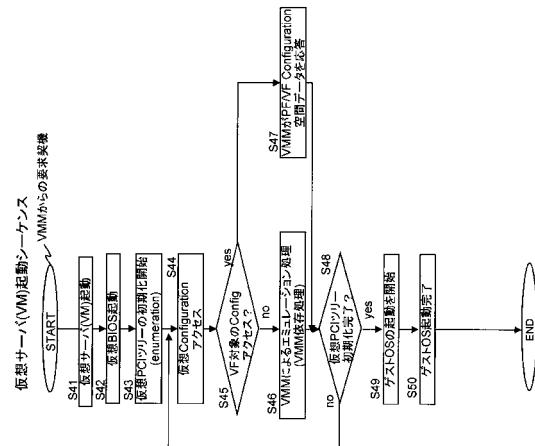

図 21 は、上記図 18 のステップ S27 で行われる仮想計算機 101-0 (101-1) の起動処理の一例を示すフローチャートである。

【0114】

仮想マシンモニタ 100-1 は、ステップ S41 で仮想計算機 101-0 を起動し、ステップ S42 で仮想計算機 101-0 に割り当たる仮想 BIOS を起動する。ステップ S42 では、仮想 BIOS によって仮想 PCI ツリーの初期化を実施する。

【0115】

ステップ S44 では、仮想 BIOS が仮想マシンモニタ 100-1 によって提供される仮想コンフィギュレーションにアクセスを開始する。ステップ S45 では、仮想マシンモニタ 100-1 は仮想 BIOS のアクセス対象が、I/O デバイス 50 の仮想機能 502 に対するものであるか否かを判定する。仮想機能 502 以外に対して仮想 BIOS がアクセスした場合には、ステップ S46 で仮想マシンモニタ (VMM) 100-1 がアクセス対象のエミュレーションを実施する。一方、仮想機能 502 に対して仮想 BIOS がアクセスした場合には、ステップ S47 で仮想マシンモニタ 100-1 が、PCI マネージャ 202 から仮想機能確保応答情報により取得した I/O デバイス 50 の物理機能 PF501 の構成情報の空間サイズと、I/O デバイス 50 の物理機能 501 の構成空間データと、I/O デバイス 50 の仮想機能 502 の構成空間サイズと、I/O デバイス 50 の仮想機能 502 の構成情報の空間データを応答する。

【0116】

ステップ S48 では、仮想マシンモニタ 100-1 が仮想 BIOS による仮想 PCI ツリーの初期化が完了したか否かを判定する。仮想 PCI ツリーの初期化が完了していなければステップ S44 に戻り上記初期化を繰り返す。一方、仮想 PCI ツリーの初期化が完了すると、ステップ S49 で仮想マシンモニタ 100-1 が OS100-0 (ゲスト OS) の起動を開始する。ステップ S50 で OS100-0 の起動が完了し、仮想計算機 101-0 でアプリケーションやサービスの提供が可能となる。

【0117】

上記により、仮想 BIOS や OS100-0 (ゲスト OS) が I/O デバイス 50 の仮想機能 502 の構成情報を取得する場合には、仮想マシンモニタ 100-1 が PCI マネージャ 202 から取得した物理機能 501 及び仮想機能 502 の情報を提供することで、OS100-0 等が VF ドライバ 103 を組み込んで仮想機能 502 を利用することが可能となる。

【0118】

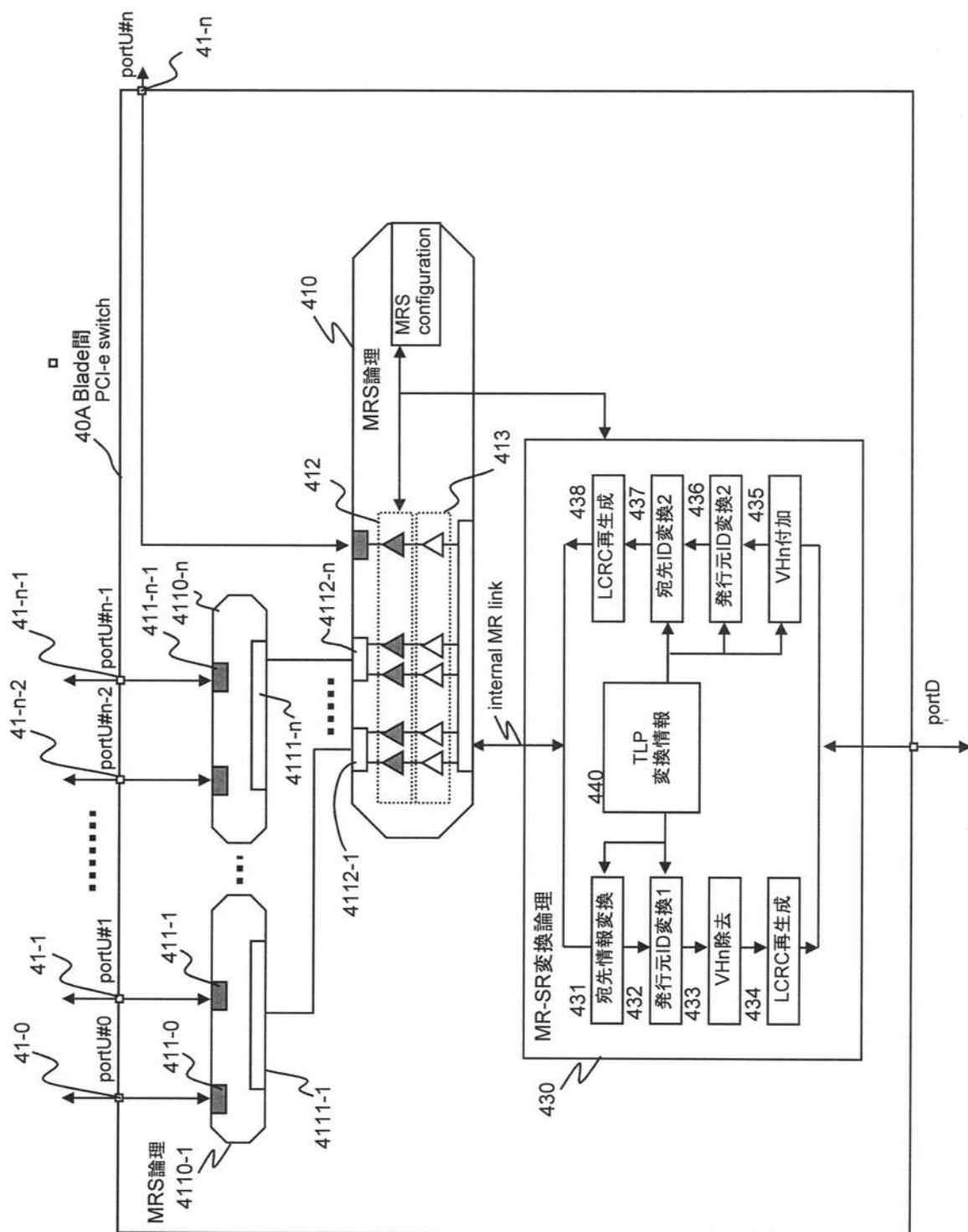

図 23 は、上記実施形態の変形例を示し、図 3 に示した MRS 論理 410 のうち、アップストリームポートブリッジ 412 に接続されるポート 411-1 ~ 411-n を MRS 論理 410 から分離して、アップストリームポート 41-0 ~ 41-n の増設を可能にしたものである。

【0119】

10

20

30

40

50

P C I - e スイッチ 4 0 のアップストリームポート 4 1 - 0 ~ 4 1 - n は、所定数（例えば、2つ）毎に M R S 論理 4 1 1 0 - 1 ~ 4 1 1 0 - n に接続される。各 M R S 論理 4 1 1 0 - 1 ~ n には、2つのポート 4 1 1 - 0、4 1 1 - 1 等がそれぞれ設けられて、アップストリームポート 4 1 - 0 ~ 4 1 - n に接続される。各 M R S 論理 4 1 1 0 - 1 ~ 4 1 1 0 - n の M R S 論理 4 1 0 側にはひとつのポート 4 1 1 1 - 1 ~ 4 1 1 1 - n が設けられており、それぞれのポート 4 1 1 1 - 1 ~ 4 1 1 1 - n は M R S 論理 4 1 0 に設けたポート 4 1 1 2 - 1 ~ 4 1 1 2 - n に接続される。

#### 【 0 1 2 0 】

この変形例では、M R S 論理 4 1 0 のアップストリームポート 4 1 - 0 ~ 4 1 - n 側を多段化することによって、ブレードサーバ 1 のアップストリームポート 4 1 - 0 ~ 4 1 - n の構成を柔軟に行うことが可能となる。 10

#### 【 0 1 2 1 】

なお、上記実施形態では、チップセット 1 3 - 1 ~ n とプロセッサ 1 1 - 1, 2 が独立した構成を示したが、プロセッサ 1 1 - 1, 2 にチップセット 1 3 - 1 ~ n が組み込まれても良い。

#### 【 0 1 2 2 】

また、上記実施形態では、P C I 管理サーバ 2 0 で P C I マネージャ 2 0 2 を稼動させる例を示したが、ブレード 1 0 - 1 ~ 1 0 - n の何れかで P C I マネージャ 2 0 2 を稼動させてもよい。

#### 【 産業上の利用可能性 】

20

#### 【 0 1 2 3 】

以上のように、本発明は、複数の物理計算機を P C I - e x p r e s s のスイッチで I / O デバイスに接続する計算機システムに適用することができ、特に、物理計算機が M R - I O V でアクセスを行い、I / O デバイスが S R - I O V でアクセスする計算機システム及び P C I スイッチに好適である。

#### 【 図面の簡単な説明 】

#### 【 0 1 2 4 】

【 図 1 】 本発明を適用したブレードサーバのハードウェア構成を示すブロック図。

【 図 2 】 同じくブレードサーバの機能要素を示すブロック図。

【 図 3 】 P C I - e スイッチの内部を示すブロック図。 30

【 図 4 】 各ブレードと P C I 管理サーバの M M I O 空間の関係を示す説明図。

【 図 5 】 各ブレードと P C I 管理サーバのルーティング I D の関係を示す説明図。

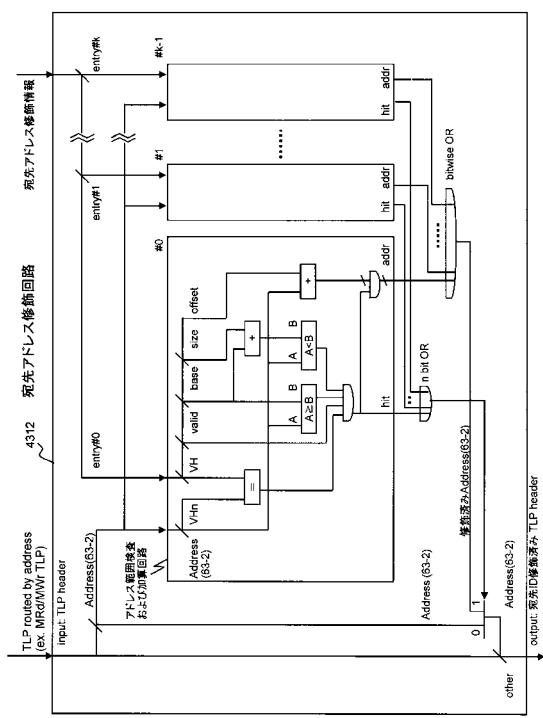

【 図 6 】 M R - S R 変換論理の宛先情報変換回路の構成を示すブロック図。

【 図 7 】 T L P 情報の構成を示す説明図。

【 図 8 】 宛先情報変換回路を構成する宛先アドレス修飾部の構成を示すブロック図。

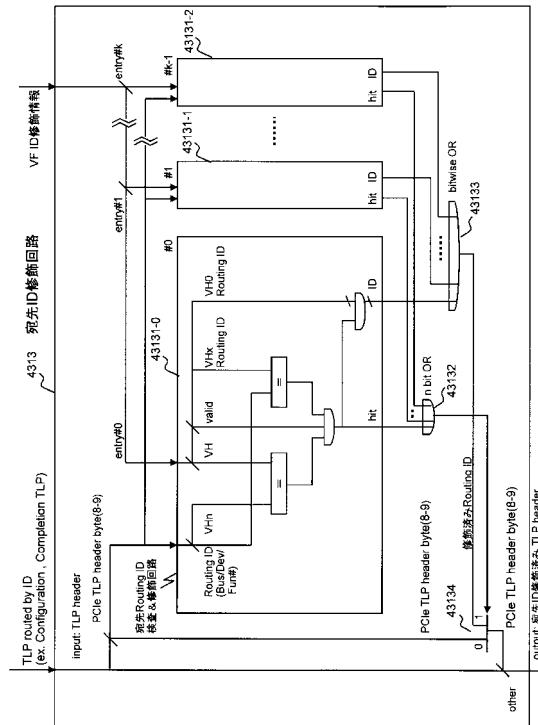

【 図 9 】 宛先情報変換回路を構成する宛先 I D 修飾部の構成を示すブロック図。

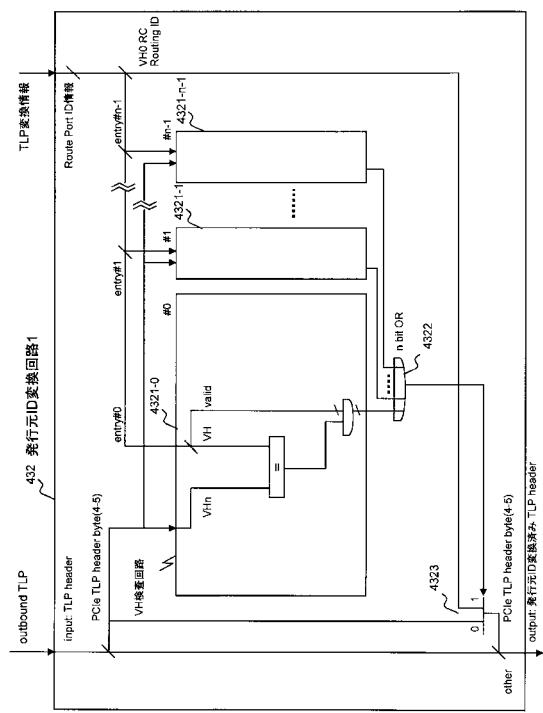

【 図 1 0 】 発行元 I D 変換回路 1 の構成を示すブロック図。

【 図 1 1 】 仮想階層ナンバー付加回路の構成を示すブロック図。

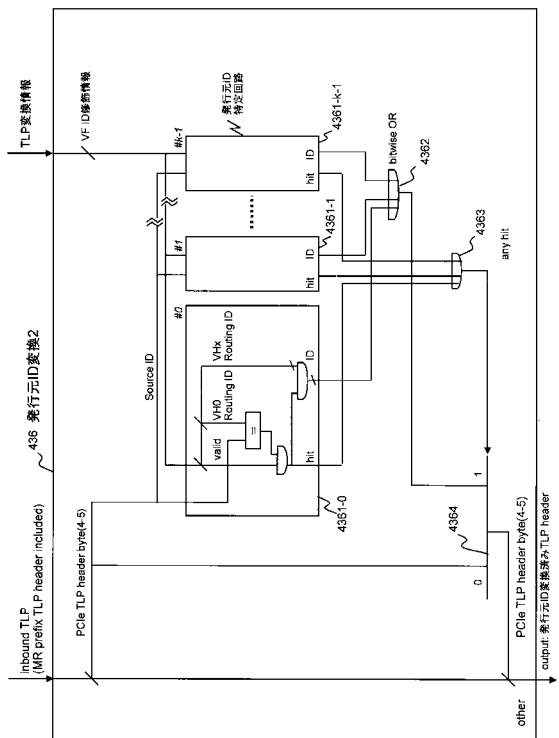

【 図 1 2 】 発行元 I D 変換回路 2 の構成を示すブロック図。

【 図 1 3 】 宛先 I D 変換回路 2 の構成を示すブロック図。 40

【 図 1 4 】 マルチルート T L P 及び P C I e ベース T L P のフォーマットを示す説明図。

【 図 1 5 】 マルチルート T L P 及び P C I e ベース T L P の T L P ヘッダのフォーマットを示す説明図。

【 図 1 6 】 ブレードサーバの電源投入の手順を示すフローチャート。

【 図 1 7 】 P C I 管理サーバ 2 0 で行われる起動処理を示すフローチャート。

【 図 1 8 】 ブレードで行われる仮想マシンモニタの起動処理を示すフローチャート。

【 図 1 9 】 マルチルート化可能フォーマットを示す説明図。

【 図 2 0 】 仮想機能確保要求情報のフォーマットを示す説明図。

【 図 2 1 】 仮想機能確保完了情報のフォーマットを示す説明図。

【 図 2 2 】 仮想計算機の起動処理を示すフローチャート。 50

【図4】

( 6 )

【図5】

( 四 7 )

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図16】

【図17】

【 図 1 8 】

【図20】

【図19】

【図21】

## 【図22】

【図3】

【図14】

## MR TLPフォーマット、およびPCIe base TLPフォーマット

【図15】

【図23】

---

フロントページの続き

(72)発明者 上原 敬太郎

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

審査官 横山 佳弘

(56)参考文献 特開2008-078887 (JP, A)

特開2009-301162 (JP, A)

国際公開第2008/018485 (WO, A1)

特開2008-021252 (JP, A)

特開2007-219873 (JP, A)

鈴木 順 Jun Suzuki, Expresser (エクスプレスイーサ)による単一ホスト仮想化対応I/Oのマルチホスト同時共有, 第70回(平成20年)全国大会講演論文集(1) アーキテクチャ ソフトウェア科学・工学 データベースとメディア, 日本, 社団法人情報処理学会, 2008年 3月13日, p. 1-23~p. 1-24

(58)調査した分野(Int.Cl., DB名)

G 06 F 13 / 10

G 06 F 13 / 14

G 06 F 9 / 46