(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6953263号

(P6953263)

(45) 発行日 令和3年10月27日(2021.10.27)

(24) 登録日 令和3年10月1日(2021.10.1)

(51) Int.Cl.

F 1

HO4N 5/3745 (2011.01)

HO4N 5/3745

HO4N 5/357 (2011.01)

HO4N 5/357

HO4N 5/3745 700

請求項の数 28 (全 19 頁)

(21) 出願番号

特願2017-195154 (P2017-195154)

(22) 出願日

平成29年10月5日(2017.10.5)

(65) 公開番号

特開2019-68382 (P2019-68382A)

(43) 公開日

平成31年4月25日(2019.4.25)

審査請求日

令和2年10月2日(2020.10.2)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100101498

弁理士 越智 隆夫

(74) 代理人 100106183

弁理士 吉澤 弘司

(74) 代理人 100128668

弁理士 斎藤 正巳

(72) 発明者 篠原 真人

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

最終頁に続く

(54) 【発明の名称】 固体撮像装置および撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換部と、前記光電変換部に電気的に接続される第1の入力ノード、第1の主ノードおよび第2の主ノードを備える増幅トランジスタとを各々が有する複数の画素と、

第2の入力ノードと、第3の主ノードと、第4の主ノードとを備え、前記増幅トランジスタと同じ極性の第1のトランジスタと、

前記複数の画素の各々の前記第1の主ノードが電気的に接続される信号線と、

前記信号線に電気的に接続される電流源と、

前記複数の画素を各々が含む複数の画素群と、

を有し、

前記第3の主ノードには電源電圧が与えられ、

前記第4の主ノードと、前記第2の主ノードとが電気的に接続され、

前記第1の主ノードと前記第2の入力ノードとが電気的に接続され、

前記複数の画素群のそれぞれに対応して、複数の前記信号線の各々が対応して設けられ、

前記第1のトランジスタが、複数の前記信号線の各々に対応して設けられていることを特徴とする固体撮像装置。

## 【請求項 2】

光電変換部と、前記光電変換部に電気的に接続される第1の入力ノード、第1の主ノードおよび第2の主ノードを備える増幅トランジスタとを各々が有する複数の画素と、

10

20

第2の入力ノードと、第3の主ノードと、第4の主ノードとを備え、前記增幅トランジスタと同じ極性の第1のトランジスタと、

前記複数の画素の各々の前記第1の主ノードが電気的に接続される信号線と、

前記信号線に電気的に接続される電流源とを有し、

前記電流源が供給する駆動電流によって動作するフィードバック回路を有し、

前記フィードバック回路は、前記第1のトランジスタを備え、前記画素毎に設けられていることを特徴とする固体撮像装置。

【請求項3】

前記電流源は前記增幅トランジスタに駆動電流を供給することを特徴とする請求項2に記載の固体撮像装置。

10

【請求項4】

前記第1のトランジスタの前記第2の入力ノードは前記增幅トランジスタの前記第1の主ノードに電気的に接続され、前記第1のトランジスタの前記第4の主ノードは前記增幅トランジスタの前記第2の主ノードに電気的に接続され、前記第1のトランジスタの前記第3の主ノードには電源電圧が印加されることを特徴とする請求項3に記載の固体撮像装置。

【請求項5】

前記第1のトランジスタは、ソースフォロワ動作を行うことを特徴とする請求項4に記載の固体撮像装置。

【請求項6】

前記第1のトランジスタの極性は前記增幅トランジスタの極性と同じであって、前記第1のトランジスタはデプレッション型であることを特徴とする請求項4または5に記載の固体撮像装置。

20

【請求項7】

前記增幅トランジスタの前記第1の入力ノードをリセット電圧にリセットするリセットトランジスタを備え、

前記第1のトランジスタの閾値電圧を  $V_{th1}$ 、前記第1のトランジスタの電流値およびコンダクタンスによって定まる電圧を  $V_1$ 、前記增幅トランジスタの電流値およびコンダクタンスによって定まる電圧を  $V_2$  とした場合において、

$$- V_2 - V_1 = V_{th1}$$

30

が満たされることを特徴とする請求項6に記載の固体撮像装置。

【請求項8】

前記增幅トランジスタの閾値電圧を  $V_{th2}$ 、前記リセット電圧を  $V_{RES}$ 、前記電源電圧を  $V_{DD}$  とした場合において、

$$V_{RES} = V_{DD} + V_{th2} + V_{th1} + V_2$$

が満たされることを特徴とする請求項7に記載の固体撮像装置。

【請求項9】

前記リセット電圧  $V_{RES}$  は前記電源電圧  $V_{DD}$  よりも低いことを特徴とする請求項8に記載の固体撮像装置。

【請求項10】

前記画素は複数の前記光電変換部を備えることを特徴とする請求項3乃至9のいずれか1項に記載の固体撮像装置。

40

【請求項11】

前記增幅トランジスタの前記第1の主ノードの領域と前記第1のトランジスタの前記第2の入力ノードの電極とを電気的に接続する第1の配線は、平面視において、前記增幅トランジスタの前記第1の入力ノードの電極の少なくとも一部と交差することを特徴とする請求項4に記載の固体撮像装置。

【請求項12】

前記增幅トランジスタの前記第1の主ノードと前記信号線との間に設けられた選択トランジスタと、

50

浮遊拡散領域と前記増幅トランジスタの前記第1の入力ノードの電極とを電気的に接続する第2の配線と、

前記選択トランジスタの入力ノードの電極に電気的に接続された第3の配線とを備え、

前記第1の配線の少なくとも一部は、平面視において前記第2の配線と前記第3の配線との間に位置することを特徴とする請求項1\_1に記載の固体撮像装置。

【請求項13】

請求項1～1\_2のいずれか1項に記載の固体撮像装置と、

前記固体撮像装置から出力された画像信号を処理する信号処理部と

を有することを特徴とする撮像システム。

【請求項14】

前記画素が2つの前記光電変換部を含み、

前記信号処理部は、2つの前記光電変換部にて生成された前記画像信号をそれぞれ処理し、前記固体撮像装置から被写体までの距離情報を取得することを特徴とする請求項1\_3に記載の撮像システム。

【請求項15】

光電変換部と、前記光電変換部に電気的に接続される第1の入力ノード、第1の主ノードおよび第2の主ノードを備える増幅トランジスタとを各々が有する複数の画素と、

第2の入力ノードと、第3の主ノードと、第4の主ノードとを備え、前記増幅トランジスタと同じ極性の第1のトランジスタと、

前記複数の画素の各々の前記第1の主ノードが電気的に接続される信号線と、

前記信号線に電気的に接続される電流源とを有し、

前記第3の主ノードには電源電圧が与えられ、

前記第4の主ノードと、前記第2の主ノードとが電気的に接続され、

前記第1の主ノードと前記第2の入力ノードとが電気的に接続され、

前記増幅トランジスタの前記第1の主ノードと前記第1のトランジスタの前記第2の入力ノードとを電気的に接続する第1の配線は、平面視において、前記増幅トランジスタの前記第1の入力ノードの電極の少なくとも一部と交差することを特徴とする固体撮像装置。

【請求項16】

前記複数の画素の各々が前記第1のトランジスタを有することを特徴とする請求項1\_5に記載の固体撮像装置。

【請求項17】

前記複数の画素の各々は、

前記増幅トランジスタの前記第1の主ノードと前記信号線との間に設けられた選択トランジスタと、

前記光電変換部に電気的に接続される浮遊拡散領域と、

前記浮遊拡散領域と前記増幅トランジスタの前記第1の入力ノードとを電気的に接続する第2の配線と、

前記選択トランジスタの入力ノードに電気的に接続された第3の配線とを備え、

前記第1の配線の少なくとも一部は、平面視において前記第2の配線と前記第3の配線との間に位置することを特徴とする請求項1\_6に記載の固体撮像装置。

【請求項18】

光電変換部と、前記光電変換部に電気的に接続される第1の入力ノード、第1の主ノードおよび第2の主ノードを備える増幅トランジスタとを各々が有する複数の画素と、

第2の入力ノードと、第3の主ノードと、第4の主ノードとを備え、前記増幅トランジスタと同じ極性の第1のトランジスタと、

前記複数の画素の各々の前記第1の主ノードが電気的に接続される信号線と、

前記信号線に電気的に接続される電流源とを有し、

前記電流源が供給する駆動電流によって動作するフィードバック回路を有し、

前記増幅トランジスタの前記第1の主ノードと前記第1のトランジスタの前記第2の入

10

20

30

40

50

力ノードとを電気的に接続する第1の配線は、平面視において、前記增幅トランジスタの前記第1の入力ノードの電極の少なくとも一部と交差することを特徴とする固体撮像装置。

【請求項19】

前記フィードバック回路は前記画素毎に設けられていることを特徴とする請求項18に記載の固体撮像装置。

【請求項20】

前記複数の画素の各々は、

前記增幅トランジスタの前記第1の主ノードと前記信号線との間に設けられた選択トランジスタと、

前記光電変換部に電気的に接続される浮遊拡散領域と、

前記浮遊拡散領域と前記增幅トランジスタの前記第1の入力ノードとを電気的に接続する第2の配線と、

前記選択トランジスタの入力ノードに電気的に接続された第3の配線とを備え、

前記第1の配線の少なくとも一部は、平面視において前記第2の配線と前記第3の配線との間に位置することを特徴とする請求項19に記載の固体撮像装置。

【請求項21】

光電変換部と、前記光電変換部に電気的に接続される第1の入力ノード、第1の主ノードおよび第2の主ノードを備える増幅トランジスタとを各々が有する複数の画素と、

第2の入力ノードと、第3の主ノードと、第4の主ノードとを備え、前記增幅トランジスタと同じ極性の第1のトランジスタと、

前記複数の画素の各々の前記第1の主ノードが電気的に接続される信号線と、

前記信号線に電気的に接続される電流源とを有し、

前記第3の主ノードには電源電圧が与えられ、

前記第4の主ノードと、前記第2の主ノードとが電気的に接続され、

前記第1の主ノードと前記第2の入力ノードとが電気的に接続され、

前記增幅トランジスタの前記第1の入力ノードをリセット電圧にリセットするリセットトランジスタを備え、

前記第1のトランジスタの閾値電圧をV<sub>th1</sub>、前記第1のトランジスタの電流値およびコンダクタンスによって定まる電圧をV<sub>1</sub>、前記增幅トランジスタの電流値およびコンダクタンスによって定まる電圧をV<sub>2</sub>とした場合において、

- V<sub>2</sub> - V<sub>1</sub> V<sub>th1</sub>

が満たされることを特徴とする固体撮像装置。

【請求項22】

前記複数の画素の各々が前記第1のトランジスタを有することを特徴とする請求項21に記載の固体撮像装置。

【請求項23】

前記增幅トランジスタの前記第1の主ノードと前記第1のトランジスタの前記第2の入力ノードとを電気的に接続する第1の配線は、平面視において、前記增幅トランジスタの前記第1の入力ノードの電極の少なくとも一部と交差することを特徴とする請求項22に記載の固体撮像装置。

【請求項24】

前記複数の画素の各々は、

前記增幅トランジスタの前記第1の主ノードと前記信号線との間に設けられた選択トランジスタと、

前記光電変換部に電気的に接続される浮遊拡散領域と、

前記浮遊拡散領域と前記增幅トランジスタの前記第1の入力ノードとを電気的に接続する第2の配線と、

前記選択トランジスタの入力ノードに電気的に接続された第3の配線とを備え、

前記第1の配線の少なくとも一部は、平面視において前記第2の配線と前記第3の配線

10

20

30

40

50

との間に位置することを特徴とする請求項2\_3に記載の固体撮像装置。

【請求項 2\_5】

光電変換部と、前記光電変換部に電気的に接続される第1の入力ノード、第1の主ノードおよび第2の主ノードを備える増幅トランジスタとを各々が有する複数の画素と、

第2の入力ノードと、第3の主ノードと、第4の主ノードとを備え、前記増幅トランジスタと同じ極性の第1のトランジスタと、

前記複数の画素の各々の前記第1の主ノードが電気的に接続される信号線と、

前記信号線に電気的に接続される電流源とを有し、

前記電流源が供給する駆動電流によって動作するフィードバック回路を有し、

前記電流源は前記増幅トランジスタに駆動電流を供給し、

前記フィードバック回路は前記第1のトランジスタを備え、

前記第1のトランジスタの前記第2の入力ノードは前記増幅トランジスタの前記第1の主ノードに電気的に接続され、前記第1のトランジスタの前記第4の主ノードは前記増幅トランジスタの前記第2の主ノードに電気的に接続され、前記第1のトランジスタの前記第3の主ノードには電源電圧が印加され、

前記第1のトランジスタは、ソースフォロワ動作を行い、

前記第1のトランジスタの極性は前記増幅トランジスタの極性と同じであって、前記第1のトランジスタはデプレッション型であり、

前記増幅トランジスタの前記第1の入力ノードをリセット電圧にリセットするリセットトランジスタを備え、

前記第1のトランジスタの閾値電圧を  $V_{th1}$ 、前記第1のトランジスタの電流値およびコンダクタンスによって定まる電圧を  $V_1$ 、前記増幅トランジスタの電流値およびコンダクタンスによって定まる電圧を  $V_2$  とした場合において、

-  $V_2 - V_1 = V_{th1}$

が満たされることを特徴とする固体撮像装置。

【請求項 2\_6】

前記フィードバック回路は前記画素毎に設けられていることを特徴とする請求項2\_5に記載の固体撮像装置。

【請求項 2\_7】

前記増幅トランジスタの前記第1の主ノードと前記第1のトランジスタの前記第2の入力ノードとを電気的に接続する第1の配線は、平面視において、前記増幅トランジスタの前記第1の入力ノードの電極の少なくとも一部と交差することを特徴とする請求項2\_6に記載の固体撮像装置。

【請求項 2\_8】

前記複数の画素の各々は、

前記増幅トランジスタの前記第1の主ノードと前記信号線との間に設けられた選択トランジスタと、

前記光電変換部に電気的に接続される浮遊拡散領域と、

前記浮遊拡散領域と前記増幅トランジスタの前記第1の入力ノードとを電気的に接続する第2の配線と、

前記選択トランジスタの入力ノードに電気的に接続された第3の配線とを備え、

前記第1の配線の少なくとも一部は、平面視において前記第2の配線と前記第3の配線との間に位置することを特徴とする請求項2\_7に記載の固体撮像装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、固体撮像装置および撮像システムに関する。

【背景技術】

【0002】

固体撮像装置として近年主流となっているCMOSイメージセンサは、入射光に応じた

10

20

30

40

50

信号電荷を蓄積するフォトダイオードと、信号電荷に応じた信号電圧を出力する増幅トランジスタと、増幅トランジスタの負荷となる定電流回路とを備える。増幅トランジスタのゲートはフォトダイオードの信号電荷を信号電圧に変換する浮遊拡散容量を形成する。増幅トランジスタはソースフォロワとして動作し、浮遊拡散容量における信号電圧を低インピーダンスで出力する。ここで、浮遊拡散容量の容量を小さくすることにより、信号電圧の振幅は大きくなり、画素の後段の信号処理部における信号対雑音比を向上させることができる。

#### 【 0 0 0 3 】

特許文献 1 には、増幅トランジスタから出力された信号電圧を増幅トランジスタのドレインにフィードバックすることにより、増幅トランジスタのゲートおよびドレイン間の容量を実効的に小さくするフィードバック回路が記載されている。 10

#### 【先行技術文献】

#### 【特許文献】

#### 【 0 0 0 4 】

#### 【特許文献 1】特開 2008 - 42814 号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【 0 0 0 5 】

特許文献 1 に記載のフィードバック回路は増幅トランジスタのみならず定電流回路にも電流を供給している。このため、撮像装置の消費電流が増大するという課題が生じていた。 20

#### 【課題を解決するための手段】

#### 【 0 0 0 6 】

本発明の一実施形態における固体撮像装置は、光電変換部と、前記光電変換部に電気的に接続される第 1 の入力ノード、第 1 の主ノードおよび第 2 の主ノードを備える増幅トランジスタとを各々が有する複数の画素と、第 2 の入力ノードと、第 3 の主ノードと、第 4 の主ノードとを備え、前記増幅トランジスタと同じ極性の第 1 のトランジスタと、前記複数の画素の各々の前記第 1 の主ノードが電気的に接続される信号線と、前記信号線に電気的に接続される電流源と、前記複数の画素を各々が含む複数の画素群と、を有し、前記第 3 の主ノードには電源電圧が与えられ、前記第 4 の主ノードと、前記第 2 の主ノードとが電気的に接続され、前記第 1 の主ノードと前記第 2 の入力ノードとが電気的に接続され、前記複数の画素群のそれぞれに対応して、複数の前記信号線の各々が対応して設けられ、前記第 1 のトランジスタが、複数の前記信号線の各々に対応して設けられている。 30

#### 【 0 0 0 7 】

本発明の他の実施形態における固体撮像装置は、光電変換部と、前記光電変換部に電気的に接続される第 1 の入力ノード、第 1 の主ノードおよび第 2 の主ノードを備える増幅トランジスタとを各々が有する複数の画素と、第 2 の入力ノードと、第 3 の主ノードと、第 4 の主ノードとを備え、前記増幅トランジスタと同じ極性の第 1 のトランジスタと、前記複数の画素の各々の前記第 1 の主ノードが電気的に接続される信号線と、前記信号線に電気的に接続される電流源とを有し、前記電流源が供給する駆動電流によって動作するフィードバック回路を有し、前記第 1 のトランジスタを備え、前記フィードバック回路は前記画素毎に設けられている。 40

#### 【発明の効果】

#### 【 0 0 0 8 】

本発明によれば、消費電流の増加を抑制しながら、信号対雑音比を向上させることが可能となる。

#### 【図面の簡単な説明】

#### 【 0 0 0 9 】

#### 【図 1】第 1 実施形態における固体撮像装置のブロック図である。

10

20

30

40

50

【図2】第1実施形態における画素の等価回路図である。

【図3】第2実施形態における画素の等価回路図である。

【図4】第2実施形態における画素の平面図である。

【図5】第3実施形態における画素の等価回路図である。

【図6】第4実施形態における画素の等価回路図である。

【図7】第5実施形態における画素の等価回路図である。

【図8】第6実施形態における撮像システムのブロック図である。

【図9】第7実施形態における車載カメラにおける撮像システムのブロック図である。

【発明を実施するための形態】

【0010】

10

以下、本発明の実施形態を説明する。第1乃至第5実施形態における固体撮像装置は、光電変換部および増幅トランジスタを各々が有する複数の画素と、増幅トランジスタと同じ極性のトランジスタとを備える。増幅トランジスタは第1の入力ノード、第1の主ノード、第2の主ノードを備え、増幅トランジスタと同じ極性のトランジスタは第2の入力ノード、第3の主ノード、第4の主ノードを備える。複数の画素の各々の増幅トランジスタの第1の入力ノードは信号線に電気的に接続され、信号線は電流源に電気的に接続される。トランジスタは信号線毎または画素毎に設けられ得る。第3の主ノードには電源電圧が与えられ、第4の主ノードと、第2の主ノードとが電気的に接続され、増幅トランジスタの第1の主ノードとトランジスタの第2の入力ノードとが電気的に接続される。したがって、トランジスタは、増幅トランジスタの第1の主ノードの電圧に応じた電圧を増幅トランジスタの第2の主ノードに供給し、増幅トランジスタがソースフォロワとして動作する駆動電流によって動作する。

20

【0011】

30

増幅トランジスタの入力ノードの電圧と第2の主ノードの電圧とは一定の電圧差を保持しながら変化する。増幅トランジスタの入力ノードと第2の主ノードとの間の容量を実質的に無くし、若しくは極めて小さくするとともに、チャネル長変調効果を抑制することができる。これにより、出力ゲインを高くし、信号対雑音比を向上させることができる。また、フィードバックのためのトランジスタは増幅トランジスタの駆動電流のみによって動作するため、消費電流の増加を抑制しながら信号対雑音比を高めることができる。

【0012】

以下、本発明の実施形態について図面を用いて説明する。本発明は、以下に説明される実施形態に限定されない。例えば、以下のいずれかの実施形態の一部の構成を、他の実施形態に追加し、あるいは他の実施形態の一部の構成と置換してもよい。

【0013】

[第1実施形態]

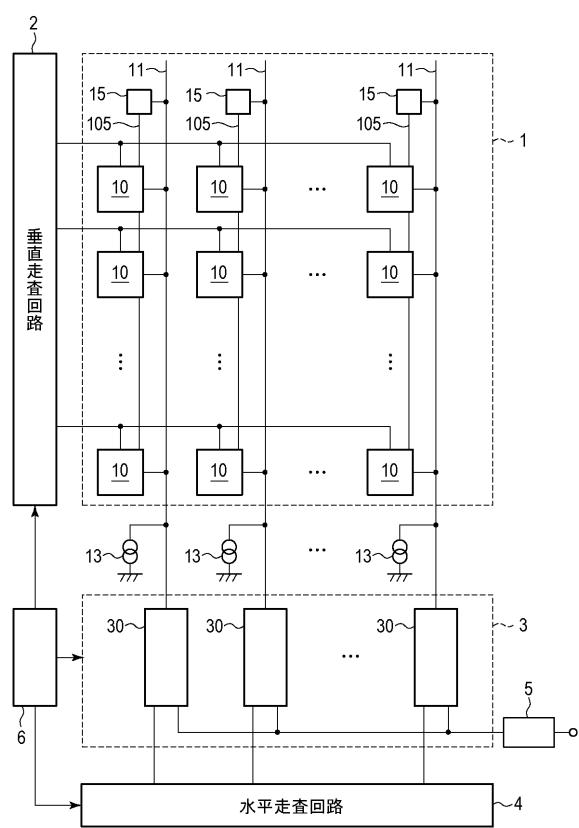

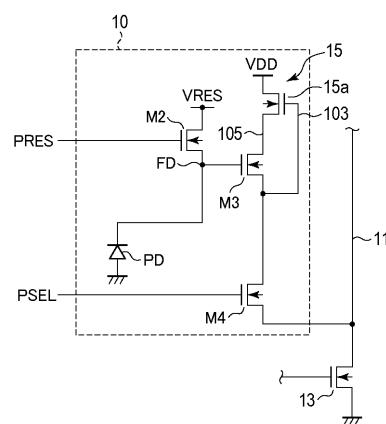

図1は本実施形態における固体撮像装置のブロック図である。固体撮像装置は、例えばCMOS (C o m p l e m e n t a r y M e t a l O x i d e S e m i c o n d u c t o r) イメージセンサであって、画素部1、垂直走査回路2、列回路3、水平走査回路4、出力回路5、制御回路6、列信号線11、電流源13を備える。

40

【0014】

画素部1は行列状に配列された複数の画素10を備え、それぞれの画素10は照射光に基づき信号電荷を生成および蓄積する光電変換部を備える。なお、本明細書において、行方向とは図面における水平方向を示し、列方向とは図面において垂直方向を示すものとする。画素10上にはマイクロレンズ、カラーフィルタが配置され得る。カラーフィルタは例えば赤、青、緑の原色フィルタであって、ペイヤー配列に従って各画素10に設けられている。一部の画素10はOB画素（オブティカル・ブラック画素）として遮光されている。複数の画素10には、焦点検出用の画素信号を出力する焦点検出画素が配された測距行と、画像を生成するための画素信号を出力する撮像画素が配された複数の撮像行とが設けられ得る。列信号線11は画素10の列毎に設けられ、列信号線11には電流源13が

50

電気的に接続される。本実施形態においては、列信号線 11 每にフィードバック回路 15 が設けられているが、複数の画素 10 を含む画素群毎にフィードバック回路 15 が設けられても良い。フィードバック回路 15 は列信号線 11 における信号電圧に応じた電圧を電圧供給線 105 を介して各列の複数の画素 10 に供給している。

#### 【0015】

垂直走査回路 2 はシフトレジスタ、ゲート回路、バッファ回路などから構成され、垂直同期信号、水平同期信号、クロック信号などに基づき行毎に駆動パルスを選択的に画素 10 に出力する。駆動パルスは、行ごと、順次、もしくはランダムに供給され得る。列回路 3 は列信号線 11 每の信号処理回路 30 を備える。信号処理回路 30 は差動增幅回路、保持回路を備え、画素 10 から列信号線 11 に出力された画素信号を增幅するとともに、一時的に保持する。信号処理回路 30 は画素 10 のリセット時の画素信号と光電変換時の画素信号との差分を算出することにより、相関二重サンプリングを行うことができる。

10

#### 【0016】

水平走査回路 4 はシフトレジスタを備え、信号処理回路 30 に保持された画素信号を順に読み出す。出力回路 5 は差動增幅回路、バッファ回路、クランプ回路を備え、水平走査回路 4 から読み出された画素信号を固体撮像装置の外部へと出力する。このような構成により、光学系を介して画素部 1 上に照射された光を電気信号である二次元の画像信号として出力させることができる。なお、出力回路 5 にアナログ・デジタル変換回路を設け、デジタルの画像信号を出力しても良い。または、列毎にアナログ・デジタル変換回路を設けても良い。制御回路 6 は、クロック、同期信号などに基づき様々な制御信号、駆動信号を生成するタイミングジェネレータとして機能する。

20

#### 【0017】

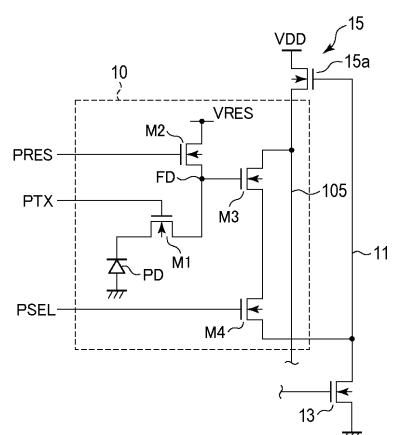

図 2 は本実施形態における画素 10 の等価回路図である。画素 10 は、光電変換部 PD、転送トランジスタ M1、浮遊拡散領域 FD (Floating Diffusion)、リセットトランジスタ M2、増幅トランジスタ M3、選択トランジスタ M4 を含む。以下の説明は、画素 10 を構成するトランジスタが N チャネル MOS トランジスタである例を示している。光電変換部 PD は例えばフォトダイオードから構成されており、入射光による光電変換および電荷の蓄積を行なう。なお、光電変換部 PD はフォトダイオードに限定されず、光電効果を生じさせる材料であれば良い。さらに、埋め込み型のフォトダイオードを構成することで、暗電流ノイズを低減できる。光電変換部 PD にはマイクロレンズが設けられており、マイクロレンズにより集光された光が光電変換部 PD に入射する。

30

#### 【0018】

転送トランジスタ M1 は光電変換部 PD に対応して設けられ、ゲートには垂直走査回路 2 から駆動パルス P TX が印加される。駆動パルス P TX がハイレベルとなると、転送トランジスタ M1 がオン状態（導通状態）となり、光電変換部 PD に蓄積された信号電荷が増幅トランジスタ M3 のゲート（第 1 の入力ノード）に形成された浮遊拡散領域 FD に転送される。また、駆動パルス P TX がローレベルとなると、転送トランジスタ M1 はオフ状態（非導通状態）となる。転送トランジスタ M1 をオンまたはオフすることにより、光電変換部 PD の信号電荷を浮遊拡散領域 FD に転送することができる。浮遊拡散領域 FD は信号電荷を電圧に変換し、増幅トランジスタ M3 はゲート電圧に応じた信号電圧をソース（第 1 の主ノード）から選択トランジスタ M4 を介して列信号線 11 へ出力する。

40

#### 【0019】

リセットトランジスタ M2 のソースは浮遊拡散領域 FD に接続され、ゲートには垂直走査回路 2 から駆動パルス P RES が印加される。駆動パルス P RES がハイレベルとなると、リセットトランジスタ M2 はオン状態となり、浮遊拡散領域 FD にリセット電圧 V RES が供給される。選択トランジスタ M4 は増幅トランジスタ M3 と列信号線 11 との間に設けられており、選択トランジスタ M4 のゲートには垂直走査回路 2 から駆動パルス P SEL が印加される。駆動パルス P SEL がハイレベルとなると、増幅トランジスタ M3 と列信号線 11 とが電気的に導通する。列信号線 11 には電流源 13 が電気的に接続されている。電流源 13 は MOS トランジスタから構成され、ドレインは列信号線 11 に電気

50

的に接続され、ソースはグランド配線に電気的に接続される。電流源 13 のゲートには所定の電位が印加され、電流源 13 は列信号線 11 を介して増幅トランジスタ M3 のソースに一定のバイアス電流を供給する。

【0020】

フィードバック回路 15 は、本実施形態においては列信号線 11 毎に設けられ、増幅トランジスタ M3 から出力された信号電圧に追従して変化する電圧を増幅トランジスタ M3 のドレイン（第 2 の主ノード）に供給する。フィードバック回路 15 は、一例として、N チャネル MOS のフィードバック用トランジスタ 15a から構成され、フィードバック用トランジスタ 15a の極性は増幅トランジスタ M3 の極性と同じであり得る。フィードバック用トランジスタ 15a において、ゲート（第 2 の入力ノード）は列信号線 11 に接続され、ドレイン（第 3 の主ノード）は電源電圧 VDD の電源配線に接続され、ソース（第 4 の主ノード）は電圧供給線 105 を介して増幅トランジスタ M3 のドレインに接続される。このように、フィードバック用トランジスタ 15a は電源配線と増幅トランジスタ M3 のドレインとの間に直列に接続される。選択トランジスタ M4 がオン状態である場合、電流源 13 から増幅トランジスタ M3 に駆動電流が供給され、フィードバック用トランジスタ 15a は増幅トランジスタ M3 に供給された駆動電流のみによってソースフォロワとして動作する。ここで、「駆動電流のみによって」は、実質的に解釈されるべきであって、漏れ電流などのように半導体設計上、回避し得ない電流分を排除する趣旨ではない。

10

【0021】

ここで、フィードバック用トランジスタ 15a の閾値電圧を  $V_{th1}$  とすると、フィードバック用トランジスタ 15a のソース電圧、すなわち増幅トランジスタ M3 のドレイン電圧  $V_D$  は、列信号線 11 の信号電圧よりも電圧  $V_1$  および閾値電圧  $V_{th1}$  だけ低くなる。よって、ドレイン電圧  $V_D$  は式 1 で表される。電圧  $V_0$  は列信号線 11 の信号電圧であり、電圧  $V_1$  は電流源 13 から供給される電流値およびコンダクタンスによって定まる電圧である。

20

$$V_D = V_0 - V_{th1} - V_1 \quad (式 1)$$

【0022】

一方、増幅トランジスタ M3 がソースフォロワとして動作する場合、増幅トランジスタ M3 のゲート電圧  $V_G$  およびドレイン電圧  $V_D$  は一定の電圧差を保ちながら変化する。このため、増幅トランジスタ M3 のゲート・ドレイン間の容量は実質的にゼロ、若しくは極めて低い値となる。さらに、増幅トランジスタ M3 のソース・ドレイン間の電圧は信号電圧の大きさによらず一定であるため、チャンネル長変調効果が抑制され、ソースフォロワの出力ゲインを高くすることが可能となる。

30

【0023】

また、増幅トランジスタ M3 の閾値電圧を  $V_{th2}$ 、ドレイン電圧を  $V_D$ 、ゲート電圧を  $V_G$  とした場合、増幅トランジスタ M3 がソースフォロワとして動作するためには以下の式 2 の条件を満たせば良い。

$$V_D = V_G - V_{th2} \quad (式 2)$$

【0024】

さらに、列信号線 11 の信号電圧  $V_0$  は、以下の式 3 によって表される。

40

$$V_0 = V_G - V_{th2} - V_2 \quad (式 3)$$

【0025】

ここで、 $V_2$  は、電流源 13 から供給される電流値と増幅トランジスタ M3 のコンダクタンスと選択トランジスタ M4 のオン抵抗とによって定まる電圧である。式 1 および式 3 から以下の式 4 が導かれる。

$$V_D = V_G - V_{th2} - V_2 - V_{th1} - V_1 \quad (式 4)$$

【0026】

よって、ソースフォロワ動作条件に関する式 2 を式 4 に代入することにより以下の式 5 が導かれる。

$$V_G - V_{th2} - V_2 - V_{th1} - V_1 = V_G - V_{th2} \quad (式 5)$$

50

## 【0027】

式5を整理し、以下の式6が導かれる。

$$- V_2 - V_1 V_{th1} \quad (\text{式6})$$

## 【0028】

$V_1$ 、 $V_2$ はともに正の値なので閾値電圧 $V_{th1}$ は負の値となる。增幅トランジスタM3がソースフォロワとして動作するために、フィードバック用トランジスタ15aはデプレッション型であって、式6の閾値電圧 $V_{th1}$ を有することが好ましい。

## 【0029】

電圧 $V_0$ がフィードバック用トランジスタ15aのゲート電圧であることから、フィードバック用トランジスタ15aがソースフォロワ動作するため、以下の式7を満たすことが好ましい。

$$V_{DD} V_0 - V_{th1} \quad (\text{式7})$$

## 【0030】

式7および式3から式8が導かれる。

$$V_{DD} V_G - V_{th2} - V_2 - V_{th1} \quad (\text{式8})$$

## 【0031】

式8はさらに式9で表される。

$$V_G V_{DD} + V_{th2} + V_{th1} + V_2 \quad (\text{式9})$$

## 【0032】

增幅トランジスタM3のゲート電圧 $V_G$ はリセット電圧 $V_{RES}$ にリセットされることから、式9は式10で表される。

$$V_{RES} V_{DD} + V_{th2} + V_{th1} + V_2 \quad (\text{式10})$$

## 【0033】

以上により、式6および式10が満たされることで、增幅トランジスタM3はソースフォロワとして動作する。なお、式10において、閾値電圧 $V_{th1}$ 、 $V_{th2}$ の値によつては、リセット電圧 $V_{RES}$ は電源電圧 $V_{DD}$ よりも低く設定されることが好ましい。

## 【0034】

上述のように構成された固体撮像装置の概略の動作を説明する。垂直走査回路2は駆動パルス $PRES$ をハイレベルとすることで、浮遊拡散領域FDの電荷をリセットする。垂直走査回路2は駆動パルス $PRES$ をローレベルとし、リセット動作を終了する。列信号線11には、画素10のリセット状態における信号電圧が output され、信号処理回路30の容量に保持される。次に、垂直走査回路2は駆動パルス $PTX$ をハイレベルとした後にロー レベルとし、光電変換部PDに蓄積された信号電荷を浮遊拡散領域FDに転送する。浮遊拡散領域FDの電位は、電荷量に応じて所定電位だけ低くなる。增幅トランジスタM3からは、浮遊拡散領域FDの信号電荷に基づく信号電圧が列信号線11に出力される。フィードバック用トランジスタ15aのゲートには列信号線11における信号電圧が入力され、フィードバック用トランジスタ15aのソースの電位は信号電圧に追従して所定電位だけ低くなる。上述したように、增幅トランジスタM3がソースフォロワとして動作する場合、增幅トランジスタM3のゲート電圧およびドレイン電圧は一定の電圧差を保ちながら変化する。增幅トランジスタM3のソースから光電変換時の信号電圧が列信号線11に出力され、信号処理回路30の容量に保持される。信号処理回路30のコンパレータ回路はリセット情報における信号電圧と光電変換時の信号電圧の差分の信号を出力することで、ノイズ成分が除去された信号を得ることができる。

## 【0035】

以上、述べたように、本実施形態によれば、フィードバック回路15は、增幅トランジスタM3の信号電圧に追従して変化する電圧を增幅トランジスタM3の第2のドレインに供給する。增幅トランジスタM3のゲート・ドレイン間の容量を実質的に無くし、若しくは極めて小さくすることができるとともに、チャネル長変調効果を抑制することができる。これにより、出力ゲインを高くし、信号対雑音比を向上させることができる。また、フィードバック回路15は增幅トランジスタM3の駆動電流のみによって動作するため、消

10

20

30

40

50

費電流の増加を抑制しながら、信号対雑音比を高めることが可能となる。

【0036】

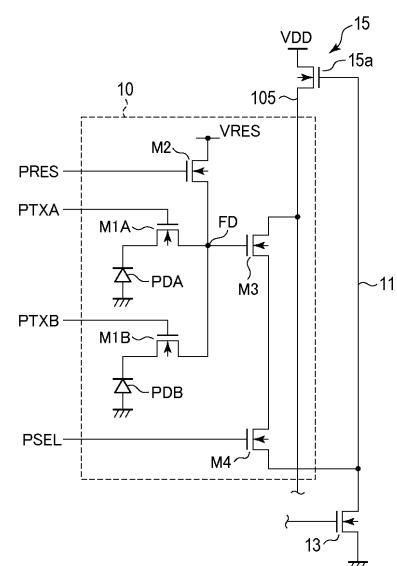

【第2実施形態】

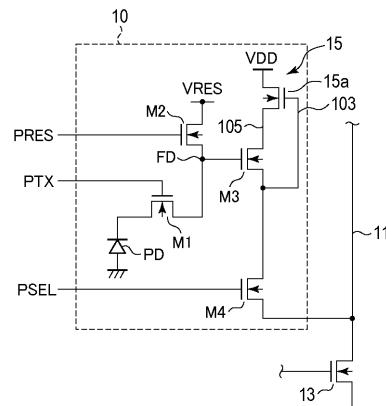

続いて、本発明の第2実施形態における固体撮像装置について、第1実施形態と異なる構成を中心に説明する。図3は本実施形態における画素10の等価回路図である。本実施形態において、フィードバック回路15は画素10毎に設けられている。画素10において、1つのフィードバック用トランジスタ15aが1つの増幅トランジスタM3に対応して設けられ、フィードバック用トランジスタ15aのソースは電圧供給線105を介して増幅トランジスタM3のドレインにのみ接続されている。フィードバック用トランジスタ15aのゲートは配線103を介して増幅トランジスタM3のソースに接続される。

10

【0037】

本実施形態においても、フィードバック用トランジスタ15aは、増幅トランジスタM3のソースから出力された信号電圧に追従して変化する電圧を増幅トランジスタM3のドレインに供給する。これにより、増幅トランジスタM3のゲート・ドレイン間の容量を実質的に無くし、若しくは極めて小さくすることができ、信号対雑音比を高めることができる。また、フィードバック用トランジスタ15aは増幅トランジスタM3の駆動電流のみによって動作するため、消費電流の増加を抑制することができる。

【0038】

さらに、本実施形態においては、フィードバック用トランジスタ15aは画素10毎に設けられ、フィードバック用トランジスタ15aからの電圧供給線105には1つの増幅トランジスタM3のドレインが接続されている。このため、第1実施形態と比較して、電圧供給線105における容量を小さくすることができ、フィードバックの遅延時間を大幅に低減することができる。

20

【0039】

また、本実施形態においては、フィードバックされる信号電圧は、列信号線11の信号電圧ではなく、増幅トランジスタM3のソースの信号電圧である。このため、上述の式6 $(-V_2 - V_1 V_{th1})$ において、 $V_2$ の値は、第1実施形態における $V_2$ と比較して、選択トランジスタM4のオン抵抗による電圧降下分だけ小さくなる。したがって、フィードバック用トランジスタ15aの閾値電圧 $V_{th1}$ が満たすべき条件は第1実施形態に比較して緩和され、設計の自由度を高めることができる。

30

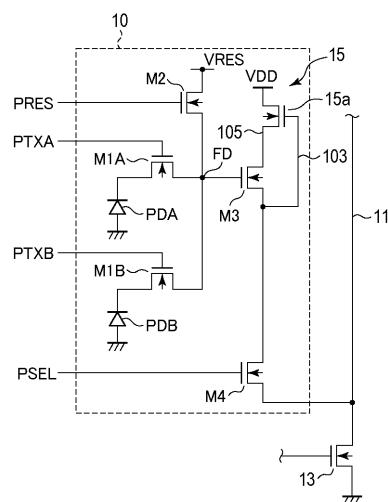

【0040】

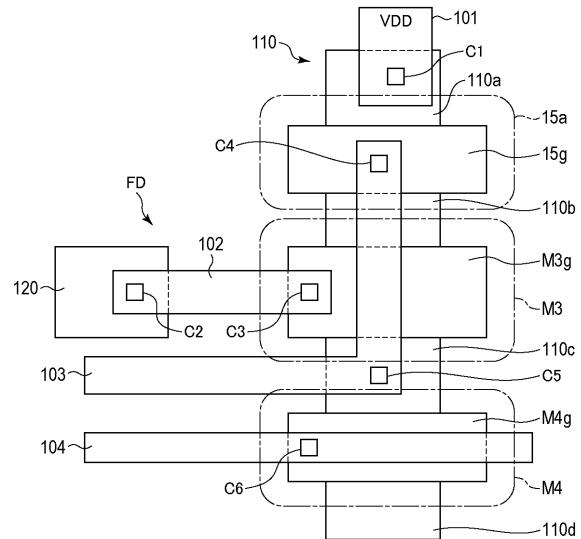

図4は本実施形態における画素の平面図である。図4において、図3における回路要素に対応する構成には同一の参照符号が付されている。アクティブ領域110、120には薄いゲート酸化膜が形成され、アクティブ領域110、120以外の領域には厚い酸化膜が付された素子分離領域が形成されている。

【0041】

アクティブ領域120には転送トランジスタM1のソース領域が形成され、ソース領域は光電変換部PDから転送された信号電荷を保持する浮遊拡散領域FDを構成する。浮遊拡散領域FDにはコンタクトホールC2を介して配線102の一端に接続される。配線102の他端はコンタクトホールC3を介して増幅トランジスタM3のゲート電極M3gに接続される。

40

【0042】

アクティブ領域110において、増幅トランジスタM3のゲート電極M3gは領域110bと領域110cとの間のチャネル領域上に絶縁層を介して形成される。領域110cは増幅トランジスタM3のソース領域および選択トランジスタM4のドレイン領域を兼ねている。領域110cと領域110dとの間のチャネル領域上には絶縁層を介して選択トランジスタM4のゲート電極M4gが形成される。ゲート電極M4gはコンタクトホールC6を介して駆動配線104に接続される。領域110dは選択トランジスタM4のソース領域を構成し、図示されていない列信号線11に接続される。さらに、アクティブ領域110において、領域110aと領域110bとの間のチャネル領域上には、絶縁層を介

50

してフィードバック用トランジスタ 15a のゲート電極 15g が形成される。ゲート電極 15g はコンタクトホール C4 を介して配線 103 に接続されている。配線 103 はさらにコンタクトホール C5 を介して領域 110c、すなわち増幅トランジスタ M3 のソース領域および選択トランジスタ M4 のドレイン領域に接続されている。領域 110a はフィードバック用トランジスタ 15a のドレイン領域を構成し、領域 110a はコンタクトホール C1 を介して電源配線 101 に接続される。領域 110b はフィードバック用トランジスタ 15a のソース領域および増幅トランジスタ M3 のドレイン領域を兼ねている。

#### 【 0043 】

図 4において、配線（第1の配線）103 は増幅トランジスタ M3 のゲート電極 M3g と交差するとともに、配線（第2の配線）102 および浮遊拡散領域 FD に隣接している。しかし、配線 103 と、ゲート電極 M3g、配線 102、浮遊拡散領域 FD との間の容量は、配線 103 が増幅トランジスタ M3 の出力であるから実質的に無くなり、若しくは極めて小さくなる。また、配線 102 と駆動配線（第3の配線）104 との間に配線 103 の少なくとも一部が平面視において位置することにより、駆動配線 104 と配線 102 との間の容量は電気的遮蔽効果によって低減される。選択トランジスタ M4 の駆動配線 104 と同様に、転送トランジスタ M1 の駆動配線およびリセットトランジスタ M2 の駆動配線についても配線 102 との容量を低減することが可能である。さらに、図示されていないが、配線 103 に接続される上層の配線を浮遊拡散領域 FD、配線 102 の大部分を覆うように配置してもよい。これにより、浮遊拡散領域 FD、配線 102、ゲート電極 M3g と駆動配線、電源配線 101 等との間の容量を電気的遮蔽効果によって低減できる。

10

20

#### 【 0044 】

以上説明したように、本実施形態によれば、消費電流の増加を抑制しながら、信号対雑音比を高めることができる。また、フィードバック回路 15 が画素 10 毎に設けられているため、第 1 実施形態と比較して、電圧供給線 105 における容量を小さくすることができ、フィードバックの遅延時間を大幅に低減することができる。

#### 【 0045 】

##### 【 第3実施形態 】

続いて、本発明の第3実施形態における固体撮像装置について、第2実施形態と異なる構成を中心に説明する。図 5 は本実施形態における画素 10 の等価回路図である。本実施形態において、画素 10 は転送トランジスタ M1 を備えておらず、光電変換部 PDA の N 電極は浮遊拡散領域 FD を構成している。このような構成の画素 10 においては、第1、第2実施形態と異なり、相関二重サンプリングによるノイズ除去を行うことができない。この場合、増幅トランジスタ M3 の信号電圧をリセット電圧 VRES にフィードバックする回路を設けても良い。

30

#### 【 0046 】

本実施形態においても、増幅トランジスタ M3 がソースフォロワとして動作するための駆動電流のみによって動作するフィードバック回路を用いることにより、消費電流の増加を抑制しながら、信号対雑音比を高めることができる。

#### 【 0047 】

##### 【 第4実施形態 】

続いて、本発明の第4実施形態における固体撮像装置について、第1実施形態と異なる構成を中心に説明する。図 6 は本実施形態における画素 10 の等価回路図である。画素 10 は、光電変換部 PDA、PDB、転送トランジスタ M1A、M1B、浮遊拡散領域 FD、リセットトランジスタ M2、増幅トランジスタ M3、選択トランジスタ M4 を含む。光電変換部 PDA、PDB は例えばフォトダイオードから構成されており、入射光による光電変換および電荷の蓄積を行なう。光電変換部 PDA、PDB には共通のマイクロレンズが設けられており、マイクロレンズにより集光された光が光電変換部 PDA、PDB に入射する。このように、2つの光電変換部 PDA、PDB は瞳分割されている。なお、画素 10 を構成する光電変換部の個数は2個に限定されず、それ以上の個数であっても良い。

40

#### 【 0048 】

50

転送トランジスタM1A、M1Bは光電変換部PDA、PDBに対応して設けられ、それぞれのゲートには駆動パルスPTXA、PTXBが印加される。駆動パルスPTXA、PTXBがハイレベルとなると、転送トランジスタM1A、M1Bがオン状態（導通状態）となり、光電変換部PDA、PDBの信号が増幅トランジスタM3の入力ノードである浮遊拡散領域FDに転送される。また、駆動パルスPTXA、PTXBがローレベルとなると、転送トランジスタM1A、M1Bはオフ状態（非導通状態）となる。転送トランジスタM1A、M1Bを同時にオンまたはオフすることにより、光電変換部PDA、PDBの信号電荷を浮遊拡散領域FDに転送することができる。増幅トランジスタM3は、浮遊拡散領域FDにおいて加算された信号電荷に応じた信号電圧をソースから出力する。また、駆動パルスPTXAをオンまたはオフすることにより、光電変換部PDAの信号電荷が浮遊拡散領域FDに転送され、増幅トランジスタM3は信号電荷に応じた信号電圧をソースから出力する。以上の構成により、光電変換部PDA、PDBのそれぞれの信号電荷を加算した（A+B）信号、光電変換部PDAのA信号を得ることができる。（A+B）信号は画像信号として用いられる。光電変換部PDBのB信号は（A+B）信号からA信号を減算することで求められる。なお、減算を行わずに、光電変換部PDBからの信号電荷を独立に読み出しても良い。A信号、B信号は位相差検出のための焦点検出信号として用いられる。

#### 【0049】

フィードバック回路15は第1実施形態と同様に列信号線11毎に設けられ、増幅トランジスタM3から出力された信号電圧に追従して変化する電圧を電圧供給線105を介して増幅トランジスタM3のドレインに供給する。また、フィードバック用トランジスタ15aは電源電圧VDDの電源配線と増幅トランジスタM3のドレインとの間に直列に接続され、フィードバック用トランジスタ15aは増幅トランジスタM3に供給された駆動電流のみでソースフォロワとして動作する。

#### 【0050】

本実施形態においても、瞳分割の画素10における浮遊拡散領域FDの容量を実質的に無くし、若しくは極めて小さくし、信号ゲインを大きくすることができる。また、フィードバック回路は増幅トランジスタの駆動電流のみによって動作するため、消費電流の増加を抑制しながら、信号対雑音比を高めることができる。

#### 【0051】

続いて、本発明の第5実施形態における固体撮像装置について、第4実施形態と異なる構成を中心に説明する。図7は本実施形態における画素10の等価回路図である。フィードバック回路15は画素10毎に設けられている。画素10において、1つのフィードバック用トランジスタ15aが1つの増幅トランジスタM3に対応して設けられ、フィードバック用トランジスタ15aのソースは電圧供給線105を介して増幅トランジスタM3のドレインにのみ接続されている。本実施形態においても、瞳分割の画素10における浮遊拡散領域FDの容量を実質的に無くし、若しくは極めて小さくし、信号電圧の出力ゲインを大きくすることができる。また、フィードバック回路は増幅トランジスタの駆動電流のみによって動作するため、消費電流の増加を抑制しながら、信号対雑音比を高めることができる。

#### 【0052】

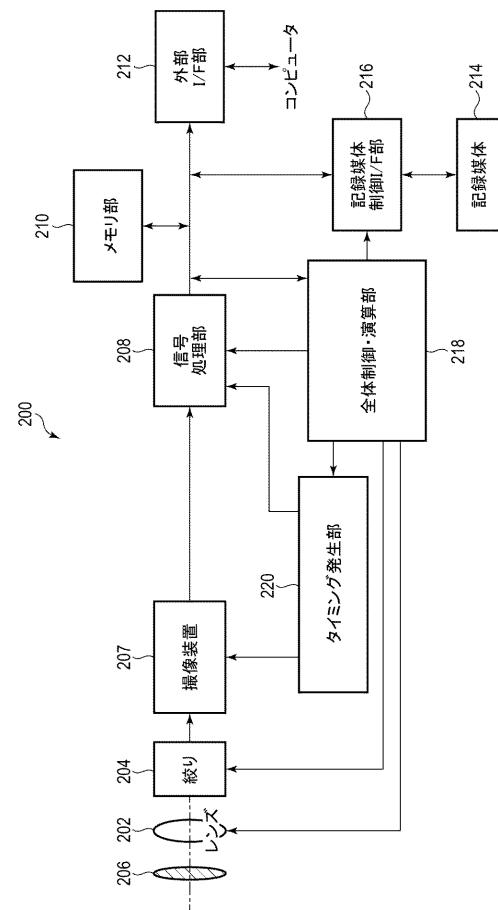

#### 【第6実施形態】

上述の実施形態における固体撮像装置は種々の撮像システムに適用可能である。撮像システムとして、デジタルスチルカメラ、デジタルカムコーダ、カメラヘッド、複写機、ファックス、携帯電話、車載カメラ、観測衛星、監視カメラなどがあげられる。図8に、撮像システムの例としてデジタルスチルカメラのブロック図を示す。

#### 【0053】

図8に示す撮像システムは、バリア206、レンズ202、絞り204、撮像装置207、信号処理部208、タイミング発生部220、全体制御・演算部218、メモリ部2

10

20

30

40

50

10、記録媒体制御 I / F 部 216、記録媒体 214、外部 I / F 部 212 を含む。バリア 206 はレンズ 202 を保護し、レンズ 202 は被写体の光学像を撮像装置 207 に結像させる。絞り 204 はレンズ 202 を通った光量を可変する。撮像装置 207 は上述の実施形態の固体撮像装置を含み、レンズ 202 により結像された光学像を画像データに変換する。ここで、撮像装置 207 の半導体基板には A/D 変換部が形成されているものとする。信号処理部 208 は撮像装置 207 より出力された撮像データに各種の補正やデータを圧縮する。タイミング発生部 220 は撮像装置 207 および信号処理部 208 に、各種タイミング信号を出力する。全体制御・演算部 218 はデジタルスチルカメラ全体を制御し、メモリ部 210 は画像データを一時的に記憶する。記録媒体制御 I / F 部 216 は記録媒体 214 に画像データの記録または読み出しを行うためのインターフェースであり、記録媒体 214 は撮像データの記録または読み出しを行うための半導体メモリ等の着脱可能な記録媒体である。外部 I / F 部 212 は外部コンピュータ等と通信するためのインターフェースである。タイミング信号などは撮像システムの外部から入力されてもよく、撮像システムは少なくとも撮像装置 207 と、撮像装置 207 から出力された撮像信号を処理する信号処理部 208 とを有すればよい。

#### 【0054】

本実施形態では、撮像装置 207 と A/D 変換部とが別の半導体基板に設けられた構成を説明した。しかし、撮像装置 207 と A/D 変換部とが同一の半導体基板に形成されていてもよい。また、撮像装置 207 と信号処理部 208 とが同一の半導体基板に形成されていてもよい。

#### 【0055】

また、それぞれの画素が第 1 の光電変換部と、第 2 の光電変換部を含んでもよい。信号処理部 208 は、第 1 の光電変換部で生じた電荷に基づく画素信号と、第 2 の光電変換部で生じた電荷に基づく画素信号とを処理し、撮像装置 207 から被写体までの距離情報を取得するように構成されてもよい。

#### 【0056】

##### 【第 7 実施形態】

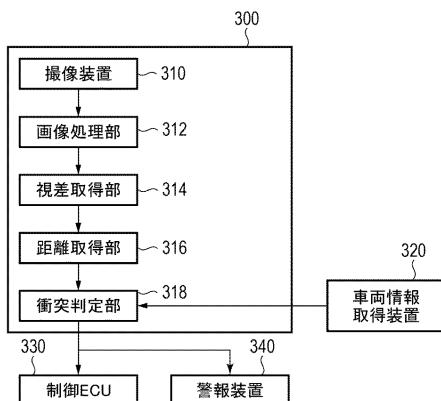

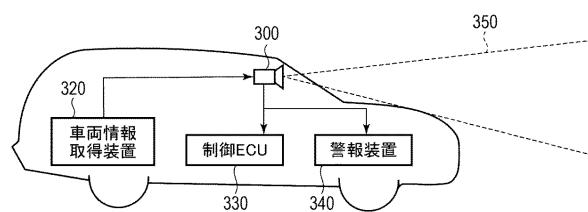

図 9 (a)、図 9 (b) は、本発明の第 7 実施形態における車載カメラに関する撮像システムの一例を示したものである。撮像システム 300 は、上述した実施形態の撮像装置 310 を有する。撮像システム 300 は、撮像装置 310 により取得された複数の画像データに対し、画像処理を行う画像処理部 312 と、撮像システム 300 より取得された複数の画像データから視差（視差画像の位相差）の算出を行う視差取得部 314 を有する。また、撮像システム 300 は、算出された視差に基づいて対象物までの距離を算出する距離取得部 316 と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部 318 とを有する。ここで、視差取得部 314、距離取得部 316 は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部 318 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA (Field Programmable Gate Array)、ASIC (Application Specific Integrated Circuit) によって実現されてもよいし、これらの組合せによって実現されてもよい。

#### 【0057】

撮像システム 300 は車両情報取得装置 320 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、撮像システム 300 は、衝突判定部 318 での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御 ECU 330 が接続されている。また、撮像システム 300 は、衝突判定部 318 での判定結果に基づいて、ドライバーへ警報を発する警報装置 340 とも接続されている。例えば、衝突判定部 318 の判定結果として衝突可能性が高い場合、制御 ECU 330 はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突

10

20

30

40

50

を回避、被害を軽減する車両制御を行う。警報装置 340 は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。撮像システム 300 は上述のように車両を制御する動作の制御を行う制御手段として機能する。

#### 【 0058 】

本実施形態では車両の周囲、例えば前方または後方を撮像システム 300 で撮像する。図 9 ( b ) に、車両前方 ( 撮像範囲 350 ) を撮像する場合の撮像システムを示した。撮像制御手段としての車両情報取得装置 320 が、上述の第 1 乃至第 6 の実施形態に記載した動作を行うように撮像システム 300 ないしは撮像装置 310 に指示を送る。撮像装置 310 の動作は、第 1 乃至第 6 の実施形態と同じなので、ここでは説明を省略する。このような構成により、測距の精度をより向上させることができる。 10

#### 【 0059 】

上述では、他の車両と衝突しないように制御する例を説明したが、他の車両に追従して自動運転する制御、車線からはみ出さないように自動運転する制御などにも適用可能である。さらに、撮像システムは、自車両等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体 ( 移動装置 ) に適用することができる。加えて、移動体に限らず、高度道路交通システム ( ITS ) 等、広く物体認識を利用する機器に適用することができる。

#### 【 0060 】

【 他の実施形態 】 20

本発明は、上述の実施形態に限らず種々の変形が可能である。例えば、いずれかの実施形態の一部の構成を他の実施形態に追加した例や、他の実施形態の一部の構成と置換した例も、本発明の実施形態である。

#### 【 0061 】

上述の実施形態においては、1つの画素が1つの増幅トランジスタを備えた構成を説明したが、本発明はこれらの構成に限定されない。例えば、1つの画素が複数の光電変換部に対応して複数の増幅トランジスタを備えている場合、フィードバックトランジスタを増幅トランジスタ毎に設けても良い。

#### 【 0062 】

上述の実施形態では、トランジスタを N 型トランジスタにより構成する場合を想定して説明を行ったが、トランジスタを P 型トランジスタにより構成するようにしてもよい。この場合、上述した各駆動信号のレベルは逆になる。 30

#### 【 0063 】

なお、上述の実施形態は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならない。すなわち、本発明はその技術思想、またはその主要な特徴から逸脱することなく、様々な形で実施することができる。

#### 【 符号の説明 】

#### 【 0064 】

1 画素部

2 垂直走査回路

3 列回路

4 水平走査回路

5 出力回路

6 制御回路

10 画素

11 列信号線

13 電流源

15 フィードバック回路

102 配線 ( 第 2 の配線 )

10

20

30

40

50

103 配線（第1の配線）

104 配線（第3の配線）

PD 光電変換回路

FD 浮遊拡散領域

M3 増幅トランジスタ

M4 選択トランジスタ

【図1】

【図2】

【 図 3 】

【 図 4 】

【 図 5 】

【図6】

【図7】

【図8】

【図9】

(a)

(b)

---

フロントページの続き

審査官 大室 秀明

(56)参考文献 国際公開第2014/049901 (WO, A1)

特開2008-042814 (JP, A)

国際公開第2013/099723 (WO, A1)

(58)調査した分野(Int.Cl. , DB名)

H 01 L 21 / 339

H 01 L 27 / 14 - 27 / 148

H 01 L 27 / 30

H 01 L 29 / 762

H 04 N 5 / 222 - 5 / 257

H 04 N 5 / 30 - 5 / 378