(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2017년08월11일

(11) 등록번호 10-1767864

(24) 등록일자 2017년08월07일

(51) 국제특허분류(Int. Cl.)

H01L 29/786 (2006.01) H01L 27/12 (2006.01)

H01L 29/45 (2006.01)

(52) CPC특허분류

H01L 29/7869 (2013.01)

H01L 27/1214 (2013.01)

(21) 출원번호 10-2016-7027185(분할)

(22) 출원일자(국제) 2009년08월27일

심사청구일자 2016년09월30일

(85) 번역문제출일자 2016년09월30일

(65) 공개번호 10-2016-0119272

(43) 공개일자 2016년10월12일

(62) 원출원 특허 10-2011-7008333

원출원일자(국제) 2009년08월27일

심사청구일자 2014년08월27일

(86) 국제출원번호 PCT/JP2009/065374

(87) 국제공개번호 WO 2010/029885

국제공개일자 2010년03월18일

(30) 우선권주장

JP-P-2008-235111 2008년09월12일 일본(JP)

(56) 선행기술조사문헌

KR1020080007813 A\*

JP2007150158 A\*

JP11288007 A

KR1019980072529 A

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 9 항

심사관 : 최혜미

(54) 발명의 명칭 반도체 장치 및 그 생산 방법

### (57) 요 약

본 발명의 목적은 인듐(In), 갈륨(Ga) 및 아연(Zn)을 포함하는 산화물 반도체 막을 사용하고 소스 또는 드레인 전극 층의 접촉 저항이 감소된 박막 트랜지스터 및 그 생산 방법을 제공하는 것이다. IGZO 층은 소스 전극층 및 드레인 전극층 위에 제공되고, IGZO 반도체층보다 더 낮은 산소 농도를 가지는 소스 및 드레인 영역은 의도적으

(뒷면에 계속)

### 대 표 도

로 소스 및 드레인 전극층과 게이트 절연층 사이에 제공되어, 음 접촉이 이루어진다.

(52) CPC특허분류

*H01L 27/1225* (2013.01)

*H01L 29/45* (2013.01)

*H01L 29/78618* (2013.01)

*H01L 29/78693* (2013.01)

(72) 발명자

**고모리, 시게끼**

일본 243-0036 가나가와쿄 아쓰기시 하세 398 가부

시키가이샤 한도오따이 에네루기 켄큐쇼 내

**우오찌, 히데끼**

일본 243-0036 가나가와쿄 아쓰기시 하세 398 가부

시키가이샤 한도오따이 에네루기 켄큐쇼 내

## 명세서

### 청구범위

#### 청구항 1

반도체 장치로서,

제1 전도성 층;

상기 제1 전도성 층 위의 제1 절연층;

상기 제1 절연층 위의 산화물 반도체층;

상기 산화물 반도체층 위의 제2 전도성 층;

상기 제2 전도성 층 위의 제2 절연층; 및

상기 제2 절연층 위의 제3 전도성 층

을 포함하고,

상기 제1 전도성 층은 픽셀부의 바깥에 있고,

상기 산화물 반도체층은 상기 제1 전도성 층과 중첩하며,

상기 제2 전도성 층은 상기 산화물 반도체층과 전기적으로 접속되고,

상기 제2 전도성 층은 상기 제1 전도성 층과 중첩하고,

상기 제2 전도성 층은, 상기 제2 절연층 내의 컨택트 홀을 통해 상기 제3 전도성 층에 전기적으로 접속되며,

상기 제1 전도성 층의 전위는 부동(floating) 상태에 있고,

상기 제3 전도성 층은 연성 인쇄 회로(flexible printed circuit)와의 접속을 위해 사용되는 전극으로서 기능하는, 반도체 장치.

#### 청구항 2

반도체 장치로서,

제1 전도성 층;

상기 제1 전도성 층 위의 제1 절연층;

상기 제1 절연층 위의 산화물 반도체층;

상기 산화물 반도체층 위의 제2 전도성 층;

상기 제2 전도성 층 위의 제2 절연층; 및

상기 제2 절연층 위의 제3 전도성 층

을 포함하고,

상기 제1 전도성 층은 픽셀부의 바깥에 있고,

상기 산화물 반도체층은 상기 제1 전도성 층과 중첩하며,

상기 제2 전도성 층은 상기 산화물 반도체층과 전기적으로 접속되고,

상기 제2 전도성 층은 상기 제1 전도성 층과 중첩하고,

상기 제2 전도성 층은, 상기 제2 절연층 내의 컨택트 홀을 통해 상기 제3 전도성 층에 전기적으로 접속되며,

상기 제1 전도성 층은 상기 제2 전도성 층과 전기적으로 접속되지 않고,

상기 제1 전도성 층의 전위는 부동(floating) 상태에 있고,

상기 제3 전도성 층은 연성 인쇄 회로와의 접속을 위해 사용되는 전극으로서 기능하는, 반도체 장치.

#### 청구항 3

반도체 장치로서,

제1 전도성 층;

상기 제1 전도성 층 위의 제1 절연층;

상기 제1 절연층 위의 산화물 반도체층;

상기 산화물 반도체층 위의 제2 전도성 층;

상기 제2 전도성 층 위의 제2 절연층; 및

상기 제2 절연층 위의 제3 전도성 층

을 포함하고,

상기 제1 전도성 층은 픽셀부의 바깥에 있고,

상기 산화물 반도체층은 상기 제1 전도성 층과 중첩하며,

상기 제2 전도성 층은 상기 산화물 반도체층과 접촉해 있고,

상기 제2 전도성 층은 상기 제1 전도성 층과 중첩하고,

상기 제2 전도성 층은, 상기 제2 절연층 내의 컨택트 훌을 통해 상기 제3 전도성 층에 전기적으로 접속되며,

상기 제1 전도성 층의 전위는 부동(floating) 상태에 있고,

상기 제3 전도성 층은 연성 인쇄 회로와의 접속을 위해 사용되는 전극으로서 기능하는, 반도체 장치.

#### 청구항 4

제1항 내지 제3항 중 어느 한 항에 있어서,

상기 제3 전도성 층은 투명 전도성 막을 포함하는, 반도체 장치.

#### 청구항 5

제1항 내지 제3항 중 어느 한 항에 있어서,

상기 제1 전도성 층의 상기 전위는 상기 제2 전도성 층의 전위와 상이한, 반도체 장치.

#### 청구항 6

제1항 내지 제3항 중 어느 한 항에 있어서,

상기 산화물 반도체층은 인듐 및 아연을 포함하는, 반도체 장치.

#### 청구항 7

제1항 내지 제3항 중 어느 한 항에 있어서,

상기 산화물 반도체층은 인듐, 아연 및 갈륨을 포함하는, 반도체 장치.

#### 청구항 8

제1항 내지 제3항 중 어느 한 항에 있어서,

상기 산화물 반도체층은 상기 제1 절연층을 개재하여 상기 제1 전도성 층과 중첩하는, 반도체 장치.

#### 청구항 9

제1항 내지 제3항 중 어느 한 항에 있어서,

상기 제2 전도성 층은 상기 제1 절연층 및 상기 산화물 반도체층을 개재하여 상기 제1 전도성 층과 중첩하는, 반도체 장치.

### 발명의 설명

#### 기술 분야

[0001]

본 발명은 산화물 반도체 막을 사용하여 채널 형성 영역(channel formation region)을 형성하는 박막 트랜지스터(이하 "TFT")를 포함하는 회로를 갖는 반도체 장치 및 그 생산 방법에 관한 것이다. 예를 들어, 본 발명은 액정 디스플레이 패널 또는 유기 발광 소자를 포함하는 발광 디스플레이 장치로 대표되는 전자광학 장치가 컴포넌트로서 탑재되는 전자 기기에 관한 것이다.

[0002]

본 명세서의 반도체 장치는 반도체 특성을 사용하여 동작될 수 있는 모든 장치를 나타내며, 전자광학 장치, 반도체 회로 및 전자 기기 모두 그 반도체 장치에 포함된다.

### 배경 기술

[0003]

최근, 매트릭스(matrix)로 배열된 각각의 디스플레이 퍽셀에 대해 TFT를 사용하여 형성된 스위칭 소자가 제공되는, (액정 디스플레이 장치, 발광 디스플레이 장치 또는 전기영동 디스플레이 장치{electrophoretic display devices}와 같은)액티브 매트릭스 디스플레이 장치가 활발히 개발되었다. 액티브 매트릭스 디스플레이 장치에서, 스위칭 소자는 각각의 퍽셀(또는 각각의 도트)에 제공되며, 따라서, 액티브 매트릭스 장치는, 퍽셀 밀도가 증가된 경우의 간단한 매트릭스 디스플레이 장치(simple matrix display devices)보다 더 낮은 전압으로 구동될 수 있는 장점이 있다.

[0004]

또한, 산화물 반도체 막을 사용하여 채널 형성 영역을 형성하는 박막 트랜지스터 등을 생산하고 이러한 TFT 등을 전자 장치 또는 광학 장치에 적용하는 기술은 관심을 끌어 모았다. 예를 들어, 산화아연(zinc oxide; ZnO)을 산화물 반도체 막으로 사용하는 TFT, 또는  $\text{InGaO}_3(\text{ZnO})_m$ 을 산화물 반도체 막으로 사용하는 TFT가 주어질 수 있다. 이러한 산화물 반도체 막을 포함하는 TFT를 광 전달 기판(light-transmitting substrate) 위에 형성하여 이미지 디스플레이 장치의 스위칭 소자 등으로 사용하는 기술이 특히 문헌 1 및 특히 문헌 2에서 개시된다.

### 선행기술문헌

#### 특허문헌

[0005]

(특허문헌 0001) 특허 문헌 1: 일본 공개 특허 출원 번호 2007-123861

(특허문헌 0002) 특허 문헌 2: 일본 공개 특허 출원 번호 2007-096055

### 발명의 내용

#### 해결하려는 과제

[0006]

산화물 반도체 막을 사용하여 채널 형성 영역을 형성하는 박막 트랜지스터의 경우, 고속 동작, 비교적 쉬운 생산 공정 및 충분한 신뢰도가 요구된다.

[0007]

박막 트랜지스터의 형성에서, 낮은 저항 금속 재료(low-resistance metal material)가 소스 및 드레인 전극층에 사용된다. 특히, 대면적 디스플레이를 갖는 디스플레이 장치가 생산되는 경우에는, 배선의 저항으로 인한 신호 지연의 문제가 현저해진다. 따라서, 배선 및 전극의 재료에 낮은 전기 저항값을 갖는 금속 재료를 사용하는 것이 바람직하다. 산화물 반도체 막과 낮은 전기 저항값을 갖는 금속 재료를 사용하여 형성된 소스 및 드레인 전극층이 서로 직접 접촉해 있는 구조를 갖는 박막 트랜지스터에서는, 접촉 저항이 증가하는 위험이 있다. 접촉 저항의 증가에 대해 고려해볼 수 있는 이유 중 하나는 소스 및 드레인 전극 층과 산화물 반도체 막 사이의 접촉 면(contact surface)에 쇼트키 접합(Schottky junction)의 형성이다.

[0008]

또한, 소스 및 드레인 전극 층과 산화물 반도체 막이 서로 직접 접촉해 있는 부분에 캐패시턴스가 형성되며, 주

파수 특성("f 특성"이라 불림)이 감소하고 박막 트랜지스터의 고속 동작이 방해되는 위험이 있다.

[0009] 본 발명의 실시예의 목적은 인듐(In), 갈륨(Ga) 및 아연(Zn)을 포함하는 산화물 반도체 막을 사용하고 소스 또는 드레인 전극 층의 접촉 저항이 감소된 박막 트랜지스터 및 그 생산 방법을 제공하는 것이다.

[0010] 또 다른 목적은 인듐, 갈륨 및 아연을 포함하는 산화물 반도체 막을 사용한 박막 트랜지스터의 동작 특성 및 신뢰도를 향상시키는 것이다.

[0011] 나아가, 또 다른 목적은 각각 인듐, 갈륨 및 아연을 포함하는 산화물 반도체 막을 사용한 박막 트랜지스터의 전기적 속성(properties)의 변동(variation)을 감소시키는 것이다. 특히, TFT 간의 전기적 특성의 변동이 큰 액정 디스플레이 장치에서는, TFT 간의 전기적 특성의 변동으로 인한 디스플레이 비균질성(unevenness)이 발생될 위험이 있다.

[0012] 나아가, 또한 발광 소자를 포함하는 디스플레이 장치에서, 발광 소자로 일정한 전류 흐름(current flow)를 만들도록 된 TFT(구동 회로 내의 TFT 또는 픽셀에 배열된 발광 소자로 전류를 공급하는 TFT)의 온 전류(ON current;  $I_{on}$ )에 큰 변동이 있는 경우, 디스플레이 화면에 휘도의 변동이 생성될 위험이 있다.

[0013] 본 발명의 실시예는 전술된 목적 중 적어도 하나를 달성하는 것을 목표로 한다.

### 과제의 해결 수단

[0014] 본 발명의 실시예는 게이트 절연층 위에 낮은-저항 산화물 반도체층을 소스 또는 드레인 영역(source or drain region)으로서 형성한 후 드레인 전극층 또는 소스 전극층을 형성하고, 그 위에 비-단결정(non-single-crystal) 산화물 반도체 막을 반도체층으로서 형성하기 위한 것이다. 산소-과잉(oxygen-excess) 산화물 반도체층을 반도체층으로서 사용하고, 산소-부족(oxygen-deficient) 산화물 반도체층을 소스 영역 및 드레인 영역으로서 사용하는 것이 바람직하다. 소스 영역 및 드레인 영역의 기능을 하는 이러한 산소-부족 산화물 반도체층은 대략 1nm 내지 10nm, 통상적으로는 대략 2nm 내지 4nm의 지름을 갖는 결정 입자를 포함할 수 있다.

[0015] 본 명세서에서, 인듐, 갈륨 및 아연을 포함하는 산화물 반도체 막을 사용하여 형성한 반도체층은 또한 "IGZO 반도체층"이라고 지칭된다. IGZO 반도체층은 비-단결정 반도체층이고, 적어도 비정질 캠포넌트를 포함한다.

[0016] 소스 전극층과 IGZO 반도체층 사이에 옴 접촉(Ohmic contact)이 필요하고, 더욱이 그 접촉 저항은 가능한 한 최대한으로 감소되는 것이 바람직하다. 마찬가지로, 드레인 전극층과 IGZO 반도체층 사이에 옴 접촉이 필요하고, 그 접촉 저항은 가능한 한 최대한으로 감소되는 것이 바람직하다. 따라서, IGZO 반도체층보다 더 높은 캐리어 농도(carrier concentration)를 가지는 소스 및 드레인 영역은 의도적으로 소스 및 드레인 전극층과 게이트 절연층 사이에 제공되어, 옴 접촉이 이루어진다. 소스 및 드레인 영역으로서 기능하는 낮은-저항 IGZO 반도체층은 n 형 전도도를 가지며,  $n^+$  영역으로도 지칭된다. 소스 및 드레인 영역이  $n^+$  영역으로 불리는 경우에는, 채널 형성 영역으로서 기능하는 IGZO 반도체층 또한 i 형 영역으로 불린다.

[0017] 본 명세서에 개시된 본 발명의 구성은 절연면(insulating surface) 위에 게이트 전극, 게이트 전극 위에 게이트 절연층, 게이트 절연층 위에 소스 영역 및 드레인 영역, 소스 영역 및 드레인 영역 위에 금속층, 및 금속층 위에 반도체층을 포함하는 반도체 장치이다. 위의 구성에서, 반도체층은 비-단결정 산화물 반도체층이고, 반도체층과 게이트 전극 사이에 삽입되어있는(interposed) 게이트 절연층과 함께 게이트 전극과 중첩되며, 소스 영역 및 드레인 영역의 산소 농도는 반도체층의 산소 농도보다 더 낮다. 그리고, 금속층은 소스 전극층 및 드레인 전극층이다.

[0018] 본 발명의 실시예는 위의 목적 중 적어도 하나를 해결한다.

[0019] 전술된 구성에서, 소스 영역 및 드레인 영역은 인듐, 갈륨 및 아연을 포함하는 산화물층을 사용하여 형성된다. 소스 영역 및 드레인 영역은 IGZO 반도체층보다 더 낮은 저항을 가진다. 또한, 소스 영역의 측면(side face) 및 소스 영역의 옆면(side surface)을 향하고 있는 드레인 영역의 옆면은 반도체층과 접촉해 있다.

[0020] 비-단결정 반도체층 또는 소스 영역 및 드레인 영역으로, 인듐, 갈륨 및 아연을 포함하는 산화물 반도체 막이 사용될 수 있음을 알 수 있다. 또한, 인듐, 갈륨 및 아연 중 어느 것이든 텡스텐, 몰리브덴(molybdenum), 티타늄, 니켈 또는 알루미늄으로 대체될 수 있다.

[0021] 반도체 장치를 생산하는 방법 또한 본 발명의 실시예이며, 소스 전극층 및 드레인 전극층이 형성된 후 플라즈마 처리(plasma treatment)가 수행된다. 그리고, 플라즈마 처리 후, 반도체층은 공기에 노출되지 않고 스퍼터링

방법(sputtering method)에 의해 형성된다. 반도체층이 형성되기 전에 막 형성 기판이 공기에 노출되면, 수분 등이 부착되고, 계면 상태(interface state)가 안 좋은 영향을 받아 문턱 전압의 변동, 전기적 특성의 열화(deterioration) 및 정상-온 TFT(normally-on TFT)와 같은 결함이 발생될 수 있다. 플라즈마 처리를 위해, 산소 가스 또는 아르곤 가스가 사용된다. 아르곤 가스 대신에, 또 다른 희유 가스(rare gas)가 사용될 수 있다.

[0022] 본 명세서에 개시된 생산하는 방법에 관련된 본 발명의 구성은 절연면 위에 게이트 전극을 형성하는 단계, 게이트 전극 위에 게이트 절연층을 형성하는 단계, 게이트 절연층 위에 소스 영역, 드레인 영역 및 금속 영역을 포함하는 스택(stack)을 형성하는 단계, 금속층을 선택적으로 에칭(etching)하여 소스 전극층 및 드레인 전극층을 형성하는 단계, 노출된 게이트 절연층, 소스 전극층 및 드레인 전극층 위에 플라즈마 처리를 수행하는 단계, 게이트 전극과 중첩되고 플라즈마 처리를 받는 게이트 절연층 위에 중첩되는 반도체층을 형성하는 단계를 포함하는 반도체 장치를 생산하기 위한 방법이다. 위의 구성에서, 반도체층은 비-단결정 산화물 반도체층이며, 소스 영역 및 드레인 영역의 산소 농도는 반도체층의 산소 농도보다 더 낮다.

[0023] 플라즈마 처리에 의해, 게이트 절연층, 소스 전극층 및 드레인 전극층의 노출된 표면은 세정될 수 있다. IGZO 반도체층이 형성되기 전에, 소스 전극층 및 드레인 전극층은 포토리소그래피(photolithography) 기술을 사용하여 패터닝(patterning)하여 처리되며, 따라서, 유기 물질과 같은 표면 위에 남아있는 먼지와의 반응을 발생시키고 먼지를 제거하는 플라즈마 처리를 수행하는 것이 효과적이다.

[0024] 특히, 플라즈마 처리 후 공기에 노출하지 않고 스퍼터링 방법에 의해 IGZO 반도체층을 형성하기 위해서는, IGZO 반도체층의 형성과 동일한 챔버(chamber)에서 수행될 수 있는 역 스퍼터링(reverse sputtering)이라 불리는 일종의 플라즈마 처리를 수행하는 것이 바람직하다. 역 스퍼터링은 산소 대기 또는 산소와 아르곤 대기 내에서 전압이 타겟측(target side)이 아닌 기판측(substrate side)에 인가되는 방법이며 기판 표면이 변형될 수 있도록 플라즈마가 생성된다.

[0025] 챔버에서 산소 가스를 사용하여 플라즈마 처리를 수행하는 경우에, 게이트 절연층의 표면은 산소 라디칼(oxygen radicals)을 조사하는 것에 의해 산소-파잉 영역으로 변형되어, 추후에 형성될 IGZO 반도체층과의 계면에서의 산소 농도가 증가된다. 게이트 절연층의 산소 라디칼 처리 후 반도체층이 적층되고(stacked) 그 다음 열 처리가 수행되면, 게이트 절연층 층 위의 IGZO 반도체층에서의 산소 농도 또한 증가될 수 있다. 따라서, 게이트 절연층과 IGZO 반도체층 사이의 계면에서 산소 농도의 정점부(peak)가 존재하고, 게이트 절연층에서의 산소 농도는 기울기(gradient)를 가지며, 산소 농도는 게이트 절연층과 IGZO 반도체층 사이의 계면으로 갈수록 증가한다. 산소-파잉 영역 및 산소-파잉 산화물 반도체층(IGZO 반도체층)을 가지는 게이트 절연층은, 서로 양립할 수 있고(compatible), 좋은 계면(favorable interface)을 제공할 수 있다.

[0026] 산소 라디칼은 산소를 포함하는 가스를 사용하는 플라즈마 생성 기구(plasma generating apparatus)로부터 또는 오존 생성 기구로부터 공급될 수 있다. 산소 라디칼 또는 공급된 산소를 박막에 조사하는 것에 의해, 막 표면이 변형될 수 있다.

[0027] 또한, 본 발명은 산소 라디칼 처리에 제한되지 않고, 아르곤 및 산소 라디칼 처리가 수행될 수 있다. "아르곤 및 산소 라디칼"이란 용어는 아르곤 가스 및 산소 가스를 주입하여 플라즈마를 생성하는 것에 의해 박막 표면을 변형하는 것을 의미한다.

[0028] 전기장이 인가되고 방전 플라즈마가 생성되는 반응성 공간(reactive space) 내의 아르곤 원자(Ar)는 방전 플라즈마 내의 전자(e)에 의해 아르곤 라디칼( $Ar^*$ ), 아르곤 이온( $Ar^+$ ) 또는 전자(e)로 여기되거나 이온화된다. 아르곤 라디칼( $Ar^*$ )은 높은 에너지를 갖는 준안정 상태(metastable state)이며, 그 부근의 동일한 종류 또는 상이한 종류의 원자 및 여기된 또는 이온화된 원자와 반응하는 것에 의해 안정 상태로 돌아오는 경향이 있고, 따라서 반응은 전자사태 증식(avalanche multiplication)처럼 일어난다. 그때 그 부근에 산소가 있는 곳에서, 산소 원자(0)는 산소 라디칼( $O^*$ ), 산소 이온( $O^+$ ) 또는 산소(0)로 여기되거나 이온화된다. 산소 라디칼( $O^*$ )은, 처리하고자 하는 목표물인 박막의 표면의 재료와 반응하여, 표면 변형이 수행되고, 표면의 유기 물질과 반응하여, 유기 물질이 제거되며, 따라서 플라즈마 처리가 수행된다. 아르곤 가스의 라디칼의 특징은 반응성 가스(산소 가스)에 비교하여 더 긴 시간 동안 준안정 상태를 유지한다는 것임을 알아야 하며, 따라서 아르곤 가스는 일반적으로 플라즈마를 생성하기 위해 사용된다.

[0029] 또한, 산소 가스를 사용하는 경우에, 소스 전극층 및 드레인 전극층의 표면은 플라즈마 처리의 특정 조건하에서 산화된다. 소스 전극층 및 드레인 전극층의 표면이 산화되고 산화물 막에 의해 덮이더라도, 소스 전극층 또는

드레인 전극층과 접촉하기 위해 소스 전극층 또는 드레인 전극층 아래 형성되는 소스 영역 또는 드레인 영역은 추후에 형성될 반도체 층과 전기적으로 접속될 수 있다. 이 경우에, 바람직하게는, 소스 영역(또는 드레인 영역)의 측면은 그 단면에서 소스 전극층(또는 드레인 전극층)의 측면을 넘어 돌출된다(projected). 따라서, 소스 영역과 드레인 영역 사이의 거리는 소스 전극층과 드레인 전극층 사이의 거리보다 더 짧게 된다. 예를 들어, 소스 전극층 및 드레인 전극층의 패터닝은 소스 영역 및 드레인 영역의 패터닝에 사용되는 것과 상이한 포토마스크를 사용하여 수행될 수 있다. 이렇게 얻어진 박막 트랜지스터의 채널 길이 L은 소스 영역과 드레인 영역 사이의 거리에 해당한다.

[0030] 사용되는 포토마스크의 개수를 감소시키기 위해서, 패터닝에 의해 소스 전극층 및 드레인 전극층을 프로세싱한 후, 소스 전극층 및 드레인 전극층을 마스크로 사용하여 소스 영역 및 드레인 영역이 자기 정렬 방식(self-aligned manner)으로 형성될 수 있다. 이 경우에, 소스 영역(또는 드레인 영역)의 측면은 실질적으로 소스 전극층(또는 드레인 전극층)의 측면과 맞춰지고(aligned), 따라서, 소스 영역과 드레인 영역 사이의 거리는 실질적으로 소스 전극층과 드레인 전극층 사이의 거리와 같다. 또한, 소스 영역 및 드레인 영역은 특정 에칭 조건 하에서 테이퍼 형상이 된다(tapered). 이 경우에, 소스 영역과 드레인 영역 사이의 거리는 소스 전극층과 드레인 전극층 사이의 거리보다 더 짧게 된다. 이렇게 얻어진 박막 트랜지스터의 채널 길이 L은 소스 영역과 드레인 영역 사이의 거리에 해당함을 알아야한다.

[0031] IGZO 반도체층, 소스 영역, 드레인 영역, 소스 전극층 및 드레인 전극층은 스퍼터링 방법에 의해 형성될 수 있다.

[0032] 스퍼터링 방법의 예는 스퍼터링 전력원으로 고주파수 전력원(high-frequency power source)이 사용되는 RF 스퍼터링 방법, DC 스퍼터링 방법 및 바이어스(bias)가 펄스형 방식으로 인가되는 펄스형 DC 스퍼터링 방법을 포함한다. RF 스퍼터링 방법은 절연막을 적층하는(depositing) 경우에 주로 사용되고, DC 스퍼터링 방법은 금속막을 적층하는 경우에 주로 사용된다.

[0033] 또한, 복수의 상이한 재료의 타겟이 설치될 수 있는 멀티-소스 스퍼터링 기구(multi-source sputtering apparatus)도 있다. 멀티-소스 스퍼터링 기구로는, 상이한 재료의 막이 동일한 챔버에서 적층되도록 적층될 수 있거나, 복수의 종류의 재료가 동일한 챔버에서 동시에 전기 방전에 의해 적층될 수 있다.

[0034] 또한, 챔버 내에 자석 시스템을 가지며 마그네트론 스퍼터링 방법(magnetron sputtering method)에 사용되는 스퍼터링 기구 또는 글로우 방전(glow discharge)을 사용하지 않고, 마이크로웨이브를 사용하여 생성된 플라즈마를 사용하는 ECR 스퍼터링 방법에 사용되는 스퍼터링 기구도 있다.

[0035] 또한, 스퍼터링 방법을 사용하는 적층 방법으로서, 적층하는 동안에 타겟 물질과 스퍼터링 가스 컴포넌트가 그 얇은 화합물 막(thin compound film)을 형성하기 위해 서로 화학적으로 반응하는 반응성 스퍼터링 방법 및 적층하는 동안에 전압이 기판에도 인가되는 바이어스 스퍼터링 방법도 있다.

[0036] 이러한 다양한 스퍼터링 방법의 사용으로, IGZO 반도체층, 소스 영역, 드레인 영역, 소스 전극층 및 드레인 전극층이 형성된다.

[0037] 소스 영역 및 드레인 영역은 또한 인듐, 갈륨 및 아연을 포함하는 산화물층이고 IGZO 반도체층의 막 형성 조건과 상이한 막 형성 조건하에서 형성된다. 소스 영역 및 드레인 영역의 막 형성 조건은 그 영역이 막 형성 직후 1nm에서 10nm 사이즈의 결정 입자를 포함하는 조건을 포함한다. 예를 들어,  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO} = 1:1:1$ 의 타겟이 사용된 막 형성 조건하에서, DC 스퍼터링 방법이 채용되고, 아르곤 가스 및 산소가 2:1의 아르곤 가스 대 산소 플로우 비율로 챔버 안으로 주입되거나 또는 아르곤 가스만이 주입되며, 몇몇 경우에 1nm에서 10nm 사이즈의 결정 입자를 포함하는 막이 막 형성 직후 얻어진다.  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO} = 1:1:1$ 의 타겟은 비정질 산화물 반도체 막(amorphous oxide semiconductor film)을 얻기 위해 의도적으로 그 비율을 가지도록 설계되고, 타겟의 조성비(composition ratio)는 소스 영역 및 드레인 영역에 대해 더 높은 결정도(crystallinity)를 가지는 막을 얻기 위해 변경될 수 있음을 알아야 한다. 더 간단한 공정 또는 더 낮은 비용을 실현하기 위해서는, IGZO 반도체층에 사용되는 막과 소스 영역 및 드레인 영역에 사용되는 막을, 동일한 타겟을 사용하여 단순히 주입될 가스를 변경하는 것에 의해 별도로 형성하는 것이 바람직하다.

[0038] 산소-부족 산화물 반도체층이 소스 영역 또는 드레인 영역으로서 적극적으로 마련되면(positively provided), 금속층인 소스 또는 드레인 전극층과 IGZO 막 사이의 접합이 좋고(favorable), 쇼트키 접합보다 열(heat)적인 면에서도 더 높은 동작 안정성(operation stability)을 가진다. 또한, 채널(소스측)에 캐리어(carriers)를 공

급하기 위해, 채널(드레인측)로부터 캐리어를 안정적으로 흡수하기(absorb) 위해, 또는 소스 전극층(또는 드레인 전극층)과의 계면에서 저항이 형성되는 것을 방지하기 위해 소스 영역 또는 드레인 영역을 적극적으로 마련하는 것이 중요하다. 저항의 감소는 또한, 높은 드레인 전압에서도 좋은 이동도(mobility)를 보장하기 위해 중요하다.

[0039] 또한, 소스 전극층 및 드레인 전극층에 티타늄막을 사용하는 것이 바람직하다. 예를 들어, 티타늄막, 알루미늄막 및 티타늄막이 적층된 층은 낮은 저항을 가지며, 알루미늄막에서 힐락(hilllock)이 거의 생성되지 않는다.

[0040] 또한, 스퍼터링 방법에서, Ar 이온에 의해 강한 에너지가 타겟에 가해지고, 따라서 형성된 IGZO 반도체층에는 강한 변형에너지(strain energy)가 존재한다고 여겨진다. 변형에너지를 방출하기 위해 200°C 내지 600°C, 통상적으로는 300°C 내지 500°C에서 열 처리를 수행하는 것이 바람직하다. 이 열 처리를 통해, 원자 수준에서의 재배열이 일어난다. 열처리에 의해 캐리어 움직임을 억제하는 변형에너지가 방출되므로, 막 형성 및 열 처리(광학 어닐링{optical annealing}을 포함함)는 중요하다.

### 발명의 효과

[0041] 작은 광전류, 작은 기생 캐패시턴스 또는 높은 점멸비(on-off ratio)를 갖는 박막 트랜지스터가 얻어질 수 있어, 뛰어난 동적 특성(dynamic characteristics)을 가지는 박막 트랜지스터가 생산될 수 있다. 또한, 우수한 전기적 특성 및 높은 신뢰도를 가지는 박막 트랜지스터를 포함하는 반도체 장치가 제공될 수 있다.

### 도면의 간단한 설명

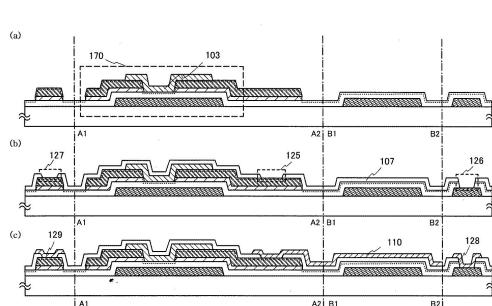

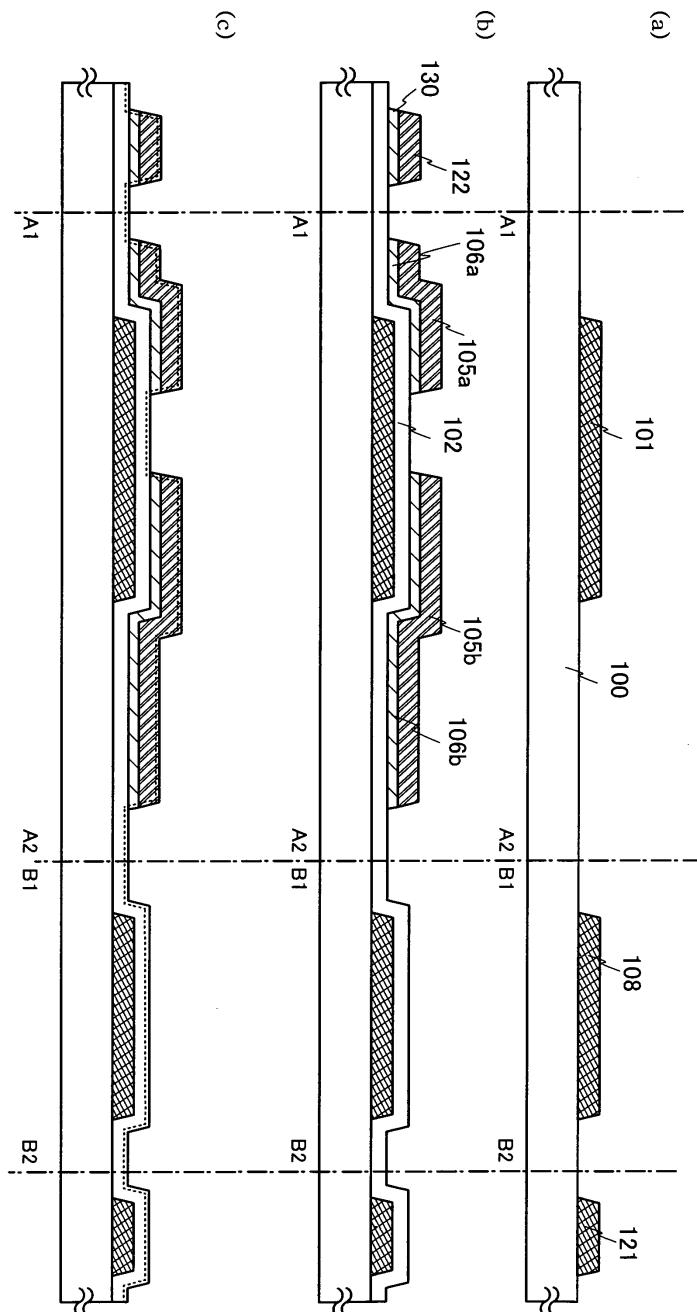

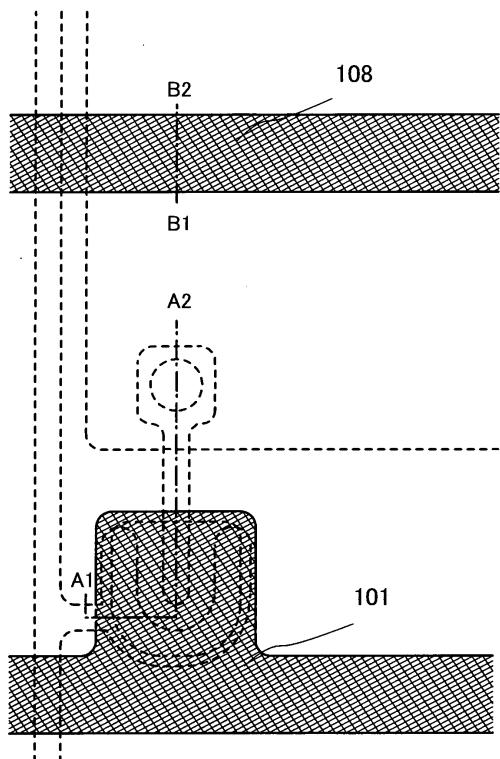

[0042] 도 1의 (a) 내지 (c)는 본 발명의 일 실시예의 반도체 장치의 공정 단면도.

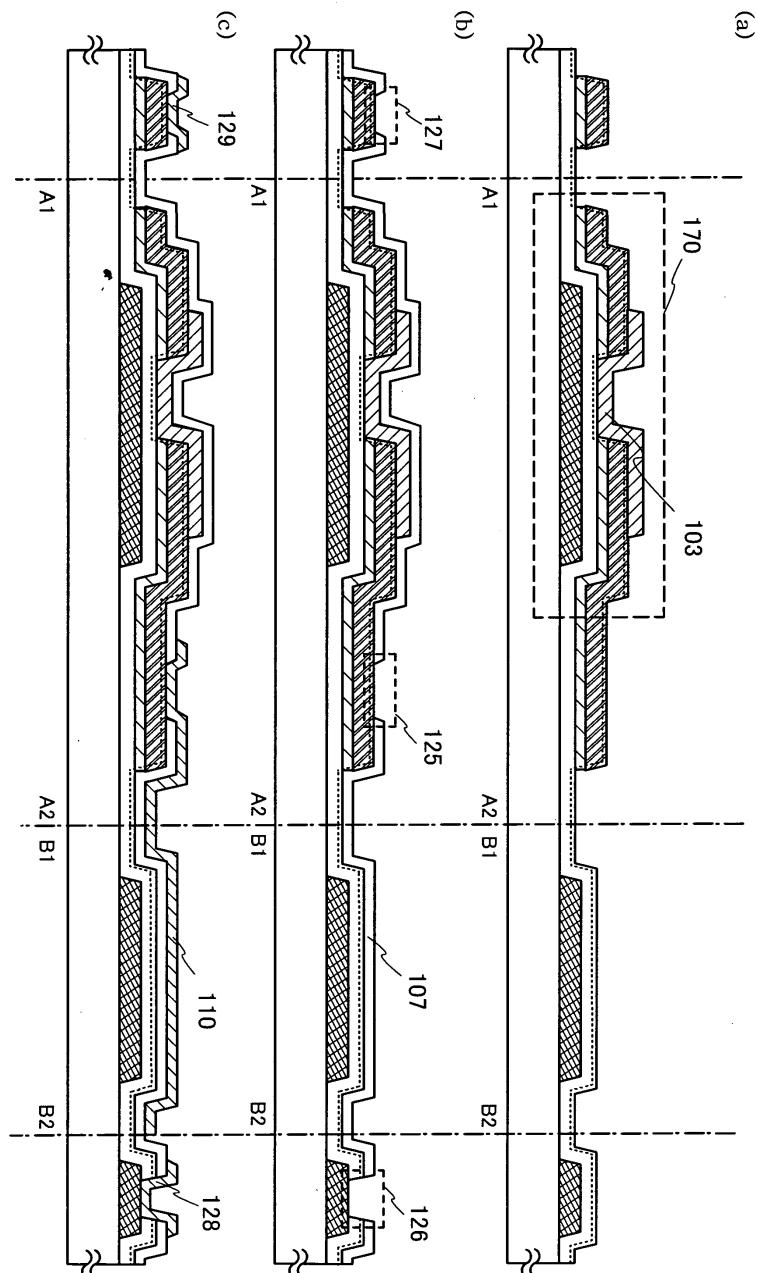

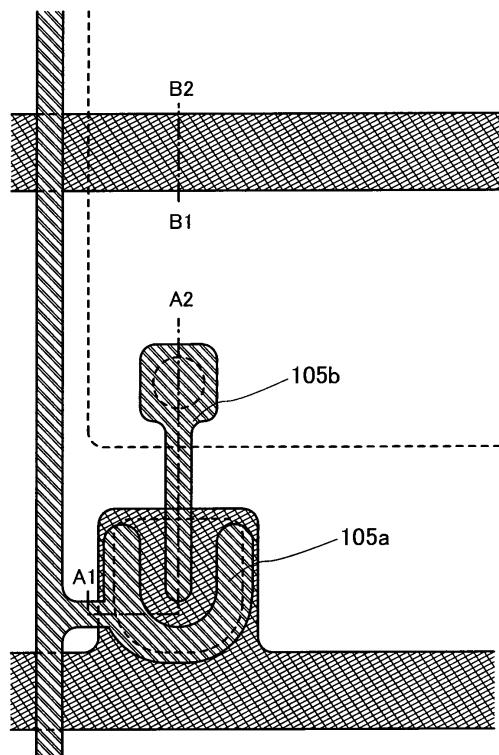

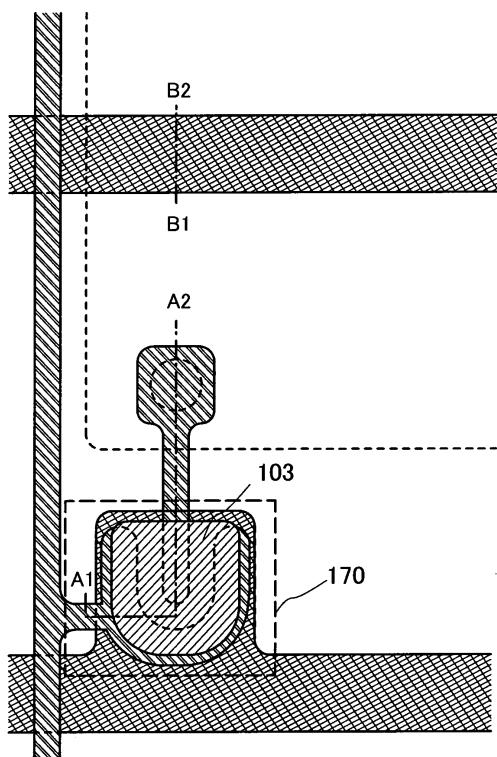

도 2의 (a) 내지 (c)는 본 발명의 일 실시예의 반도체 장치의 공정 단면도.

도 3은 본 발명의 일 실시예의 반도체 장치의 평면도.

도 4는 본 발명의 일 실시예의 반도체 장치의 평면도.

도 5는 본 발명의 일 실시예의 반도체 장치의 평면도.

도 6은 본 발명의 일 실시예의 반도체 장치의 평면도.

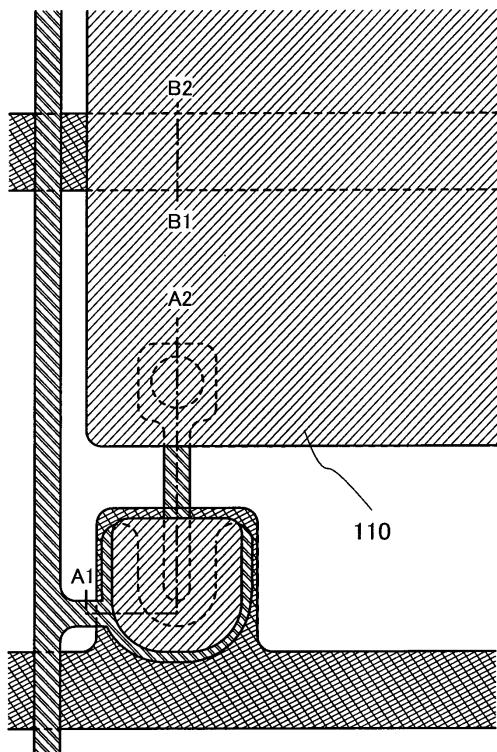

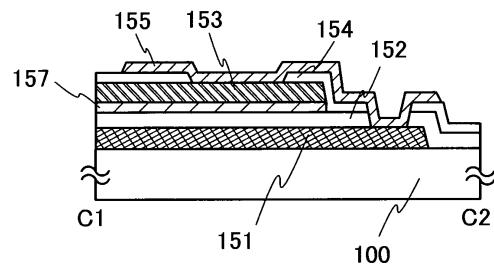

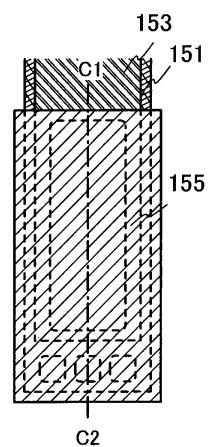

도 7a 내지 도 7d는 본 발명의 일 실시예의 반도체 장치의 터미널부의 평면도 및 단면도.

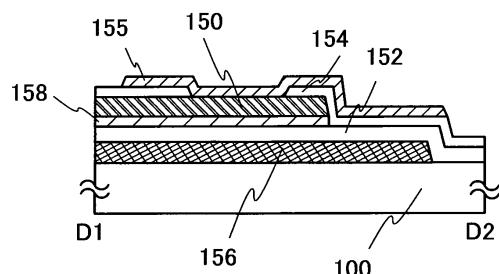

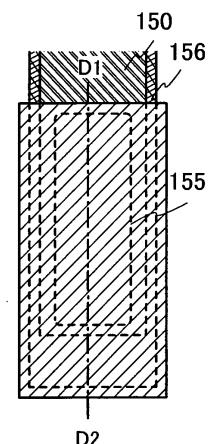

도 8은 본 발명의 일 실시예의 반도체 장치의 픽셀의 평면도.

도 9는 전자 종이의 단면도.

도 10a 내지 10b는 반도체 장치의 블록도.

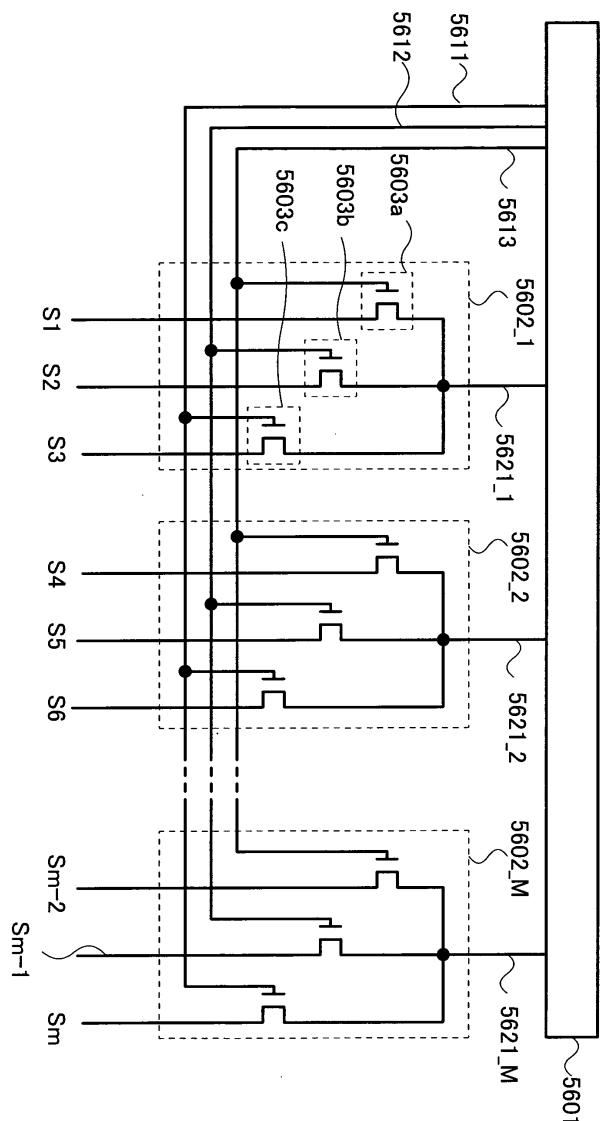

도 11은 신호 라인 구동 회로의 구조를 도시한 도면.

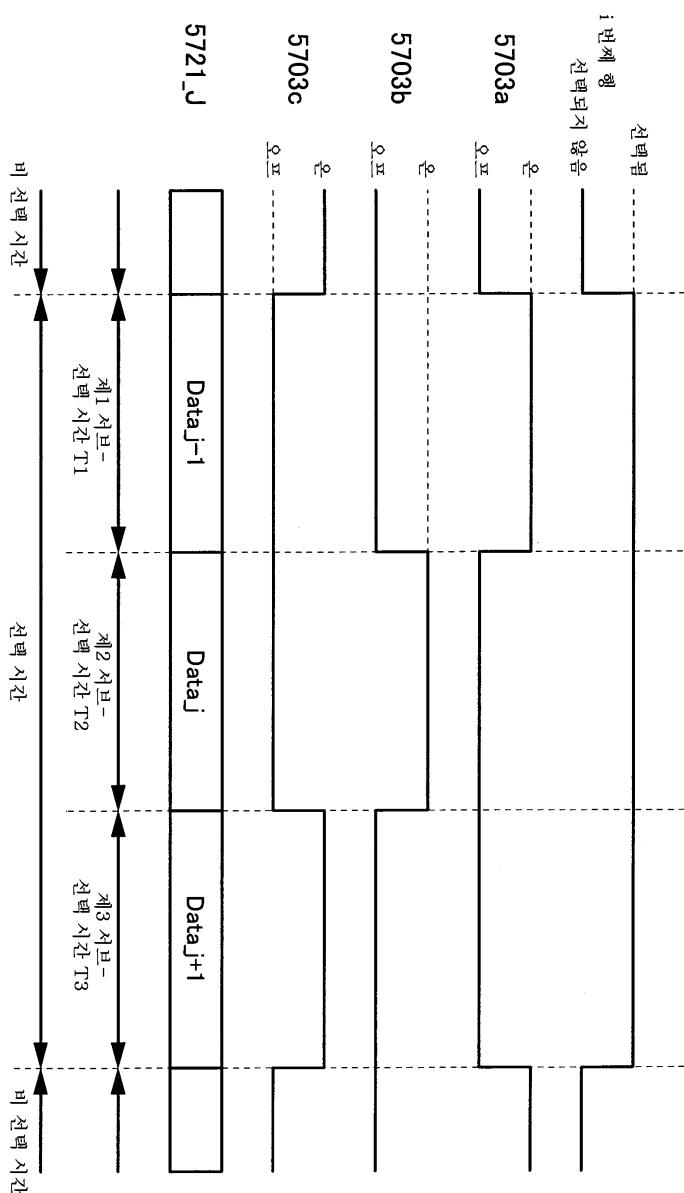

도 12는 신호 라인 구동 회로의 동작을 도시한 타이밍 차트.

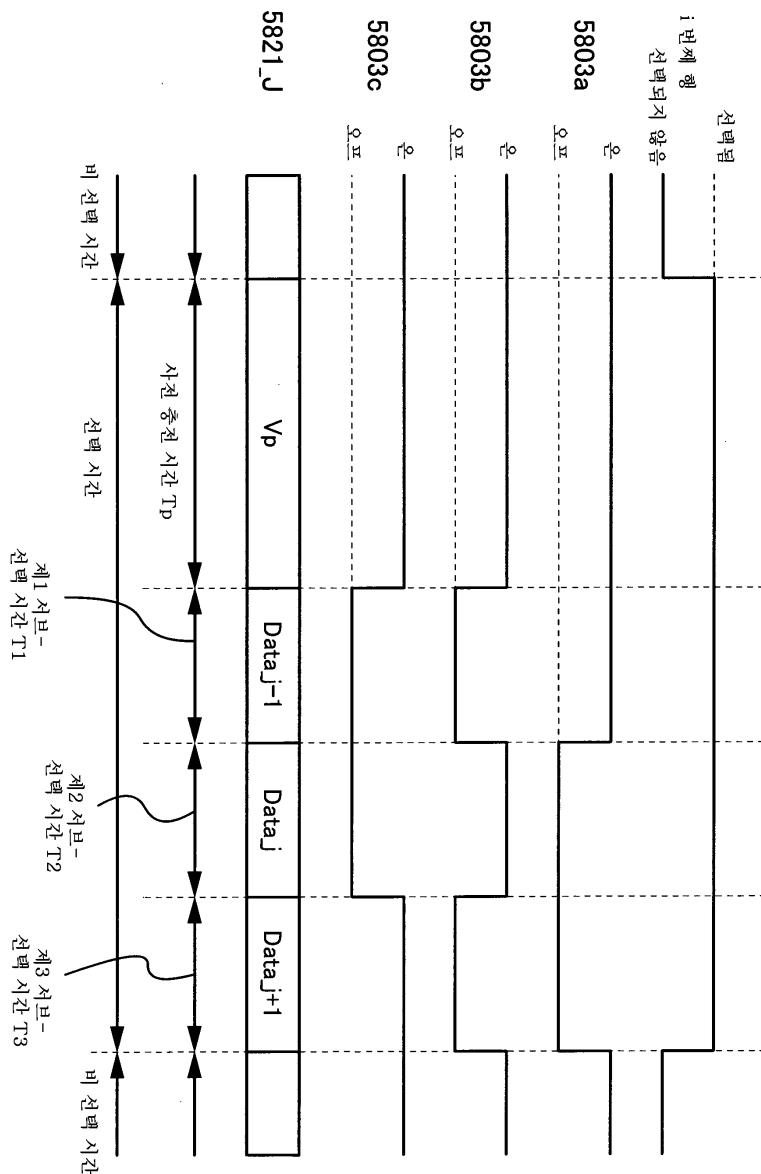

도 13은 신호 라인 구동 회로의 동작을 도시한 타이밍 차트.

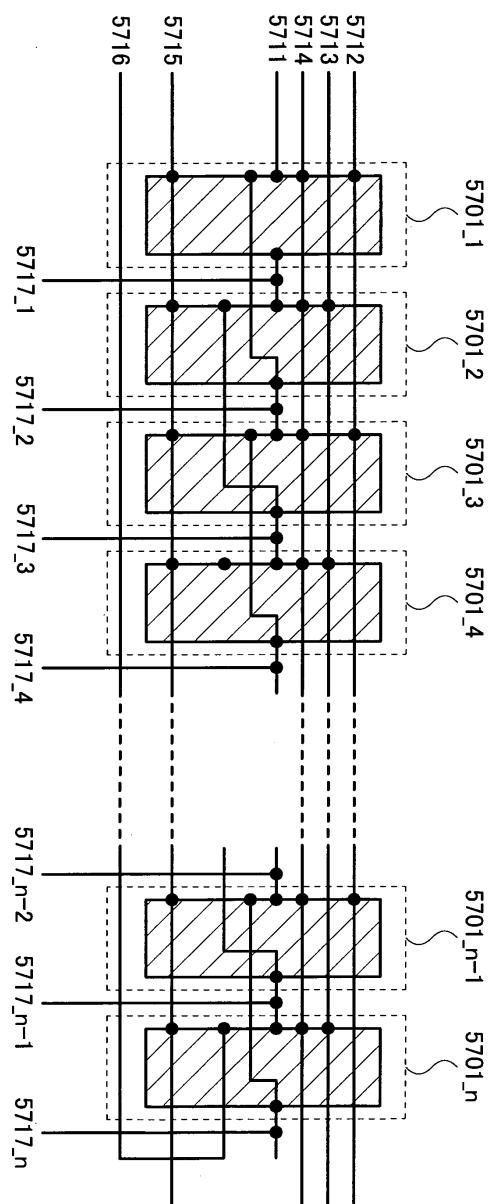

도 14는 시프트 레지스터(shift register)의 구조를 도시한 도면.

도 15는 도 14에 도시된 플립플롭(flip-flop)의 접속 구조를 도시한 도면.

도 16a 내지 16c는 본 발명의 일 실시예의 반도체 장치를 도시한 평면도 및 단면도.

도 17은 본 발명의 일 실시예의 반도체 장치를 도시한 단면도.

도 18은 본 발명의 일 실시예의 반도체 장치의 픽셀 등가 회로(pixel equivalent circuit)를 도시한 도면.

도 19a 내지 19c는 본 발명의 일 실시예의 반도체 장치를 도시한 그림.

도 20a 내지 20b는 본 발명의 일 실시예의 반도체 장치를 도시한 평면도 및 단면도.

도 21a 내지 21b는 전자 종이의 사용의 예를 도시한 그림.

도 22는 전자 책 판독기의 예를 도시한 외면도.

도 23a 내지 23b는 텔레비전 장치 및 디지털 사진 프레임의 예를 도시한 외면도.

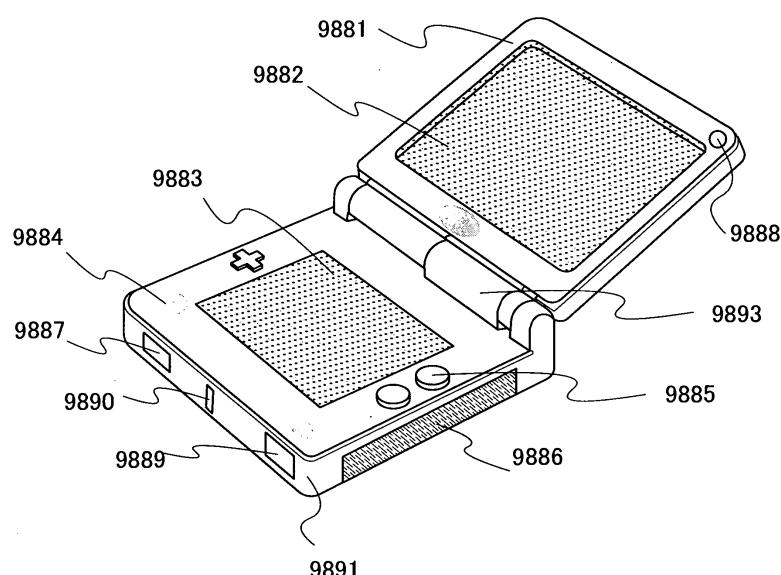

도 24a 내지 24b는 게임 머신의 예를 도시한 외면도.

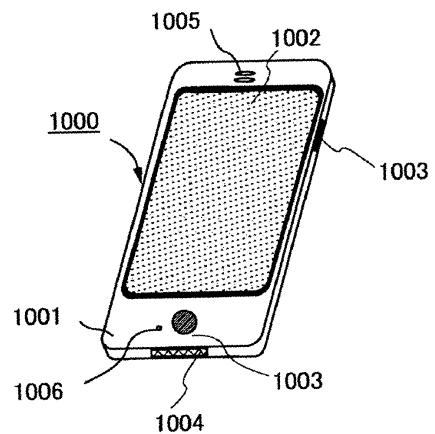

도 25는 휴대폰의 예를 도시한 외면도.

### 발명을 실시하기 위한 구체적인 내용

[0043] 본 발명의 실시예는 첨부된 도면을 참조하여 후술될 것이다. 하지만, 당업자라면, 본 발명이 다음에 주어진 기술에 제한되지 않고, 본 발명의 취지 및 범위를 벗어나지 않으면서 그 모드와 세부 사항에 다양한 변경 및 수정이 이루어질 수 있음을 바로 명백하게 이해할 것이다. 따라서, 본 발명은 다음에 주어진 실시예의 기술에 제한되는 것으로 해석되어서는 안 된다. 동일한 부분 또는 동일한 기능을 가지는 부분은 실시예를 설명하기 위한 모든 구성에서 동일한 참조 부호에 의해 표시되고, 그 반복적인 설명은 생략된다.

[0044] (실시예 1)

[0045] 이 실시예에서, 박막 트랜지스터 및 그 생산 공정은 도 1의 (a) 내지 (c), 도 2의 (a) 내지 (c), 도 3 내지 6 및 도 7a 내지 도 7d를 참조하여 기술된다.

[0046] 도 1의 (a)에서, 광 전달 속성을 가지는 기판(100)으로, 코닝 주식회사(Corning, Inc.)에 의해 생산된 7059 유리, 1737 유리 등으로 대표되는 바륨 봉규산 유리(barium borosilicate glass), 알루미노보로실리케이트 유리(aluminoborosilicate glass) 등이 사용될 수 있다.

[0047] 그 다음, 전도성 층이 기판(100)의 전체 면 위에 형성되고, 레지스트 마스크를 형성하기 위해 제1 포토리소그래피 단계가 수행되며, 배선 및 전극(게이트 전극{101}, 캐패시터 배선{108} 및 제1 터미널{121}을 포함하는 게이트 배선)을 형성하기 위해 불필요한 부분은 에칭에 의해 제거된다. 이 때, 적어도 게이트 전극(101)의 가장자리 부분은 테이퍼 형상(tapered shape)이 형성되도록 에칭이 수행된다. 이 스테이지(stage)에서의 단면도는 도 1의 (a)에 도시된다. 이 스테이지에서의 평면도는 도 3에 해당한다.

[0048] 게이트 전극(101)을 포함하는 게이트 배선, 캐패시터 배선(108) 및 터미널부의 제1 터미널(121)은 알루미늄(Al) 또는 구리(Cu)와 같은 낫은-저항 전도성 재료를 사용하여 형성하는 것이 바람직하지만, 알루미늄 하나만으로는 낫은 내열성 및 부식되는 경향(tendency toward corrosion)과 같은 단점을 가지기 때문에, 게이트 전극(101)을 포함하는 게이트 배선, 캐패시터 배선(108) 및 제1 터미널(121)을 형성하기 위해 내열 전도성 재료(heat-resistant conductive material)와 조합하여 사용된다. 내열 전도성 재료로서, 티타늄(Ti), 탄탈륨(Ta), 텅스텐(W), 몰리브덴(Mo), 크롬(Cr) 및 네오디뮴(Nd)에서 선택한 원소, 그 원소 중 어느 하나를 자신의 컴포넌트로 포함하는 합금, 그 원소 중 임의의 원소를 조합한 합금, 그 원소 중 어느 하나를 자신의 컴포넌트로 포함하는 질화물(nitride)이 사용된다.

[0049] 그 다음, 게이트 절연층(102)이 게이트 전극(101) 위의 전체 면 위에 형성된다. 게이트 절연층(102)은 스퍼터링 방법 등에 의해 50nm 내지 250nm의 두께로 형성된다.

[0050] 예를 들어, 게이트 절연층(102)은 스퍼터링 방법에 의해 100nm의 두께의 산화 실리콘 막을 사용하여 형성된다. 당연한 말이지만, 게이트 절연층(102)은 이와 같은 산화 실리콘 막으로 제한되지 않는다. 게이트 절연층(102)은 단일층 구조 또는 산화질화 실리콘 막(silicon oxynitride film), 질화 실리콘 막(silicon nitride film), 산화 알루미늄 막 또는 산화 탄탈륨 막과 같은 또 다른 절연막을 사용한 적층 구조를 가지도록 형성될 수 있다.

[0051] 그 다음, 제1 IGZO 막이 스퍼터링 방법에 의해 게이트 절연층(102) 위에 형성된다. 이 실시예에서, 스퍼터링은 0.4Pa의 압력, 500W의 전력, 형성 온도는 실온, 아르곤 가스는 40sccm의 플로우 비율로 주입되는 막 형성 조건 하에서  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO} = 1:1:1$ 의 타겟을 사용하여 수행된다.  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO} = 1:1:1$ 의 타겟의 의도적인 사용에도 불구하고, 막 형성 직후 1nm 내지 10nm 사이즈의 결정 입자를 포함하는 IGZO 막이 형성될 수 있다. 결정 입자의 존재 또는 부재, 또는 결정 입자의 밀도는 조절될 수 있고, 지름 사이즈는 타겟의 조성비, 막 형성 압력(0.1Pa 내지 2.0Pa), 전력(250W 내지 3000W; 8 인치 Ø), 온도(실온 내지 100°C), 반응성 스퍼터링 막 형성 조건 등의 적절한 조절에 의해 1nm 내지 10nm의 범위 내에서 조절될 수 있음을 알아야 한다. 제1 IGZO 막의 두께는 5nm 내지 20nm 이다. 당연한 말이지만, 막이 결정 입자를 포함하면, 결정 입자의 사이즈는 막 두께를 초과하지 않는다. 이 실시예에서, 제1 IGZO 막의 두께는 5nm이다.

[0052] 그 다음, 금속 재료로 만든 전도성 막은 스퍼터링 방법 또는 진공 적층 방법에 의해 제1 IGZO 막 위에 형성된다. 전도성 막의 재료의 예로서, Al, Cr, Ta, Ti, Mo 및 W에서 선택한 원소, 그 원소 중 어느 하나를

자신의 컴포넌트로 포함하는 합금, 그 원소 중 임의의 원소의 조합을 포함하는 합금 등이 주어질 수 있다. 이 실시예에서, 전도성 막은, Ti 막이 형성되고, Ti 막 위에 알루미늄(Al) 막이 적층되며, 그 위에 Ti 막이 더 형성된 3층 구조를 가진다. 이와 달리, 전도성 막은 2층 구조를 가질 수도 있고, 티타늄 막이 알루미늄 막 위에 적층될 수 있다. 이와 또 달리, 전도성 막은 실리콘을 포함하는 알루미늄 막의 단일층 구조 또는 티타늄 막의 단일층 구조를 가질 수 있다.

[0053] 게이트 절연층, 전도성 막 및 제1 IGZO 막은, 스퍼터링 방법을 사용하여 챔버에 주입될 가스와 챔버에 위치될 타겟을 적절히 변경하는 것에 의해 공기에 노출되지 않고 연속적으로 형성될 수 있다. 공기에 노출되지 않는 연속적 형성은 불순물의 진입을 방지할 수 있다. 공기에 노출되지 않고 막을 연속적으로 형성할 때는, 멀티-챔버 생산 기구를 사용하는 것이 바람직하다.

[0054] 그 다음, 레지스트 마스크를 형성하기 위해 제2 포토리소그래피 공정이 수행되고, 소스 전극층(105a) 및 드레인 전극층(105b)을 형성하기 위해 불필요한 부분이 에칭에 의해 제거된다. 이 때의 에칭 방법으로는, 습식 에칭(wet etching) 또는 건식 에칭(dry etching)이 사용된다. 이 실시예에서, 소스 전극층(105a) 및 드레인 전극층(105b)을 형성하기 위하여 Ti 막, Al 막 및 Ti 막이 차례대로 적층된 전도성 막이  $SiCl_4$ ,  $Cl_2$  및  $BCl_3$ 의 혼합 가스를 반응성 가스로 사용하는 건식 에칭에 의해 에칭된다.

[0055] 제2 포토리소그래피 단계에서, 소스 전극층(105a) 및 드레인 전극층(105b)과 동일한 재료로 만들어진 제2 터미널(122)도 터미널부에 남겨진다. 제2 터미널(122)은 소스 배선(소스 전극층{105a}을 포함하는 소스 배선)에 전기적으로 접속되어있음을 알아야한다.

[0056] 그 다음, 제1 IGZO 막은 소스 전극층(105a) 및 드레인 전극층(105b)을 마스크로 사용하여 자기 정렬 방식으로 에칭된다. 여기서, 소스 영역(106a) 및 드레인 영역(106b)을 형성하기 위해 제1 IGZO 막의 불필요한 부분이 ITO-07N(칸토 케미칼 주식회사{KANTO CHEMICAL CO., INC.}에 의해 생산됨)을 사용하는 습식 에칭에 의해 제거된다. 여기서의 에칭은 습식 에칭으로 제한되는 것이 아니고, 건식 에칭이 채용될 수 있음을 알아야한다. 이 스테이지에서의 단면도는 도 1의 (b)에 도시된다. 이 스테이지에서의 평면도는 도 4에 해당한다.

[0057] 캐패시터 부분에서, 캐패시터 배선(108)과 중첩되는 제1 IGZO 막은 제거된다. 터미널부에는, 제2 터미널(122) 아래 위치하고 제2 터미널과 중첩되어 있는 IGZO 층(123)이 남는다.

[0058] 그 다음, 레지스트 마스크가 제거된 후에, 플라즈마 처리가 수행된다. 이 스테이지에서의 단면도는 도 1의 (c)에 도시된다. 이 실시예에서, 산소 가스 및 아르곤 가스가 주입되고 플라즈마가 생성되는 역 스퍼터링이 수행되며, 게이트 절연층의 노출된 부분에는 산소 라디칼 또는 산소가 조사된다. 따라서, 표면에 부착된 먼지가 제거되고, 나아가, 게이트 절연층의 표면은 산소-파이드 영역으로 변형된다. 표면을 산소-파이드 영역으로 변경하기 위해 게이트 절연층의 표면 위에 수행되는 산소 라디칼 처리는 추후 단계에서 신뢰도 향상을 위한 열 처리(200°C 내지 600°C) 동안에 IGZO 반도체층의 계면 변형을 위한 산소의 소스(source of oxygen)를 형성하는데 효과적이다.

[0059] 그 다음, 플라즈마 처리 후에, 제2 IGZO 막이 공기에 노출되지 않고 형성된다. 플라즈마 처리 후 공기에 노출되지 않는 제2 IGZO 막의 형성은 먼지와 수분이 게이트 절연층과 반도체 막 사이의 계면에 부착되는 것을 방지하는데 효과적이다. 이 실시예에서, 제2 IGZO 막은 In, Ga 및 Zn를 포함하고 8인치( $In_2O_3:Ga_2O_3:ZnO = 1:1:1$ )의 지름을 가지는 산화물 반도체 타겟을 사용하여 기판과 타겟 사이의 거리를 170mm로 설정하고, 0.4Pa의 압력하에서, 0.5kW의 직류(DC) 전력원으로 아르곤 또는 산소 대기에서 형성된다. 먼지가 감소될 수 있고 두께 분포가 고르게 될 수 있는 펄스형 직류(DC) 전력원을 사용하는 것이 바람직하다. 제2 IGZO 막은 5nm 내지 200nm의 두께를 가진다. 이 실시예에서, 제2 IGZO 막의 두께는 100nm이다.

[0060] 제1 IGZO 막의 막 형성 조건과 다른 막 형성 조건하에서 제2 IGZO 막을 형성하는 것에 의해, 제2 IGZO 막은 제1 IGZO 막의 산소보다 더 높은 농도의 산소를 포함하도록 만들어진다. 예를 들어, 제2 IGZO 막은 산소 가스 플로우 비율이 제1 IGZO 막의 막 형성 조건하의 산소 가스 플로우의 비율보다 더 높은 조건하에서 형성된다. 특히, 제1 IGZO 막은 희유가스(아르곤 또는 헬륨과 같은) 대기(또는 10%이하의 산소 가스 및 90%이상의 아르곤 가스)에서 형성되고, 제2 IGZO 막은 산소 대기(또는 산소 가스 플로우 이하의 아르곤 가스 플로우)에서 형성된다. 제2 IGZO 막이 더 많은 양의 산소를 포함하도록 하는 것에 의해, 전도도를 제1 IGZO 막의 전도도보다 더 낮게 만들 수 있다. 또한, 제2 IGZO 막이 더 많은 양의 산소를 포함하도록 하는 것에 의해, 오프-전류(off-current)를 감소시킬 수 있고, 따라서, 높은 점멸비를 가지는 박막 트랜지스터가 얻어질 수 있다.

- [0061] 제2 IGZO 막은 역 스퍼터링이 수행되었던 챔버와 동일한 챔버 내에서 형성될 수 있거나, 공기에 노출되지 않는 한 역 스퍼터링이 수행되었던 챔버와 상이한 챔버 내에서 수행될 수도 있다.

- [0062] 그 다음, 열 처리는 200°C 내지 600°C, 통상적으로는 300°C 내지 500°C에서 수행되는 것이 바람직하다. 이 실시예에서, 열 처리는 질소 대기 내의 350°C의 노(furnace) 안에서 한 시간 동안 수행된다. 이러한 열 처리를 통해, IGZO 막에서 원자 수준에서의 재배열이 일어난다. 열 처리에 의해 캐리어 움직임을 억제하는 변형에너지가 방출될 수 있기 때문에, 열 처리(광학 어닐링을 포함함)는 중요하다. 열 처리의 타이밍은 제2 IGZO 막의 형성 후이면, 특별히 제한되지 않으며, 예를 들어, 열 처리는 픽셀 전극의 형성 후에 수행될 수 있음을 알아야 한다.

- [0063] 그 다음, 레지스트 마스크를 형성하기 위해 제3 포토리소그래피 단계가 수행되고, IGZO 반도체층(103)을 형성하기 위해 불필요한 부분이 에칭에 의해 제거된다. 위의 단계들을 통해, IGZO 반도체층(103)을 채널 형성 영역으로서 포함하는 박막 트랜지스터(170)가 생산될 수 있다. 이 스테이지의 단면도는 도 2의 (a)에 도시된다. 이 스테이지의 평면도는 도 5에 해당한다. 이 실시예에서, IGZO 반도체층(103)을 형성하기 위해 제2 IGZO 막은 ITO-07N(칸토 케미칼 주식회사)를 사용하여 습식 에칭에 의해 제거된다. 제1 IGZO 막의 에칭 및 제2 IGZO 막의 에칭에 동일한 에칭제(etchant)가 사용됨을 알아야 하고, 따라서, 이러한 에칭에 의해, 제1 IGZO 막이 제거된다. 이에 따라, 제2 IGZO 막으로 덮인 제1 IGZO 막의 측면은 보호되는 반면, 제1 IGZO 막의 다른 측면은 노출되어 약간 에칭되고, 도 2의 (a)에 도시된 것과 같이 측면의 형상이 변경된다. IGZO 반도체층(103)의 에칭은 습식 에칭에 제한되지 않고, 건식 에칭일 수 있음을 알아야 한다.

- [0064] 그 다음, 레지스트 마스크가 제거되고, IGZO 반도체층을 덮기 위해 보호 절연막(107)이 형성된다. 보호 절연막(107)으로서, 스퍼터링 방법에 의해 얻어지는 질화 실리콘 막, 산화질화 실리콘 막, 산화 알루미늄 막, 산화 탄탈륨 막 등이 사용될 수 있다.

- [0065] 그 다음, 레지스트 마스크를 형성하기 위해 제4 포토리소그래피 단계가 수행되고, 드레인 전극층(105b)에 도달하는(reaching) 컨택트 홀(contact hole; 125)을 형성하기 위해 보호 절연막(107)이 에칭된다. 또한, 이러한 에칭에 의해, 제2 터미널(122)에 도달하는 컨택트 홀(127)도 형성된다. 마스크의 개수를 감소시키기 위해, 동일한 레지스트 마스크를 사용하여 게이트 절연층을 더 에칭하여 게이트 전극에 도달하는 컨택트 홀(126)을 형성하는 것이 바람직함을 알아야 한다. 이 스테이지의 단면도는 도 2의 (b)에 도시된다.

- [0066] 그 후, 레지스트 마스크가 제거된 후, 투명 전도성 막이 형성된다. 투명 전도성 막은 스퍼터링 방법, 진공 증착 방법 등에 의해 인듐 산화물( $In_2O_3$ ), 인듐 산화물 및 주석 산화물의 합금( $In_2O_3-SnO_2$ , ITO로 약칭됨) 등을 사용하여 형성된다. 이와 같은 재료의 에칭 처리는 염산 기반의 용액으로 수행된다. 대신에, 특히 ITO의 에칭에서 잔여물이 생성되는 경향이 있으므로, 에칭 가공성(etching processability)을 항상시키기 위해 인듐 산화물과 아연 산화물( $In_2O_3-ZnO$ )이 사용될 수 있다.

- [0067] 그 다음, 레지스트 마스크를 형성하기 위해 제5 포토리소그래피 단계가 수행되고, 픽셀 전극(110)을 형성하기 위해 투명 전도성 막의 불필요한 부분이 에칭에 의해 제거된다.

- [0068] 제5 포토리소그래피 단계에서, 캐패시터 부분의 게이트 절연막(102)과 보호 절연막(107)이 유전체로 사용되고 캐패시터 배선(108) 및 픽셀 전극(110)으로 인해 저장 캐패시터(storage capacitor)가 형성된다.

- [0069] 또한, 제5 포토리소그래피 단계에서, 제1 터미널 및 제2 터미널은 레지스트 마스크로 덮이고, 투명 전도성 막(128과 129)은 터미널부에 남아있게 된다. 투명 전도성 막(128과 129)은 FPC와 접속하기 위해 사용되는 전극 또는 배선으로서 기능한다. 제2 터미널(122) 위에 형성되는 투명 전도성 막(129)은 소스 배선의 입력 터미널로서 기능하는 접속 터미널 전극이다.

- [0070] 그 후, 레지스트 마스크는 제거되며, 이 스테이지의 단면도는 도 2의 (c)에 도시된다. 이 스테이지의 평면도는 도 6에 해당한다.

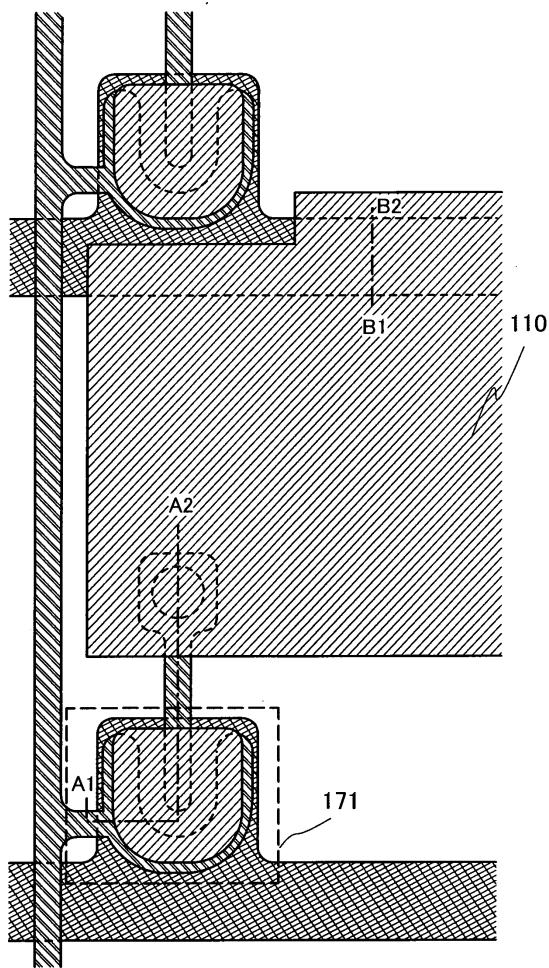

- [0071] 도 7a 및 7b는 각각 이 스테이지의 게이트 배선 터미널부의 단면도와 평면도를 도시한다. 도 7a는 도 7b에서 라인 C1-C2에 따라 취한 단면도에 해당한다. 도 7a에서, 보호 절연막(154) 위에 형성된 투명 전도성 막(155)은 입력 터미널로서 기능하는 접속 터미널 전극이다. 도 7a의 터미널부에서, 게이트 배선과 동일한 재료로부터 형성된 제1 터미널(151) 및 소스 배선과 동일한 재료로부터 형성된 접속 전극(153)은 그 사이에 삽입되어 있는 게이트 절연층(152)과 함께 서로 중첩되어 있고, 투명 전도성 막(155)에 의해 전기적으로 접속된다. 도 2의 (c)에 도시된 투명 전도성 막(128)과 제1 터미널(121)이 서로 접촉되어 있는 부분은 도 7a에 도시된 투명 전도성

막(155)과 제1 터미널(151)이 서로 접촉되어 있는 부분에 해당함을 알아야 한다. 또한, 제1 IGZO 막(157)은 게이트 절연층(152) 및 접속 전극(153) 사이에 형성된다.

[0072] 도 7c 및 7d는 각각 도 2의 (c)에 도시된 소스 배선 터미널부와는 상이한 소스 배선 터미널부의 단면도 및 평면도를 도시한다. 도 7c는 도 7d에서 라인 D1-D2에 따라 취한 단면도에 해당한다. 도 7c에서, 보호 절연막(154) 위에 형성된 투명 전도성 막(155)은 입력 터미널로서 기능하는 접속 터미널 전극이다. 도 7c의 터미널부에서, 게이트 배선과 동일한 재료로부터 형성된 전극(156)은 제2 터미널(150) 아래에 위치하고, 그 사이에 삽입된 게이트 절연층(152)과 함께 소스 배선과 전기적으로 접속된 제2 터미널과 중첩된다. 전극(156)은 제2 터미널(150)에 전기적으로 접속되지 않으며, 전극(156)이 부동(floating), GND 또는 0V와 같이 제2 터미널(150)과 상이한 전위에 설정된다면, 노이즈(noise)에 대한 대책으로서의 캐패시터 또는 정전기에 대한 대책으로서의 캐패시터가 형성될 수 있다. 제2 터미널(150)은 보호 절연막(154)에 의해 투명 전도성 막(155)에 전기적으로 접속된다. 또한 제1 IGZO 막(158)은 게이트 절연층(152)과 제2 터미널(150) 사이에 형성된다.

[0073] 복수의 게이트 배선, 소스 배선 및 캐패시터 배선은 픽셀 밀도에 따라 제공된다. 터미널부에, 게이트 배선과 동일한 전위에 있는 복수의 제1 터미널, 소스 배선과 동일한 전위에 있는 제2 터미널, 캐패시터 배선과 동일한 전위에 있는 제3 터미널 등이 배열된다. 각 유형의 터미널의 개수는 실시자에 의해 선택에 따라 적절하게 결정될 수 있다.

[0074] 이러한 다섯 개의 포토리소그래피 단계에 의해, 다섯 개의 포토마스크를 사용하여, 바텀 게이트 n-채널 TFT(bottom-gate n-channel TFT)인 박막 트랜지스터(170)를 포함하는 픽셀 TFT 부분 및 저장 캐패시터가 완성될 수 있다. 이들은 각각의 픽셀에 매트릭스로 배열되어, 액티브 매트릭스 디스플레이 장치를 생산하기 위한 기판의 하나로 사용될 수 있는 픽셀부가 형성된다. 본 명세서에서, 이와 같은 기판은 편의를 위해 액티브 매트릭스 기판이라고 지칭된다.

[0075] 액티브 매트릭스 액정 디스플레이 장치를 생산하는 경우, 액정 층이 액티브 매트릭스 기판 및 카운터 전극이 제공된 카운터 기판 사이에 제공되고, 액티브 매트릭스 기판 및 카운터 기판은 서로에게 고정된다. 공통 전극은 카운터 기판 위에 제공된 카운터 전극에 전기적으로 접속되기 위해 액티브 매트릭스 기판 위에 제공되고, 제4 터미널은 공통 전극에 전기적으로 접속되기 위해 터미널부에 제공된다. 이러한 제4 터미널은 GND 또는 0V와 같은 고정된 전위에 있는 공통 전극을 설정하기 위한 터미널이다.

[0076] 본 발명의 일 실시예는 도 6의 픽셀 구조에 제한되지 않으며, 도 6과 상이한 평면도의 예는 도 8에 도시된다. 도 8은 캐패시터 배선이 제공되지 않고, 저장 캐패시터가 서로 중첩되는 픽셀 전극과 인근 픽셀의 게이트 배선으로 형성되고 그 사이에 보호 절연막과 게이트 절연층이 삽입된 예를 도시한다. 이 경우에, 캐패시터 배선 및 캐패시터 배선에 접속된 제3 터미널은 생략될 수 있다. 도 8에서, 도 6에서와 동일한 부분은 동일한 참조 부호에 의해 표시됨을 알아야 한다.

[0077] 액티브 매트릭스 액정 디스플레이 장치에서, 디스플레이 패턴은 매트릭스로 배열된 픽셀 전극의 구동에 의해 화면 위에 형성된다. 구체적으로, 전압이 선택된 픽셀 전극 및 픽셀 전극에 대응하는 카운터 전극 사이에 인가되고, 따라서, 픽셀 전극과 카운터 전극 사이에 배치된 액정 층은 광학적으로 변조된다. 이러한 광변조(optical modulation)는 시청자에 의해 디스플레이 패턴으로 인식된다.

[0078] 액정 디스플레이 장치는 동영상을 디스플레이할 때, 액정 분자 자체의 응답속도가 느리기 때문에 찬상(image sticking)이 생기거나 동영상이 흐려진다(blurred). 액정 디스플레이 장치의 동영상 특성을 향상시키기 위한 기술로서, 한 개 걸러 한 프레임마다(every other frame) 전체적으로 검은색 이미지를 디스플레이하는 소위 블랙 삽입(black insertion)이라 불리는 구동 기술이 있다.

[0079] 또한, 소위 더블-프레임 비율 구동(double-frame rate driving)이라 불리는 또 다른 구동 기술이 있다. 더블-프레임 비율 구동에서, 수직 주기(vertical cycle)는 통상의 수직 주기보다 1.5배 또는 그 이상으로(바람직하게는 2배 또는 그 이상) 더 많도록 설정되어, 동영상 특성이 향상된다.

[0080] 또한, 액정 디스플레이 장치의 동영상 특성을 향상시키기 위한 기술로, 복수의 LED(발광 다이오드) 광원 또는 복수의 EL 광원을 포함하는 면광원(surface light source)이 백라이트(backlight)로 사용되고 면광원에 포함된 각각의 광원은 한 프레임 시간(one frame period)에 간헐 점등(intermittent lightning)을 수행하기 위하여 독립적으로 구동되는 또 다른 구동 기술이 있다. 면광원으로, 3가지 종류 이상의 LED가 사용될 수 있거나, 백색-발광 LED(white-light-emitting LED)가 사용될 수 있다. 복수의 LED가 독립적으로 제어될 수 있으므로, LED가 발광하는 타이밍은 액정의 광변조가 전환되는 타이밍과 동기화될 수 있다. 이 구동 기술에서, LED의 일부는 턴

오프(turned off)될 수 있다. 따라서, 특히 한 화면에서 검은색 이미지 구역의 비율이 높은 경우에는, 액정 디스플레이 장치가 낮은 전력 소비로 구동될 수 있다.

[0081] 액정 디스플레이 장치를 이러한 구동 기술과 조합하는 것에 의해, 동영상 특성과 같은 액정 디스플레이 장치의 디스플레이 특성이 종래의 기술에 비해 향상될 수 있다.

[0082] 이 실시예에서 얻어진 n-채널 트랜지스터(n-channel transistor)는 IGZO 반도체층을 채널 형성 영역으로 포함하고, 우수한 동적 특성을 가지며, 따라서, n-채널 트랜지스터는 이러한 구동 기술과 조합될 수 있다.

[0083] 발광 디스플레이 장치를 생산하는 경우에, 유기 발광 소자의 한 전극(캐소드라고도 불림)은 GND 또는 0V와 같이 낮은 전력 공급 전위(power supply potential)에 설정되고, 따라서, GND 또는 0V와 같이 낮은 전력 공급 전위를 설정하기 위한 제4 터미널이 터미널부에 제공된다. 또한, 발광 디스플레이 장치를 생산하는 경우에, 소스 배선 및 게이트 배선 외에 전력 공급 라인이 제공된다. 따라서, 전력 공급 라인에 전기적으로 접속되는 제5 터미널이 터미널부에 제공된다.

[0084] (실시예 2)

[0085] 이 실시예에서는, 전자 종이(electronic paper)의 예가 본 발명의 실시예에 따른 반도체 장치로서 기술될 것이다.

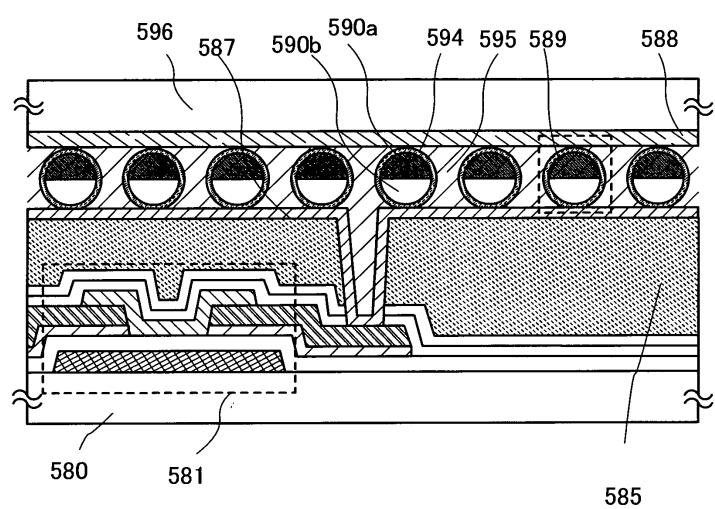

[0086] 도 9는 본 발명의 실시예가 적용된 반도체 장치의 예로서 액티브 매트릭스 전자 종이를 도시한다. 반도체 장치에 사용된 박막 트랜지스터(581)는, 실시예 1에서 기술된 박막 트랜지스터(170)와 유사한 방식으로 생산될 수 있고, 게이트 절연층이 산소 라디칼 처리를 받고, 소스 영역 및 드레인 영역 위에 소스 전극층 및 드레인 전극층, 게이트 절연층, 소스 전극층 및 드레인 전극층 위에 IGZO 반도체층을 포함하는 좋은 전기적 특성을 갖는 박막 트랜지스터이다.

[0087] 도 9의 전자 종이는 트위스팅 볼 디스플레이 시스템(twisting ball display system)의 예이다. 트위스팅 볼 디스플레이에는 각각 검은색과 백색으로 착색된 구형 입자가 디스플레이 소자에 사용되는 전극층인 제1 전극층과 제2 전극층 사이에 배열되는 방법을 지칭하고, 구형 입자의 배향(orientation)을 제어하기 위하여 제1 전극층과 제2 전극층 사이에 전위차를 생성하여 디스플레이가 수행된다.

[0088] 기판(580)과 기판(596) 사이에 밀봉된 박막 트랜지스터(581)는 바텀-게이트 박막 트랜지스터이고, 그 소스 전극층 또는 드레인 전극층은 절연층(585)에 형성된 개구에서 제1 전극층(587)과 접촉해 있음으로써, 박막 트랜지스터(581)는 제1 전극층(587)에 전기적으로 접속된다. 제1 전극층(587)과 제2 전극층(588) 사이에, 각각 검은색 영역(590a), 백색 영역(590b) 및 액체로 채워진 영역 주위의 공동(cavity; 594)을 가지는 구형 입자(589)가 제공된다. 구형 입자(589) 주위의 공간은 수지(resin)와 같은 충진제(filler; 595)로 채워진다 (도 9).

[0089] 또한, 트위스팅 볼 대신에, 전기영동 소자가 사용될 수도 있다. 약 10 $\mu$ m 내지 200 $\mu$ m의 지름을 가지고 투명한 액체 내에 양으로 대전된 백색 마이크로입자 및 음으로 대전된 검은색 마이크로입자가 인캡슐화된 마이크로캡슐이 사용된다. 제1 전극층과 제2 전극층 사이에 제공된 마이크로캡슐에서, 제1 전극층 및 제2 전극층에 의해 전기장이 인가되면, 백색 마이크로입자 및 검은색 마이크로입자는 반대쪽으로 움직여서, 백색 또는 검은색이 디스플레이될 수 있다. 이 원리를 사용한 디스플레이 소자는 전기영동 디스플레이 소자이며, 일반적으로 전자 종이라고 불린다. 전기영동 디스플레이 소자는 액정 디스플레이 소자 보다 더 높은 반사율을 가지며, 따라서 보조라이트가 불필요하고, 전력 소모가 낮으며, 어두운 곳에서도 디스플레이부가 인식될 수 있다. 또한, 전력이 디스플레이부에 공급되지 않을 때라도, 한번 디스플레이된 이미지는 유지될 수 있다. 따라서, 디스플레이 기능(단순히 디스플레이 장치 또는 디스플레이 장치가 제공된 반도체 장치로 지칭될 수 있음)을 가지는 반도체 장치가 전파 소스(electric wave source)로부터 떨어져 있더라도, 디스플레이된 이미지는 저장될 수 있다.

[0090] 이러한 공정을 통해, 높은 신뢰도의 전자 종이가 반도체 장치로서 생산될 수 있다.

[0091] 이 실시예는 실시예 1에 기술된 어느 구조와도 조합하여 구현될 수 있다.

[0092] (실시예 3)

[0093] 이 실시예에서, 적어도 구동 회로의 일부와 픽셀부에 배열된 박막 트랜지스터가 디스플레이 장치의 동일한 기판 위에 형성되는 하나의 예가 이하에서 기술될 것이며, 이는 본 발명의 실시예의 반도체 장비의 한 예이다.

[0094] 픽셀부에 배열되는 박막 트랜지스터는 실시예 1에 따라 형성된다. 또한 실시예 1에 기술된 박막 트랜지스터는 n-채널형 TFT이고, 따라서, 구동 회로 중에 n-채널 TFT를 포함할 수 있는 구동 회로의 일부는 픽셀부의 박막 트

랜지스터와 동일 기판 위에 형성된다.

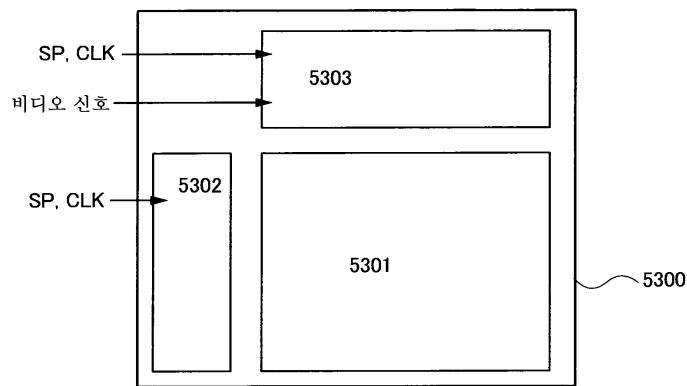

[0095] 도 10a는 본 발명의 실시예의 반도체 장치의 예인 액티브 매트릭스 액정 디스플레이 장치의 블록도의 예를 도시한다. 도 10a에 도시된 디스플레이 장치는 기판(5300) 위에, 디스플레이 소자가 제공되는 복수의 픽셀을 포함하는 픽셀부(5301), 픽셀을 선택하는 스캔 라인 구동 회로(5302) 및 선택된 픽셀로의 비디오 신호 입력을 제어하는 신호 라인 구동 회로(5303)를 포함한다.

[0096] 또한, 실시예 1에 기술된 박막 트랜지스터는 n-채널 TFT이며, n-채널 TFT를 포함하는 신호 라인 구동 회로는 도 11을 참조하여 기술된다.

[0097] 도 11에 기술된 신호 라인 구동 회로는 구동 IC(5601), 스위치 그룹(5602\_1 내지 5602\_M), 제1 배선(5611), 제2 배선(5612), 제3 배선(5613) 및 배선(5621\_1 내지 5621\_M)을 포함한다. 스위치 그룹(5602\_1 내지 5602\_M) 각각은 제1 박막 트랜지스터(5603a), 제2 박막 트랜지스터(5603b) 및 제3 박막 트랜지스터(5603c)를 포함한다.

[0098] 픽셀부(5301)는 신호 라인 드라이버 회로(5303)로부터 열 방향으로 연장된 복수의 신호 라인(S1 내지 Sm; 도시하지 않음)에 의해 신호 라인 구동 회로(5303)에 접속되고, 스캔 라인 구동 회로(5302)로부터 행 방향으로 연장된 복수의 스캔 라인(G1 내지 Gn; 도시하지 않음)에 의해 스캔 라인 구동 회로(5302)에 접속된다. 픽셀부(5301)는 신호 라인(S1 내지 Sm) 및 스캔 라인(G1 내지 Gn)에 대응하도록 매트릭스로 배열된 복수의 픽셀(도시하지 않음)을 포함한다. 각각의 픽셀은 신호 라인(Sj; 신호 라인{S1 내지 Sm} 중 하나) 및 스캔 라인(Gj; 스캔 라인{G1 내지 Gn} 중 하나)에 접속된다.

[0099] 구동 IC(5601)는 제1 배선(5611), 제2 배선(5612), 제3 배선(5613) 및 배선(5621\_1 내지 5621\_M)에 접속된다. 스위치 그룹(5602\_1 내지 5602\_M) 각각은 제1 배선(5611), 제2 배선(5612), 제3 배선(5613) 및 배선(5621\_1 내지 5621\_M)에 접속되고, 배선(5621\_1 내지 5621\_M)은 각각 스위치 그룹(5602\_1 내지 5602\_M)에 접속된다. 배선(5621\_1 내지 5621\_M) 각각은 제1 박막 트랜지스터(5603a), 제2 박막 트랜지스터(5603b) 및 제3 박막 트랜지스터(5603c)를 통해 세 개의 신호 라인에 접속된다. 예를 들어, J 번째 열의 배선(5621\_J; 배선{5612\_1 내지 5612\_M} 중 하나)은 제1 박막 트랜지스터(5603a), 제2 박막 트랜지스터(5603b) 및 제3 박막 트랜지스터(5603c)를 통해 신호 라인(Sj-1), 신호 라인(Sj) 및 신호 라인(Sj+1)에 접속된다.

[0100] 신호는 제1 배선(5611), 제2 배선(5612) 및 제3 배선(5613) 각각에 입력된다.

[0101] 구동 IC(5601)는 단결정 반도체 기판 위에 형성되는 것이 바람직함을 알아야 한다. 스위치 그룹(5602\_1 내지 5602\_M)은 픽셀부가 있는 곳과 동일한 기판 위에 형성되는 것이 바람직하다. 따라서, 구동 IC(5601) 및 스위치 그룹(5602\_1 내지 5602\_M)은 FPC 등을 통해 접속되는 것이 바람직하다.

[0102] 그 다음, 도 11에 도시된 신호 라인 구동 회로의 동작은 도 12의 타이밍 차트를 참조하여 기술된다. 도 12의 타이밍 차트는 i 번째 행의 스캔 라인(Gi)이 선택된 경우를 도시한다. i 번째 행의 스캔 라인(Gi)의 선택 시간(selection period)은 제1 서브-선택 시간(T1), 제2 서브-선택 시간(T2) 및 제3 서브-선택 시간(T3)으로 분할된다. 또한, 도 11의 신호 라인 구동 회로는 또 다른 행의 스캔 라인이 선택되었을 때도 도 12와 유사하게 동작한다.

[0103] 도 12의 타이밍 차트는 J 번째 열의 배선(5621\_J)이 제1 박막 트랜지스터(5603a), 제2 박막 트랜지스터(5603b) 및 제3 박막 트랜지스터(5603c)를 통해 신호 라인(Sj-1), 신호 라인(Sj), 신호 라인(Sj+1)에 접속되는 경우를 보여준다.

[0104] 도 12의 타이밍 차트는 i 번째 행의 스캔 라인(Gi)이 선택되는 타이밍, 제1 박막 트랜지스터(5603a)의 온/오프(on/off) 타이밍(5703a), 제2 박막 트랜지스터(5603b)의 온/오프 타이밍(5703b), 제3 박막 트랜지스터(5603c)의 온/오프 타이밍(5703c) 및 J 번째 열의 배선(5621\_J)으로 입력된 신호(5721\_J)를 보여준다.

[0105] 제1 서브-선택 시간(T1), 제2 서브-선택 시간(T2) 및 제3 서브-선택 시간(T3)에서, 상이한 비디오 신호가 배선(5621\_1 내지 5621\_M)에 입력된다. 예를 들어, 제1 서브-선택 시간(T1)에서 배선(5621\_J)에 입력된 비디오 신호는 신호 라인(Sj-1)에 입력되고, 제2 서브-선택 시간(T2)에 배선(5621\_J)에 입력된 비디오 신호는 신호 라인(Sj)에 입력되며, 제3 서브-선택 시간(T3)에 배선(5621\_J)에 입력된 비디오 신호는 신호 라인(Sj+1)에 입력된다. 또한, 제1 서브-선택 시간(T1), 제2 서브-선택 시간(T2) 및 제3 서브-선택 시간(T3)에서, 배선(5621\_J)에 입력된 비디오 신호는 Data\_j-1, Data\_j 및 Data\_j+1로 표시된다.

[0106] 도 12에 도시된 바와 같이, 제1 서브-선택 시간(T1)에서, 제1 박막 트랜지스터(5603a)는 턴 온(turn on)되고 제2 박막 트랜지스터(5603b) 및 제3 박막 트랜지스터(5603c)는 턴 오프된다. 이 때, 배선(5621\_J)에 입력된

Data\_j-1이 제1 박막 트랜지스터(5603a)를 통해 신호 라인(Sj-1)에 입력된다. 제2 서브-선택 시간(T2)에서, 제2 박막 트랜지스터(5603b)가 턴 온되고, 제1 박막 트랜지스터(5603a) 및 제3 박막 트랜지스터(5603c)는 턴 오프된다. 이 때, 배선(5621\_J)에 입력된 Data\_j는 제2 박막 트랜지스터(5603b)를 통해 신호 라인(Sj)에 입력된다. 제3 서브-선택 시간(T3)에서, 제3 박막 트랜지스터(5603c)가 턴 온되고, 제1 박막 트랜지스터(5603a) 및 제2 박막 트랜지스터(5603b)는 턴 오프된다. 이 때, 배선(5621\_J)에 입력된 Data\_j+1은 제3 박막 트랜지스터(5603c)를 통해 신호 라인(Sj+1)에 입력된다.

[0107] 전술된 것과 같이, 도 11의 신호 라인 구동 회로에서, 하나의 게이트 선택 시간을 세 개로 분할하는 것에 의해, 비디오 신호는 하나의 게이트 선택 시간에서 하나의 배선(5621)으로부터 세 개의 신호 라인으로 입력될 수 있다. 따라서, 도 11의 신호 라인 구동 회로에서, 구동 IC(5601)가 제공된 기판 및 픽셀부가 제공된 기판의 접속의 개수는 신호 라인의 개수의 대략 1/3 정도 일 수 있다. 접속의 개수는 신호 라인의 개수의 대략 1/3 정도 까지 감소되어 도 11의 신호 라인 구동 회로의 신뢰도, 수율(yield) 등이 향상될 수 있다.

[0108] 하나의 게이트 선택 시간이 복수의 서브-선택 시간으로 분할되고, 비디오 신호가 도 11에 도시된 바와 같이 복수의 서브-선택 시간의 각각에서 하나의 배선으로부터 복수의 신호 라인에 입력되는 한, 박막 트랜지스터의 배열, 개수, 구동 방법 등에 특정한 제한이 없음을 알아야 한다.

[0109] 예를 들어, 비디오 신호가 세 개 이상의 서브-선택 시간의 각각에서 하나의 배선으로부터 세 개 이상의 신호 라인에 입력되면, 박막 트랜지스터 및 박막 트랜지스터를 제어하기 위한 배선을 추가해야 할 필요성이 있다. 하나의 게이트 선택 시간이 네 개 이상의 서브-선택 시간으로 분할되면, 하나의 서브-선택 시간이 더 짧아진다는 것을 알아야 한다. 따라서, 하나의 게이트 선택 시간은 두 개 또는 세 개의 서브-선택 시간으로 분할되는 것이 바람직하다.

[0110] 또 다른 예로서, 하나의 게이트 선택 시간은 도 13의 타이밍 차트에 도시된 바와 같이 사전 충전 시간(Tp; precharge period), 제1 서브-선택 시간(T1), 제2 서브-선택 시간(T2) 및 제3 서브-선택 시간(T3)의 네 개의 시간으로 분할될 수 있다. 도 13의 타이밍 차트는 i 번째 행의 스캔 라인(Gi)이 선택되는 타이밍, 제1 박막 트랜지스터(5603a)의 온/오프 타이밍(5803a), 제2 박막 트랜지스터(5603b)의 온/오프 타이밍(5803b), 제3 박막 트랜지스터(5603c)의 온/오프 타이밍(5803c) 및 J 번째 열의 배선(5621\_J)에 입력된 신호(5821\_J)를 도시한다. 도 13에서 도시된 바와 같이, 제1 박막 트랜지스터(5603a), 제2 박막 트랜지스터(5603b) 및 제3 박막 트랜지스터(5603c)는 사전 충전 시간(Tp)에서 턴 온된다. 이 때, 배선(5621\_J)에 입력된 사전 충전 전압(Vp)은 제1 박막 트랜지스터(5603a), 제2 박막 트랜지스터(5603b) 및 제3 박막 트랜지스터(5603c)를 통해 신호 라인(Sj-1), 신호 라인(Sj), 신호 라인(Sj+1) 각각에 입력된다. 제1 서브-선택 시간(T1)에서, 제1 박막 트랜지스터(5603a)는 턴 온되고, 제2 박막 트랜지스터(5603b) 및 제3 박막 트랜지스터(5603c)는 턴 오프된다. 이 때, 배선(5621\_J)에 입력된 Data\_j-1은 제1 박막 트랜지스터(5603a)를 통해 신호 라인(Sj-1)에 입력된다. 제2 서브-선택 시간(T2)에서, 제2 박막 트랜지스터(5603b)는 턴 온되고, 제1 박막 트랜지스터(5603a) 및 제3 박막 트랜지스터(5603c)는 턴 오프된다. 이 때, 배선(5621\_J)에 입력된 Data\_j는 제2 박막 트랜지스터(5603b)를 통해 신호 라인(Sj)에 입력된다. 제3 서브-선택 시간(T3)에서, 제3 박막 트랜지스터(5603c)는 턴 온되고, 제1 박막 트랜지스터(5603a) 및 제2 박막 트랜지스터(5603b)는 턴 오프된다. 이 때, 배선(5621\_J)에 입력된 Data\_j+1은 제3 박막 트랜지스터(5603c)를 통해 신호 라인(Sj+1)에 입력된다.

[0111] 전술된 것과 같이, 도 13의 타이밍 차트가 적용되는 도 13의 신호 라인 구동 회로에서, 서브-선택 시간 전에 사전 충전 선택 시간을 제공하는 것에 의해 신호 라인이 사전 충전될 수 있으므로, 비디오 신호는 높은 속도로 픽셀에 기록될 수 있다. 도 12의 부분과 유사한 도 13의 부분은 공통 참조 부호로 표시되고, 동일한 부분의 상세한 설명 및 유사한 기능을 가지는 부분은 생략된다.

[0112] 또한, 스캔 라인 구동 회로의 구조가 기술된다. 스캔 라인 구동 회로는 시프트 레지스터(shift register) 및 버퍼를 포함한다. 추가적으로, 스캔 라인 구동 회로는 몇몇의 경우에 레벨 시프터(level shifter)를 포함할 수 있다. 스캔 라인 구동 회로에서, 클럭 신호(clock signal; CLK) 및 시작 펄스 신호(start pulse signal; SP)가 시프트 레지스터에 입력될 때, 선택 신호가 생성된다. 생성된 선택 신호는 버퍼되고 버퍼에 의해 증폭되며, 결과 신호는 대응하는 스캔 라인에 공급된다. 한 라인의 픽셀의 트랜지스터의 게이트 전극은 스캔 라인에 접속된다. 또한, 한 라인의 픽셀의 트랜지스터가 동시에 턴 온되어야 하므로, 큰 전류를 공급할 수 있는 버퍼가 사용된다.

[0113] 스캔 라인 구동 회로의 일부로 사용되는 시프트 레지스터의 한 모드는 도 14 및 도 15를 참조하여 기술된다.

- [0114] 도 14는 시프트 레지스터의 회로 구성을 도시한다. 도 14에 도시된 시프트 레지스터는 복수의 플립플롭(5701\_i; 플립플롭{5701\_1 내지 5701\_n})을 포함한다. 시프트 레지스터는 제1 클럭 신호의 입력, 제2 클럭 신호, 시작 펄스 신호 및 리셋 신호로 동작된다.

- [0115] 도 14의 시프트 레지스터의 접속 관계가 기술된다. 도 14의 시프트 레지스터의 i 번째 스테이지 플립플롭(5701\_i; 플립플롭{5701\_1 내지 5701\_n} 중 하나)에서, 도 15에 도시된 제1 배선(5501)은 제7 배선(5717\_i-1)에 접속되고, 도 15에 도시된 제2 배선(5502)은 제7 배선(5717\_i+1)에 접속되며, 도 15에 도시된 제3 배선(5503)은 제7 배선(5717\_i)에 접속되고, 도 15에 도시된 제6 배선(5506)은 제5 배선(5715)에 접속된다.

- [0116] 또한, 도 15에 도시된 제4 배선(5504)은, 홀수 번호 스테이지의 플립플롭에서 제2 배선(5712)에 접속되고, 짝수 번호 스테이지의 플립플롭에서 제3 배선(5713)에 접속된다. 도 15에 도시된 제5 배선(5505)은 제4 배선(5714)에 접속된다.

- [0117] 도 15에 도시된 제1 스테이지 플립플롭(5701\_1)의 제1 배선(5501)은 제1 배선(5711)에 접속됨을 알아야 한다. 또한, 도 15에 도시된 n 번째 스테이지 플립플롭(5701\_n)의 제2 배선(5502)은 제6 배선(5716)에 접속된다.

- [0118] 제1 배선(5711), 제2 배선(5712), 제3 배선(5713) 및 제6 배선(5716)은 각각 제1 신호 라인, 제2 신호 라인, 제3 신호 라인 및 제4 신호 라인으로 지칭될 수 있다. 제4 배선(5714) 및 제5 배선(5715)은 각각 제1 전력 공급 라인 및 제2 전력 공급 라인으로 지칭될 수 있다.

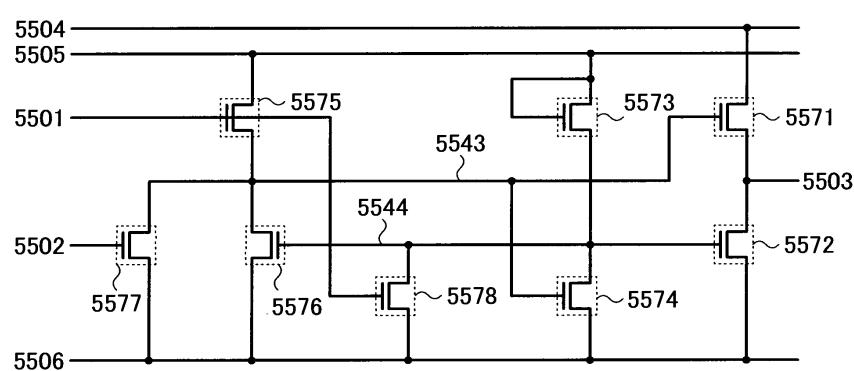

- [0119] 그 다음, 도 15는 도 14에 도시된 플립플롭의 세부사항을 도시한다. 도 15에 도시된 플립플롭은 제1 박막 트랜지스터(5571), 제2 박막 트랜지스터(5572), 제3 박막 트랜지스터(5573), 제4 박막 트랜지스터(5574), 제5 박막 트랜지스터(5575), 제6 박막 트랜지스터(5576), 제7 박막 트랜지스터(5577) 및 제8 박막 트랜지스터(5578)를 포함한다. 제1 박막 트랜지스터(5571), 제2 박막 트랜지스터(5572), 제3 박막 트랜지스터(5573), 제4 박막 트랜지스터(5574), 제5 박막 트랜지스터(5575), 제6 박막 트랜지스터(5576), 제7 박막 트랜지스터(5577) 및 제8 박막 트랜지스터(5578) 각각은 n-채널 트랜지스터이고, 게이트-소스 전압(Vgs)이 문턱 전압(Vth)을 초과할 때 턴 온된다.

- [0120] 그 다음, 도 15에 도시된 플립플롭의 접속 구조가 후술된다.

- [0121] 제1 박막 트랜지스터(5571)의 제 1 전극(소스 전극 및 드레인 전극 중 하나)은 제4 배선(5504)에 접속된다. 제 1 박막 트랜지스터(5571)의 제 2 전극(소스 전극 및 드레인 전극 중 다른 하나)은 제3 배선(5503)에 접속된다.

- [0122] 제2 박막 트랜지스터(5572)의 제1 전극은 제6 배선(5506)에 접속된다. 제2 박막 트랜지스터(5572)의 제2 전극은 제3 배선(5503)에 접속된다.

- [0123] 제3 박막 트랜지스터(5573)의 제1 전극은 제5 배선(5505)에 접속된다. 제3 박막 트랜지스터(5573)의 제2 전극은 제2 박막 트랜지스터(5572)의 게이트 전극에 접속된다. 제3 박막 트랜지스터(5573)의 게이트 전극은 제5 배선(5505)에 접속된다.

- [0124] 제4 박막 트랜지스터(5574)의 제1 전극은 제6 배선(5506)에 접속된다. 제4 박막 트랜지스터(5574)의 제2 전극은 제2 박막 트랜지스터(5572)의 게이트 전극에 접속된다. 제4 박막 트랜지스터(5574)의 게이트 전극은 제1 박막 트랜지스터(5571)의 게이트 전극에 접속된다.

- [0125] 제5 박막 트랜지스터(5575)의 제1 전극은 제5 배선(5505)에 접속된다. 제5 박막 트랜지스터(5575)의 제2 전극은 제1 박막 트랜지스터(5571)의 게이트 전극에 접속된다. 제5 박막 트랜지스터(5575)의 게이트 전극은 제1 배선(5501)에 접속된다.

- [0126] 제6 박막 트랜지스터(5576)의 제1 전극은 제6 배선(5506)에 접속된다. 제6 박막 트랜지스터(5576)의 제2 전극은 제1 박막 트랜지스터(5571)의 게이트 전극에 접속된다. 제6 박막 트랜지스터(5576)의 게이트 전극은 제2 박막 트랜지스터(5572)의 게이트 전극에 접속된다.

- [0127] 제7 박막 트랜지스터(5577)의 제1 전극은 제6 배선(5506)에 접속된다. 제7 박막 트랜지스터(5577)의 제2 전극은 제1 박막 트랜지스터(5571)의 게이트 전극에 접속된다. 제7 박막 트랜지스터(5577)의 게이트 전극은 제2 배선(5502)에 접속된다. 제8 박막 트랜지스터(5578)의 제1 전극은 제6 배선(5506)에 접속된다. 제8 박막 트랜지스터(5578)의 제2 전극은 제2 박막 트랜지스터(5572)의 게이트 전극에 접속된다. 제8 박막 트랜지스터(5578)의 게이트 전극은 제1 배선(5501)에 접속된다.

- [0128] 제1 박막 트랜지스터(5571)의 게이트 전극, 제4 박막 트랜지스터(5574)의 게이트 전극, 제5 박막 트랜지스터

(5575)의 제2 전극, 제6 박막 트랜지스터(5576)의 제2 전극 및 제7 박막 트랜지스터(5577)의 제2 전극이 접속된 지점은 각각 노드(node; 5543)로 지칭됨을 알아야 한다. 제2 박막 트랜지스터(5572)의 게이트 전극, 제3 박막 트랜지스터(5573)의 제2 전극, 제4 박막 트랜지스터(5574)의 제2 전극, 제6 박막 트랜지스터(5576)의 게이트 전극 및 제8 박막 트랜지스터(5578)의 제2 전극이 접속된 지점은 각각 노드(5544)로 지칭된다.

[0129] 제1 배선(5501), 제2 배선(5502), 제3 배선(5503) 및 제4 배선(5504)은 각각 제1 신호 라인, 제2 신호 라인, 제3 신호 라인 및 제4 신호 라인으로 지칭될 수 있다. 제5 배선(5505) 및 제6 배선(5506)은 각각 제1 전력 공급 라인 및 제2 전력 공급 라인으로 지칭될 수 있다.

[0130] 또한, 신호 라인 구동 회로 및 스캔 라인 구동 회로는 실시예 1에서 기술된 n-채널 TFT만을 사용하여 형성될 수 있다. 실시예 1에서 기술된 n-채널 TFT는 높은 이동도를 가지고 있으며, 따라서 구동 회로의 구동 주파수가 증가될 수 있다. 또한 기생 캐패시턴스는 인듐, 갈륨 및 아연을 포함하는 산소-부족 산화물 반도체인 소스 영역 또는 드레인 영역에 의해 감소되고, 따라서 실시예 1에서 기술된 n-채널 TFT는 높은 주파수 특성(f 특성이라고 지칭됨)을 가진다. 예를 들어, 실시예 1에서 기술된 n-채널 TFT를 사용하는 스캔 라인 구동 회로는 높은 속도에서 동작할 수 있고, 따라서, 프레임 주파수는 감소될 수 있으며, 검은색 이미지의 삽입이 실현될 수 있다.

[0131] 또한, 스캔 라인 구동 회로에서 트랜지스터의 채널의 폭이 증가되거나 복수의 스캔 라인 구동 회로가 제공될 때, 예를 들어, 더 높은 프레임 주파수가 실현될 수 있다. 복수의 스캔 라인 구동 회로가 제공될 때, 짹수 번호 스캔 라인을 구동하기 위한 스캔 라인 구동 회로가 한쪽에 제공되고 홀수 번호 스캔 라인을 구동하기 위한 스캔 라인 구동 회로는 반대 쪽에 제공되며, 따라서, 프레임 주파수의 증가가 실현될 수 있다.

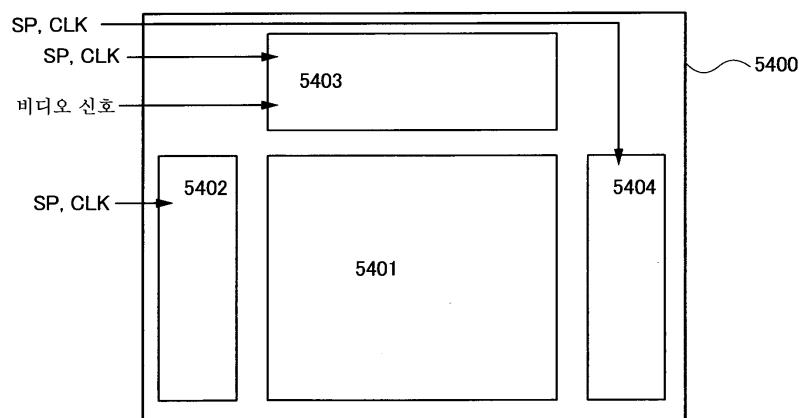

[0132] 또한, 본 발명의 실시예의 반도체 장치의 예인 액티브 매트릭스 발광 디스플레이 장치가 생산될 때, 복수의 박막 트랜지스터가 적어도 하나의 픽셀에 배열되며, 따라서 복수의 스캔 라인 구동 회로가 배열되는 것이 바람직하다. 도 10b는 액티브 매트릭스 발광 디스플레이 장치의 예를 도시하는 블록도이다.

[0133] 도 10b에 도시된 발광 디스플레이 장치는 기판(5400) 위에, 디스플레이 소자가 제공된 복수의 픽셀을 가지는 픽셀부(5401), 픽셀을 선택하는 제1 스캔 라인 구동 회로(5402) 및 제2 스캔 라인 구동 회로(5404) 및 선택된 픽셀로의 비디오 신호의 입력을 제어하는 신호 라인 구동 회로(5403)를 포함한다.

[0134] 도 10b에 도시된 발광 디스플레이 장치의 픽셀에 입력된 비디오 신호가 디지털 신호일 때, 픽셀은 트랜지스터의 온/오프 스위칭에 의해 발광하거나 발광하지 않는다. 따라서, 그레이스케일(grayscale)은 구역 비율 그레이스케일 방법(area ratio grayscale method) 또는 타임 비율 그레이스케일 방법(time ratio grayscale method)을 사용하여 디스플레이될 수 있다. 구역 비율 그레이스케일 방법은 한 픽셀이 복수의 서브픽셀로 분할되고 비디오 신호에 기초하여 각각의 서브픽셀이 독립적으로 구동되어 그레이스케일이 디스플레이되는 구동 방법을 지칭한다. 또한, 타임 비율 그레이스케일 방법은 픽셀이 발광 상태에 있는 시간을 제어하여 그레이스케일을 디스플레이하는 구동 방법을 지칭한다.

[0135] 발광 소자의 응답 속도(response speed)가 액정 소자 등의 응답 속도보다 더 빠르기 때문에, 타임 비율 그레이스케일 방법은 액정 디스플레이 소자보다 발광 소자에 더 적절하다. 특히, 타임 그레이스케일 방법으로 디스플레이를 하는 경우에는, 한 프레임 시간이 복수의 서브프레임 시간으로 분할된다. 그 다음, 비디오 신호에 따라, 픽셀의 발광 소자는 각각의 서브프레임 시간에서 발광 상태 또는 비발광 상태(non-light-emitting state)로 설정된다. 한 프레임을 복수의 서브프레임으로 분할하는 것에 의해, 한 프레임 시간에 픽셀이 실제로 발광하는 타임의 전체 길이가 비디오 신호로 제어될 수 있어, 그레이스케일이 디스플레이된다.

[0136] 도 10b에 도시된 발광 디스플레이 장치의 예에서, 스위칭 TFT와 전류 제어 TFT의 두 개의 TFT가 한 픽셀에 배열된 경우에, 제1 스캔 라인 구동 회로(5402)는 스위칭 TFT의 게이트 배선으로서 기능을 하는 제1 스캔 라인에 입력되는 신호를 생성하고, 제2 스캔 라인 구동 회로(5404)는 전류 제어 TFT의 게이트 배선으로서 기능을 하는 제2 스캔 라인에 입력되는 신호를 생성하지만, 하나의 스캔 라인 구동 회로가 제1 스캔 라인에 입력되는 신호와 제2 스캔 라인에 입력되는 신호 둘 다를 생성할 수 있다. 또한, 예를 들어, 스위칭 소자에 포함된 트랜지스터의 개수에 따라, 스위칭 소자의 동작을 제어하는데 사용되는 복수의 제1 스캔 라인이 각각의 픽셀에 제공될 가능성이 있다. 그 경우에, 하나의 스캔 라인 구동 회로는 복수의 제1 스캔 라인에 입력되는 모든 신호를 생성할 수 있거나, 복수의 스캔 라인 구동 회로는 복수의 제1 스캔 라인에 입력되는 신호를 생성할 수 있다.

[0137] 또한, 발광 디스플레이 장치에서도, 구동 회로 중에 n-채널 TFT를 포함할 수 있는 구동 회로의 일부는 픽셀부의 박막 트랜지스터와 동일한 기판 위에 형성될 수 있다. 이와 달리, 신호 라인 구동 회로 및 스캔 라인 구동 회로는 실시예 1에 기술된 n-채널 TFT를 사용하여 형성될 수 있다.

- [0138] 또한, 전술된 구동 회로는, 액정 디스플레이 장치 또는 발광 디스플레이 장치에 대한 응용에 제한되지 않고, 스위칭 소자에 전기적으로 접속된 소자를 사용하여 전자 잉크를 구동하는 전자 종이에 사용될 수 있다. 전자 종이는 또한 전기영동 디스플레이 장치(전기영동 디스플레이)로 지칭되고, 일반 종이와 같은 레벨의 가독성(readability)을 가지는 장점이 있으며, 다른 디스플레이 장치보다 전력 소모가 낮고, 얇고 가볍게 만들 수 있다.

- [0139] 전기영동 디스플레이는 다양한 모드를 가질 수 있다. 전기영동 디스플레이는 용매(solvent) 또는 용질(solute)에 분산된 복수의 마이크로캡슐을 포함하고, 각각의 마이크로 캡슐은 양으로 대전된 제1 입자 및 음으로 대전된 제2 입자를 포함한다. 마이크로캡슐에 전기장을 인가하는 것에 의해, 마이크로캡슐 내의 입자가 서로의 반대 방향으로 움직이고 한 쪽에 집중된 입자의 색만이 나타난다. 제1 입자 및 제2 입자는 각각 안료를 포함하고, 전기장이 없으면 움직이지 않는다. 또한, 제1 입자 및 제2 입자의 색은 서로 상이하다(색은 무색 또는 아크로마{achroma}를 포함함).

- [0140] 이렇게 하여, 전기영동 디스플레이는 높은 유전 상수를 가지는 물질이 높은 전기장 영역으로 움직이는 소위 유전영동 효과(dielectrophoretic effect)를 이용하는 디스플레이이다. 전기영동 디스플레이는 액정 디스플레이 장치에서 필요로 하는 편광자 및 카운터 기판을 사용할 필요가 없고, 전기영동 디스플레이 장치의 두께 및 무게는 액정 디스플레이 장치의 절반일 수 있다.

- [0141] 전술한 마이크로캡슐이 용매의 도체에 분산되어 있는 용액(solution)은 전자 잉크라고 지칭된다. 이 전자 잉크는 유리, 플라스틱, 천, 종이 등의 표면 위에 인쇄될 수 있다. 또한, 안료를 가지는 색 필터 또는 입자의 사용에 의해 색 디스플레이도 가능해진다.

- [0142] 또한, 복수의 전술된 마이크로캡슐이 두 전극 사이에 삽입되도록 액티브 매트릭스 기판 위에 적절히 배치되면, 액티브 매트릭스 디스플레이 장치는 완성될 수 있으며, 디스플레이는 마이크로캡슐에 대한 전기장의 인가에 의해 수행될 수 있다. 예를 들어, 실시예 1에 기술된 박막 트랜지스터에 의해 얻어진 액티브 매트릭스 기판이 사용될 수 있다.

- [0143] 마이크로캡슐 내의 제1 입자 및 제2 입자는 각각 전도성 재료, 절연 재료, 반도체 재료, 자기 재료, 액정 재료, 강유전성 재료(ferroelectric material), 전계 발광 재료(electroluminescent material), 일렉트로크로믹 재료(electrochromic material) 또는 마그네토포레틱 재료(magnetophoretic material)로부터 선택된 단일 재료로 형성될 수 있거나 이를 중 임의의 복합 재료로 형성될 수 있다.

- [0144] 위의 단계를 통하여, 반도체 장치로서의 높은 신뢰도의 디스플레이 장치가 생산될 수 있다.

- [0145] 이 실시예는 다른 실시예에서 개시된 구성과 적절히 조합될 수 있다.

- [0146] (실시예 4)

- [0148] \*본 발명의 실시예의 발명의 박막 트랜지스터는 생산되고, 디스플레이 기능을 가지는 반도체 장치(디스플레이 장치로도 지칭됨) 또는 발광 소자(발광 디스플레이 소자로도 지칭됨)가 사용하여 생산될 수 있다. 또한, 구동 회로의 일부 또는 전부는 본 발명의 실시예의 박막 트랜지스터를 사용하여 픽셀부와 동일한 기판 위에 형성될 수 있어 시스템 온 패널(system-on-panel)이 얻어질 수 있다.

- [0149] 디스플레이 장치는 디스플레이 소자를 포함한다. 디스플레이 소자로, 액정 소자(액정 디스플레이 소자로도 지칭됨) 또는 발광 소자(발광 디스플레이 소자로도 지칭됨)가 사용될 수 있다. 발광 소자는 그 카테고리에 광도가 전류 또는 전압에 의해 제어되는 소자를 포함하고, 특히 무기 전계 발광(EL) 소자, 유기 EL 소자 등을 포함한다. 또한, 전기 잉크와 같이 전기 효과(electric effect)에 의해 그 명암(contrast)이 변경될 수 있는 전기 디스플레이 매체가 사용될 수 있다.

- [0150] 또한, 디스플레이 장치는 디스플레이 소자가 밀봉된 패널 및 제어기 등을 포함하는 IC가 패널 위에 탑재된 모듈을 포함한다. 본 발명의 실시예는 디스플레이 소자가 디스플레이 장치의 생산 공정에서 완성되기 전의 소자 기판(element substrate)의 한 모드에 관련되고, 소자 기판에는 복수의 픽셀 각각의 디스플레이 소자에 전류를 공급하기 위한 유닛이 제공된다. 보다 구체적으로, 소자 기판은, 픽셀 전극이 되는 전도성 막이 형성된 후이며 픽셀 전극을 형성하기 위해 전도성 막이 예정되기 전의 상태인, 디스플레이 소자의 픽셀 전극만이 제공되는 상태에 있을 수 있거나 다른 상태들 중 임의의 하나의 상태에 있을 수 있다.

- [0151] 본 명세서의 디스플레이 장치는 이미지 디스플레이 장치, 디스플레이 장치 또는 광원(점등 장치를 포함함)을 의미한다. 또한, 디스플레이 장치는 그 카테고리에, 연성 인쇄 회로(flexible printed circuit; FPC), 테입 오

토메이티드 본딩(tape automated bonding; TAB) 테입 또는 테입 캐리어 패키지(tape carrier package; TCP)와 같은 접속부가 부착된 모듈, 그 단부에 인쇄 배선판(printed wiring board)이 제공되고 TAB 테입 또는 TCP를 가지는 모듈 및 칩 온 글라스(chip on glass; COG) 방법에 의해 디스플레이 소자 위에 직접 탑재된 접착 회로(IC)를 가지는 모듈 중의 임의의 하나를 포함한다.

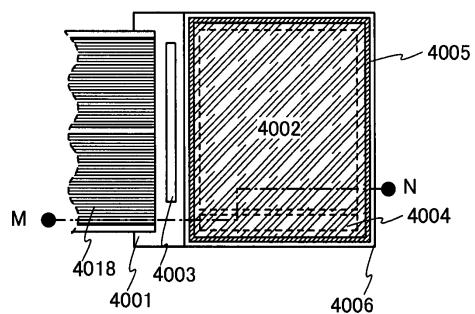

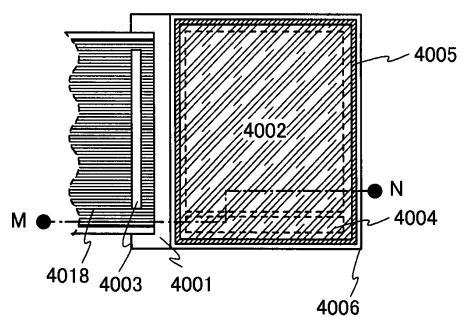

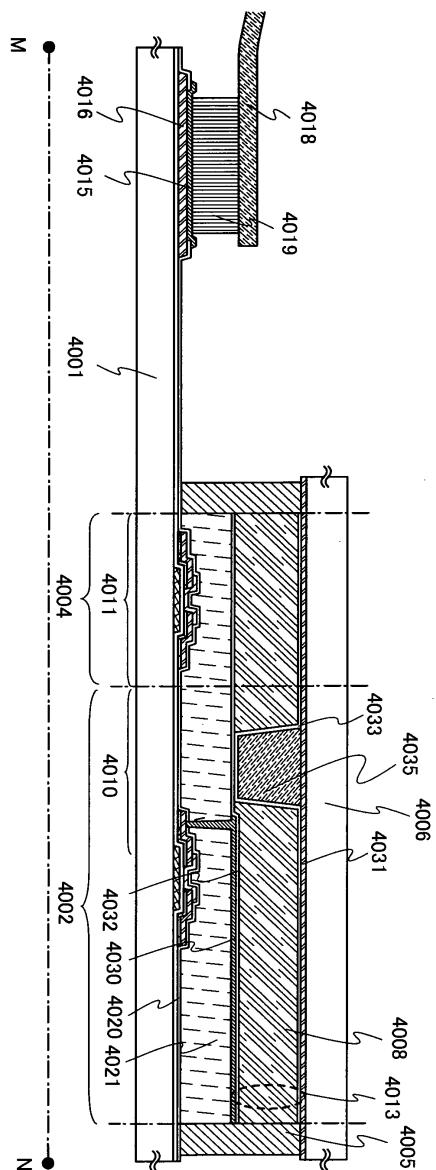

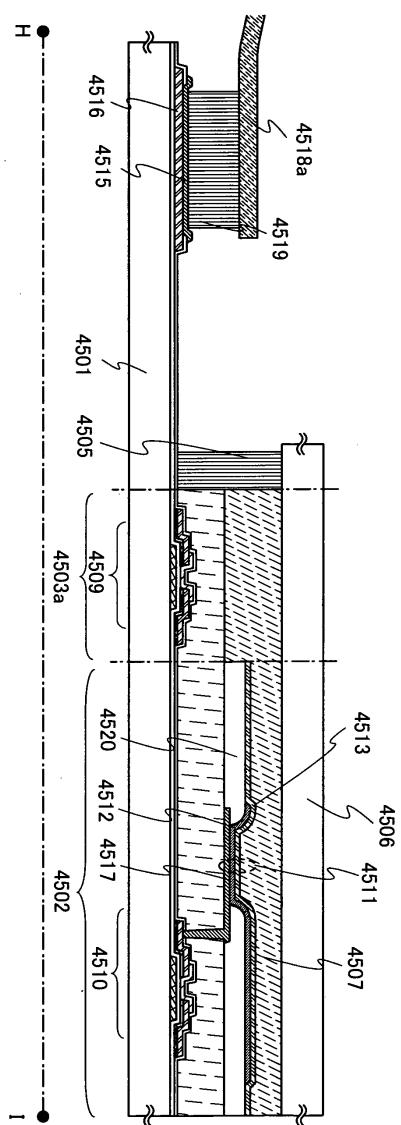

[0152] 이 실시예에서, 본 발명의 반도체 장치의 한 실시예인 액정 디스플레이의 외형 및 단면은 도 16a 내지 16c를 참조하여 기술될 것이다. 도 16a 및 도 16b는 제1 기판(4001) 위에 형성되고 산소 라디칼 처리를 받는 게이트 절연층, 소스 영역 및 드레인 영역 위에 소스 전극층 및 드레인 전극층, 그리고 게이트 절연층, 소스 전극층 및 드레인 전극층 위에 IGZO 반도체층을 포함하는 좋은 전기적 특성을 갖는 박막 트랜지스터(4010 및 4011) 및 액정 소자(4013)가 제1 기판(4001)과 제2 기판(4006) 사이에 밀봉제(sealant; 4005)에 의해 밀봉된 패널의 평면도이다. 도 16c는 도 16a 및 16b의 라인 M-N을 따라 취한 단면도이다.

[0153] 밀봉제(4005)는 제1 기판(4001) 위에 제공된 꽈셀부(4002) 및 스캔 라인 구동 회로(4004)를 둘러싸도록 제공된다. 제2 기판(4006)은 꽈셀부(4002) 및 스캔 라인 구동 회로(4004) 위에 제공된다. 따라서, 꽈셀부(4002) 및 스캔 라인 구동 회로(4004)는 액정층(4008)과 함께 제1 기판(4001), 밀봉제(4005) 및 제2 기판(4006)에 의해 밀봉된다. 따로 준비된 기판 위에 단결정 반도체 막 또는 다결정 반도체 막을 사용하여 형성된 신호 라인 구동 회로(4003)가 제1 기판(4001) 위의 밀봉제(4005)에 의해 둘러싸인 영역과 상이한 영역에 탑재된다.

[0154] 따로 형성된 구동 회로의 접속 방법은 특별히 제한되지 않고, COG 방법, 배선 본딩 방법, TAB 방법 등이 사용될 수 있음을 알아야 한다. 도 16a는 COG 방법에 의해 신호 라인 구동 회로(4003)를 탑재하는 예를 도시하고, 도 16b는 TAB 방법에 의해 신호 라인 구동 회로(4003)를 탑재하는 예를 도시한다.

[0155] 제1 기판(4001) 위에 제공된 꽈셀부(4002) 및 스캔 라인 구동 회로(4004)는 복수의 박막 트랜지스터를 포함한다. 도 16c는 꽈셀부(4002)에 포함된 박막 트랜지스터(4010) 및 스캔 라인 구동 회로(4004)에 포함된 박막 트랜지스터(4011)를 도시한다. 절연층(4020 및 4021)은 박막 트랜지스터(4010 및 4011) 위에 형성된다.

[0156] 박막 트랜지스터(4010 및 4011) 각각은, 산소 라디칼 처리를 받는 게이트 절연층, 소스 영역 및 드레인 영역 위에 소스 전극 및 드레인 전극층 그리고 게이트 절연층, 소스 전극층 및 드레인 전극층 위에 IGZO 반도체층을 사용하는 높은 전기 특성을 갖는 박막 트랜지스터에 해당하고, 박막 트랜지스터(4010 및 4011)로서, 실시예 1에서 기술된 박막 트랜지스터(170)가 채용될 수 있다. 이 실시예에서, 박막 트랜지스터(4010 및 4011)는 n-채널 박막 트랜지스터이다.

[0157] 액정 소자(4013)에 포함된 꽈셀 전극층(4030)은 박막 트랜지스터(4010)에 전기적으로 접속된다. 액정 소자(4013)의 카운터 전극층(4031)은 제2 기판(4006)에 형성된다. 꽈셀 전극층(4030), 카운터 전극층(4031) 및 액정층(4008) 서로 간에 중첩되는 부분은 액정 소자(4013)에 해당한다. 꽈셀 전극층(4030) 및 카운터 전극층(4031)에는 각각 배향막(alignment film)으로 기능하는 절연층(4032) 및 절연층(4033)이 각각 제공되고 꽈셀 전극층(4030) 및 카운터 전극층(4031) 사이에 삽입된 절연층(4032 및 4033)을 갖는 액정층(4008)으로 샌드위치 형태를 이룸을 알아야 한다.

[0158] 제1 기판(4001) 및 제2 기판(4006)은 유리, 금속(통상적으로 스테인레스 강), 세라믹 또는 플라스틱을 사용하여 형성됨을 알아야 한다. 플라스틱으로, 유리 섬유 강화 플라스틱(fiberglass-reinforced plastics; FRP), 폴리비닐 플루오라이드(polyvinyl fluoride; PVF) 막, 폴리에스테르 막(polyester film) 또는 아크릴 수지 막(acrylic resin film)이 사용될 수 있다. 또한, 알루미늄 포일(foil)이 PVF 막 또는 폴리에스테르 막 사이에 샌드위치 형태로 끼워진 구조를 갖는 시트(sheet)가 사용될 수 있다.

[0159] 참조 부호(4035)는 절연막을 선택적으로 예칭하는 것에 의해 얻어진 원주형 스페이서(columnar spacer)를 표시하고, 꽈셀 전극층(4030)과 카운터 전극층(4031) 사이의 거리(셀 갭)를 제어하기 위해 제공된다. 또한, 구형 스페이서가 사용될 수도 있다.

[0160] 이와 달리, 배향막이 불필요한 블루상(blue phase)을 나타내는 액정이 사용될 수 있다. 블루상은 콜레스테릭 액정(cholesteric liquid crystal)의 온도가 증가됨에 따라 콜레스테릭상(cholesteric phase)이 등방상(isotropic phase)으로 변하기 직전에 생성되는 액정상들 중 하나이다. 블루상이 오직 좁은 범위의 온도 내에서만 생성되므로, 온도 범위를 향상시키기 위해 5 wt%의 카이랄제(chiral agent)를 포함하는 액정 조성물이 액정층(4008)에 사용된다. 블루상을 보여주는 액정과 카이랄제를 포함하는 액정 조성물은 응답 시간이 10μs 내지 100μs으로 짧고, 액정 조성물이 광학 등방성을 가지므로 배향 공정이 필요하지 않고 시야각 의존도가 낮은 특성이 있다.

- [0161] 이 실시예가 투과형 액정 디스플레이 장치의 예를 도시하지만, 본 발명의 실시예는 또한 반사형 액정 디스플레이 장치 및 반투과형 액정 디스플레이 장치에 적용될 수 있다.

- [0162] 이 실시예는 기판의 바깥 위치(시청자 측)에 제공된 편광판 및 기판의 안쪽 위치에 차례로 제공된 채색층 (coloring layer) 및 디스플레이 소자에 사용되는 전극층을 기술하지만, 편광판은 기판보다 안쪽 위치에 제공될 수 있다. 편광판과 채색층이 적층된 구조는, 이 실시예에만 제한되지 않고, 편광판과 채색층의 재료 또는 생산 단계의 조건에 따라 적절하게 설정될 수 있다. 또한, 블랙 매트릭스(black matrix)로 기능하는 광차단 막 (light-blocking film)이 제공될 수 있다.

- [0163] 이 실시예에서, 박막 트랜지스터의 표면 비균일도(unevenness)를 감소시키고 박막 트랜지스터의 신뢰도를 항상 시키기 위해, 실시예 1에서 얻어진 박막 트랜지스터는 보호막 또는 평탄화 절연막(planarizing insulating film)으로서 기능하는 절연층(절연층{4020} 및 절연층{4021})으로 덮인다. 보호막은 유기 물질, 금속 물질 또는 공기 중에 떠다니는 수분과 같은 오염 불순물(contaminant impurities)의 진입을 방지하기 위해 제공되며 고밀도(dense) 막이 바람직함을 알아야 한다. 보호막은 단일층 또는 산화 실리콘 막, 질화 실리콘 막, 산화질화 실리콘 막, 질화 산화 실리콘 막, 산화 알루미늄 막, 알루미늄 질화물 막, 산화질화 알루미늄 막 및/또는 질화 산화 알루미늄 막의 적층으로 스퍼터링 방법에 의해 형성될 수 있다. 이 실시예에서, 보호막이 스퍼터링 방법에 의해 형성된 예가 보여지나, 이는 특정 방법에 제한되지 않고 다양한 방법이 사용될 수 있다.

- [0164] 여기서, 적층 구조를 갖는 절연층(4020)은 보호막으로 형성된다. 여기서, 산화 실리콘 막은 스퍼터링 방법에 의해 절연층(4020)의 제1 층으로 형성된다. 보호막으로 산화 실리콘 막을 사용하는 것에 의해, 소스 전극층 및 드레인 전극층으로 사용되는 알루미늄막에서 힐락을 방지할 수 있다.

- [0165] 또한, 절연층은 보호막의 제2 층으로 형성될 수 있다. 여기서, 절연층(4020)의 제2 층으로, 질화 실리콘 막이 스퍼터링 방법에 의해 형성될 수 있다. 보호막으로서 질화 실리콘 막의 사용은 나트륨의 이동 이온 등이 반도체 영역으로 유입되는 것을 방지하여 TFT의 전기적 속성의 변동이 억제될 수 있다.

- [0166] 보호막이 형성된 후, IGZO 반도체층은 300°C 내지 400°C에서 어닐링될 수 있다.

- [0167] 절연층(4021)이 평탄화 절연막으로서 형성된다. 절연층(4021)으로, 폴리이미드(polyimide), 아크릴, 폴리아미드, 벤조사이클로부텐(benzocyclobutene), 폴리아미드(polyamide) 또는 에폭시와 같이 내열성을 가지는 유기 재료가 사용될 수 있다. 이러한 유기 재료 외에는, 낮은 유전 상수 재료(low-k 재료), 실록세인 기반의 수지 (siloxane-based resin), PSG(phosphosilicate glass), BPSG(borophosphosilicate glass) 등을 사용하는 것이 가능하다. 실록세인 기반의 수지는 치환기로서, 수소뿐만 아니라 플루오린(fluorine), 알킬 그룹 및 아릴 그룹(aryl group) 중 적어도 하나를 포함할 수 있다. 절연층(4021)은 이들 재료로 형성된 복수의 절연막을 적층하는 것에 의해 형성될 수 있다.

- [0168] 실록세인 기반의 수지는 출발 재료인 실로세인 재료로부터 형성되며 Si-O-Si 본드를 가진다. 실록세인 기반의 수지는 치환기로서, 수소뿐만 아니라 플루오린, 알킬 그룹 및 방향족탄화수소(aromatic hydrocarbon) 중 적어도 하나를 포함할 수 있다.

- [0169] 절연층(4021)을 형성하는 방법에는 특정한 제한이 없고, 재료에 따라, 스퍼터링 방법, SOG 방법, 스판 코팅 방법, 담금 방법(dipping method), 스프레이 인가 방법(spray application method), 액적 방전 방법(droplet discharge method; 예를 들어, 잉크젯 방법, 스크린 인쇄, 오프셋 인쇄 등), 닥터 나이프(doctor knife), 롤 코팅기(roll coater), 커튼 코팅기, 나이프 코팅기 등의 방법이 채용될 수 있다. 재료 용액을 사용하여 절연층(4021)을 형성하는 경우에, IGZO 반도체층의 어닐링(300°C 내지 400°C)은 베이킹 단계(baking step)와 동일한 타임에 수행될 수 있다. 절연층(4021)의 베이킹 단계는 또한 IGZO 반도체층의 어닐링으로서 기능하여, 반도체 장치가 효율적으로 생산될 수 있다.

- [0170] 픽셀 전극층(4030) 및 카운터 전극층(4031)은 텅스텐 산화물을 포함하는 인듐 산화물, 텅스텐 산화물을 포함하는 인듐 아연 산화물, 티타늄 산화물을 포함하는 인듐 산화물, 티타늄 산화물을 포함하는 인듐 틴 산화물, 인듐 틴 산화물(이하 ITO로 지칭함), 인듐 아연 산화물, 산화 실리콘에 추가된 인듐 틴 산화물 등과 같은 광 전달 전도성 재료(light-transmitting conductive material)를 사용하여 형성될 수 있다.

- [0171] 전도성 고분자(전도성 중합체{polymer}로도 지칭됨)를 포함하는 전도성 조성물이 픽셀 전극층(4030) 및 카운터 픽셀 전극층(4031)에 사용될 수 있다. 전도성 조성물을 사용하여 형성된 픽셀 전극은 1제곱 당 10000옴 이하의 시트 저항 및 550nm의 파장에서 70% 이상의 투과율을 가지는 게 바람직하다. 또한, 전도성 조성물에 포함된

전도성 고분자의 비저항은  $0.1\Omega \cdot \text{cm}$  이하인 것이 바람직하다.

[0172] 전도성 고분자로서, 소위  $\pi$  전자가 공액된(conjugated) 전도성 중합체가 사용될 수 있다. 예를 들어, 폴리아닐린(polyaniline) 또는 그 유도체(derivative), 폴리피롤(polypyrrole) 또는 그 유도체, 폴리티오펜(polythiophene) 또는 그 유도체, 그 중 두 종류 이상의 공중합체(copolymer) 등이 주어질 수 있다.

[0173] 또한, 다양한 신호 및 전위가 FPC(4018)로부터, 따로 생성된 신호 라인 구동 회로(4003), 스캔 라인 구동 회로(4004) 또는 광셀부(4002)에 공급될 수 있다.

[0174] 이 실시예에서, 접속 터미널 전극(4015)은 액정 소자(4013)에 포함된 광셀 전극층(4030)과 동일한 전도성 막으로부터 형성되고, 터미널 전극(4016)은 박막 트랜지스터(4010 및 4011)의 소스 전극층 및 드레인 전극층과 동일한 전도성 막으로부터 형성된다.

[0175] 접속 터미널 전극(4015)은 이방성 전도성 막(4019)을 통해 FPC(4018)에 포함된 터미널에 전기적으로 접속된다.

[0176] 도 16a 내지 16c는 신호 라인 구동 회로(4003)가 따로 형성되고 제1 기판(4001)에 탑재되는 예를 도시하지만, 이 실시예는 이 구조에 제한되지 않음을 알아야 한다. 스캔 라인 구동 회로는 따로 형성된 후 탑재될 수 있고, 신호 라인 구동 회로의 일부 또는 스캔 라인 구동 회로의 일부만이 따로 형성된 후 탑재될 수도 있다.

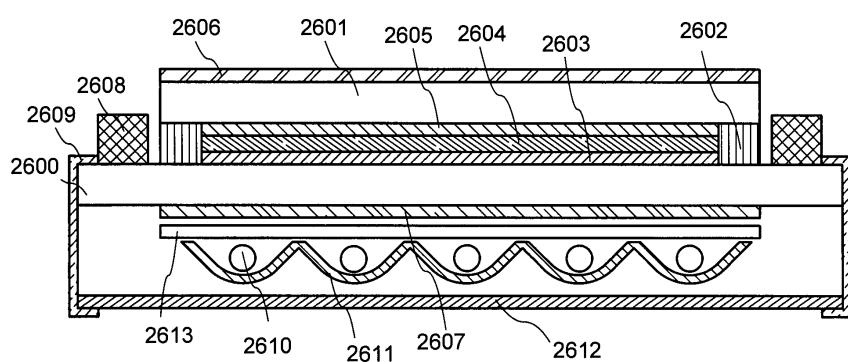

[0177] 도 17은 액정 디스플레이 모듈이 본 발명의 실시예를 적용하여 생산된 TFT 기판(2600)을 사용하는 것에 의해 반도체 장치로 형성된 예를 도시한다.

[0178] 도 17은 TFT 기판(2600) 및 카운터 기판(2601)이 밀봉제(2602)로 서로에게 고정되고, TFT 등을 포함하는 광셀부(2603), 액정층을 포함하는 디스플레이 소자(2604), 채색층(2605) 및 편광판(2606)이 디스플레이 영역을 형성하기 위해 기판 사이에 제공되는 액정 디스플레이 모듈의 예를 도시한다. 채색층(2605)은 컬러 디스플레이를 수행하는데 필수적이다. RGB 시스템의 경우에, 빨간색, 녹색, 파란색에 대응되는 각각의 채색층은 각각의 광셀에 제공된다. 편광판(2606 및 2607) 및 확산판(2613)은 TFT 기판(2600) 및 카운터 기판(2601) 바깥에 제공된다. 광원은 냉음극관(cold cathode tube; 2610) 및 반사판(2611)을 포함하고 회로 기판(2612)은 연성 배선판(2609)을 통하여 TFT 기판(2600)의 배선 회로부(2608)에 접속되며, 제어 회로 또는 전력원 회로와 같은 외부 회로를 포함한다. 편광판 및 액정층은 그 사이에 위상지연판(retardation plate)이 삽입되어 적층될 수 있다.

[0179] 액정 디스플레이 모듈로서, TN(twisted nematic) 모드, IPS(in-plane-switching) 모드, FFS(fringe field switching) 모드, MVA(multi-domain vertical alignment) 모드, PVA(patterned vertical alignment) 모드, ASM(axially symmetric aligned micro-cell) 모드, OCB(optical compensated birefringence) 모드, FLC(ferroelectric liquid crystal) 모드, AFLC(antiferroelectric liquid crystal) 모드 등이 사용될 수 있다.

[0180] 이 공정을 통해, 고 신뢰도의 액정 디스플레이 패널이 반도체 장치로 생산될 수 있다.

[0181] 이 실시예는 다른 실시예에서 개시된 구조와 적절히 조합될 수 있다.

[0182] (실시예 5)

[0183] 이 실시예에서, 발광 디스플레이 장치의 예가 본 발명의 한 실시예의 반도체 장치로 기술될 것이다. 디스플레이 장치에 포함된 디스플레이 소자로서, 전계 발광을 이용하는 발광 소자가 여기서 기술된다. 전계 발광을 이용하는 발광 소자는 발광 재료가 유기 화합물(compound)인지 무기 화합물인지에 따라서 분류된다. 일반적으로, 전자는 유기 EL 소자로 지칭되고, 후자는 무기 EL 소자로 지칭된다.

[0184] 유기 EL 소자에서, 발광 소자에 대한 전압의 인가에 의해, 전자와 정공(holes)은 전극 쌍으로부터 발광 유기 화합물을 포함하는 층으로 각기 주입되어, 전류가 흐른다. 캐리어(전자 및 정공)는 재결합되며, 따라서, 발광 유기 화합물은 여기된다(excited). 발광 유기 화합물은 여기 상태에서 기저 상태(ground state)로 돌아옴으로써 발광한다. 이러한 메카니즘 때문에, 이 발광 소자는 전류-여기 발광 소자(current-excitation light-emitting element)로 지칭된다.

[0185] 무기 EL 소자는 그 소자 구조에 따라 분산형 무기 EL 소자(dispersion-type inorganic EL element) 및 박막 무기 EL 소자로 분류된다. 분산형 무기 EL 소자는 발광 재료의 입자가 접합제(binder)에 분산되어있는 발광층을 가지며, 그 발광 메카니즘은 도너 레벨(donor level) 및 억셉터 레벨(acceptor level)을 이용하는 도너-억셉터 재결합형 발광이다. 박막 무기 EL 소자는 발광층이 유전층 사이에 샌드위치 형태로 끼워진 구조를 가지고, 유전층은 전극 사이에 샌드위치 형태로 끼워지며, 그 발광 메카니즘은 금속 이온의 안쪽 접질 전자 전이(inner-

shell electron transition)를 이용하는 국부형 발광(localized type light emission)이다. 여기서는 유기 EL 소자를 발광 소자로 사용하여 기술되는 것을 알아야 한다.

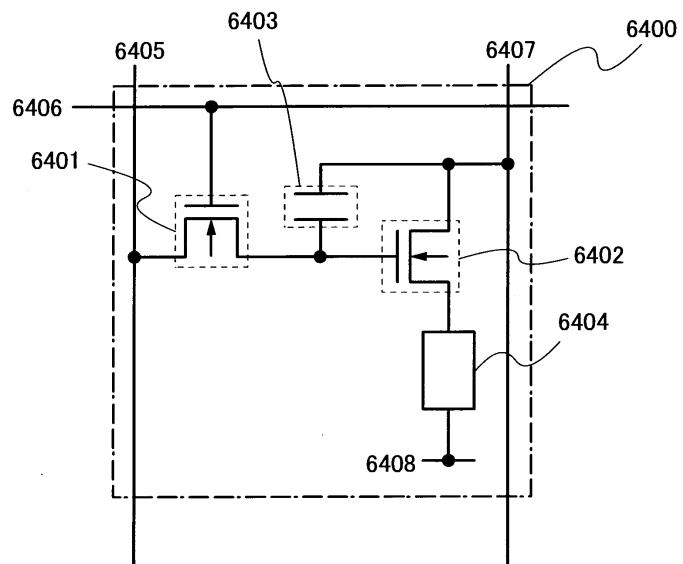

[0186] 도 18은 티지털 타임 그레이스케일 구동이 적용될 수 있는 픽셀 구조의 예를 본 발명의 한 실시예가 적용되는 반도체 장치의 예로서 도시한다.

[0187] 디지털 타임 그레이스케일 구동이 적용될 수 있는 픽셀의 구조 및 동작이 기술된다. 이 예에서, 하나의 픽셀은 각각 IGZO 반도체층을 채널 형성 영역으로 포함하는 두 개의 n-채널 트랜지스터를 포함한다.

[0188] 픽셀(6400)은 스위칭 트랜지스터(6401), 구동 트랜지스터(6402), 발광 소자(6404) 및 캐패시터(6403)을 포함한다. 스위칭 트랜지스터(6401)의 게이트는 스캔 라인(6406)에 접속되고, 스위칭 트랜지스터(6401)의 제1 전극(소스 전극 및 드레인 전극 중 하나)은 신호 라인(6405)에 접속되며, 스위칭 트랜지스터(6401)의 제2 전극(소스 전극 및 드레인 전극 중 다른 하나)은 구동 트랜지스터(6402)의 게이트에 접속된다. 구동 트랜지스터(6402)의 게이트는 캐패시터(6403)를 통해 전력 공급 라인(6407)에 접속되고, 구동 트랜지스터(6402)의 제1 전극은 전력 공급 라인(6407)에 접속되며, 구동 트랜지스터(6402)의 제2 전극은 발광 소자(6404)의 제1 전극(픽셀 전극)에 접속된다. 발광 소자(6404)의 제2 전극은 공통 전극(6408)에 해당한다.

[0189] 발광 소자(6404)의 제2 전극(공통 전극(6408))은 낮은 전력 공급 전위로 설정된다. 낮은 전력 공급 전위는 전력 공급 라인(6407)에 설정된 높은 전력 공급 전위를 참조하여, 낮은 전력 공급 전위 < 높은 전력 공급 전위를 만족하는 전위임을 알아야 한다. 예를 들어, 낮은 전력 공급 전위로서, GND, OV 등이 채용될 수 있다. 높은 전력 공급 전위 및 낮은 전력 공급 전위 사이의 전위차가 발광 소자(6404)에 인가되고, 전류가 발광 소자(6404)에 공급되어, 발광 소자(6404)가 발광된다. 여기서, 발광 소자(6404)가 발광되게 만들기 위해, 각각의 전위는 높은 전력 공급 전위 및 낮은 전력 공급 전위 사이의 전위차가 순방향 문턱 전압(forward threshold voltage) 이상이 되도록 설정된다.

[0190] 구동 트랜지스터(6402)의 게이트 캐패시턴스는 캐패시터(6403)에 대한 대체물로 사용될 수 있어, 캐패시터(6403)는 생략될 수 있음을 알아야 한다. 구동 트랜지스터(6402)의 게이트 캐패시턴스는 채널 영역과 게이트 전극 사이에 형성될 수 있다.

[0191] 전압 입력 전압 구동 방식(voltage-input voltage driving method)의 경우, 구동 트랜지스터(6402)가 충분히 턴 온되거나 턴 오프된 상태 중 어느 하나의 상태에 있도록 비디오 신호가 구동 트랜지스터(6402)의 게이트에 입력된다. 즉, 구동 트랜지스터(6402)는 선형 영역에서 동작한다. 구동 트랜지스터(6402)가 선형 영역에서 동작하므로, 전력 공급 라인(6407)의 전압보다 높은 전압이 구동 트랜지스터(6402)의 게이트에 인가된다. (전력 공급 라인의 전압 + 구동 트랜지스터(6402)의  $V_{th}$ ) 이상의 전압이 신호 라인(6405)에 인가됨을 알아야 한다.

[0192] 디지털 타임 그레이스케일 구동 대신에 아날로그 그레이스케일 구동을 수행하는 경우에는, 신호를 변경하는 것에 의해 도 18에서와 동일한 픽셀 구조가 사용될 수 있다.

[0193] 아날로그 그레이스케일 구동을 수행하는 경우에는, (발광 소자(6404)의 순방향 전압 + 구동 트랜지스터(6402))의  $V_{th}$  이상의 전압이 구동 트랜지스터(6402)의 게이트에 인가된다. 발광 소자(6404)의 순방향 전압은 원하는 광도가 얻어지는 전압을 나타내며, 적어도 순방향 문턱 전압을 포함한다. 발광 소자(6404)에 전류가 공급될 수 있도록 구동 트랜지스터(6402)가 포화 영역(saturation region)에서 동작하게 하는 비디오 신호가 입력된다. 구동 트랜지스터(6402)로 하여금 포화 영역에서 동작하게 하기 위해, 전력 공급 라인(6407)의 전위는 구동 트랜지스터(6402)의 게이트 전위보다 더 높게 설정된다. 아날로그 비디오 신호가 사용되는 때는, 비디오 신호에 따라 발광 소자(6404)에 전류를 공급하여 아날로그 그레이스케일 구동을 수행하는 것이 가능하다.

[0194] 도 18에 도시된 픽셀 구조는 이에 제한되지 않는다는 것을 알아야 한다. 예를 들어, 스위치, 저항, 캐패시터, 트랜지스터, 로직 회로 등이 도 18에 도시된 픽셀에 추가될 수 있다.

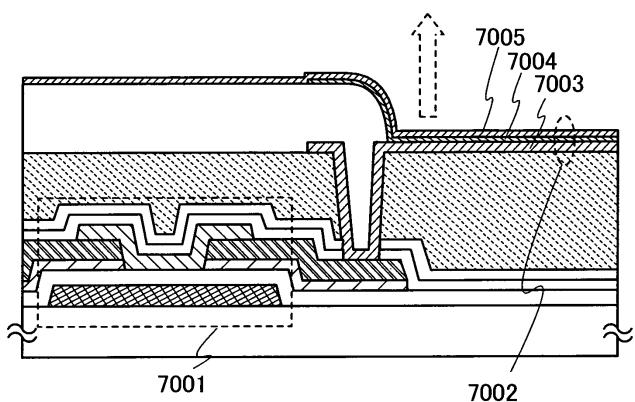

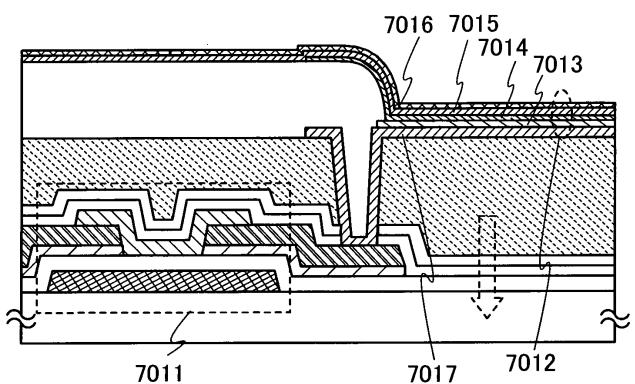

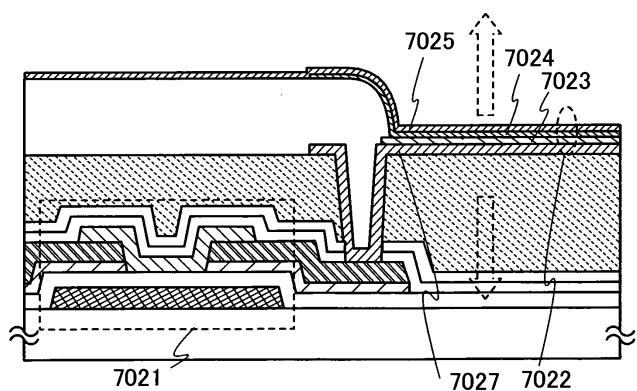

[0195] 그 다음, 발광 소자의 구조는 도 19a 내지 19c를 참조하여 기술될 것이다. 픽셀의 단면 구조는 그 예로 n-채널 구동 TFT를 가지고 기술될 것이다. 도 19a 내지 19c에 도시된 반도체 장치에 사용되는 구동 TFT(7001, 7011 및 7021)는, 실시예 1에 기술된 박막 트랜지스터와 유사한 방식으로 생산될 수 있으며, 각각 산소 라디칼 처리를 받는 게이트 절연층, 소스 전극층, 드레인 전극층, 게이트 절연층, 소스 전극층 및 드레인 전극층 위에 산소 파이 산화물 반도체층 및 소스 영역 및 드레인 영역으로서 산소 부족 산화물 반도체층을 포함하는 고신뢰도의 박막 트랜지스터이다.

[0196] 발광 소자로부터의 발광을 추출하기 위하여, 애노드(anode) 및 캐소드(cathode) 중 적어도 하나는 광을 투과시

킬 것이 요구된다. 박막 트랜지스터 및 발광 소자는 기판 위에 형성된다. 발광 소자는 발광이 기판 반대쪽의 표면을 통해 발광이 추출되는 전면 발광 구조(top emission structure), 기판쪽의 표면을 통해 발광이 추출되는 배면 발광 구조(bottom emission structure) 또는 기판의 반대쪽 표면과 기판쪽 표면을 통해 발광이 추출되는 이중 발광 구조(dual emission structure)를 가질 수 있다. 픽셀 구조는 이러한 발광 구조 중 임의의 하나를 가지는 발광 소자에 적용될 수 있다.

[0197] 전면 발광 구조를 가지는 발광 소자는 도 19a를 참조하여 기술될 것이다.

도 19a는 구동 TFT(7001)가 n-채널 TFT이고, 발광 소자(7002)로부터 공통 전극(애노드{7005}) 쪽으로 발광되는 경우의 픽셀의 단면도이다. 도 19a에서, 발광 소자(7002)의 픽셀 전극(캐소드{7003})은 구동 TFT(7001)에 전기적으로 접속되고, 발광층(7004) 및 애노드(7005)는 이 순서대로 캐소드(7003) 위에 적층된다. 캐소드(7003)는, 전도성 재료가 낮은 일 함수(work function)을 가지고 광을 반사하기만 하면, 다양한 전도성 재료를 사용하여 형성될 수 있다. 예를 들어, Ca, Al, CaF, MgAg, AlLi 등을 사용하는 것이 바람직하다. 발광층(7004)은 단일 층 또는 복수의 적층을 사용하여 형성될 수 있다. 발광층(7004)이 복수의 층을 사용하여 형성되는 경우, 발광층(7004)은 전자 주입층(electron-injecting layer), 전자 수송층(electron transporting layer), 발광층, 정공 수송층(hole-transporting layer) 및 정공 주입층(hole-injecting layer)을 캐소드(7003) 위에 이 순서로 적층하는 것에 의해 형성된다. 이 층들을 모두 형성하는 것이 필수적인 것은 아니다. 애노드(7005)는 텅스텐 산화물을 포함하는 인듐 산화물, 텅스텐 산화물을 포함하는 인듐 아연 산화물, 티타늄 산화물을 포함하는 인듐 산화물, 티타늄 산화물을 포함하는 인듐 틴 산화물, 인듐 틴 산화물(이하 ITO로 지칭됨), 인듐 아연 산화물 또는 산화 실리콘이 추가된 인듐 틴 산화물의 막과 같은 광 전달 전도성막을 사용하여 형성된다.

[0199] 발광 소자(7002)는 캐소드(7003)와 애노드(7005)가 발광층(7004)을 샌드위치형태로 끼우는 영역에 해당한다. 도 19a에 도시된 픽셀의 경우에, 화살표에 의해 나타난 바와 같이 발광 소자(7002)로부터 애노드(7005) 쪽으로 발광한다.

[0200] 그 다음, 배면 발광 구조를 가지는 발광 소자는 도 19b를 참조하여 기술될 것이다. 도 19b는 구동 TFT(7011)가 n-채널 트랜지스터이고 발광 소자(7012)로부터 픽셀 전극(캐소드{7013}) 쪽으로 발광되는 경우의 픽셀의 단면도이다. 도 19b에서, 발광 소자(7012)의 캐소드(7013)는 구동 TFT(7011)에 전기적으로 접속된 광 전달 전도성막(7017) 위에 형성되고, 발광층(7014)과 공통 전극(애노드{7015})은 이 순서로 캐소드(7013) 위에 적층된다. 애노드(7015)가 광 전달 속성을 가지고 있으면 광을 반사 또는 차단하기 위한 광차단 막(7016)은 애노드(7015)를 덮기 위하여 사용될 수 있다. 캐소드(7013)에는, 낮은 일 함수를 가지는 전도성 재료인 한 도 19a의 경우와 같이 다양한 재료가 사용될 수 있다. 캐소드(7013)는 광을 전달할 수 있는 두께(바람직하게는 약 5nm 내지 30nm)를 가지도록 형성된다. 예를 들어, 20nm의 두께를 갖는 알루미늄 막은 캐소드(7013)로 사용될 수 있다. 도 19a의 경우와 유사하게, 발광층(7014)은 단일층 또는 복수의 적층 중 어느 하나를 사용하여 형성될 수 있다. 애노드(7015)는 광을 전달할 필요는 없지만, 도 19a의 경우와 같이 광 전달 전도성 재료로 형성될 수 있다. 광차단막(7016)으로, 예를 들어 광을 반사하는 금속 등이 사용될 수 있지만, 금속막으로 제한되지는 않는다. 예를 들어, 검은색 안료가 추가된 수지 등이 사용될 수도 있다.

[0201] 발광 소자(7012)는 캐소드(7013)와 애노드(7015)가 발광층(7014)을 샌드위치 형태로 끼우는 영역에 해당한다. 도 19b에 도시된 픽셀의 경우, 화살표에 의해 나타난 바와 같이, 발광 소자(7012)로부터 캐소드(7013) 쪽으로 발광된다.

[0202] 그 다음, 이중 발광 구조를 가지는 발광 소자는 도 19c를 참조하여 기술될 것이다. 도 19c에서, 발광 소자(7022)의 픽셀 전극(캐소드{7023})은 구동 TFT(7021)에 전기적으로 접속된 광 전달 전도성막(7027) 위에 형성되고 발광층(7024)과 공통 전극(애노드{7025})은 이 순서로 캐소드(7023) 위에 적층된다. 도 19a의 경우, 캐소드(7023)는 전도성 물질이 낮은 일 함수를 가지는 한 다양한 전도성 재료를 사용하여 형성될 수 있다. 캐소드(7023)는 광을 전달할 수 있는 두께를 가지도록 형성된다. 예를 들어, 20nm의 두께를 가지는 Al의 막이 캐소드(7023)로 사용될 수 있다. 도 19a에서와 같이, 발광층(7024)은 단일층 또는 복수의 적층을 사용하여 형성될 수 있다. 애노드(7025)는 도 19a의 경우와 같은 광 전달 전도성 재료를 사용하여 형성될 수 있다.

[0203] 발광 소자(7022)는 캐소드(7023), 발광층(7024) 및 애노드(7025)가 서로 중첩되는 영역에 해당한다. 도 19c에 도시된 픽셀의 경우에는, 화살표에 의해 나타난 바와 같이, 발광 소자(7022)로부터 애노드(7025) 쪽 및 캐소드(7023) 쪽 양 쪽 모두로 발광된다.

[0204] 여기서는 비록 유기 EL 소자가 발광 소자로 기술되었지만, 무기 EL 소자가 발광 소자로 제공될 수도 있다.

- [0205] 이 실시예에서는, 발광 소자의 구동을 제어하는 박막 트랜지스터(구동 TFT)가 발광 소자에 전기적으로 접속되는 예가 기술되지만, 전류 제어를 위한 TFT가 구동 TFT와 발광 소자 사이에 접속되는 구조가 채용될 수 있다.

- [0206] 이 실시예에서 기술된 반도체 장치는 도 19a 내지 19c에 도시된 구조에 제한되지 않으며, 본 명세서에서 개시된 본 발명에 따른 기술의 사상에 기초하여 다양한 방법으로 변형될 수 있다.

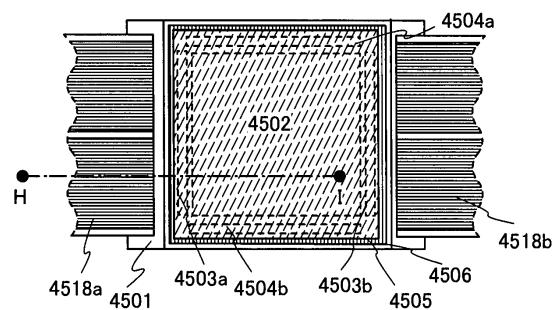

- [0207] 그 다음, 본 발명의 반도체 장치의 한 실시예인 발광 디스플레이 패널(발광 패널로도 지칭됨)의 외형 및 단면은 도 20a 내지 20b를 참조하여 기술될 것이다. 도 20a는 산소 라디칼 처리를 받는 게이트 절연층, 소스 영역 및 드레인 영역 위에 소스 전극층 및 드레인 전극층, 그리고 게이트 절연층, 소스 전극층 및 드레인 전극층 위에 IGZO 반도체층을 포함하는 좋은 전기적 특성을 갖는 박막 트랜지스터 및 발광 소자가 제1 기판과 제2 기판 사이에 밀봉제로 밀봉된 패널의 평면도이다. 도 20b는 도 20a의 라인 H-I를 따라 취한 단면도이다.

- [0208] 밀봉제(4505)는 제1 기판(4501) 위에 제공되는 픽셀부(4502), 신호 라인 구동 회로(4503a 및 4503b) 및 스캔 라인 구동 회로(4504a 및 4504b)를 둘러싸도록 제공된다. 또한, 제2 기판(4506)은 픽셀부(4502), 신호 라인 구동 회로(4503a 및 4503b) 및 스캔 라인 구동 회로(4504a 및 4504b) 위에 제공된다. 따라서, 픽셀부(4502), 신호 라인 구동 회로(4503a 및 4503b) 및 스캔 라인 구동 회로(4504a 및 4504b)는 충진제(4507)와 함께 제1 기판(4501), 밀봉제(4505) 및 제2 기판(4506)에 의해 밀봉된다. 공기에 노출을 방지하기 위하여 보호막(첨부막 {attachment film}, 자외선 경화성 수지막 등) 또는 덮개 재료(cover material)를 사용하여 패키징(밀봉)을 더 수행하는 것이 바람직하다.

- [0209] 제1 기판(4501) 위에 형성된 픽셀부(4502), 신호 라인 구동 회로(4503a 및 4503b) 및 스캔 라인 구동 회로(4504a 및 4504b)는 각각 복수의 박막 트랜지스터를 포함하고, 픽셀부(4502)에 포함된 박막 트랜지스터(4510) 및 신호 라인 구동 회로(4503a)에 포함된 박막 트랜지스터(4509)는 도 20b에서 예로서 도시된다.

- [0210] 박막 트랜지스터(4509 및 4510)의 각각은 산소 라디칼 처리를 받는 게이트 절연층, 소스 영역 및 드레인 영역 위에 소스 전극층 및 드레인 전극층, 그리고 게이트 절연층, 소스 전극층 및 드레인 전극층 위에 IGZO 반도체층을 사용하는 박막 트랜지스터에 해당하고, 높은 전기적 특성을 갖는 박막 트랜지스터 및 실시예 1에서 기술된 박막 트랜지스터는 그곳에 적용될 수 있다. 이 실시예에서, 박막 트랜지스터(4509 및 4510)는 n-채널 박막 트랜지스터이다.

- [0211] 또한, 참조 부호(4511)는 발광 소자를 표시한다. 발광 소자(4511)에 포함된 픽셀 전극인 제1 전극층(4517)은 박막 트랜지스터(4510)의 소스 전극층 또는 드레인 전극층에 전기적으로 접속된다. 발광 소자(4511)의 구조는 이 실시예에서 기술된 구조에 제한되지 않음을 알아야 한다. 발광 소자(4511)의 구조에서, 제1 전극층(4517), 전계 발광층(4512) 및 제2 전극층(4513)이 적층되지만, 이 실시예에서 기술된 구조로 제한되지 않는다. 발광 소자(4511) 등으로부터 광이 추출되는 방향에 따라 적절히 변경될 수 있다.

- [0212] 파티션 벽(partition wall; 4520)은 유기 수지막, 무기 절연막 또는 유기 폴리실록산(polysiloxane)을 사용하여 형성된다. 파티션 벽(4520)은 감광성 재료를 사용하여 형성하고 제1 전극층(4517) 위에 개구를 형성하여 개구의 측벽(sidewall)이 연속적인 곡선을 갖는 경사진 표면으로 형성되도록 하는 것이 특히 바람직하다.

- [0213] 전계 발광층(4512)은 단일층 또는 복수의 적층으로 형성될 수 있다.

- [0214] 보호막은 발광 소자(4511)로의 산소, 수소, 수분, 이산화 탄소 등의 진입을 방지하기 위해 제2 전극층(4513) 및 파티션 벽(4520) 위에 형성될 수 있다. 보호막으로, 질화 실리콘 막, 질화 산화 실리콘 막, DLC 막 등이 형성될 수 있다.

- [0215] 또한, 다양한 신호 및 전위가 신호 라인 구동 회로(4503a 및 4503b), 스캔 라인 구동 회로(4504a 및 4504b), 또는 FPCs(4518a 및 4518b)로부터의 픽셀부(4502)에 공급된다.

- [0216] 이 실시예에서, 접속 터미널 전극(4515)은 제1 전극층(4517)과 동일한 전도성막으로부터 형성되고 터미널 전극(4516)은 박막 트랜지스터(4509 및 4510)에 포함되는 소스 전극층 및 드레인 전극층과 동일한 전도성막을 사용하여 형성된다.

- [0217] 접속 터미널 전극(4515)은 이방성 전도성막(4519)을 통해 FPC(4518a)에 포함된 터미널에 전기적으로 접속된다.

- [0218] 발광 소자(4511)로부터 광이 추출되는 방향에 위치한 제2 기판(4506)은 광 전달 속성을 가지고 있어야 한다. 이 경우, 유리판, 플라스틱판, 폴리에스테르 막 또는 아크릴 막과 같은 광 전달 재료가 사용된다.

- [0219] 충진제(4507)로, 질소 또는 아르곤과 같은 불활성 기체와 더불어 자외선 경화성 수지 또는 열경화성 수지가 사

용될 수 있다. 예를 들어, PVC(polyvinyl chloride; 폴리비닐 클로라이드), 아크릴, 폴리이미드, 에폭시 수지, 실리콘 수지, PVB(polyvinyl butyral; 폴리비닐 부티랄) 또는 EVA(에틸렌 비닐 아세테이트)가 사용될 수 있다. 이 실시예에서, 충진제(4507)로 질소가 사용된다.

[0220] 또한, 필요하다면, 편광판, 원형 편광판(타원형 편광판을 포함함), 위상지연판(1/4 파장판 또는 1/2 파장판) 또는 컬러 필터(color filter)와 같은 광학 막(optical film)이 빛광 소자의 빛광면 위에 적절히 제공될 수 있다. 또한, 편광판 또는 원형 편광판에는 반사 방지막(anti-reflection film)이 제공될 수 있다. 예를 들어, 눈부심(glare)을 감소시키기 위하여 표면 위의 돌출부(projection)와 함몰부(depression)에 의해 반사된 광이 확산될 수 있는 눈부심 방지 처리(anti-glare treatment)가 수행될 수 있다.

[0221] 신호 라인 구동 회로(4503a 및 4503b) 및 스캔 라인 구동 회로(4504a 및 4504b)는 단결정 반도체 막 또는 다결정 반도체 막을 사용하여 따로 준비된 기판 위에 형성된 구동 회로로서 제공될 수 있다. 또한, 신호 라인 구동 회로 또는 그 부분만, 또는 스캔 라인 구동 회로 또는 그 부분만 따로 형성되고 탑재될 수 있다. 이 실시예는 도 20a 및 20b에 도시된 구조로 제한되지 않는다.

[0222] 이 공정을 통해, 고신뢰도의 빛광 디스플레이 장치(디스플레이 패널)가 반도체 장치로서 생산될 수 있다.

[0223] 이 실시예는 다른 실시예에서 개시된 구조와 적절히 조합될 수 있다.

[0224] (실시예 6)

[0225] 본 발명의 실시예의 반도체 장치는 전자 종이에 적용될 수 있다. 전자 종이는 데이터를 디스플레이 할 수 있는 한 다양한 분야의 전자 제품에 사용될 수 있다. 예를 들어, 전자 종이는 전자 책(e-book) 판독기, 포스터, 기차와 같은 차량에서의 광고, 신용카드와 같은 다양한 카드의 디스플레이 등에 적용될 수 있다. 전자 제품의 예는 도 21a 및 21b 및 도 22에 도시된다.

[0226] 도 21a는 전자 종이를 사용하여 형성된 포스터(2631)를 도시한다. 광고 매체가 인쇄된 종이인 경우, 광고는 인력(manpower)에 의해 교체되지만, 본 발명의 실시예인 전자 종이를 사용하는 것에 의해, 단시간에 광고 디스플레이가 변경될 수 있다. 또한, 이미지가 왜곡되지 않고 안정적으로 디스플레이된다. 포스터는 무선으로 데이터를 송신하고 수신할 수 있음을 알아야 한다.

[0227] 도 21b는 기차와 같은 차량에서의 광고(2632)를 도시한다. 광고 매체가 인쇄된 종이인 경우, 광고는 인력에 의해 교체되지만, 본 발명의 실시예인 전자 종이를 사용하는 것에 의해, 많은 인력 없이 단시간에 광고 디스플레이가 변경될 수 있다. 또한, 이미지가 왜곡되지 않고 안정적으로 디스플레이된다. 포스터는 무선으로 데이터를 송신하고 수신할 수 있음을 알아야 한다.

[0228] 도 22는 전자 책 판독기(electronic book reader; 2700)의 예를 도시한다. 예를 들어, 전자 책 판독기(2700)는 두개의 틀(housing), 틀(2701) 및 틀(2703)을 포함한다. 틀(2701) 및 틀(2703)은 힌지(2711)와 결합되어 전자 책 판독기(2700)는 힌지(2711)를 축으로 하여 열고 닫을 수 있다. 이와 같은 구조로, 전자 책 판독기(2700)는 종이 책과 비슷하게 동작될 수 있다.

[0229] 디스플레이부(2705)와 디스플레이부(2707)는 각각 틀(2701)과 틀(2703) 안에 들어있다(incorporated). 디스플레이부(2705)와 디스플레이부(2707)는 하나의 이미지 또는 상이한 이미지를 디스플레이할 수 있다. 디스플레이부(2705)와 디스플레이부(2707)가 서로 다른 이미지를 디스플레이하는 경우에는, 예를 들어 디스플레이부의 오른쪽(도 22의 디스플레이부{2705})은 텍스트를 디스플레이할 수 있고, 디스플레이의 왼쪽(도 22의 디스플레이부{2707})은 그림을 디스플레이할 수 있다.

[0230] 도 22는 동작부 등이 제공된 틀(2701)의 예를 도시한다. 예를 들어, 틀(2701)에는 전원 스위치(2721), 동작키(2723), 스피커(2725) 등이 제공된다. 동작키(2723)로 페이지를 넘길 수 있다. 키보드, 포인팅 장치 등은 디스플레이부가 제공되는 틀의 표면에 제공될 수 있음을 알아야 한다. 또한, 외부 접속 터미널(이어폰 터미널, USB 터미널, AC 어댑터 및 USB 케이블과 같은 다양한 케이블에 접속될 수 있는 터미널), 기록 매체 삽입부 등이 틀의 측면 또는 뒷면에 제공될 수 있다. 또한, 전자 책 판독기(2700)는 전자 사전의 기능을 가질 수 있다.

[0231] 전자 책 판독기(2700)는 데이터를 무선으로 송신하고 수신할 수 있다. 원하는 책 데이터 등을 전자 책 서버로 부터 무선으로 구입하고 다운로드하는 구성이 채용될 수 있다.

[0232] (실시예 7)

[0233] 본 발명의 실시예에 따른 반도체 장치는 다양한 전자 제품(오락 머신을 포함함)에 적용될 수 있다. 전자 제품

의 예는 텔레비전 세트(텔레비전 또는 텔레비전 수신기로도 지칭됨), 컴퓨터 등의 모니터, 디지털 카메라 또는 디지털 비디오 카메라와 같은 카메라, 휴대폰 핸드세트(휴대폰 또는 휴대폰 장치로도 지칭됨), 휴대용 게임 콘솔, 휴대용 정보 터미널, 오디오 재생 장치, 패친코 머신(pachinko machine)과 같은 큰 사이즈의 게임 머신 등이 있다.

[0234] 도 23a는 텔레비전 세트(9600)의 예를 도시한다. 텔레비전 세트(9600)에서, 디스플레이부(9603)는 틀(9601)에 들어있다. 디스플레이부(9603)는 이미지를 디스플레이할 수 있다. 또한, 여기서는 틀(9601)이 스탠드(9605)에 의해 지지된다.

[0235] 텔레비전 세트(9600)는 틀(9601)의 동작 스위치 또는 별개의 원격 제어기(9610)에 의해 동작될 수 있다. 채널과 볼륨은 원격 제어기(9610)의 동작키(9609)에 의해 제어될 수 있어, 디스플레이부(9603) 상에 디스플레이된 이미지가 제어될 수 있다. 또한 원격 제어기(9610)에는 원격 제어기(9610)로부터 출력된 데이터를 디스플레이하기 위한 디스플레이부(9607)가 제공될 수 있다.

[0236] 텔레비전 세트(9600)에는 수신기, 모뎀 등이 제공된다. 수신기로 일반 텔레비전 방송이 수신될 수 있다. 또한, 텔레비전 세트(9600)가 모뎀을 통한 유선 또는 무선 접속에 의해 통신 네트워크에 접속되면, 한방향(송신기로부터 수신기로) 또는 양방향(송신기와 수신기 간에 또는 수신기들 간에) 데이터 통신이 수행될 수 있다.

[0237] 도 23b는 디지털 사진 프레임(9700)의 예를 도시한다. 예를 들어, 디지털 사진 프레임(9700)에서는, 디스플레이부(9703)가 틀(9701)에 들어있다. 디스플레이부(9703)는 다양한 이미지를 디스플레이할 수 있다. 예를 들어, 디스플레이부(9703)는 일반 사진 프레임과 같이 기능하기 위하여 디지털 카메라 등에 의한 이미지 촬영의 데이터를 디스플레이할 수 있다.

[0238] 디지털 사진 프레임(9700)에는 동작부, 외부 접속부(USB 터미널, USB 케이블 등과 같은 다양한 케이블에 접속될 수 있는 터미널), 기록 매체 삽입부 등이 제공된다. 그것들은 디스플레이부가 제공된 표면 위에 제공될 수 있지만, 디지털 사진 프레임(9700)의 디자인을 위하여 옆면이나 뒷면 위에 제공되는 것이 바람직하다. 예를 들어, 디지털 카메라에 의한 이미지 촬영을 저장하는 메모리가 디지털 사진 프레임의 기록 매체 삽입부에 삽입되어, 이미지 데이터가 전송되고 그 후 디스플레이부(9703) 상에 디스플레이될 수 있다.

[0239] 디지털 사진 프레임(9700)은 무선으로 데이터를 송신하고 수신할 수 있다. 원하는 이미지 데이터가 디스플레이되기 위해 무선으로 전송되는 구성이 채용될 수 있다.

[0240] 도 24a는 휴대용 게임 머신이고, 휴대용 게임 머신이 열리고 접힐 수 있도록 이음부(9893)로 접속되는 틀(9881)과 틀(9891)의 두개의 틀에 의해 구성된다. 디스플레이부(9882)는 틀(9881)에 들어있고, 디스플레이부(9883)는 틀(9891)에 들어있다. 또한, 도 24a에 도시된 휴대용 게임 머신에는 스피커부(9884), 기록 매체 삽입부(9886), LED 램프(9890), 입력 수단(동작키{9885}, 접속 터미널{9887}, 센서{9888; 힘, 변위, 포지션, 속력, 가속, 각속도, 회전수, 거리, 광, 액체, 자기, 온도, 화학 성분, 음성, 타임, 강도, 전기장, 전류, 전압, 전력, 방사선, 플로우 비율, 습도, 구배, 진동, 냄새 또는 전위선을 측정하는 기능을 가짐}, 및 마이크{9889}) 등이 제공된다. 당연한 것이지만, 휴대용 게임 머신의 구조는 전술된 것에 제한되지 않는다. 휴대용 게임 머신은 적어도 본 발명의 실시예에 따른 반도체 장치가 제공되는 한, 추가적인 악세사리 장비가 적절히 제공되는 구성을 가질 수 있다. 도 24a에 도시된 휴대용 게임 머신은 프로그램 또는 기록 매체에 저장된 데이터를 디스플레이부 상에 디스플레이하기 위하여 판독하는 기능을 가지고, 무선 통신에 의해 또 다른 휴대용 게임 머신과 정보를 공유하는 기능을 가진다. 도 24a에 도시된 휴대용 게임 머신의 기능은 전술된 것에 제한되지 않으며, 휴대용 게임 머신은 다양한 기능을 가질 수 있다.

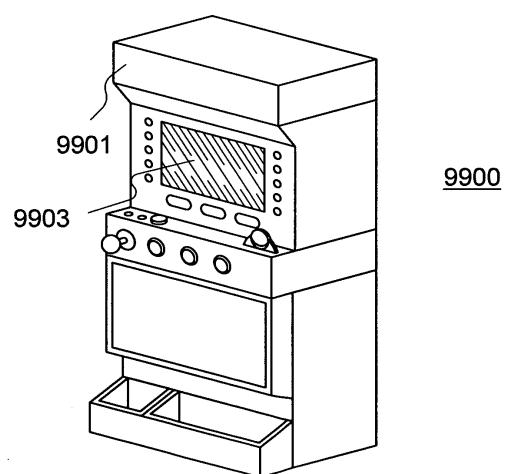

[0241] 도 24b는 큰 사이즈의 오락 머신인 슬롯 머신(9900)의 예를 도시한다. 슬롯 머신(9900)에서, 디스플레이부(9903)는 틀(9901)에 들어있다. 또한, 슬롯 머신(9900)에는 시작 레버 및 정지 스위치와 같은 동작 수단, 동전 슬롯, 스피커 등이 제공된다. 당연한 것이지만, 슬롯 머신(9900)의 구조는 전술된 구조에 제한되지 않는다. 슬롯 머신은 적어도 본 발명의 실시예에 따른 반도체 장치가 제공되는 한 추가적인 악세사리 장비가 적절히 제공되는 구조를 가질 수 있다.

[0242] 도 25는 휴대폰 핸드세트(1000)의 예를 도시한다. 휴대폰 핸드세트(1000)에는 틀(1001)에 들어있는 디스플레이부(1002), 동작 버튼(1003), 외부 접속 포트(1004), 스피커(1005), 마이크(1006) 등이 제공된다.

[0243] 도 25에 도시된 디스플레이부(1002)가 손가락 등으로 터치되었을 때, 데이터는 휴대폰 핸드세트(1000)로 입력될 수 있다. 또한, 전화를 거는 것과 메일을 작성하는 것과 같은 동작이 손가락 등으로 디스플레이부(1002)를 터

치하는 것에 의해 수행될 수 있다.

[0244] 디스플레이부(1002)에는 주로 세 가지 모드가 있다. 제1 모드는 주로 이미지를 디스플레이하기 위한 디스플레이 모드이다. 제2 모드는 텍스트와 같은 데이터를 주로 입력하기 위한 입력 모드이다. 제3 모드는 디스플레이 모드와 입력 모드가 조합된 디스플레이 및 입력 모드이다.

[0245] 예를 들어, 전화를 걸거나 메일을 작성하는 경우, 주로 텍스트를 입력하기 위한 텍스트 입력 모드가 화면에 디스플레이된 텍스트가 입력될 수 있도록 디스플레이부(1002)에 대해 선택된다. 이 경우에는, 디스플레이부(1002)의 화면의 거의 모든 면 위에 키보드 또는 숫자 버튼이 디스플레이되는 것이 바람직하다.

[0246] 자이로스콥 또는 가속 센서와 같이 경사를 감지하기 위한 센서를 포함하는 감지 장치가 휴대폰 핸드셋(1000)에 제공되면, 디스플레이부(1002)의 화면 내의 디스플레이는 휴대폰(1000)의 방향(휴대폰{1000})이 똑바로 서있는지 또는 옆면으로 누워있는지 여부)을 판정하는 것에 의해 자동으로 전환될 수 있다.

[0247] 화면 모드는 디스플레이부(1002)를 터치하는 것 또는 틀(1001)의 동작 버튼(1003)을 동작하는 것에 의해 전환될 수 있다. 이와 달리, 화면 모드는 디스플레이부(1002) 상에 디스플레이된 이미지의 종류에 따라 전환될 수 있다. 예를 들어, 디스플레이부 상에 디스플레이된 이미지의 신호가 동영상 데이터 중 하나이면, 화면 모드는 디스플레이 모드로 전환된다. 신호가 텍스트 데이터 중 하나이면, 화면 모드는 입력 모드로 전환된다.

[0248] 또한, 입력 모드에서, 디스플레이부(1002) 내의 광센서에 의해 신호가 감지되는 동안 디스플레이부(1002)를 터치하는 것에 의한 입력이 특정 시간 동안 수행되지 않으면, 화면 모드는 입력 모드로부터 디스플레이 모드로 전환되도록 제어될 수 있다.

[0249] 디스플레이부(1002)는 이미지 센서로 기능할 수 있다. 예를 들어, 장문(palm print), 지문 등의 이미지가 손바닥 또는 손가락으로 디스플레이부(1002)를 터치하는 것에 의해 채취되어, 개인 인증이 수행될 수 있다. 또한, 디스플레이부에 대해 근적외선이 방출하는 센서 광원 또는 백라이트를 제공하는 것에 의해, 손가락 정맥, 손바닥 정맥 등이 채취될 수 있다.

[0250] 본 명세서는 2008년 9월 12일자로 일본 특허청에 출원된 일련 번호 2008-235111의 일본 특허 출원에 기초한 것이고, 이 일본 특허 출원의 전체 내용은 본 명세서에서 참조한다.

## 부호의 설명

[0251] 100: 기판, 101: 게이트 전극, 102: 게이트 절연층, 103: IGZO 반도체층, 105a: 소스 전극층, 105b: 드레인 전극층, 106a: 소스 영역, 106b: 드레인 영역, 107: 보호 절연막, 108: 캐페시터 배선, 110: 픽셀 전극, 121: 제1 터미널, 122: 제2 터미널, 125: 컨택트 홀, 126: 컨택트 홀, 127: 컨택트 홀, 128: 투명 전도성 막, 129: 투명 전도성 막, 130: 제1 IGZO 막, 150: 제2 터미널, 151: 제1 터미널, 152: 게이트 절연층, 153: 접속 전극, 154: 보호 절연막, 155: 투명 전도성 막, 156: 전극, 157: 제1 IGZO 막, 158: 제1 IGZO 막, 170: 박막 트랜지스터, 581: 박막 트랜지스터, 585: 절연층, 587: 전극층, 588: 전극층, 589: 구형 입자, 590a: 검은색 영역, 590b: 백색 영역, 594: 공동(cavity), 595: 충진체, 1000: 휴대폰 핸드셋, 1001: 틀, 1002: 디스플레이부, 1003: 동작 버튼, 1004: 외부 접속 포트, 1005: 스피커, 1006: 마이크, 2600: TFT 기판, 2601: 카운터 기판(counter substrate), 2602: 밀봉제, 2603: 픽셀부, 2604: 디스플레이 장치, 2605: 채색층(coloring layer), 2606: 편광판, 2607: 편광판, 2608: 배선 회로부, 2609: 연성 배선판(flexible wiring board), 2610: 냉음극관, 2611: 반사판, 2612: 회로 기판, 2613: 확산판(diffusion plate), 2631: 포스터, 2632: 차량에서의 광고, 2700: 전자 책 판독기, 2701: 틀, 2703: 틀, 2705: 디스플레이부, 2707: 디스플레이부, 2711: 힌지(hinge), 2721: 전원 스위치, 2723: 동작키, 2725: 스피커, 4001: 기판, 4002: 픽셀부, 4003: 신호 라인 구동 회로, 400: 스캐닝 라인 구동 회로, 4005: 밀봉제, 4006: 기판, 4008: 액정층, 4010: 박막 트랜지스터, 4011: 박막 트랜지스터, 4013: 액정 장치, 4015: 접속 터미널 전극, 4016: 터미널 전극, 4018: FPC, 4019: 이방성 전도성 막, 4020: 절연층, 4020: 절연층, 4021: 절연층, 4030: 픽셀 전극층, 4031: 카운터 전극층, 4032: 절연층, 4033: 절연층, 4501: 기판, 4502: 픽셀부, 4503a: 신호 라인 구동 회로, 4503b: 신호 라인 구동 회로, 4504a: 스캔 라인 구동 회로, 4504b: 스캔 라인 구동 회로, 4505: 밀봉제, 4506: 기판, 4507: 충진체, 4509: 박막 트랜지스터, 4510: 박막 트랜지스터, 4511: 발광 소자, 4512: 전계 발광층, 4513: 전극층, 4515: 접속 터미널 전극, 4516: 터미널 전극, 4517 전극층, 4518a: FPC, 4518b: FPC, 4519: 이방성 전도성 막, 4520: 파티션 벽, 5300: 기판, 5301: 픽셀부, 5302: 스캔 라인 구동 회로, 5303: 신호 라인 구동 회로, 5400: 기판, 5401: 픽셀부, 5402: 스캔 라인 구동 회로, 5403: 신호 라인 구동 회로, 5404: 스캔 라인 구동 회로, 5501: 제1 배선, 5502: 제2 배선, 5503: 제3 배선, 5504: 제4 배선, 5505: 제5 배선, 5506: 제6 배선, 5543: 노드, 5544: 노드,

5571: 제1 박막 트랜지스터, 5572: 제2 박막 트랜지스터, 5573: 제3 박막 트랜지스터, 5574: 제4 박막 트랜지스터, 5575: 제5 박막 트랜지스터, 5576: 제6 박막 트랜지스터, 5577: 제7 박막 트랜지스터, 5578: 제8 박막 트랜지스터, 5601: 구동 IC, 5602: 스위치 그룹, 5603a: 제1 박막 트랜지스터, 5603b: 제2 박막 트랜지스터, 5603c: 제3 박막 트랜지스터, 5611: 제1 배선, 5612: 제2 배선, 5613: 제3 배선, 5621\_1 내지 5621\_M: 배선, 5701\_1 내지 5701\_n: 플립플롭(Flip-flop), 5701\_i: 플립플롭, 5703a: 제1 박막트랜지스터의 온-오프 타이밍, 5703b: 제2 박막트랜지스터의 온-오프 타이밍, 5703c: 제3 박막트랜지스터의 온-오프 타이밍, 5803a: 제1 박막트랜지스터의 온/오프의 타이밍, 5803b: 제2 박막트랜지스터의 온/오프의 타이밍, 5803c: 제3 박막트랜지스터의 온/오프의 타이밍, 5711: 제1 배선, 5712: 제2 배선, 5713: 제3 배선, 5714: 제4 배선, 5715: 제5 배선, 5716: 제6 배선, 5717: 제7 배선, 5721: 신호, 5821: 신호, 6400: 광셀, 6402: 구동 트랜지스터, 6403: 캐패시터, 6404: 발광 소자, 6405: 신호 라인, 6406: 스캔 라인, 6407: 전력 공급 라인, 6408: 공통 전극, 7001: TFT, 7002: 발광 소자, 7003: 캐소드, 7004: 발광층, 7005: 애노드, 7011: 구동 TFT, 7012: 발광 소자, 7013: 캐소드, 7014: 발광층, 7015: 애노드, 7016: 광 차단막, 7017

전도성 막, 7021: 구동 TFT, 7022: 발광 소자, 7023: 캐소드, 7024: 발광층, 7025: 애노드, 7027: 전도성 막, 9600: 텔레비전 세트, 9601: 틀, 9603: 디스플레이부, 9605: 스텐드, 9607: 디스플레이부, 9609: 동작키, 9700: 원격 제어 머신, 9701: 디지털 사진 프레임, 9610: 원격 제어기, 9703

디스플레이부, 9881: 틀, 9882: 디스플레이부, 9883: 디스플레이부, 9884

스피커부, 9885: 동작키, 9886: 기록 매체 삽입부, 9887 접속 터미널, 9888: 센서, 9889: 마이크, 9890: LED 램프, 9891: 틀, 9893: 이음부(joint), 9900: 슬롯 머신, 9901: 틀, 9903: 디스플레이부

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7a

도면7b

도면7c

도면7d

도면8

도면9

도면10a

도면10b

도면11

도면12

## 도면13

도면14

도면15

도면16a

도면16b

도면16c

도면17

도면18

도면19a

도면19b

도면19c

도면20a

도면20b

도면21a

도면21b

도면22

도면23a

도면23b

도면24a

도면24b

도면25