(12) 发明专利

(10) 授权公告号 CN 112993000 B

(45) 授权公告日 2024.08.09

(21) 申请号 202110190257.8

(74) 专利代理机构 北京德琦知识产权代理有限

(22) 申请日 2014.04.23

公司 11018

(65) 同一申请的已公布的文献号

专利代理人 张燕 朴圣洁

申请公布号 CN 112993000 A

(51) Int.CI.

(43) 申请公布日 2021.06.18

H10K 59/38 (2023.01)

(30) 优先权数据

H10K 59/122 (2023.01)

10-2013-0093599 2013.08.07 KR

H10K 59/123 (2023.01)

(62) 分案原申请数据

H10K 59/131 (2023.01)

201410165737.9 2014.04.23

(56) 对比文件

(73) 专利权人 三星显示有限公司

CN 1469330 A, 2004.01.21

地址 韩国京畿道

US 2012217516 A1, 2012.08.30

(72) 发明人 金泳道 洪正武 奇仁叙 朱永吉

崔硕

审查员 孙汝杰

权利要求书1页 说明书11页 附图14页

(54) 发明名称

显示面板及其制造方法

(57) 摘要

本发明涉及显示面板及其制造方法，该显示面板包括第一开关元件；第一像素电极，电气连接到第一开关元件，第一像素电极包括反射材料；第一发光层，布置在第一像素电极上，配置第一发光层以当电压被施加到第一像素电极时发出具有第一颜色的光；封装膜，布置在第一发光层上并配置为保护第一发光层；压敏粘合层，布置在封装膜上；以及第一滤色片，布置在压敏粘合层上，面向第一发光层并且包括第一颜色。

1.一种显示面板,包括:

第一底层;

第一开关元件,布置在所述第一底层上;

第一像素电极,电气连接到所述第一开关元件;

第一发光层,布置在所述第一像素电极上,所述第一发光层被配置为当电压被施加到所述第一像素电极时发出具有第一颜色的光;

封装层,布置在所述第一发光层上并被配置为保护所述第一发光层;

压敏粘合层,布置在所述封装层上;

第一滤色片,布置在所述压敏粘合层上并对应于所述第一发光层;以及

第二底层,布置在所述第一滤色片上,

其中所述封装层包括循序堆叠的第一有机层、第一无机层、第二有机层、第二无机层和第三有机层,并且所述第一有机层、所述第二有机层和所述第三有机层包括丙烯酸酯类材料,并且所述第一无机层和所述第二无机层包括氧化物类材料。

2.根据权利要求1所述的显示面板,其中所述第一滤色片具有所述第一颜色。

3.根据权利要求1所述的显示面板,其中所述第一底层和所述第二底层包括玻璃、金属和聚合物中的任一种。

4.根据权利要求1所述的显示面板,其中所述第一开关元件包括通过使用激光退火将非晶硅薄膜结晶而形成的低温多晶硅。

5.根据权利要求1所述的显示面板,其中所述压敏粘合层包括丙烯酸聚合物。

6.根据权利要求1所述的显示面板,其中所述压敏粘合层具有 $100\mu\text{m}$ 的厚度。

7.根据权利要求1所述的显示面板,其中所述第一滤色片是通过喷墨法形成的。

## 显示面板及其制造方法

[0001] 本申请是申请日为2014年4月23日,申请号为201410165737.9,发明名称为“显示面板及其制造方法”的发明专利申请的分案申请。

### 技术领域

[0002] 本发明的示例性实施方式涉及显示面板和显示面板的制造方法。更具体地,本发明的示例性实施方式涉及用于有机发光二极管(OLED)显示设备的显示面板和制造该显示面板的方法。

### 背景技术

[0003] 近来已制造轻量且小尺寸的液晶显示设备。因为阴极射线管(CRT)显示设备的良好性能及其有竞争力的价格,所以其已使用多年。然而CRT显示设备具有其相对大的尺寸、高重量和缺乏便携性的缺点。因此,因为液晶显示设备的相对小尺寸、轻量和低功耗,所以其近来高度需求。

[0004] 有机发光显示设备一般包括发射红、绿和蓝光的有机发光层,以及像素电极,因此有机发光显示设备可以显示各种颜色。有机发光显示设备的像素电极是用于反射光的反射电极。然而像素电极也反射外部光,因此有机发光显示设备的可见性可以降低。

[0005] 在该背景技术部分中披露的以上信息仅用于增强理解本发明的背景技术,并因此其可以含有不构成现有技术的信息。

### 发明内容

[0006] 本发明的示例性实施方式提供能够通过降低外部光的反射比改善显示面板可见性的显示面板。

[0007] 本发明的示例性实施方式也提供制造显示面板的方法。

[0008] 本发明的另外特征在以下描述中阐述,或部分地从描述变得明显,或可以从本发明的实践学习。

[0009] 本发明的示例性实施方式披露显示面板,其包括第一开关元件、电气连接到第一开关元件的第一像素电极,该第一像素电极包括反射材料。第一发光层布置在第一像素电极上,并在电压施加到第一像素电极时发射具有第一颜色的光。薄封装膜布置在第一发光层上并保护第一发光层。压敏粘合层布置在薄封装膜上,并且第一滤色片布置在压敏粘合层上。第一滤色片对应于第一发光层并具有第一颜色。

[0010] 本发明的示例性实施方式披露制造显示面板的方法,该方法包括形成显示基板、形成上保护膜并将上保护膜的压敏粘合层附加到显示基板的薄封装膜,形成上保护膜包括在基层上形成具有第一颜色的第一滤色片并在第一滤色片上形成压敏粘合层。显示基板包括第一开关元件、电气连接到第一开关元件并包括反射材料的第一像素电极、第一发光层和薄封装膜,该第一发光层布置在第一像素电极上,并在电压施加到第一像素电极时发射具有第一颜色的光,该薄封装膜布置在第一发光层上并保护第一发光层。

[0011] 理解前面一般描述和以下详细描述是示范性和解释性的，并且意图提供如要求的本发明进一步解释。

## 附图说明

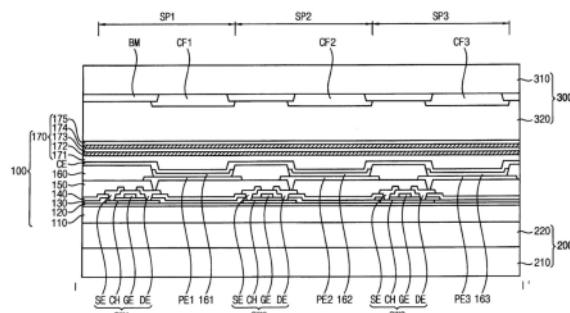

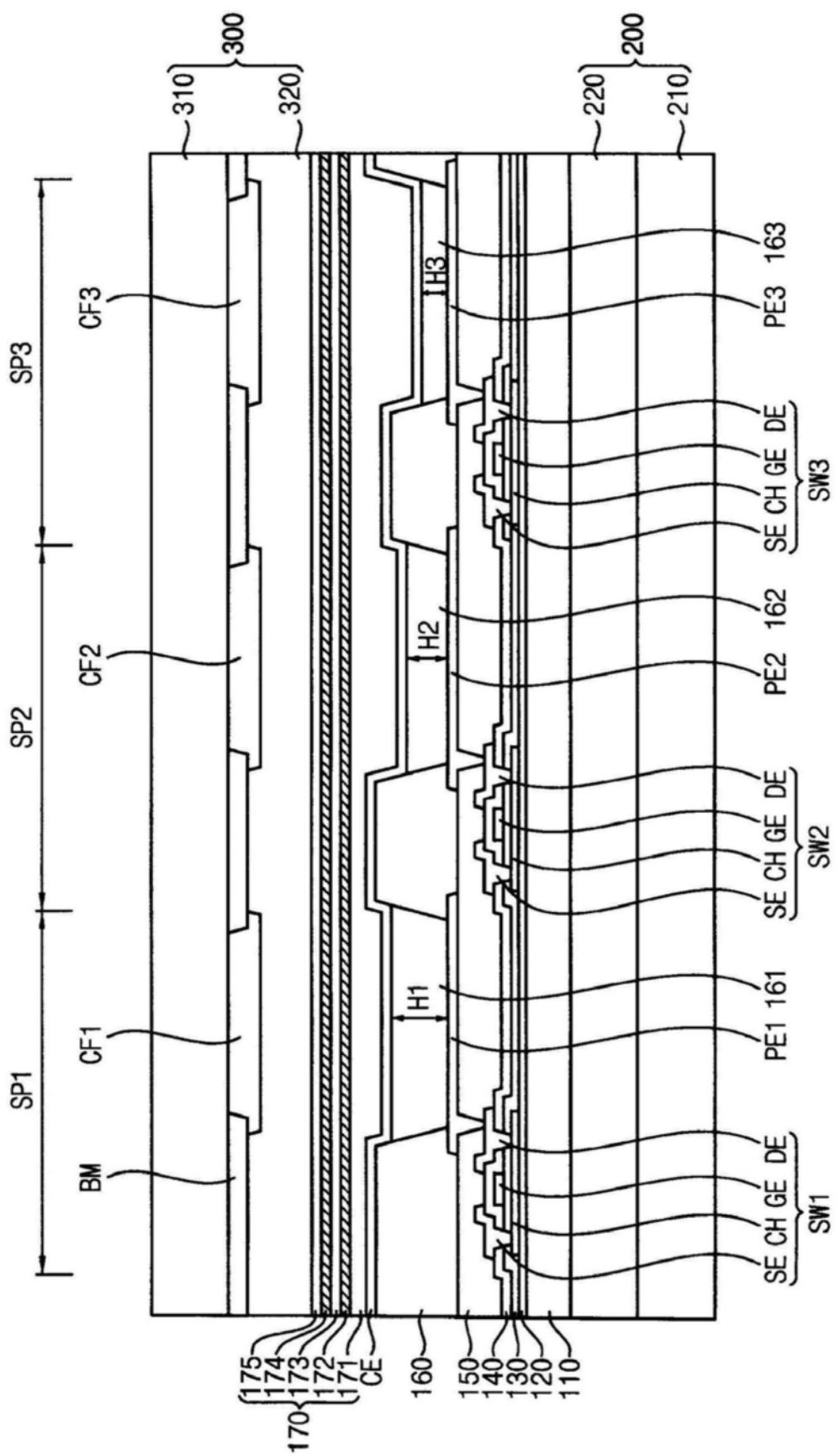

[0012] 被包括从而提供本发明进一步理解的附图结合与本说明书并构成本说明书的一部分，图解本发明的示例性实施方式，并与描述一起用来解释本发明的原理。图1是图解根据本发明的示例性实施方式的显示面板的平面图。

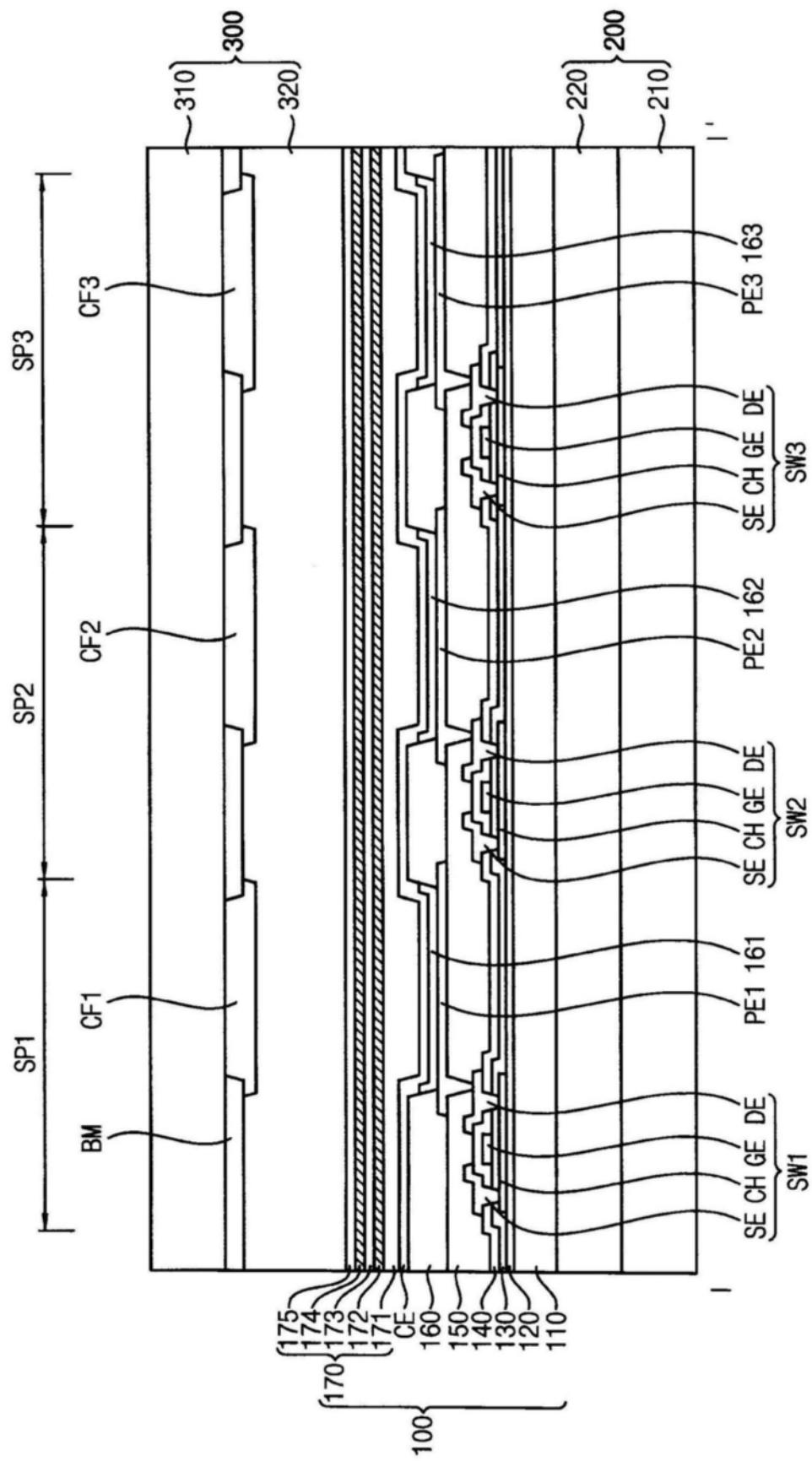

[0013] 图2是沿图1的直线I-I'取得的剖面图。

[0014] 图3是图解根据本发明的示例性实施方式的显示面板的平面图。

[0015] 图4是图解根据本发明的示例性实施方式的显示面板的平面图。

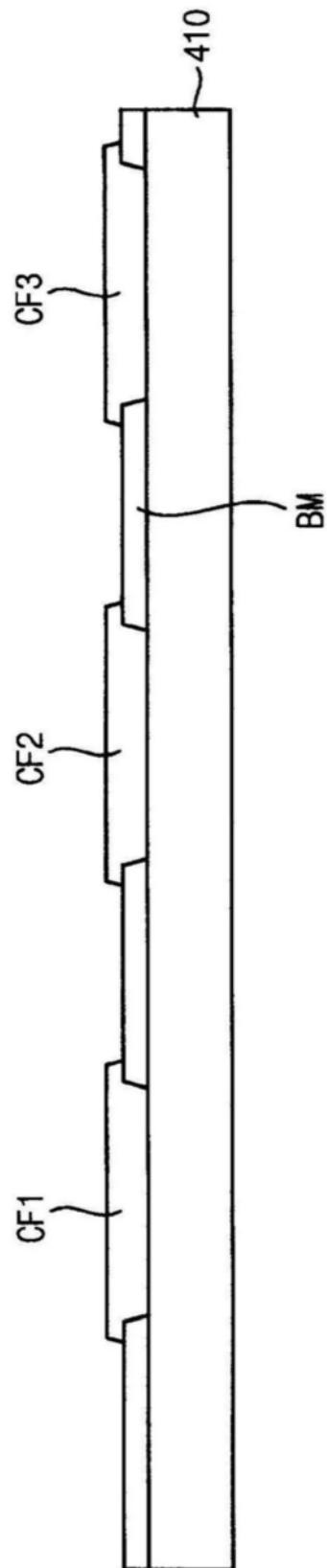

[0016] 图5A到图5C是图解制造图2的显示面板的上保护膜的方法的剖面图。

[0017] 图6A到图6C是图解制造图3的显示面板的上保护膜的方法的剖面图。

[0018] 图7A到图7G是图解制造图2的显示面板的显示基板的方法的剖面图。

[0019] 图8是图解将上保护膜和下保护膜附加到显示基板以便制造显示面板的步骤的剖面图。

## 具体实施方式

[0020] 本发明在下文中参考其中示出本发明的示例性实施方式的附图更详细描述。然而这些实施例可以用许多不同形式实施，并且不应解释为限于在此阐述的示例性实施方式。相反，提供这些示例性实施方式因此本披露是详尽的，并向本领域技术人员完全传达本发明的保护范围。在附图中元件的大小和相对大小可以为清晰放大。附图中相似参考号指代相似元件。

[0021] 理解当元件或层称为“在另一元件或层上”、“连接到”或“耦接到”另一元件或层时，其可以直接在该另一元件或层上、连接到该另一元件或层或耦接到另一元件或层，或中间元件或层可以存在。相反，当元件称为“直接在另一元件或层上”、“直接连接到”或“直接耦接到”另一元件或层时，没有中间元件或层存在。如在此使用，术语“和/或”包括关联列出条目的一个或多个的任何与全部组合。理解为了本披露，“X、Y和Z中的至少一个”可以解释为仅X、仅Y、仅Z，或两个或更多个条目X、Y和Z的任何组合（例如，XYZ、XYY、YZ、ZZ）。

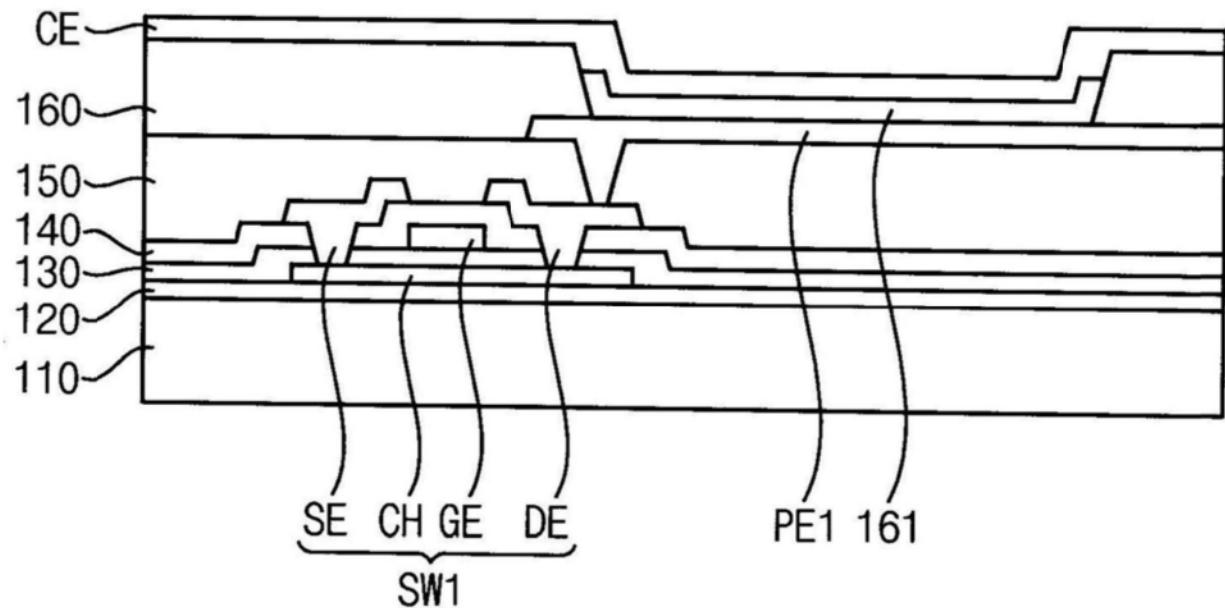

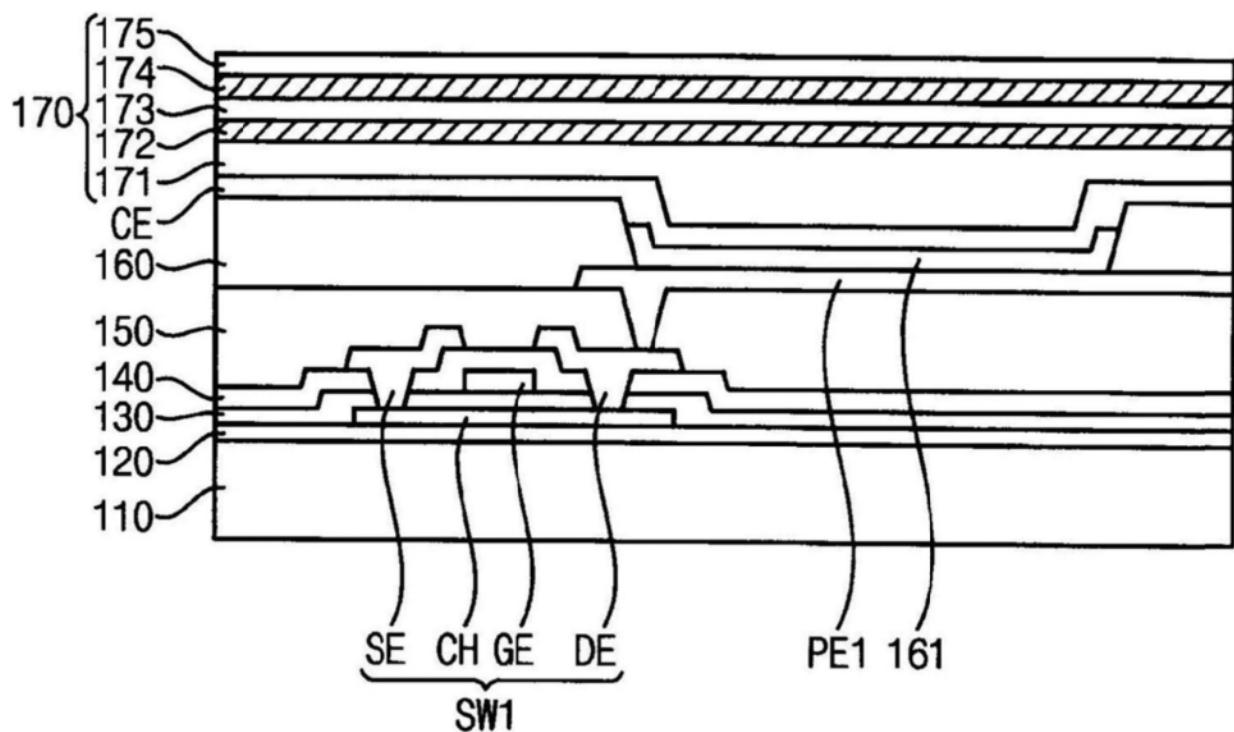

[0022] 图1是图解根据本发明的示例性实施方式的显示面板的平面图。图2是沿图1的直线I-I'取得的剖面图。

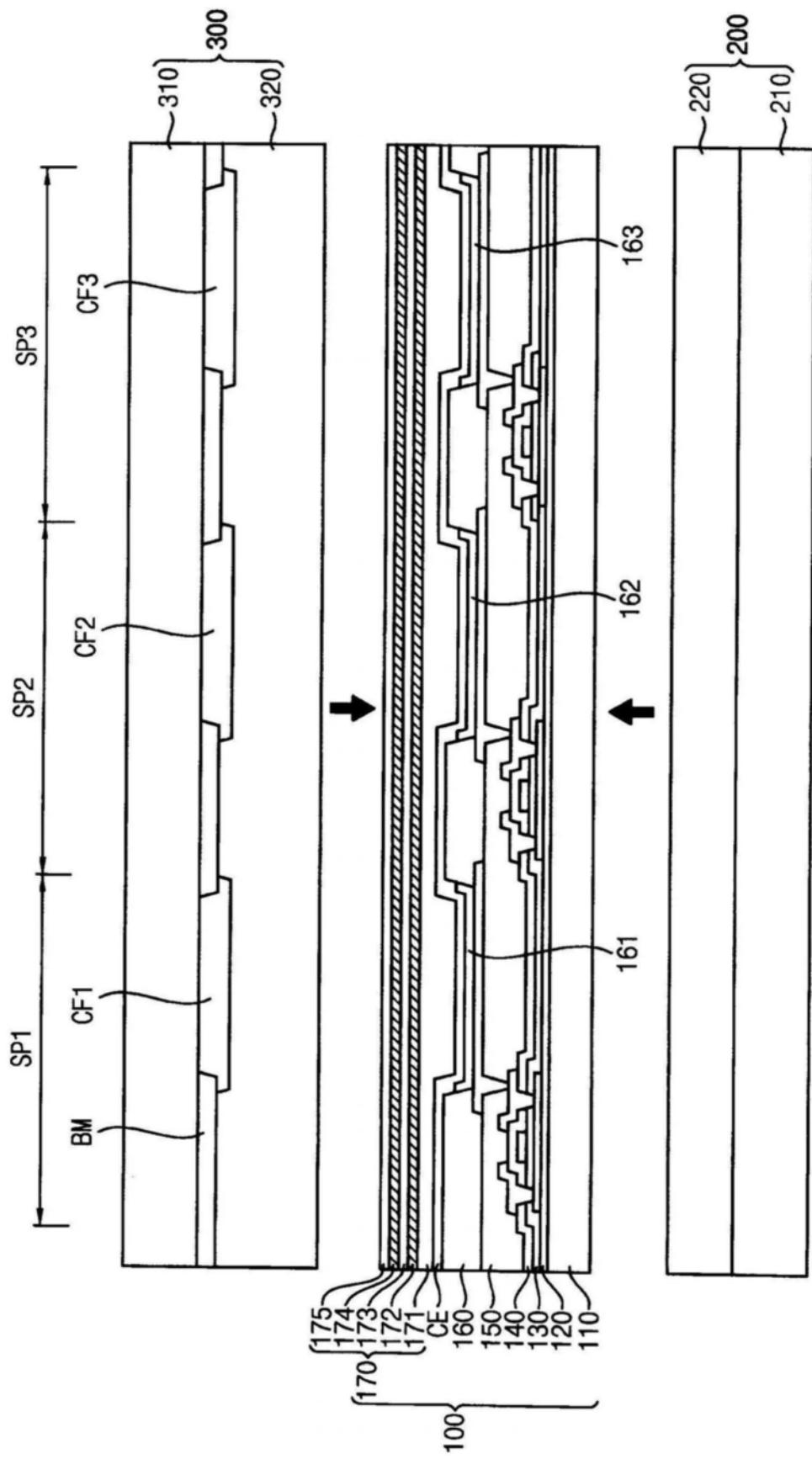

[0023] 参考图1和图2，显示面板包括显示基板100、上保护膜300和下保护膜200。显示面板包括多个单元像素。在图中描述了包括第一子像素SP1、第二子像素SP2和第三子像素SP3的一个单元像素（单位像素，unit pixel）。

[0024] 显示基板100包括底部基板110，缓冲层120，第一绝缘层130，第二绝缘层140，第一到第三开关元件SW1、SW2和SW3，第三绝缘层150，第一到第三像素电极PE1、PE2和PE3，像素定义层160，第一到第三发光层161、162和163，共同电极CE，以及薄封装膜170。

[0025] 底部基板110可以包括绝缘基板。另外底部基板110可以包括柔性基板。例如底部基板110可以包括玻璃基板、石英基板、透明树脂基板等。用于底部基板110的透明树脂基板的例子可以包括聚酰亚胺类树脂、丙烯酸类树脂、聚丙烯酸酯类树脂、聚碳酸酯类树脂、聚

醚类树脂、含磺酸的树脂、聚对苯二甲酸乙二醇酯类树脂等。

[0026] 缓冲层120可以布置在底部基板110上。缓冲层120可以防止金属原子和/或杂质从底部基板110扩散。缓冲层120可以改善底部基板110表面的平坦度。另外，缓冲层120可以为信道层CH调整连续结晶工艺的热传递速率，由此获得基本均匀的信道层CH。缓冲层120可以使用硅化合物形成。例如缓冲层120可以包括氧化硅( $\text{SiO}_x$ )、氮化硅( $\text{SiN}_x$ )、氮氧化硅( $\text{SiO}_x\text{N}_y$ )，碳氧化硅( $\text{SiO}_x\text{C}_y$ )，碳氮化硅( $\text{SiC}_x\text{N}_y$ )等。这些可以单独或在其混合物中使用。

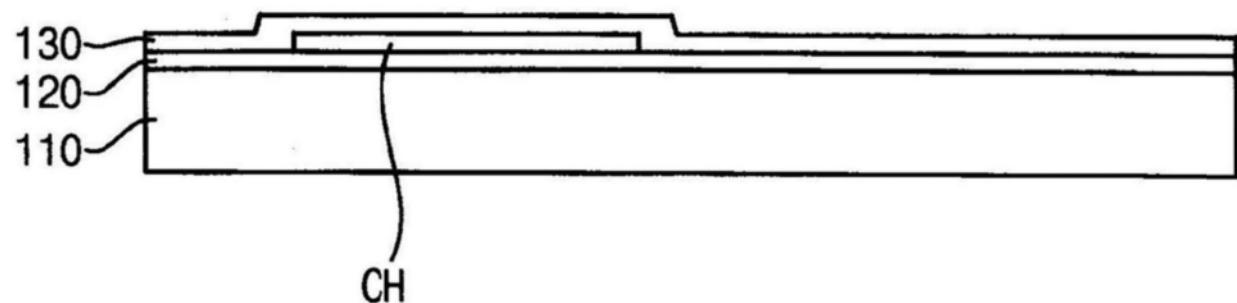

[0027] 信道层CH布置在缓冲层120上。信道层CH可以包括通过使用激光退火法将非晶硅薄膜结晶形成的低温多晶硅(LTPS)。另外信道层CH可以包括非晶硅的半导体层(a-Si:H)和n+非晶硅的欧姆接触层(n+a-Si:H)。另外信道层CH可以包括氧化物半导体。

[0028] 第一绝缘层130布置在其上布置信道层CH的缓冲层120上。第一绝缘层130可以包括氧化硅、金属氧化物等。

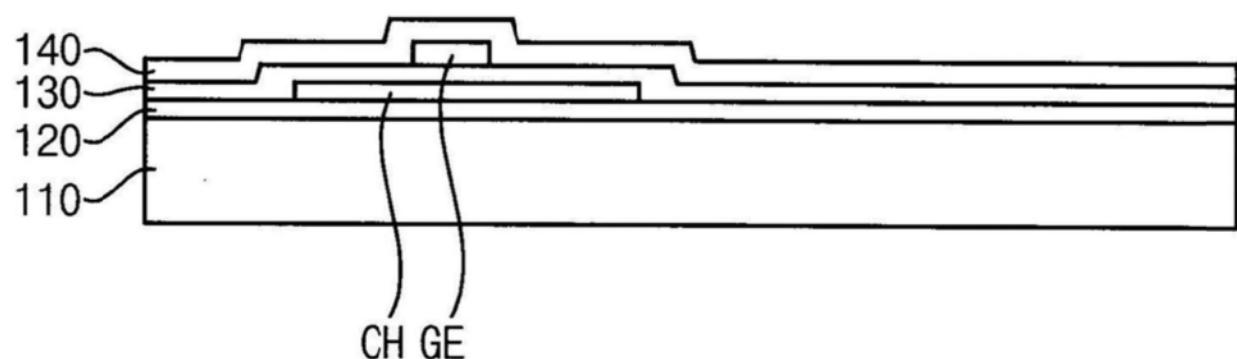

[0029] 栅电极GE布置在第一绝缘层130上并与信道层CH重叠。栅电极GE电气连接到栅极线GL。栅电极可以包括金属、合金、导电金属氧化物、透明导电材料等。

[0030] 第二绝缘层140布置在其上布置栅电极GE的第一绝缘层130上。第二绝缘层140可以包括氧化硅( $\text{SiO}_x$ )、氮化硅( $\text{SiN}_x$ )、氮氧化硅( $\text{SiO}_x\text{N}_y$ )，碳氧化硅( $\text{SiO}_x\text{C}_y$ )，碳氮化硅( $\text{SiC}_x\text{N}_y$ )等。这些可以单独或在其混合物中使用。另外第二绝缘层140可以具有单层结构或多层结构。例如，第二绝缘层140可以具有包括氧化硅膜、氮化硅膜、氮氧化硅膜、碳氧化硅膜或碳氮化硅膜的单层结构。可替换地，第二绝缘层140可以具有包括氧化硅膜、氮化硅膜、氮氧化硅膜、碳氧化硅膜、碳氮化硅膜等中的至少两个的多层结构。

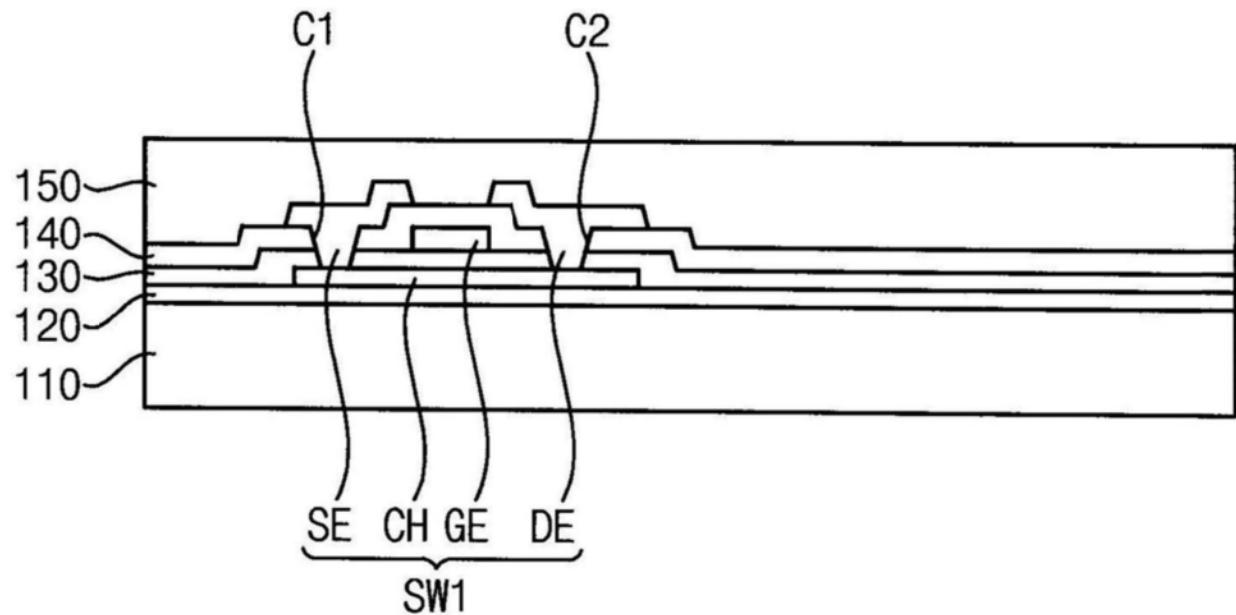

[0031] 第一接触孔C1穿过第一和第二绝缘层130和140形成，因此第一接触孔C1部分地暴露信道层CH。第二接触孔C2穿过第一和第二绝缘层130和140形成，因此第二接触孔C2部分地暴露信道层CH。

[0032] 源电极SE和漏电极DE布置在第二绝缘层140上。源电极SE穿过第一接触孔C1电气连接到信道层CH。漏电极DE穿过第二接触孔C2电气连接到信道层CH。源电极SE和漏电极DE可以包括金属、合金、导电金属氧化物、透明导电材料等。

[0033] 信道层CH、栅电极GE、源电极SE和漏电极DE形成第一开关元件SW1。第一开关元件SW1对应于第一子像素SP1形成。相似地，第二开关元件SW2对应于第二子像素SP2形成，并且第三开关元件SW3对应于第三子像素SP3形成。

[0034] 第三绝缘层150布置在其上布置源电极SE和漏电极DE的第二绝缘层140上。第三绝缘层150可以使用有机材料形成。例如第三绝缘层150可以包括光致抗蚀剂、丙烯酸类树脂、聚酰亚胺类树脂、聚酰胺类树脂、硅氧烷类树脂等。这些可以单独或在其组合中使用。可替换地，第三绝缘层150可以包括无机材料。例如第三绝缘层150可以使用氧化硅、氮化硅、氮氧化硅、碳氧化硅、铝、镁、锌、铪、钽、氧化铝、氧化钛、氧化钽、氧化镁、氧化锌、氧化铪、氧化钽、氧化钛等形成。这些元素和化合物可以单独或在其混合物中使用。

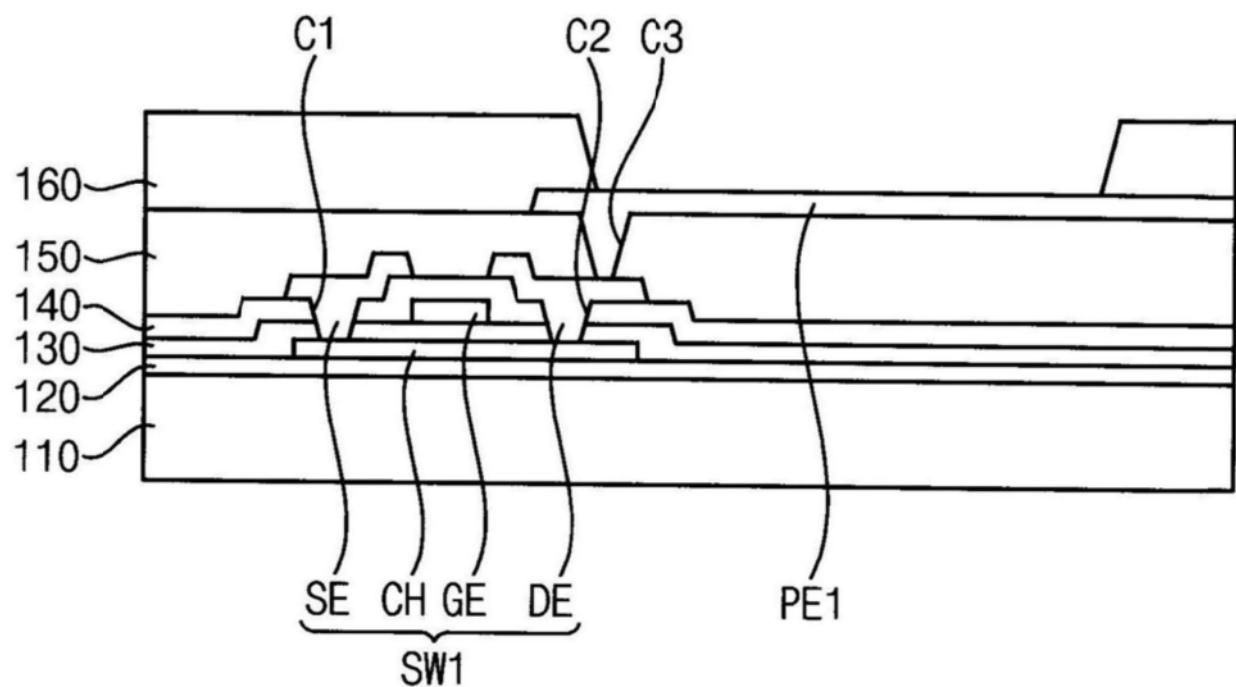

[0035] 第三接触孔C3穿过第三绝缘层150形成，因此第三接触孔C3部分地暴露漏电极DE。

[0036] 第一到第三像素电极PE1、PE2和PE3布置在第三绝缘层150上。第一像素电极PE1穿过第三接触孔C3电气连接到第一开关元件SW1的漏电极DE。第一像素电极PE1对应于第一子像素SP1形成。相似地，第二像素电极PE2对应于第二子像素SP2形成，并且电气连接到第二开关元件SW2。第三像素电极PE3对应于第三子像素SP3形成，并且电气连接到第三开关元件

SW3。

[0037] 第一到第三像素电极PE1、PE2和PE3可以包括反射材料。第一到第三像素电极PE1、PE2和PE3可以具有约100%的反射比。例如第一到第三像素电极PE1、PE2和PE3可以包括铝，含铝、氮化铝、银的合金，含银、钨、氮化钨、铜的合金，含铜、镍的合金，含镍、铬、氮化铬、钼的合金，含钼、钛、氮化钛、铂、钽、氮化钽、钕、钪、锶钇氧化物、氧化锌、铟锡氧化物、氧化锡、氧化铟、氧化镓、铟锌氧化物的合金，等等。

[0038] 像素定义层160布置在其上布置第一到第三像素电极PE1、PE2和PE3的第三绝缘层150上。暴露第一到第三像素电极PE1、PE2和PE3的开孔可以穿过像素定义层160形成。

[0039] 像素定义层160可以包括有机材料或无机材料。例如像素定义层160可以使用光致抗蚀剂、丙烯酸类树脂、聚丙烯酸类树脂、聚酰亚胺类树脂、硅化合物等形成。

[0040] 第一到第三发光层161、162和163布置在通过像素定义层160的开孔暴露的第一到第三像素电极PE1、PE2和PE3上。另外，第一到第三发光层161、162和163可以在像素定义层100开孔的侧壁上延伸。第一到第三发光层161、162和163的每个可以包括发光材料从而生成相互不同的颜色。第一发光层161对应于第一子像素SP1形成，并生成具有第一颜色的光。例如第一发光层161可以生成红光。第二发光层162对应于第二子像素SP2形成，并生成具有与第一颜色不同的第二颜色的光。例如第二发光层162可以生成绿光。第三发光层163对应于第三子像素SP3形成，并生成具有与第一和第二颜色不同的第三颜色的光。例如第三发光层163可以生成蓝光。

[0041] 共同电极CE布置在其上布置第一到第三发光层161、162和163的像素定义层160上。根据显示装置的发光类型，共同电极CE可以包括透射材料或反射材料。例如共同电极CE可以使用铝，含铝、氮化铝、银的合金，含银、钨、氮化钨、铜的合金，含铜、镍的合金，含镍、铬、氮化铬、钼的合金，含钼、钛、氮化钛、铂、钽、氮化钽、钕、钪、锶钇氧化物、氧化锌、铟锡氧化物、氧化锡、氧化铟、氧化镓、铟锌氧化物的合金等形成。这些可以单独或在其组合中使用。

[0042] 薄封装膜170布置在共同电极CE上。薄封装膜170保护第一到第三发光层161、162和163。

[0043] 薄封装膜170包括交替堆叠的多个有机和无机层。例如薄封装膜170可以包括循序堆叠的第一有机层171、第一无机层172、第二有机层173、第二无机层174和第三有机层175。第一、第二和第三有机层171、173和175可以包括丙烯酸酯类材料，并且第一和第二无机层172和174可以包括氧化物类材料。薄封装膜170可以使用低温工艺形成以便不损坏第一到第三发光层161、162和163。例如薄封装膜170可以通过在低温例如低于约100°C的温度使用生长法形成。依靠低温生长法，薄封装膜170可以在共同电极CE上之直接生长并形成，不损坏第一到第三发光层161、162和163。薄封装膜170可以具有约1到10μm的厚度。

[0044] 下保护膜200包括第一底层210和第一压敏粘合剂层220。下保护膜200保护显示基板100底部。

[0045] 第一底层210可以包括玻璃、金属或聚合物。当第一底层210包括聚合物时，第一底层210可以包括聚酰亚胺、聚碳酸酯、聚对苯二甲酸乙二醇酯(PET)、聚氨酯、聚丙烯腈(PAN)、聚乙烯(PE)、聚丙烯(PP)等。第一底层210可以具有约75μm的厚度。

[0046] 第一压敏粘合层220布置在第一底层210和显示基板100的底部基板110之间。第一

压敏粘合层220用来将下保护膜200附着到显示基板100的底部基板110上。例如第一压敏粘合层220可以包括丙烯酸聚合物。第一压敏粘合层220可以具有约25 $\mu\text{m}$ 的厚度。

[0047] 上保护膜300包括第二底层310、黑矩阵BM、第一到第三滤色片CF1、CF2和CF3，以及第二压敏粘合层320。上保护膜300保护显示基板100顶部。

[0048] 第二底层310可以包括玻璃、金属或聚合物。当第二底层310包括聚合物时，第一底层210可以包括聚酰亚胺、聚碳酸酯、聚对苯二甲酸乙二醇酯(PET)、聚氨酯、聚丙烯腈(PAN)、聚乙烯(PE)、聚丙烯(PP)等。第二底层310可以具有约100 $\mu\text{m}$ 的厚度。

[0049] 当黑矩阵BM与第一到第三滤色片CF1、CF2和CF3在第二底层310上形成时，第二底层310的耐热温度可以比黑矩阵BM与第一到第三滤色片CF1、CF2和CF3的制造工艺温度更高。例如第二底层310的耐热温度可以是约200°C到约300°C。

[0050] 黑矩阵BM布置在第二底层310上。黑矩阵BM与数据线DL、栅极线GL以及开关元件SW1、SW2和SW3重叠，并包括遮光材料。黑矩阵BM至少部分定义邻近子像素的边界。

[0051] 第一到第三滤色片CF1、CF2和CF3布置在其上布置黑矩阵BM的第二底层310上。第一到第三滤色片CF1、CF2和CF3分别对应于第一到第三子像素SP1、SP2和SP3而被布置。另外，第一到第三滤色片CF1、CF2和CF3对应于第一到第三发光层161、162和163而被布置。第一滤色片CF1具有与源自第一发光层161的光的第一颜色相同颜色。例如当第一发光层161生成红光时，第一滤色片CF1可以具有红色。第二滤色片CF2具有与源自第二发光层162的光的第二颜色相同颜色。例如当第二发光层162生成绿光时，第二滤色片CF2可以具有绿色。第三滤色片CF3具有与源自第三发光层163的光的第三颜色相同颜色。例如当第三发光层163生成蓝光时，第三滤色片CF3可以具有蓝色。

[0052] 黑矩阵BM与第一到第三滤色片CF1、CF2和CF3可以由传统制造工艺形成。例如，可以使用包括预烘烤和后烘烤步骤的用于液晶显示设备的黑矩阵和滤色片的制造工艺。预烘烤步骤可以在约90到110°C发生。后烘烤步骤可以在约220到230°C发生。

[0053] 第二压敏粘合层320布置在黑矩阵BM与第一到第三滤色片CF1、CF2和CF3上。第二压敏粘合层320用来将上保护膜300附着到显示基板100的薄封装膜170上。第二压敏粘合层320可以执行粘合功能。例如第二压敏粘合层320可以包括丙烯酸类聚合物。第二压敏粘合层320可以具有约100 $\mu\text{m}$ (微米)的厚度。

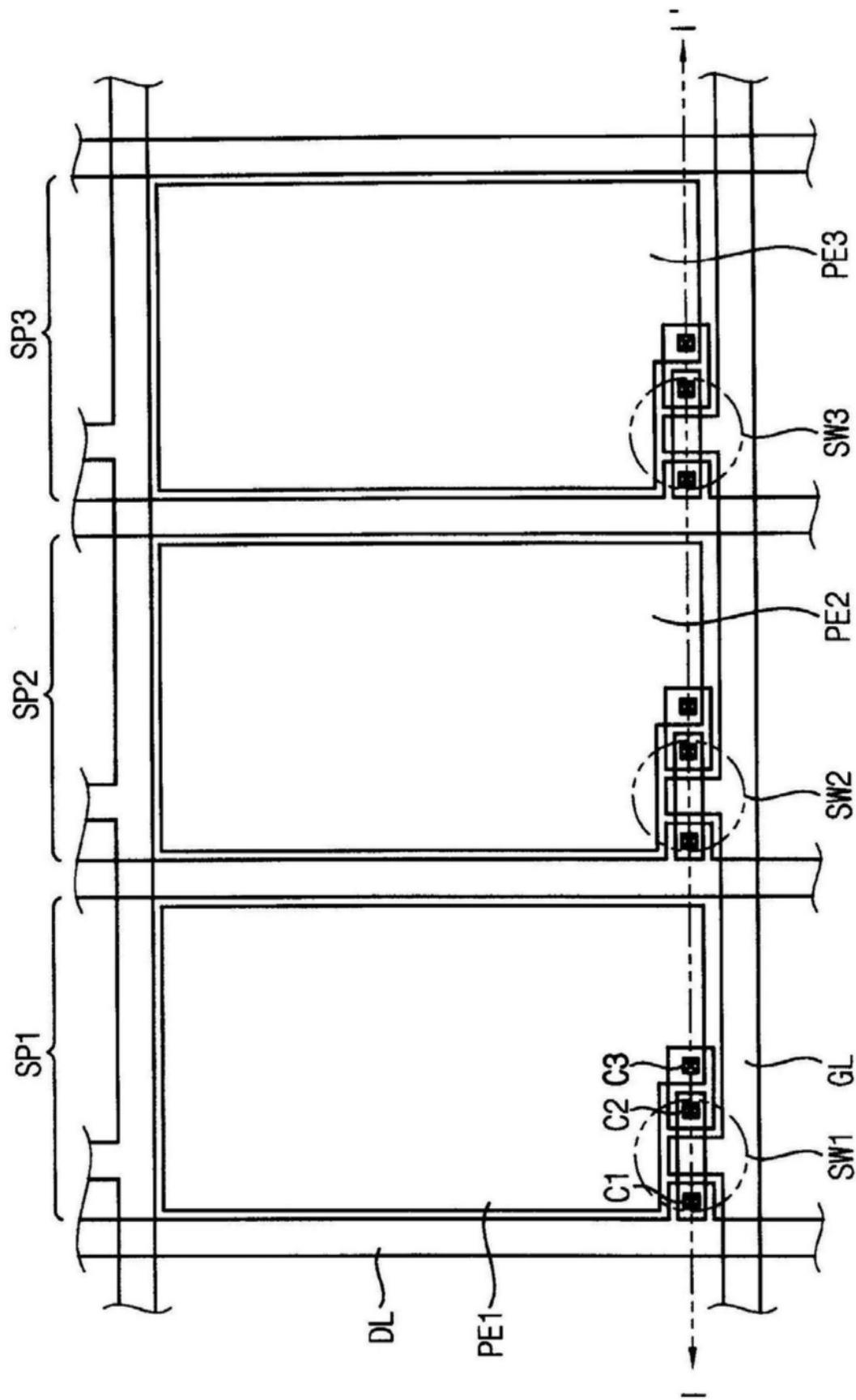

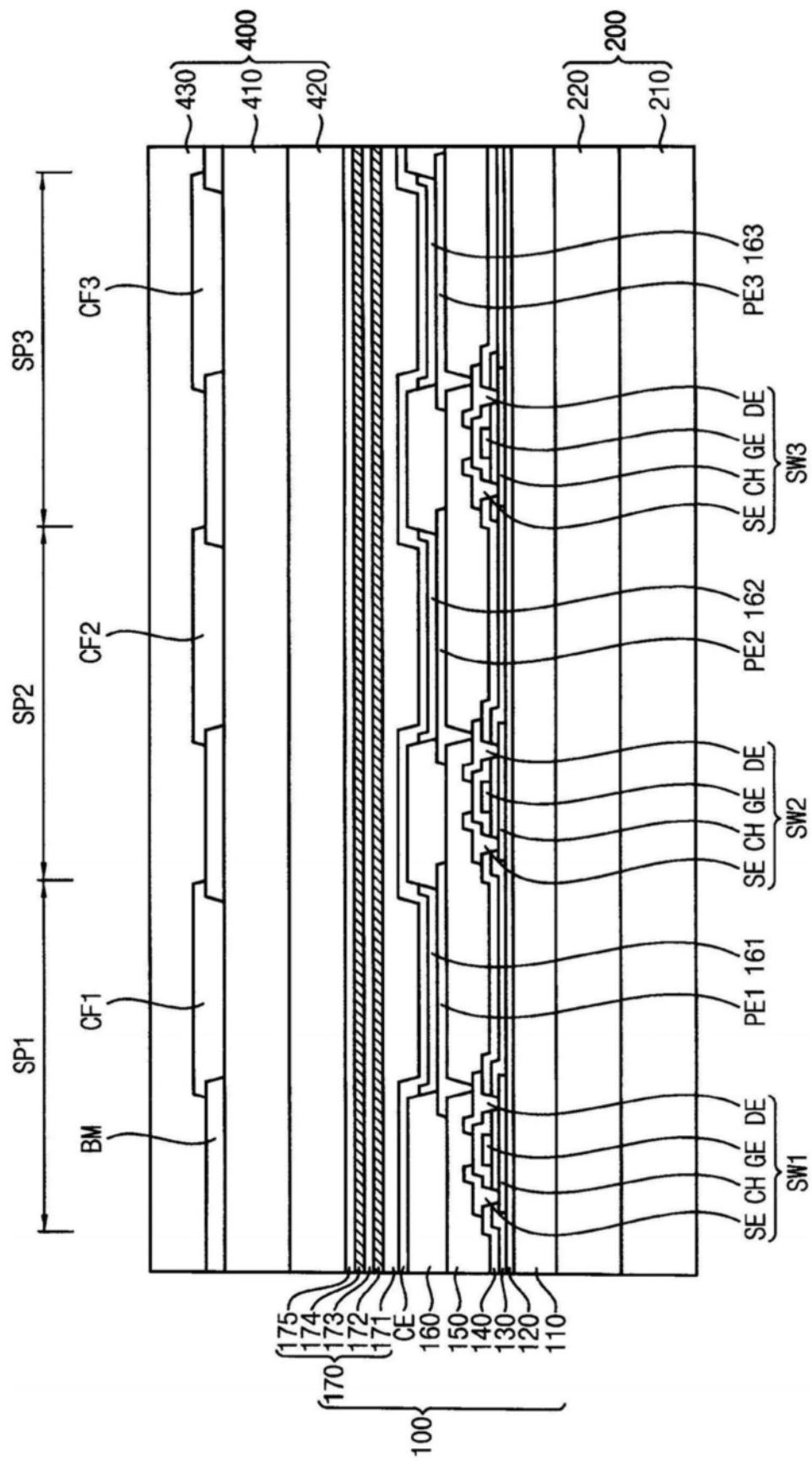

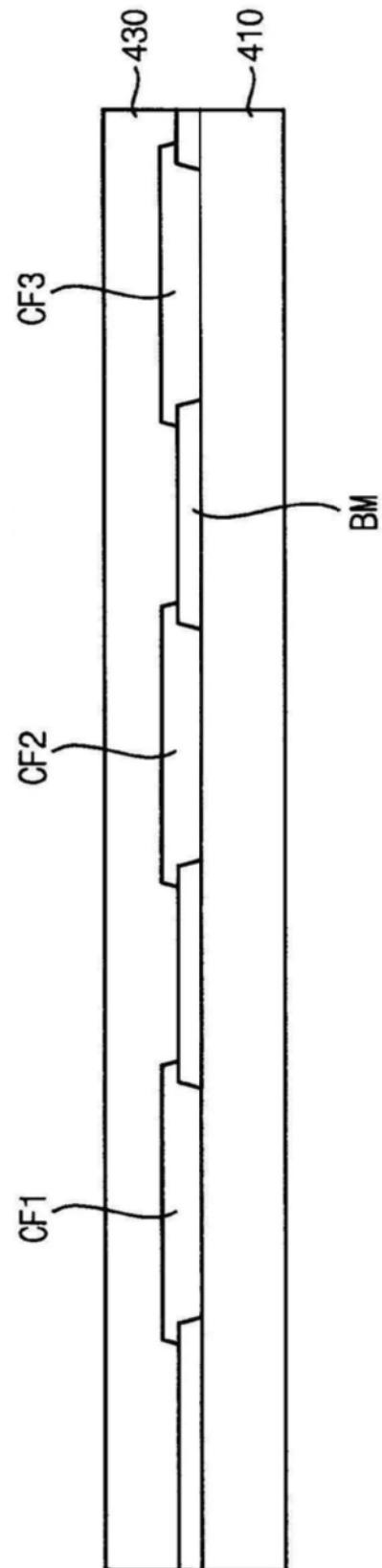

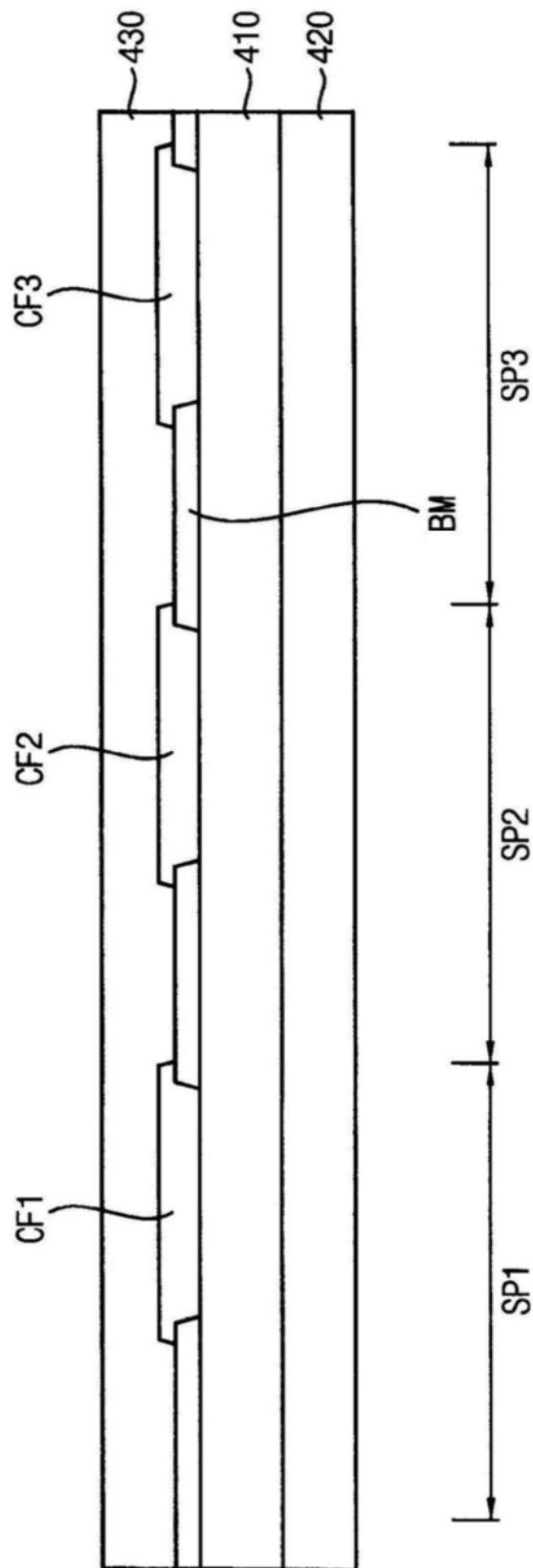

[0054] 图3是图解根据本发明的示例性实施方式的显示面板的平面图。

[0055] 参考图3，除存在上保护膜400之外，显示面板与图2的显示面板基本相同。因此关于相同元件的进一步详细描述简要解释或省略。

[0056] 显示面板包括显示基板100、上保护膜400和下保护膜200。显示面板包括多个单元像素。单元像素包括第一子像素SP1、第二子像素SP2和第三子像素SP3。

[0057] 显示基板100包括底部基板110，缓冲层120，第一绝缘层130，第二绝缘层140，第一到第三开关元件SW1、SW2和SW3，第三绝缘层150，第一到第三像素电极PE1、PE2和PE3，像素定义层160，第一到第三发光层161、162和163，共同电极CE，以及薄封装膜170。下保护膜200包括第一底层210和第一压敏粘合层220。

[0058] 上保护膜400包括第二底层410、黑矩阵BM、第一到第三滤色片CF1、CF2和CF3、第二压敏粘合层420，以及防护涂层430。上保护膜400保护显示基板100顶部。

[0059] 第二底层410可以包括玻璃、金属或聚合物。当第二底层410包括聚合物时，第一底

层210可以包括聚酰亚胺、聚碳酸酯、聚对苯二甲酸乙二醇酯(PET)、聚氨酯、聚丙烯腈(PAN)、聚乙烯(PE)、聚丙烯(PP)等。第二底层410可以具有约100μm的厚度。

[0060] 当黑矩阵BM与第一到第三滤色片CF1、CF2和CF3在第二底层410上形成时，第二底层410的耐热温度可以比黑矩阵BM与第一到第三滤色片CF1、CF2和CF3的制造工艺温度更高。例如第二底层410的耐热温度可以是约200°C到约300°C。

[0061] 黑矩阵BM布置在第二底层410上。黑矩阵BM与各种布线例如数据线、栅极线和开关元件重叠，并包括遮光材料。黑矩阵BM定义邻近子像素的边界。

[0062] 第一到第三滤色片CF1、CF2和CF3布置在其上布置黑矩阵BM的第二底层410上。第一到第三滤色片CF1、CF2和CF3分别对应于第一到第三子像素SP1、SP2和SP3而被布置。另外，第一到第三滤色片CF1、CF2和CF3分别对应于第一到第三发光层161、162和163而被布置。第一滤色片CF1具有与源自第一发光层161的光的第一颜色相同颜色。例如当第一发光层161生成红光时，第一滤色片CF1可以具有红色。第二滤色片CF2具有与源自第二发光层162的光的第二颜色相同颜色。例如当第二发光层162生成绿光时，第二滤色片CF2可以具有绿色。第三滤色片CF3具有与源自第三发光层163的光的第三颜色相同颜色。例如当第三发光层163生成蓝光时，第三滤色片CF3可以具有蓝色。

[0063] 第一到第三滤色片CF1、CF2和CF3分别具有与源自第一到第三发光层的光的第一到第三颜色相同颜色。因此外部光经过显示面板并在第一到第三像素电极PE1、PE2和PE3上反射，然后仅特定波长的外部光可以经过滤色片。因此滤色片可以通过防止反射外部光降低显示质量来改善显示面板的显示质量。

[0064] 黑矩阵BM与第一到第三滤色片CF1、CF2和CF3可以由传统制造工艺形成。例如，可以使用包括预烘烤和后烘烤步骤的用于液晶显示设备的黑矩阵和滤色片的制造工艺。预烘烤步骤可以在约90到110°C发生。后烘烤步骤可以在约220到230°C发生。

[0065] 防护涂层430布置在第一到第三滤色片CF1、CF2和CF3与黑矩阵BM上。防护涂层430将第一到第三滤色片CF1、CF2和CF3平面化，保护第一到第三滤色片CF1、CF2和CF3，并将第一到第三滤色片CF1、CF2和CF3绝缘。防护涂层430可以包括丙烯酸类环氧树脂(acrylic-epoxy)材料。

[0066] 第二压敏粘合层420布置在第二底层410下面。因此，第二压敏粘合层420布置在与第一到第三滤色片CF1、CF2和CF3以及黑矩阵BM相反的第二底层410的一侧上。第二压敏粘合层420用来将上保护膜400附着到显示基板100的薄封装膜170上。例如第二压敏粘合层420可以包括丙烯酸类聚合物。第二压敏粘合层420可以具有约100μm的厚度。

[0067] 图4是图解根据本发明的另一个示例性实施方式的显示面板的平面图。

[0068] 参考图4，除第一到第三发光层161、162和163与像素定义层160之外，显示面板与图2的显示面板基本相同。因此关于相同元件的进一步详细描述简要解释或省略。

[0069] 显示面板包括显示基板100、上保护膜300和下保护膜200。显示面板包括多个单元像素。单元像素包括第一子像素SP1、第二子像素SP2和第三子像素SP3。

[0070] 显示基板100包括底部基板110，缓冲层120，第一绝缘层130，第二绝缘层140，第一到第三开关元件SW1、SW2和SW3，第三绝缘层150，第一到第三像素电极PE1、PE2和PE3，像素定义层160，第一到第三发光层161、162和163，共同电极CE，以及薄封装膜170。

[0071] 像素定义层160布置在其上布置第一到第三像素电极PE1、PE2和PE3的第三绝缘层

150上。暴露第一到第三像素电极PE1、PE2和PE3的开孔可以穿过像素定义层160形成。像素定义层160根据第一到第三发光层161、162和163的高度可以在子像素的每个中具有不同高度。

[0072] 像素定义层160可以包括有机材料或无机材料。例如像素定义层160可以使用光致抗蚀剂、丙烯酸类树脂、聚丙烯酸类树脂、聚酰亚胺类树脂、硅化合物等形成。

[0073] 第一到第三发光层161、162和163布置在通过像素定义层160的开孔暴露的第一到第三像素电极PE1、PE2和PE3上。另外，第一到第三发光层161、162和163可以在像素定义层100开孔的侧壁上延伸。第一到第三发光层161、162和163的每个可以包括发光材料从而生成不同颜色。第一发光层161对应于第一子像素SP1形成，并生成具有第一颜色的光。例如第一发光层161可以生成红光。第二发光层162对应于第二子像素SP2形成，并生成具有与第一颜色不同的第二颜色的光。例如第二发光层162可以生成绿光。第三发光层163对应于第三子像素SP3形成，并生成具有与第一和第二颜色不同的第三颜色的光。例如第三发光层163可以生成蓝光。

[0074] 第一到第三发光层161、162和163可以具有不同高度。第一到第三发光层161、162和163的每个具有引起相消干涉，从而降低外部光在第一到第三像素电极PE1、PE2和PE3上与共同电极CE上的反射比的高度。第一到第三发光层161、162和163的高度取决于第一到第三发光层161、162和163的颜色波长和反射率。

[0075] 例如第一发光层161可以发射红光，第二发光层162可以发射绿光，并且第三发光层163可以发射蓝光。在此情况下，因为共同电极CE的半透明性质，所以在共同电极CE上反射的外部光的一部分和外部光的另一部分经过共同电极CE。在红光的情况下，经过共同电极CE、经过第一发光层161的外部光的部分然后由第一像素电极161反射，并然后经过第一发光层161和共同电极CE。因此由第一像素电极PE1反射的外部光的红光，以及经过共同电极CE并由第一像素电极PE1反射的外部光的红光相消干涉，因此源自外部光的红光的反射比可以降低。

[0076] 当第一发光层161的高度(H1)满足以下条件时：

$$2n_R(H1) = (m+1/2)\lambda_R,$$

[0077] 其中 $n_R$ 和 $\lambda_R$ 分别是第一发光层161的折射率和入射的红光的波长，并且m是整数，

[0078] 那么在共同电极CE上反射的红光，以及经过共同电极CE并在第一像素电极PE1上反射的红光可以互相相消干涉。因此源自外部光的红光的反射比可以降低。

[0079] 相似地，当第二发光层162的高度(H2)满足以下条件时：

$$2n_G(H2) = (m+1/2)\lambda_G,$$

[0080] 其中 $n_G$ 和 $\lambda_G$ 分别是第二发光层162的折射率和入射的绿光的波长，并且m是整数，

[0081] 那么在共同电极CE上反射的绿光，以及经过共同电极CE并由第一像素电极PE1上反射的绿光可以互相相消干涉。因此源自外部光的绿光的反射比可以降低。

[0082] 另外，当第三发光层163的高度(H3)满足以下条件时：

$$2n_B(H3) = (m+1/2)\lambda_B,$$

[0083] 其中 $n_B$ 和 $\lambda_B$ 分别是第三发光层163的折射率和入射的蓝光的波长，并且m是整数，

[0084] 那么在共同电极CE上反射的蓝光，以及经过共同电极CE并在第一像素电极PE1上反射的蓝光可以互相相消干涉。因此源自外部光的蓝光的反射比可以降低。

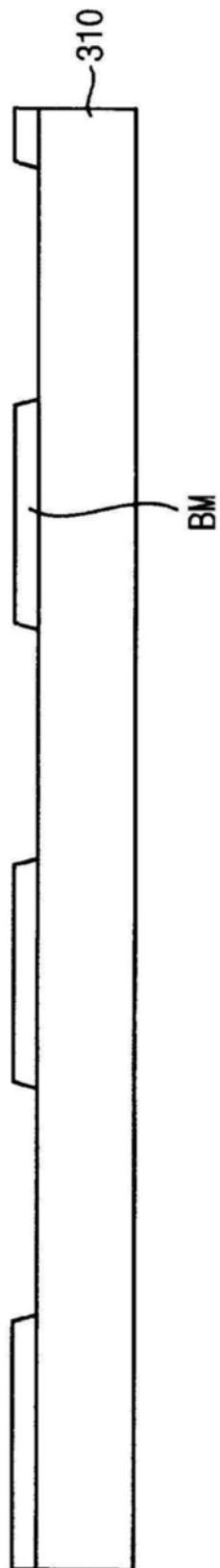

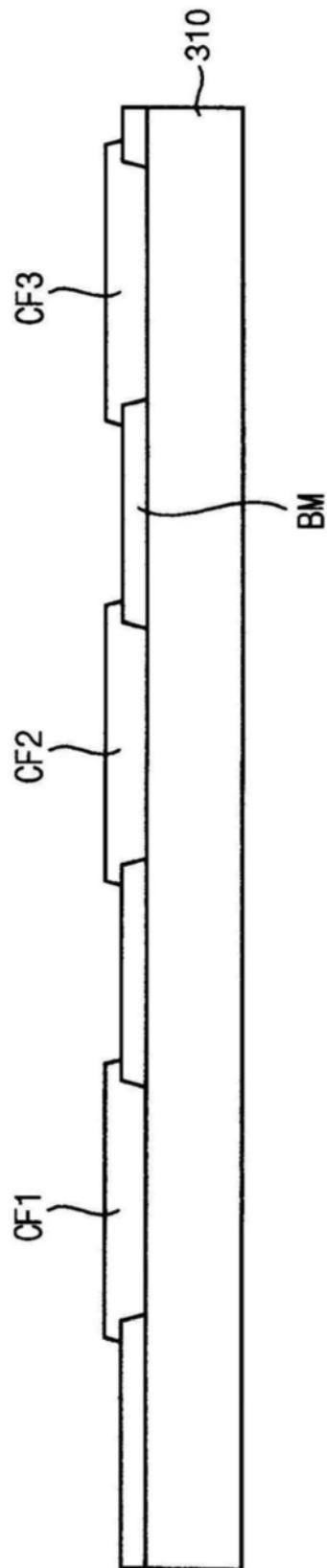

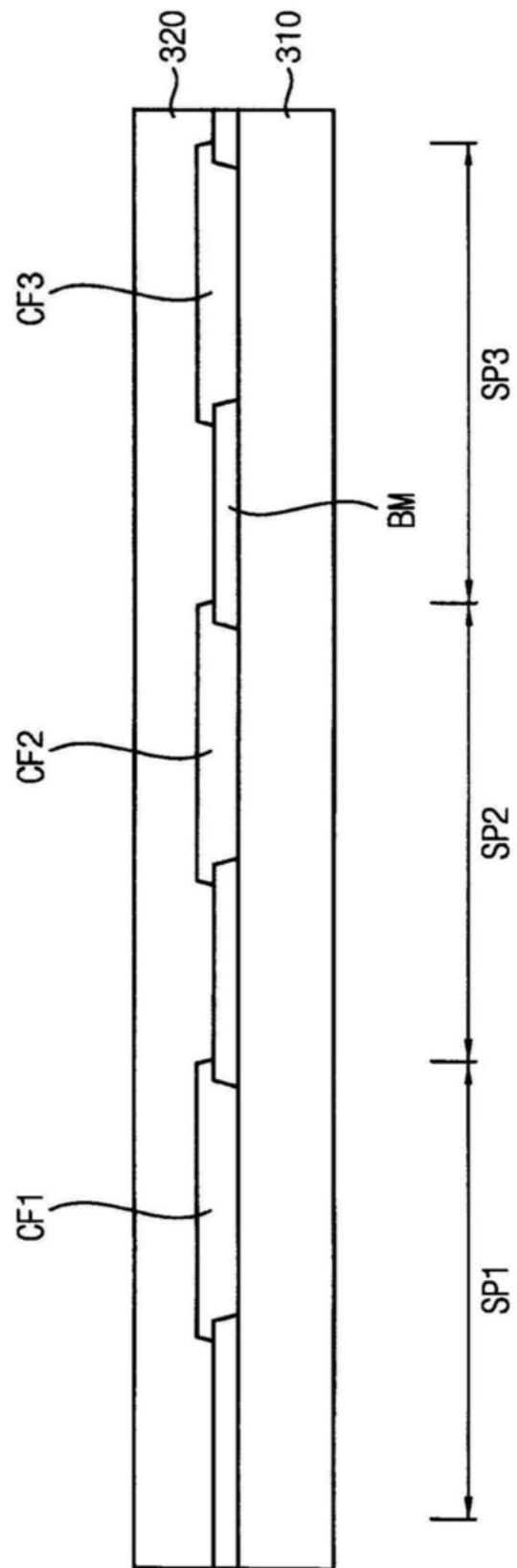

[0088] 图5A到图5C是图解制造图2的显示面板的上保护膜300的方法的剖面图。制造上保护膜300的方法包括形成黑矩阵BM、形成第一到第三滤色片CF1、CF2和CF3，以及形成第二压敏粘合层320。

[0089] 参考图5A，在形成黑矩阵BM中，黑矩阵BM在第二底层310上形成。遮光材料由溅射法在第二底层310上形成。遮光材料然后使用图案化掩模曝光，并然后将遮光材料显影从而形成黑矩阵BM。第二底层310可以包括玻璃、金属或聚合物。当第二底层310包括聚合物时，第一底层210可以包括聚酰亚胺、聚碳酸酯、聚对苯二甲酸乙二醇酯(PET)、聚氨酯、聚丙烯腈(PAN)、聚乙烯(PE)、聚丙烯(PP)等。第二底层310可以具有约100μm的厚度。遮光材料可以包括金属例如铬(Cr)、碳基有机材料等。

[0090] 参考图5A-图5C，在形成第一到第三滤色片CF1、CF2和CF3中，第一到第三滤色片CF1、CF2和CF3在其上形成黑矩阵BM的第二底层310上形成。第一到第三滤色片CF1、CF2和CF3可以分别对应于第一到第三子像素SP1到SP3形成。可以形成滤色片CF1、CF2和CF3的每一个从而与黑矩阵BM上邻近滤色片重叠。第一到第三滤色片CF1、CF2和CF3可以循序形成。

[0091] 形成第一滤色片CF1可以包括在其上形成黑矩阵BM的第二底层310上形成第一彩色光阻剂(color esist)，使用图案化掩模将第一彩色光阻剂曝光，并将第一彩色光阻剂显影从而形成第一滤色片CF1。

[0092] 在此情况下，在将第一彩色光阻剂曝光之前，形成第一滤色片CF1可以进一步包括真空干燥工艺和/或预烘烤工艺。在预烘烤工艺中，第一彩色光阻剂可以在约90到110°C热硬化。另外在将第一彩色光阻剂显影后，形成第一滤色片CF1可以进一步包括后烘烤工艺。在后烘烤工艺中，第一滤色片CF1可以在约220到230°C热硬化。

[0093] 形成第二滤色片CF2可以包括在其上形成第一滤色片CF1的第二底层310上形成第二彩色光阻剂，使用图案化掩模将第二彩色光阻剂曝光，并将第二彩色光阻剂显影从而形成第二滤色片CF2。

[0094] 在此情况下，在将第二彩色光阻剂曝光之前，形成第二滤色片CF2可以进一步包括真空干燥工艺和/或预烘烤工艺。在预烘烤工艺中，第二彩色光阻剂可以在约90到110°C热硬化。另外在将第二彩色光阻剂显影后，形成第二滤色片CF2可以进一步包括后烘烤工艺。在后烘烤工艺中，第二滤色片CF2可以在约220到230°C热硬化。

[0095] 形成第三滤色片CF3可以包括在其上形成第一和第二滤色片CF1和CF2的第二底层310上形成第三彩色光阻剂，使用图案化掩模将第三彩色光阻剂曝光，并将第三彩色光阻剂显影从而形成第三滤色片CF3。

[0096] 在此情况下，在将第三彩色光阻剂曝光之前，形成第三滤色片CF3可以进一步包括真空干燥工艺和/或预烘烤工艺。在预烘烤工艺中，第三彩色光阻剂可以在约90到110°C热硬化。另外在将第三彩色光阻剂显影后，形成第三滤色片CF3可以进一步包括后烘烤工艺。在后烘烤工艺中，第三滤色片CF3可以在约220到230°C热硬化。另外，第一到第三滤色片CF1、CF2和CF3可以由喷墨法形成。

[0097] 参考图5C，在形成第二压敏粘合层320中，第二压敏粘合层320在黑矩阵BM与第一到第三滤色片CF1、CF2和CF3上形成。第二压敏粘合层320可以通过在黑矩阵BM与第一到第三滤色片CF1、CF2和CF3上附加另外粘合带来形成。例如第二压敏粘合层320可以是包括丙烯酸类聚合物的带。第二压敏粘合层320可以具有约100μm的厚度。

[0098] 图6A到图6C是图解制造图3的显示面板的上保护膜400的方法的剖面图。除形成防护涂层430并形成第二压敏粘合层420之外,制造上保护膜400的方法与图5A到5C的制造上保护膜300的方法基本相同。因此关于相同元件的任何进一步详细描述简要解释或省略。

[0099] 制造上保护膜的方法包括形成黑矩阵BM、形成第一到第三滤色片CF1、CF2和CF3,形成防护涂层430,以及形成第二压敏粘合层420。

[0100] 参考图6A,在形成黑矩阵BM中,黑矩阵BM在第二底层410上形成。遮光材料由溅射法在第二底层410上形成,遮光材料使用图案化掩模曝光,并然后遮光材料显影从而形成黑矩阵BM。

[0101] 参考图6A,在形成第一到第三滤色片CF1、CF2和CF3中,第一到第三滤色片CF1、CF2和CF3在其上形成黑矩阵BM的第二底层410上形成。第一到第三滤色片CF1、CF2和CF3可以分别对应于第一到第三子像素(参考图5C的SP1到SP3)形成。可以形成滤色片CF1、CF2和CF3以使每个滤色片在黑矩阵BM上重叠。第一到第三滤色片CF1、CF2和CF3可以循序形成。

[0102] 形成第一滤色片CF1可以包括在其上形成黑矩阵BM的第二底层410上形成第一彩色光阻剂,使用图案化掩模将第一彩色光阻剂曝光,并将第一彩色光阻剂显影。

[0103] 在此情况下,在将第一彩色光阻剂曝光之前,形成第一滤色片CF1可以进一步包括真空干燥工艺和/或预烘烤工艺。在预烘烤工艺中,第一彩色光阻剂可以在约90到110°C热硬化。另外在将第一彩色光阻剂显影后,形成第一滤色片CF1可以进一步包括后烘烤工艺。在后烘烤工艺中,第一滤色片CF1可以在约220到230°C热硬化。

[0104] 形成第二滤色片CF2可以包括在其上形成第一滤色片CF1的第二底层410上形成第二彩色光阻剂,使用图案化掩模将第二彩色光阻剂曝光,并将第二彩色光阻剂显影从而形成第二滤色片CF2。

[0105] 在此情况下,在将第二彩色光阻剂曝光之前,形成第二滤色片CF2可以进一步包括真空干燥工艺和/或预烘烤工艺。在预烘烤工艺中,第二彩色光阻剂可以在约90到110°C热硬化。另外在将第二彩色光阻剂显影后,形成第二滤色片CF2可以进一步包括后烘烤工艺。在后烘烤工艺中,第二滤色片CF2可以在约220到230°C热硬化。

[0106] 形成第三滤色片CF3可以包括在其上形成第一和第二滤色片CF1和CF2的第二底层410上形成第三彩色光阻剂,使用图案化掩模将第三彩色光阻剂曝光,并将第三彩色光阻剂显影从而形成第三滤色片CF3。

[0107] 在此情况下,在将第三彩色光阻剂曝光之前,形成第三滤色片CF3可以进一步包括真空干燥工艺和/或预烘烤工艺。在预烘烤工艺中,第三彩色光阻剂可以在约90到110°C热硬化。另外在将第三彩色光阻剂显影后,形成第三滤色片CF3可以进一步包括后烘烤工艺。在后烘烤工艺中,第三滤色片CF3可以在约220到230°C热硬化。

[0108] 另外,第一到第三滤色片CF1、CF2和CF3可以由喷墨法形成。

[0109] 参考图6B,在形成防护涂层430中,防护涂层430在黑矩阵BM与第一到第三滤色片CF1、CF2和CF3上形成。防护涂层430将第一到第三滤色片CF1、CF2和CF3平面化,保护第一到第三滤色片CF1、CF2和CF3,并将第一到第三滤色片CF1、CF2和CF3绝缘。防护涂层430可以由丙烯酸类环氧树脂材料形成。

[0110] 参考图6C,第二压敏粘合层420在防护涂层430下形成。因此第二压敏粘合层420在与第一到第三滤色片CF1、CF2和CF3以及黑矩阵BM相反的第二底层410的一侧上形成。第二

压敏粘合层420可以通过在防护涂层430上附加另外粘合带来形成。例如第二压敏粘合层320可以是包括丙烯酸类聚合物的带。第二压敏粘合层420可以具有约100 $\mu\text{m}$ (微米)的厚度。

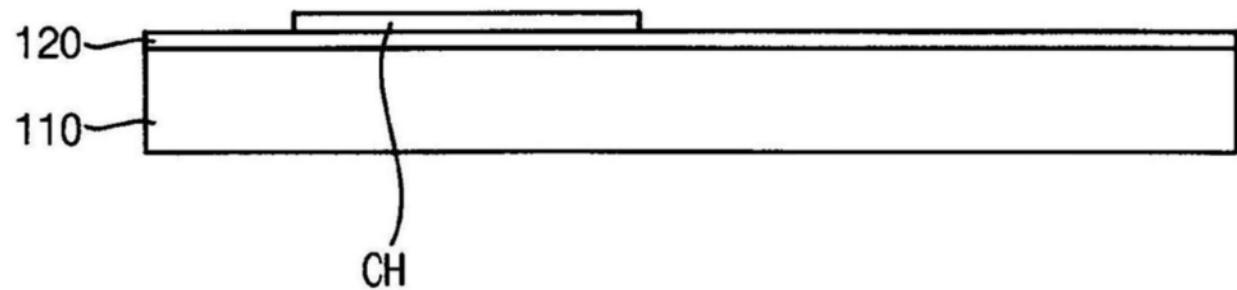

[0111] 图7A到图7G是图解制造图2的显示面板的显示基板的方法的剖面图,其中描述一个像素。

[0112] 参考图7A,缓冲层120在底部基板110上形成。缓冲层120可以由旋涂工艺、化学气相沉积(CVD)工艺、等离子体增强化学汽相沉积(PECVD)工艺、高密度等离子体化学汽相沉积(HDP-CVD)工艺、印刷工艺等形式。

[0113] 信道层CH在缓冲层120上形成。半导体层可以在缓冲层120上形成,并然后信道层CH通过将半导体层图案化来形成。信道层CH可以由CVD工艺、PECVD工艺、低压化学气相沉积(LPCVD)工艺、溅射工艺等形式。另外信道层CH可以包括低温多晶硅(LTPS)。

[0114] 参考图7B,第一绝缘层130在其上形成信道层CH的缓冲层120上形成。根据在第一绝缘层130中包括的成分,第一绝缘层130可以由旋涂工艺、印刷工艺、溅射工艺、CVD工艺、ALD工艺、PECVD工艺、HDP-CVD工艺或真空蒸发工艺形成。

[0115] 参考图7C,与信道层CH重叠的栅电极GE在第一绝缘层130上形成。导电层在第一绝缘层130上形成,并然后导电层可以由光刻工艺或使用另外蚀刻掩模的蚀刻工艺部分蚀刻。因此形成栅电极GE。

[0116] 第二绝缘层140在其上形成栅电极GE的第一绝缘层130上形成。根据在第二绝缘层140中包括的成分,第二绝缘层140可以由旋涂工艺、印刷工艺、溅射工艺、CVD工艺、ALD工艺、PECVD工艺、HDP-CVD工艺或真空蒸发工艺形成。

[0117] 参考图7D,暴露信道层CH的第一和第二接触孔C1、C2穿过第一和第二绝缘层130和140形成。第一和第二接触孔C1、C2可以由光刻工艺或使用另外蚀刻掩模的蚀刻工艺形成。

[0118] 源电极SE和漏电极DE在第一和第二接触孔穿过的第二绝缘层140上形成。源电极SE穿过第一接触孔电气连接到信道层CH。漏电极DE穿过第二接触孔电气连接到信道层CH。导电层在第二绝缘层140上形成,并然后导电层可以由光刻工艺或使用另外蚀刻掩模的蚀刻工艺部分蚀刻。因此形成源电极SE和漏电极DE。

[0119] 第三绝缘层150在其上布置源电极SE和漏电极DE的第二绝缘层140上形成。根据在第三绝缘层150中包括的成分,第三绝缘层150可以由旋涂工艺、印刷工艺、溅射工艺、CVD工艺、ALD工艺、PECVD工艺、HDP-CVD工艺或真空蒸发工艺形成。

[0120] 参考图7E,第三接触孔C3穿过第三绝缘层150形成,因此第三接触孔C3部分暴露漏电极DE。第三接触孔C3可以由光刻工艺或使用另外蚀刻掩模的蚀刻工艺形成。

[0121] 第一像素电极PE1在第三接触孔C3穿过其形成的第三绝缘层150上形成。第一像素电极PE1穿过第三接触孔C3电气连接到第一开关元件SW1的漏电极DE。第一像素电极PE1可以由印刷工艺、溅射工艺、CVD工艺、脉冲激光淀积(PLD)工艺、真空蒸发工艺、原子激光淀积(ALD)工艺等形式。

[0122] 像素定义层160布置在其上形成第一像素电极PE1的第三绝缘层150上。像素定义层160可以由旋涂工艺、喷雾工艺、印刷工艺、CVD工艺、PECVD工艺、HDP-CVD工艺等获得。

[0123] 参考图7F,发光层161在通过像素定义层160的开孔暴露的第一像素电极PE1上形成。第一发光层161可以由激光诱发热成像工艺、印刷工艺等形式。

[0124] 共同电极CE在像素定义层160和第一像素电极PE1上形成。共同电极CE可以由印刷

工艺、溅射工艺、CVD工艺、PLD工艺、真空蒸发工艺、ALD工艺等形成。

[0125] 参考图7G,薄封装膜170在共同电极CE上形成。薄封装膜170通过交替堆叠多个有机和无机层来形成。薄封装膜170可以使用生长法在低温例如约100°C或更低的温度形成。依靠低温生长法,薄封装膜170可以直接在共同电极CE上生长并形成,不损坏第一发光层161。例如薄封装膜170可以包括循序堆叠的第一有机层171、第一无机层172、第二有机层173、第二无机层174和第三有机层175。第一有机层171在共同电极CE上形成,并然后第一无机层172在第一有机层171上形成。第二有机层173在第一无机层172上形成,并然后第二无机层174在第二有机层173上形成。第三有机层175在第二无机层174上形成。

[0126] 图8是图解将上保护膜和下保护膜附加到显示基板以便制造显示面板的步骤的剖面图。

[0127] 在完成显示基板100后,上保护膜300和下保护膜200可以由另外工艺形成。然后,通过挤压下保护膜200将下保护膜200的第一压敏粘合层220附着到显示基板100的底部基板110上,并且将上保护膜300的第二压敏粘合层320附着到显示基板100的薄封装膜170上,由此完成显示面板。

[0128] 根据本发明,显示面板包括具有与源自发光层的光相同颜色的滤色片,由此降低了在像素电极上外部光的反射比。因此显示面板的显示质量可以改善。

[0129] 另外,使用压敏粘合层在包括发光层的显示基板上附着包括滤色片的保护膜,由此即使滤色片由相对高温的工艺形成,仍可以防止由热导致的对发光层的损坏。

[0130] 另外,当显示面板是柔性显示器时,滤色片可以替代用于降低反射比的传统偏振片,由此显示面板厚度可以减小。因此显示面板的柔性可以改善。

[0131] 本领域技术人员认识到各种修改和变化可以不背离本发明的精神或保护范围在本发明中做出。因此意图如果本发明的修改和变化在附加权利要求及其等效的保护范围内,则本发明覆盖该修改和变化。

图1

图2

图3

图4

图5A

图5B

图5C

图6A

图6B

图6C

图7A

图7B

图7C

图7D

图7E

图7F

图7G

图8