(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5994679号

(P5994679)

(45) 発行日 平成28年9月21日(2016.9.21)

(24) 登録日 平成28年9月2日(2016.9.2)

(51) Int.Cl.

HO3K 19/177 (2006.01)

F 1

HO3K 19/177

請求項の数 6 (全 18 頁)

(21) 出願番号 特願2013-36080 (P2013-36080)

(22) 出願日 平成25年2月26日 (2013.2.26)

(65) 公開番号 特開2014-165748 (P2014-165748A)

(43) 公開日 平成26年9月8日 (2014.9.8)

審査請求日 平成27年11月2日 (2015.11.2)

(73) 特許権者 514315159

株式会社ソシオネクスト

神奈川県横浜市港北区新横浜2丁目10番

23

(74) 代理人 100105957

弁理士 恩田 誠

(74) 代理人 100068755

弁理士 恩田 博宣

(72) 発明者 岡田 一彦

愛知県春日井市高蔵寺町二丁目1844番

2 富士通VLSI株式会社内

審査官 緒方 寿彦

最終頁に続く

(54) 【発明の名称】処理装置、及び処理装置の制御方法

## (57) 【特許請求の範囲】

## 【請求項1】

複数の処理ユニットを含み回路構成情報に応じた前記処理ユニットにより論理回路を再構成するプログラマブル論理回路を有する処理装置であって、

第1の処理に応じた第1の回路構成情報により構築される論理回路に含まれる前記処理ユニット内の情報保持部に、前記第1の処理に関連し前記第1の処理の次に実施される第2の処理に応じた第2の回路構成情報を格納し、前記第1の処理の実行制御信号を出力する第1の制御回路と、

前記第1の処理の終了に応じて、前記情報保持部から取得した前記第2の回路構成情報により前記プログラマブル論理回路の再構成を制御する第2の制御回路と、

10

を有することを特徴とする処理装置。

## 【請求項2】

前記第1の制御回路は、前記第2の回路構成情報を格納する前記情報保持部に、前記第2の処理に関連し前記第2の処理の次に実施する第3の処理に応じた第3の回路構成情報を格納し、

前記第2の制御回路は、前記情報保持部から取得した前記第2の回路構成情報により前記第2の処理を実施する論理回路に含まれる前記処理ユニット内の前記情報保持部に前記第3の回路構成情報を設定し、前記第2の処理を実施する前記処理ユニットに処理の実行を指示すること、

を特徴とする請求項1に記載の処理装置。

**【請求項 3】**

前記第1の制御回路は、前記第1の回路構成情報をメモリに格納し、再構成制御信号を出力し、

前記第2の制御回路は、前記再構成制御信号に応じて、前記メモリから取得した前記第1の回路構成情報により前記プログラマブル論理回路の再構成を制御して前記第1の処理に応じた論理回路を構築させること、

を特徴とする請求項1又は2に記載の処理装置。

**【請求項 4】**

前記第1の制御回路は、前記プログラマブル論理回路において再構成される論理回路に応じた実行パラメータを、前記メモリの複数のメモリ領域のうち前記第2の回路情報を取得する前記処理ユニットに応じたメモリ領域に格納し、10

前記第2の制御回路は、前記第2の回路構成情報を取得する前記情報保持部を含む前記処理ユニットに応じた前記メモリ領域に格納された動作パラメータを取得して再構成された論理回路の処理ユニットに設定すること、

を特徴とする請求項3に記載の処理装置。

**【請求項 5】**

複数の処理ユニットを含み回路構成情報に応じた前記処理ユニットにより論理回路を再構成するプログラマブル論理回路によって第1の演算処理と第2の演算処理を実施する処理装置であって、

前記第1の演算処理は連続的に実施される第1の処理及び第2の処理を含み、20

前記第1の処理に応じた回路構成情報と前記第2の演算処理に応じた回路構成情報をメモリに格納し、前記第1の処理に応じた第1の回路構成情報により構築される論理回路に含まれる前記処理ユニット内の情報保持部に、前記第2の処理に応じた第2の回路構成情報を格納し、前記第1の処理の実行制御信号を出力する第1の制御回路と、

前記実行制御信号に応じて、前記メモリから前記回路構成情報を読み出して前記プログラマブル論理回路に前記第1の処理に応じた論理回路と前記第2の演算処理に応じた論理回路を構築する再構成を制御し、前記第1の処理の終了に応じて、前記情報保持部から取得した前記第2の回路構成情報により前記プログラマブル論理回路の再構成を制御する第2の制御回路と、

を有することを特徴とする処理装置。30

**【請求項 6】**

複数の処理ユニットを含み回路構成情報に応じた前記処理ユニットによりプログラマブル論理回路を再構成する処理装置の制御方法であって、

第1の処理に応じた第1の回路構成情報により構築される論理回路に含まれる前記処理ユニット内の情報保持部に、前記第1の処理に関連し前記第1の処理の次に実施される第2の処理に応じた第2の回路構成情報を格納して前記第1の処理を実行させ、

前記第1の処理の終了に応じて、前記情報保持部から取得した前記第2の回路構成情報により前記プログラマブル論理回路を再構成して前記第2の処理に応じた論理回路を構築すること、

を特徴とする処理装置の制御方法。40

**【発明の詳細な説明】****【技術分野】****【0001】**

処理装置、及び処理装置の制御方法に関する。

**【背景技術】****【0002】**

従来、論理構造をプログラマブルに変更可能な論理回路を有する半導体装置が提案されている（例えば、特許文献1参照）。論理回路は、複数の演算器を有している。論理回路は、半導体装置に含まれる制御回路（例えばCPU）によって設定される構成情報に従つて演算器を接続する。論理回路は、演算器の接続、つまり構成情報に応じた論理構造を構

成すると、終了フラグを出力する。制御回路は、終了フラグに応じて論理回路に対して演算の実行を指示する。そして、論理回路は、指示に応じて処理を実行し、処理を終了すると終了フラグを出力する。制御回路は、その終了フラグに応じて、次の構成情報を論理回路に設定する。このように、論理回路が処理を終了する毎に次の構成情報を設定する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001-68993号公報

【発明の概要】

【発明が解決しようとする課題】

10

【0004】

ところで、制御回路は、論理回路における処理の終了に応じた終了フラグに応じて構成情報をその論理回路に設定する。このため、論理回路において、複数の処理を実行させると、全ての処理が終了しなければ次の構成情報を設定することができない。このような論理回路における構成情報の設定は、処理時間の短縮を妨げる要因となる。

【課題を解決するための手段】

【0005】

本発明の一観点によれば、複数の処理ユニットを含み回路構成情報に応じた前記処理ユニットにより論理回路を再構成するプログラマブル論理回路を有する処理装置であって、第1の処理に応じた第1の回路構成情報により構築される論理回路に含まれる前記処理ユニット内の情報保持部に、前記第1の処理に関連し前記第1の処理の次に実施される第2の処理に応じた第2の回路構成情報を格納し、前記第1の処理の実行制御信号を出力する第1の制御回路と、前記第1の処理の終了に応じて、前記情報保持部から取得した前記第2の回路構成情報により前記プログラマブル論理回路の再構成を制御する第2の制御回路とを有する。

20

【発明の効果】

【0006】

本発明の一観点によれば、処理時間の短縮を図ることができる。

【図面の簡単な説明】

【0007】

30

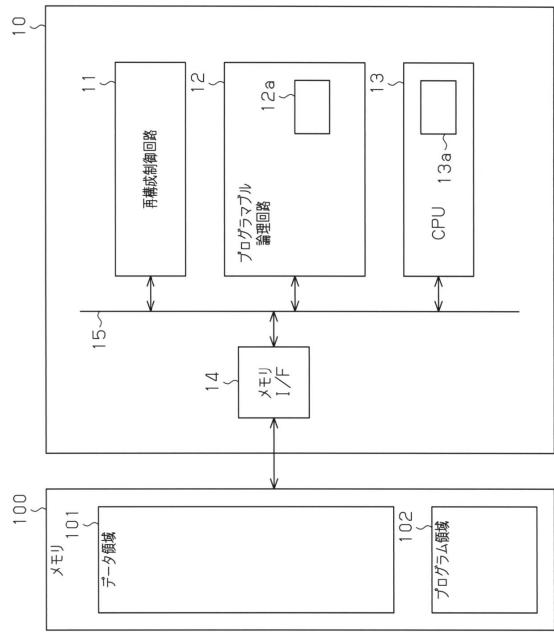

【図1】半導体装置及びメモリの概略ブロック回路図である。

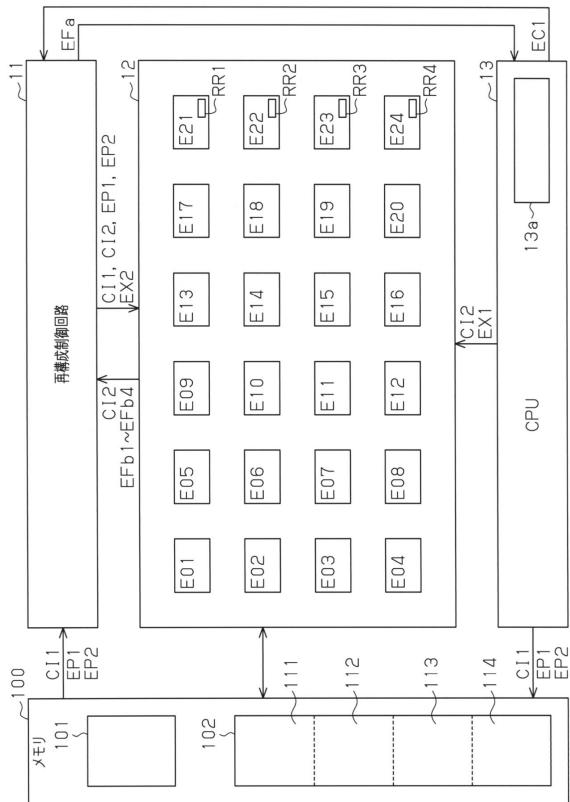

【図2】半導体装置及びメモリの概略動作を説明するためのブロック回路図である。

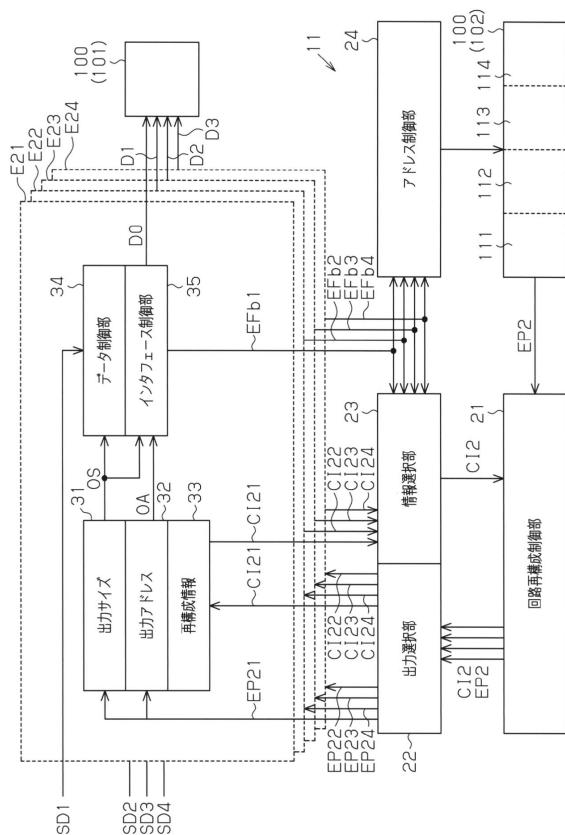

【図3】出力インターフェース部、再構成制御部のブロック回路図である。

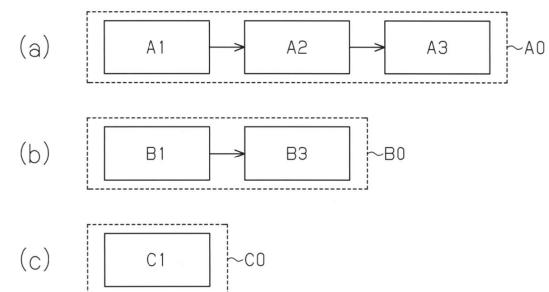

【図4】(a)～(c)は処理の一例を示す説明図である。

【図5】プログラマブル論理回路の再構成の説明図である。

【図6】プログラマブル論理回路の再構成の説明図である。

【図7】プログラマブル論理回路の再構成の説明図である。

【図8】再構成処理のフローチャートである。

【図9】再構成処理のフローチャートである。

【図10】再構成処理のフローチャートである。

40

【図11】(a)は半導体装置の動作を示すタイミング図、(b)は比較例の動作を示すタイミング図である。

【発明を実施するための形態】

【0008】

以下、一実施形態を添付図面に従って説明する。

図1に示すように、処理装置10は、再構成制御回路11、プログラマブル論理回路12、中央演算処理装置(以下、CPU)13、メモリインターフェース(「メモリI/F」と表記)14を有し、それらはバス15を介して互いに通信可能に接続されている。

【0009】

メモリインターフェース14は、メモリ100と接続される。メモリ100は、例えばダ

50

イナミックランダムアクセスメモリ( D R A M )である。再構成制御回路 1 1 、プログラマブル論理回路 1 2 、 C P U 1 3 は、バス 1 5 とメモリインターフェース 1 4 を介してメモリ 1 0 0 をアクセスする。

#### 【 0 0 1 0 】

C P U 1 3 はメモリ 1 3 a を有している。メモリ 1 3 a は不揮発性メモリである。メモリ 1 3 a には、 C P U 1 3 が実行するプログラムデータが格納されている。 C P U 1 3 は、メモリ 1 3 a に格納されたプログラムデータに従って処理を順次実行する。 C P U 1 3 は、プログラマブル論理回路 1 2 にて実行する処理に応じた再構成情報を、メモリ 1 0 0 とプログラマブル論理回路 1 2 に格納する。 C P U 1 3 は第 1 の制御回路の一例である。

#### 【 0 0 1 1 】

再構成制御回路 1 1 は、プログラマブル論理回路 1 2 における論理回路の再構築を制御する。再構成制御回路 1 1 は、メモリ 1 0 0 に格納された再構成情報をプログラマブル論理回路 1 2 に設定する。また、再構成制御回路 1 1 は、プログラマブル論理回路 1 2 に格納された再構成情報を読み出し、その再構成情報をプログラマブル論理回路 1 2 に設定する。再構成制御回路 1 1 は第 2 の制御回路の一例である。

10

#### 【 0 0 1 2 】

プログラマブル論理回路 1 2 は、設定される再構成情報に応じた論理回路を構築する機能を有している。プログラマブル論理回路 1 2 は、複数の論理回路を構築可能である。また、プログラマブル論理回路 1 2 は、1つの論理回路の動作中に、別の複数の論理回路の再構築が可能である。論理回路は例えば演算回路である。プログラマブル論理回路 1 2 は、再構成情報を保持する情報保持部 1 2 a を有している。プログラマブル論理回路 1 2 は、複数の処理ユニットを有している。プログラマブル論理回路 1 2 は、再構成情報に応じて、複数の処理ユニットを互いに接続して論理回路を構築する。

20

#### 【 0 0 1 3 】

再構成情報は、回路構成情報と動作パラメータを含む。回路構成情報は例えば、構築する論理回路に含める処理ユニットを指定するためのユニット情報と、2つの処理ユニットの間及び処理ユニットと外部回路の間を接続するための接続情報を含む。動作パラメータは、構築した論理回路の動作のための初期値や、設定値を含む。設定値は、例えば処理ユニットが行う処理に必要なデータの構成を示す値( 例えばビット数 ) や、処理により生成するデータの量、である。

30

#### 【 0 0 1 4 】

C P U 1 3 は、メモリ 1 0 0 のプログラム領域 1 0 2 とプログラマブル論理回路 1 2 の情報保持部 1 2 a に回路構成情報を設定する。また、 C P U 1 3 は、メモリ 1 0 0 のプログラム領域 1 0 2 に、プログラマブル論理回路 1 2 の動作に必要な動作パラメータを設定する。

#### 【 0 0 1 5 】

再構成制御回路 1 1 は、プログラマブル論理回路 1 2 における論理回路の再構築を制御する。再構成制御回路 1 1 は、 C P U 1 3 の指示に従って、メモリ 1 0 0 のプログラム領域 1 0 2 に格納された回路構成情報と動作パラメータを読み出し、その回路構成情報と動作パラメータをプログラマブル論理回路 1 2 に設定する。プログラマブル論理回路 1 2 は、設定された回路構成情報に応じた論理回路を構築する。この論理回路は、設定された動作パラメータに基づいて、メモリ 1 0 0 のデータ領域 1 0 1 から読み出したデータ( リードデータ ) を処理し、処理後のデータ( ライトデータ ) をデータ領域 1 0 1 に格納する。そして、論理回路は、処理終了フラグ出力する。

40

#### 【 0 0 1 6 】

また、再構成制御回路 1 1 は、プログラマブル論理回路 1 2 から出力される処理終了フラグに基づいて、プログラマブル論理回路 1 2 の情報保持部 1 2 a に格納された回路構成情報を読み出し、メモリ 1 0 0 のプログラム領域 1 0 2 に格納された動作パラメータを読み出す。そして、再構成制御回路 1 1 は、回路構成情報及び動作パラメータをプログラマブル論理回路 1 2 に設定する。上記と同様に、プログラマブル論理回路 1 2 は、設定され

50

た回路構成情報に応じた論理回路を構築する。この論理回路は、設定された動作パラメータに基づいて、メモリ100のデータ領域101から読み出したデータ(リードデータ)を処理し、処理後のデータ(ライトデータ)をデータ領域101に格納する。

#### 【0017】

図2は、プログラマブル論理回路12の構成例と、再構成制御回路11、プログラマブル論理回路12、CPU13、及びメモリ100の間の各種信号の授受を説明するものである。なお、図2では、図1に示すメモリインターフェース14及びバス15を省略している。

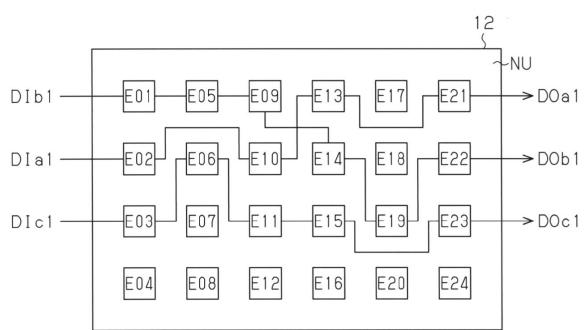

#### 【0018】

プログラマブル論理回路12は、複数(図2では24個)の処理ユニットE00～E23と接続部NUを有している。処理ユニットE01～E20は例えば演算器である。処理ユニットE21～E24は例えば出力インターフェース部である。以下の説明において、演算器E01～E20、出力インターフェース部E21～E24を用いる場合がある。

10

#### 【0019】

接続部NUは、回路構成情報に従って、回路構成情報に応じた処理ユニットを互いに接続する。また、接続部NUは、回路構成情報に応じた処理ユニットを図1に示すバス15に接続する。例えば、図5に示すように、接続部NUは、第1の回路構成情報に応じて、処理ユニットE01と処理ユニットE05の間を接続する。同様に接続部NUは、第1の回路構成情報に応じて、処理ユニットE05～E09、処理ユニットE09～E14、処理ユニットE14～E19、処理ユニットE19～E22を接続する。また、接続部NUは、第1の回路構成情報に応じて、処理ユニットE01、E22を図1に示すバス15に接続する。

20

#### 【0020】

また、接続部NUは、第2の回路構成情報に応じて、処理ユニットE02～E10～E13～E21を接続するとともに、処理ユニットE02、E21を図1に示すバス15に接続する。また、接続部NUは、第3の回路構成情報に応じて、処理ユニットE03～E06～E11～E15～E23を接続するとともに、処理ユニットE03、E23を図1に示すバス15に接続する。

#### 【0021】

処理ユニットE21は、情報保持部RR1を有している。同様に、処理ユニットE22～E24は、情報保持部RR2～RR4を有している。これらの情報保持部RR1～RR4は、図1に示す情報保持部12aの一例である。

30

#### 【0022】

処理ユニットE21～E24は例えば出力インターフェース部である。プログラマブル論理回路12において再構築される論理回路はデータをプログラマブル論理回路12の外部に出力するため、少なくとも1つの出力インターフェース部、つまり処理ユニットE21～E24を含む。

#### 【0023】

メモリ100のプログラム領域102は、情報保持部RR1～RR4を含む処理ユニットE21～E24に対応する4つのメモリ領域111～114を含む。CPU13は、各メモリ領域111～114に、プログラマブル論理回路12にて最初に実施する処理のための回路構成情報CI1を格納する。また、CPU13は、各メモリ領域111～114に、対応する処理ユニットE01～E24を利用する処理のための動作パラメータEP1、EP2を設定する。

40

#### 【0024】

CPU13は、各処理ユニットE21～E24の情報保持部RR1～RR4に、各処理ユニットE21～E24を利用する処理の次に実行する処理のための回路構成情報CI2を設定する。

#### 【0025】

CPU13は、再構成制御回路11に対して再構成制御信号EC1を出力する。

50

再構成制御回路 11 は、再構成制御信号 E C 1 に応答してプログラマブル論理回路 12 に対する最初の処理のための再構成処理を行う。この再構成処理において、再構成制御回路 11 は、先ずメモリ領域 111～114 に格納された最初の処理のための回路構成情報 C I 1 を各メモリ領域 111～114 から読み出し、この回路構成情報 C I 1 をプログラマブル論理回路 12 に出力する。プログラマブル論理回路 12 は、回路構成情報 C I 1 に応じた論理回路を再構成する。

#### 【0026】

次に、再構成制御回路 11 は、メモリ領域 111～114 に格納された最初の処理のための動作パラメータ E P 1 を各メモリ領域 111～114 から読み出し、この動作パラメータ E P 1 をプログラマブル論理回路 12 に出力する。プログラマブル論理回路 12 は、10 供給される動作パラメータ E P 1 を対応する処理ユニットに設定する。

#### 【0027】

そして、再構成制御回路 11 は、プログラマブル論理回路 12 における再構成処理を終了し、終了フラグ E F a を出力する。

C P U 13 は、再構成制御回路 11 から出力される終了フラグ E F a に応答して、プログラマブル論理回路 12 に実行制御信号 E X 1 を出力する。

#### 【0028】

プログラマブル論理回路 12 は、実行制御信号 E X 1 に応答して、構築した各論理回路を起動する。各論理回路は、動作パラメータ E P 1 に基づいて、メモリ 100 のデータ領域 101 の処理データを読み出し、その処理データに対して所定の処理（例えば、演算処理）を実施する。そして、実行中の論理回路に含まれる処理ユニット E 21～E 24 は、20 処理後のデータを、動作パラメータ E P 1 に応じたメモリ 100 の領域に格納する。

#### 【0029】

各処理ユニット E 21～E 24 は、それが含まれる論理回路の処理に従って終了フラグ（E F b 1～E F b 4）を出力する。

再構成制御回路 11 は、終了フラグ E F b 1～E F b 4 を受け、処理を終了した論理回路を判定する。再構成制御回路 11 は、処理を終了した論理回路に含まれる処理ユニットの情報保持部 R R 1～R R 4 から次に実行する処理のための回路構成情報 C I 2 を読み出す。また、再構成制御回路 11 は、次に実行する処理のための動作パラメータ E P 2 を対応するメモリ領域 111～114 から読み出す。そして、再構成制御回路 11 は、情報保持部 R R 1～R R 4 から読み出した回路構成情報 C I 2 とメモリ領域から読み出した動作パラメータ E P 2 をプログラマブル論理回路 12 に出力する。プログラマブル論理回路 12 は、回路構成情報 C I 2 に応じた論理回路を再構成し、論理回路に含まれる処理ユニットに動作パラメータ E P 2 を設定する。30

#### 【0030】

そして、再構成制御回路 11 はプログラマブル論理回路 12 に実行制御信号 E X 2 を出力する。

プログラマブル論理回路 12 は、実行制御信号 E X 2 に応答して、構築した各論理回路を起動する。各論理回路は、動作パラメータ E P 2 に基づいて、メモリ 100 のデータ領域 101 の処理データを読み出し、その処理データに対して所定の処理（例えば、演算処理）を実施する。そして、実行中の論理回路に含まれる処理ユニット E 21～E 24 は、40 処理後のデータを、動作パラメータ E P 1 に応じたメモリ 100 の領域に格納する。

#### 【0031】

上記したように、終了フラグ E F b 1～E F b 4 は、処理を終了した論理回路に含まれる処理ユニット E 21～E 24 から出力される。再構成制御回路 11 は、この終了フラグ E F b 1～E F b 4 に基づいて、次の処理のための回路構成情報 C I 2 を、処理を終了した論理回路に含まれる処理ユニットから読み出す。また、再構成制御回路 11 は、処理が終了した論理回路の処理ユニット E 21～E 24 に対応するメモリ領域 111～114 から動作パラメータ E P 2 を読み出す。そして、再構成制御回路 11 は、回路構成情報 C I 2 及び動作パラメータ E P 2 を、プログラマブル論理回路 12 に供給し、プログラマブル50

論理回路 1 2 を再構築する。

**【 0 0 3 2 】**

従って、プログラマブル論理回路 1 2において処理を実行中の論理回路があつても、別の論理回路の再構築し、その再構築した論理回路における処理の実行が可能となる。このため、プログラマブル論理回路 1 2において再構築された複数の論理回路の全ての処理が終了した後に次の処理のための論理回路を再構築する場合と比べ、プログラマブル論理回路 1 2 に含まれる処理ユニットを有効に使用することができる。そして、連続的に実施する複数の処理における待ち時間を少なくし、プログラマブル論理回路 1 2 船体における処理時間を短縮することができる。

**【 0 0 3 3 】**

10

図 3 は、再構成制御回路 1 1 と処理ユニット E 2 1 ~ E 2 4 (出力インターフェース部 E 2 1 ~ E 2 4) の構成例を説明するものである。なお、出力インターフェース部 E 2 1 ~ E 2 4 は互いに同じ構成であるため、出力インターフェース部 E 2 1 について主に説明し、出力インターフェース部 E 2 2 ~ E 2 4 の説明の一部を省略する。また、図 3 において、出力インターフェース部 E 2 2 ~ E 2 4 に含まれる部材を省略する。なお、図 3 では、図 1 に示すメモリインターフェース 1 4 及びバス 1 5 を省略している。

**【 0 0 3 4 】**

出力インターフェース部 E 2 1 は、レジスタ 3 1 ~ 3 3 、データ制御部 3 4 、インターフェース制御部 3 5 を有している。

第 1 のレジスタ 3 1 と第 2 のレジスタ 3 2 は、出力インターフェース部 E 2 1 の動作パラメータを格納するために設けられている。例えば、第 1 のレジスタ 3 1 に格納される動作パラメータは出力サイズであり、第 2 のレジスタ 3 2 に格納される動作パラメータは出力アドレスである。出力サイズは、メモリ 1 0 0 に対して 1 回の転送より転送するデータの量であり、出力アドレスはデータを書き込む領域を指定するものである。第 3 のレジスタ 3 3 は、回路構成情報 C I 2 を格納するために設けられている。レジスタ 3 1 ~ 3 3 は、情報保持部 R R 1 の一例である。尚、図示しないが、出力インターフェース部 E 2 2 ~ E 2 4 は同様にレジスタ 3 1 ~ 3 3 をそれぞれ有し、これらのレジスタ 3 1 ~ 3 3 は情報保持部 R R 2 ~ R R 4 の一例である。

20

**【 0 0 3 5 】**

データ制御部 3 4 には、この出力インターフェース部 E 2 1 に接続された処理ユニットの出力データ S D 1 が供給される。データ制御部 3 4 は、出力データ S D 1 のデータ量を監視し、最初のデータ到着を意味する制御信号をインターフェース制御部 3 5 に出力し、更にデータ量が出力サイズ分に達した時点で終了を意味する制御信号をインターフェース制御部 3 5 に出力する。

30

**【 0 0 3 6 】**

インターフェース制御部 3 5 は、データ制御部 3 4 から出力される制御信号に応答して、レジスタ 3 1 の出力サイズ O S とレジスタ 3 2 の出力アドレス O A に基づいて、データ制御部 3 4 に保持された出力データ D 0 をメモリ 1 0 0 に出力する。これにより、データ制御部 3 4 のデータが、出力アドレスにて指定されるメモリ 1 0 0 のデータ領域 1 0 1 に格納される。

40

**【 0 0 3 7 】**

また、インターフェース制御部 3 5 は、メモリ 1 0 0 に対してデータを出力すると、終了フラグ E F b 1 を出力する。同様に、各出力インターフェース部 E 2 2 ~ E 2 4 のインターフェース制御部は、出力データ S D 2 ~ S D 4 に応じたデータ D 1 ~ D 3 をメモリ 1 0 0 に対して出力し、終了フラグ E F b 2 ~ E F b 4 を出力する。

**【 0 0 3 8 】**

再構成制御回路 1 1 は、回路再構成制御部 2 1 、出力選択部 2 2 、情報選択部 2 3 、アドレス制御部 2 4 を含む。

アドレス制御部 2 4 は、終了フラグ E F b 1 ~ E F b 4 に基づいて、処理を終了した出力インターフェース部 E 2 1 ~ E 2 4 に対応するメモリ領域 1 1 1 ~ 1 1 4 をアクセスする

50

ためのアドレスを決定する。プログラマブル論理回路12にて実行する処理にて利用される出力インタフェース部E21～E24と処理の順番は予め決定されている。例えば、プログラマブル論理回路12が実行する処理に従ってポインタを変更し、そのポインタと終了フラグEFb1～EFb4にしたがってアドレスを決定する。そして、アドレス制御部24は、決定したアドレスをメモリ100に出力する。メモリ100は、アドレス制御部24から供給されるアドレスに基づいて、対応するメモリ領域111～114の動作パラメータを出力する。

#### 【0039】

情報選択部23は、終了フラグEFb1～EFb4に基づいて、処理を終了した出力インタフェース部を判定し、判定結果に基づいて処理を終了した出力インタフェース部のレジスタ33から回路構成情報を読み出す。例えば、情報選択部23は終了フラグEFb1に基づいて出力インタフェース部E21のレジスタ33から回路構成情報CI21を読み出す。同様に、情報選択部23は、終了フラグEFb2～EFb4に基づいて、出力インタフェース部E22～E24のレジスタから回路構成情報CI22～CI24を読み出す。そして、情報選択部23は、レジスタから読み出した回路構成情報を回路再構成制御部21に出力する。なお、図3では、回路構成情報CI21～CI24の何れか1つをしめすために「CI2」を用いている。なお、動作パラメータEP2についても同様である。

10

#### 【0040】

回路再構成制御部21は、回路構成情報CI2と動作パラメータEP2を出力選択部22に出力する。出力選択部22は、回路構成情報CI2をプログラマブル論理回路12に出力する。プログラマブル論理回路12は、回路構成情報CI2に応じた論理回路を構築する。出力選択部22は、回路構成情報CI2に基づいて、次に動作する処理ユニットに動作パラメータEP2を設定する。

20

#### 【0041】

例えば、回路構成情報CI2に基づいて、次に実行する論理回路は出力インタフェース部E21を含む。この場合、出力選択部22は、出力インタフェース部E21のレジスタ31, 32に動作パラメータEP21を設定する。同様に、次に実行する論理回路に出力インタフェース部E22～E24が含まれる場合、出力選択部22は、出力インタフェース部E22～E24のレジスタに動作パラメータEP22～EP24を設定する。

30

#### 【0042】

したがって、再構成制御回路11は、回路構成情報CI2と動作パラメータEP2に基づいて、次に処理を実行する論理回路の再構成を制御する。回路構成情報CI2は、再構成する論理回路に含まれる処理ユニットを指定する情報（ユニット番号）が含まれる。再構成制御回路11は、回路構成情報CI2をプログラマブル論理回路12に出力する。また、再構成制御回路11は、プログラマブル論理回路12において再構成される論理回路に含まれる処理ユニットに動作パラメータEP2を設定する。

#### 【0043】

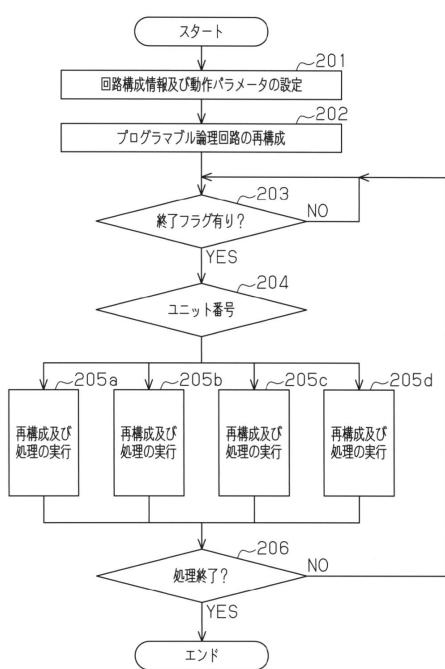

次に、プログラマブル論理回路12に対する再構成処理の流れを説明する。なお、処理の説明において用いる部材等は、上記の図1～図4を参照されたい。

図8に示すように、先ず、ステップ201において、CPU13は、プログラマブル論理回路12と図1に示すメモリ100に対して、回路構成情報を及び動作パラメータを設定する。そして、CPU13は、再構成制御信号EC1を出力する。

40

#### 【0044】

次に、ステップ202において、再構成制御回路11は、再構成制御信号EC1に応答してプログラマブル論理回路12を再構成し、終了フラグEFaを出力する。CPU13は、その終了フラグEFaに応答して実行制御信号EX1を出力し、プログラマブル論理回路12を起動する。

#### 【0045】

次に、ステップ203において、再構成制御回路11は、終了フラグEFb1～EFb4があるか否かを判定する。終了フラグEFb1～EFb4がない（出力されていない）

50

場合、ステップ203へ移行し、終了フラグE F b 1 ~ E F b 4がある（出力されている）場合、次のステップ204へ移行する。

#### 【0046】

ステップ204において、再構成制御回路11は、終了フラグE F b 1 ~ E F b 4を出力する出力インターフェース部のユニット番号に応じて、ステップ205a~205dの処理を実行する。例えば、終了フラグが出力インターフェース部E21から出力される場合、ステップ205aの処理を実行する。同様に、終了フラグが出力インターフェース部E22~E24から出力される場合、ステップ205b~205dの処理を実行する。

#### 【0047】

ステップ205aにおいて、再構成制御回路11は、図2に示す処理ユニットE21（出力インターフェース部E21）のレジスタ33から読み出した回路構成情報C I 2 1と、終了フラグに応じてメモリ領域111（図2参照）から出力される動作パラメータE P 2 1に基づいてプログラマブル論理回路12を再構成する。そして、再構成制御回路11は、プログラマブル論理回路12において再構成した論理回路を起動する。

#### 【0048】

ステップ205bにおいて、再構成制御回路11は、図2に示す処理ユニットE22（出力インターフェース部E22）のレジスタから読み出した回路構成情報C I 2 2と、終了フラグに応じてメモリ領域112（図2参照）から出力される動作パラメータE P 2 2に基づいてプログラマブル論理回路12を再構成する。そして、再構成制御回路11は、プログラマブル論理回路12において再構成した論理回路を起動する。

10

#### 【0049】

ステップ205cにおいて、再構成制御回路11は、図2に示す処理ユニットE23（出力インターフェース部E23）のレジスタから読み出した回路構成情報C I 2 3と、終了フラグに応じてメモリ領域113（図2参照）から出力される動作パラメータE P 2 3に基づいてプログラマブル論理回路12を再構成する。そして、再構成制御回路11は、プログラマブル論理回路12において再構成した論理回路を起動する。

20

#### 【0050】

ステップ205dにおいて、再構成制御回路11は、図2に示す処理ユニットE24（出力インターフェース部E24）のレジスタから読み出した回路構成情報C I 2 4と、終了フラグに応じてメモリ領域114（図2参照）から出力される動作パラメータE P 2 4に基づいてプログラマブル論理回路12を再構成する。そして、再構成制御回路11は、プログラマブル論理回路12において再構成した論理回路を起動する。

30

#### 【0051】

次に、ステップ206において、再構成制御回路11は、全ての論理回路を実行したか否かを判定する。実行する論理回路がある場合、ステップ203へ移行し、全ての論理回路を実行した場合、処理を終了する。

#### 【0052】

ここで、プログラマブル論理回路12において実施する処理を説明する。

図4(a)に示すように、処理A0は、処理A1と処理A2と処理A3を含む。例えば、処理A1は、図1に示すメモリ100のデータ領域101から読み出したデータを処理し、処理後のデータをデータ領域101に格納する。処理A2は、処理A1によってデータ領域101に格納されたデータを読み出し、そのデータを処理してデータ領域101に格納する。処理A3は、処理A1によってデータ領域101に格納されたデータを読み出し、そのデータを処理してデータ領域101に格納する。したがって、これらの処理A1~A3の実行順序は矢印で示すように、先ず処理A1を実行し、次に処理A2を実行し、最後に処理A3を実行する。

40

#### 【0053】

図4(b)に示すように、処理B0は、処理B1と処理B2を含む。例えば、処理B1は、図1に示すメモリ100のデータ領域101から読み出したデータを処理し、処理後のデータをデータ領域101に格納する。処理B2は、処理B1によってデータ領域10

50

1に格納されたデータを読み出し、そのデータを処理してデータ領域101に格納する。したがって、これらの処理B1, B2の実行順序は矢印で示すように、先ず処理B1を実行し、次に処理B2を実行する。

#### 【0054】

図4(a)に示すように、処理C0は、処理C1を含む。例えば、処理C1は、図1に示すメモリ100のデータ領域101から読み出したデータを処理し、処理後のデータをデータ領域101に格納する。

#### 【0055】

なお、上記の処理A0(A1~A3), B0(B1, B2), C0(C1)は演算処理である。このため、各処理A0(A1~A3), B0(B1, B2), C0(C1)を演算A0(A1~A3), B0(B1, B2), C0(C1)として説明する場合がある。

10

#### 【0056】

次に、再構成情報によりプログラマブル論理回路12に構築する論理回路の一例を説明する。

例えば、図2に示すプログラマブル論理回路12において、図4(a)~図4(c)に示す各処理を実行するための論理回路を構築する。

#### 【0057】

例えば、図4(a)に示す処理A1は、図5に示す処理ユニットE02-E10-E13-E21を含む論理回路により実施される。したがって、処理A1に対応する再構成情報(回路構成情報)は、各処理ユニットE02, E10, E13, E21を示すユニット番号と、処理ユニットE02, E10, E13, E21を接続する接続情報を含む。処理ユニットE02には、処理A1に必要なデータDIa1が供給される。そして、処理ユニットE21は、処理A1の処理結果であるデータDOa1を出力する。

20

#### 【0058】

図4(b)に示す処理B1は、図5に示す処理ユニットE01-E05-E09-E14-E19-E22を含む論理回路により実施される。処理B1に対応する再構成情報(回路構成情報)は、各処理ユニットE01, E05, E09, E14, E19, E22のユニット番号と接続情報を含む。処理ユニットE01には、処理B1に必要なデータDIb1が供給される。処理ユニットE22は、処理B1の処理結果であるデータDOB1を出力する。

30

#### 【0059】

図4(c)に示す処理C1は、図5に示す処理ユニットE03-E06-E11-E15-E23を含む論理回路により実施される。処理C1に対応する再構成情報(回路構成情報)は、各処理ユニットE03, E06, E11, E15, E23のユニット番号と接続情報を含む。処理ユニットE03には、処理C1に必要なデータDIc1が供給される。処理ユニットE23は、処理C1の処理結果であるデータDOC1を出力する。

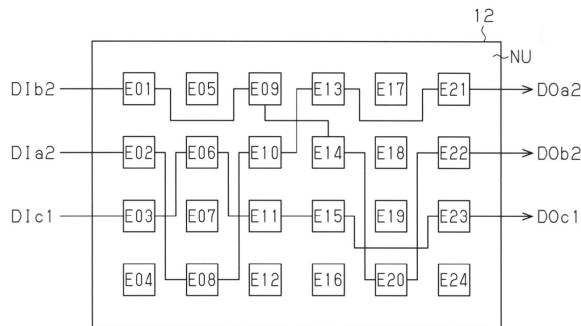

#### 【0060】

図4(a)に示す処理A2は、図6に示す処理ユニットE02-E08-E10-E13-E21を含む論理回路により実施される。したがって、処理A2に対応する再構成情報(回路構成情報)は、各処理ユニットE02, E08, E10, E13, E21のユニット番号と接続情報を含む。処理ユニットE02には、処理A2に必要なデータDIa2が供給される。そして、処理ユニットE21は、処理A2の処理結果であるデータDOa2を出力する。

40

#### 【0061】

図4(b)に示す処理B2は、図6に示す処理ユニットE01-E09-E14-E20-E22を含む論理回路により実施される。処理B2に対応する再構成情報(回路構成情報)は、各処理ユニットE01, E09, E14, E20, E22のユニット番号と接続情報を含む。処理ユニットE01には、処理B2に必要なデータDIb2が供給される。処理ユニットE22は、処理B2の処理結果であるデータDOB2を出力する。

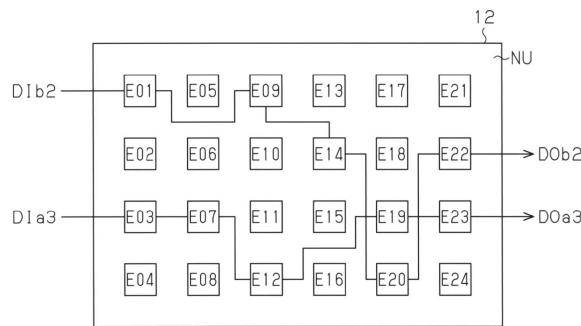

#### 【0062】

図4(a)に示す処理A3は、図7に示す処理ユニットE03-E07-E12-E19-E23を含む論理回路により実施される。したがって、処理A3に対応する再構成情報(回路構成情報)は、各処理ユニットE03,E07,E12,E19,E23を示すユニット番号と接続情報を含む。処理ユニットE03には、処理A3に必要なデータDIA3が供給される。そして、処理ユニットE23は、処理A3の処理結果であるデータDOA3を出力する。

#### **【0063】**

次に、回路構成情報及び動作パラメータの設定処理の一例を説明する。

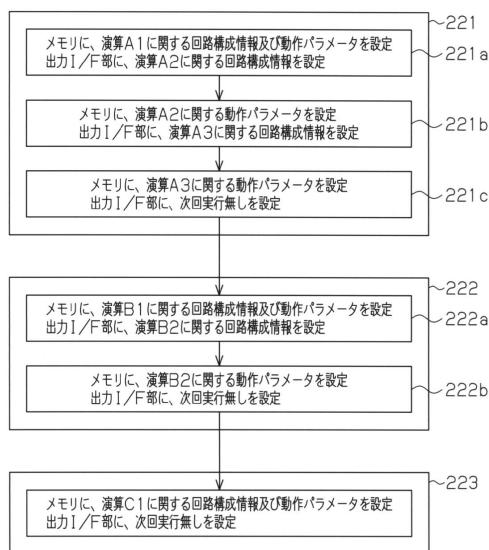

図9に示すステップ221~223は、図8に示すステップ201のサブステップである。

10

#### **【0064】**

先ず、ステップ221において、図4(a)に示す処理A0の再構成情報を設定する。即ち、ステップ221aにおいて、メモリ100に演算A1に関する回路構成情報及び動作パラメータを設定する。そして、演算A1において使用する出力インターフェース部E21のレジスタ33に、演算A2に関する回路構成情報を設定する。次いで、ステップ221bにおいて、メモリ100に演算A2に関する動作パラメータを設定する。そして、演算A1において使用する出力インターフェース部E21のレジスタ33に、演算A3に関する回路構成情報を設定する。次いで、ステップ221cにおいて、メモリ100に演算A3に関する動作パラメータを設定する。そして、演算A3において使用する出力インターフェース部E21のレジスタ33に「次回実行無し」を設定する。

20

#### **【0065】**

次に、ステップ222において、図4(b)に示す処理B0の再構成情報を設定する。即ち、ステップ222aにおいて、メモリ100に演算B1に関する回路構成情報及び動作パラメータを設定する。そして、演算B1において使用する出力インターフェース部E22のレジスタ33に、演算B2に関する回路構成情報を設定する。次いで、ステップ222bにおいて、メモリ100に演算B2に関する動作パラメータを設定する。そして、演算B2において使用する出力インターフェース部E22のレジスタ33に「次回実行無し」を設定する。

#### **【0066】**

次に、ステップ223において、図4(c)に示す処理C0の再構成情報を設定する。即ち、ステップ223aにおいて、メモリ100に演算C1に関する回路構成情報及び動作パラメータを設定する。そして、演算C1において使用する出力インターフェース部E21のレジスタ33に「次回実行無し」を設定する。

30

#### **【0067】**

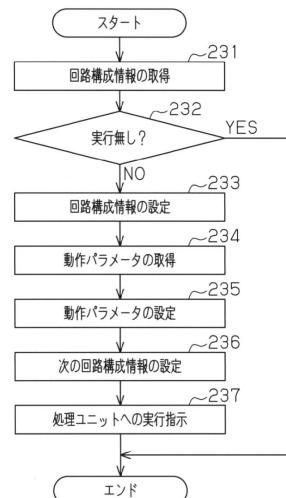

次に、出力インターフェース部E21~E24に対する処理の一例を説明する。なお、各出力インターフェース部E21~E24に対する処理は互いに同じであるため、出力インターフェース部E21に対する処理を説明する。

#### **【0068】**

図10に示すステップ231~237は、図8に示すステップ205aのサブステップである。

40

先ず、ステップ231において、次に構築する論理回路のための回路構成情報を図3に示すレジスタ33から取得する。そして、ステップ232において、実行無しが設定されているか否かを判定する。レジスタ33に実行無しが設定されている場合、この処理を終了する。一方、レジスタ33に次の回路構成情報が設定されている場合、次のステップ233へ移行する。

#### **【0069】**

ステップ233において、回路構成情報をプログラマブル論理回路12に設定する。これにより、次に処理を実行する論理回路が構築される。

次に、ステップ234において、図3に示すメモリ領域111から動作パラメータを取得し、ステップ235において、構築した論理回路に含まれる処理ユニットに対して動作

50

パラメータを設定する。

**【0070】**

次に、ステップ236において、次の回路構成情報を出力インターフェース部のレジスタに設定する。このとき、ステップ233において構築した論理回路に含まれる出力インターフェース部のレジスタ33に、次に処理を実行する論理回路のための回路構成情報を格納する。

**【0071】**

例えば、所定の処理は、n回(1~n)の再構成処理により構築する論理回路によって実施される。そして、上記のステップ233において、m回目(1~m < n)の再構成処理によって論理回路が構築される。この場合、ステップ236では、m+1回目以降の再構成処理に用いられる回路構成情報が、m回目の論理回路に含まれる出力インターフェース部のレジスタ33に格納される。10

**【0072】**

次に、ステップ237において、構築した論理回路に含まれる処理ユニットに対し、実行を指示する。

次に、処理装置10の作用を説明する。

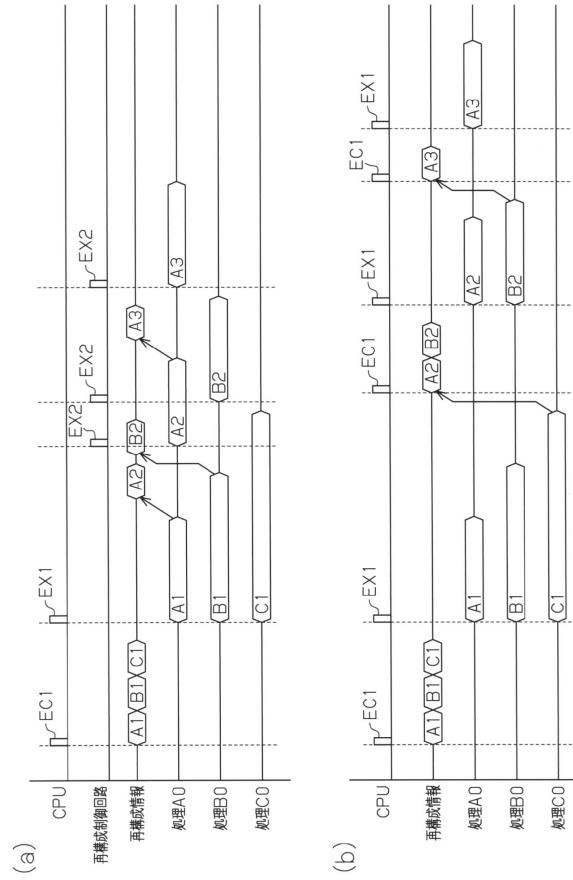

**【0073】**

図11(a)に示すように、CPU13は、再構成制御信号EC1を出力する。再構成制御回路11は、再構成制御信号EC1に応答して処理A1, B1, C1の再構成情報をプログラマブル論理回路12に設定する。プログラマブル論理回路12は、設定された再構成情報に応じた論理回路を構築する。次に、CPU13が実行制御信号EX1を出力する。プログラマブル論理回路12に構築された複数の論理回路は、それぞれ処理A1, B1, C1を実行する。20

**【0074】**

先ず、処理A1が終了すると、再構成制御回路11は、次の処理A2の再構成情報をプログラマブル論理回路12に設定する。プログラマブル論理回路12は、設定された再構成情報に応じた論理回路を構築する。そして、再構成制御回路11は、実行制御信号EX2を出力する。プログラマブル論理回路12に構築された論理回路は、処理A2を実行する。

**【0075】**

このとき、処理B1, C1は実行中である。このように、処理B1, C1の実行中に、次の処理A2の論理回路が構築され、その処理A2が実行される。

次に、処理B1が終了すると、再構成制御回路11は、次の処理B2の再構成情報をプログラマブル論理回路12に設定する。プログラマブル論理回路12は、設定された再構成情報に応じた論理回路を構築する。そして、再構成制御回路11は、実行制御信号EX2を出力する。プログラマブル論理回路12に構築された論理回路は、処理B2を実行する。

**【0076】**

次に、処理C1が終了すると、再構成制御回路11は、処理C1について次に実行する処理が無いため、処理C0に係る処理を終了する。40

先ず、処理A2が終了すると、再構成制御回路11は、次の処理A3の再構成情報をプログラマブル論理回路12に設定する。プログラマブル論理回路12は、設定された再構成情報に応じた論理回路を構築する。そして、再構成制御回路11は、実行制御信号EX2を出力する。プログラマブル論理回路12に構築された論理回路は、処理A3を実行する。

**【0077】**

次に、処理B2が終了すると、再構成制御回路11は、処理B2について次に実行する処理が無いため、処理B0に係る処理を終了する。

次に、処理A3が終了すると、再構成制御回路11は、処理A3について次に実行する処理が無いため、処理A0に係る処理を終了する。50

**【 0 0 7 8 】**

次に、比較例を説明する。なお、ここで説明する比較例は、CPUが複数の処理に係る再構成情報の設定を管理するものである。なお、同様の部材については上記の実施形態と同じ名称及び符号を用いて説明する。

**【 0 0 7 9 】**

図11(b)に示すように、CPU13は、再構成制御信号EC1を出力する。再構成制御回路11は、再構成制御信号EC1に応答して処理A1, B1, C1の再構成情報をプログラマブル論理回路12に設定する。プログラマブル論理回路12は、設定された再構成情報に応じた論理回路を構築する。次に、CPU13が実行制御信号EX1を出力する。プログラマブル論理回路12に構築された複数の論理回路は、それぞれ処理A1, B1, C1を実行する。10

**【 0 0 8 0 】**

先ず、処理A1が終了する。次に、処理B1が終了する。そして、処理C1が終了すると、プログラマブル論理回路12におけるすべての処理が終了する。このため、CPU13は、再構成制御信号EC1を出力し、再構成制御回路11は次の処理A2, B2の再構成情報をプログラマブル論理回路12に設定する。プログラマブル論理回路12は、設定された再構成情報に応じた論理回路を構築する。そして、CPU13は、実行制御信号EX1を出力する。プログラマブル論理回路12に構築された論理回路は、処理A2, B2を実行する。

**【 0 0 8 1 】**

次に、先ず処理A2が終了し、次いで処理B2が終了すると、CPU13は再構成制御信号EC1を出力し、再構成制御回路11は、次の処理A3の再構成情報をプログラマブル論理回路12に設定する。プログラマブル論理回路12は、設定された再構成情報に応じた論理回路を構築する。そして、CPU13は、実行制御信号EX1を出力する。プログラマブル論理回路12に構築された論理回路は、処理A3を実行する。20

**【 0 0 8 2 】**

次に、処理A3が終了すると、全ての処理を終了する。

このように、図11(a)に示す本実施形態は、図11(b)に示す比較例と比べ、処理A0, B0の処理に要する時間が短い。したがって、本実施形態は、処理時間を短縮することができる。30

**【 0 0 8 3 】**

以上記述したように、本実施形態によれば、以下の効果を奏する。

(1) プログラマブル論理回路12は、複数の処理ユニットE01～E24を有している。処理ユニットE01～E20は例えば演算器であり、処理ユニットE21～E24は出力インターフェース部である。処理ユニットE21～E24はそれぞれ情報保持部RR1～RR4を有している。

**【 0 0 8 4 】**

CPU13は、メモリ100のプログラム領域102に、最初に実行する処理の回路構成情報CI1と、各演算処理を実行するための動作パラメータEP1, EP2を格納する。また、CPU13は、次回以降に実行する処理の回路構成情報CI2を、前回の演算処理に用いられる処理ユニットE21～E24の情報保持部RR1～RR4に格納する。再構成制御回路11は、プログラマブル論理回路12から出力される終了フラグEFb1～EFb4に基づいて、処理を終了した処理ユニットE21～E24を選択し、その選択した処理ユニットE21～E24の情報保持部RR1～RR4に格納された回路構成情報CI2を取得する。そして、再構成制御回路11は、回路構成情報CI2をプログラマブル論理回路12に設定する。40

**【 0 0 8 5 】**

従って、他の処理B1, C1を実行しているときに、読み出した回路構成情報CI2に基づいて処理A2のための論理回路を構築することができる。このため、他の処理B1, C1の終了を待つことなく、次の処理A2が開始できるため、処理時間の短縮を図ること50

ができる。

**【0086】**

(2) 複数の処理ユニット E01 ~ E24 のうち、データを出力する処理ユニット E21 ~ E24 (出力インターフェース部 E21 ~ E24) は、回路構成情報を格納する情報保持部 RR1 ~ RR4 を含む。プログラマブル論理回路 12において実行する処理では、データの出力が必要である。従って、出力インターフェース部 E21 ~ E24 に情報保持部 RR1 ~ RR4 を含めることで、処理の終了に応じて次の処理のための回路構成情報を容易に取得することができる。

**【0087】**

尚、上記各実施形態は、以下の様で実施してもよい。

10

- ・上記実施形態のプログラマブル論理回路 12 にて実行する処理 A0 ~ C0 は、メモリ 100 から読み出したデータを処理したが、外部装置から供給されるデータを処理するようにしてもよい。

**【0088】**

また、処理後のデータをメモリ 100 に格納したが、処理後のデータを外部装置へ出力するようにしてもよい。

- ・上記実施形態に対し、同じ処理を複数回繰り返し実行するようにしてもよい。例えば、図 11 (a) において、処理 A1 を複数回繰り返し実行した後、処理 A2 を実行するようにしてもよい。

**【0089】**

20

- ・上記実施形態では、最初に複数の処理 A1, B1, C1 を実行するようにしたが、処理を開始するタイミングを適宜変更してもよい。例えば、3つの処理 A, B, C を実行する場合、先ず処理 A を実行し、処理 A の終了に応じて処理 A と処理 B を実行し、処理 A, B の終了に応じて処理 A ~ C を実行するようにしてもよい。このように必要な処理を順次実行することにより、パイプライン処理の実行が可能となる。

**【0090】**

- ・上記実施形態では、回路構成情報を保持する情報保持部 (レジスタ 33) を出力インターフェース部 E21 ~ E24 に含めたが、他の処理ユニット E01 ~ E20 に含めるようにしてもよい。

**【符号の説明】**

30

**【0091】**

10 処理装置

11 再構成制御回路

12 プログラマブル論理回路

13 CPU

E01 ~ E24 処理ユニット

RR1 ~ RR4 情報保持部

C11, C12 回路構成情報

100 メモリ

102 プログラム領域

111 ~ 114 メモリ領域

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

---

フロントページの続き

(56)参考文献 特開2013-030906(JP,A)

特開2001-068993(JP,A)

特開2003-198361(JP,A)

特開2009-182438(JP,A)

特表2007-510325(JP,A)

特開2013-013077(JP,A)

米国特許出願公開第2011/0216247(US,A1)

(58)調査した分野(Int.Cl., DB名)

H03K 19/098 - 19/23