(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6533470号

(P6533470)

(45) 発行日 令和1年6月19日(2019.6.19)

(24) 登録日 令和1年5月31日(2019.5.31)

(51) Int.Cl.

F 1

|            |           |            |

|------------|-----------|------------|

| GO6N 20/00 | (2019.01) | GO6N 20/00 |

| GO6F 3/06  | (2006.01) | GO6F 3/06  |

| GO6F 9/50  | (2006.01) | GO6F 9/50  |

301Z

150E

請求項の数 21 (全 57 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2016-248 (P2016-248)        |

| (22) 出願日     | 平成28年1月4日 (2016.1.4)          |

| (65) 公開番号    | 特開2016-126801 (P2016-126801A) |

| (43) 公開日     | 平成28年7月11日 (2016.7.11)        |

| 審査請求日        | 平成30年12月17日 (2018.12.17)      |

| (31) 優先権主張番号 | 62/099, 067                   |

| (32) 優先日     | 平成26年12月31日 (2014.12.31)      |

| (33) 優先権主張国  | 米国 (US)                       |

| (31) 優先権主張番号 | 14/877, 421                   |

| (32) 優先日     | 平成27年10月7日 (2015.10.7)        |

| (33) 優先権主張国  | 米国 (US)                       |

早期審査対象出願

|           |                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路 129<br>129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic<br>of Korea |

| (74) 代理人  | 110000051<br>特許業務法人共生国際特許事務所                                                                                                                                    |

| (72) 発明者  | チエインソク スティーブン<br>アメリカ合衆国 94063 カリフォルニア州 レッドウッドシティ メインストリート スイート 301, 333<br>最終頁に続く                                                                              |

(54) 【発明の名称】学習メカニズムを有する電子システム及びその動作方法並びに不揮発性コンピュータ読み取り可能ストレージ媒体

## (57) 【特許請求の範囲】

## 【請求項 1】

ストレージ装置とシステム装置との間の通信を提供するように構成されたストレージインターフェイスと、

前記ストレージ装置に含まれて前記ストレージインターフェイスに接続され、分散機械学習プロセスを実行するために、前記システム装置と前記ストレージ装置との間の前記ストレージインターフェイスの入出力の使用に基づいて、データを前記ストレージ装置によって処理される第1部分データと、前記システム装置によって処理される第2部分データとに分割する前処理ブロックを実行するように構成されたストレージコントロールユニットと、

前記分散機械学習プロセスの一部として前記第1部分データを処理するための学習ブロックと、を備えることを特徴とする電子システム。

## 【請求項 2】

前記ストレージコントロールユニットは、適応的な前処理ブロックを実行するように構成されることを特徴とする請求項1に記載の電子システム。

## 【請求項 3】

前記ストレージコントロールユニットは、プログラミングインターフェイスを実行するように構成されることを特徴とする請求項1に記載の電子システム。

## 【請求項 4】

前記ストレージコントロールユニットは、スケジュールブロックを実行するように構成

されることを特徴とする請求項 1 に記載の電子システム。

【請求項 5】

前記ストレージコントロールユニットは、選択ブロックを実行するように構成されることを特徴とする請求項 1 に記載の電子システム。

【請求項 6】

前記ストレージコントロールユニットは、スキャン及び選択ブロックを実行するように構成されることを特徴とする請求項 1 に記載の電子システム。

【請求項 7】

前記入出力の使用に基づいて前記データを分割するための前記前処理ブロックは、前記入出力の飽和に基づいて分割することを特徴とする請求項 1 に記載の電子システム。

10

【請求項 8】

電子システムの動作方法において、

ストレージ装置に含まれて前処理ブロックを実行するように構成されたストレージコントロールユニットで、分散機械学習プロセスを実行するために、システム装置と前記ストレージ装置との間のストレージインターフェイスの入出力の使用に基づいて、データを前記ストレージ装置によって処理される第 1 部分データと、前記システム装置によって処理される第 2 部分データとに分割する段階と、

前記第 2 部分データを前記システム装置に分配し、前記第 1 部分データを前記ストレージ装置の学習ブロックに分配する段階と、を有し、

前記学習ブロックは、前記分散機械学習プロセスの一部を実行することを特徴とする電子システムの動作方法。

20

【請求項 9】

前記データを分割する段階は、前記ストレージコントロールユニットで適応的な前処理ブロックを実行する段階を含むことを特徴とする請求項 8 に記載の電子システムの動作方法。

【請求項 10】

前記データを分割する段階は、前記ストレージコントロールユニットでプログラミングインターフェイスを実行する段階を含むことを特徴とする請求項 8 に記載の電子システムの動作方法。

30

【請求項 11】

前記分散機械学習プロセスは、前記ストレージコントロールユニットでスケジューラー ブロックを実行する段階を含むことを特徴とする請求項 8 に記載のメモリシステムの動作方法。

【請求項 12】

前記データを分割する段階は、前記ストレージコントロールユニットで選択ブロックを実行する段階を含むことを特徴とする請求項 8 に記載の電子システムの動作方法。

【請求項 13】

前記データを分割する段階は、前記ストレージコントロールユニットでスキャン及び選択ブロックを実行する段階を含むことを特徴とする請求項 8 に記載の電子システムの動作方法。

40

【請求項 14】

前記データを分割する段階は、前記入出力の使用に基づき、前記入出力の飽和に基づいて分割することを特徴とする請求項 8 に記載の電子システムの動作方法。

【請求項 15】

コントロールユニットによって実行される命令語が格納された不揮発性のコンピュータ 読取可能ストレージ媒体において、

ストレージ装置に含まれて前処理ブロックを実行するように構成されたストレージコントロールユニットで、分散機械学習プロセスを実行するために、システム装置と前記ストレージ装置との間のストレージインターフェイスの入出力の使用に基づいて、データを前記ストレージ装置によって処理される第 1 部分データと、前記システム装置によって処理

50

される第2部分データとに分割する動作と、

前記第2部分データを前記システム装置に分配し、前記第1部分データを前記ストレージ装置の学習ブロックに分配する動作と、を実行させ、

前記学習ブロックが、前記分散機械学習プロセスの一部を実行するように動作させることを特徴とする不揮発性コンピュータ読取可能ストレージ媒体。

【請求項16】

前記データを分割する動作は、前記ストレージコントロールユニットで適応的な前処理ブロックを実行する動作を含むことを特徴とする請求項15に記載の不揮発性コンピュータ読取可能ストレージ媒体。

【請求項17】

前記データを分割する動作は、前記ストレージコントロールユニットでプログラミングインターフェイスを実行する動作を含むことを特徴とする請求項15に記載の不揮発性コンピュータ読取可能ストレージ媒体。

【請求項18】

前記分散機械学習プロセスは、前記ストレージコントロールユニットでスケジュールブロックを実行する動作を含むことを特徴とする請求項15に記載の不揮発性コンピュータ読取可能ストレージ媒体。

【請求項19】

前記データを分割する動作は、前記ストレージコントロールユニットで選択ブロックを実行する動作を含むことを特徴とする請求項15に記載の不揮発性コンピュータ読取可能ストレージ媒体。

【請求項20】

前記データを分割する動作は、前記ストレージコントロールユニットでスキャン及び選択ブロックを実行する段階を含むことを特徴とする請求項15に記載の不揮発性コンピュータ読取可能ストレージ媒体。

【請求項21】

前記データを分割する動作は、前記入出力の使用に基づき、前記入出力の飽和に基づいて分割することを特徴とする請求項15に記載の不揮発性コンピュータ読取可能ストレージ媒体。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は電子システムに関し、さらに詳細には、学習機能を有する電子システム及びその動作方法並びに不揮発性コンピュータ読取可能ストレージ媒体に関する。

【背景技術】

【0002】

グラフィックディスプレイシステム、テレビジョン、プロジェクタ、セルラーフォン、携帯型デジタル補助装置、クライアントワークステーション、データセンターサーバ、及び複合装置のような現代消費者及び産業電子装置は現代の日常を支援するための増加する機能のレベルを提供している。

現存する技術に対する研究及び開発は多様な方向に行っている。

【0003】

増加する機能のレベルは、増加するメモリとストレージ処理を要求する。

プロセッサとメモリ容量及び帯域幅は増加する装置又はシステムの性能と機能において主要な要因になる。

他の電子部品やモジュールでと同様に、メモリ面積及び費用は性能及び機能とトレードオフの関係を有する。

大容量データの処理は、装置又はシステムの性能と機能を向上させることができる。しかし、大容量データの処理は大量のシステム帯域幅を消費し、システムアクセスコンフリクト、及びシステム資源（リソース）を消費し、このような特性はシステム性能及び機能

10

20

30

40

50

を低下させる。

【0004】

したがって、システムの性能を向上させるための大容量データ処理のための学習メカニズムを有する電子システムに対する要求が必要になった。

日々に増加する商業的な競争圧力、消費者の増加する期待、そして市場での意味ある商品の差別化のための機会の減少の側面を考慮する時、このような問題の改善に対する事項はますます重要になっている。

その上に、費用の減少、性能と効率の増大、そして商業的な競争圧力に対する要求はこのような問題を迅速に解決することを要求している。

【0005】

10

上述した問題を解決するための多くの試みが長い間行われてきたが、上述した問題に対する決定的な解決策を提示、或は提案はされておらず、このような問題は相変わらず、当業者に困難な問題として存在している。

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は上記従来の電子システムにおける問題点に鑑みてなされたものであって、本発明の目的は、大容量データ処理のための学習メカニズムを有する電子システムを通じて具現できる低費用及び高効率の電子システム及びその動作方法並びに不揮発性コンピュータ読み取り可能ストレージ媒体を提供することにある。

20

【課題を解決するための手段】

【0007】

上記目的を達成するためになされた本発明による電子システムは、ストレージ装置とシステム装置との間の通信を提供するように構成されたストレージインターフェイスと、前記ストレージ装置に含まれて前記ストレージインターフェイスに接続され、分散機械学習プロセスを実行するために、前記システム装置と前記ストレージ装置との間の前記ストレージインターフェイスの入出力の使用に基づいて、データを前記ストレージ装置によって処理される第1部分データと、前記システム装置によって処理される第2部分データとに分割する前処理ロックを実行するように構成されたストレージコントロールユニットと、前記分散機械学習プロセスの一部として前記第1部分データを処理するための学習ブロックと、を備えることを特徴とする。

30

【0008】

上記目的を達成するためになされた本発明による電子システムの動作方法は、ストレージ装置に含まれて前処理ロックを実行するように構成されたストレージコントロールユニットで、分散機械学習プロセスを実行するために、システム装置と前記ストレージ装置との間のストレージインターフェイスの入出力の使用に基づいて、データを前記ストレージ装置によって処理される第1部分データと、前記システム装置によって処理される第2部分データとに分割する段階と、前記第2部分データを前記システム装置に分配し、前記第1部分データを前記ストレージ装置の学習ブロックに分配する段階と、を有し、前記学習ブロックは、前記分散機械学習プロセスの一部を実行することを特徴とする。

40

【0009】

上記目的を達成するためになされた本発明による不揮発性コンピュータ読み取り可能ストレージ媒体は、コントロールユニットによって実行される命令語が格納された不揮発性のコンピュータ読み取り可能ストレージ媒体において、ストレージ装置に含まれて前処理ロックを実行するように構成されたストレージコントロールユニットで、分散機械学習プロセスを実行するために、システム装置と前記ストレージ装置との間のストレージインターフェイスの入出力の使用に基づいて、データを前記ストレージ装置によって処理される第1部分データと、前記システム装置によって処理される第2部分データとに分割する動作と、前記第2部分データを前記システム装置に分配し、前記第1部分データを前記ストレージ装置の学習ブロックに分配する動作と、を実行させ、前記学習ブロックが、前記分散機械

50

学習プロセスの一部を実行するように動作させることを特徴とする。

【発明の効果】

【0010】

本発明に係る電子システム及びその動作方法並びに不揮発性コンピュータ読取可能ストレージ媒体によれば、学習プロセスを通じて具現できる低費用及び高効率の電子システムを構成することができる。

【図面の簡単な説明】

【0011】

【図1】本発明の実施形態による電子システムである。

10

【図2】本発明の実施形態による電子システムの電子学習システムの一部を示すブロック図である。

【図3】本発明の実施形態による電子システムの電子学習システムの一部を示すブロック図である。

【図4】本発明の実施形態による電子システムの電子学習システムの一部を示すブロック図である。

【図5】本発明の実施形態による電子システムの電子学習システムの一部を示すブロック図である。

【図6】本発明の実施形態による電子システムの電子学習システムの一部を示すブロック図である。

20

【図7】本発明の実施形態による電子システムのストレージ装置の一部を示すブロック図である。

【図8】本発明の実施形態による電子システムの電子学習システムの一部を示すブロック図である。

【図9】本発明の実施形態による電子システムの電子学習システムの一部を示すブロック図である。

【図10】本発明の実施形態による電子システムの電子学習システムの一部を示すブロック図である。

【図11】本発明の実施形態による電子システムの電子学習システムの一部を示すブロック図である。

30

【図12】本発明の実施形態による電子システムの電子学習システムの一部を示すブロック図である。

【図13】本発明の実施形態による電子システムの電子学習システムの一部を示すブロック図である。

【図14】本発明の実施形態による電子システムの電子学習システムの処理を説明するためのフローチャートである。

【図15】本発明の実施形態による電子システムの電子学習システムの一部を示すブロック図である。

【図16】本発明の実施形態による電子システムの例を示す図である。

【図17】本発明の実施形態による電子システムの動作方法を説明するためのフローチャートである。

40

【発明を実施するための形態】

【0012】

次に、本発明に係る電子システム及びその動作方法並びに不揮発性コンピュータ読取可能ストレージ媒体を実施するための形態の具体例を図面を参照しながら説明する。

【0013】

本発明の実施形態で、学習システムはデータから学習を遂行するアルゴリズムを含むマシン学習システムを含む。

このようなアルゴリズムは、人工知能、外部からのプログラム無しでコンピュータを動作させる、自動推論、自動適応、自動決定、自動学習、外部のプログラム無しでコンピュ

50

ータが自動に学習する機能、人工知能 A I 、又はこれらの組み合わせを含むことができる。

マシン学習は、分類、回帰分析、特性学習、オンライン学習、自律的学習、地図学習、クラスター分析、次元縮小、構造予測、非正常行為の探知、神経網、又はこれらの組み合わせを含むことができる。

#### 【 0 0 1 4 】

本発明の実施形態において、学習システムは“ビックデータ ( b i g d a t a ) ”を処理するか、或いは分析するマシン学習システムを含むことができる。

ストレージ内部コンピューティング ( I n s t o r a g e c o m p u t i n g : 以下、 I S C ) 機能を有する並列又は分散ストレージ装置は、ビックデータの学習と分析とを加速化させることができる。 10

このような並列又は分散学習システムは、ストレージ内部コンピューティングの機能のための追加的な帯域幅や、ホストとストレージへの入出力量を減らすことができる。

並列又は分散学習システムは、マシン学習システムにストレージ内部コンピューティング I S C 機能を提供することができる。 20

#### 【 0 0 1 5 】

本発明の実施形態で、並列又は分散学習システムは、ストレージ内コンピューティング ( I S C ) 、スケジューラー、又はこれらの組み合わせと共に実行することができる。

ストレージ内コンピューティング ( I S C ) は、並列又は分散学習システムを含む学習システムで画期的な向上を提供することができる。 20

ストレージ内コンピューティング ( I S C ) は、検出された帯域幅のボトルネック ( b o t t l e n e c k 、出口が狭い) 現象を低下させるための I S C での前処理のようなマシン学習のためのその他のプロセッサ、ホスト C P U を支援するための加速器、又はこれらの組み合わせを提供することができる。

スケジューラーは、知的 ( i n t e l l i g e n t l y ) にデータ、タスク、機能、動作、又はこれらの組み合わせを割り当てを行うことができる。

#### 【 0 0 1 6 】

以下ではこの分野で技術を習得した者が容易に実施できる程度に本発明が詳細に説明される。

本発明の開示、即ち、システム、プロセス、又は機械的な変形は、本発明の実施形態の範囲を逸脱しなく、他の実施形態も容易に実施されることは容易に理解できる。 30

以下の説明で、本発明の実施形態の理解のために多い具体的な説明が提供される。

しかし、本発明の実施形態は上述した具体的な説明無しでも実施されることは明かである。本発明の実施形態に対する曖昧なことを避けるために幾つかの広く公知された回路、システム設定、及び処理段階に対する詳細な説明は省略する。

#### 【 0 0 1 7 】

システムの実施形態を示す図面は明確な説明をするために寸法を省略するか、或いは幾つかのディメンションは部分的に誇張されて図示した部分が存在する。

同様に、たとえ容易な説明をするために図面に図示した幾つかの方向は一般的に類似であるが、このような表現はほとんど任意の方向である。 40

一般的に、実施形態は何らかの方向に対しても動作することができる。第 1 実施形態、第 2 実施形態等の序数的に表現された実施形態は実施形態の限定や重要度を示す意図ではなく、表現の便宜のための表現に過ぎない。

#### 【 0 0 1 8 】

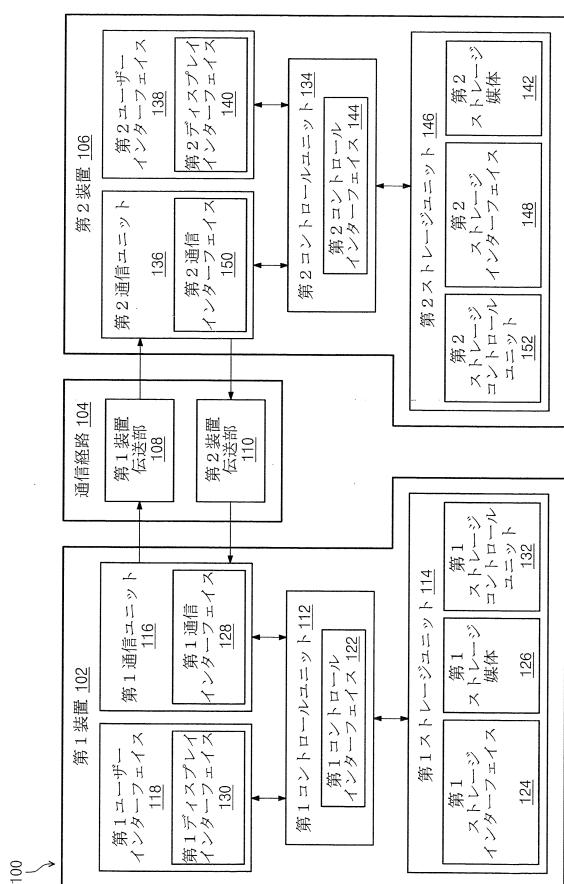

図 1 は、本発明の一実施形態による電子システム 1 0 0 を示す。

図 1 を参照すると、学習メカニズムを有する電子システム 1 0 0 は、クライアント又はサーバのような第 1 装置 1 0 2 と、有線又は無線ネットワークのような通信経路 1 0 4 とを含む。

第 1 装置 1 0 2 は、クライアントやサーバのような第 2 装置 1 0 6 と接続することができる。 50

第1装置102は、通信経路104を通じて第2装置106と接続することができる。例えば、第1装置102と第2装置106、又はこれらの組み合わせは、クライアント、サーバ、ディスプレイ装置、クラスターのノード、スーパーコンピュータのノード、セルラーフォン、個人デジタル補助機、ノートブック型コンピュータ、他のマルチ機能装置、又はこれらの組み合わせのような装置の変形された例であってもよい。

【0019】

第1装置102は第2装置106と通信経路104を通じて直接又は間接的に接続させるか、或いは、単独装置であってもよい。

容易である説明のために、電子システム100は、第1装置102と第2装置106とが通信経路104の終端点として図示したが、電子システム100は、第1装置102、第2装置106、及び通信経路104の間に別の部分をさらに含み得ることを容易に理解できる。

例えば、第1装置102と第2装置106、又はこれらの組み合わせは通信経路104の一部の機能として動作することができる。

【0020】

一実施形態として、通信経路104は多様なネットワークを示す。

例えば、通信経路104は、システムバス、無線通信、有線通信、光通信、超音波通信、又はこれらの組み合わせを含む。

システムバスの例として、PCIe (Peripheral Component Interconnect Express)、PCI (Peripheral Component Interconnect)、ISA (Industry Standard Architecture)、SATA (Serial Advanced Technology Attachment)、SCSI (Small Computer Serial Interface)、EIDE (Enhanced Integrated Drive Electronics)、NVMホストコントローラインターフェイス (Non-Volatile Memory host controller interface)、NVMe (Non-Volatile Memory express)、SATAe (Serial Attached Advanced Technology Attachment express)、及びAGP (Accelerated Graphics Port) がある。

【0021】

無線通信の例として、衛星通信、セルラー通信、ブルートゥース (登録商標)、Wi-Fi (Wireless Fidelity) 等がある。

有線通信の例として、イーサーネット (登録商標)、10ギガビットイーサーネット (登録商標)、40ギガビットイーサーネット (登録商標)、100ギガビットイーサーネット (登録商標)、インフィニバン (InfiniBand (登録商標))、デジタル加入者回線 (DSL)、FTTH (fiber to the home) 等がある。

先に言及されたすべての構成が通信経路104に含まれ得る。

【0022】

一実施形態において、第1装置102は、第1コントロールユニット112、第1ストレージユニット114、第1通信ユニット116、及び第1ユーザーインターフェイス118を含む。

第1コントロールユニット112は、第1コントロールインターフェイス122を含むことができる。

第1コントロールユニット112は、電子システム100の知能を提供するための第1ストレージユニット114の第1ソフトウェアを実行することができる。

第1コントロールユニット112は複数の互いに異なる方式で駆動させることができる。

【0023】

例えば、第1コントロールユニット112は、プロセッサ、ASIC (Application

10

20

30

40

50

tion Specific Integrated Circuit)、FPGA (field programmable gate array)、SoC (system on a chip)、埋め込み型プロセッサ、マイクロプロセッサ、マルチプロセッサ、チッププロセッサ (CMP)、ハードウェア制御ロジック、ハードウェア有限状態マシン (FSM) (hardware finite state machine)、デジタル信号処理器 (DSP)、又はこれらの組み合わせであってもよい。

第1コントロールインターフェイス122は、第1コントロールユニット112と第1装置102内の異なる機能ユニットとの通信に使用することができる。また、第1コントロールインターフェイス122は第1装置102の外部装置との通信に使用することができる。

10

#### 【0024】

一実施形態において、第1コントロールインターフェイス122は、異なる機能ユニットや外部ソースから提供される情報を受信するか、或いは異なる機能ユニット又は外部目的地に情報を送信することができる。

外部ソースや外部目的地は、第1装置102の外部ソース又は外部目的地を意味する。

第1コントロールインターフェイス122は、第1コントロールインターフェイス122と通信する機能ユニットや外部ユニットに従って互いに異なる構成又は互いに異なる方法によって具現することができる。

例えば、第1コントロールインターフェイス122は、圧力センサー、加速センサー、MEMS (Microelectromechanical System)、光回路、導波管、無線回路、有線回路、又はこれらの組み合わせで具現することができる。

20

#### 【0025】

一実施形態において、第1ストレージユニット114は、第1ストレージ媒体126に第1ソフトウェアを格納することができる。

第1ストレージユニット114は、イメージ、情報、サウンドファイル、ソーシャルネットワークデー (social network day) の任意のフォーム、ユーザープロフィール、行動情報、クッキー、大きいサイズ形態の使用者データ収集、又はこれらの組み合わせを格納することができる。

第1ストレージユニット114は、揮発性メモリ、不揮発性メモリ、内部メモリ、外部メモリ、又はこれらの組み合わせであってもよい。

30

例えば、第1ストレージユニット114は、不揮発性ランダムアクセスメモリ (NVRAM)、不揮発性メモリ (NVM)、NVMeフラッシュメモリ、ディスクストレージ、又はSRAMのような揮発性ストレージであってもよい。

#### 【0026】

一実施形態において、第1ストレージユニット114は、第1ストレージインターフェイス124を含む。

第1ストレージインターフェイス124は、第1装置内の異なる機能ユニットと通信のために使用することができる。

第1ストレージインターフェイス124は、第1装置102外部との通信のために使用することができる。

40

第1ストレージインターフェイス124は、異なる機能ユニットや外部ソースから情報を受信するか、或いは異なる機能ユニット又は外部目的地に情報を伝送することができる。外部ソースと外部目的地とは第1装置の外部ソースや目的地を意味する。

#### 【0027】

一実施形態において、第1ストレージインターフェイス124は、第1ストレージユニット114がインターフェイシングする機能ユニットや外部ユニットにしたがって互いに異なる方式で具現することができる。

第1ストレージインターフェイス124は、第1コントロールインターフェイス122と類似の方式の技術によって具現することができる。

#### 【0028】

50

一実施形態において、第1通信ユニット116は、第1装置102の外部通信を可能する。

例えば、第1通信ユニット116は、第1装置102が付属装置やデスクトップコンピュータコンピュータ、通信経路104、又は第2通信ユニット136と通信するように許諾する。

第1通信ユニット116は通信ハブのような機能を遂行して第1装置102が通信経路104の一部として動作するようになるので、第1装置102が通信経路104の終端や終端装置に限定されないように使用することができる。

第1通信ユニット116は、通信経路104とのインターフェイスのためにマイクロ電子回路やアンテナのような能動及び受動要素を含むことができる。 10

#### 【0029】

一実施形態において、第1通信ユニット116は、第1通信インターフェイス128を含む。

第1通信インターフェイス128は、第1通信ユニット116と第1装置102内の異なる機能ユニットとの通信のために使用することができる。

第1通信インターフェイス128は、異なる機能ユニットや外部ソースから情報を受信するか、或いは異なる機能ユニット又は外部目的地に情報を伝送することができる。

第1通信インターフェイス128は、第1通信ユニット116がインターフェイシングする機能ユニットにしたがって互いに異なる方式で具現することができる。

第1通信インターフェイス128は、第1コントロールインターフェイス122と類似の技術方式で具現することができる。 20

#### 【0030】

一実施形態において、第1ユーザーインターフェイス118は、ユーザー（未図示）と第1装置102とのインターフェイスや相互作用手段を提供する。

第1ユーザーインターフェイス118は、入力装置と出力装置とを含むことができる。

例えば、第1ユーザーインターフェイス118の入力装置は、データ及び通信入力を提供するためのキーパッド、マウス、タッチパッド、ソフトキー、キーボード、マイク、リモート信号を受信するための赤外線センサー、リモートアクセスのための仮想ディスプレイコンソール、リモートアクセスのための仮想ディスプレイターミナル、又はこれらの組み合わせを含むことができる。 30

#### 【0031】

一実施形態において、第1ユーザーインターフェイス118は、第1ディスプレイインターフェイス130を含むことができる。

第1ディスプレイインターフェイス130は、ディスプレイ、プロジェクタ、ビデオスクリーン、スピーカー、リモートネットワークディスプレイ、仮想ネットワークディスプレイ、又はこれらの組み合わせの中のいずれかを含むことができる。

一実施形態において、第1ストレージインターフェイス124は、第1コントロールインターフェイス122と同様に、第1ストレージコントロールユニット132のために異なる機能ユニット、外部ソース、外部目的地等にデータを伝送するか、或いは受信することができる。 40

#### 【0032】

第1ストレージコントロールユニット132は、プロセッサ、ASIC (Application Specific Integrated Circuit)、SoC (system on a chip)、埋め込み型プロセッサ、マルチプロセッサ、チッププロセッサ(CMP)、ハードウェア制御ロジック、ハードウェア有限状態マシン(FSM)、デジタル信号処理器(DSP)、FPGA (field programmable gate array)、又はこれらの組み合わせであってもよい。

#### 【0033】

一実施形態において、第2装置106は、第1装置102の実施形態を具現するためのマルチプルディバイスで最適化することができる。 50

第2装置106は、第1装置に比べて追加的に又は高性能の処理能力を提供することができる。

第2装置106は、第2コントロールユニット134、第2通信ユニット136、及び第2ユーザーインターフェイス138を含むことができる。

#### 【0034】

一実施形態において、第2ユーザーインターフェイス138は、ユーザー（未図示）が第2装置106とのインターフェイスや相互作用手段を提供する。

第2ユーザーインターフェイス138は、入力装置と出力装置を含むことができる。

例えば、第2ユーザーインターフェイス138の入力装置はデータ及び通信入力を提供するためのキーパッド、マウス、タッチパッド、ソフトキー、キーボード、マイク、リモート信号を受信するための赤外線センサー、リモートアクセスのための仮想ディスプレイコンソール、リモートアクセスのための仮想ディスプレイターミナル、又はこれらの組み合わせを含むことができる。10

第2ユーザーインターフェイス138の出力装置の例としては、第2ディスプレイインターフェイス140を含むことができる。

第2ディスプレイインターフェイス140は、ディスプレイ、プロジェクタ、ビデオスクリーン、スピーカー、リモートネットワークディスプレイ、仮想ネットワークディスプレイ、又はこれらの組み合わせの中のいずれかを含むことができる。

#### 【0035】

一実施形態において、第2コントロールユニット134は、電子システム100の知能を提供するための第2ストレージ媒体142の第2ソフトウェアを実行することができる。20

第2ストレージ媒体142の第2ソフトウェアは第1ストレージ媒体126の第1ソフトウェアと連動して動作することができる。

第2コントロールユニット134は、第1コントロールユニット112に追加性能を提供することができる。

第2コントロールユニット134は、情報を表示するために第2ユーザーインターフェイス138を駆動させることができる。

第2コントロールユニット134は、電子システム100の異なる機能、例えば、通信経路104を通じて第1装置102と通信するための第2通信ユニット136を駆動する等の機能のために第2ストレージ媒体142に格納された第2ソフトウェアを実行することができる。30

#### 【0036】

一実施形態において、第2コントロールユニット134は、複数の互いに異なる方式で具現することができる。

例えば、第2コントロールユニット134は、プロセッサ、ASIC (Application Specific Integrated Circuit)、FPGA (field programmable gate array)、SoC (system on a chip)、埋め込み型プロセッサ、マイクロプロセッサ、マルチプロセッサ、チッププロセッサ (CMP)、ハードウェア制御ロジック、ハードウェア有限状態マシン (FSM)、デジタル信号処理器 (DSP)、又はこれらの組み合わせであってもよい。40

第2コントロールユニット134は、第2コントロールインターフェイス144を含む。

第2コントロールインターフェイス144は、第2コントロールユニット134と第2装置106内の異なる機能ユニットとの通信に使用することができる。また、第2コントロールインターフェイス144は、第2装置106の外部装置との通信に使用することができる。

#### 【0037】

一実施形態において、第2コントロールインターフェイス144は、異なる機能ユニッ50

トや外部ソースから提供される情報を受信するか、或いは異なる機能ユニット又は外部目的地に情報を送信することができる。

外部ソースや外部目的地は、第2装置106の外部ソース又は外部目的地を意味する。

第2コントロールインターフェイス144は、第2コントロールインターフェイス144と通信する機能ユニットや外部ユニットにしたがって互いに異なる構成又は互いに異なる方法によって具現することができる。

例えば、第2コントロールインターフェイス144は、圧力センサー、加速センサー、MEMS (Microelectromechanical System)、光回路、導波管、無線回路、有線回路、又はこれらの組み合わせで具現することができる。

#### 【0038】

10

一実施形態において、第2ストレージユニット146は、第2ストレージ媒体142に第2ソフトウェアを格納することができる。

第2ストレージユニット146は、イメージ、情報、サウンドファイル、ソーシャルネットワークデーの任意のフォーム、ユーザープロフィール、行動情報、クッキー、大きいサイズ形態の使用者データ収集、又はこれらの組み合わせを格納することができる。

第2ストレージユニット146は、第1ストレージユニット114に追加的なストレージ容量を提供するための大きさで提供することができる。

例えば、第2ストレージユニット146は、1つの構成で図に示しているが、複数のストレージ要素が分散された形態で提供できることは容易に理解できる。

例示的に、電子システム100は、第2ストレージユニット146がシングル階層のストレージシステムで図に示したが、電子システム100の第2ストレージユニット146は異なる設定で構成することもできる。

#### 【0039】

20

例えば、第2ストレージユニット146は、互いに異なるレベルのキャッシュ、メインメモリ、回転型媒体、又はオンラインストレージのような異なる方式の技術によって提供される階層的メモリであってもよい。

第2ストレージユニット146は、揮発性メモリ、不揮発性メモリ、内部メモリ、外部メモリ、又はこれらの組み合わせであってもよい。

例えば、第2ストレージユニット146は、不揮発性ランダムアクセスメモリ(NVRAM)、不揮発性メモリ(NVM)、NVMeフラッシュメモリ、ディスクストレージ、又はSRAMのような揮発性ストレージであってもよい。

#### 【0040】

30

一実施形態において、第2ストレージユニット146は、第2ストレージインターフェイス148を含む。

第2ストレージインターフェイス148は、第2装置内の異なる機能ユニットと通信のために使用することができる。

第2ストレージインターフェイス148は、第2装置106の外部との通信のために使用することができる。

#### 【0041】

40

一実施形態において、第2ストレージインターフェイス148は、異なる機能ユニットや外部ソースから情報を受信するか、或いは異なる機能ユニット又は外部目的地に情報を伝送することができる。

外部ソースと外部目的地とは第2装置106の外部ソースや目的地を意味する。

第2ストレージインターフェイス148は、第2ストレージユニット146がインターフェイシングする機能ユニットや外部ユニットにしたがって互いに異なる方式で具現することができる。

第2ストレージインターフェイス148は、第2コントロールインターフェイス144と類似な方式の技術によって具現することができる。

第2通信ユニット136は、第2装置106の外部通信を可能するようにする。

例えば、第2通信ユニット136は、第2装置106が通信経路104を通じて第1装

50

置 1 0 2 と通信するように許諾する。

【 0 0 4 2 】

一実施形態において、第 2 通信ユニット 1 3 6 は、通信ハブのような機能を遂行して第 2 装置 1 0 6 が通信経路 1 0 4 の一部として動作するようにするので、第 2 装置 1 0 6 が通信経路 1 0 4 の終端や終端装置に限定されないように使用することができる。

第 2 通信ユニット 1 3 6 は、通信経路 1 0 4 とのインターフェイスのためにマイクロ電子回路やアンテナのような能動及び受動要素を含むことができる。

一実施形態において、第 2 通信ユニット 1 3 6 は、第 2 通信インターフェイス 1 5 0 を含む。

第 2 通信インターフェイス 1 5 0 は、第 2 通信ユニット 1 3 6 と第 2 装置 1 0 6 内の異なる機能ユニットとの通信のために使用することができる。 10

第 2 通信インターフェイス 1 5 0 は、異なる機能ユニットや外部ソースから情報を受信するか、或いは異なる機能ユニット又は外部目的地に情報を伝送することができる。

【 0 0 4 3 】

一実施形態において、第 2 通信インターフェイス 1 5 0 は、第 2 通信ユニット 1 3 6 がインターフェイシングする機能ユニットにしたがって互いに異なる方式で具現することができる。

第 2 通信インターフェイス 1 5 0 は、第 2 コントロールインターフェイス 1 4 4 と類似の技術方式で具現することができる。

第 1 通信ユニット 1 1 6 は、第 2 装置 1 0 6 に情報を伝送するために通信経路 1 0 4 の第 1 装置伝送部 1 0 8 に接続される。 20

第 2 装置 1 0 6 は、第 2 通信ユニット 1 3 6 を通じて通信経路 1 0 4 の第 1 装置伝送部 1 0 8 からの情報を受信することができる。

【 0 0 4 4 】

一実施形態において、第 2 通信ユニット 1 3 6 は、第 1 装置 1 0 2 に情報を伝送するために通信経路 1 0 4 の第 2 装置伝送部 1 1 0 に接続される。

第 1 装置 1 0 2 は、第 1 通信ユニット 1 1 6 を通じて通信経路 1 0 4 の第 2 装置伝送部 1 1 0 からの情報を受信することができる。

電子システム 1 0 0 は、第 1 コントロールユニット 1 1 2 、第 2 コントロールユニット 1 3 4 、又はこれらの組み合わせによって駆動することができる。 30

【 0 0 4 5 】

例示的な説明のために、第 2 装置 1 0 6 が第 2 ユーザーインターフェイス 1 3 8 、第 2 ストレージユニット 1 4 6 、第 2 コントロールユニット 1 3 4 、及び第 2 通信ユニット 1 3 6 に分離したもので説明したが、第 2 装置 1 0 6 は異なる方式で分離することができることは容易に理解できる。

例えば、第 2 ストレージ媒体 1 4 2 に格納された第 2 ソフトウェアは一部機能又はすべての機能が第 2 コントロールユニット 1 3 4 と第 2 通信ユニット 1 3 6 に割り当ててもよい。

同様に、第 2 装置 1 0 6 は、図 1 に示さなかった機能ユニットをさらに含むことができる。 40

【 0 0 4 6 】

一実施形態において、第 2 ストレージインターフェイス 1 4 8 は、第 2 コントロールインターフェイス 1 4 4 と同様に、第 2 ストレージコントロールユニット 1 5 2 のために異なる機能ユニット、外部ソース、外部目的地等にデータを伝送するか、或いは受信することができる。

第 2 ストレージコントロールユニット 1 5 2 は、プロセッサ、A S I C ( A p p l i c a t i o n S p e c i f i c I n t e g r a t e d C i r c u i t ) 、S o C ( s y s t e m o n a c h i p ) 、埋め込み型プロセッサ、マルチプロセッサ、チッププロセッサ ( C M P ) 、ハードウェア制御ロジック、ハードウェア有限状態マシン ( F S M ) 、デジタル信号処理器 ( D S P ) 、F P G A ( f i e l d p r o g r a m m a b l e ) 50

e\_gate\_array)、又はこれらの組み合わせであってもよい。

【0047】

一実施形態において、第1装置102に含まれる機能ユニットは、異なる機能ユニットと個別的にそして独立的に動作することができる。

第1装置102は、第2装置106と通信経路104と個別的にそして独立的に作業することができる。

同様に、第2装置106の機能ユニットも異なる機能ユニットと個別的にそして独立的に動作することができる。

第2装置106は、第1装置102と通信経路104と独立的に個別的にそして独立的に動作することができる。

例示的な説明のために、電子システム100は第1装置102と第2装置106との動作の説明を通じて説明される。

第1装置102と第2装置106とは電子システム100の特定機能、プロセス、アプリケーション、又はこれらの組み合わせで動作することができる。

【0048】

一実施形態において、本発明で記述される上述した機能、プロセス、アプリケーション、又はこれらの組み合わせは第1コントロールユニット112によって実行される不揮発性コンピュータ読取可能ストレージ媒体に格納された指示の一部であってもよい。

不揮発性コンピュータ読取可能ストレージ媒体は、ハードディスクドライブ(HDD)、不揮発性ランダムアクセスメモリ(NVRAM)、ソリッドステートストレージ装置(SSD)、コンパクトディスク(CD)、デジタルビデオディスク(DVD)、ユニバーサル直列バス(USB)、フラッシュメモリ装置、ブルーレイディスク(登録商標)(Blu-ray(登録商標)Disc)、コンピュータ読取可能である他の媒体、又はこれらの組み合わせを含む不揮発性メモリ装置を含むことができる。

不揮発性コンピュータ読取可能ストレージ媒体は、電子システム100の一部に集積されるか、又は電子システム100に脱着可能である部分として設置することができる。

【0049】

一実施形態において、本発明で記述される上述した機能、プロセス、アプリケーション、又はこれらの組み合わせは、第1コントロールユニット112、第2コントロールユニット134、又はこれらの組み合わせによって実行される不揮発性コンピュータ読取可能ストレージ媒体に格納された指示の一部であってもよい。

不揮発性コンピュータ読取可能ストレージ媒体は、第1ストレージユニット114、第2ストレージユニット146、又はこれらの組み合わせを含むことができる。

【0050】

不揮発性コンピュータ読取可能ストレージ媒体は、ハードディスクドライブ(HDD)、不揮発性ランダムアクセスメモリ(NVRAM)、ソリッドステートストレージ装置(SSD)、コンパクトディスク(CD)、デジタルビデオディスク(DVD)、ユニバーサル直列バス(USB)、フラッシュメモリ装置、ブルーレイディスク(登録商標)(Blu-ray(登録商標)Disc)、コンピュータ読取可能である他の媒体、又はこれらの組み合わせを含む不揮発性メモリ装置を含むことができる。

不揮発性コンピュータ読取可能ストレージ媒体は、電子システム100の一部に集積されるか、又は電子システム100に脱着可能である部分として設置することができる。

【0051】

一実施形態において、本発明で記述される上述した機能、プロセス、アプリケーション、又はこれらの組み合わせは第1ストレージ媒体126の第1ソフトウェア、第2ストレージ媒体142の第2ソフトウェア、又はこれらの組み合わせの一部であってもよい。

上述した機能、プロセス、アプリケーション、又はこれらの組み合わせは第1ストレージユニット114、第2ストレージユニット146、又はこれらの組み合わせに格納することができる。

第1コントロールユニット112、第2コントロールユニット134、又はこれらの組

み合わせは、上述した機能、プロセス、アプリケーション、又はこれらの組み合わせを電子システム 100 で駆動するために実行することができる。

【0052】

一実施形態において、電子システム 100 は、機能、プロセッサ、アプリケーション、順序、又はこれらの組み合わせを例として説明した。

電子システム 100 は、機能、プロセッサ、アプリケーション、順序、又はこれらの組み合わせを異なるように分割するか、或は他の順序にしたがって分割することができる。

上述した機能、プロセッサ、アプリケーション、又はこれらの組み合わせは、第 1 コントロールユニット 112 又は第 2 コントロールユニット 134 内部のハードウェアによる具現、ハードウェア回路、又はハードウェアアクセラレータ等であってもよい。 10

上述した機能、プロセッサ、アプリケーション、又はこれらの組み合わせは、第 1 装置 102 又は第 2 装置 106 の内部に具備されるが、第 1 コントロールユニット 112 又は第 2 コントロールユニット 134 各々の外部に存在するハードウェアによる具現、ハードウェア回路、又はハードウェアアクセラレータ等であってもよい。

【0053】

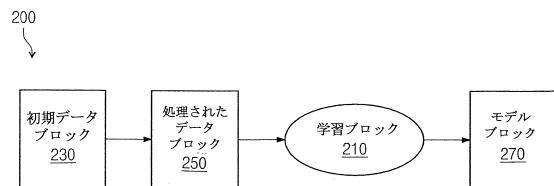

図 2 は、本発明の一実施形態による電子システム 100 の電子学習システム 200 の一部を示すブロック図である。

図 2 を参照すると、電子学習システム 200 は、図 1 の第 1 装置 102、図 1 の第 2 装置 106、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。 20

【0054】

一実施形態において、電子学習システム 200 は、機械学習機能を提供する。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するようにするか、或は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

機械学習は、人工知能 AI の 1 つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である。 30

【0055】

一実施形態において、電子学習システム 200 は、予測、推薦、スパム電子メールフィルタリングのようなフィルタリング、機械学習プロセス、機械学習機能、又はこれらの組み合わせを含む機械学習メカニズムを提供する。

ある実施形態で、ピックデータ分析のような機械学習を提供するための予測は、クリックや広告又は広告主の選択に基づき、品目の推薦、スパムフィルタリング、プロセス、又はこれらの組み合わせであってもよい。

一実施形態において、電子学習システム 200 は、ストレージ内コンピューティング (ISC) のみならず、システムプロセッサでの並列処理のためのクラスター・コンピューティングを含む並列又は分散機械学習メカニズムを含むことができる。 40

【0056】

並列処理のための並列又は分散機械学習メカニズムは、図 1 の第 1 コントロールユニット 112、図 1 の第 2 コントロールユニット 134、図 1 の第 1 ストレージユニット 114、図 1 の第 1 ストレージ媒体 126、図 1 の第 2 ストレージ媒体 142、図 1 の第 2 ストレージユニット 146、図 1 の第 1 ストレージコントロールユニット 132、図 1 の第 2 ストレージコントロールユニット 152、又はこれらの組み合わせの中の少なくとも 1 つで実行することができる。

【0057】

例えば、電子学習システム 200 は、機械学習ブロックのような学習ブロック 210、ローデータブロックのような初期データブロック 230、処理されたデータブロック 25 50

0、モデルブロック 270、又はこれらの組み合わせを含むことができる。

処理されたデータブロック 250 は、追加的な処理や機械学習のために初期データブロック 230 の部分データブロック、初期データブロック 230 の知的にアップデートされたブロック、初期データブロック 230 の知的に選択されたブロック、他のフォーマットのデータ、他の資料構造のデータ、又はこれらの組み合わせを含むことができる。

学習ブロック 210、初期データブロック 230、処理されたデータブロック 250、モデルブロック 270、又はこれらの組み合わせは集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

#### 【0058】

10

例示的に、学習ブロック 210、初期データブロック 230、処理されたデータブロック 250、モデルブロック 270、又はこれらの組み合わせは、各々分離されたブロックで図示しているが、いずれか 1 つのブロックは他のブロックとハードウェアの一部を共有できることが容易に理解できる。

例えば、学習ブロック 210、初期データブロック 230、処理されたデータブロック 250、モデルブロック 270、又はこれらの組み合わせは、ハードウェアメモリ回路や、第 1 ストレージユニット 114、第 2 ストレージユニット 146、第 1 ストレージ媒体 126、第 2 ストレージ媒体 142、又はこれらの組み合わせのようなコンポーネントの一部を共有することができる。

#### 【0059】

20

一実施形態において、学習ブロック 210 は、並列又は分散処理、クラスター・コンピューティング、又はこれらの組み合わせを含むことができる。

学習ブロック 210 は、システムプロセッサ、ストレージコンピューティングプロセッサ、第 1 コントロールユニット 112、第 2 コントロールユニット 134、第 1 ストレージコントロールユニット 132、第 2 ストレージコントロールユニット 152、第 1 ストレージユニット 114、第 2 ストレージユニット 146、又はこれらの組み合わせの中の少なくとも 1 つで実行することができる。

#### 【0060】

一実施形態において、初期データブロック 230 は、処理されないローデータ、部分的に処理されたデータ、又はこれらの組み合わせを格納するストレージ装置を含む。

30

初期データブロック 230 は、ストレージ装置、メモリ装置、第 1 ストレージユニット 114、第 2 ストレージユニット 146、第 1 ストレージ媒体 126、第 2 ストレージ媒体 142、又はこれらの組み合わせを含むことができる。

処理されたデータブロック 250 は、初期データブロック 230 で処理された以後に未だ追加的な処理がされないデータを格納するためのストレージ装置を含むことができる。

処理されたデータブロック 250 は、ストレージ装置、メモリ装置、第 1 ストレージユニット 114、第 2 ストレージユニット 146、第 1 ストレージ媒体 126、第 2 ストレージ媒体 142、又はこれらの組み合わせで具現されることができる。

#### 【0061】

40

一実施形態において、モデルブロック 270 は、ストレージ装置を含むことができる。

例えば、ストレージ装置は、データ、情報、アプリケーション、機械学習データ、分析されたビックデータ、ビックデータ分析アルゴリズム、又はこれらの組み合わせを格納することができる。

モデルブロック 270 は、ストレージ装置、メモリ装置、システムプロセッサ、ストレージ内コンピューティング (ISC) プロセッサ、第 1 ストレージユニット 114、第 2 ストレージユニット 146、第 1 コントロールユニット 112、第 2 コントロールユニット 134、第 1 ストレージコントロールユニット 132、第 2 ストレージコントロールユニット 152、又はこれらの組み合わせ内で具現することができる。

#### 【0062】

初期データブロック 230 の初期データ、処理されたデータブロック 250 の第 1 デー

50

夕他、又はこれらの組み合わせのような選択データの割り当て制御は、性能向上を提供することとして公知である。

割り当て制御は、図1の通信経路104のような入出力帯域幅の通信資源の飽和、中央処理装置(CPU)、コントロールユニット、第1コントロールユニット112、第2コントロールユニット134、第1ストレージコントロールユニット132、第2ストレージコントロールユニット152、又はこれらの組み合わせのようなコンピューティング資源の飽和を検出することを含む。

#### 【0063】

例えば、初期データブロック230の初期データを処理されたデータブロック250の第1データに計算する処理は後述するシステム情報に基づいてコンピューティング装置とストレージ装置との間で処理を指定し、割り当てるための前処理ブロックによってアドレッシングされる第1コントロールユニット112、第2コントロールユニット134、通信経路104、インターフェイス、又はこれらの組み合わせの容量の限界である帯域幅の飽和をもたらす可能性がある。

#### 【0064】

例示的に、学習ブロック210、初期データブロック230、処理されたデータブロック250、モデルブロック270、又はこれらの組み合わせは各々分離されたブロックで図示しているが、ブロックの複数、組み合わせ、分布、分割、パーティショニング、又はこれらの組み合わせによる割り当ても可能であることは容易に理解できる。

例えば、学習ブロック210は、複数の装置に掛けて分布する複数のブロックを含むことができる。追加的な詳細な説明は学習ブロック210、初期データブロック230、処理されたデータブロック250、モデルブロック270、又はこれらの組み合わせに対する以下の図3によって提供される。

#### 【0065】

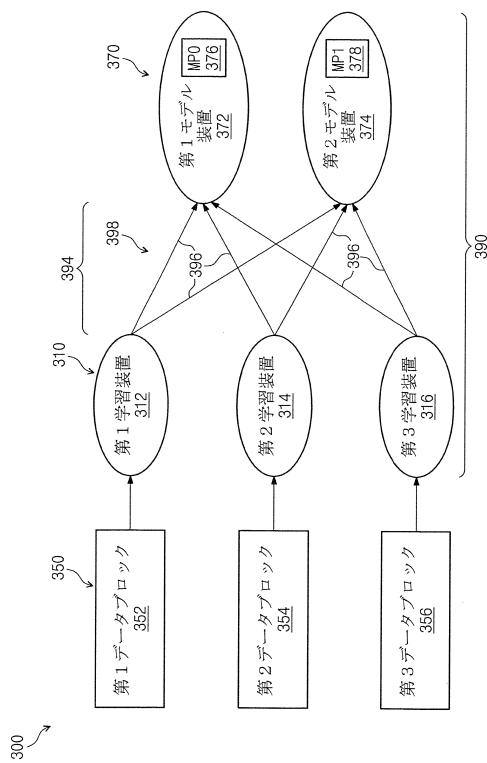

図3は、本発明の一実施形態による電子システム100の電子学習システム300の一部を示すブロック図である。

図3を参照すると、図2の電子学習システム200と同様に、電子学習システム300は、図1の第1装置102、図1の第2装置106、集積回路、集積回路コア、集積回路コンポーネント、MEMS(Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

#### 【0066】

一実施形態において、電子学習システム300は、機械学習機能を提供する。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するようにするか、又は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

機械学習は、人工知能AIの1つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である。

#### 【0067】

一実施形態において、電子学習システム300は、予測、推薦、スパム電子メールフィルタリングのようなフィルタリング、機械学習プロセス、機械学習機能、又はこれらの組み合わせを含む機械学習メカニズムを提供する。

ある実施形態では、ピックデータ分析のような機械学習を提供するための予測はクリックや広告又は広告主の選択に基づき、品目の推薦、スパムフィルタリング、プロセス、又はこれらの組み合わせであってもよい。

#### 【0068】

一実施形態において、電子学習システム300は、ストレージ内コンピューティング(ISC)のみならず、システムプロセッサでの並列処理のためのクラスター・コンピューティングを含む並列又は分散機械学習メカニズムを含むことができる。

10

20

30

40

50

並列処理のための並列又は分散機械学習メカニズムは、図1の第1コントロールユニット112、図1の第2コントロールユニット134、図1の第1ストレージユニット114、図1の第2ストレージユニット146、図1の第1ストレージコントロールユニット132、図1の第2ストレージコントロールユニット152、図1の第1ストレージ媒体126、図1の第2ストレージ媒体142、又はこれらの組み合わせの中の少なくとも1つで実行することができる。

【0069】

一実施形態において、電子学習システム300は、機械学習ブロックと第1学習装置312、第2学習装置314、第3学習装置316、又はこれらの組み合わせを含む学習装置310を含むことができる。10

また、電子学習システム300は、第1データブロック352、第2データブロック354、第3データブロック356、又はこれらの組み合わせのような学習データブロックのようなデータブロック350を含むことができる。

電子学習システム300は、第1モデル装置372、第2モデル装置374、又はこれらの組み合わせを含むモデル装置370を含むことができる。

学習装置310、データブロック350、モデルブロック370、又はこれらの組み合わせは、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

【0070】

一実施形態において、学習装置310は、第1コントロールユニット112、第2コントロールユニット134、第1ストレージコントロールユニット132、第2ストレージコントロールユニット152、又はこれらの組み合わせによって具現することができる。20

データブロック350は、第1ストレージユニット114、第2ストレージユニット146、第1ストレージ媒体126、第2ストレージ媒体142、又はこれらの組み合わせによって具現することができる。

モデル装置370は、第1コントロールユニット112、第2コントロールユニット134、第1ストレージコントロールユニット132、第2ストレージコントロールユニット152、第1ストレージユニット114、第2ストレージユニット146、又はこれらの組み合わせによって具現することができる。30

例示的に、学習装置310、データブロック350、モデル装置370、又はこれらの組み合わせは、各々分離したブロックで図示しているが、電子学習システム200と同様にいずれか1つのブロックは他のブロックのハードウェアの部分を共有できることは容易に理解できる。

【0071】

一実施形態において、電子学習システム300は、第1モデル装置372、第2モデル装置374、又はこれらの組み合わせのようにアップデート、訂正、修正、代替、記入、記録、挿入、又はこれらの組み合わせのような動作のための投入モデルプロセス390を含むことができる。

このモデルは、モデル装置370が駆動される学習装置310によってアップデート、訂正、修正、代替、記入、記録、挿入、又はこれらの組み合わせが可能である。40

【0072】

一実施形態において、投入モデルプロセス390、機械学習プロセス、ピックデータブロセス、他のプロセッサ、又はこれらの組み合わせは、ネットワーク394を含むことができる。

例えば、ネットワーク394は、図1の通信経路104と類似な方式のネットワークの多様な変形を含み、ネットワーク伝送部396、ネットワーク容量398、又はこれらの組み合わせを含むことができる。

ネットワーク伝送部396は、モデルやモデルパラメーター(376、378)を伝送することができる。50

ネットワーク容量 398 は、ネットワーク 394 によって支援可能であるネットワーク伝送部 396 の伝送量を含むことができる。

【0073】

一実施形態において、学習システム 300 は、ネットワーク 394、ネットワーク伝送部 396、ネットワーク容量 398、又はこれらの組み合わせに、検出、識別、モニターリング、測定、チェック、又はこれらの組み合わせ的な動作を提供することができる。

学習装置 310、データブロック 350、モデル装置 370、及びこれらの組み合わせを含む学習システム 300 は、ネットワーク容量 398 の問題を検出又は識別し、ボトルネック現象を検出することができる。

学習システム 300 は、並列又は分散機械学習システムのボトルネック現象を検出できるることは公知である。 10

学習システム 300 は、少なくともネットワーク容量 398 の問題を検出するか、或いは識別することができる。

【0074】

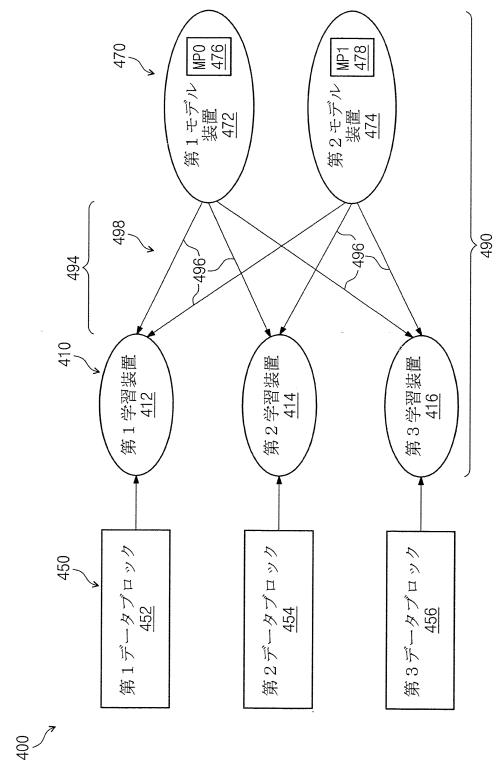

図 4 は、本発明の一実施形態による電子システム 100 の電子学習システム 400 の一部を示すブロック図である。

図 4 を参照すると、図 2 の電子学習システム 200 と同様に、電子学習システム 400 は、図 1 の第 1 装置 102、図 1 の第 2 装置 106、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。 20

【0075】

一実施形態において、電子学習システム 400 は、機械学習機能を提供することができる。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するようになるか、或は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

機械学習は、人工知能 AI の 1 つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である。 30

【0076】

一実施形態において、電子学習システム 400 は、予測、推薦、スパム電子メールフィルタリングのようなフィルタリング、機械学習プロセス、機械学習機能、又はこれらの組み合わせを含む機械学習メカニズムを提供する。

ある実施形態では、ビックデータ分析のような機械学習を提供するための予測はクリックや広告又は広告主の選択に基づき、品目の推薦、スパムフィルタリング、プロセス、又はこれらの組み合わせであってもよい。

【0077】

一実施形態において、電子学習システム 400 は、ストレージ内コンピューティング (ISC) のみならず、システムプロセッサでの並列処理のためのクラスター・コンピューティングを含む並列又は分散機械学習メカニズムを含むことができる。 40

並列処理のための並列又は分散機械学習メカニズムは、図 1 の第 1 コントロールユニット 112、図 1 の第 2 コントロールユニット 134、図 1 の第 1 ストレージユニット 114、図 1 の第 2 ストレージユニット 146、図 1 の第 1 ストレージコントロールユニット 132、図 1 の第 2 ストレージコントロールユニット 152、図 1 の第 1 ストレージ媒体 126、図 1 の第 2 ストレージ媒体 142、又はこれらの組み合わせの中の少なくとも 1 つで実行することができる。

【0078】

一実施形態において、電子学習システム 400 は、図 3 の学習装置 310 と同様に、学習ブロックと第 1 学習装置 412、第 2 学習装置 414、第 3 学習装置 416、又はこれ 50

らの組み合わせを含む学習装置 410 を含むことができる。

また、電子学習システム 400 は、図 3 のデータブロック 350 と同様に第 1 データブロック 452、第 2 データブロック 454、第 3 データブロック 456、又はこれらの組み合わせのような学習データブロックであるデータブロック 450 を含むことができる。

#### 【0079】

一実施形態において、電子学習システム 400 は、図 3 のモデル装置 370 と同様に第 1 モデル装置 472、第 2 モデル装置 474、又はこれらの組み合わせを含む、例えばモデルサーバのようなモデル装置 470 を含むことができる。

学習装置 410、データブロック 450、モデル装置 470、又はこれらの組み合わせは集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせのようなハードウェアの一部で具現することができる。

#### 【0080】

例えば、一実施形態において、学習装置 410 は、第 1 コントロールユニット 112、第 2 コントロールユニット 134、第 1 ストレージコントロールユニット 132、第 2 ストレージコントロールユニット 152、又はこれらの組み合わせによって具現することができる。

データブロック 450 は、第 1 ストレージユニット 114、第 2 ストレージユニット 146、又はこれらの組み合わせによって具現することができる。

モデル装置 470 は、第 1 コントロールユニット 112、第 2 コントロールユニット 134、第 1 ストレージコントロールユニット 132、第 2 ストレージコントロールユニット 152、第 1 ストレージユニット 114、第 2 ストレージユニット 146、又はこれらの組み合わせによって具現することができる。

例示的に、学習装置 410、データブロック 450、モデル装置 470、又はこれらの組み合わせは各々分離されたブロックで図示しているが、電子学習システム 200 と同様にいずれか 1 つのブロックは他のブロックのハードウェアの部分を共有できることを容易に理解できる。

#### 【0081】

一実施形態において、電子学習システム 400 は、第 1 モデル装置 472、第 2 モデル装置 474、第 1 モデル装置 372、第 2 モデル装置 374、又はこれらの組み合わせのようにアップデート、訂正、修正、代替、記入、記録、挿入、又はこれらの組み合わせのような動作のための投入モデルプロセス 490 を含むことができる。

このモデルは、モデル装置 370 が駆動される学習装置 310 又はモデル装置 370 が駆動される学習装置 310 によってアップデート、訂正、修正、代替、記入、記録、挿入、又はこれらの組み合わせが可能である。

#### 【0082】

一実施形態において、投入モデルプロセス 490、機械学習プロセス、ピックデータブロセス、他のプロセッサ、又はこれらの組み合わせはネットワーク 494 を含むことができる。

例えば、ネットワーク 494 は、図 1 の通信経路 104 と類似な方式のネットワークの多様な変形を含み、ネットワーク伝送部 496、ネットワーク容量 498、又はこれらの組み合わせを含むことができる。

ネットワーク伝送部 496 は、モデルやモデルパラメーター (476、478) を伝送することができる。

ネットワーク容量 498 は、ネットワーク 494 によって支援可能であるネットワーク伝送部 496 の伝送量を含むことができる。

#### 【0083】

一実施形態において、電子学習システム 400 は、ネットワーク 494、ネットワーク伝送部 496、ネットワーク容量 498、又はこれらの組み合わせに、検出、識別、モニターリング、測定、チェック、又はこれらの組み合わせ的な動作を提供することができる

。

学習装置 410、データブロック 450、モデル装置 470、及びこれらの組み合わせを含む電子学習システム 400 は、ネットワーク容量 498 の問題を検出又は識別し、ボトルネック現象を検出することができる。

#### 【0084】

一実施形態において、電子学習システム 400 は、図 3 の投入モデルプロセス 390 と同様に獲得モデルプロセス 490 と機械学習プロセス、ビックデータプロセス、他のプロセッサ、又はこれらの組み合わせを含む投入モデルプロセスを含むことができる。

これらのプロセスは、ネットワーク 494 での組み合わせされた問題、ボトルネック現象、又はこれらの組み合わせを提供する可能性がある。同様に、ある実施形態では、図 3 の電子学習システム 300 は図 3 のネットワーク 394 に対する獲得モデルプロセス 490、投入モデルプロセス 390、機械学習プロセス、ビックデータプロセス、他のプロセッサ、又はこれらの組み合わせを提供することができる。

#### 【0085】

例示的に、電子学習システム 400 及び電子学習システム 300 は、分離されたシステムで図示しているが、電子学習システム 400、及び電子学習システム 300、又はこれらの組み合わせは部分的に又は全体的に結合することができる。

例えば、電子学習システム 400 及び電子学習システム 300 は互いに異なるモードで動作する 1 つのシステムであってもよい。

電子学習システム 400 は、並列又は分散機械学習システムのボトルネック現象を検出できることは公知である。

電子学習システム 400 は、少なくともネットワーク容量 498 の問題を検出するか、或いは識別することができる。

#### 【0086】

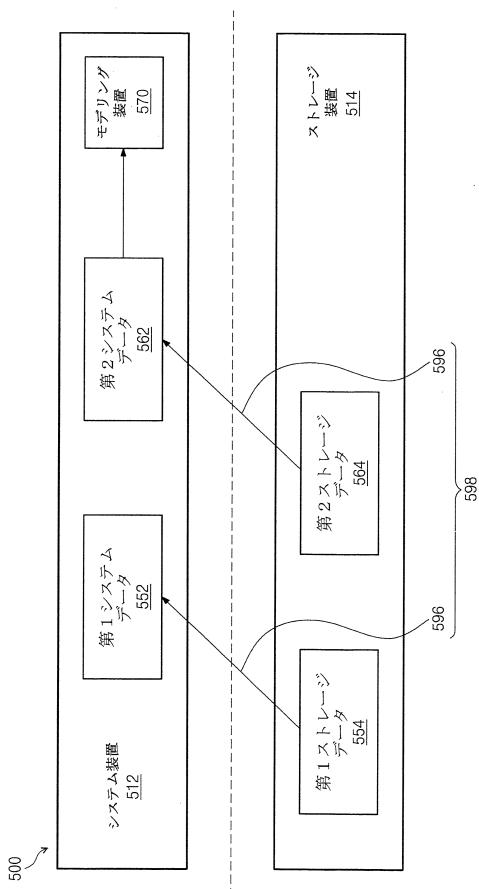

図 5 は、本発明の一実施形態による電子システム 100 の電子学習システム 500 の一部を示すブロック図である。

図 5 を参照すると、図 2 の電子学習システム 200 と同様に、電子学習システム 500 は、図 1 の第 1 装置 102、図 1 の第 2 装置 106、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

#### 【0087】

一実施形態において、電子学習システム 500 は、機械学習機能を提供する。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するようになるか、或は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

機械学習は、人工知能 AI の 1 つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である。

#### 【0088】

一実施形態において、電子学習システム 500 は、スキャニング、フィルタリング、予測、推薦、機械学習プロセス、機械学習機能、ビックデータ解釈、又はこれらの組み合わせを含む機械学習メカニズムを提供する。

電子学習システム 500 は、ストレージ内コンピューティング (ISC) プロセッサのみならず、システムプロセッサでの並列処理のためのクラスター・コンピューティングを含む並列又は分散機械学習メカニズムを含むことができる。

並列処理のための並列又は分散機械学習メカニズムは、図 1 の第 1 コントロールユニット 112、図 1 の第 2 コントロールユニット 134、図 1 の第 1 ストレージユニット 114、図 1 の第 2 ストレージユニット 146、図 1 の第 1 ストレージコントロールユニット 132、図 1 の第 2 ストレージコントロールユニット 152、図 1 の第 1 ストレージ媒体

10

20

30

40

50

126、図1の第2ストレージ媒体142、又はこれらの組み合わせの中の少なくとも1つで実行することができる。

【0089】

一実施形態において、電子学習システム500は、システム装置512、ストレージ装置514、学習データのような第1システムデータ552、学習データのような第1ストレージデータ554、又はこれらの組み合わせを含むことができる。

また、電子学習システム500は、学習データのような第2システムデータ562、第1システムデータ552のアップデートされたシステムデータ、第1システムデータ552の部分データ、第1システムデータ552の中で知的に選択されたデータ、第1システムデータ552の知的にアップデートされたデータ、又はこれらの組み合わせと、学習データのような第2ストレージデータ564、第1ストレージデータ554のアップデートされたシステムデータ、第1ストレージデータ554の部分データ、第1ストレージデータ554の中で知的に選択されたデータ、又はこれらの組み合わせを含むことができる。

電子学習システム500は、モデリング装置570を提供することができる。

【0090】

一実施形態において、電子学習システム500は、ネットワーク伝送部596、ネットワーク容量598、又はこれらの組み合わせを含むことができる。

電子学習システム500は、ネットワーク伝送部596、ネットワーク容量598、又はこれらの組み合わせに、検出、識別、モニターリング、測定、チェック、又はこれらの組み合わせ的な動作を提供することができる。

電子学習システム500は、システム装置512、ストレージ装置514、第1システムデータ552、第1ストレージデータ554、第2システムデータ562、第2ストレージデータ564、モデリング装置570、又はこれらの組み合わせを含んで、ネットワーク容量598の問題を検出又は識別し、ボトルネック現象を検出することができる。

学習システム500は、並列又は分散機械学習システムのボトルネック現象を検出できることは公知である。

学習システム500は、少なくともネットワーク容量598の問題を検出するか、或いは識別することができる。

【0091】

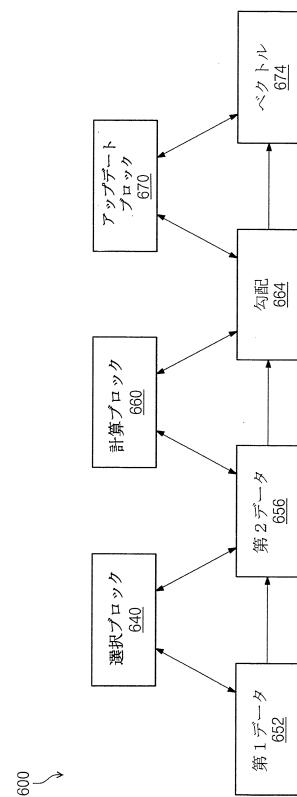

図6は、本発明の一実施形態による電子システム100の電子学習システム600の一部を示すブロック図である。

図6を参照すると、電子学習システム600は、図1の第1装置102、図1の第2装置106、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

【0092】

一実施形態において、電子学習システム600は、機械学習機能を提供する。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するようになるか、或は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

機械学習は、人工知能AIの1つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である。

【0093】

一実施形態において、電子学習システム600は、確率的勾配降下法 (Stochastic Gradient Descent: 以下、SGD) を含む勾配降下最適化方法のような確率的機械学習方式を含む機械学習メカニズムを提供することができる。

確率的勾配法は、高速の収斂率、増加されたステップサイズ、並列処理で複数のプロセッサによって駆動できる点、又はこれらの組み合わせのような特性を提供することができ

10

20

30

40

50

る。

また、確率的勾配降下法は、確率方式で高速の初期収斂特性と、確率的勾配降下法で低廉な反復費用を維持するための全勾配法 (full - gradient method) の速い最終段階収斂特性を提供することができる。

#### 【0094】

一実施形態において、電子学習システム 600 は、データ選択、一括選択、ランダム一括選択、又はこれらの組み合わせのような機械学習プロセスを提供するための選択ブロック 640 を含むことができる。

選択ブロック 640 は、データを受信、処理、選択、分割、伝送、又はこのような動作の組み合わせを遂行することができる。

10

例えば、選択ブロック 640 は、学習データ、第 1 データ 652 の部分データのような第 2 データ 656、第 1 データ 652 の知的なアップデートデータ、第 1 データ 652 の中で知的に選択されたデータ、又はこれらの組み合わせを処理することができる。

また、例えば、選択ブロック 640 は、第 1 データ 652 から第 2 データ 656 を選択するか、或いは分割することができる。

#### 【0095】

一実施形態において、電子学習システム 600 は、勾配 664 を計算するための計算ブロック 660、モデルのベクトル 674 をアップデートするためのアップデートブロック 670、又はこれらの組み合わせを含むことができる。

アップデートブロック 670 は、ベクトル 674 を含むすべてのモデルをアップデートすることができる。

20

選択ブロック 640、計算ブロック 660、及びアップデートブロック 670 は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

#### 【0096】

一実施形態において、選択ブロック 640、計算ブロック 660、アップデートブロック 670、又はこれらの組み合わせを含む電子学習システム 600 は、ビックデータ機械学習アルゴリズム、ビックデータ解釈アルゴリズム、又はこれらの組み合わせを提供することができる。

30

選択ブロック 640、計算ブロック 660、アップデートブロック 670、又はこれらの組み合わせは、データや、プロセス、機能を選択するか、或いは分割することができる。

選択、分割、又はこれらの組み合わせはストレージ内コンピューティング (ISC) において機械学習プロセスや機械学習機能の負担を軽減 (offload) させることができる。

負担の軽減 (offload) は、高い複雑度の計算、高い入出力オーバーヘッド、又はこれらの組み合わせに対応する機能を分散させるか、或いは分割することができる。

#### 【0097】

例示的に、選択ブロック 640、計算ブロック 660、及びアップデートブロック 670、又はこれらの組み合わせは互いに分離されたものとして図示したが、いずれか 1 つのブロックは他のブロックとハードウェアの一部を共有できることが容易に理解できる。

40

例えば、選択ブロック 640、計算ブロック 660、及びアップデートブロック 670、又はこれらの組み合わせは、ハードウェアメモリ回路や、第 1 コントロールユニット 112、第 2 コントロールユニット 134、第 1 ストレージユニット 114、第 2 ストレージユニット 146、又はこれらの組み合わせのようなコンポーネントの一部を共有することができる。

#### 【0098】

さらに詳細に説明すれば、選択ブロック 640、計算ブロック 660、及びアップデートブロック 670、又はこれらの組み合わせは、相互分離されたブロックで図示している

50

が、ブロックの複数、組み合わせ、分布、分割、パーティショニング、又はこれらの組み合わせによる割り当ても可能であることは容易に理解できる。

例えば、選択ブロック 640、計算ブロック 660、及びアップデートブロック 670、又はこれらの組み合わせは、複数の装置に掛けて分布する複数のブロックを含むことができる。

#### 【0099】

選択ブロック 640、計算ブロック 660、及びアップデートブロック 670、又はこれらの組み合わせを含む電子システム 100 の電子学習システム 600 は、機械学習プロセスと機械学習機能の負担を軽減させることができる。

高い複雑度の計算、高い入出力オーバーヘッド、又はこれらの組み合わせに対応する機能は、ストレージ内コンピューティングのために部分的に分割されるか、或いは分割することができる。

#### 【0100】

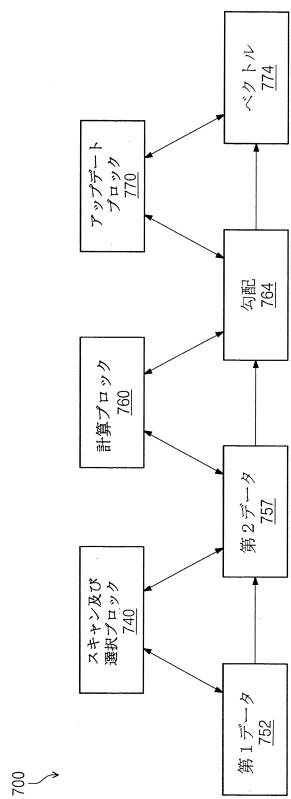

図 7 は、本発明の一実施形態による電子システム 100 の電子学習システム 700 の一部を示すブロック図である。

図 7 を参照すると、電子学習システム 700 は図 1 の第 1 装置 102、図 1 の第 2 装置 106、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

#### 【0101】

一実施形態において、電子学習システム 700 は、機械学習機能を提供する。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するようにするか、或は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

機械学習は、人工知能 AI の 1 つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である。

#### 【0102】

一実施形態において、電子学習システム 700 は、並列又は分散機械学習で部分データの画期的な向上を提供するためにデータトレーニングのような知的にデータを選択、又は分割する機能を提供することができる。

部分データの画期的な向上は、モデル、ベクトル、又はこれらの組み合わせのアップデート動作を向上させることができる。

知的な選択又は分割は、入出力データの増加にも高速の収斂特性を提供することができる。

#### 【0103】

例えば、電子学習システム 600 と同様に、電子学習システム 700 は、確率的勾配降下 (Stochastic Gradient Descent: 以下、SGD) 方法を含む勾配降下最適化方法のような確率的機械学習方式を含む機械学習メカニズムを提供することができる。

確率平均勾配アルゴリズムを含む確率的勾配降下法 (SGD) は、高速の収斂率、増加されたステップサイズ、並列処理で複数のプロセッサ各々によって独立的に駆動することができる点、高速の初期収斂特性と、確率的勾配降下法で低廉な反復費用を維持するための全勾配法の速い最終段階収斂特性を提供することができる。

#### 【0104】

一実施形態において、電子学習システム 700 は、スキーニング、選択、又はこれらの組み合わせを遂行するスキャン及び選択ブロック 730 を含むことができる。

スキャン及び選択ブロック 730 は、データを受信、スキャン、処理、選択、分割、伝送、又はこれらの組み合わせを遂行することができる。

10

20

30

40

50

例えば、スキャン及び選択ブロック 730 は、ローデータのような第1データ 752、トレーニングデータを処理するための入力データ、処理されたデータのような第2データ 757、第1データ 752 の中で知的に選択されたトレーニングデータ、第1データ 752 の部分データ、第1データ 752 の知的なアップデートデータ、第1データ 752 の中で知的に選択されたデータ、又はこれらの組み合わせを知的に処理することができる。

また、例えば、スキャン及び選択ブロック 740 は、第1データ 752 から第2データ 757 を知的に選択するか、或いは分割できる。

#### 【0105】

一実施形態において、電子学習システム 700 は、勾配 764 を計算するための計算ブロック 760、モデルのベクトル 774 をアップデートするためのアップデートブロック 770、又はこれらの組み合わせを含むことができる。10

アップデートブロック 770 は、すべてのモデルをアップデートすることができる。

スキャン及び選択ブロック 740、計算ブロック 760、及びアップデートブロック 770 は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

#### 【0106】

例えば、スキャン及び選択ブロック 740、計算ブロック 760、及びアップデートブロック 770、又はこれらの組み合わせを含む電子学習システム 700 は、ビックデータ機械学習アルゴリズム、ビックデータ解釈アルゴリズム、又はこれらの組み合わせを提供することができる。20

スキャン及び選択ブロック 740、計算ブロック 760、及びアップデートブロック 770、又はこれらの組み合わせは、データや、プロセス、機能を選択するか、或いは分割することができる。

選択、分割、又はこれらの組み合わせはストレージ内コンピューティング (ISC) において機械学習プロセスや機械学習機能の負担を軽減 (offload) させることができる。

負担の軽減 (offload) は高い複雑度の計算、高い入出力オーバーヘッド、又はこれらの組み合わせに対応する機能を分散させるか、或いは分割することができる。

#### 【0107】

例示的に、スキャン及び選択ブロック 740、計算ブロック 760、及びアップデートブロック 770、又はこれらの組み合わせは、互いに分離されたものとして図示したが、いずれか 1 つのブロックは他のブロックとハードウェアの一部を共有できることが容易に理解できる。

例えば、スキャン及び選択ブロック 740、計算ブロック 760、及びアップデートブロック 770、又はこれらの組み合わせは、ハードウェアメモリ回路や、第1コントロールユニット 112、第2コントロールユニット 134、第1ストレージユニット 114、第2ストレージユニット 146、又はこれらの組み合わせのようなコンポーネントの一部を共有することができる。

#### 【0108】

さらに詳細には、スキャン及び選択ブロック 740、計算ブロック 760、及びアップデートブロック 770、又はこれらの組み合わせは、相互分離されたブロックで図示しているが、ブロックの複数、組み合わせ、分布、分割、パーティショニング、又はこれらの組み合わせによる割り当ても可能であることは容易に理解できる。

例えば、スキャン及び選択ブロック 740、計算ブロック 760、及びアップデートブロック 770、又はこれらの組み合わせは、複数の装置に掛けて分布する複数のブロックを含むことができる。

#### 【0109】

電子システム 100 のスキャン及び選択ブロック 740、計算ブロック 760、及びアップデートブロック 770、又はこれらの組み合わせを含む電子学習システム 700 は、50

機械学習プロセスと機械学習機能の負担、特に、増加された入出力機能による負担を軽減させることができる。

高い複雑度の計算、高い入出力オーバーヘッド、又はこれらの組み合わせに対応する機能はストレージ内コンピューティングのために部分的に分割されるか、或いは分割することができる。

#### 【0110】

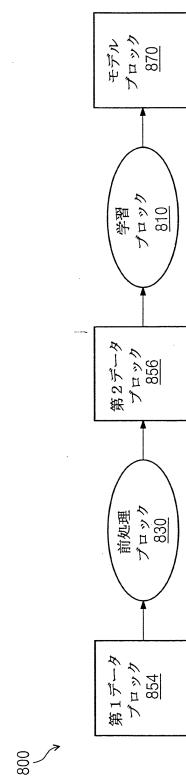

図8は、本発明の一実施形態による電子システム100の電子学習システム800の一部を示すブロック図である。

図8を参照すると、電子学習システム800は、図1の第1装置102、図1の第2装置106、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

10

#### 【0111】

一実施形態において、電子学習システム800は、機械学習機能を提供する。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するようにするか、或は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

機械学習は、人工知能AIの1つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である。

20

#### 【0112】

一実施形態において、電子学習システム800は、予測、推薦、スパム電子メールフィルタリングのようなフィルタリング、機械学習プロセス、機械学習機能、又はこれらの組み合わせを含む機械学習メカニズムを提供する。

ある実施形態では、ビックデータ分析のような機械学習を提供するための予測は、クリックや広告又は広告主の選択に基づき、品目の推薦、スパムフィルタリング、プロセス、又はこれらの組み合わせであってもよい。

#### 【0113】

一実施形態において、電子学習システム800は、ストレージ内コンピューティング (ISC) のみならず、システムプロセッサでの並列処理のためのクラスター・コンピューティングを含む並列又は分散機械学習メカニズムを含むことができる。

30

並列処理のための並列又は分散機械学習メカニズムは、図1の第1コントロールユニット112、図1の第2コントロールユニット134、図1の第1ストレージユニット114、図1の第2ストレージユニット146、図1の第1ストレージコントロールユニット132、図1の第2ストレージコントロールユニット152、図1の第1ストレージ媒体126、図1の第2ストレージ媒体142、又はこれらの組み合わせの中の少なくとも1つで実行することができる。

#### 【0114】

一実施形態において、電子学習システム800は、機械学習アルゴリズム、ビックデータ機械学習アルゴリズム、ビックデータ解釈アルゴリズム、又はこれらの組み合わせを具現又は実行するための機械学習ブロックのような学習ブロック810を含むことができる。

40

学習ブロック810は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせのようなハードウェアの一部で具現することができる。

#### 【0115】

一実施形態において、学習ブロック810は、並列又は分散処理、クラスター・コンピューティング、又はこれらの組み合わせを含むことができる。

学習ブロック810は、システムプロセッサ、ストレージコンピューティングプロセッサ

50

サ、第1コントロールユニット112、第2コントロールユニット134、第1ストレージコントロールユニット132、第2ストレージコントロールユニット152、第1ストレージユニット114、第2ストレージユニット146、又はこれらの組み合わせの中の少なくとも1つで実行することができる。

【0116】

一実施形態において、電子学習システム800は、図6の選択ブロック640や図7のスキャン及び選択ブロック740、又はこれらの組み合わせのような方式にデータを受信、スキャン、処理、選択、分割、伝送、又はこれらの組み合わせを含む学習プロセスを遂行するためのスキャン及びフィルタのような前処理ブロック830を含むことができる。

前処理ブロック830は、分割データの画期的向上のためのトレーニングデータのよう10

な知的に選択するか、或いは分割することができる。

画期的に向上された分割データは、モデル、ベクトル、又はこれらの組み合わせのアップデートを向上させることができる。

知的な選択又は分割は、増加された入出力データに対して高速の収斂特性を提供することができる。

前処理ブロック830は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

【0117】

一実施形態で、前処理ブロック830は、トレーニングデータのような第1データブロック854の第1データ、第2データブロック856の第2データ、又はこれらの組み合わせに対する処理、スキャン、フィルタリング、選択、分割、受信、伝送等を遂行することができる。

第2データブロック856は、第1データブロック854から知的に選択されたデータ、第1データブロック854から知的にアップデートされたデータ、第1データブロック854の部分データ、又はこれらの組み合わせを含むことができる。

第1データブロック854、第2データブロック856は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、第1ストレージユニット114、第2ストレージユニット146、第1ストレージ媒体126、第2ストレージ媒体142、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

【0118】

例えば、前処理ブロック830は、第1データブロック854から第2データブロック856に提供する一部又は全てに対するスキャン、フィルタリング、選択、分割、受信、伝送、又はこれらの組み合わせを遂行することができる。

第1データブロック854は、ローデータ、トレーニングデータ、初期データ、又はこれらの組み合わせを含むことができる。

前処理ブロック830は、第2データブロック856に提供するために第1データブロック854の一部又はすべてのデータをスキャン及びフィルタリングすることができる。

ここにはフィルタリングされたデータ、選択されたデータ、分割されたデータ、トレーニングデータ、部分データ、部分トレーニングデータ、又はこれらの組み合わせを含むことができる。

【0119】

一実施形態において、学習ブロック810は、モデルブロック870に少なくとも一部のデータ、モデルパラメーター、ベクトル、すべてのモデル、又はこれらの組み合わせを提供するために第2データブロック865の一部又はすべてのデータに対するスキャン、フィルタリング、選択、分割、受信、伝送、又はこれらの組み合わせを遂行することができる。

モデルブロック870は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、第1

10

20

30

40

50

ストレージユニット 114、第2ストレージユニット 146、第1ストレージ媒体 126、第2ストレージ媒体 142、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

【0120】

一実施形態において、モデルブロック 870 は、機械学習データ、分析されたピックデータ、ピックデータ解釈アルゴリズム、又はこれらの組み合わせを格納するストレージ装置を含むことができる。

モデルブロック 870 は、ストレージ装置、メモリ装置、システムプロセッサ、ストレージ内コンピューティング (ISC) プロセッサ、第1ストレージユニット 114、第2ストレージユニット 146、第1コントロールユニット 112、第2コントロールユニット 134、第1ストレージコントロールユニット 132、第2ストレージコントロールユニット 152、又はこれらの組み合わせ内で具現することができる。

【0121】

例えば、第1データブロック 854 は、未処理されるか、或いは部分処理されたデータを格納するストレージ装置を含むことができる。

第1データブロック 854 は、ストレージ装置、メモリ装置、第1ストレージユニット 114、第2ストレージユニット 146、第1ストレージ媒体 126、第2ストレージ媒体 142、又はこれらの組み合わせを含むことができる。

第2データブロック 856 は、第1データブロック 854 での処理で未処理されたデータを処理したデータを格納するためのストレージ装置を含むことができる。

第2データブロック 856 は、ストレージ装置、メモリ装置、第1ストレージユニット 114、第2ストレージユニット 146、第1ストレージ媒体 126、第2ストレージ媒体 142、又はこれらの組み合わせによって具現することができる。

【0122】

例示的に、学習ブロック 810、前処理ブロック 830、第1データブロック 854、第2データブロック 856、モデルブロック 870、又はこれらの組み合わせは各々分離されたブロックで図示しているが、いずれか1つのブロックは他の1つのブロックとハードウェアの一部を共有できることが容易に理解できる。

例えば、第1データブロック 854、第2データブロック 856、モデルブロック 870、又はこれらの組み合わせは、ハードウェアメモリ回路や、第1ストレージユニット 114、第2ストレージユニット 146、第1ストレージ媒体 126、第2ストレージ媒体 142、又はこれらの組み合わせのようなコンポーネントの一部を共有することができる。

【0123】

さらに具体的に、学習ブロック 810、前処理ブロック 830、モデルブロック 870、又はこれらの組み合わせは相互分離されたブロックで図示しているが、ブロックの複数、組み合わせ、分布、分割、パーティショニング、又はこれらの組み合わせによる割り当て也可能であることは容易に理解できる。

例えば、学習ブロック 810、前処理ブロック 830、モデルブロック 870、又はこれらの組み合わせは、複数の装置に掛けて分布する複数のブロックを含むことができる。

【0124】

電子学習システム 800 の学習ブロック 810、前処理ブロック 830、第1データブロック 854、第2データブロック 856、モデルブロック 870、又はこれらの組み合わせは、並列又は分散処理、クラスターコンピューティング、又はこれらの組み合わせを提供することができる。

電子学習システム 800 は、前処理ブロック 830、モデルブロック 870、又はこれらの組み合わせに対応する機能はストレージ内コンピューティングのために部分的に分割されるか、或いは分割することができる。

【0125】

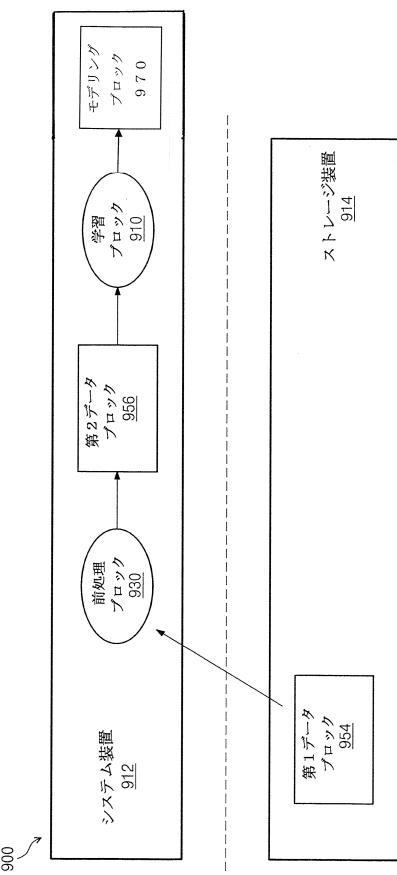

図9は、本発明の一実施形態による電子システム 100 の電子学習システム 900 の一

10

20

30

40

50

部を示すブロック図である。

図9を参照すると、電子学習システム900は、図1の第1装置102、図1の第2装置106、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

#### 【0126】

一実施形態において、電子学習システム900は、機械学習機能を提供する。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するよう10するか、或は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

機械学習は、人工知能AIの1つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である。

#### 【0127】

一実施形態において、電子学習システム900は、ストレージ内コンピューティング (ISC) のみならず、システムプロセッサでの並列処理のためのクラスター・コンピューティングを含む並列又は分散機械学習メカニズムを含むことができる。

並列処理のための並列又は分散機械学習メカニズムは、図1の第1コントロールユニット112、図1の第2コントロールユニット134、図1の第1ストレージユニット114、図1の第2ストレージユニット146、図1の第1ストレージコントロールユニット132、図1の第2ストレージコントロールユニット152、図1の第1ストレージ媒体126、図1の第2ストレージ媒体142、又はこれらの組み合わせの中の少なくとも1つで実行することができる。

例示的に、電子学習システム900は、学習ブロック910がシステム装置912の一部として図示しているが、ストレージ装置914は、学習ブロック910のような学習ブロックを含む他のブロックを含むことが容易に理解できる。

#### 【0128】

一実施形態において、電子学習システム900は、データをスキャン、フィルタリング、選択、分割、伝送、処理、受信、又はこれらの組み合わせのためのスキャン及びフィルタブロックのような前処理ブロック930を含むことができる。

前処理ブロック930は、分割データの画期的向上のためのトレーニングデータのような知的に選択するか、或いは分割することができる。

画期的に向上された分割データは、モデル、ベクトル、又はこれらの組み合わせのアップデートを向上させることができる。

知的な選択又は分割は、増加された入出力データに対して高速の収斂特性を提供することができる。

前処理ブロック930は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

#### 【0129】

例えれば、一実施形態において、前処理ブロック930は、トレーニングデータのような第1データブロック954の第1データ、第2データブロック956の第2データ、又はこれらの組み合わせに対する処理、スキャン、フィルタリング、選択、分割、受信、伝送等を遂行することができる。

第2データブロック956は、第1データブロック954から知的に選択されたデータ、第1データブロック954から知的にアップデートされたデータ、第1データブロック954の部分データ、又はこれらの組み合わせを含むことができる。

第1データブロック954、第2データブロック956は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical

10

20

30

40

50

System)、受動素子、第1ストレージユニット114、第2ストレージユニット146、第1ストレージ媒体126、第2ストレージ媒体142、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

【0130】

一実施形態において、学習ブロック910は、第2データブロック956のデータに対して処理、分析、予測、推薦、フィルタリング、学習、受信、伝送、又はこれらの組み合わせを遂行することができる。

例えば、電子学習システム900は、予測、推薦、フィルタリング、機械学習プロセス、機械学習機能、又はこれらの組み合わせを遂行することができる。

ある実施形態では、ピックデータ分析のような機械学習を提供するための予測は、クリックや広告又は広告主の選択に基づき、品目の推薦、スパムフィルタリング、プロセス、又はこれらの組み合わせであってもよい。

【0131】

学習ブロック910、前処理ブロック930、第1データブロック954、第2データブロック956、システム装置912、ストレージ装置914、又はこれらの組み合わせを含む電子学習システム900は、並列又は分散処理、クラスター・コンピューティング等を含む機械学習プロセスと機械学習機能を提供することができる。

前処理ブロック930、モデリングブロック970、又はこれらの組み合わせはシステム装置912、ストレージ装置914、又はこれらの組み合わせによって具現することができる。

【0132】

図10は、本発明の一実施形態による電子システム100の電子学習システム1000の一部を示すブロック図である。

図10を参照すると、電子学習システム1000は、図1の第1装置102、図1の第2装置106、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

例えば、後述する割り当ての決定のための条件や環境での電子システム100に基づいてシステムコントロールユニット又は中央処理装置(CPU)のようなストレージ装置やシステム装置によって前処理機能を遂行することができる。

【0133】

一実施形態において、電子学習システム1000は、機械学習機能を提供する。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するようにするか、又は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

機械学習は、人工知能AIの1つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である。

【0134】

一実施形態において、電子学習システム1000は、予測、推薦、フィルタリング、機械学習プロセス、機械学習機能、又はこれらの組み合わせを含む機械学習メカニズムを提供する。

ある実施形態では、ピックデータ分析のような機械学習を提供するための予測は、クリックや広告又は広告主の選択に基づき、品目の推薦、スパムフィルタリング、プロセス、又はこれらの組み合わせであってもよい。

【0135】

例えば、電子学習システム1000は、ストレージ内コンピューティング(ISC)のみならず、システムプロセッサでの並列処理のためのクラスター・コンピューティングを含む並列又は分散機械学習メカニズムを含むことができる。

10

20

30

40

50

並列処理のための並列又は分散機械学習メカニズムは、図1の第1コントロールユニット112、図1の第2コントロールユニット134、図1の第1ストレージユニット114、図1の第2ストレージユニット146、図1の第1ストレージコントロールユニット132、図1の第2ストレージコントロールユニット152、図1の第1ストレージ媒体126、図1の第2ストレージ媒体142、又はこれらの組み合わせの中の少なくとも1つで実行することができる。

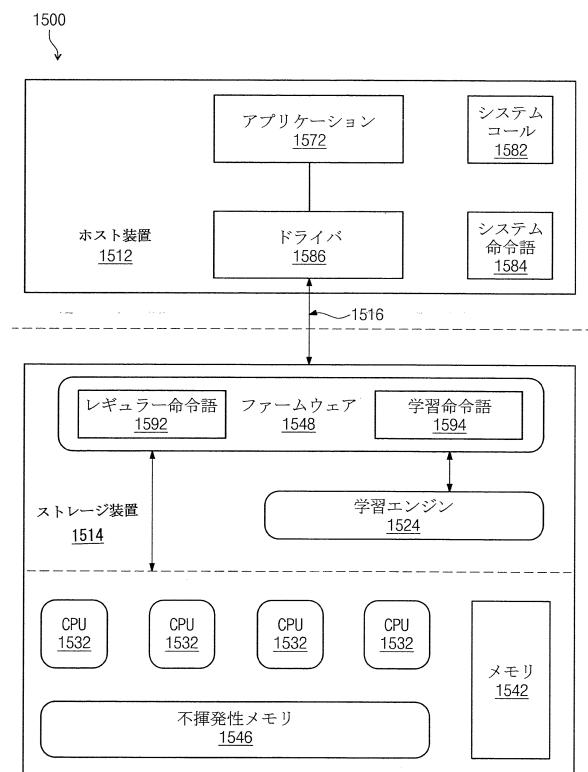

【0136】

一実施形態において、電子学習システム1000は、システム装置1012、ストレージ装置1014、インターフェイス1016、又はこれらの組み合わせを含むことができる。

10

システム装置1012とストレージ装置1014とはインターフェイス1016を通じて互いに又は内部的に通信することができる。

システム装置1012、ストレージ装置1014、インターフェイス1016は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせのようなハードウェアの一部で具現することができる。

【0137】

一実施形態において、電子学習システム1000は、機械学習アルゴリズム、ピックデータ機械学習アルゴリズム、ピックデータ解釈アルゴリズム、又はこれらの組み合わせを具現又は実行するための機械学習ブロックのような学習ブロック1020を含むことができる。

20

電子学習システム1000は、ストレージ学習ブロック1024、システム学習ブロック1028、又はこれらの組み合わせを含むことができる。

ストレージ学習ブロック1024、システム学習ブロック1028、又はこれらの組み合わせは、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせのようなハードウェアの一部で具現することができる。

【0138】

例えば、ストレージ学習ブロック1024、システム学習ブロック1028、又はこれらの組み合わせは、並列又は分散処理、クラスター・コンピューティング、又はこれらの組み合わせを含むことができる。

30

ストレージ学習ブロック1024、システム学習ブロック1028、又はこれらの組み合わせは、システムプロセッサ、ストレージコンピューティングプロセッサ、第1コントロールユニット112、第2コントロールユニット134、第1ストレージコントロールユニット132、第2ストレージコントロールユニット152、第1ストレージユニット114、第2ストレージユニット146、又はこれらの組み合わせの中の少なくとも1つで実行することができる。

【0139】

一実施形態において、電子学習システム1000は、データを受信、スキャン、処理、選択、分割、伝送、又はこれらの組み合わせを含む学習プロセスを遂行するためのスキャン及びフィルタのような前処理ブロック1030を含むことができる。

40

前処理ブロック1030は、分割データの画期的向上のためにトレーニングデータのようなデータを知的に選択するか、或いは分割することができる。

画期的に向上された分割データは、モデル、ベクトル、又はこれらの組み合わせのアップデートを向上させることができる。

知的な選択又は分割は、増加された入出力データに対して高速の収斂特性を提供することができる。

前処理ブロック1030は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

50

## 【0140】

一実施形態において、プロセシングブロックは、ストレージコントロールユニット1032を含むことができる。

ストレージコントロールユニット1032は、第1ストレージコントロールユニット132又は第2ストレージコントロールユニット152と同様にプロセッサ、ASIC (Application Specific Integrated Circuit)、埋め込み型プロセッサ、マイクロプロセッサ、ハードウェア制御ロジック、ハードウェア有限状態マシン (FSM)、デジタル信号処理器 (DSP)、又はこれらの組み合わせであってもよい。

## 【0141】

10

同様に、システムコントロールユニット1034は、第1コントロールユニット112又は第2コントロールユニット134のような方式で、プロセッサ、ASIC (Application Specific Integrated Circuit)、埋め込み型プロセッサ、マイクロプロセッサ、ハードウェア制御ロジック、ハードウェア有限状態マシン (FSM)、デジタル信号処理器 (DSP)、又はこれらの組み合わせであってもよい。

## 【0142】

一実施形態において、ストレージ装置1014の前処理ブロック1030は、スキャン、フィルタ、学習、又はこれらの組み合わせのような機能1040でシステムコントロールユニット1034からストレージコントロールユニット1032に負担を軽減させることができる。

20

同様に、ホストは、これらの機能1040をストレージコントロールユニット1032に負担させることができる。

機能1040は、機械学習、ビックデータ処理、ビックデータ分析、ビックデータ分析アルゴリズム、又はこれらの組み合わせを含むことができる。

機能1040、システム装置1012、ストレージ装置1014、又はこれらの組み合わせは、スマートソリッドステートストレージ装置 (SSD) のようなストレージ装置1014に分散機械学習のためのスケジューリングアルゴリズムを提供することができる。

## 【0143】

一実施形態において、電子学習システム1000は、オフロード (offload) 可能である機械学習コンポーネントや機能を含む機能1040を含むか、或いは定義することができる。

30

オフロード可能である機械学習コンポーネントや機能は、メイン機械学習アルゴリズム、フィルタ、スキャン、ある機械学習アルゴリズム、及びこれらの組み合わせを含むことができる。

また、電子学習システム1000は、オフロード可能である機械学習コンポーネントや機能を分離、分割、選択することができる。

オフロード可能である機械学習コンポーネントや機能は、1つ以上の反複学習のために分離されるか、分割されるか、或は選択され得る。

電子学習システム1000は、動的スケジューリングのためにモニターリング機能を提供することができる。

40

## 【0144】

例示的に、電子学習システム1000の前処理ブロック1030がストレージ装置1014の内部に存在することとして図示したが、システム装置1012がスキャン、フィルタ、前処理ブロック1030の機能を含むことが容易に理解できる。

ストレージ装置1014、システム装置1012、及びこれらの組み合わせは所定の数や形態のブロックをさらに含むことができる。

例えば、前処理ブロック1030は、第1データブロック1052、第2データブロック1054、第3データブロック1056のデータをトレーニングするか、或は選択する等の処理をすることができる。

50

## 【0145】

前処理ブロック1030は、データトレーニングブロックのような第1データブロック1052から受信されたデータを処理、選択、分割して、第2データブロック1054や第3データブロック1056に提供することができる。

第2データブロック1054や第3データブロック1056、又はこれらの組み合わせは、第1データブロック1052から提供されたデータを知的に選択するデータブロック、知的にアップデートするデータブロック、部分的にデータを格納するブロックを含むことができる。

## 【0146】

一実施形態において、第1データブロック1052、第2データブロック1054、第3データブロック1056、及びこれらの組み合わせは、機械学習のための選択データを提供することができる。 10

第1データブロック1052、第2データブロック1054、第3データブロック1056、又はこれらの組み合わせは、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、第1ストレージユニット114、第2ストレージユニット146、第1ストレージ媒体126、第2ストレージ媒体142、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

## 【0147】

一実施形態において、ストレージ学習ブロック1024は、第3データブロック1056のデータに対して処理、分析、予測、推薦、フィルタリング、学習、受信、伝送、又はこれらの組み合わせを遂行することができる。 20

例えば、電子学習システム1000は、予測、推薦、フィルタリング、機械学習プロセス、機械学習機能、又はこれらの組み合わせを遂行することができる。

ある実施形態では、ピックデータ分析のような機械学習を提供するための予測はクリックや広告又は広告主の選択に基づき、品目の推薦、スパムフィルタリング、プロセス、又はこれらの組み合わせであってもよい。

## 【0148】

一実施形態において、電子学習システム1000のシステム装置1012は、システム装置1012の外部で遂行される機械学習プロセスを含む機械学習のためのアプリケーションプログラムインターフェイス(API)を含むプログラムインターフェイス1082を含むことができる。 30

例えば、プログラムインターフェイス1082は、プログラム言語、C、C++、スクリプト言語、Perl、Python、又はこれらの組み合わせを含むことができる。

プログラムインターフェイス1082は、処理、スキャン、フィルタ、分析、圧縮、Karush-Kuhn-Tucker (KKT) フィルタリング、Karush-Kuhn-Tucker (KKT) ベクトルエラーフィルタリング、ランダムフィルタリング、予測、推薦、学習等を含むすべての機械学習プロセスやアルゴリズムのためのピックデータを含むデータを適用することができる。

## 【0149】

一実施形態において、システム装置1012、ストレージ装置1014、又はこれらの組み合わせは、ボトルネック現象、資源飽和、圧力、資源の制限等の問題を識別することができる。 40

例えば、インターフェイス1016は、飽和された入出力状態を有すると、電子学習システム1000の減らされた入出力を提供する。

システム装置1012、ストレージ装置1014、これらの組み合わせは、インターフェイス1016の入出力飽和状態を識別し、機能1040の機能をストレージコントロールユニット1032、システムコントロールユニット1034、又はこれらの組み合わせで知的に軽減、スロットル、並列化、分散処理することができる。

## 【0150】

一実施形態において、知的に軽減、スロットル、並列化、分散処理するシステム装置1012、ストレージ装置1014、これらの組み合わせは、ボトルネック現象、資源飽和、圧力、資源限界等を軽減させることができる。

負担の軽減事項は、電子学習システム1000、電子システム100に画期的に高いスループットを提供することができる。

例えば、プログラムインターフェイス1082は“LEARN(学習)“命令語を含むことができる。

“LEARN(学習)“命令語は、並列又は分散処理のための機能1040のプログラムインターフェイス1082を遂行するためのメタデータを含むことができる。

システム装置1012、ストレージ装置1014、又はこれらの組み合わせは、機能1040、スケジューリングアルゴリズム、機能割り当て、データ割り当て等を遂行するための高級プログラム言語を含むことができる。

10

#### 【0151】

一実施形態において、スケジューラーブロック1084は、ノード当たりアドホックスタイル(ad-hoc style per-node)スケジューラーと第1コントロールユニット112、第2コントロールユニット134等の機械学習に対する選択、分割、分離、又はこれらの組み合わせを遂行する第1ストレージコントロールユニット132、第2ストレージコントロールユニット152、又はこれらの組み合わせのようなストレージ装置1014のコントロールユニットを含むことができる。

電子学習システム1000は、入出力飽和のような入出力ボトルネック現象に基づいてスキャン及びフィルタリング、メイン反複アルゴリズム等の負担を減らすためにSSD駆動可能である二進コードを前処理ブロック1030に提供することができる。

20

#### 【0152】

例えば、前処理ブロック1030は、入出力ボトルネック現象、入出力飽和のようなボトルネック現象に対する判断にしたがって第1データブロック1052の第1データのような追加データに対するフィルタリングを遂行することができる。

前処理ブロック1030は、インターフェイス1016の帯域幅に追加的な帯域幅が必要である状況で第1データを含むデータに対して少ないデータをフィルタリングすることができる。

スケジューラーブロック1084を含む電子学習システム1000は、スキャン及びフィルタリングに対する負担軽減の後にも追加的な入出力ボトルネック現象が検出されれば、メイン反複アルゴリズムの少なくとも一部に対する負担軽減を決定することができる。

30

入出力ボトルネック現象に対する決定のために、データは、システム装置1012、ストレージ装置1014等によってランダムに又は規則的に復旧することができる。

#### 【0153】

この実施形態において、プログラムインターフェイス1082、機能1040等を遂行するするためにプログラムインターフェイス1082、スケジューラーブロック1084等は新しいシステムコール(system call)、拡張システムコール等を含むシステムコールを含むことができる。

プログラムインターフェイス1082、機能1040等は、システム情報1086に基づいて具現することができる。

40

追加的に、前処理ブロック1030は、システム情報1086に基づいて第1データに対する知的な選択、分割、フィルタ等の動作を遂行することができる。

#### 【0154】

一実施形態において、システム情報1086は、システム使用率、システム帯域幅、システムパラメーター、入出力使用率、メモリ使用率、メモリアクセス、ストレージ使用率、ストレージアクセス、コントロールユニット使用率、コントロールユニットアクセス、CPU使用率、CPUアクセス、メモリプロセッサ使用率、メモリプロセスアクセス等であってもよい。

システム情報1086は、集積回路、集積回路コア、集積回路コンポーネント、MEM

50

S (Microelectromechanical System)、受動素子、第1ストレージ媒体126、第2ストレージ媒体142、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

【0155】

一実施形態において、プログラムインターフェイス1082、機能1040、スケジューラープロック1084、又はこれらの組み合わせは、ウェブサービスインターフェイスを含むサービスインターフェイス1088と通信することができる。

例えば、サービスインターフェイス1088は、電子学習システム1000、電子システム100、又はこれらの組み合わせの外部への通信サービスを提供することができる。

サービスインターフェイス1088は、REST (Representational state transfer)、SOAP (simple object access protocol) のようなデータを交換するためのプロトコルスペック、電子システム100の外部サービス、電子システム100の外部プロトコル、電子システム100の外部アーキテクチャのようなクライアント・サーバーアプリケーションを構築するためのアーキテクチャと通信することができる。

【0156】

一実施形態において、ストレージ装置1014は、フラッシュメモリ、ソリッドステートドライブ (SSD)、相変化メモリ (PCM)、スピンドルクラッシュアクセスメモリ (STT-RAM)、抵抗性ランダムアクセスメモリ (ReRAM)、磁気抵抗ランダムアクセスメモリ (MRAM)、所定の形態のストレージ装置、所定の形態のメモリ装置等を含むことができる。

ストレージ装置1014、システム装置1012はメモリバス、SAS (serial attached small computer system interface)、SATA (serial attached advanced technology)、NVMe (non-volatile memory express)、光チャンネル、イーサネット (登録商標) (Ethernet (登録商標))、RDMA (remote direct memory access) 等を含むインターフェイス1016と接続されることができる。

【0157】

例示的に、電子学習システム1000は、各々1つのコンポーネントで図示しているが、任意の数のコンポーネントが含まれることは容易に理解できる。

例えば、電子学習システム1000は、各々1つ以上のストレージ装置1014、第1データブロック1052、第2データブロック1054、第3データブロック1056を含むことができる。

予測、推薦、フィルタリング、機械学習プロセス、機械学習機能、又はこれらの組み合わせは、ピックデータ解析法のような機械学習メカニズムを提供することができる。

同様に、システム学習ブロック1028、ストレージ学習ブロック1024等は、第2データブロック1054のデータに対する予測、推薦、フィルタリング、機械学習プロセス、機械学習機能等のために処理、分析、予測、推薦、フィルタリング、学習、受信、伝送等を遂行することができる。

【0158】

システム装置1012、ストレージ装置1014を含む電子システム100の電子学習システム1000は、知的なプロセス、スロットリング、並列処理、分散処理等で発生する問題を識別し、負担を減らすことができる。

知的なプロセス分担、スロットリング、並列処理、分散処理等は、少なくともインターフェイス1016でのボトルネック現象、資源飽和、作業累積等を軽減させ、機能1040を遂行するためのストレージ装置1014での高い帯域幅使用率を提供することができる。

【0159】

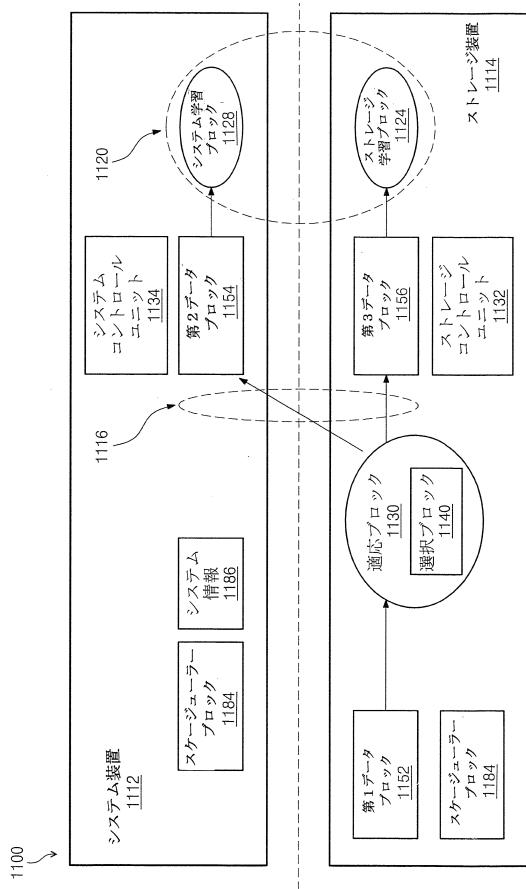

図11は、本発明の一実施形態による電子システム100の電子学習システム1100

10

20

30

40

50

の一部を示すブロック図である。

図11を参照すると、電子学習システム1100は、図1の第1装置102、図1の第2装置106、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

#### 【0160】

一実施形態において、電子学習システム1100は、機械学習機能を提供する。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するよう10するか、或は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

機械学習は、人工知能AIの1つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である

#### 【0161】

一実施形態において、電子学習システム1100は、予測、推薦、フィルタリング、機械学習プロセス、機械学習機能、又はこれらの組み合わせを含む機械学習メカニズムを提供する。

ある実施形態では、ビックデータ分析のような機械学習を提供するための予測は、クリックや広告又は広告主の選択に基づき、品目の推薦、スパムフィルタリング、プロセス、又はこれらの組み合わせであってもよい。

#### 【0162】

例えば、電子学習システム1100は、ストレージ内コンピューティング (ISC) のみならず、システムプロセッサでの並列処理のためのクラスター-コンピューティングを含む並列又は分散機械学習メカニズムを含むことができる。

並列処理のための並列又は分散機械学習メカニズムは、図1の第1コントロールユニット112、図1の第2コントロールユニット134、図1の第1ストレージユニット114、図1の第2ストレージユニット146、図1の第1ストレージコントロールユニット132、図1の第2ストレージコントロールユニット152、図1の第1ストレージ媒体126、図1の第2ストレージ媒体142、又はこれらの組み合わせの中の少なくとも1つで実行することができる。

#### 【0163】

一実施形態において、電子学習システム1100は、システム装置1112、ストレージ装置1114、インターフェイス1116、又はこれらの組み合わせを含むことができる。

システム装置1112とストレージ装置1114とはインターフェイス1116を通じて互いに又は内部的に通信することができる。

システム装置1112、ストレージ装置1114、インターフェイス1116は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせのようなハードウェアの一部で具現することができる。

#### 【0164】

一実施形態において、電子学習システム1100は、機械学習アルゴリズム、ビックデータ機械学習アルゴリズム、ビックデータ解釈アルゴリズム、又はこれらの組み合わせを具現又は実行するための機械学習ブロックのような学習ブロック1120を含むことができる。

電子学習システム1100は、ストレージ学習ブロック1124、システム学習ブロック1128、又はこれらの組み合わせを含むことができる。

ストレージ学習ブロック1124、システム学習ブロック1128、又はこれらの組み合わせは、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせを含むことができる。

10

20

30

40

50

electromechanical System)、受動素子、又はこれらの組み合わせのようなハードウェアの一部で具現することができる。

【0165】

例えば、ストレージ学習ブロック1124、システム学習ブロック1128、又はこれらの組み合わせは、並列又は分散処理、クラスター・コンピューティング、又はこれらの組み合わせを含むことができる。

ストレージ学習ブロック1124、システム学習ブロック1128、又はこれらの組み合わせは、システムプロセッサ、ストレージ・コンピューティング・プロセッサ、第1コントロールユニット112、第2コントロールユニット134、第1ストレージコントロールユニット132、第2ストレージコントロールユニット152、第1ストレージユニット114、第2ストレージユニット146、又はこれらの組み合わせの中の少なくとも1つで実行することができる。

【0166】

一実施形態において、電子学習システム1100は、データをスキャン、フィルタリング、選択、分割、処理、受信、伝送、又はこれらの組み合わせを含む適応処理ブロックのような適応ブロック1130を含むことができる。

スキャン及びフィルタブロックのような適応ブロック1130は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

例えば、適応プロセシングブロックのような適応ブロック1130は、分割データの画期的な向上のためにトレーニングデータのようなデータを知的に選択するか、或いは分割することができる。

画期的に向上された分割データは、モデル、ベクトル、又はこれらの組み合わせのアップデートを向上させることができる。

知的な選択又は分割は、増加された入出力データに対して高速の収斂特性を提供することができる。

【0167】

一実施形態において、適応ブロック1130は、ストレージコントロールユニット1132を含むことができる。

ストレージコントロールユニット1132は、第1ストレージコントロールユニット132又は第2ストレージコントロールユニット152と同様にプロセッサ、ASIC (Application Specific Integrated Circuit)、埋め込み型プロセッサ、マイクロプロセッサ、ハードウェア制御ロジック、ハードウェア有限状態マシン (FSM)、デジタル信号処理器 (DSP)、又はこれらの組み合わせであってもよい。

【0168】

同様に、システムコントロールユニット1134は、第1コントロールユニット112又は第2コントロールユニット134のような方式でプロセッサ、ASIC (Application Specific Integrated Circuit)、埋め込み型プロセッサ、マイクロプロセッサ、ハードウェア制御ロジック、ハードウェア有限状態マシン (FSM)、デジタル信号処理器 (DSP)、又はこれらの組み合わせであってもよい。

【0169】

一実施形態において、適応ブロック1130は、適応選択率、適応学習率、図7の勾配(764)、等を計算する選択ブロック1140を含むことができる。

ストレージ装置1114の適応ブロック1130は、システムコントロールユニット1134からストレージコントロールユニット1132に、ストレージコントロールユニット1132からシステムコントロールユニット1134に伝達されるデータのスキャン、フィルタ、選択、分割、処理、受信、伝送、学習等の負担軽減機能を提供することができ

10

20

30

40

50

る。

これら機能は、機械学習、ビックデータ処理、バックデータ解釈、ビックデータ解釈アルゴリズム、又はこれらの組み合わせであってもよい。

例えば、適応ブロック1130は、適応選択率によるスキャン及び選択のみならず、適応学習率によるシステム資源使用率のような機能のためにシステム資源使用率、ストレージ帯域幅を決定することができる。

適応選択率、学習率等に基づいて、適応ブロック1130は、ホスト演算とストレージ演算とを負担軽減率にしたがって制御することができる。

#### 【0170】

一実施形態において、適応ブロック1130、システム装置1112、ストレージ装置1114、又はこれらの組み合わせは、システム装置1112、ストレージ装置1114、又はこれらの組み合わせに対する分散機械学習のためのスケジューリングを提供することができる。

スマートSSDのようなストレージ装置1114は、機械学習の負担軽減、機械学習の分散、機械学習の分割等を提供することができる。

#### 【0171】

一実施形態において、電子学習システム1100は、オフロード可能である機械学習コンポーネントや機能を含むか、或いは定義することができる。

オフロード可能である機械学習コンポーネントや機能は、メイン機械学習アルゴリズム、フィルタ、スキャン、所定の機械学習アルゴリズム、及びこれらの組み合わせを含むことができる。

また、電子学習システム1100は、オフロード可能である機械学習コンポーネントや機能を分離、分割、選択することができる。

オフロード可能である機械学習コンポーネントや機能は、1つ以上の反復学習のために分離されるか、分割されるか、或は選択され得る。

電子学習システム1100は、動的スケジューリングのためにモニターリング機能を提供することができる。

#### 【0172】

例示的に、電子学習システム1100は、ストレージ装置1114の適応ブロック1130を含むこととして図示しているが、システム装置1112も適応ブロック1130、選択ブロック1140のような選択ブロック、機能、スキャンのためのブロック、フィルタリングのためのブロック、又はこれらの組み合わせを含むことが容易に理解できる。

ストレージ装置114、システム装置1112、又はこれらの組み合わせは任意の数や形態のブロックに提供することができる。

#### 【0173】

一実施形態において、適応ブロック1130は、第1データブロック1152、第2データブロック1154、第3データブロック1156のデータをトレーニングするか、或は選択する等の処理をすることができる。

適応ブロック1130は、データトレーニングブロックのような第1データブロック1152から受信されたデータを処理、選択、分割して、第2データブロック1154や第3データブロック1156に提供することができる。

第2データブロック1154や第3データブロック1156、又はこれらの組み合わせは、第1データブロック1152から提供されたデータを知的に選択するデータブロック、知的にアップデートするデータブロック、部分的にデータを格納するブロックを含むことができる。

#### 【0174】

第1データブロック1152、第2データブロック1154、第3データブロック1156、及びこれらの組み合わせは、機械学習のための選択データを提供することができる。

第1データブロック1152、第2データブロック1154、第3データブロック1156

10

20

30

40

50

56、又はこれらの組み合わせは、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、第1ストレージユニット114、第2ストレージユニット146、第1ストレージ媒体126、第2ストレージ媒体142、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

【0175】

一実施形態において、ストレージ学習ブロック1124は、第3データブロック1156のデータに対して処理、分析、予測、推薦、フィルタリング、学習、受信、伝送、又はこれらの組み合わせを遂行することができる。

例えば、電子学習システム1100は、予測、推薦、フィルタリング、機械学習プロセス、機械学習機能、又はこれらの組み合わせを遂行することができる。 10

ある実施形態では、ピックデータ分析のような機械学習を提供するための予測は、クリックや広告又は広告主の選択に基づき、品目の推薦、スパムフィルタリング、プロセス、又はこれらの組み合わせであってもよい。

同様に、システム学習ブロック1128は、予測、推薦、フィルタ、機械学習プロセス、機械学習機能等を提供するために第2データブロック1154のデータを処理、予測、推薦、フィルタリング、学習、受信、伝送、又はこれらの組み合わせによって処理することができる。

【0176】

一実施形態において、電子学習システム1100のシステム装置1112は、並列又は分散機械学習のためにシステム装置1112の外部で遂行される機械学習プロセスを含む機械学習のためのアプリケーションプログラムインターフェイス(API)を含む図10のプログラムインターフェイス1082を含むことができる。 20

命令語としてはピックデータのようなデータに処理、スキャン、フィルタ、分析、圧縮、Karush-Kuhn-Tucker (KKT) フィルタリング、Karush-Kuhn-Tucker (KKT) ベクトルエラーフィルタリング、ランダムフィルタリング、予測、推薦、学習等を含むすべての機械学習プロセスやアルゴリズムを適用することができる。

【0177】

一実施形態において、システム装置1112、ストレージ装置1114、又はこれらの組み合わせは、ボトルネック現象、資源飽和、圧力、資源の制限等の問題を識別することができる。 30

例えば、インターフェイス1116は、飽和された入出力状態を有すると、電子学習システム1100の減らされた入出力を提供する。

システム装置1112、ストレージ装置1114、これらの組み合わせは、インターフェイス1116の入出力飽和状態を識別し、図10の機能1040のような機能をストレージコントロールユニット1132、システムコントロールユニット1134、又はこれらの組み合わせで知的に軽減、スロットル、並列化、分散処理することができる。

【0178】

一実施形態において、知的に負担軽減、スロットル、並列化、分散、又はこれらの組み合わせを遂行する適応ブロック1130、システム装置1112、ストレージ装置1114、又はこれらの組み合わせは、ボトルネック現象、資源飽和、圧力、資源限界等を軽減させることができる。 40

負担の軽減事項は、電子学習システム1100、電子システム100に画期的に高いスループットを提供することができる。

【0179】

一実施形態において、システム装置1112、ストレージ装置1114、及びこれらの組み合わせは、これら機能を実行するための高級プログラム言語、スケジューリングアルゴリズム、割り当て機能、データ割り当て、等を遂行するための高級プログラム言語のようなスケジューラーブロック1184を含むことができる。 50

スケジューラーブロック 1184 は、ノード当たりアドホックスタイルスケジューラーと、第1コントロールユニット 112、第2コントロールユニット 134 等のようなシステム装置 1112 の制御ユニットによる並列又は分散機械学習のための選択、分割、分離、又はこれらの組み合わせを遂行する第1ストレージコントロールユニット 132、第2ストレージコントロールユニット 152、又はこれらの組み合わせのようなストレージ装置 1114 のコントロールユニットにアクセス又は制御することができる。

#### 【0180】

電子学習システム 1100 は、入出力飽和のような入出力ボトルネック現象に基づいてスキャン及びフィルタリング、メイン反復アルゴリズム等の負担を減らすために SSD 駆動可能である二進コードを適応ブロック 1130 に提供することができる。 10

例えば、適応ブロック 1130 は、入出力ボトルネック現象、入出力飽和のようなボトルネック現象に対する判断にしたがって第1データブロック 1152 の第1データのような追加データに対するフィルタリングを遂行することができる。

適応ブロック 1130 は、インターフェイス 1116 の帯域幅に追加的な帯域幅が必要である状況で第1データを含むデータに対して少ないデータをフィルタリングすることができる。

スケジューラーブロック 1184 を含む電子学習システム 1100 は、スキャン及びフィルタリングに対する負担軽減の後にも追加的な入出力ボトルネック現象が検出されれば、メイン反復アルゴリズムの少なくとも一部に対する負担軽減を決定することができる。

入出力ボトルネック現象に対する決定のために、データは、システム装置 1112、ストレージ装置 1114 等によってランダムに又は規則的に復旧することができる。 20

#### 【0181】

電子学習システム 1000 と同様に、システム装置 1112、ストレージ装置 1114、又はこれらの組み合わせは、命令語の実行、機能、スケジューリングアルゴリズム、割り当てアルゴリズム、データ割り当て等を遂行するための高級プログラム言語のようなスケジューラーブロック 1184 を含むことができる。

一実施形態において、命令語、プログラムインターフェイス等は、命令語、機能等を実行するための新しいシステムコール、拡張システムコール、システム状態、入出力帯域幅のシステム状態、演算使用率に関連されたシステム状態、スロットリングに関連されたシステム状態等を含むシステムコールを含むことができる。 30

命令語、プログラムインターフェイス等は、システム情報 1186 に基づくことができる。

その上に、適応ブロック 1130 は、システム情報 1186 に基づいて第1データに対する知的な選択、分割、フィルタ等の動作を遂行することができる。

#### 【0182】

一実施形態において、システム情報 1186 は、システム使用率、システム帯域幅、システムパラメーター、入出力使用率、メモリ使用率、メモリアクセス、ストレージ使用率、ストレージアクセス、コントロールユニット使用率、コントロールユニットアクセス、CPU 使用率、CPU アクセス、メモリプロセッサ使用率、メモリプロセスアクセス等であってもよい。 40

システム情報 1086 は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、第1ストレージ媒体 126、第2ストレージ媒体 142、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

#### 【0183】

一実施形態において、システム装置 1112、ストレージ装置 1114、又はこれらの組み合わせは、ウェブサービスインターフェイスを含む図 10 のサービスインターフェイス 1088 と通信することができる。

サービスインターフェイス 1088 は、電子学習システム 1100、電子システム 100、又はこれらの組み合わせの外部への通信サービスを提供することができる。 50

## 【0184】

一実施形態において、ストレージ装置1114は、フラッシュメモリ、ソリッドステートドライブ(S SSD)、相変化メモリ(PCM)、スピンドルクラッシュアクセスメモリ(STT-RAM)、抵抗性ランダムアクセスメモリ(ReRAM)、磁気抵抗ランダムアクセスメモリ(MRAM)、所定の形態のストレージ装置、所定の形態のメモリ装置等を含むことができる。

ストレージ装置1114、システム装置1112は、メモリバス、SAS(serial attached small computer system interface)、SATA(serial attached advanced technologylogy attachment)、NVMe(non-volatile memory express)、光チャンネル、イーサーネット(登録商標)(Ethernet(登録商標))、RDMA(remote direct memory access)等を含むインターフェイス1116と接続することができる。

## 【0185】

例示的に、電子学習システム1100は、各々1つのコンポーネントで図示しているが、任意の数のコンポーネントが含まれることは容易に理解できる。

例えば、電子学習システム1100は、各々1つ以上のストレージ装置1114、第1データブロック1152、第2データブロック1154、第3データブロック1156を含むことができる。

## 【0186】

適応ブロック1130、ストレージ学習ブロック1124、システム学習ブロック1128、又はこれらの組み合わせを含む電子学習システム1100は、知的なプロセス、スロットリング、並列処理、分散処理等で発生する問題を識別し、負担を減らすことができる。

知的なプロセス分担、スロットリング、並列処理、分散処理等は、少なくともインターフェイス1116でのボトルネック現象、資源飽和、作業累積等を軽減させ、システム装置1112とストレージ装置1114での高い帯域幅使用率を提供することができる。

## 【0187】

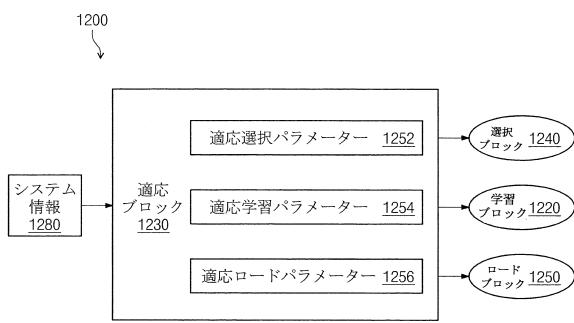

図12は、本発明の一実施形態による電子システム100の電子学習システム1200の一部を示すブロック図である。

図12を参照すると、電子学習システム1200は、図1の第1装置102、図1の第2装置106、集積回路、集積回路コア、集積回路コンポーネント、MEMS(Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

## 【0188】

一実施形態において、電子学習システム1200は、図11の適応ブロック1130や図10の前処理ブロック1030を含み、機械学習機能を制御するか、或いは割り当て動作を行うことができる。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するようになるか、或は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

機械学習は、人工知能AIの1つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である。

## 【0189】

例えば、電子学習システム1200は、ストレージ内コンピューティング(ISC)のみならず、システムプロセッサでの並列処理のためのクラスター-コンピューティングを含む並列又は分散機械学習メカニズムを含むことができる。

並列処理のための並列又は分散機械学習メカニズムは、図1の第1コントロールユニッ

10

20

30

40

50

ト 1 1 2 、 図 1 の第 2 コントロールユニット 1 3 4 、 図 1 の第 1 ストレージユニット 1 1 4 、 図 1 の第 2 ストレージユニット 1 4 6 、 図 1 の第 1 ストレージコントロールユニット 1 3 2 、 図 1 の第 2 ストレージコントロールユニット 1 5 2 、 図 1 の第 1 ストレージ媒体 1 2 6 、 図 1 の第 2 ストレージ媒体 1 4 2 、 又はこれらの組み合わせの中の少なくとも 1 つで実行することができる。

【 0 1 9 0 】

一 実施形態において、電子学習システム 1 2 0 0 は、スキャニング、フィルタリング、予測、推薦、機械学習機能、ビックデータ解釈アルゴリズム等のような並列及び分散機械学習メカニズムを実行するための適応プロセスを含むことができる。

適応プロセスは、並列及び分散機械学習及びストレージ内コンピューティング ( I S C ) 及び S S D のようなシステムのハードウェアコントロールのためのコントロールパラメーター、選択率、学習率、ホスト演算対ストレージ演算割合等を含むことができる。

例えば、電子学習システム 1 2 0 0 は、並列又は分散機械学習で部分データの画期的な向上を提供するためにデータトレーニングのような知的にデータを選択、又は分割する機能を提供することができる。

部分データの画期的な向上は、モデル、ベクトル、又はこれらの組み合わせのアップデート動作を向上させることができる。

知的な選択又は分割は、入出力データの増加にも高速の収斂特性を提供することができる。

【 0 1 9 1 】

一 実施形態において、電子学習システム 1 2 0 0 は、機械学習ブロックのような学習ブロック 1 2 2 0 、適応メカニズムブロックのような適応ブロック 1 2 3 0 、負担軽減ブロックのようなロードブロック 1 2 5 0 、ストレージ内コンピューティング ( I S C ) 等を含むことができる。

学習ブロック 1 2 2 0 、適応ブロック 1 2 3 0 、ロードブロック 1 2 5 0 等は、集積回路、集積回路コア、集積回路コンポーネント、M E M S ( M i c r o e l e c t r o m e c h a n i c a l S y s t e m ) 、受動素子、又はこれらの組み合わせで具現することができる。

例えば、学習ブロック 1 2 2 0 は、図 1 1 の機械学習アルゴリズム、機械学習ブロック、学習ブロック 1 1 2 0 、図 1 0 の学習ブロック 1 0 2 0 、図 9 の学習ブロック 9 2 0 、図 8 の学習ブロック 8 2 0 、図 2 の学習ブロック 2 1 0 等を含むことができる。

【 0 1 9 2 】

実施形態において、適応ブロック 1 2 3 0 は、適応選択パラメーター 1 2 5 2 、適応学習パラメーター 1 2 5 4 、適応ロードパラメーター 1 2 5 6 等を処理、計算、決定することができる。

適応選択パラメーター 1 2 5 2 、適応学習パラメーター 1 2 5 4 、適応ロードパラメーター 1 2 5 6 等は、集積回路、集積回路コア、集積回路コンポーネント、M E M S ( M i c r o e l e c t r o m e c h a n i c a l S y s t e m ) 、受動素子、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

例えば、適応プロセシングブロックに提供される適応ブロック 1 2 3 0 は、動的に変化するシステム動作のモニターリング結果に基づいてパーティショニングのためのパラメーターを知的に処理、計算、決定することができる。

【 0 1 9 3 】

例えば、学習ブロック 1 2 2 0 、適応ブロック 1 2 3 0 、ロードブロック 1 2 5 0 、又はこれらの組み合わせは、ハードウェアメモリ回路や、第 1 コントロールユニット 1 1 2 、第 2 コントロールユニット 1 3 4 、第 1 ストレージコントロールユニット 1 3 2 、第 2 ストレージコントロールユニット 1 5 2 、又はこれらの組み合わせのようなコンポーネントの一部を共有することができる。

適応選択パラメーター 1 2 5 2 、適応学習パラメーター 1 2 5 4 、適応ロードパラメーター 1 2 5 6 、又はこれらの組み合わせは、第 1 ストレージユニット 1 1 4 、第 2 ストレ

10

20

30

40

50

ージユニット 146、第1ストレージ媒体 126、第2ストレージ媒体 142、又はこれらの組み合わせの一部で具現することができる。

【0194】

一実施形態において、適応ブロック 1230 は、学習ブロック 1220、選択ブロック 1240 等の機械学習アルゴリズムを含む並列又は分散機械学習プロセスのために適応選択パラメーター 1252、適応学習パラメーター 1254 等を含むソフトウェア制御パラメーターを処理することができる。

適応選択パラメーター 1252、適応学習パラメーター 1254 等のようなソフトウェアコントロールは、機械学習アルゴリズム、選択率、学習率、又はこれらの組み合わせを含むことができる。

10

【0195】

例えば、選択ブロック 1240 は、選択率によるスキャン、選択、任意の機械学習プロセス、任意の機械学習機能、又はこれらの組み合わせを含むことができる。

一実施形態において、適応ブロック 1230 は、ストレージ内コンピューティング (ISC)、スマートソリッドステート装置 (SSD) のようなロードブロック 1250 のロードを軽減するための処理のために適応ロードパラメーター 1256 を含むハードウェア制御パラメーターを処理することができる。

適応ロードパラメーター 1256 のようなハードウェアコントロールは、ホスト演算に対するストレージ演算、負担軽減率の制御比率を含むことができる。

20

【0196】

一実施形態において、適応選択パラメーター 1252、適応学習パラメーター 1254、適応ロードパラメーター 1256、又はこれらの組み合わせは、システム使用率、システム帯域幅、システムパラメーター、入出力使用率、メモリ使用率、メモリアクセス、ストレージ使用率、ストレージアクセス、コントロールユニット使用率、コントロールユニットアクセス、CPU 使用率、CPU アクセス、ストレージプロセッサ使用率、ストレージプロセッサアクセス等のシステム情報 1280 に基づいて適応ブロック 1230 で計算される選択率、学習率、ロード率を各々含むことができる。

システム情報 1280 は、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、第1ストレージユニット 114、第2ストレージユニット 146、第1ストレージ媒体 126、第2ストレージ媒体 142、又はこれらの組み合わせで具現されるハードウェアの一部で具現することができる。

30

【0197】

例示的に、電子学習システム 1200 は、適応ブロック 1230、適応選択パラメーター 1252、適応学習パラメーター 1254、適応ロードパラメーター 1256、又はこれらの組み合わせが各々 1 つの構成で図示しているが、電子学習システム 1200 は任意の数の適応ブロック 1230、適応選択パラメーター 1252、適応学習パラメーター 1254、適応ロードパラメーター 1256、又はこれらの組み合わせを含むことは容易に理解できる。

【0198】

40

システム情報 1280 を含む電子学習システム 1200 は、適応選択パラメーター 1252、適応学習パラメーター 1254、適応ロードパラメーター 1256 を含む適応ブロックに基づいて増加する入出力単位の高速収斂を提供するためのストレージ内コンピューティング (ISC) のみならず、システムプロセッサでの並列処理のためのクラスター・コンピューティングを含む並列又は分散機械学習メカニズムを含むことができる。

システム情報 1280 を使用する適応ブロック 1230 は、画期的に向上された部分データを提供するためにトレーニングデータのようなデータを知的に選択し、分離することができる。

【0199】

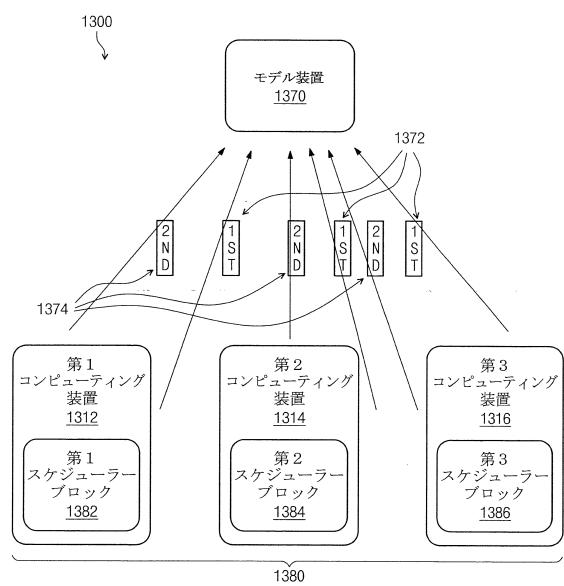

図 13 は、本発明の一実施形態による電子システム 100 の電子学習システム 1300

50

の一部を示すブロック図である。

図13を参照すると、電子学習システム1300は、図1の第1装置102、図1の第2装置106、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

#### 【0200】

一実施形態において、電子学習システム1300は、機械学習機能を提供する。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するよう 10 するか、或は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

機械学習は、人工知能AIの1つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である。

#### 【0201】

一実施形態において、電子学習システム1300は、ストレージ内コンピューティング (ISC) のみならず、システムプロセッサでの並列処理のためのクラスター・コンピューティングを含む並列又は分散機械学習メカニズムを含むことができる。

並列処理のための並列又は分散機械学習メカニズムは、図1の第1コントロールユニット112、図1の第2コントロールユニット134、図1の第1ストレージユニット114、図1の第2ストレージユニット146、図1の第1ストレージコントロールユニット132、図1の第2ストレージコントロールユニット152、図1の第1ストレージ媒体126、図1の第2ストレージ媒体142、又はこれらの組み合わせの中の少なくとも1つで実行することができる。

#### 【0202】

一実施形態において、電子学習システム1300は、スキャニング、フィルタリング、予測、推薦、機械学習機能、ビックデータ解釈アルゴリズム等のような並列及び分散機械学習メカニズムを実行するための適応プロセスを含むことができる。

適応プロセスは、並列及び分散機械学習及びストレージ内コンピューティング (ISC) 及びSSDのようなシステムのハードウェアコントロールするためのコントロールパラメーター、選択率、学習率、ホスト演算対ストレージ演算割合等を含むことができる。

例えば、電子学習システム1300は、並列又は分散機械学習で部分データの画期的な向上を提供するためにデータトレーニングのような知的にデータを選択、又は分割する機能を提供することができる。

部分データの画期的な向上は、モデル、ベクトル、又はこれらの組み合わせのアップデート動作を向上させることができる。

知的な選択又は分割は、入出力データの増加にも高速の収斂特性を提供することができる。

#### 【0203】

一実施形態において、電子学習システム1300は、第1コンピューティング装置1312、第2コンピューティング装置1314、第3コンピューティング装置1316、又はこれらの組み合わせを含むことができる。

第1コンピューティング装置1312、第2コンピューティング装置1314、第3コンピューティング装置1316、又はこれらの組み合わせは、図5のシステム装置512とストレージ装置514、図9のシステム装置912とストレージ装置914、図10のシステム装置1012とストレージ装置1014、図11のシステム装置1112とストレージ装置1114、第1装置102、第2装置106、何らかの演算装置、又はこれらの組み合わせを含むシステム装置で具現することができる。

例示的に、電子学習システム1300は、3つのコンピューティング装置を含むこととして図示しているが、任意の数のコンピューティング装置が含まれることは容易に理解で

10

20

30

40

50

きる。

【0204】

この実施形態において、電子学習システム1300は、モデルサーバのようなモデル装置1370を含むことができる。

モデル装置1370は、システム装置、ストレージ装置等で具現することができる。

モデル装置1370は、コンピューティング資源を含むが、要求はしない。

モデル装置1370は、機械学習データ、ピックデータ機械学習、分析されたピックデータ、ピックデータ解析法等に基づいて機械学習データ、ベクトル、パラメーター、モデル等を含むことができる。

【0205】

10

例示的に、第1コンピューティング装置1312、第2コンピューティング装置1314、第3コンピューティング装置1316、又はこれらの組み合わせは、分離されたブロックで表示されているが、いずれか1つのブロックは他の1つのブロックとハードウェアの一部を共有できることは容易に理解できる。

例えば、第1コンピューティング装置1312、第2コンピューティング装置1314、第3コンピューティング装置1316、又はこれらの組み合わせは、ハードウェア回路の一部を共有することができる。

【0206】

電子学習システム1300は、ストレージ装置で計算されたモデルである第1モデル1372のベクトルを含むことができる。

20

また、電子学習システム1300は、ホスト装置やシステム装置で計算されたモデルである第2モデル1374のベクトルを含むことができる。

電子学習システム1300は、第1モデル1372、第2モデル1374の新しい又はアップデートされたベクトルを提供することができる。

第1モデル1372、第2モデル1374は、モデル装置1370上で提供され、格納され、アップデートされ、訂正され、記入され、記録され、入力され、集積され、置換されることができる。

例示的に、第1モデル1372は、ストレージ装置で計算されたモデルで図示しているが、第1モデル1372は他の装置で計算されることは容易に理解できる。

同様に、第2モデル1374は、ホスト又はシステム装置で計算されたモデルで図示しているが、第2モデル1374は他の装置で計算されることは容易に理解できる。

30

【0207】

スケジューラー1380は、第1コンピューティング装置1312、第2コンピューティング装置1314、第3コンピューティング装置1316、モデル装置1370、又はこれらの組み合わせに、データ、タスク、機能、動作等を知的に割り当てすることができる。

トレーニングデータのようなデータに対する知的な選択又は分割は、画期的に向上された部分データを提供することができる。

画期的に向上された部分データは、モデル、ベクトル等をアップデートを向上させることができる。

40

データに対する知的な選択又は分割は、増加された入出力装置で高速の収斂特性を提供することができる。

【0208】

スケジューラー1380は、第1スケジューラーブロック1382、第2スケジューラーブロック1384、第3スケジューラーブロック1386を含み、図10の機能1040のような機能を実行するための高級プログラム言語、スケジューリングアルゴリズム、割り当て機能、データ割り当て等を遂行することができる。

第1スケジューラーブロック1382、第2スケジューラーブロック1384、第3スケジューラーブロック1386、又はこれらの組み合わせは、ノード当たりアドホックスタイルスケジューラーと、第1コンピューティング装置1312、第2コンピューティン

50

グ装置 1314、第3コンピューティング装置 1316 等のコントロールユニットにアクセス又は制御することができる。

【0209】

例示的に、スケジューラー 1380 は、第1スケジューラーブロック 1382、第2スケジューラーブロック 1384、第3スケジューラーブロック 1386 のように 3 つのブロックで図示しているが、スケジューラー 1380 は任意の数のブロックを含むことは容易に理解できる。

スケジューラー 1380 は、第1スケジューラーブロック 1382、第2スケジューラーブロック 1384、第3スケジューラーブロック 1386 のマルチサブブロックを有する單一ブロックで構成されてもよい。

10

【0210】

スケジューラー 1380 を有する電子学習システム 1300 は、ピックデータ分析法のような並列又は分散機械学習のためにデータに対する知的な選択、分割、フィルタ等の動作を遂行することができる。

スケジューラー 1380 は、第1コンピューティング装置 1312、第2コンピューティング装置 1314、第3コンピューティング装置 1316 を有する第1モデル 1372、第2モデル 1374 の機能を提供するためにデータ、プロセス、分析、機能、学習等を知的に負担の軽減をさせ、選択、分割、分離等の演算を遂行することができる。

【0211】

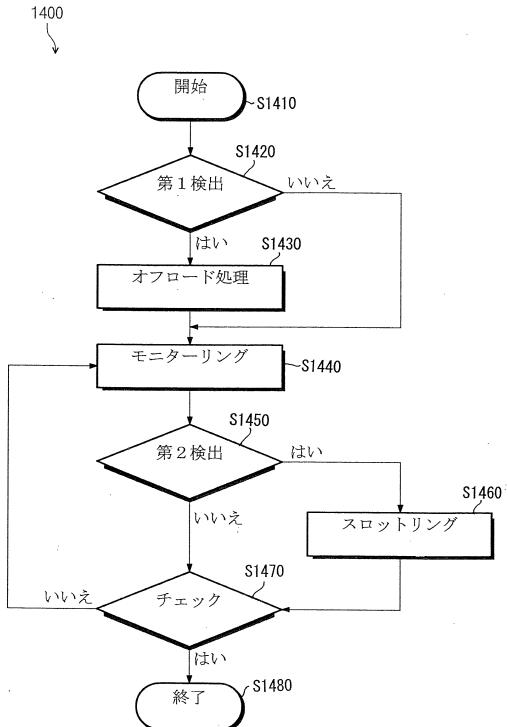

図 14 は、本発明の一実施形態による電子システム 100 の電子学習システム 1400 の処理を説明するためのフローチャートである。

20

図 14 を参照すると、電子学習システム 1400 は、図 1 の第1装置 102、図 1 の第2装置 106、集積回路、集積回路コア、集積回路コンポーネント、MEMS (Microelectromechanical System)、受動素子、又はこれらの組み合わせで具現することができる。

【0212】

一実施形態において、電子学習システム 1400 は、機械学習機能を提供する。

機械学習機能は、人工知能、明示的なプログラム無しでコンピュータが動作するようになるか、或は自動推論、自動適応、自動決定、自動学習、明示的なプログラム無しでコンピュータが自動に学習するようにする機能、又はこれらの組み合わせに該当するアルゴリズムを含むことができる。

30

機械学習は、人工知能 AI の 1 つの形態として考慮することができる。

機械学習は、明示的な設計やプログラム工程で具現され、ルールベースアルゴリズムとしては実行が不可能である。

【0213】

例えば、電子学習システム 1400 は、ストレージ内コンピューティング (ISC) のみならず、システムプロセッサでの並列処理のためのクラスター・コンピューティングを含む並列又は分散機械学習メカニズムを含むことができる。

並列処理のための並列又は分散機械学習メカニズムは、図 1 の第1コントロールユニット 112、図 1 の第2コントロールユニット 134、図 1 の第1ストレージユニット 114、図 1 の第2ストレージユニット 146、図 1 の第1ストレージコントロールユニット 132、図 1 の第2ストレージコントロールユニット 152、図 1 の第1ストレージ媒体 126、図 1 の第2ストレージ媒体 142、又はこれらの組み合わせの中の少なくとも 1 つで実行することができる。

40

【0214】

一実施形態において、電子学習システム 1400 は、スキャニング、フィルタリング、予測、推薦、機械学習機能、ピックデータ解釈アルゴリズム等のような並列及び分散機械学習メカニズムを実行するための適応プロセスを含むことができる。

適応プロセスは、並列及び分散機械学習及びストレージ内コンピューティング (ISC) 及び SSD のようなシステムのハードウェアコントロールするためのコントロールパラ

50

メーター、選択率、学習率、ホスト演算対ストレージ演算割合等を含むことができる。

例えば、電子学習システム 1400 は、部分データの画期的な向上を提供するためにトレーニングデータのようなデータを知的に又は分割する機能を提供することができる。

部分データの画期的な向上は、モデル、ベクトル、又はこれらの組み合わせのアップデート動作を向上させることができる。