(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6518890号

(P6518890)

(45) 発行日 令和1年5月29日(2019.5.29)

(24) 登録日 令和1年5月10日(2019.5.10)

|                   |                  |             |              |

|-------------------|------------------|-------------|--------------|

| (51) Int.Cl.      | F 1              |             |              |

| <b>G09F 9/00</b>  | <b>(2006.01)</b> | <b>G09F</b> | <b>9/00</b>  |

| <b>G09G 3/30</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/30</b>  |

| <b>H05B 33/08</b> | <b>(2006.01)</b> | <b>H05B</b> | <b>33/08</b> |

| <b>H01L 51/50</b> | <b>(2006.01)</b> | <b>H05B</b> | <b>33/14</b> |

| <b>G09G 3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  |

請求項の数 8 (全 29 頁) 最終頁に続く

|           |                              |                    |                                   |

|-----------|------------------------------|--------------------|-----------------------------------|

| (21) 出願番号 | 特願2014-71920(P2014-71920)    | (73) 特許権者          | 514188173                         |

| (22) 出願日  | 平成26年3月31日(2014.3.31)        | 株式会社 J O L E D     |                                   |

| (65) 公開番号 | 特開2015-194577(P2015-194577A) | 東京都千代田区神田錦町三丁目23番地 |                                   |

| (43) 公開日  | 平成27年11月5日(2015.11.5)        | (74) 代理人           | 110001357                         |

| 審査請求日     | 平成29年1月17日(2017.1.17)        | 特許業務法人つばさ国際特許事務所   |                                   |

|           |                              | (72) 発明者           | 寺口 晋一<br>東京都港区港南1丁目7番1号 ソニー株式会社内  |

|           |                              | (72) 発明者           | 根岸 英輔<br>東京都港区港南1丁目7番1号 ソニー株式会社内  |

|           |                              | (72) 発明者           | 横関 弥樹博<br>東京都港区港南1丁目7番1号 ソニー株式会社内 |

最終頁に続く

(54) 【発明の名称】表示装置および電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

それが表示素子を含み2次元配置された複数の画素を有する画素部と、前記複数の画素を表示駆動する駆動回路部とを備え、基板上に、前記駆動回路部を含む第1層と、前記画素部を含む第2層とがこの順に積層され、

前記第1層と前記第2層とは、互いに積層方向に沿って連通する光透過部を有し、前記第1層に形成されたトランジスタは、低温ポリシリコンを含み、

前記第2層に形成されたトランジスタは、酸化物半導体を含み、前記画素部は、画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、

前記書き込みトランジスタが前記第1層に形成され、前記駆動トランジスタが前記第2層に形成されている

表示装置。

## 【請求項 2】

それが表示素子を含み2次元配置された複数の画素を有する画素部と、前記複数の画素を表示駆動する駆動回路部とを備え、

基板上に、前記駆動回路部を含む第1層と、前記画素部を含む第2層とがこの順に積層

10

20

され、

前記第1層と前記第2層とは、互いに積層方向に沿って連通する光透過部を有し、

前記第1層に形成されたトランジスタと、前記第2層に形成されたトランジスタとは、いずれも低温ポリシリコンを含み、

前記画素部は、画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、

前記書き込みトランジスタが前記第1層に形成され、前記駆動トランジスタが前記第2層に形成されている

表示装置。

**【請求項3】**

10

前記表示素子の電極は、前記駆動トランジスタのソース・ドレイン電極を兼ねている

請求項1または請求項2に記載の表示装置。

**【請求項4】**

前記第1層と前記第2層との間に、シールド層が設けられている

請求項1ないし請求項3のうちいずれか1項に記載の表示装置。

**【請求項5】**

前記シールド層は、レーザ光遮蔽機能を有する

請求項4に記載の表示装置。

**【請求項6】**

20

前記表示素子は有機電界発光素子である

請求項1ないし請求項5のうちいずれか1項に記載の表示装置。

**【請求項7】**

それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、

前記複数の画素を表示駆動する駆動回路部と

を備え、

基板上に、前記駆動回路部を含む第1層と、前記画素部を含む第2層とがこの順に積層され、

前記第1層と前記第2層とは、互いに積層方向に沿って連通する光透過部を有し、

前記第1層に形成されたトランジスタは、低温ポリシリコンを含み、

前記第2層に形成されたトランジスタは、酸化物半導体を含み、

30

前記画素部は、画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、

前記書き込みトランジスタが前記第1層に形成され、前記駆動トランジスタが前記第2層に形成されている

表示装置を備えた電子機器。

**【請求項8】**

それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、

複数の回路要素を有し、前記複数の画素を表示駆動する駆動回路部と

を備え、

基板上に、前記駆動回路部を含む第1層と、前記画素部を含む第2層とがこの順に積層され、

40

前記複数の回路要素は、前記第1層内に分散して設けられ、

前記第1層と前記第2層とは、互いに積層方向に沿って連通する光透過部を有し、

前記第1層に形成されたトランジスタと、前記第2層に形成されたトランジスタとは、いずれも低温ポリシリコンを含み、

前記画素部は、画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、

前記書き込みトランジスタが前記第1層に形成され、前記駆動トランジスタが前記第2層に形成されている

表示装置を備えた電子機器。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本開示は、例えば有機電界発光（EL：Electro Luminescence）素子を含む表示装置およびそれを用いた電子機器に関する。

**【背景技術】**

10

**【0002】**

近年、モバイル用途をはじめとする表示装置において狭額縫化が進んでいる。ところが、中小型の表示装置では、周辺駆動回路のレイアウトに制約があり、狭額縫化を実現することが困難である。そこで、ステンレス基板やプラスチック基板を用いて、額縫部分を折り曲げる手法が提案されている（特許文献1）。

**【先行技術文献】****【特許文献】****【0003】****【特許文献1】特開2012-128006号公報**

20

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

しかしながら、上記特許文献1の手法では、基板材料や厚み、駆動回路のレイアウトによつては、折り曲げることができない場合がある。したがつて、このような手法とは異なる手法により、狭額縫化（あるいは額縫レス化）を実現することが望まれている。

**【0005】**

本開示はかかる問題点に鑑みてなされたもので、その目的は、狭額縫あるいは額縫レスを実現することが可能な表示装置および電子機器を提供することにある。

**【課題を解決するための手段】****【0006】**

30

本開示の第1の表示装置は、それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、複数の回路要素を有し、複数の画素を表示駆動する駆動回路部とを備え、基板上に、駆動回路部を含む第1層と、画素部を含む第2層とがこの順に積層され、複数の回路要素は、第1層内に分散して設けられ、第1層と第2層とは、互いに積層方向に沿つて連通する光透過部を有し、第1層に形成されたトランジスタは、低温ポリシリコンを含み、第2層に形成されたトランジスタは、酸化物半導体を含むものである。

本開示の第2の表示装置は、それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、複数の回路要素を有し、複数の画素を表示駆動する駆動回路部とを備え、基板上に、駆動回路部を含む第1層と、画素部を含む第2層とがこの順に積層され、複数の回路要素は、第1層内に分散して設けられ、第1層と第2層とは、互いに積層方向に沿つて連通する光透過部を有し、第1層に形成されたトランジスタと、第2層に形成されたトランジスタとは、いずれも低温ポリシリコンを含むものである。

40

本開示の第3の表示装置は、それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、複数の画素を表示駆動する駆動回路部とを備え、基板上に、駆動回路部を含む第1層と、画素部を含む第2層とがこの順に積層され、第1層と第2層とは、互いに積層方向に沿つて連通する光透過部を有し、第1層に形成されたトランジスタは、低温ポリシリコンを含み、第2層に形成されたトランジスタは、酸化物半導体を含み、画素部は、画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、書き込みトランジスタが第1層に形成され、駆動トランジスタが第2層に形成されているものである。

50

本開示の第4の表示装置は、それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、複数の画素を表示駆動する駆動回路部とを備え、基板上に、駆動回路部を含む第1層と、画素部を含む第2層とがこの順に積層され、第1層と第2層とは、互いに積層方向に沿って連通する光透過部を有し、第1層に形成されたトランジスタと、第2層に形成されたトランジスタとは、いずれも低温ポリシリコンを含み、画素部は、画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、書き込みトランジスタが第1層に形成され、駆動トランジスタが第2層に形成されているものである。

#### 【0007】

本開示の第1，第2，第3，第4の電子機器は各々、上記本開示の第1，第2，第3，第4の表示装置を備えたものである。

10

#### 【0008】

本開示の第1，第2，第3，第4の表示装置および電子機器では、2次元配置された複数の画素を有する画素部と、複数の画素を表示駆動する駆動回路部とを備え、駆動回路部を含む第1層と、画素部を含む第2層とが積層されることにより、画素部の周辺領域における駆動回路部の配置スペースが削減される。

#### 【発明の効果】

#### 【0009】

本開示の第1，第2，第3，第4の表示装置および電子機器によれば、2次元配置された複数の画素を有する画素部と、複数の画素を表示駆動する駆動回路部とを備え、駆動回路部を含む第1層と、画素部を含む第2層とが積層されている。これにより、画素部の周辺領域における駆動回路部の配置スペースを削減することができる。よって、狭額縁あるいは額縁レスを実現することができる。

20

#### 【0010】

なお、上記内容は本開示の一例である。本開示の効果は、上述したものに限らず、他の異なる効果であってもよいし、更に他の効果を含んでいてもよい。

#### 【図面の簡単な説明】

#### 【0011】

30

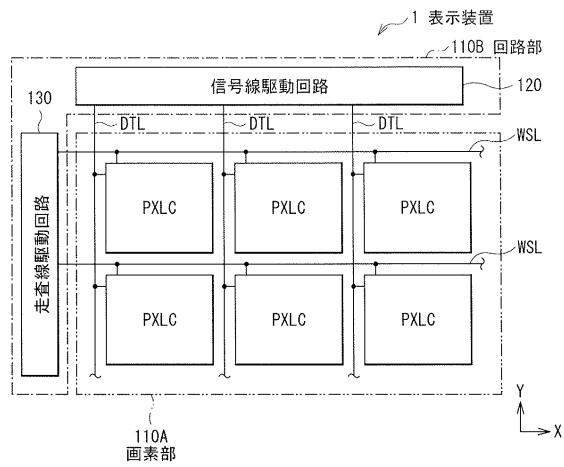

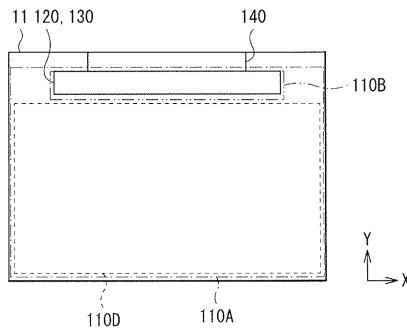

【図1】本開示の第1の実施の形態に係る表示装置の全体構成を表す機能ブロック図である。

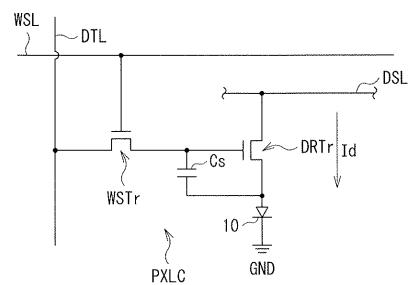

【図2】図1に示した画素の画素回路の一例を表す回路図である。

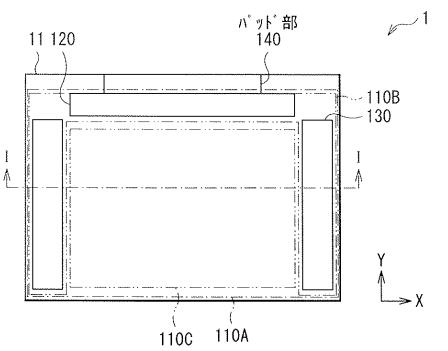

【図3A】図1に示した画素部と回路部とのレイアウトを表す平面模式図である。

【図3B】図1に示した画素部と回路部とのレイアウトを表す断面模式図である。

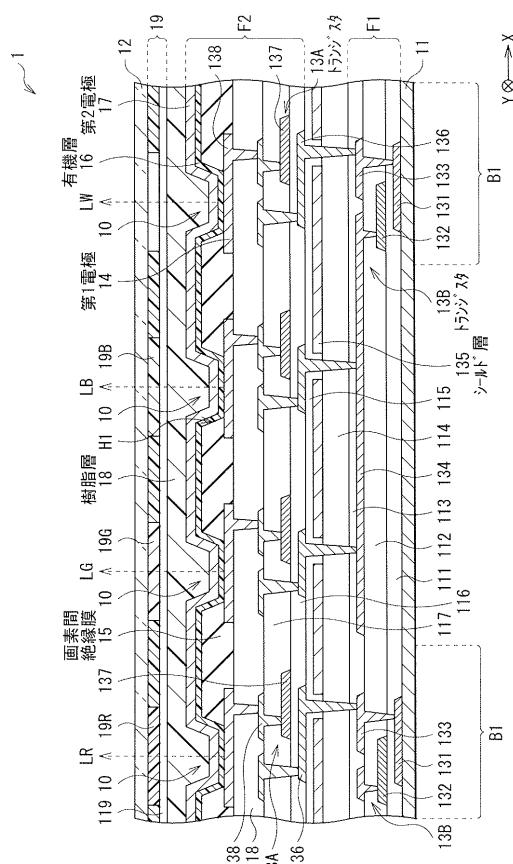

【図4】図1に示した表示装置の構成を表す断面図である。

【図5】比較例1に係る表示装置の平面構成と断面構成とを表す模式図である。

【図6】変形例1に係る表示装置の画素部と回路部とのレイアウトを表す平面模式図である。

【図7】図6に示した画素部と回路部とのレイアウトを表す断面模式図である。

40

【図8A】回路部の構成例を表す模式図である。

【図8B】回路部の構成例を表す模式図である。

【図8C】回路部の構成例を表す模式図である。

【図9】変形例2に係る表示装置の画素部と回路部とのレイアウトを表す平面模式図である。

【図10】図9に示した画素部と回路部とのレイアウトを表す断面模式図である。

【図11】図9に示した表示装置の構成を表す断面図である。

【図12】一般的なディスプレイの画素構成を説明するための模式図である。

【図13】透明ディスプレイの画素構成を表す模式図である。

【図14】本開示の第2の実施の形態に係る表示装置における駆動回路部を含む第1層の

50

平面構成と画素部を含む第2層の平面構成表す模式図である。

【図15】図14に示した第1層と第2層とを含む表示装置全体の構成を表す断面図である。

【図16】図15に示した表示装置の透過部付近の拡大断面図である。

【図17A】2辺透明ディスプレイについて説明するための模式図である。

【図17B】3辺透明ディスプレイについて説明するための模式図である。

【図18】変形例3に係る表示装置の構成を表す断面図である。

【図19】本開示の第3の実施の形態に係る表示装置の構成を表す断面図である。

【図20】図19に示した表示装置の第1層と第2層との構成を説明するための模式図である。

10

【図21】図19に示した表示装置の第1層と第2層との構成を表す模式図である。

【図22】図19に示した表示装置の効果を説明するための模式図である。

【図23】図19に示した表示装置の効果を説明するための模式図である。

【図24A】トランジスタ積層構造のメリットを説明するための断面模式図である。

【図24B】トランジスタ積層構造のメリットを説明するための断面模式図である。

【図24C】トランジスタ積層構造のメリットを説明するための断面模式図である。

【図24D】トランジスタ積層構造のメリットを説明するための断面模式図である。

【図25】変形例4に係る表示装置の構成を表す断面図である。

【図26】比較例2に係る画素部の要部構成を表す断面図である。

【図27】図26に示した画素部の平面レイアウトの一例を表す模式図である。

20

【図28】図25に示した画素部の要部構成を表す断面図である。

【図29】図25に示した画素部の第1層と第2層との各平面レイアウトの一例を表す模式図である。

【図30】変形例5に係る表示装置の構成を表す断面図である。

【図31A】適用例1の外観を表す斜視図である。

【図31B】適用例1の外観を表す斜視図である。

【図32A】適用例2の外観を表す斜視図である。

【図32B】適用例2の外観を表す斜視図である。

【図33A】適用例3の外観を表す斜視図である。

【図33B】適用例3の外観を表す斜視図である。

【図34A】適用例4の外観を表す図である。

【図34B】適用例4の外観を表す図である。

【図35】適用例5の要部構成を表す図である。

【発明を実施するための形態】

【0012】

以下、本開示の実施の形態について図面を参照して以下の順に詳細に説明する。

1. 第1の実施の形態（回路部がパネルの3辺に対応する領域において画素部と積層して設けられた表示装置の例）

2. 変形例1（回路部の構成要素が分散して設けられた例）

3. 変形例2（走査線駆動回路がパネルの1辺に集約して設けられた例）

40

4. 第2の実施の形態（透明ディスプレイに用いられる表示装置の例）

5. 変形例3（他の発光方式（ボトムエミッション方式）の表示装置の例）

6. 第3の実施の形態（書き込みトランジスタが回路部と同層に設けられた例）

7. 変形例4（第1電極と駆動トランジスタとの接続層を省略した例）

8. 変形例5（端面封止の好適例）

9. 適用例（電子機器の例）

【0013】

<第1の実施の形態>

[構成]

図1は、本開示の第1の実施の形態に係る表示装置（表示装置1）の全体構成を表すも

50

のである。この表示装置1は、有機ELディスプレイなどとして用いられるものである。表示装置1は、例えば、マトリクス状に2次元配置された複数の画素PXL<sub>C</sub>を含む画素部(画素部110A)と、画素部110Aを表示駆動するための駆動回路部(回路部110B)とを備えている。画素PXL<sub>C</sub>は、例えば赤(R), 緑(G), 青(B), 白(W)の4色のサブピクセルのいずれかに相当し、これらの4色の画素PXL<sub>C</sub>の組を1ピクセルとして画像が表示される。

#### 【0014】

画素PXL<sub>C</sub>は、例えば表示素子(例えば、後述の有機EL素子10)と、画素トランジスタと、容量素子とを含む画素(あるいは画素回路)である。この画素PXL<sub>C</sub>は、互いに直交するX方向(例えば表示画面の水平方向)およびY方向(例えば表示画面の垂直方向)の2方向に沿って配列されている。回路部110Bは、例えば、映像表示用のドライバである信号線駆動回路120と、走査線駆動回路130とを有する。なお、図示しないが、回路部110Bは、この他にも電源線駆動回路など他の回路要素を含んでいてよい。

10

#### 【0015】

図2は、画素PXL<sub>C</sub>の回路構成を表したものである。画素PXL<sub>C</sub>は、例えばアクティブ型の画素回路であり、例えば駆動トランジスタDRT<sub>r</sub>と、書き込みトランジスタWST<sub>r</sub>と、キャパシタ(保持容量)Csと、有機EL素子10とを有する。有機EL素子10は、第1の電源ラインDSL(Vcc)と第2の電源ライン(GND)との間ににおいて駆動トランジスタDRT<sub>r</sub>に直列に接続されている。駆動トランジスタDRT<sub>r</sub>および書き込みトランジスタWST<sub>r</sub>は、一般的な薄膜トランジスタ(TFT(Thin Film Transistor))であり、例えば逆スタガ構造(いわゆるボトムゲート型)またはスタガ構造(トップゲート型)を有している。これらの駆動トランジスタDRT<sub>r</sub>および書き込みトランジスタWST<sub>r</sub>の構成については後述する。

20

#### 【0016】

表示装置1では、列方向に沿って複数の信号線DTLが配置され、行方向に沿って複数の走査線WSLが配置されている。各信号線DTLと各走査線WSLとの交差点が、画素PXL<sub>C</sub>に対応している。各信号線DTLは、信号線駆動回路120に接続されており、この信号線駆動回路120から信号線DTLを介して書き込みトランジスタWST<sub>r</sub>のソース電極に映像信号が供給される。各走査線WSLは、走査線駆動回路130に接続されており、この走査線駆動回路130から走査線WSLを介して書き込みトランジスタWST<sub>r</sub>のゲート電極に走査信号が供給される。

30

#### 【0017】

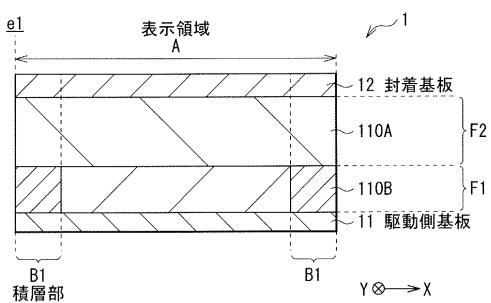

図3Aおよび図3Bは、画素部110Aと回路部110Bとのレイアウトを説明するための模式図であり、図3AがXY平面構成、図3Bが断面構成を表している。なお、図3Bは、図3AのI-I線における矢視断面図である。

#### 【0018】

画素部110Aは、基板11のほぼ全面にわたって形成されている。つまり、表示装置1では、表示パネルの一面のほぼ全域が有効表示領域となっており、パネルの端面e1付近まで発光可能となっている。回路部110Bは、画素部110Aの周辺領域ではなく、画素部110Aと対向するように設けられている。具体的には、表示装置1では、回路部110Bを含む層(第1層F1)と、画素部110Aを含む層(第2層F2)とが、積層されている。ここでは、駆動側基板11上に、第1層F1と、第2層F2とが、この順に形成されている。第2層F2上には、封止基板12が設けられる。なお、回路部110Bの走査線駆動回路120と信号線駆動回路130とは、図示しない配線を通じて外部接続用のパッド部140に電気的に接続されている。

40

#### 【0019】

第1層F1は、回路部110Bの構成要素(シフトレジスタ回路、バッファ回路およびロジック回路などの回路要素)を含む層である。本実施の形態では、回路部110Bの回路要素が、第1層F1内の選択的な領域に偏って(密に)形成されている。具体的には、

50

画素部 110A (表示領域 A) の X Y 平面形状が矩形状であり、この矩形状の 3 辺に対応する領域に、回路部 110B が形成されている。換言すると、表示装置 1 は、表示領域 A の矩形状の 3 辺に対応して、画素部 110A と回路部 110B とが積層する部分 (積層部 B1) を有している。

【0020】

第 2 層 F2 は、画素部 110A の構成要素 (例えば、有機 EL 素子 10、書き込みトランジスタ WSTr、駆動トランジスタ DRT<sub>r</sub>、キャパシタ Cs 等) を含む層である。但し、詳細は後述するが、画素部 110A の全ての構成要素が第 2 層 F2 に形成される必要はなく、一部の構成要素が第 1 層 F1 に形成されていてもよい。

【0021】

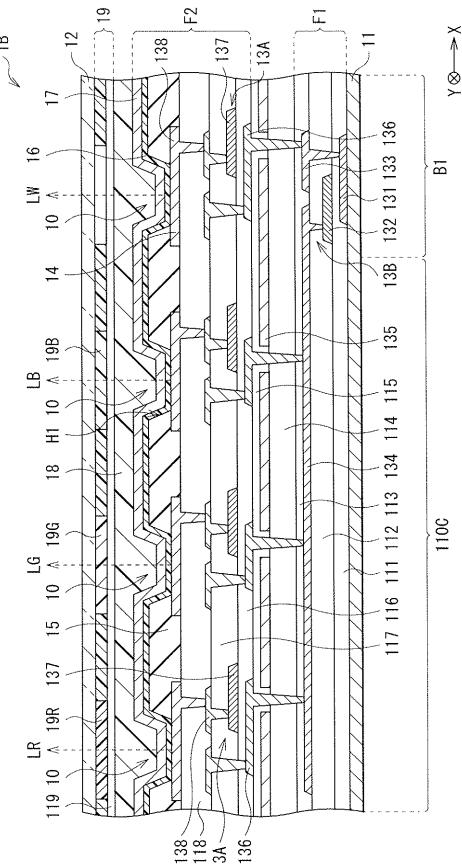

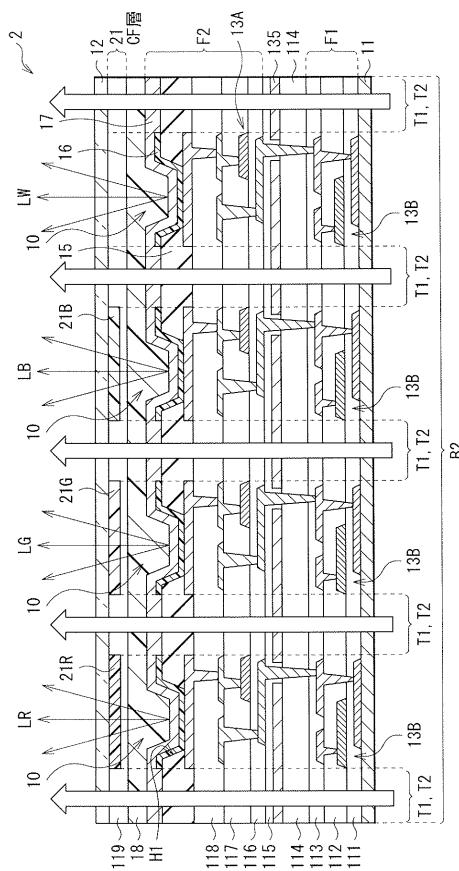

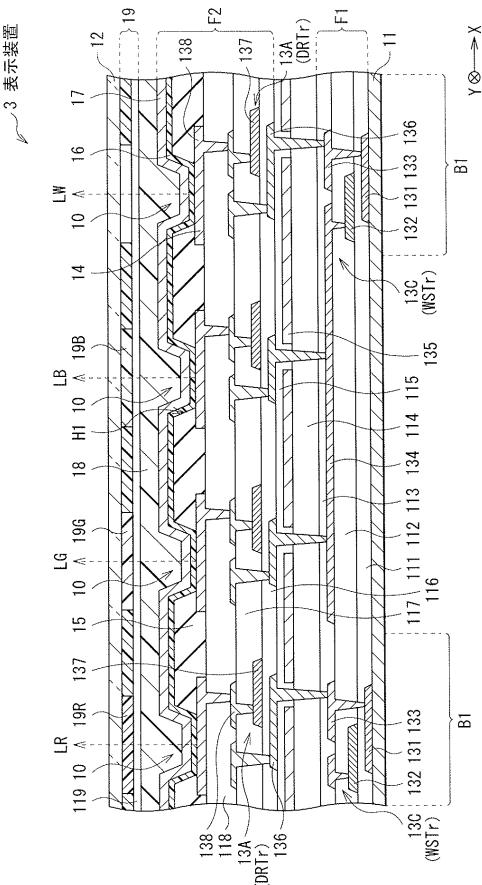

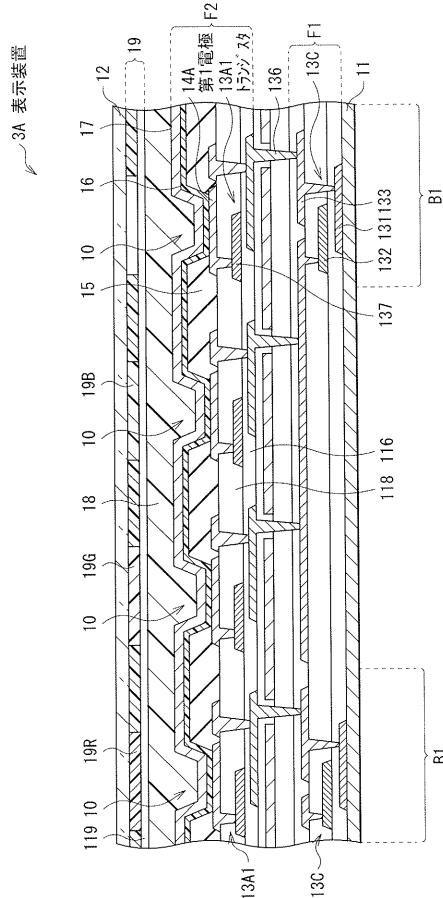

図 4 は、表示装置 1 の詳細な断面構成を表したものである。なお、図 4 では、R, G, B, W の 4 画素に対応する領域のみを示している。また、スケール、画素数、積層部 B1 の位置等についても実際のものとは異なっている。表示装置 1 は、例えばトップエミッション方式 (上面発光方式) の有機電界発光装置であり、上述のように、駆動側基板 11 と封止基板 12 との間に、回路部 110B を含む第 1 層 F1 と、画素部 110A を含む第 2 層 F2 と備えたものである。以下、各構成要素について説明する。

【0022】

駆動側基板 11 は、例えばガラスなどの基板から構成されている。但し、駆動側基板 11 は、ガラスに限定されるものではなく、この他にも、例えば石英あるいは樹脂などから構成されていてもよい。封止基板 12 は、ガラスなどの透明基板から構成されている。トップエミッション方式の場合には、封止基板 12 が透明性を有していればよく、駆動側基板 11 は透明性を持たない材料から構成されていても構わない。

【0023】

(第 1 層 F1)

第 1 層 F1 は、回路部 110B として複数の回路要素を含み、積層部 B1 には、各種素子 (トランジスタおよび容量素子など) が形成される。但し、図 4 には、一例としてトランジスタ 13B のみを図示している。トランジスタ 13B は、駆動側基板 11 上に、ゲート電極 131 と、半導体層 132 と、電極層 133 とを有している。ゲート電極 131 と半導体層 132 の間には、ゲート絶縁膜 111 が、半導体層 132 と電極層 133 の間には、層間絶縁膜 112 が、それぞれ形成されている。電極層 133 上には層間絶縁膜 113 が形成されている。なお、本実施の形態では、第 1 層 F1 内の積層部 B1 以外の領域 (図 3A 中の領域 110C) には、電源線配線などの配線層 134 が配置されている。

【0024】

ゲート電極 131 は、例えばモリブデン (Mo) から構成されている。半導体層 132 は、例えば低温ポリシリコン (LTPS : Low Temperature Poly-silicon) から構成されている。電極層 133 は、例えばソースまたはドレインとして機能する電極、信号線用配線あるいは電源線用配線である。この電極層 133 は、例えばチタン (Ti) およびアルミニウム (Al) を積層させた多層膜 (Ti / Al あるいは Ti / Al / Ti) である。なお、図 4 において、トランジスタ「13A」, 「13B」として図示した部分は、厳密にはトランジスタ構造となっていないが、説明上そのように記載している。図示した部分は、詳細には、トランジスタ 13A, 13B がそれぞれ形成される層構造に相当する。また、以降の断面図においても同様である。

【0025】

ゲート絶縁膜 111、層間絶縁膜 112, 113 は、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜および酸化アルミニウム膜などの無機膜からなり、それらのうちの 1 つからなる単層膜であってもよいし、2 つ以上からなる積層膜であってもよい。

【0026】

層間絶縁膜 113 上には、平坦化膜 114 が形成されている。平坦化膜 114 は、例えばアクリル樹脂などの有機膜により構成されている。この平坦化膜 114 上には、シールド層 135 が設けられている。

10

20

30

40

50

## 【0027】

シールド層135は、例えばチタンおよびアルミニウムの積層膜(Ti/A1/Ti)、あるいはITOなどにより構成されている。シールド層135は、第2層F2の形成過程で使用されるレーザ光の影響が第1層F1に及ばないようにするためのレーザ光遮蔽機能を有するものである。シールド層135の形成領域は、特に限定されないが、第1層F1と第2層F2との層間接続部分(コンタクト部分)を除いた、駆動側基板11のほぼ全面に形成されている。このシールド層135を覆って、層間絶縁膜115が形成されており、層間絶縁膜115上に、第2層F2が形成される。つまり、第2層F2は、第1層F1上に、平坦化膜114、シールド層135および層間絶縁膜115を介して形成されている。ただし、このシールド層135は必ずしも設けられていなくともよい。

10

## 【0028】

## (第2層F2)

第2層F2は、画素部110Aとして複数の画素PXL Cを含み、第1層F1の全域にわたって、上述した構成要素(有機EL素子10、キャパシタCs、書き込みトランジスタWSTr、駆動トランジスタDRT r)が形成されている。但し、図4には、画素PXL Cの一部の構成要素であるトランジスタ13A(上記の駆動トランジスタDRT rに相当)と、有機EL素子10のみを図示している。

## 【0029】

トランジスタ13Aは、層間絶縁膜115上に、ゲート電極136と、半導体層137と、ソース・ドレイン電極138とを有している。ゲート電極136と半導体層137の間には、ゲート絶縁膜116が、半導体層137とソース・ドレイン電極138との間には、層間絶縁膜117が、それぞれ形成されている。ソース・ドレイン電極138上には平坦化膜118が形成されている。このトランジスタ13Aは、第1層F1に形成されたトランジスタ13Bと平面視的に重畳して形成されている。

20

## 【0030】

ゲート電極136は、例えばモリブデン(Mo)から構成されている。半導体層137は、例えば低温ポリシリコン(LTPS)から構成されている。ソース・ドレイン電極138は、ソースまたはドレインとして機能する電極であり、上記電極層133と同様の材料から構成されている。なお、キャパシタCsは、図4には図示しないが、ゲート電極136、ゲート絶縁膜116および半導体層137の層構造を利用して形成されている。ゲート絶縁膜116、層間絶縁膜117は、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜および酸化アルミニウム膜などの無機膜からなり、それらのうちの1つからなる単層膜であってもよいし、2つ以上からなる積層膜であってもよい。このように、本実施の形態では、積層部B1に形成されるトランジスタ13Aとトランジスタ13Bとが、いずれもLTPSを含んでいる(半導体層132、137がLTPSから構成されている)。このため、トランジスタ13Aを形成する際のレーザ照射によって、トランジスタ13Bの特性への影響が懸念されるが、上記のように第1層F1と第2層F2との間にシールド層135が設けられていることから、トランジスタ13Bへのレーザ光の影響は軽減される。但し、シールド層135は必ずしも設けられていなくともよく、この場合には、レーザ照射条件を適切に設定することにより、所望の特性を有するトランジスタ13A、13Bを形成可能である。

30

## 【0031】

なお、第1層F1と第2層F2とにおいて、互いに異なる材料を用いてトランジスタ13A、13Bを形成することも可能である。例えば、第1層F1のトランジスタ13BがLTPSを含み、第2層F2のトランジスタ13Aが透明酸化物半導体(TOS:Transparent Oxide Semiconductor)を含んでいてもよい。換言すると、半導体層132がLTPSから構成され、半導体層137が透明酸化物半導体から構成されていてもよい。この場合、トランジスタ13Aの形成時に、トランジスタ13Bの特性が影響を受けにくいことから、トランジスタ13A、13Bの各特性を制御し易い。また、第2層F2の形成時にレーザ照射工程が不要となることから、第1層F1へのダメージコントロールが不要と

40

50

なる。また、第1層F1については、CMOS (Complementary Metal-Oxide Semiconductor) 構造により回路部を形成可能となる。

【0032】

あるいは、第1層F1のトランジスタ13Bと、第2層F2のトランジスタ13AとのいずれもがTOSを含んでいてもよい(半導体層132, 137がTOSから構成されていてもよい)。あるいは更に、第1層F1のトランジスタ13BがTOSを含み、第2層F2のトランジスタ13AがLTPSを含んでいてもよい(半導体層132がTOSから構成され、半導体層137がLTPSから構成されていてもよい)。なお、これらのLTPSおよびTOSに限らず、他の半導体、例えばアモルファスシリコン、微結晶シリコンあるいは高温ポリシリコン(HTPS: High Temperature Poly-silicon)が用いられてもよい。

10

【0033】

平坦化膜118は、例えばアクリル樹脂などの有機膜により構成されている。この平坦化膜118上に、画素PXL毎に、有機EL素子10が形成されている。

【0034】

有機EL素子10は、駆動側基板11の側から順に、第1電極14と、有機層16と、第2電極17とを有するものである。第1電極14は、画素毎に設けられており、この第1電極14上には全画素にわたって画素間絶縁膜15が形成されている。画素間絶縁膜15は、第1電極14に対向して開口H1を有している。この開口H1において、第1電極14と有機層16とが接している。第2電極17は、例えば、有機層16を覆うように、全画素にわたって形成されている。第2電極17上には、保護膜および封止樹脂を含む樹脂層18を介して、封止基板12が貼り合わせられている。封止基板12の一面(有機EL素子10に対向する面)には、BM/CF層19が形成されている。有機EL素子10は白色発光素子であり、有機EL素子10から発せられた白色光が、BM/CF層19を通過することによりR, G, B, Wのいずれかの色光(LR, LG, LB, LW)に分離されて取り出される。

20

【0035】

第1電極14は、光反射性を有する反射電極である。第1電極14は、アノードとして機能する場合には、例えばアルミニウム(A1), 白金(Pt), 金(Au), 銀(Ag), クロム(Cr), タングステン(W), ニッケル(Ni), 銅(Cu), 鉄(Fe), コバルト(Co), タンタル(Ta)などの金属の単体あるいはそれらのうちの少なくとも1種を含む合金から構成されることが望ましい。合金としては、例えばAg-Pd-Cu合金(銀とパラジウムと銅の合金)、あるいはA1-Nd合金を挙げることができる。あるいは、第1電極14は、上記のような金属よりなる膜と、透明導電膜との積層膜であってもよい。第1電極14は、正孔注入性の高い材料により構成されていることが望ましいが、そうでない材料(アルミニウム(A1)あるいはアルミニウムを含む合金等)であっても、適切な正孔注入層を設けることによってアノードとして使用することができる。透明導電膜としては、例えばインジウムとスズの酸化物(ITO)、InZnO(インジウム鉛オキシド)、および酸化亜鉛(ZnO)とアルミニウム(A1)との合金などが挙げられる。

30

【0036】

画素間絶縁膜15は、画素開口(発光領域、発光開口)を定義(区画)すると共に、第1電極14同士を電気的に分離するためのものである。この画素間絶縁膜15は、例えばアクリル樹脂あるいはポリイミドなどの有機材料から構成されている。

【0037】

有機層16は、電界をかけることにより電子と正孔との再結合が起こり、色光を発生する有機電界発光層を含むものである。ここでは、有機層16は、例えば白色光を発生する白色発光層を含み、例えば全画素にわたって形成されている。白色発光層は、例えば赤色発光層、緑色発光層および青色発光層を積層した構造、あるいは青色発光層と黄色発光層とを積層した構造を有している。但し、有機層16の構成はこれに限定されず、画素毎に

40

50

発光層が塗り分けられていてもよい。具体的には、画素 P X L C 每に、赤色発光層、緑色発光層、青色発光層および白色発光層のうちのいずれかが形成されていてもよい。また、有機層 1 6 は、そのような有機電界発光層の他にも、例えば正孔注入層、正孔輸送層および電子輸送層を含んでいてもよい。また、有機層 1 6 と第 2 電極 1 7との間には、電子注入層等が形成されていてもよい。

#### 【 0 0 3 8 】

第 2 電極 1 7 は、適度な仕事関数をもつと共に、光透過性を有する導電性材料、例えば I T O (酸化インジウム錫) あるいは I Z O (酸化インジウム亜鉛) などの透明導電膜から構成されている。また、第 2 電極 1 7 の構成材料としては、この他にも、マグネシウムと銀との合金 (M g A g 合金) が挙げられる。

10

#### 【 0 0 3 9 】

樹脂層 1 8 は、例えばシリコン窒化膜などの無機膜から構成される保護膜と、例えばエポキシ樹脂などから構成される封止樹脂とを含んでいる。

#### 【 0 0 4 0 】

B M / C F 層 1 9 は、第 2 電極 1 7 の光出射側に、全画素にわたって形成されている。この B M / C F 層 1 9 は、例えば X Y 平面形状が格子状である遮光部分 (ブラックマトリクス) と、格子状の開口部分に形成されたカラーフィルタ (赤色フィルタ 1 9 R, 緑色フィルタ 1 9 G, 青色フィルタ 1 9 B) とを含む層である。赤色フィルタ 1 9 R, 緑色フィルタ 1 9 G, 青色フィルタ 1 9 B は、それぞれ有機 E L 素子 1 0 に対向して形成されている。赤色フィルタ層 1 9 R は、赤色光を選択的に透過させ、その他の波長を吸収するものであり、緑色フィルタ層 1 9 G は、緑色光を選択的に透過させ、その他の波長を吸収するものであり、青色フィルタ層 1 9 B は、青色光を選択的に透過させ、その他の波長を吸収するものである。なお、W 画素では、カラーフィルタが設けられておらず、有機層 1 6 から発せられた白色光がそのまま封止基板 1 2 上へ取り出される。あるいは、W 画素には、輝度や色度を調整する目的で光学フィルタが設けられていてもよい。この B M / C F 層 1 9 の表面 (有機 E L 素子 1 0 側の面) は、オーバーコート層 1 1 9 によって覆われている。

20

#### 【 0 0 4 1 】

##### [ 作用 , 効果 ]

本実施の形態の表示装置 1 では、第 1 電極 1 4 と第 2 電極 1 7 とを介して有機層 1 6 に駆動電流が供給されると、有機電界発光素子 1 0 において色光 (例えば白色光) が発生する。この白色光が、第 2 電極 1 7 、樹脂層 1 8 、 B M / C F 層 1 9 および封止基板 1 2 を透過することにより、光 L R , L G , L B , L W として上方へ出射される。このようにして画像表示がなされる。

30

#### 【 0 0 4 2 】

ここで、一般的な有機 E L ディスプレイは、パネルの有効表示領域の周辺に額縁と呼ばれる非表示領域を有している。この額縁に、駆動回路が配置されている。

#### 【 0 0 4 3 】

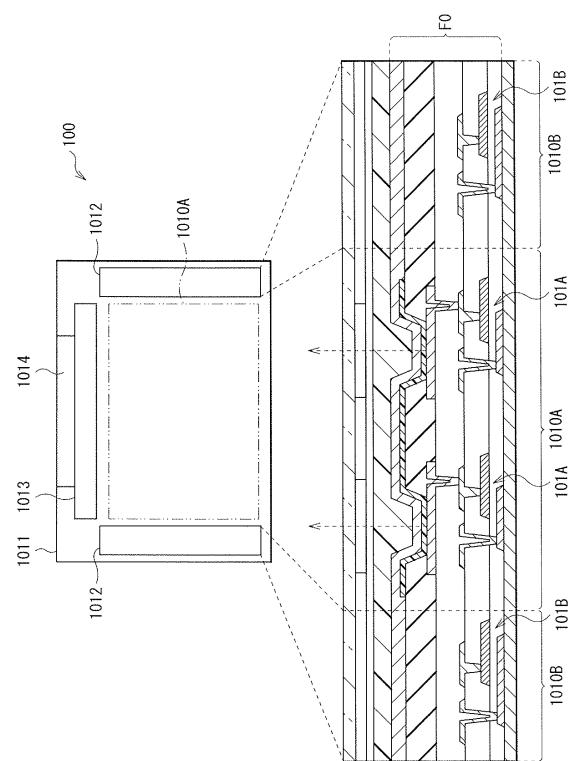

図 5 に、本実施の形態の比較例 (比較例 1) に係る表示装置 (表示装置 1 0 0) の平面構成 (上図) および断面構成 (下図) について示す。表示装置 1 0 0 は、駆動側基板 1 0 1 1 上に、複数の画素 (画素回路) を含む画素部 1 0 1 0 A を有する。この画素部 1 0 1 0 A の周辺に、走査線駆動回路 1 0 1 2 と信号線駆動回路 1 0 1 3 とを含む回路部 1 0 1 0 B が形成されている。つまり、比較例 1 では、画素部 1 0 1 0 A と、回路部 1 0 1 0 B とが、互いに同じ層 F 0 内に形成されている。詳細には、画素部 1 0 1 0 A の構成要素であるトランジスタ 1 0 1 A と、回路部 1 0 1 0 B の構成要素であるトランジスタ 1 0 1 B とが、駆動側基板 1 0 1 1 の面内方向に沿って並列に形成されている。これらのトランジスタ 1 0 1 A とトランジスタ 1 0 1 B とは、互いに同じ工程でパターン形成されるものである。

40

#### 【 0 0 4 4 】

この比較例 1 の表示装置 1 0 0 では、上記のように画素部 1 0 1 0 A の周辺に回路部 1

50

010Bが形成される。回路部1010Bの配置スペースとして額縁を確保することが望ましい。特に中小型のディスプレイでは、回路部1010Bの占有面積を減らすことが難しく、狭額縁化が困難である。

【0045】

これに対し、本実施の形態の表示装置1では、画素部110Aの周辺に回路部110Bが形成されるのではなく、回路部110Bを含む第1層F1と、画素部110Aを含む第2層F2とが積層されている。具体的には、駆動側基板11上に、第1層F1と第2層F2とがこの順に形成されている。

【0046】

このような構成により、画素部110Aの周辺に、回路部110Bを配置するためのスペースを確保する必要がなくなる。即ち、画素部110Aの周辺領域における回路部110Bの配置スペースが削減される。

【0047】

また、画素部110Aの矩形状の3辺に対応する領域に、画素部110Aと回路部110Bとが重畳する積層部B1を有している。これにより、第1層F1のうちの、回路部110Bが形成されていない領域110C（積層部B1以外の領域）には、例えば配線層134を形成することができる。このため、配線レイアウトの自由度が向上する。加えて、配線層134の線幅を十分に大きく確保することができることから、配線層134を所望のインピーダンスで形成可能となる。また、領域110Cには、このような配線層134の他にも、センサ素子やエレクトロクロミック素子などの機能素子を配置することが可能である。これにより、例えばタッチセンサ機能付きのディスプレイや、透明モードと不透明モードとを切り替えることが可能なディスプレイ（後述）などを実現可能となる。このように、回路部110Bが第1層F1内において偏って配置される場合、第1層F1にはスペース（領域110C）が生じ、このスペースを様々な用途で活用することができる。

【0048】

以上のように本実施の形態では、2次元配置された複数の画素PXL Cを有する画素部110Aと、複数の画素PXL Cを表示駆動する回路部110Bとを備え、回路部110Bを含む第1層F1と、画素部110Aを含む第2層F2とが積層されている。これにより、画素部110Aの周辺領域における回路部110Bの配置スペースを削減することができる。よって、狭額縁あるいは額縁レスを実現することができる。

【0049】

次に、上記第1の実施の形態の他の実施の形態および変形例について説明する。なお、上記第1の実施の形態と同様の構成要素については同一の符号を付し、適宜その説明を省略する。

【0050】

<変形例1>

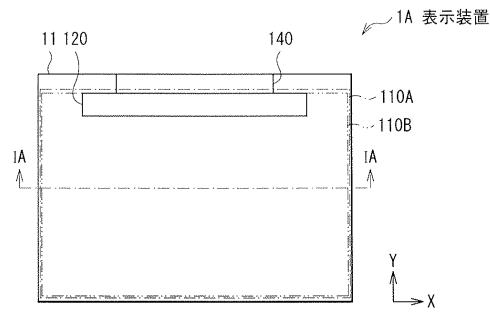

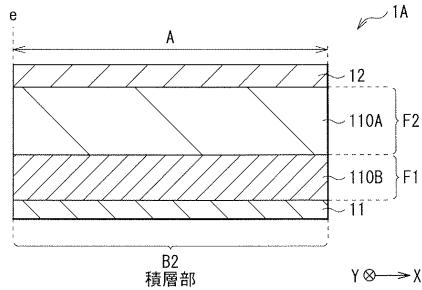

図6は、上記第1の実施の形態の変形例（変形例1）に係る表示装置（表示装置1A）の画素部110Aと回路部110Bとのレイアウトを説明するための平面模式図である。図7は、図6のIA-IA線における矢視断面図である。上記第1の実施の形態では、回路部110Bが第1層F1において、選択的な領域（矩形状の3辺に対応する領域）に偏って配置される場合について説明したが、回路部110Bのレイアウトはこれに限定されない。例えば、本変形例のように、回路部110Bを構成する複数の回路要素が第1層F1内に分散して配置されていてもよい。換言すると、第1層F1の全域にわたって回路部110Bが形成され、表示領域Aの全域が、画素部110Aと回路部110Bとが積層される積層部B2となっている。

【0051】

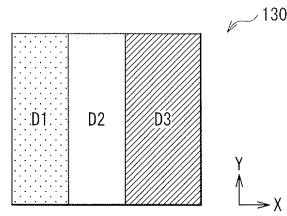

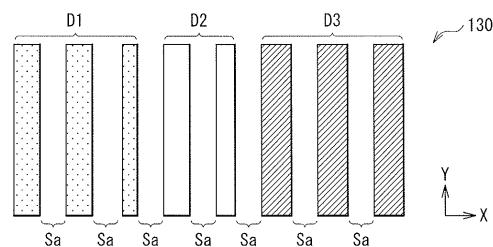

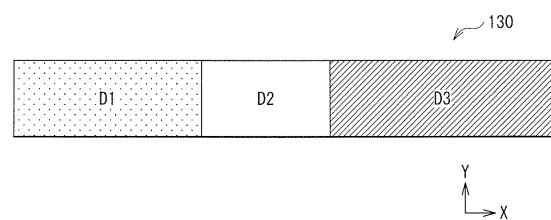

図8A～図8Cは、回路部110Bの回路要素（回路要素D1, D2, D3）のレイアウトの一例を模式的に表したものである。図8Aに示したように、上記第1の実施の形態のように所定の領域にのみ回路部110Bが配置される場合、例えば、走査線駆動回路130の回路要素D1～D3は、所定の領域内に収まるように隙間なく密に配置される。-

10

20

30

40

50

方、本変形例のように、積層部 B 2 が表示領域 A の全域に形成される場合には、例えば図 8 B に示したように、回路要素 D 1 ~ D 3 をそれぞれ細分化し、間隙 S a をおいて配置させることができる。あるいは、図 8 C に示したように、回路要素 D 1 ~ D 3 を X 方向に沿って延在する細長い領域にわたって配置することもできる。走査線駆動回路 1 3 0 は、一般的に画素部 1 1 0 A の 1 辺に対応する領域に Y 方向に沿って延在するように形成されるが、本変形例では、回路部 1 1 0 B のレイアウトの制限が小さいことから、X 方向に沿って延在するように形成することもできる。また、このような X 方向に伸びる回路要素 D 1 ~ D 3 を複数本配列させることも可能である。

#### 【 0 0 5 2 】

このように、第 1 層 F 1 に回路部 1 1 0 B の回路要素を分散して配置してもよく、これにより、回路部 1 1 0 B のレイアウトの自由度が高まる。また、回路部 1 1 0 B の分散配置により、回路要素の密度が低くなることから、空いた領域に透過窓を形成して表示領域 A の透明性を高めることもできる（詳細は後述）。なお、上記の回路部 1 1 0 B のレイアウトは一例であり、用途や他の素子のレイアウトに応じて様々なレイアウトを取りうる。

#### 【 0 0 5 3 】

< 变形例 2 >

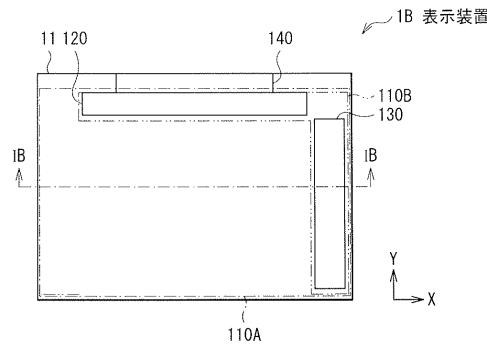

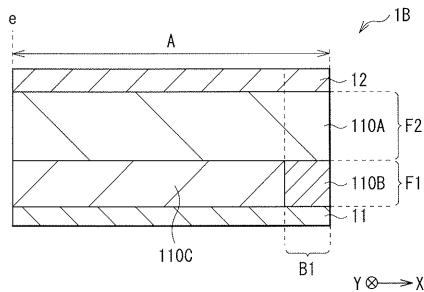

図 9 は、上記第 1 の実施の形態の変形例（変形例 2）に係る表示装置（表示装置 1 B）の画素部 1 1 0 A と回路部 1 1 0 B とのレイアウトを説明するための平面模式図である。図 1 0 は、図 9 の I B - I B 線における矢視断面図である。上記第 1 の実施の形態では、回路部 1 1 0 B が第 1 層 F 1 において、選択的な領域（矩形状の 3 辺に対応する領域）に偏って配置される場合について説明したが、回路部 1 1 0 B のレイアウトはこれに限定されない。例えば、本変形例のように、回路部 1 1 0 B を構成する複数の回路要素が第 1 層 F 1 において、矩形状の 2 辺に対応する領域に配置されていてもよい。具体的には、回路部 1 1 0 B のうち走査線駆動回路 1 3 0 が、矩形状の 1 边に集約して設けられている。この場合にも、第 1 層 F 1 のうち、画素部 1 1 0 A と回路部 1 1 0 B との積層部 B 1 以外の領域 1 1 0 C には、上記第 1 の実施の形態と同様、配線層 1 3 4 を形成することができる。その一例を、図 1 1 に示す。あるいは、領域 1 1 0 C には、上述したような機能素子が形成されていてもよい。

#### 【 0 0 5 4 】

このように、走査線駆動回路 1 3 0 を矩形状の 1 边（信号線駆動回路 1 2 0 とは異なる 1 つの辺）に対応する領域に集約して形成することにより、即ち回路部分を矩形状の 2 边に集約して形成することにより、後述の透明ディスプレイ用途において、次のような効果がある。詳細は後述するが、回路部分が集約されていない 2 边に対応する領域の第 2 層 F 2 の画素部 1 1 0 A に透過窓を設けることで、額縁レスの 2 边透明ディスプレイを実現できる。また、信号線駆動回路 1 2 0 と走査線駆動回路 1 3 0 とを、矩形状の 1 边に集約して配置するようにしてもよく、この場合には、額縁レスの 3 边透明ディスプレイを実現可能となる。

#### 【 0 0 5 5 】

< 第 2 の実施の形態 >

上記第 1 の実施の形態において説明したように、画素部 1 1 0 A と回路部 1 1 0 B との積層（第 1 層 F 1 と第 2 層 F 2 との積層）により、第 1 層 F 1 におけるレイアウトの自由度が高まり、回路部 1 1 0 B を分散して配置することが可能となる。このような回路部 1 1 0 B の分散配置を利用して、例えば、光透過性を有し、背面側の景色が透けて見えるような透明ディスプレイを実現可能となる。

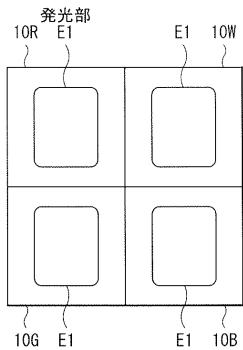

#### 【 0 0 5 6 】

ここで、一般的なディスプレイでは、図 1 2 に示したように、例えば 4 色の画素 1 0 R, 1 0 G, 1 0 B, 1 0 W のそれぞれに発光部（発光開口）E 1 が形成され、この発光部 E 1 からのみ光が射出するように構成されている。これに対し、図 1 3 に示したように、透明ディスプレイでは、画素 1 0 R, 1 0 G, 1 0 B, 1 0 W のそれぞれに、発光部 E 1 と、光透過用の窓（透過部 T 1）とが形成されている。この透過部 T 1 により、各画素を

10

20

30

40

50

光が透過可能となり、透明性を有するディスプレイを実現可能となる。

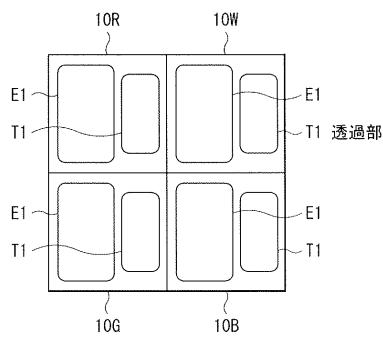

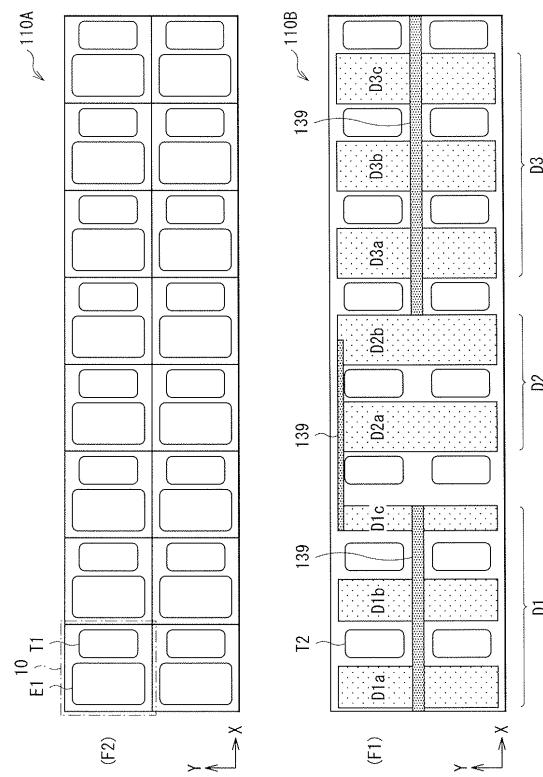

【0057】

図14は、本開示の第2の実施の形態の表示装置（表示装置2）の要部構成を表すXY平面図である。図14において、上図は、画素部110Aを含む第2層F2の要部構成を、下図は、回路部110Bを含む第1層F1の要部構成を、それぞれ表す。このように、本実施の形態では、第2層F2において、有機EL素子10毎（画素PXL每）に、発光部E1と透過部T1とが設けられている。一方、第1層F1にも、透過部T2が設けられている。上記変形例1と同様、第1層F1では、回路部110Bの回路要素D1～D3が分散配置され、これによって生じた間隙に透過部T2が形成されている。第1層F1における透過部T2と第2層F2における透過部T1とは、積層方向において互いに連通する位置に設けられ、これらの透過部T1、T2を貫通して光が透過する。なお、第1層F1では、回路要素D1、D2、D3をそれぞれ電気的に接続する配線層139が、透過部T2を避けるように配置されている。10

【0058】

図15は、表示装置2の具体的な断面構成を表したものである。このように、第1層F1に回路部110Bの回路要素が分散配置されており（ここではトランジスタ13Bのみを図示する）、積層方向において連通する透過部T1、T2を光が透過する。なお、本実施の形態では、ブラックマトリクスは形成されておらず、樹脂層18上には、赤色フィルタ21R、緑色フィルタ21G、青色フィルタ21Bを含むCF層21が形成されている。20 CF層21の表面は、オーバーコート層119によって覆われている。

【0059】

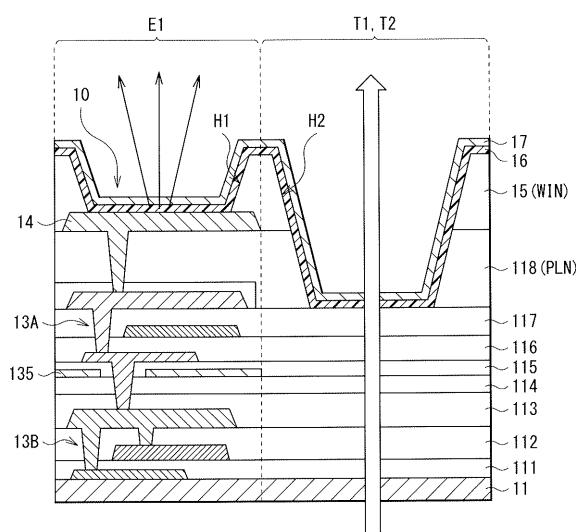

図16は、発光部E1および透過部T1、T2付近の素子構造を拡大したものである。このように、発光部E1に対応する領域では、トランジスタ13A、13Bが重畳すると共に、有機EL素子10が形成されている。金属などの不透明な層は、透過部T1、T2を避けて設けられている。一方、透過部T1、T2に対応する領域では、比較的透明性の高い膜が積層されている。材料や厚みに起因して透明性が低い層（例えば、ここでは平坦化膜118、画素間絶縁膜15）では、開口（開口H2）を設けることにより、あるいは厚みを薄くすることによって光透過性が高められている。なお、図16において、トランジスタ「13A」、「13B」として図示した部分は、厳密にはトランジスタ構造となっていないが、説明上そのように付記している。図示した部分は、トランジスタ13A、13Bがそれぞれ形成される層構造に相当する。30

【0060】

本実施の形態の表示装置2においても、回路部110Bを含む第1層F1と、画素部110Aを含む第2層F2とが積層されることにより、画素部110Aの周辺領域における回路部110Bの配置スペースを削減することができる。よって、上記第1の実施の形態と同等の効果を得ることができる。また、第1層F1内に回路部110Bを分散して配置することにより、第1層F1と第2層F2とにおいて連通する透過部T1、T2を形成することができ、透明ディスプレイを実現可能となる。

【0061】

また、上記変形例2において述べたように走査線駆動回路130を矩形状の1辺（信号線駆動回路120とは異なる1つの辺）に対応する領域に集約し、即ち回路部分を矩形状の2辺に集約して形成する。その上で、他の2辺に対応する領域の第2層F2の画素部110Aに透過窓を設けることで、図17Aに示したように、回路部110Bが形成されていない2辺に対応する領域を透明にし、かつ端面発光とすることができる。つまり、回路部110Bの集約されている2辺を除いた領域が透明領域（透明領域110D）となり、額縁レスの2辺透明ディスプレイを実現可能となる。また、信号線駆動回路120と走査線駆動回路130とを、矩形状の1辺に集約して配置するようにもよく、この場合には、額縁レスの3辺透明ディスプレイを実現可能となる（図17B）。但し、この場合、走査線WSLは、信号線DTLと同様にY方向に沿って延伸して形成される。この走査線WSLは、他の層にX方向に沿って形成された配線とクロスする位置で層間接続される。4050

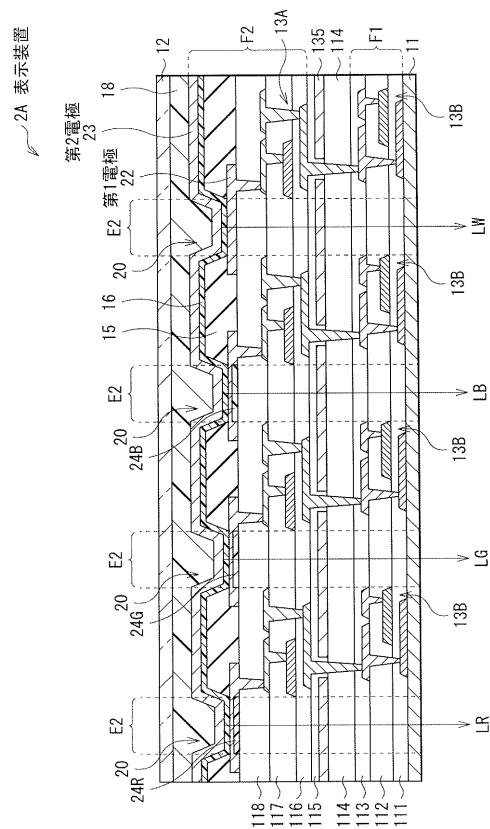

## 【0062】

## &lt;変形例3&gt;

図18は、上記第1, 第2の実施の形態の変形例(変形例3)に係る表示装置(表示装置2A)の断面構成を表したものである。上記実施の形態等では、トップエミッション方式の有機EL素子10を用いた表示装置を例に挙げて説明したが、本変形例のように、ボトムエミッション方式(下面発光方式)の有機EL素子(有機EL素子20)が用いられてよい。本変形例の表示装置2Aでは、第1層F1において、上記変形例1および第2の実施の形態と同様、回路部110Bが分散配置され、回路要素同士の間隙を光(発光光、あるいは発光光および透過光)が通るように構成される。有機EL素子20は、第1電極22と第2電極23との間に有機層16を有している。有機EL素子20(発光部E2)が、トランジスタ13A, 13Bに非重畳となるように形成されている。第1電極22は、ITOなどの透明導電膜により構成され、画素間絶縁膜15によって画素毎に電気的に分離されている。第2電極23は、反射電極であり、例えば上記第1の実施の形態の第1電極14と同様の材料により構成されている。カラーフィルタ(赤色フィルタ24R, 緑色フィルタ24G, 青色フィルタ24B)は、第1電極22よりも下層に形成され、いわゆるオンチップカラーフィルタ(OCCF)となっている。

## 【0063】

このように、第1層F1と第2層F2との積層構造において、第1層F1内に回路部110Bを分散配置することにより、ボトムエミッション方式のディスプレイ、あるいはボトムエミッション方式の透明ディスプレイを実現可能となる。表示装置2Aにおいても、狭額縁あるいは額縁レスを実現可能となる。

## 【0064】

## &lt;第3の実施の形態&gt;

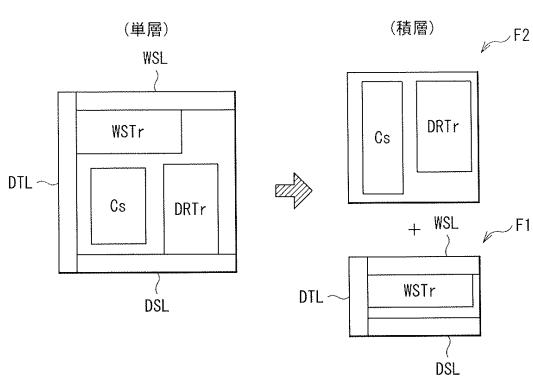

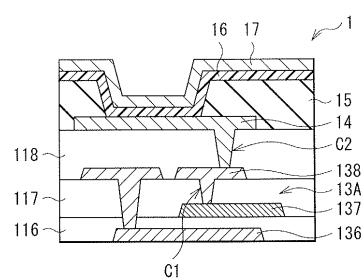

図19は、本開示の第3の実施の形態の表示装置(表示装置3)の断面構成を表したものである。本実施の形態においても、上記第1の実施の形態と同様、回路部110Bを含む第1層F1と、画素部110Aを含む第2層F2とが積層されている。また、回路部110Bと画素部110Aとは、積層部B1において重畳する。但し、本実施の形態では、上記第1の実施の形態と異なり、画素PXLcのうちの一部が、第2層F2ではなく第1層F1に形成されている。例えば、書き込みトランジスタWSTrに相当するトランジスタ13Cが第1層F1に形成されている。第2層F2には、駆動トランジスタDRT<sub>r</sub>に相当するトランジスタ13Aが、トランジスタ13Cに平面視的に重畳するように形成されている。トランジスタ13Aとトランジスタ13Cとは、平坦化膜114等を介して層間接続されている。

## 【0065】

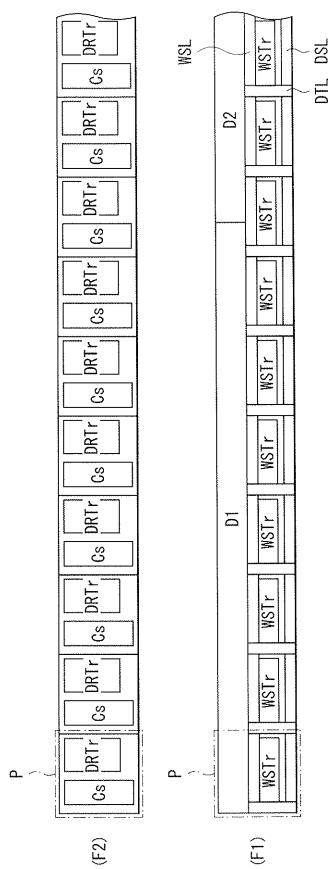

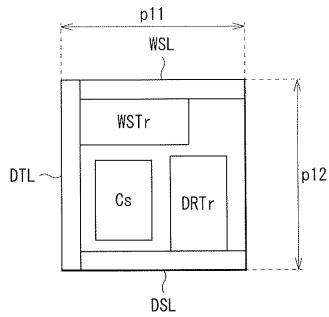

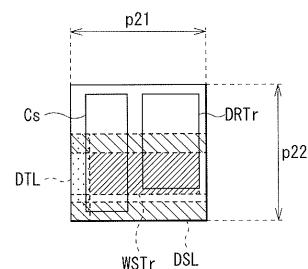

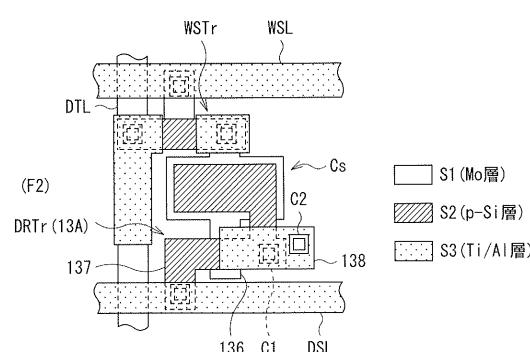

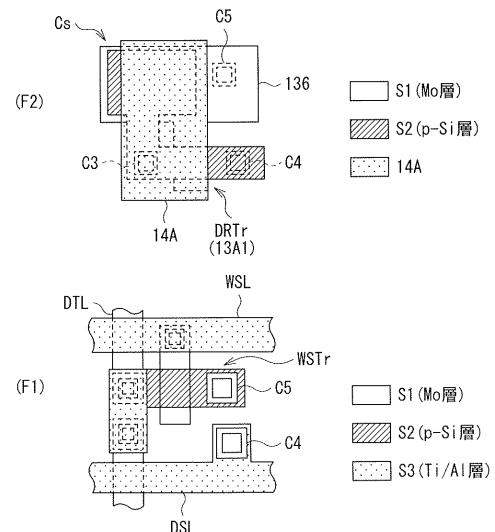

図20は、画素PXLcの構成要素(書き込みトランジスタWSTr, 駆動トランジスタDRT<sub>r</sub>, キャパシタCs)を1つの層に配置(以下、「単層配置」という)した場合と、2層(第1層F1と第2層F2)に分けて配置(以下、「積層配置」という)した場合とレイアウトの一例を表したものである。なお、信号線DTL, 走査線WSLおよび電源線DSLについても図示している。このように、単層配置の場合には、書き込みトランジスタWSTr, 駆動トランジスタDRT<sub>r</sub>, キャパシタCsが互いに重畳しないように配置される。一方、積層配置の場合には、例えば第1層F1に、書き込みトランジスタWSTrと、信号線DTL, 走査線WSLおよび電源線DSLとが配置され、第2層F2に、駆動トランジスタDRT<sub>r</sub>とキャパシタCsとが配置される。このように、積層配置では、第1層F1および第2層F2のそれぞれにおける素子の占有面積が、単層配置の場合よりも減少する。

## 【0066】

図21は、上記のような積層配置と、回路要素の分散配置とを組み合わせてレイアウトを行った例である。なお、領域Pは、1つの画素に相当する領域である。このように、第1層F1では、書き込みトランジスタWSTrと、信号線DTL, 走査線WSLおよび電源線DSLと共に、回路要素D1, D2, ...が配置されている。換言すると、第1層F1

では、回路要素の分散配置によって、空きスペースができるから、その空きスペースを利用して、書き込みトランジスタ W S T r 等が配置される。

#### 【0067】

本実施の形態では、上記第1の実施の形態と同様、回路部 110B を含む第1層 F 1 と、画素部 110A を含む第2層 F 2 とが積層されることにより、画素部 110A の周辺領域における回路部 110B の配置スペースを削減することができる。よって、上記第1の実施の形態と同等の効果を得ることができる。また、画素部 110A の一部を第1層 F 1 に形成することにより、図 2 2 の単層配置の場合と同じ構成要素を、図 2 3 に示したように、第1層 F 1 (書き込みトランジスタ W S T r , 信号線 D T L , 走査線 W S L および電源線 D S L ) と、第2層 F 2 (駆動トランジスタ D R T r , キャパシタ C s ) とにそれぞれ形成することができる。つまり、書き込みトランジスタ W S T r , 信号線 D T L , 走査線 W S L および電源線 D S L と、駆動トランジスタ D R T r , キャパシタ C s を、平面視的に重畳して配置することができる。このため、画素幅 p 12 が、単層配置の場合の画素幅 p 11 よりも小さくなり、高精細化を実現可能となる。

#### 【0068】

また、上記のような積層配置では、トランジスタ 13A (駆動トランジスタ D R T r ) とトランジスタ 13C (書き込みトランジスタ W S T r ) とが、それぞれ独立したプロセスにより形成される。このため、トランジスタ 13A とトランジスタ 13C との性能を個別に制御することができる。

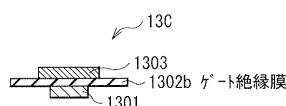

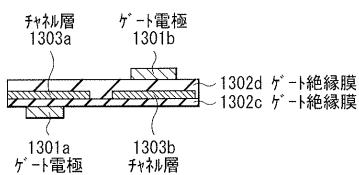

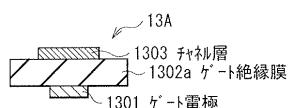

#### 【0069】

例えば、第2層 F 2 のトランジスタ 13A (駆動トランジスタ D R T r ) では、第1層 F 1 のトランジスタ 13C (書き込みトランジスタ W S T r ) に比べ、高い性能 (例えば、高移動度) が要求されない。このため、例えば、図 2 4 A に示したように、トランジスタ 13A では、ゲート電極 1301 とチャネル層 1303 との間のゲート絶縁膜 1303a の厚みを比較的大きく設定する。一方、図 2 4 B に示したように、トランジスタ 13C では、ゲート電極 1301 とチャネル層 1303 との間のゲート絶縁膜 1303b の厚みを比較的小さく設定する。このようにトランジスタ 13A , 13C の性能を個別に制御することができる。

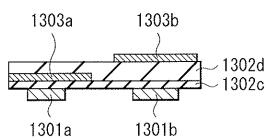

#### 【0070】

また、第1層 F 1 には、同一のパターニング工程により、トランジスタ 13C を含む複数のトランジスタが形成されてもよい。例えば、図 2 4 C に示したように、ゲート絶縁膜 1302c を間にしたゲート電極 1301a とチャネル層 1303a が配置されたトランジスタと、ゲート絶縁膜 1302d を間にしたゲート電極 1301b とチャネル層 1303b が配置されたトランジスタとが形成されてもよい。あるいは、図 2 4 D に示したように、ゲート絶縁膜 1302c を間にしたゲート電極 1301a とチャネル層 1303a が配置されたトランジスタと、ゲート絶縁膜 1302c , 1302d を間にしたゲート電極 1301b とチャネル層 1303b が配置されたトランジスタとが形成されてもよい。なお、上述したように、上下のトランジスタにおいて、構成材料 (L T P S , T O S , アモルファスシリコン, 微結晶シリコン, H T P S 等) を変えることによっても性能に変化を持たせることができる。このように、積層配置によって、様々な性能のトランジスタを組み合わせて使用することができる。

#### 【0071】

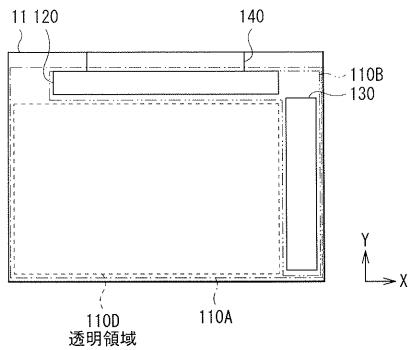

##### <変形例 4 >

図 2 5 は、上記第3の実施の形態の変形例 (変形例 4 ) に係る表示装置 (表示装置 3A ) の断面構成を表したものである。本変形例では、画素部 110A において、有機 E L 素子 10 の第1電極 (第1電極 14A ) が、駆動トランジスタ D R T r に相当するトランジスタ (トランジスタ 13A 1 ) のソース・ドレイン電極を兼ねている。換言すると、第1電極 14A とトランジスタ 13A 1 との間の接続層 (図 4 に示したソース・ドレイン電極 138 に相当) が省略されており、上記第1の実施の形態よりも簡易な層構造となっている。詳細には、本変形例では、上記第1の実施の形態における層間絶縁膜 117 とソース

10

20

30

40

50

・ドレイン電極 138 とが省略され、半導体層 137 に第 1 電極 14A が直接に接続されることで、プロセス工程数が削減される。この理由について、以下に説明する。

#### 【0072】

図 26 は、本変形例の比較例（比較例 2）として上記第 1 の実施の形態に係る表示装置 1 の要部断面構成を表したものである。図 27 は、表示装置 1 の要部構成の平面レイアウトを表したものである。第 2 層 F2 に、画素 PXL C の構成要素（書き込みトランジスタ WSTR, 駆動トランジスタ DRT r, キャパシタ Cs 等）が形成される場合、例えば図 27 に示したようなレイアウトで配置される。即ち、ゲート電極 136 と同一層内に金属層（Mo 層）S1 がパターン形成され、半導体層 137 と同一層内には、半導体層（p-Si 層）S2 がパターン形成されている。これらの金属層 S1 および半導体層 S2 は、ソース・ドレイン電極 138 と同一層内にパターン形成される金属層（Ti/A1 層）S3 と、コンタクト部 C1 等を介して層間接続されている。金属層 S3 には、走査線 WSL や電源線 DSL などの配線層も形成される。このため、比較例 2 では、金属層 S3 と同一層内に、第 1 電極 14 を形成するスペースが乏しいことから、金属層 S3 とは異なる層に、第 1 電極 14 が形成される。具体的には、第 1 電極 14 は、平坦化膜 118 を介して形成されており、第 1 電極 14 とソース・ドレイン電極 138 とが、コンタクト部 C2 を介して電気的に接続されている。10

#### 【0073】

ここで、上記第 3 の実施の形態では、書き込みトランジスタ WSTR（トランジスタ 13C）が第 1 層 F1 に、駆動トランジスタ DRT r（トランジスタ 13A）が第 2 層 F2 に、それぞれ形成された「積層配置」について説明したが、この積層配置によって、第 2 層 F2 では、上記比較例 2 の金属層 S3 のうち、書き込みトランジスタ WSTR, 走査線 WSL および電源線 DSL に使用されている部分が不要となる。換言すると、本変形例の表示装置 3A では、上記金属層 S3 のうち、駆動トランジスタ DRT r に使用されている部分（第 1 電極 14A を兼ねる部分）のみが配置される。このため、第 1 電極 14A の面積を比較例 2 よりも広く確保することができる。20

#### 【0074】

図 28 は、表示装置 3A の要部断面構成を表したものである。図 29 は、表示装置 3A の要部構成の平面レイアウトを表したものである。なお、図 29 の上図は第 2 層 F2 のレイアウト、下図は第 1 層 F1 のレイアウトにそれぞれ対応する。本変形例においても、上記第 3 の実施の形態と同様、第 1 層 F1 に、書き込みトランジスタ WSTR（トランジスタ 13C），走査線 WSL，信号線 DTL および電源線 DSL が形成されている。第 2 層 F2 には、駆動トランジスタ DRT r（トランジスタ 13A1）およびキャパシタ Cs が形成されている。30

#### 【0075】

第 1 層 F1 では、例えば図 29 の下図に示したようなレイアウトで、ゲート電極 131 と同一層内に形成された金属層（Mo 層）S1 と、半導体層 132 と同一層内に形成された半導体層（p-Si 層）S2 と、電極層 133 と同一層内に形成された金属層（Ti/A1 層）S3 と、が平面視的に重畳して配置されている。第 2 層 F2 では、例えば図 29 の上図に示したレイアウトで、ゲート電極 136 と同一層内に形成された金属層（Mo 層）S1 と、半導体層 137 と同一層内に形成された半導体層（p-Si 層）S2 と、第 1 電極 14A とが、平面視的に重畳して配置されている。40

#### 【0076】

このような積層配置において、コンタクト部 C4, C5 等を介して第 1 層 F1 と第 2 層 F2 とが層間接続されている。第 2 層 F2 では、コンタクト部 C3 を介して半導体層 137 と第 1 電極 14A が層間接続されている。

#### 【0077】

本変形例では、上記のように、積層配置によって第 2 層 F2 内に空きスペースが生じることから、第 1 電極 14A を、金属層 S3 と同一層内に形成可能となる。よって、層間絶縁膜 117 およびソース・ドレイン電極 138 を省略して、第 1 電極 14A を形成可能と50

なり、層構造およびプロセス工程を簡略化することができる。

【0078】

<変形例5>

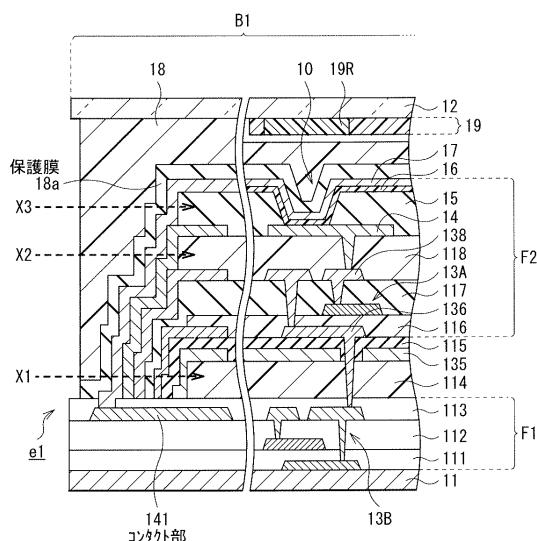

図30は、上記実施の形態等の変形例(変形例5)に係る表示装置の端面付近の断面構成を表したものである。上記実施の形態等の表示装置は、第1層F1と第2層F2との積層構造を有するが、この積層構造は、本変形例のように、端面e1において無機絶縁膜あるいは金属膜などにより覆われていることが望ましい。具体的には、駆動側基板11上には、第1層F1、平坦化膜114、シールド層135、層間絶縁膜115および第2層F2がこの順に形成されている。第2層F2の上に、樹脂層18およびBM/CF層19を介して封止基板12が貼り合わせられている。

10

【0079】

この積層構造のうち、特に平坦化膜114と、第2層F2内の平坦化膜118および画素間絶縁膜15とは、有機材料から構成されることが多い。このため、これらの平坦化膜114, 118および画素間絶縁膜15を介した水分の浸入が懸念される(X1, X2, X3)。このため、表示装置の端面e1では、平坦化膜114, 118および画素間絶縁膜15を覆うように、他の層(無機絶縁膜あるいは金属膜)が延在して形成されていることが望ましい。ここでは、シールド層135、層間絶縁膜115、ゲート電極136(M0層S1)、層間絶縁膜117、ソース・ドレイン電極138(Ti/A1層S3)、第1電極14および第2電極17が端面e1まで延在形成されている。なお、第2電極17は、駆動側基板11上の第1層F1に形成されたコンタクト部141(カソードコンタクト)に接続されている。また、第2層F2と樹脂層18との間に、表示領域の全面と端面e1とを覆うように保護膜18aが形成されている。保護膜18aは、例えばシリコン酸化膜あるいはシリコン窒化膜などよりなる無機膜である。

20

【0080】

本変形例のように、端面e1において無機絶縁膜あるいは金属膜よりなる層が、有機膜よりなる層を覆うように形成されることにより、表示装置の封止性能が向上し、信頼性を高めることができる。上記実施の形態等では、第1層F1と第2層F2との積層構造により、層数が増えることから、有機膜による水分の浸入経路が増える可能性があることから、本変形例のような封止構造が有効である。

30

【0081】

<適用例>

以下、上記実施の形態等で説明した表示装置の適用例について説明する。上記実施の形態の表示装置は、テレビジョン装置、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置、ビデオカメラ、スマートフォン、タブレット型ディスプレイなど、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器の表示装置に適用することが可能である。特に、中小型のディスプレイあるいは透明ディスプレイに好適である。以下にその一例を示す。

【0082】

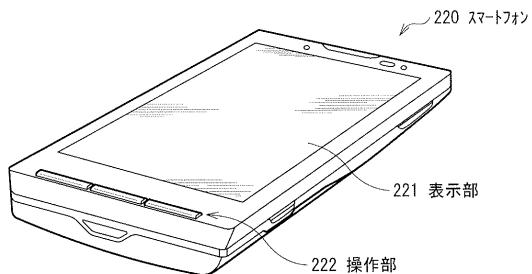

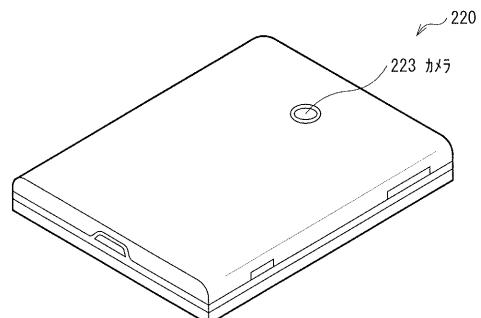

図31Aおよび図31Bは、スマートフォン220の外観を表したものである。このスマートフォン220は、例えば、表側に表示部221および操作部222を有し、裏側にカメラ223を有しており、表示部221に上記実施の形態等の表示装置が搭載されている。

40

【0083】

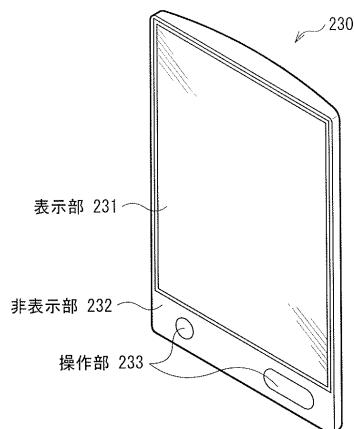

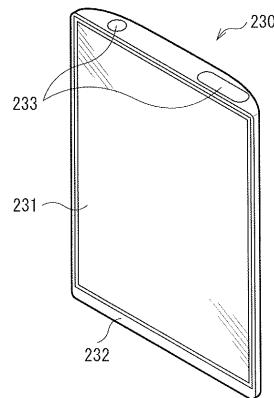

図32Aおよび図32Bは、タブレット型ディスプレイ230の外観を表したものである。このタブレット型ディスプレイ230は、例えば、タッチパネル部231、筐体232および操作部233を有しており、タッチパネル部231に上記実施の形態等の表示装置が搭載されている。操作部233は、タッチパネル部231の額縁部分に設けられてもよいし(図32A)、筐体232の側面に設けられていてもよい(図32B)。

【0084】

50

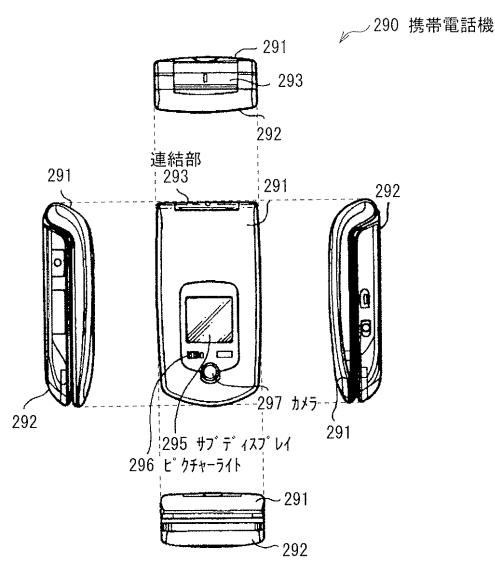

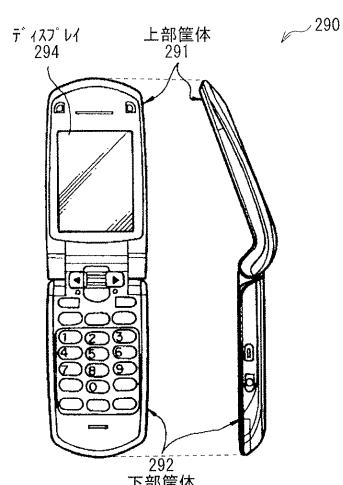

図33Aおよび図33Bは、携帯電話機290の外観を表したものである。この携帯電話機290は、例えば、上側筐体291と下側筐体292とを連結部(ヒンジ部)293で連結したものであり、ディスプレイ294、サブディスプレイ295、ピクチャーライト296およびカメラ297を有している。ディスプレイ294またはサブディスプレイ295が上記実施の形態等の表示装置により構成されている。

#### 【0085】

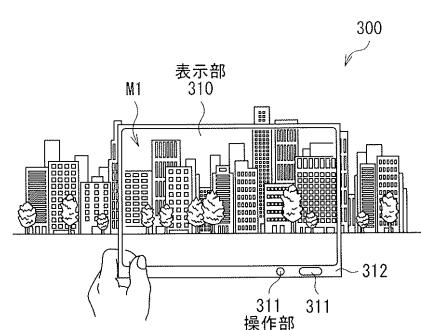

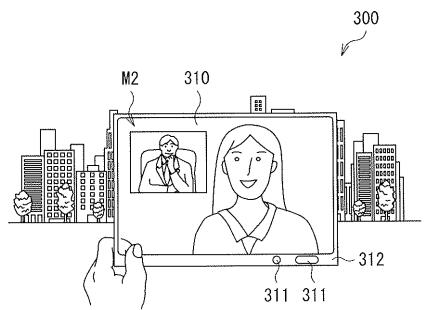

図34Aおよび図34Bは、タブレット型透明ディスプレイ300の外観を表したものである。このタブレット型透明ディスプレイ300は、例えば表示部310と、操作部311と、筐体312とを有しており、表示部310に上記実施の形態等の表示装置が搭載されている。このタブレット型透明ディスプレイ300では、例えばエレクトロクロミック素子を用いることにより、透明ディスプレイモードM1(図34A)とディスプレイモードM2(図34B)とを切り替えることができる。エレクトロクロミック素子は、上記第1の実施の形態において説明したように、第1層F1の積層部B1以外のスペースを利用して配置することができる。透明ディスプレイモードM1では、表示部310の背景を透過しつつ、画像や文字情報を表示することが可能である。

10

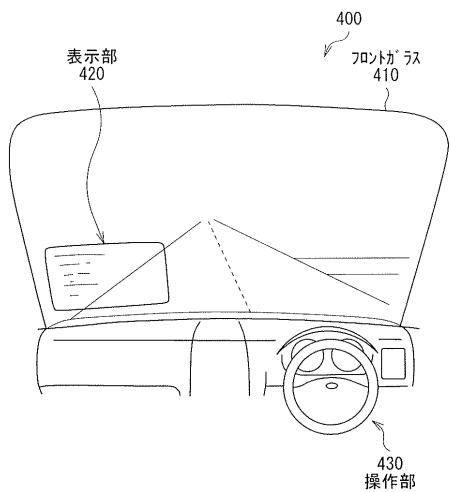

#### 【0086】

図35は、ヘッドアップディスプレイ400の外観を表したものである。このヘッドアップディスプレイ400は、例えば自動車のフロントガラス410に埋め込まれた表示部420を有しており、表示部420が上記実施の形態等の表示装置に相当する。表示部420は、ガラス越しの景色を透過しつつ、画像や文字情報を表示可能であり、例えばドライバーの視界を狭めることなく情報提示を行うものである。

20

#### 【0087】

上記実施の形態等の表示装置は、狭額縁、額縁レスあるいは透明ディスプレイを実現可能であることから、上記タブレット型透明ディスプレイ300およびヘッドアップディスプレイ400のような環境一体型のアンビエントディスプレイとして好適に用いることができる。また、狭額縁あるいは額縁レスの実現により、複数枚のパネルを敷き詰めて配置する、いわゆるタイリング型のディスプレイにも適している。

#### 【0088】

以上、実施の形態および変形例を挙げて本開示を説明したが、本開示は上記実施の形態等に限定されるものではなく、種々変形が可能である。例えば、上記実施の形態等では、1つのピクセルがR、G、B、Wの4つのサブピクセルにより構成される場合を例示したが、本開示の画素構成はこれに限定されるものではない。例えば、1ピクセルを、R、G、Bの3画素構成としてもいし、あるいは2画素構成としてもよい。また、R、G、B、Y(黄)の4画素構成であってもよい。

30

#### 【0089】

また、上記実施の形態等では、画素の表示素子として、有機EL素子を例に挙げたが、本開示の表示素子は、これに限定されず、他の表示素子、例えば液晶表示素子あるいは電気泳動素子などであってもよい。

#### 【0090】

さらに、上記実施の形態等では、有機電界発光素子から発せられた白色光を、カラーフィルタを用いて色分離することが可能な素子構造を例示したが、本開示は、カラーフィルタを用いない素子構造にも適用可能である。

40

#### 【0091】

加えて、上記実施の形態等において説明した各層の材料および厚み、または成膜方法および成膜条件などは特に限定されるものではなく、他の材料および厚みとしてもよく、または他の成膜方法および成膜条件としてもよい。

#### 【0092】

また、上記実施の形態では、アクティブマトリクス型の表示装置の場合について説明したが、本開示はパッシブマトリクス型の表示装置への適用も可能である。更にまた、アクティブマトリクス駆動のための画素駆動回路の構成は、上記実施の形態で説明したものに

50

限られず、必要に応じて容量素子やトランジスタを追加してもよい。その場合、画素駆動回路の変更に応じて、上述した信号線駆動回路 120 や走査線駆動回路 130 のほかに、必要な駆動回路を追加してもよい。また、上記実施の形態等において説明した効果は一例であり、他の効果であってもよいし、更に他の効果を含んでいてもよい。

## 【0093】

なお、本開示は、以下のような構成であってもよい。

## (1)

それぞれが表示素子を含み 2 次元配置された複数の画素を有する画素部と、前記複数の画素を表示駆動する駆動回路部とを備え、

10

前記駆動回路部を含む第 1 層と、前記画素部を含む第 2 層とが積層されている表示装置。

## (2)

基板上に、前記第 1 層と前記第 2 層とがこの順に形成されている上記(1)に記載の表示装置。

## (3)

前記駆動回路部は、複数の回路要素を有し、前記複数の回路要素は、前記第 1 層内に分散して設けられている上記(1)または(2)に記載の表示装置。

## (4)

前記第 1 層と前記第 2 層とは、互いに積層方向に沿って連通する光透過部を有する上記(1)～(3)のいずれかに記載の表示装置。

20

## (5)

前記駆動回路部は、複数の回路要素を有し、前記複数の回路要素は、前記第 1 層内に分散して設けられ、前記光透過部は、前記複数の回路要素同士の間隙に形成されている上記(4)に記載の表示装置。

## (6)

前記駆動回路部は、複数の回路要素を有し、前記複数の回路要素は、前記第 1 層のうちの選択的な第 1 の領域に設けられている上記(1)～(5)のいずれかに記載の表示装置。

30

## (7)

前記第 1 層のうちの他の選択的な第 2 の領域に、配線層が形成されている上記(6)に記載の表示装置。

## (8)

前記第 1 層のうちの他の選択的な第 2 の領域に、機能素子が形成されている上記(6)または(7)に記載の表示装置。

## (9)

前記画素部は平面視的に矩形状を成し、前記第 1 の領域は、前記矩形状の少なくとも 1 辺に対応する領域である上記(6)～(8)のいずれかに記載の表示装置。

40

## (10)

前記画素部に形成されたトランジスタと、前記回路部に形成されたトランジスタとは、平面視的に重畠して形成されている

上記(1)～(9)のいずれかに記載の表示装置。

## (11)

前記画素部は複数の画素トランジスタを含み、前記複数の画素トランジスタのうちの 1 つが、前記第 1 層に形成されている上記(1)～(10)のいずれかに記載の表示装置。

## (12)

50

前記画素部は、前記画素トランジスタとして、書き込みトランジスタと駆動トランジスタとを含み、

前記書き込みトランジスタが前記第1層に形成され、前記駆動トランジスタが前記第2層に形成されている

上記(11)に記載の表示装置。

(13)

前記表示素子の電極は、前記駆動トランジスタのソース・ドレイン電極を兼ねている

上記(12)に記載の表示装置。

(14)

前記第1層に形成されたトランジスタは、低温ポリシリコンを含み、

10

前記第2層に形成されたトランジスタは、酸化物半導体を含む

上記(2)～(13)のいずれかに記載の表示装置。

(15)

前記第1層に形成されたトランジスタと、前記第2層に形成されたトランジスタとは、

いずれも酸化物半導体を含む

上記(2)～(13)のいずれかに記載の表示装置。

(16)

前記第1層に形成されたトランジスタと、前記第2層に形成されたトランジスタとは、

いずれも低温ポリシリコンを含む

20

上記(2)～(13)のいずれかに記載の表示装置。

(17)

前記第1層に形成されたトランジスタは、酸化物半導体を含み、

前記第2層に形成されたトランジスタは、低温ポリシリコンを含む

上記(2)～(13)のいずれかに記載の表示装置。

(18)

前記第1層と前記第2層との間に、シールド層が設けられている

上記(1)～(17)のいずれかに記載の表示装置。

(19)

前記表示素子は有機電界発光素子である

30

上記(1)～(18)のいずれかに記載の表示装置。

(20)

それぞれが表示素子を含み2次元配置された複数の画素を有する画素部と、

前記複数の画素を表示駆動する駆動回路部と

を備え、

前記駆動回路部を含む第1層と、前記画素部を含む第2層とが積層されている

表示装置を備えた電子機器。

【符号の説明】

【0094】

1, 1A, 1B, 2, 2A, 3, 3A...表示装置、10, 20...有機EL素子、11...

駆動側基板、12...封止基板、13A, 13A1, 13B, 13C...トランジスタ、14

, 22...第1電極、15...画素間絶縁膜、16...有機層、17, 23...第2電極、18...

樹脂層、19...BM / CF層、19R, 21R, 24R...赤色フィルタ、19G, 21G

, 24G...緑色フィルタ、19B, 21B, 24B...青色フィルタ、110A...画素部、

110B...回路部、A...表示領域、B1, B2...積層部、F1...第1層、F2...第2層、

D1～D3...回路要素、e...端面、E1...発光部、T1, T2...透過部。

40

【 図 1 】

【図2】

【 四 4 】

### 【図3A】

【図3B】

【図5】

【図6】

【 义 7 】

【 囮 9 】

【図10】

【 図 8 A 】

【 図 8 B 】

【 図 8 C 】

【 図 1 1 】

【図12】

### 【図13】

【図15】

【図14】

【図16】

【図 17A】

【図17B】

【 図 1 9 】

【図18】

### 【図20】

### 【図21】

【図24B】

【図24C】

## 【図24D】

【 図 2 2 】

【 図 2 3 】

### 【図24A】

〔 四 25 〕

【図26】

【図28】

【図27】

【図29】

【図30】

【図31A】

【図31B】

【図32A】

【図32B】

【図33A】

【図33B】

【図34A】

【図3-4B】

【図3-5】

## フロントページの続き

| (51)Int.Cl.    |             | F I              |         |      |

|----------------|-------------|------------------|---------|------|

| <b>G 0 9 F</b> | <b>9/30</b> | <b>(2006.01)</b> | G 0 9 G | 3/20 |

|                |             |                  | G 0 9 G | 3/20 |

|                |             |                  | G 0 9 F | 9/30 |

|                |             |                  | G 0 9 F | 9/30 |

(72)発明者 工藤 秀治

神奈川県藤沢市辻堂新町3丁目3番1号 ソニーエンジニアリング株式会社内

審査官 後藤 亮治

(56)参考文献 特開2013-225620(JP, A)

国際公開第2012/176422(WO, A1)

特開2010-003910(JP, A)

特開2011-175962(JP, A)

特開2013-117719(JP, A)

特開2006-147712(JP, A)

特表2012-518208(JP, A)

特表2012-529673(JP, A)

## (58)調査した分野(Int.Cl., DB名)

|         |             |   |           |

|---------|-------------|---|-----------|

| G 0 9 F | 9 / 0 0     | - | 9 / 4 6   |

| H 0 1 L | 2 1 / 3 3 6 |   |           |

|         | 2 7 / 3 2   |   |           |

|         | 2 9 / 7 8 6 |   |           |

|         | 5 1 / 5 0   |   |           |

| H 0 5 B | 3 3 / 0 0   | - | 3 3 / 2 8 |