**Brevet d'invention délivré pour la Suisse et le Liechtenstein**

Traité sur les brevets, du 22 décembre 1978, entre la Suisse et le Liechtenstein

**(12) FASCICULE DU BREVET A5**

**634 449**

**(21)** Numéro de la demande: 7118/78

**(73)** Titulaire(s):

Compagnie Internationale pour l'Informatique

CII-Honeywell Bull, Paris (FR)

**(22)** Date de dépôt: 29.06.1978

**(30)** Priorité(s): 07.07.1977 FR 77 20972

**(72)** Inventeur(s):

Georges Giraud, Le Vésinet (FR)

**(24)** Brevet délivré le: 31.01.1983

**(45)** Fascicule du brevet

publié le: 31.01.1983

**(74)** Mandataire:

Dr. A.R. Egli & Co., Patentanwälte, Zürich

**(54)** Dispositif comportant un circuit émetteur et un circuit récepteur entre lesquels sont transmis des signaux électriques.

**(57)** Le dispositif comporte un circuit émetteur (A) et un circuit récepteur (B) entre lesquels sont transmis des signaux électriques par l'intermédiaire d'un premier contact (E/S/H) et d'un contact de retour (0). Le circuit émetteur (A) comprend des moyens (20, 21) produisant un signal de donnée (S) sous la forme d'un courant impulsionnel modulé en durée, à l'aide d'une commutation alternative de deux courants. Ces durées sont respectivement représentatives des valeurs binaires "0" et "1". Le circuit récepteur (B) comprend des moyens (36, 42) produisant un signal de donnée (E) sous la forme d'un signal impulsionnel en fonction de la valeur binaire "0" ou "1" à transmettre.

## REVENDICATIONS

1. Dispositif comportant un circuit émetteur et un circuit récepteur entre lesquels sont transmis des signaux électriques, le circuit émetteur et le circuit récepteur étant reliés temporairement pendant tout le temps de la transmission par des contacts physiques, afin d'assurer un échange de données numériques entre les deux circuits et l'envoi par le circuit émetteur au circuit récepteur d'impulsions d'horloge de synchronisation de période T, caractérisée en ce qu'il comprend, outre un contact de retour (0), un contact unique (E/S/H) assurant les liaisons électriques; en ce que le circuit émetteur (A) comprend des moyens chargés d'élaborer le signal de donnée (S) émis par le circuit émetteur (A) comprend des moyens chargés d'élaborer le signal de donnée (S) émis par le circuit émetteur (A) sous la forme d'un courant impulsif modulé en durée, une première durée ( $\tau_1$ ) correspondant à la transmission d'un bit de valeur logique «1» et une deuxième durée ( $\tau_2$ ) correspondant à la transmission d'un bit de valeur logique «0», et en ce que le circuit récepteur (B) comprend des moyens chargés d'élaborer le signal de donnée (E) émis par le circuit récepteur (B) sous la forme d'un courant impulsif, une première amplitude correspondant à la transmission d'un bit de valeur logique «1» et une deuxième amplitude correspondant à une transmission d'un bit de valeur logique «0».

2. Dispositif selon la revendication 1, caractérisé en ce que les moyens chargés d'élaborer le signal de donnée émis par le circuit émetteur (A) comprennent un premier élément (20) chargé de fournir deux courants d'intensités différentes ( $I_0, I_1$ ) et un deuxième élément (21) chargé de commander une Commutation alternative de ces deux courants de manière à obtenir le courant impulsif modulé en durée.

3. Dispositif selon la revendication 2, caractérisé en ce que le deuxième élément (21) est agencé de manière à obtenir un courant impulsif ayant une période égale à la période (T) des impulsions de synchronisation, une impulsion étant transmise pendant chaque période.

4. Dispositif selon la revendication 2, caractérisé en ce que le deuxième élément (21) est agencé de manière à obtenir l'émission d'une impulsion de durée égale à  $T/2$  pour commander l'émission du signal de donnée (E) émis par le circuit récepteur (B).

5. Dispositif selon la revendication 4, caractérisé en ce que le circuit émetteur (A) comporte un circuit de détection du signal (E) émis par le circuit récepteur (B), constitué d'une bascule bistable (32), et en ce que le circuit récepteur (B) comporte un circuit de détection de potentiel constitué d'une résistance (33) et d'une diode (34) en parallèle, un circuit de détection du signal (S) émis par le circuit émetteur (A) et comprenant une bascule bistable (40) reliée au circuit de détection de potentiel et une première bascule monostable (42) reliée également au circuit de détection de potentiel par l'intermédiaire d'une porte logique ET (43), d'une seconde bascule monostable (39) reliée à une première entrée de la porte ET (43), d'une troisième (38) et d'une quatrième (41) bascule monostable, toutes deux en parallèle avec la seconde bascule monostable (39) et reliées à une deuxième entrée de la porte ET (43), l'une de ces bascules monostables commandant la bascule bistable (40), la seconde bascule monostable (39) étant sensible au front descendant alors que la troisième bascule monostable (38) reliée au circuit de détection de potentiel est sensible au front montant, et un circuit d'émission du signal (E) destiné au circuit émetteur (A) constitué par un élément générateur de courant (36) validé par la première bascule monostable (42).

6. Dispositif selon la revendication 5, caractérisé en ce que le circuit émetteur comporte une première mémoire (A), une seconde mémoire d'entrée-sortie (E/S) et un générateur d'adresse (GAA) relié aux deux mémoires, et en ce que le circuit récepteur comporte une première mémoire (B) à laquelle est

rélié un générateur d'adresse (GAB) évoluant en synchronisme avec le générateur d'adresse (GAA) du circuit émetteur (A).

7. Dispositif selon la revendication 6, caractérisé en ce que la mémoire d'entrée-sortie (E/S) est une mémoire morte et les 5 premières mémoires des circuits émetteur (A) et récepteur (B) sont des mémoires vives.

La présente invention concerne la transmission de signaux 10 électriques entre deux circuits reliés par des contacts et plus particulièrement la transmission de différents signaux de l'un des circuits vers l'autre ou inversement, alternativement.

De manière encore plus particulière, l'invention concerne la transmission de l'un des circuits vers l'autre ou inversement de 15 signaux sous forme de courants électriques correspondant à des états logiques engendrés dans l'un des circuits et à transmettre l'autre.

Un système de ce type est décrit par exemple dans le brevet français No. 2 319 949 au nom de la titulaire et intitulée «Dispositif de contrôle d'un contact inséré entre un circuit émetteur 20 et un circuit récepteur pour la transmission de signaux électriques».

Dans ce type de dispositif, il faut généralement prévoir, outre un contact de retour, autant de circuits de liaison, c'est-à- 25 dire de contacts, qu'il y a de types de signaux électriques à transmettre dans un sens ou dans l'autre.

C'est ainsi que dans le cas de l'application du dispositif décrit dans le brevet précité au cas où le circuit émetteur est un système de traitement de données et où le circuit récepteur est 30 une carte de crédit, le circuit émetteur doit envoyer deux types de signaux au récepteur: des signaux de données et des signaux d'horloge de synchronisme et le circuit récepteur doit envoyer à l'émetteur des signaux de lecture de données inscrites dans la carte de crédit.

Il faut donc prévoir quatre liaisons par quatre contacts distincts.

Le but de l'invention est de réduire dans des dispositifs de ce type les risques de mauvais fonctionnement ou d'anomalies imputables aux contacts en réduisant au minimum le nombre de 40 ces derniers.

A cet effet, l'invention a pour objet un dispositif comportant un circuit émetteur et un circuit récepteur entre lesquels sont transmis des signaux électriques, le circuit émetteur et le circuit récepteur étant reliés temporairement pendant tout le 45 temps de la transmission par des contacts physiques, afin d'assurer l'échange de données numériques entre les deux circuits et l'envoi par le circuit émetteur au circuit récepteur d'impulsions d'horloge de synchronisation de période T. Ce dispositif est caractérisé en ce qu'il comprend, outre un contact de retour, un 50 contact unique assurant les liaisons électriques; en ce que le circuit émetteur comprend des moyens chargés d'élaborer le signal de donnée émis par le circuit émetteur sous la forme d'un courant impulsif modulé en durée, une première durée correspondant à la transmission d'un bit de valeur logique «1» et une deuxième durée correspondant à la transmission d'un bit de valeur logique «0», et en ce que le circuit récepteur comprend des moyens chargés d'élaborer le signal de donnée émis par le circuit récepteur sous la forme d'un courant impulsif, une première amplitude correspondant à la transmission d'un bit de 60 valeur logique «1» et une deuxième amplitude correspondant à la transmission d'un bit de valeur logique «0».

De préférence, le circuit émetteur comprend un premier élément chargé de fournir deux courants d'intensités différentes et un deuxième élément chargé de commander une commutation alternative de ces deux courants de manière à obtenir le courant impulsif modulé en durée.

Le deuxième élément permet d'obtenir un courant impulsif de période égale à la période des impulsions de synchro-

nisation, une impulsion étant transmise pendant chaque période.

D'autres particularités et avantages ressortiront de la description qui va suivre d'un mode de réalisation du dispositif de l'invention, description donnée à titre d'exemple uniquement et en regard des dessins annexés sur lesquels:

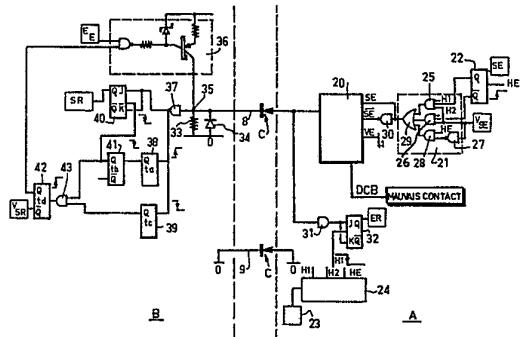

Fig. 1 représente schématiquement des circuits émetteur et récepteur destinés à l'échange de données digitales;

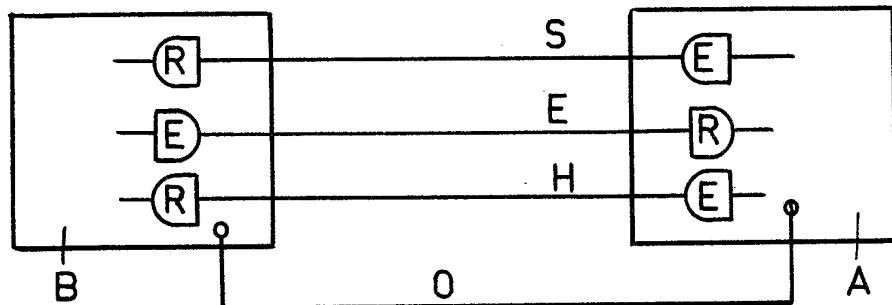

Fig. 2 représente schématiquement des circuits émetteur et récepteur destinés également à l'échange de données digitales et conformes à l'invention;

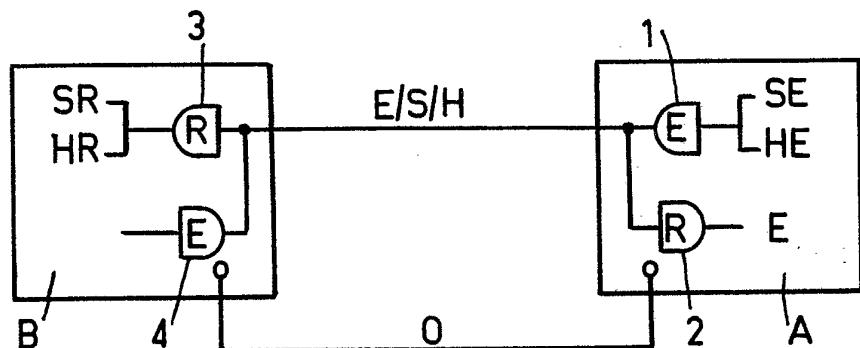

Fig. 3 représente schématiquement le principe de la liaison électrique entre l'émetteur et le récepteur du dispositif de la fig. 2;

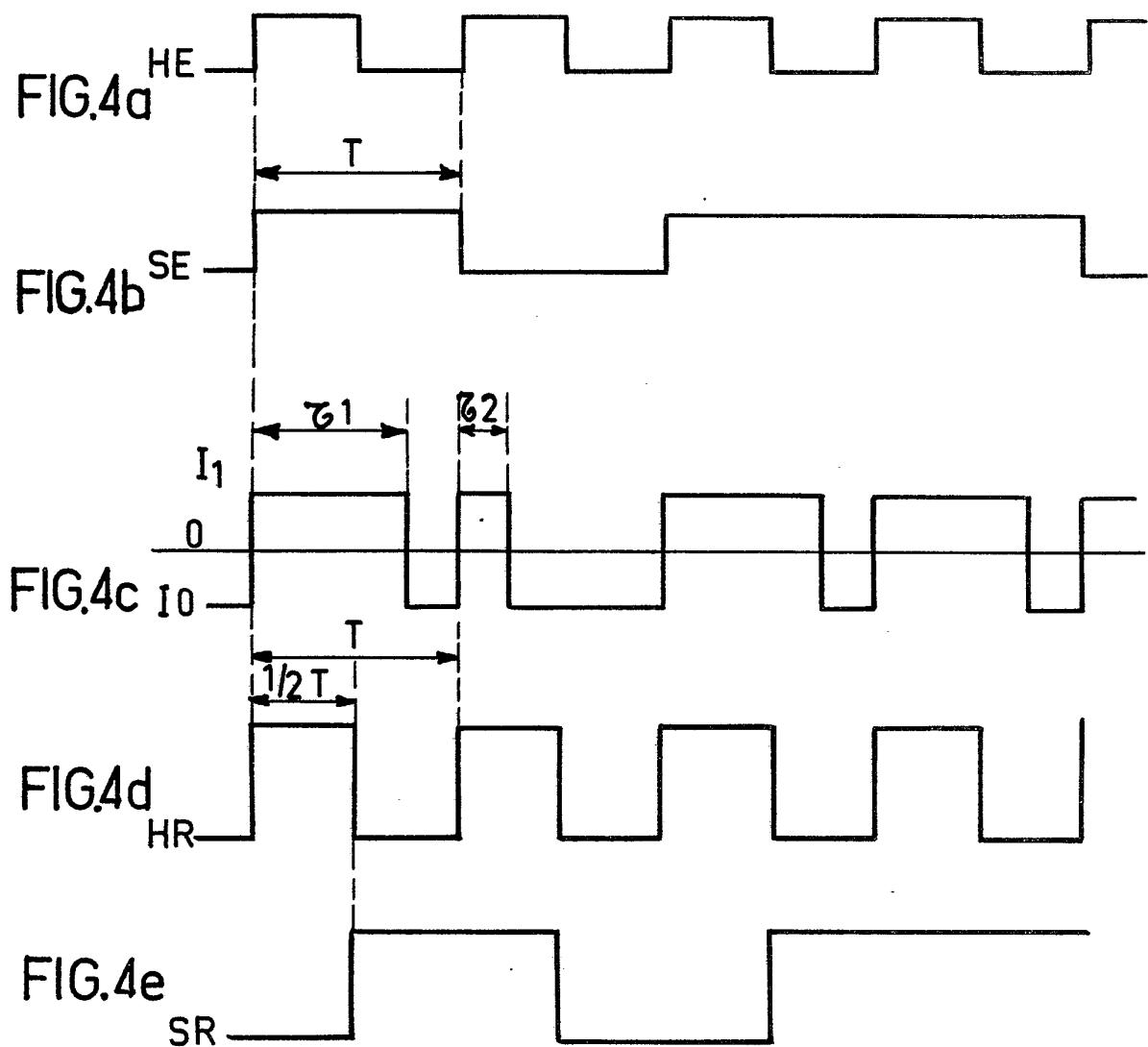

Fig. 4a, 4b, 4c et 4e représentent respectivement le signal d'horloge (émission), le signal de donnée (émission) et le signal modulé de transport de ces signaux, le signal d'horloge (à la réception) et le signal de donnée (à la réception);

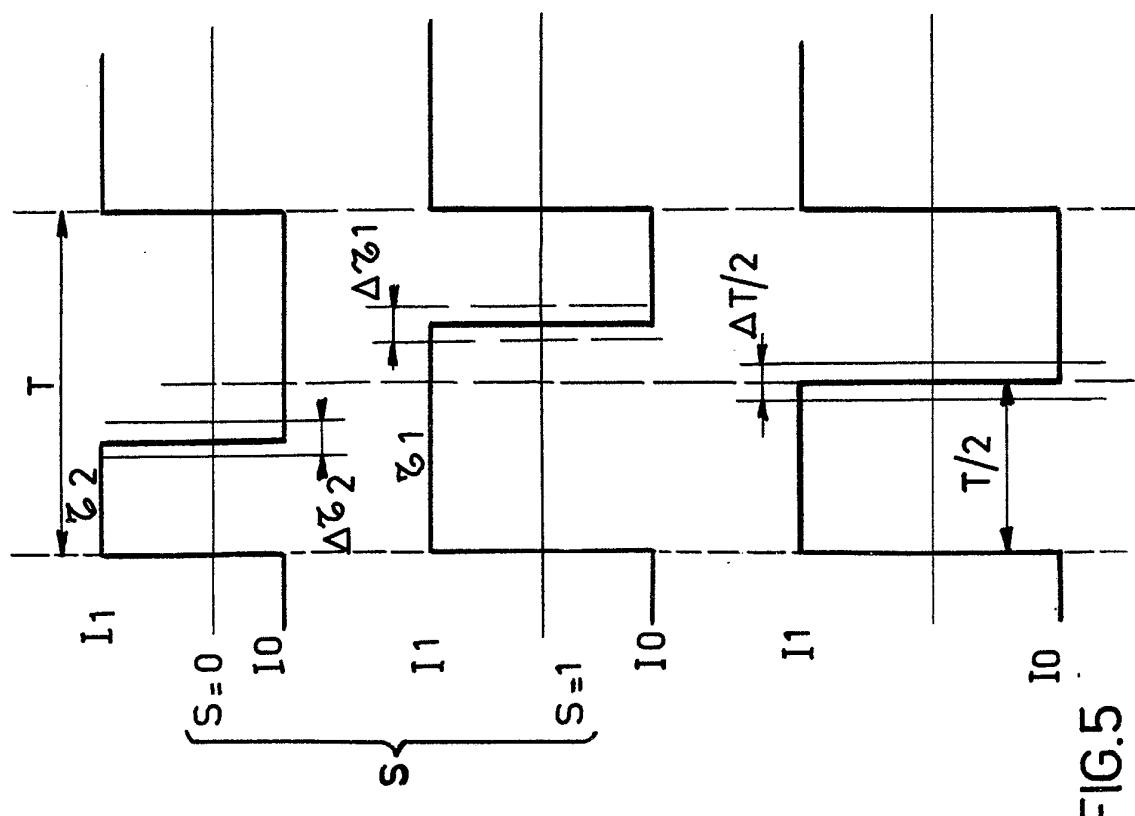

Fig. 5 représente les formes d'ondes des courants sur les lignes de liaison entre l'émetteur et le récepteur.

Fig. 6 représente l'émission du signal de données depuis le récepteur vers l'émetteur;

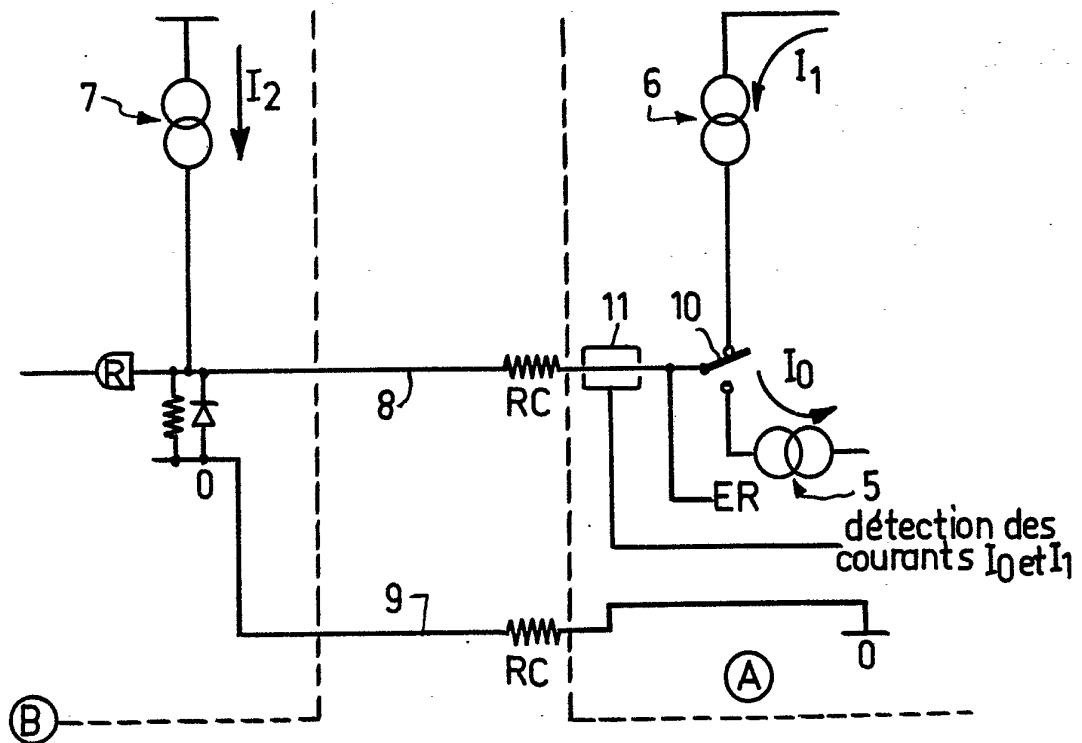

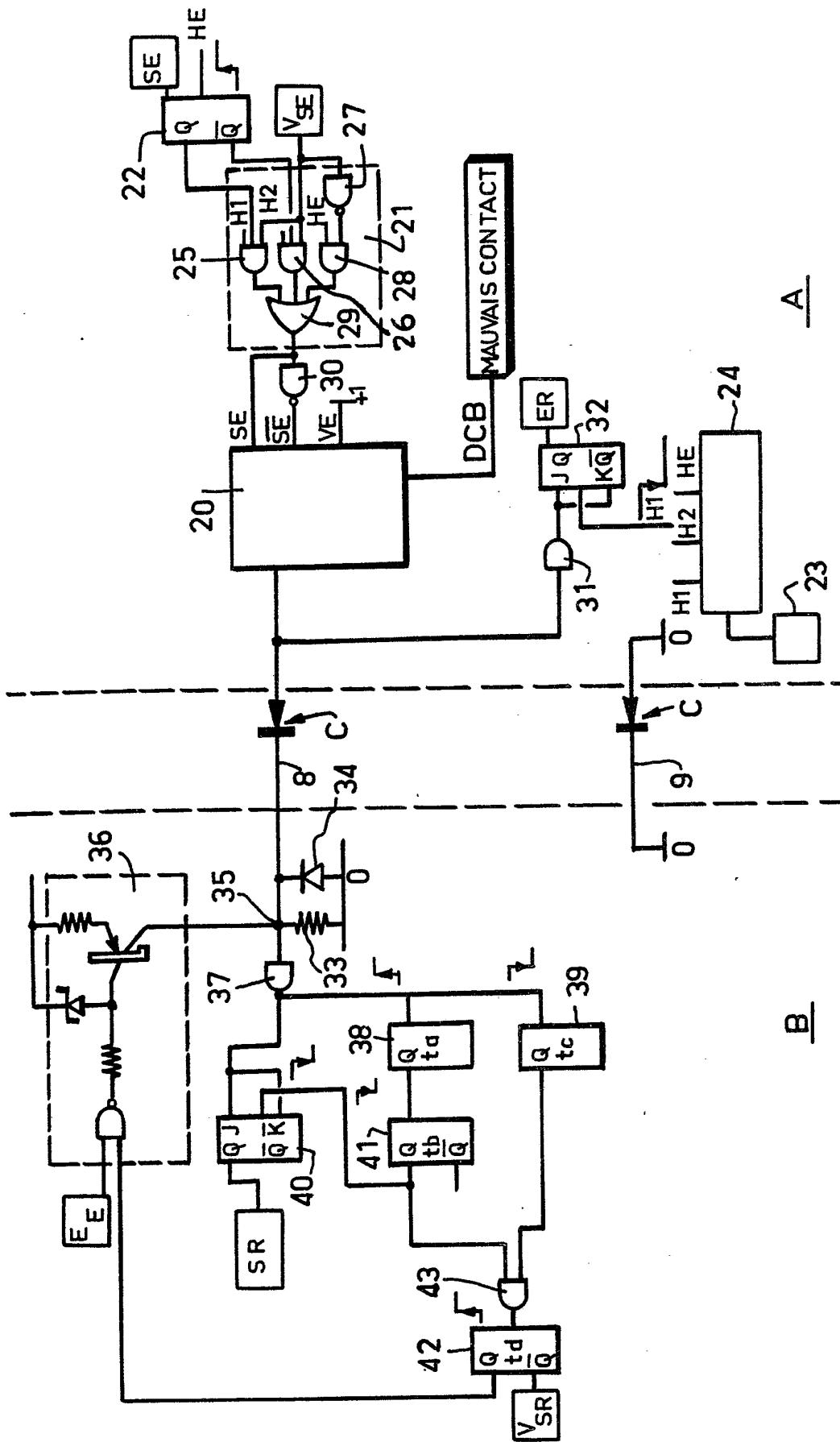

Fig. 7 représente le schéma logique d'un mode de réalisation du dispositif de l'invention;

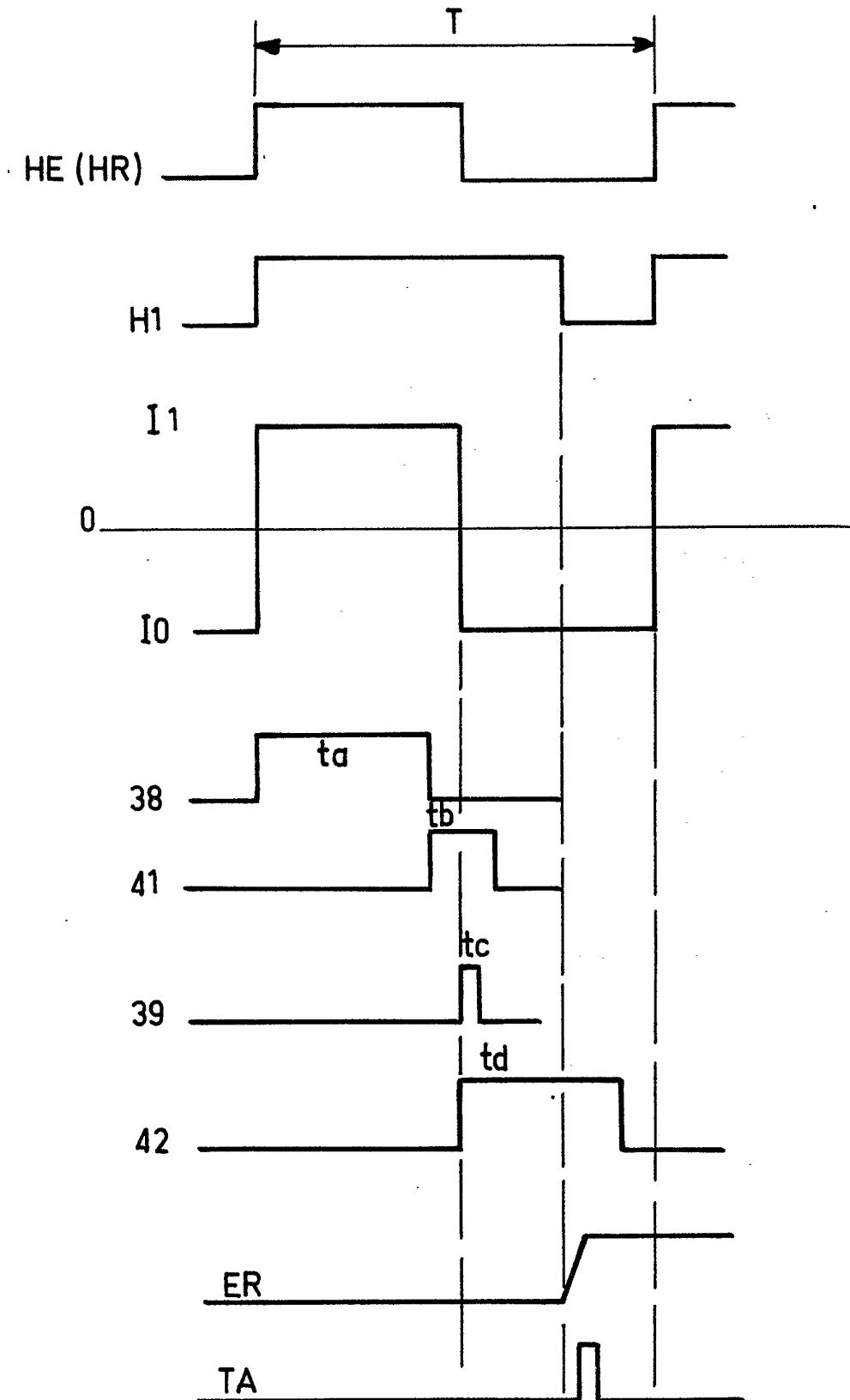

Fig. 8 représente les divers signaux d'horloge élaborés dans le dispositif de la fig. 7;

Fig. 9 représente divers signaux élaborés au niveau du circuit récepteur.

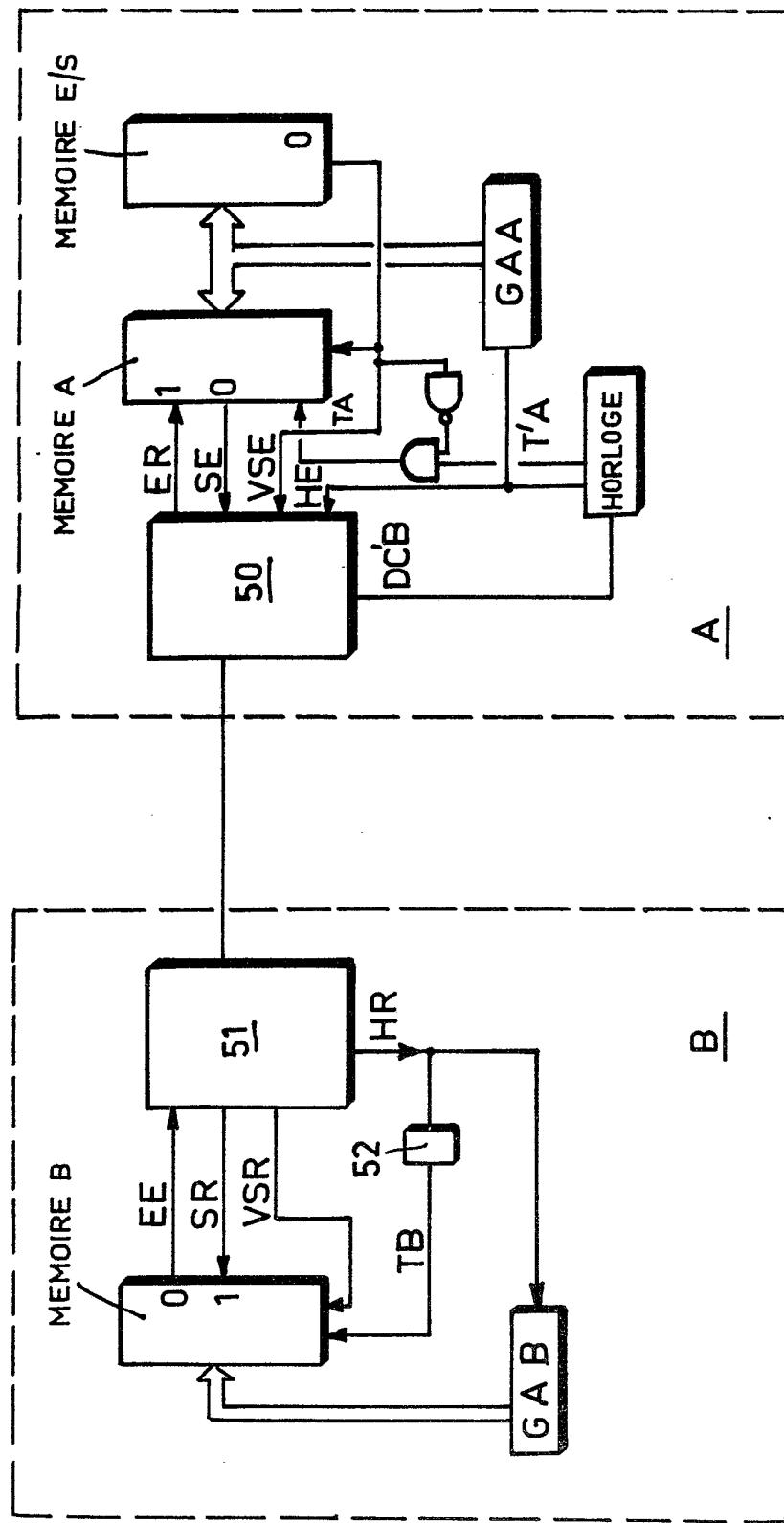

Fig. 10 représente schématiquement la lecture et/ou l'écriture d'une mémoire du circuit récepteur à partir d'une mémoire du circuit émetteur, et

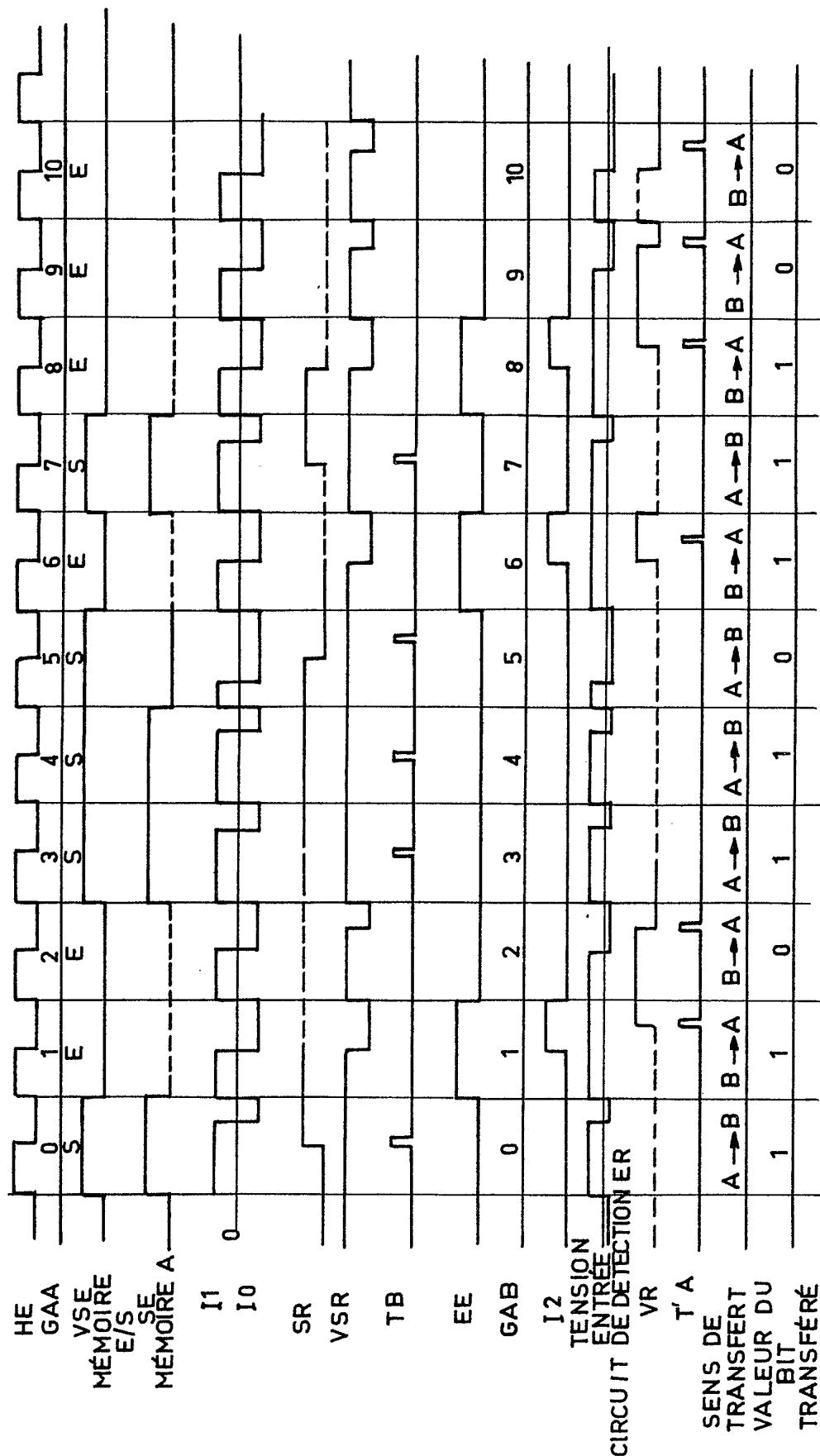

Fig. 11 représente le diagramme des divers signaux utilisés dans le dispositif de la fig. 7 avec la valeur du bit transféré et le sens de transfert.

La fig. 1 représente schématiquement un circuit émetteur A et un circuit récepteur B, entre lesquels s'effectuent des transmissions de signaux par les liaisons à contact temporaire.

Plus particulièrement, dans le cas de l'échange de données digitales par transmission d'impulsions d'un circuit à l'autre, le circuit émetteur est constitué par un élément fixe et le circuit récepteur est constitué par un élément portatif pourvu de contacts électriques coopérant durant tout le temps de la transmission avec des contacts électriques appropriés dont est équipé l'élément fixe.

Dans ce cas un signal porteur de données S doit être envoyé de l'émetteur A vers le récepteur B, un signal porteur de données E doit être envoyé du récepteur B vers le récepteur A et un signal d'horloge H de synchronisation doit être envoyé de l'émetteur A vers le récepteur B pour traiter en synchronisme les données échangées traitées dans chacun des deux circuits.

A l'intérieur des rectangles symbolisant les circuits émetteur A et récepteur B sur la fig. 1, les lettres E et R signifient Emission et Réception.

Il est donc nécessaire de prévoir trois contacts distincts plus un contact 0 dit de retour.

La présente invention a pour but de réduire le nombre de ces contacts de 4 à 2, afin de réduire les problèmes et inconvénients que posent de tels contacts.

On a schématisé sur la fig. 2 le dispositif selon l'invention, lequel ne comporte, outre la liaison 0 de retour, qu'une seule liaison par contact assurant la transmission des signaux E, S et H entre l'émetteur A et le récepteur B.

Au niveau de l'émetteur A, le circuit 1 assure l'émission SE du signal S et l'émission HE du signal d'horloge H cependant que le circuit 2 assure la réception du signal E provenant de B.

Au niveau du récepteur B, le circuit 3 assure la réception SR du signal S et la réception HR du signal d'horloge H, cependant que le circuit 4 assure l'émission du signal E.

La fig. 3 illustre le schéma de principe de la liaison entre les circuits A et B.

L'émetteur A comporte un premier générateur de courant 5 engendrant un courant  $I_0$  et un second générateur de courant 6 engendrant un courant  $I_1$ .

Le récepteur B comporte un générateur de courant 7 engendrant un courant  $I_2$ .

La liaison entre les circuits A et B est symbolisée par deux conducteurs 8 et 9 dans lesquels sont insérées des résistances 10 RC correspondant aux contacts.

L'un de ses conducteurs (8) est relié à un commutateur 10 à deux positions, situé dans l'émetteur A et assurant la connexion soit avec le générateur 6, soit avec le générateur 5. Sur ce conducteur 8, est prévu dans l'émetteur A un circuit 11 de détection 15 des courants  $I_0$  et  $I_1$ .

Le générateur 7 est chargé de l'émission du signal E à destination de l'émetteur A, cependant que le circuit R est chargé de la réception des signaux S et H, en provenance de l'émetteur A.

Les figures 4a et 4b représentent la forme d'onde des signaux HE et SE respectivement au niveau de l'émission dans l'émetteur A.

Cette émission est réalisée par modulation en durée des courants  $I_1$  et  $I_0$ , de façon à transporter les informations S et H.

A cet effet, le signal qui est envoyé au récepteur a la forme 25 représentée sur la fig. 4c.

Dans le circuit récepteur B, les courants  $I_1$  et  $I_0$  sont démodulés de manière à obtenir le signal HR (signal d'horloge à la réception) représenté sur la fig. 4d et le signal SR (signal S à la réception) représenté sur la fig. 4e qui est décalé d'une demi-période ( $1/2 T$ ) par rapport au signal SE de la fig. 4b, T étant la période du signal d'horloge HE.

La durée  $\tau 1$  est égale à  $3/4 T$  et représente l'état binaire 1 du signal S et la durée  $\tau 2$  est égale à  $1/4 T$  et représente l'état binaire 0 de ce même signal.

35 Lorsque le circuit émetteur A émet le signal S, l'impulsion de courant  $I_1$  a la durée  $\tau 1$  ou  $\tau 2$ .

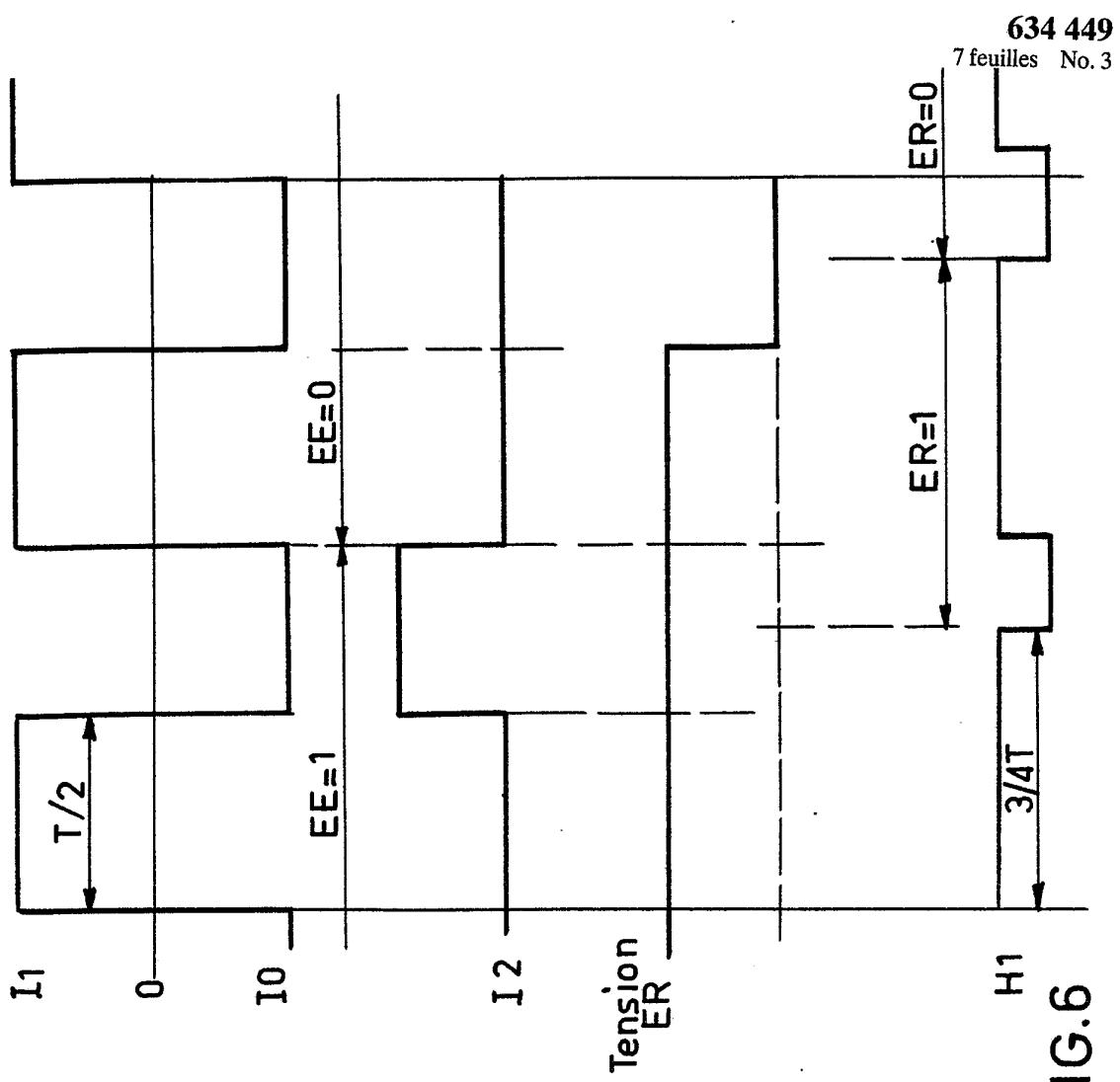

Sur la fig. 5, on a représenté les caractéristiques des courants sur les lignes de liaison entre l'émetteur et le récepteur.

40 Lorsque l'émetteur A émet le signal S, celui-ci transmettra l'état binaire 1 ou 0 selon que la durée de l'impulsion de courant  $I_1$  sera  $\tau 1$  ou  $\tau 2$ , respectivement.

Lorsque l'émetteur A passe en position de réception du signal E provenant du récepteur B, il envoie un signal constitué par une impulsion de courant  $I_1$  de durée égale à  $T/2$  et représenté sur la fig. 5 au dessous des deux formes d'onde du signal S. Ce signal informe le récepteur B qu'il doit émettre le signal E.

La fig. 6 illustre l'émission de ce signal E par le récepteur B.

50 La forme d'onde de la partie supérieure de la fig. 6 est celle du signal  $I_1$  de durée  $T/2$  envoyé par l'émetteur A.

Si le signal E doit représenter l'état binaire 1, l'impulsion de courant  $I_2$  est envoyée vers l'émetteur A durant un temps égal à  $T/2$  coïncidant avec l'envoi du courant  $I_0$ . Si l'on rend  $I_2$  égal à  $2I_0$ , cela se traduit sur le circuit ER (fig. 3) de l'émetteur par une 55 tension constante (fig. 6) pendant une durée égale à  $3/2T$ .

Si le signal E doit représenter l'état binaire 0, le courant  $I_2$  n'est pas envoyé sur la ligne de transmission, en sorte que ladite tension en ER revient au niveau correspondant au courant  $I_0$ . Par cette variation de tension au niveau de l'émetteur A, on 60 détecte donc les deux états 0 ou 1 véhiculés par le signal E.

La fig. 7 représente le schéma d'un mode de réalisation d'un dispositif conforme à l'invention.

Ce dispositif comporte un circuit émetteur A et un circuit récepteur B reliés par deux liaisons à contact, schématisées par 65 les lignes 8 et 9, dans lesquels les contacts sont symbolisés en C.

Dans le circuit émetteur A, on a représenté en 20 un élément groupant les deux générateurs de courant 5 et 6 de la fig. 3. Un élément 21 est chargé de commander la modulation des

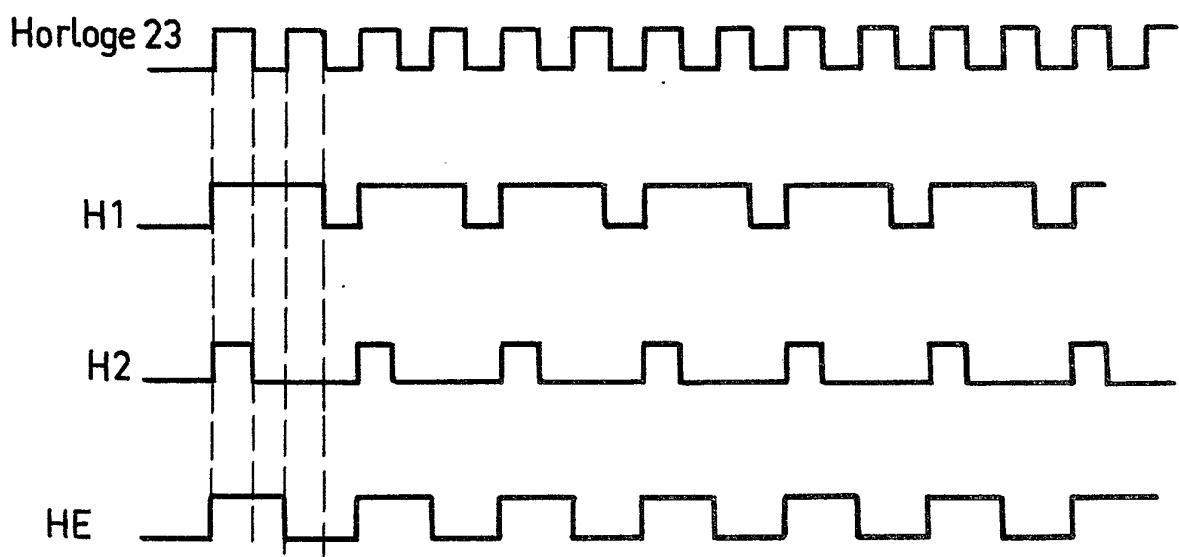

courants  $I_0$  et  $I_1$  générés par l'élément 20. L'élément 21 est commandé par une bascule bistable 22, commandée par un signal d'horloge HE généré à partir d'une horloge 23 et par l'intermédiaire d'un élément 24 chargé de définir 3 signaux d'horloge différents HE, H1 et H2, qui seront déterminés plus loin en référence à la fig. 8.

La sortie Q de la bascule 22 est reliée à une porte ET 25 de l'élément 21, tandis que la sortie  $\bar{Q}$  est reliée à une entrée d'une seconde porte ET 26. La porte ET 25 reçoit également un signal d'horloge H1 et un signal de validation  $V_{SE}$ . La porte ET 26 reçoit également le signal d'horloge H2, ainsi que le signal de validation  $V_{SE}$ . Ce dernier signal est également appliqué à un inverseur 27 relié à une porte ET 28 recevant également le signal d'horloge HE. Les trois portes ET 25, 26 et 28 sont reliées à une porte OU 29 dont la sortie est reliée, d'une part directement (signal SE) à l'élément 20 et, d'autre part, par l'intermédiaire d'un inverseur 30 (signal  $\bar{SE}$ ).

L'élément 20 est susceptible de délivrer un signal logique DCB informant sur la bonne réception par le circuit B des signaux émis par le circuit A. La sortie de l'élément 20 est reliée à la ligne 8.

Cette ligne 8 est également reliée à un élément 31 de détection de l'état 0. Sur la ligne 8, cet état est pris en compte par une bascule bistable 32 délivrant sur sa sortie Q le signal ER (signal émis par le circuit B et reçu par le circuit A). La bascule 32 reçoit les signaux d'horloge H1.

Au niveau du circuit B, la ligne 8 est reliée à une résistance 33 et une diode 34 définissant le potentiel du point 35.

A la borne 35 est connecté un élément 36 chargé de générer le courant  $I_2$ .

La borne 35 est également reliée à un élément de mise en forme 37 relié à un monostable 38 de durée  $t_a$  à un monostable 39 de durée  $t_E$  et à une bascule bistable 40 chargée de délivrer le signal SR.

Le monostable 38 est relié à un monostable 41 de durée  $t_b$ , lui-même relié à la bascule 40 et à un monostable 42 de durée  $t_d$  à travers une porte ET 43. Le monostable 39 est également relié à la porte 43. La sortie du monostable 42 valide le signal à émettre EE par l'intermédiaire de l'élément 36.

La fig. 8 représente le diagramme des différents signaux d'horloge utilisés dans le circuit émetteur A.

Le signal d'horloge H1 a une durée correspondant aux 3/2 de la période du signal de l'horloge 23. Le signal d'horloge H2 a une durée égale à une 1/2 période du signal d'horloge 23 et le signal HR a une durée correspondant à une période du signal d'horloge 23.

Le fonctionnement du dispositif représenté sur la fig. 7 est le suivant:

On va supposer que l'émetteur A envoie un signal S à destination de l'émetteur B. Cette émission est validée par un signal  $V_{SE}$  appliquée aux portes ET 25, 26 et 28. Lorsqu'apparaît un front montant du signal d'horloge HE, la bascule 22 reçoit le bit à émettre. L'élément 21 est chargé d'effectuer la modulation en durée des impulsions de courant  $I_0$  et  $I_1$ , comme expliqué plus haut (fig. 5).

Au niveau du récepteur B, le courant  $I_1$  issu du circuit A développe aux bornes de la résistance 33 une différence de potentiel qui provoque à la sortie de l'élément 37 le passage à l'état binaire 1. Ce front montant déclenche le monostable 38 de durée  $t_a$  (fig. 9). Au bout du temps  $t_a$ , le monostable 41 est déclenché durant le temps  $t_b$ .

Lorsque le courant issu du circuit A passe de  $I_1$  à  $I_0$ , le potentiel à l'entrée de 37 devient faible (légèrement négatif, tension directe à la diode 34). A la sortie de l'élément 37, le signal passe à 0 et engendre un front descendant qui déclenche le monostable 39 de durée  $t_c$ .

La bascule 40 délivre le signal SR qui est identique au signal SE, mais décalé dans le temps (fig. 4b et 4e). L'état de cette

bascule sera pris en compte par le circuit d'utilisation du récepteur B (non représenté sur la fig. 7) selon l'état du signal  $V_{SR}$  délivré par le monostable 42 et qui informe sur le sens du transfert.

Si l'impulsion  $t_c$  arrive au moment de l'impulsion tb, le monostable 42 est déclenché durant le temps  $t_d$  et sa sortie Q valide le signal à émettre EE par le circuit B à destination du circuit A.

La fig. 9 illustre le cas de l'émission du signal EE. En effet, le signal de durée  $t_c$  apparaissant au front descendant du signal passant de  $I_1$  à  $I_0$  se produit pendant la durée  $t_b$ . Cela correspond à un signal  $I_1 - I_0$  de période égale à  $T$  qui est la période du signal HE (ou HR). On a vu (fig. 5) que cette modulation des courants  $I_1, I_0$  correspond au signal envoyé par l'émetteur A au récepteur B pour l'informer d'avoir à envoyer le signal E à destination du circuit A.

A la réception du signal délivré par la sortie Q de la bascule 42, le circuit 36 génère un courant  $I_2$  tel que  $I_2 = 2I_0$  si le signal E à émettre (EE) est 1, et  $I_2 = 0$ , si EE = 0. Dans le premier cas, apparaît aux bornes de la résistance 33 une différence de potentiel qui est détectée par l'élément 31 qui présente en sortie d'état 1. Dans le deuxième cas, l'élément 31 délivre l'état 0 en sortie. Cet état est pris en compte dans la bascule 32 au moment du front descendant du signal d'horloge H1 (Fig. 6).

La bascule 32 délivre le signal ER qui est identique au signal EE, mais décalé dans le temps (fig. 6).

Si l'impulsion de durée  $t_c$  délivrée par le monostable 39 tombe en dehors de l'impulsion tb du monostable 41, soit qu'elle apparaisse avant, soit qu'elle apparaisse après, c'est que le signal émis par le circuit A est un signal S (avec S = 0 ou S = 1) du type représenté sur la fig. 5. La bascule 42 délivre sur la sortie  $\bar{Q}$  le signal  $V_{SR}$  de validation de la réception du signal S.

Le signal DCB (fig. 7) est un signal logique informant le dispositif sur la bonne réception par le circuit B des signaux émis par le circuit A.

La fig. 10 représente schématiquement un mode de réalisation de l'invention, appliquée à la transmission de données entre une mémoire A du circuit émetteur A et une mémoire B du circuit récepteur B.

Sur la fig. 10, l'élément 50 du circuit A regroupe les éléments du circuit A de la fig. 7 excepté l'horloge et l'élément 51 du circuit B regroupe les éléments du circuit A de cette même figure.

Le circuit A comporte en outre une mémoire E/S (Entrée/Sortie) connectée à la mémoire A par l'intermédiaire d'un générateur d'adresse GAA.

Le circuit B comporte en outre un générateur d'adresse GAB relié à la mémoire B et un élément 52 générant un signal TB de démarrage de l'écriture dans la mémoire B.

La fig. 11 est un tableau récapitulatif des divers signaux utilisés dans le dispositif de la fig. 10 et du sens du transfert des données sous forme binaire 0 ou 1 de A vers B, ou inversement.

Les mémoires A et B sont des mémoires vives et la mémoire E/S peut être une mémoire morte.

Dans le circuit B, la mémoire B peut être lue ou écrite à partir de la mémoire A. Les ordres de lecture ou d'écriture sont contenus dans la mémoire E/S.

Les générateurs d'adresse GAA et GAB évoluent en synchronisme. Si le générateur GAA pointe en mémoire E/S une cellule à 1, il y a transfert du bit de la mémoire A vers la mémoire B. Si la cellule est à 0, il y a transfert de la mémoire B vers la mémoire A.

Sur la fig. 10, le signal HE est un signal délivré par l'horloge. Le signal  $V_{SE}$  est un signal de validation de l'émission du signal S provenant de la mémoire E/S. SE est le signal d'émission de S provenant de la mémoire.

Pour ce qui concerne les modulations des courants  $I_0$ ,  $I_1$  et  $I_2$  et le processus de transmission des signaux de A vers B et de B vers A, il suffit de se reporter au dispositif de la fig. 7 dont le fonctionnement est tout à fait identique à celui de la fig. 10.

Les signaux ST et EE sont les mêmes que ceux de la fig. 7. Le signal  $V_{SR}$  est un signal de validation de la réception du signal S.

FIG.1

FIG.2

FIG.3

FIG.8

FIG.6

FIG.5

FIG.9

FIG.10

FIG.11