(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7146920号

(P7146920)

(45)発行日 令和4年10月4日(2022.10.4)

(24)登録日 令和4年9月26日(2022.9.26)

(51)国際特許分類

|                |                        |            |                |              |                |

|----------------|------------------------|------------|----------------|--------------|----------------|

| <b>G 0 6 F</b> | <b>13/16 (2006.01)</b> | <b>F I</b> | <b>G 0 6 F</b> | <b>13/16</b> | <b>5 2 0 A</b> |

| <b>G 0 6 F</b> | <b>11/10 (2006.01)</b> |            | <b>G 0 6 F</b> | <b>11/10</b> | <b>6 4 4</b>   |

請求項の数 14 (全19頁)

(21)出願番号 特願2020-533853(P2020-533853)

(86)(22)出願日 平成30年12月18日(2018.12.18)

(65)公表番号 特表2021-509499(P2021-509499)

A)

(43)公表日 令和3年3月25日(2021.3.25)

(86)国際出願番号 PCT/IB2018/060237

(87)国際公開番号 WO2019/135134

(87)国際公開日 令和1年7月11日(2019.7.11)

審査請求日 令和3年5月25日(2021.5.25)

(31)優先権主張番号 15/860,871

(32)優先日 平成30年1月3日(2018.1.3)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 390009531

インターナショナル・ビジネス・マシンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク州 アーモンク ニュー オーチャード ロード

New Orchard Road, Armonk, New York 10504, United States of America

(74)代理人 100112690

弁理士 太佐 種一

最終頁に続く

(54)【発明の名称】 メモリ・コントローラを動作させる方法、デュアル・チャネル・モードからシングル・チャネル・モードに切り替える方法、およびメモリ・コントローラ

## (57)【特許請求の範囲】

## 【請求項1】

メモリ・コントローラを動作させる方法であって、前記メモリ・コントローラの第1のメモリ・デバイスおよび第2のメモリ・デバイスをデュアル・チャネル・モードで駆動することであって、第1の誤り訂正符号(ECC)メモリ・デバイスおよび第2のECCメモリ・デバイスは、前記第1のメモリ・デバイスおよび前記第2のメモリ・デバイスを保護する、前記駆動すること、

前記第2のECCメモリ・デバイスがスペア・メモリ・デバイスとなるように、前記第1のメモリ・デバイスおよび前記第2のメモリ・デバイスをシングル・チャネル・モードで駆動することであって、前記第1のECCメモリ・デバイスは前記第1のメモリ・デバイスおよび前記第2のメモリ・デバイスを保護する、前記駆動することと

を含み、前記メモリ・コントローラは、前記デュアル・チャネル・モードと前記シングル・チャネル・モードを切り替えるように構成される、方法。

## 【請求項2】

前記第1のメモリ・デバイスおよび前記第2のメモリ・デバイスは、ダイナミック・ランダム・アクセス・メモリ(DRAM)である、請求項1に記載の方法。

## 【請求項3】

前記第1のメモリ・デバイスおよび前記第2のメモリ・デバイスは、DRAMデュアル・イン・ライン・メモリ・モジュール(DIMM)である、請求項1に記載の方法。

## 【請求項4】

前記第1のメモリ・デバイスは、データ記憶のために構成された第1のデータ・メモリ・デバイスと、誤り訂正のために構成された前記第1のECCメモリ・デバイスとを備え、前記第2のメモリ・デバイスは、データ記憶のために構成された第2のデータ・メモリ・デバイスと、誤り訂正のために構成された前記第2のECCメモリ・デバイスとを備える、請求項1に記載の方法。

【請求項5】

前記メモリ・コントローラは、前記第2のECCメモリ・デバイスが前記スペア・メモリ・デバイスとなるように、前記シングル・チャネル・モード中に前記第2のECCメモリ・デバイスを使用不可能にするように構成される、請求項4に記載の方法。

【請求項6】

前記メモリ・コントローラは、前記第1のメモリ・デバイスおよび前記第2のメモリ・デバイスから故障したメモリ・デバイスを検出するように構成され、

前記メモリ・コントローラは、前記スペア・メモリ・デバイスが前記故障したメモリ・デバイスの代わりに動作するように、前記故障したメモリ・デバイスを前記スペア・メモリ・デバイスと置き換えるように構成される、請求項5に記載の方法。

【請求項7】

前記故障したメモリ・デバイスの検出に応答して、前記メモリ・コントローラは、前記スペア・メモリ・デバイスに、前記第1のデータ・メモリ・デバイス、前記第1のECCメモリ・デバイスおよび前記第2のメモリ・デバイスのうちの任意の1つの代わりに動作させるように構成される、請求項6に記載の方法。

【請求項8】

前記第1のデータ・メモリ・デバイスは32ビット幅データ・インターフェースを有し、前記第2のデータ・メモリ・デバイスは別の32ビット幅データ・インターフェースを有する、請求項4に記載の方法。

【請求項9】

前記シングル・チャネル・モード中、前記メモリ・コントローラは、前記第1のECCメモリ・デバイスに、前記第1のデータ・メモリ・デバイスおよび前記第2のデータ・メモリ・デバイスの双方について64ビット幅データ・インターフェースを保護させるように構成され、前記64ビット幅データ・インターフェースは、前記32ビット幅データ・インターフェースおよび前記別の32ビット幅データ・インターフェースを含む、請求項8に記載の方法。

【請求項10】

第1のECCメモリ・デバイスは8ビットである、請求項9に記載の方法。

【請求項11】

デュアル・チャネル・モードからシングル・チャネル・モードに切り替える方法であつて、

メモリ・コントローラによって、メモリ・モジュールの動作の前記デュアル・チャネル・モードから前記シングル・チャネル・モードへの切替えが必要であると判断することであつて、前記メモリ・モジュールは、第1のチャネルおよび第2のチャネルにおいてメモリ・デバイスを含む、前記判断することと、

前記メモリ・コントローラによって、前記デュアル・チャネル・モードから前記シングル・チャネル・モードに切り替えることとを含み、前記切り替えることは、

前記メモリ・モジュールの前記メモリ・デバイスから全てのデータを読み出すことと、前記メモリ・モジュールの前記メモリ・デバイスからストレージにデータをロードすることと、

前記メモリ・デバイスの2つの誤り訂正符号(ECC)メモリ・デバイスの代わりに单一のECCメモリ・デバイスを用いて前記第1のチャネルおよび前記第2のチャネルを保護することによって、前記メモリ・デバイスのスペアECCメモリ・デバイスが利用可能になるようにすることと、

10

20

30

40

50

故障メモリ・デバイスとの間で行われることを対象とした書込みおよび読出しが、代わりに前記スペア E C C メモリ・デバイスとの間で行われる書込みおよび読出しとなるよう、前記故障メモリ・デバイスの入力および出力を前記スペア E C C メモリ・デバイスにマッピングすることと、

前記故障メモリ・デバイスを対象とするデータの一部分が代わりに前記スペア E C C メモリ・デバイスに書き込まれるように、前記ストレージからのデータを前記メモリ・モジュールの前記メモリ・デバイスに書き戻すこととを含む、方法。

【請求項 1 2】

前記メモリ・コントローラは、前記メモリ・モジュール上でスペア・メモリ・デバイスが利用可能でない前記デュアル・チャネル・モードでの動作中に所定のトリガが生じることを認識することによって、前記メモリ・モジュールの動作を前記デュアル・チャネル・モードから前記シングル・チャネル・モードに切り替えることが必要であると判断するように構成され、

前記所定のトリガは、前記メモリ・デバイスの任意の 1 つにおける 1 ビット誤り率が所定の閾値に達するときに生じる、請求項 1 1 に記載の方法。

【請求項 1 3】

前記故障メモリ・デバイスは、前記所定のトリガを発生させる、請求項 1 2 に記載の方法。

【請求項 1 4】

メモリ・モジュールを制御するように構成された回路を有するメモリ・コントローラであって、前記回路は、請求項 1 ないし 1 3 のいずれかに記載の方法を実行するように構成されている、メモリ・コントローラ。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、一般に、メモリ・モジュールに関し、より詳細には、メモリ・モジュールにおいて、デュアル・チャネル・メモリ (dual channel memory) をスペア・メモリとなるようにシングル・チャネル・メモリ (single channel memory) として使用することに関する。

【背景技術】

【0 0 0 2】

デュアル・イン・ライン・メモリ・モジュール (D I M M : dual in-line memory module) は、一連のダイナミック・ランダム・アクセス・メモリ (D R A M) 集積回路を含む。これらの D I M M は、プリント回路基板に搭載され、例えば、パーソナル・コンピュータ、ワークステーションおよびサーバにおいて用いるように設計される。D I M M は、最新技術のプロセッサにおける主流のメモリ型として、S I M M (シングル・イン・ライン・メモリ・モジュール) に置き換わった。S I M M における接点はモジュールの両側で冗長であるのに対し、D I M M は各側で別個の電気接点を有する。別の差異は、標準的な S I M M が 3 2 ビット・データ経路を有する一方で、標準的な D I M M は 6 4 ビット・データ経路を有することである。多くのプロセッサは 6 4 ビット・バス幅を有し、データ・バスを実装するために、S I M M が整合したペアで設置されることを必要とする。そして、プロセッサは 2 つの S I M M に並列にアクセスする。しかしながら、S I M M のこの不利な点を排除するために D I M M が導入された。

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 3】

本発明は、メモリ・コントローラを動作させる方法、デュアル・チャネル・モードからシングル・チャネル・モードに切り替える方法、およびメモリ・コントローラを提供する。

【課題を解決するための手段】

10

20

30

40

50

## 【0004】

本発明の実施形態のメモリ・コントローラを動作させる方法は、メモリ・コントローラによって、メモリ・コントローラの第1のメモリ・デバイスおよび第2のメモリ・デバイスをデュアル・チャネル・モードで駆動することを含み、第1の誤り訂正符号(ECC)メモリ・デバイスおよび第2のECCメモリ・デバイスは、第1のメモリ・デバイスおよび第2のメモリ・デバイスを保護する。方法は、メモリ・コントローラによって、第2のECCメモリ・デバイスがスペア・メモリ・デバイス(spare memory device)となるように、第1のメモリ・デバイスおよび第2のメモリ・デバイスをシングル・チャネル・モードで駆動することを含む。第1のECCメモリ・デバイスは第1のメモリ・デバイスおよび第2のメモリ・デバイスを保護し、メモリ・コントローラは、デュアル・チャネル・モードとシングル・チャネル・モードとの間で切り替えるように構成される。

10

## 【0005】

本発明の実施形態のメモリ・コントローラは、メモリ・モジュールを制御するように構成された回路を含む。ここで、回路は、第1のメモリ・デバイスおよび第2のメモリ・デバイスをデュアル・チャネル・モードで駆動するように構成され、第1の誤り訂正符号(ECC)メモリ・デバイスおよび第2のECCメモリ・デバイスは、第1のメモリ・デバイスおよび第2のメモリ・デバイスを保護する。回路は、第2のECCメモリ・デバイスがスペア・メモリ・デバイスとなるように、第1のメモリ・デバイスおよび第2のメモリ・デバイスをシングル・チャネル・モードで駆動するように構成される。ここで、第1のECCメモリ・デバイスは第1のメモリ・デバイスおよび第2のメモリ・デバイスを保護し、回路は、デュアル・チャネル・モードとシングル・チャネル・モードとの間で切り替えるように構成される。

20

## 【0006】

本発明の実施形態のデュアル・チャネル・モードからシングル・チャネル・モードに切り替える方法は、メモリ・コントローラによって、メモリ・モジュールの動作のデュアル・チャネル・モードからシングル・チャネル・モードへの切替えが必要であると判断することであって、メモリ・モジュールは、第1のチャネルおよび第2のチャネルにおいてメモリ・デバイスを含む、判断することと、メモリ・コントローラによって、デュアル・チャネル・モードからシングル・チャネル・モードに切り替えることとを含む。切り替えることは、メモリ・モジュールのメモリ・デバイスから全てのデータを読み出すことと、メモリ・モジュールのメモリ・デバイスからストレージにデータをロードすることと、メモリ・デバイスの2つの誤り訂正符号(ECC)メモリ・デバイスの代わりに単一のECCメモリ・デバイスを用いて第1のチャネルおよび第2のチャネルを保護することによって、メモリ・デバイスのスペアECCメモリ・デバイスが利用可能になるようにすることと、故障メモリ・デバイスとの間で行われることを対象とした書き込みおよび読み出しが、代わりにスペアECCメモリ・デバイスとの間で行われる書き込みおよび読み出しが、故障メモリ・デバイスの入力および出力をスペアECCメモリ・デバイスにマッピングすることとを含む。切り替えることは、故障メモリ・デバイスを対象とするデータの一部分が代わりにスペアECCメモリ・デバイスに書き込まれるように、ストレージからのデータをメモリ・モジュールのメモリ・デバイスに戻して書き込むことを含む。

30

## 【図面の簡単な説明】

## 【0007】

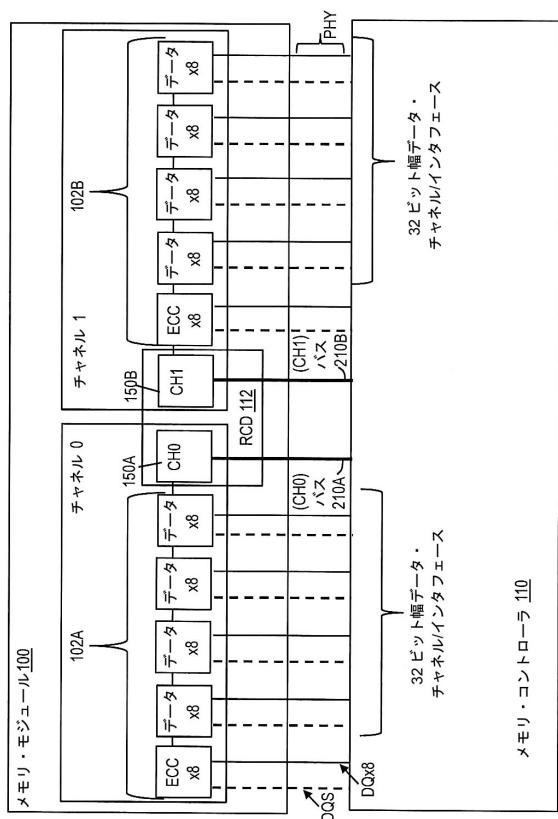

【図1】メモリ・コントローラに接続されたメモリ・モジュールの概略図である。

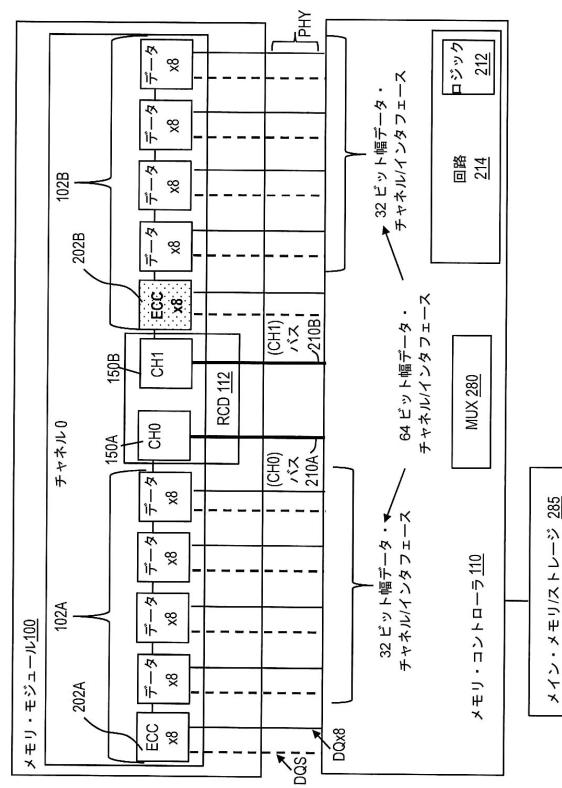

【図2】実施形態による、変更されたメモリ・コントローラに接続されたメモリ・モジュールの概略図である。

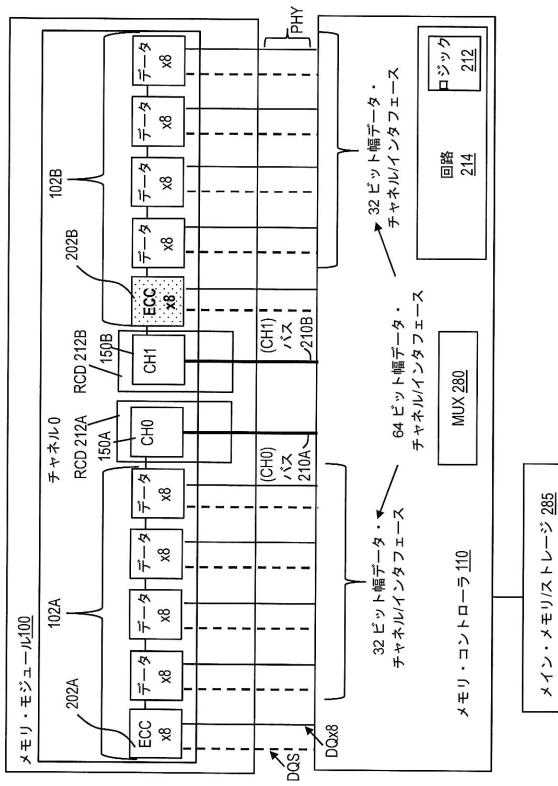

【図3】実施形態による、変更されたメモリ・コントローラに接続された、変更されたメモリ・モジュールの概略図である。

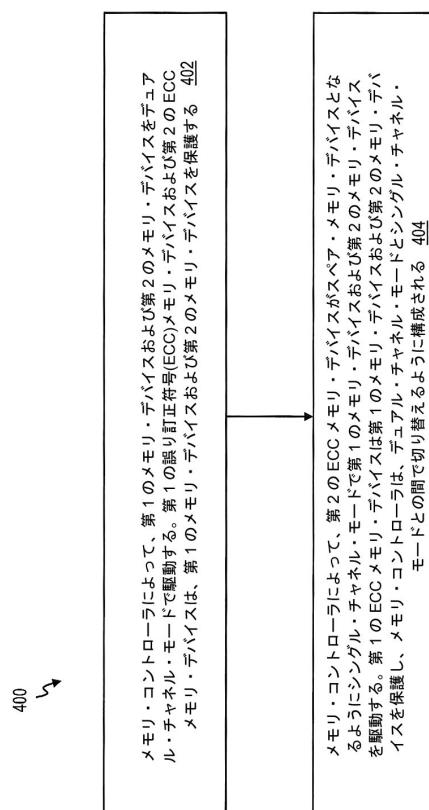

【図4】実施形態による、メモリ・コントローラを動作させるための方法のフロー・チャートである。

【図5】実施形態による、メモリ・コントローラを構成する方法のフロー・チャートであ

40

50

る。

【図6】実施形態による、デュアル・チャネル・モードをシングル・チャネル・モードに切り替える方法のフロー・チャートである。

【発明を実施するための形態】

【0008】

本明細書では、関連する図面を参照して、本発明の様々な実施形態が説明される。本発明の範囲を逸脱することなく、本発明の代替の実施形態を考案することができる。以下の説明および図面において、要素間の様々な接続および位置関係（例えば、上、下、隣接等）が示される。それらの接続または位置関係あるいはその両方は、特に規定されない限り、直接的または間接的であることができ、この点において限定するよう意図されていない。したがって、実体の結合は、直接的結合または間接的結合を指すことができ、実体間の位置関係は、直接的位置関係または間接的位置関係であることができる。間接的な位置関係の例として、層「B」の上に層「A」を形成することへの言及は、層「A」および層「B」の関連する特徴および機能性が中間層によって実質的に変化しない限り、1つまたは複数の中間層（例えば層「C」）が層「A」と層「B」との間にある状況を含む。

10

【0009】

本発明の様々な実施形態の説明は、例示の目的で提示されているが、網羅的であることも、開示された実施形態に限定されることも意図されていない。記載された実施形態の範囲および思想を逸脱することなく、多くの変更および変形が当業者にとって明らかとなる。本明細書で使用された用語は、実施形態の原理、実際の適用、または市場で見られる技術を超える技術的改良を最も適切に説明するため、または他の当業者が本明細書に記載された実施形態を理解できるようにするために選択されている。

20

【0010】

「約」という用語およびその変形形態は、本願書の出願時に使用できる機器に基づいて、特定の量の測定に関連付けられた誤差の程度を含むよう意図されている。例えば、「約」は、所与の値の±8%または5%、あるいは2%の範囲を含むことができる。

【0011】

ハイ・エンドおよびロー・エンドのコンピューティング・システムは、ほとんどの場合に、ダブル・データ・レート（DDR）同期DRAM（SDRAM）として一般的に知られるもの等の高速メモリ・インターフェースを利用する。DDRメモリおよび関連インターフェースは、合同電子デバイス委員会（JEDEC）として知られる産業標準規格本体による制約を受ける。DDRメモリはJEDECを通じて標準化されているが、DDRメモリ・サブシステムを用いるハイ・エンドおよびロー・エンド・コンピュータ・システムの需要は非常に異なる。例えば、ロー・エンド・パーソナル・コンピュータ（PC）対ハイ・エンド・メインフレームを検討するとき、復元可能性、利用可能性、およびサービス可能性（RAS）、電力/熱、ならびに性能（帯域幅、レイテンシ、速度）需要は非常に異なる。よりロー・エンドのコンピュータ・システムは、ハイ・エンド・コンピュータ・システムよりもはるかに大きい販売ボリュームを有するため、よりロー・エンドのシステム要件は、DDR SDRAMモジュールのDIMM定義の標準化において、より大きい重みを有する。この結果、よりロー・エンドでコストの低いコンピュータ・システム（PC等）についてDRAM DIMMが最適化されることになる。より高いレベルのRASを必要とする場合があり、DRAMデバイスのスペア処理を含む場合がある、よりハイ・エンドのコンピュータ・システムは、カスタマイズされたDIMMを展開する余地が残され、それによってシステムコストが大幅に増大する。実施形態は、（よりロー・エンドのコンピュータ・システムのために最適化された）デュアル・メモリ・チャネルDRAM DIMMを、スペア処理を用いたシングル・チャネルDIMMとして用いる方法およびシステムを提供する。これにより、よりハイ・エンドのコンピュータ・システムが、依然としてより高レベルのRASを達成しながら、より低コストのDIMMを利用することが可能になる。よりロー・エンドのコンピュータ・システムは、スペア・メモリ・デバイスを必要としないDIMM（メモリ・モジュール）を有する。しかしながら、よりロー・エンドの

30

40

50

コンピュータ・システムのために設計された同じDIMMを用いて、実施形態は、スペア・メモリ・デバイス（すなわち、スペアDRAMアレイ）を作成することによってDIMMのRASを改善するように構成される。

#### 【0012】

最新技術において、同じアドレスが双方のチャネルに提示される「ロックステップ」において実行されるデュアル・チャネル・メモリ・システムが存在する。最新技術は、2つのDIMMの使用を必要とする。しかしながら、実施形態は、デュアル・チャネル・メモリ・システムが、同じアドレスが双方のチャネルに提示される「ロックステップ」において実行されている間であっても、1つのみのDIMMを利用する。実施形態は、単一のデュアル・チャネルDIMMを、スペア・メモリ・デバイスの利点が加わったシングル・チャネルDIMM（ロックステップにおいて2つのチャネルに類似している）として使用することを可能にする。スペア・メモリ（DRAM）デバイスに加えて、スペアRCDデバイスも展開することができる。いくつかの実施形態では、スペアRCDおよびスペアDRAMメモリ・デバイスは、RCDデバイスおよびスペアの双方がデュアル・チャネルDIMM上でアクティブである状態で2つの別個のチャネルを実行することと比較して、電力を節減するように使用不可能にされ得る。現行のDDR DIMM技術をペアで用いる最新技術のシステムは、スペア・デバイスを可能にしない。更に、実施形態は、シングルRCDおよびデュアルRCDについて実行することができる。

10

#### 【0013】

図1は、メモリ・コントローラ110に接続されたメモリ・モジュール100の概略図である。メモリ・モジュール100は、DDR5 DIMMとすることができる。この例において、メモリ・モジュール100はチャネル0およびチャネル1を有する。チャネル0はメモリ・デバイス102Aを含むのに対し、チャネル1はメモリ・デバイス102Bを含む。メモリ・デバイス102Aおよび102Bは、当業者によって理解されるDRAMの各アレイである。メモリ・デバイス102Aおよび102Bの各々は、8倍を意味する指定「×8」を有する8ビット幅チップとして示される。メモリ・デバイスは4ビット幅チップ（すなわち、×4）であってもよいことが理解されるべきである。更に、メモリ・モジュールは、×8メモリ・デバイスから構成されて示されているが、メモリ・モジュール100は、×4、×8、×16、×32または任意の組合せを含む他の幅のDRAMデバイス（メモリ・デバイス102Aおよび102B等）から構成されてもよい。図1におけるメモリ・モジュール100は、2つのコマンド・バスで示されるが、1つまたは2つより多くのコマンド・アドレス・バスを有し得る。

20

#### 【0014】

チャネルは、ローカル・メモリ・コントローラ・レベルとして最高レベルの構造である。コンピュータは、2つ、3つまたはそれ以上のチャネルを有することができるが、この例では2つのチャネルが示される。チャネル0における各メモリ・デバイスは、チャネル1における同じロケーションに、整合するメモリ・デバイスを有する。

30

#### 【0015】

チャネル0は、専用誤り訂正符号（ECC）メモリ・デバイス102Aを有するのに対し、他のメモリ・デバイス102Aはデータ・メモリ・デバイスである。同様に、チャネル1は、専用誤り訂正符号（ECC）メモリ・デバイス102Bを有するのに対し、他のメモリ・デバイス102Bはデータ・メモリ・デバイスである。チャネル0におけるデータ・メモリ・デバイス102Aと、チャネル1におけるデータ・メモリ・デバイス102Bは、当業者に理解されるように（読み出しおよび書き込みのために）データを記憶するように構成される。ECCメモリ・デバイス102Aは、データ・メモリ・デバイス102Aのための誤り保護を提供するように構成される。ECCメモリ・デバイス102Bは、データ・メモリ・デバイス102Bのための誤り保護を提供するように構成される。メモリ・モジュール100において、チャネルあたり2つの32ビット・データが存在する。これは、読み出しありは書き込みのために、チャネル0における4つのデータ・メモリ・デバイス102Aが、メモリ・コントローラ110に32ビット幅データ・インターフェース（チ

40

50

ヤネルあたり × 32 データ ) を提供し、チャネル 1 における 4 つのデータ・メモリ・デバイス 102B が、メモリ・コントローラ 110 に 32 ビット幅データ・インターフェース ( チャネルあたり × 32 データ ) を提供することを意味する。バースト長 ( B L ) は 16 と 10 することができ、1 つの読み出しちゃは書込みにわたって、64B の総データ転送について 32b の 16 個の転送が存在する。単一の ECC メモリ・デバイス ( ECC メモリ・デバイス 102A または ECC メモリ・デバイス 102B 等 ) について、チャネルあたり追加の 8 ビット ( × 8 ) ECC メモリ・デバイスが必要とされるように、32 ビットのデータにわたる誤り訂正符号は 7 ビットの ECC メモリを要する。したがって、単一の ECC メモリ・デバイス ( ECC メモリ・デバイス 102A または ECC メモリ・デバイス 102B 等 ) は、シングル・チャネル ( 32 ビット・データ・チャネル ) のみを保護することができる。したがって、ECC メモリ・デバイス 102A は、4 つのデータ・メモリ・デバイス 102A を保護し ( すなわち、 $4 \times 8 = 32$  ビットである 32 ビット・データ・チャネルを保護し ) 、ECC メモリ・デバイス 102B は、4 つのデータ・メモリ・デバイス 102B を保護する ( すなわち、32 ビット・データ・チャネルを保護する ) 。したがって、メモリ・モジュール 100 は、ECC メモリ・デバイス 102A および ECC メモリ・デバイス 102B として示される 2 つの ECC メモリ・デバイスを要する。

#### 【 0016 】

メモリ・デバイス 102A および 102B に記憶されるデータは、ECC デバイス内に記憶された誤り訂正符号 ( ECC ) によって保護され、ECC 符号は、多くのタイプのコンピュータ・データ・ストレージと共に、最も一般的な種類のデータ破損を検出し、訂正するのに一般的に用いられる。追加のメモリビットを含む DRAM モジュール ( ECC メモリ・デバイス 102A および 102B ) と、これらのビットを利用するメモリ・コントローラ 110 とを用いることによって、問題を軽減することができる。これらの追加ビットは、パリティを記録するのに用いられる ( すなわち、誤り訂正符号を用いる ) 。パリティにより、全ての単一ビット誤り ( 実際は、任意の奇数の誤りビット ) の検出が可能になる。最も一般的な誤り訂正符号である 1 ビット誤り訂正・2 ビット誤り検出 ( SECDED : single-error correction and double-error detection ) ハミング符号は、( 通常の構成では、追加のパリティ・ビットを用いて ) 1 ビット誤りが補正され、2 ビット誤りが検出されることを可能にする。

#### 【 0017 】

レジスタリング / レジスタ・クロック・ドライバ ( RCD ) 112 は、チャネル 0 およびチャネル 1 の双方に接続される。RCD 112 は、メモリ・モジュール 100 上のチップとすることができる。RCD 112 は、チャネル 0 コマンド・アドレス ( CA ) バス 210A を介したチャネル 0 におけるデータ・メモリ・デバイス 102A へのルーティングおよびロード、ならびにチャネル 1 コマンド・アドレス ( CA ) バス 210B を介したチャネル 1 におけるデータ・メモリ・デバイス 102B へのルーティングおよびロードのために構成される。レジスタリング / レジスタ・クロック・ドライバ 112 は、バッファ・デバイスでもある。RCD 112 は、( データ・メモリ・デバイスおよび ECC メモリ・デバイスの双方を含む ) メモリ・デバイス 102A に接続される。RCD 112 は、( データ・メモリ・デバイスおよび ECC メモリ・デバイスの双方を含む ) メモリ・デバイス 102B に接続される。

#### 【 0018 】

RCD 112 は、当業者によって理解されるような、最新技術における業界標準DIMM のための、チャネル 0 を制御するためのロジック 150A と、チャネル 1 を制御するためのロジック 150B を含む。通常のデュアル・チャネル・モードにおいて、チャネル 0 ロジック 150A は、DIMM の一方の側 ( チャネル 0 ) でメモリ・コントローラ 110 から所望のメモリ・デバイス 102A へコマンドおよびアドレス情報を渡し、他方の側 ( チャネル 1 ) でメモリ・コントローラ 110 から所望のメモリ・デバイス 102B へコマンドおよびアドレス情報を渡す。

#### 【 0019 】

10

20

30

40

50

メモリ・コントローラ 110 は、RCD112 へのコマンド・アドレス (C A) ライン (CH0 バス 210A、CH1 バス 210B である) を介してメモリ・モジュール 100 と通信するように構成される。読み出しおよび書き込みコマンドは、ロジック 150A を介してチャネル 0 についてメモリ・コントローラ 110 から RCD112 へ発行され、ロジック 150B を介してチャネル 1 についてメモリ・コントローラ 110 から RCD112 へ発行される。例えば、書き込みは、(CH0 バス 210A を介して) チャネル 0 において生じ得るのに対し、読み出しは、メモリ・モジュール 100 の (CH1 バス 210B を介して) チャネル 1 において生じている。したがって、メモリ・デバイス 102A およびメモリ・デバイス 102B (すなわち、DRAM) を制御するためにメモリ・コントローラ 110 によって用いられるソフトウェアの全ては、RCD112 を通じたものである。メモリ・コントローラ 110 は、メモリ・モジュール 100 (例えば、DDR5 DIMM) に接続するための物理層インターフェース (PHY) を有する DDR5 メモリ・コントローラ とすることができる。当業者に理解されているように、現在の規格は DDR4 から DDR5 に遷移している。更に、メモリ・デバイス 102A および 102B の各々は、DQS および DQ × 8 を介してメモリ・コントローラ 110 に接続される。ここで、DQS はデータ・ストローブであり、DQ × 8 は 8 ビット単位のデータである。

#### 【0020】

図 2 は、実施形態による、変更されたメモリ・コントローラ 110 に接続されたメモリ・モジュール 100 の概略図である。メモリ・コントローラ 110 は、本明細書において論考された追加の機能と合わせて上記で論考されたメモリ・コントローラ 110 の機能を含むことができる。メモリ・モジュール 100 をデュアル・チャネル・メモリとして (すなわち、別個の 32 ビット・データ・チャネル 0 および別個の 32 ビット・データ・チャネル 1 として) 動作させる代わりに、メモリ・コントローラ 110 は、メモリ・モジュール 200 を切り替えて、単一の 64 ビット・データ・チャネル 0 を有するシングル・チャネルとして動作させるように構成される。換言すれば、メモリ・コントローラ 110 は、メモリ・モジュール 100 をデュアル・チャネル・メモリ・モードで動作させることから、シングル・チャネル・メモリ・モードで動作させることに切り替えるように構成される (逆もまた同様)。説明の目的で、単一の 64 ビット・データ・チャネル 0 が示されているが、単一の 64 ビット・データ・チャネル 0 は実際にはチャネル 0 および 1 の双方であることが理解される。

#### 【0021】

通常のデュアル・チャネル・モードでは、メモリ・コントローラ 110 は、チャネル 0 のメモリ・デバイス 102A のための CH0 コマンド・アドレス・バス 210A を介して RCD112 のチャネル 0 ロジック 150A にコマンドおよびアドレス情報を発行するように構成される。同様に、メモリ・コントローラ 110 は、デュアル・チャネル・モードにおいて、チャネル 1 のメモリ・デバイス 102B のための CH1 コマンド・アドレス・バス 210B を介して RCD112 のチャネル 1 ロジック 150B にコマンドおよびアドレス情報を発行するように構成される。デュアル・チャネル・モードでは、ECC メモリ・デバイス 102A および ECC メモリ・デバイス 102B である 2 つの ECC メモリ・デバイスが必要とされる。しかしながら、シングル・チャネル・モードにおいてチャネル 0 および 1 の双方を 1 つのチャネル (例えば、チャネル 0) として組み合わせるとき、メモリ・コントローラ 110 は、チャネル 0 および 1 の双方に同時に同じコマンドおよびアドレス情報を発行し、これらをシングル・チャネル・モードにおいて 1 つの大きいチャネルとして (すなわち、64 ビット幅のデータ・チャネルとして) 動作させるように構成され、このコマンドおよびアドレス情報は、CH0 バス 210A および CH1 バス 210B に対し同時に (またはほぼ同時に) 発行される。以下で更に論考されるように、シングル・チャネル・モードでは、ECC メモリ・デバイス 102A または ECC メモリ・デバイス 102B のいずれかとすることができます 1 つの ECC メモリ・デバイスのみが必要とされる。説明の目的で、誤り訂正符号メモリについて ECC メモリ・デバイス 102A が指定されている。

10

20

30

40

50

## 【0022】

図2に示すように、実施形態は、バースト長（BL）8を有することができる、チャネルあたり×64データで駆動されたメモリ・モジュール100を提供する。ここで、BL8は、メモリ・デバイス／モジュール100からのデータの8つのバーストを意味し、デバイスが×8である場合、データの8つのバーストは、64bのデータに等しい。一般的なDDR4メモリ・システムでは、メモリ・デバイスは、64b幅インターフェースを含み、標準的なデータ送信は、8つのバーストにわたる64bのデータに等しいBL8であり、これは64バイトのデータに等しい。DDR5メモリ・システムでは、1つの32ビット幅メモリ・チャネルにわたるデータ送信が、バーストあたり32ビットの16個のバーストとなる、BL16が存在する場合があり、ここでもまた、これはDDR4メモリ・システムにおけるような64バイトに等しい。BL4またはBL32等の他のバースト長も可能である。バースト長は、各送信において中央プロセッサ・ユニット（すなわちプロセッサ）とメモリとの間で転送されるデータ量である。図2において、書込みまたは読み出しあり合計で64バイトについて、バーストあたり64ビットのデータのBL8送信が存在するが、他のBL長も実施形態に含まれる。したがって、（保護する）64ビットのデータにわたる誤り訂正符号は、8ビットを必要とし、これは、64ビットのデータを保護することが、シングル・チャネル・モードにおいて1つの×8ECCメモリ・デバイス102Aまたは102B（ただし両方ではない）を要することを意味する。このため、1つのBL8送信中に、合計で8バイトのECCデータが存在する。実施形態によれば、メモリ・コントローラ110は、追加のECCメモリ・デバイスをスペア・メモリ・デバイス（スペア・データ・メモリ・デバイスまたはスペアECCメモリ・デバイスあるいはその両方として利用可能であり、この理由は、これらは共に、異なる目的で用いられる同じメモリ・デバイスであるためである）として用いるように構成される。メモリ・コントローラ110は、（シングル・チャネル・モードにおいて）単一の64ビット・データ・チャネルについての誤り訂正符号メモリのためにECCメモリ・デバイス102Aおよび102Bのうちの一方を利用するのに対し、他方の使用されないECCメモリ・デバイスをスペアとする（ECCのために利用されない）ように構成される。例示の目的で、64ビット・データ・インターフェースを保護するECCメモリ・デバイスとしての動作対スペア・メモリ・デバイスとしての動作を強調するために、ECCメモリ・デバイス102Aは202Aとして指定され、ECCメモリ・デバイス102Bは202Bとして指定される。メモリ・デバイス102AのECCメモリ・デバイス202Aは、シングル・チャネル・モードにおいて単一の64ビット・データ・チャネルのためのECCメモリ・デバイスとして動作することができるのに対し、メモリ・デバイス102BのECCメモリ・デバイス202Bはスペア・メモリ・デバイスとして動作する。データ・メモリ・デバイス102Aおよび102Bにおいて任意の1つのメモリ・デバイスが故障する場合、メモリ・コントローラ110は、スペア（ECC）メモリ・デバイス202Bを利用して、故障したメモリ・デバイスを置き換えるように構成される。説明の目的であり限定ではないが、以下は、実施形態に従ってこれをどのように達成することができるかの例示的なシナリオである。メモリ・コントローラ110は、メモリ・デバイス102Aもしくは102Bとメモリ・コントローラ110との接続間のメモリ送信失敗の繰返し、またはメモリ・デバイス102Aもしくは102B内のメモリ・ストレージ・ロケーションの故障等の特定の条件時にスペア・デバイス202Bの使用を開始することができる。通常、故障は、データがメモリ・コントローラ110によって受信されるときに見つかり、メモリ・コントローラ110は、（例えば、ECCメモリ・デバイス202Aを用いることによって）ECC符号に対しデータをチェックし、誤りのあるデータを示す。一般的なECC符号を用いて、1ビット・フェイル（bit fail）を訂正し、2ビット・フェイルを検出することができる。メモリ・コントローラ110は、このチェックを用いて、システム（メモリ・モジュール100）内の故障のロケーションを特定することができる。特定のメモリ・デバイス102Aまたは102Bの故障の検出時に、メモリ・コントローラ110は、そのデータ・メモリ・デバイス（例えば、102Aまたは102Bにおける1つのデータ・メモリ・

10

20

30

40

50

デバイス)を使用不可能にし、スペアECCメモリ・デバイス202Bを用いることを選択することができる。これは通例、誤りが依然として訂正可能である間に行われる。いくつかの実施形態では、メモリ・コントローラ110は、スペア・デバイス(すなわち、スペアECCメモリ・デバイス202B)を使用可能にし、次に、メモリ全体にわたって一連の読み出し動作、次に書き込み動作を行う。このスペア・デバイスにおいて、誤りのあるデバイス(例えば、102Aまたは102Bにおける1つのデータ・メモリ・デバイス)からのデータが読み出され、訂正され、メモリに戻して書き込まれる。しかしながら、書き込み時に、スペア・デバイス(すなわち、スペアECCメモリ・デバイス202B)は、故障デバイス(例えば、102Aまたは102Bにおける1つのデータ・メモリ・デバイス)からの(またはこのデバイスを対象とする)データのコピーを得る。このメカニズムは、任意のメモリ・デバイスのデータがDIMM上の別のメモリ・デバイスに書き込まれることを可能にする、プログラム可能なマルチプレクサ・ネットワーク280を必要とする場合がある。したがって、データ・メモリ・デバイス102A、102Bが故障するかまたはECCメモリ・デバイス202Aが故障する場合、メモリ・コントローラ110は、必要に応じて、データ・メモリ・デバイスまたはECCメモリ・デバイスとしてスペア・メモリ・デバイス202Bに切り替えることができる。メモリ・コントローラ110は、故障したメモリ・デバイスの代わりに、CH0バス210AおよびCH1バス210Bを介してスペア・メモリ・デバイス202Bのアドレスに対し必要なコマンドを発行し、それによって、メモリ・モジュール100がRASなしで(すなわち、スペア・メモリ・デバイス202Bなしで)元々設計された場合にRASを実装させるように構成される。

#### 【0023】

図2において、シングル・チャネルとしてのDDR5 DIMMの動作は、DDR5 DIMM(メモリ・モジュール100)自体に対する変更を必要としない。しかしながら、メモリ・コントローラ110は、(バス210Aおよび210Bを介して)チャネル0および1の双方に対し同じコマンドおよびアドレス(CA)を駆動し、単一の二重幅チャネルを生成するように構成され、ここで、メモリ・モジュール100はスペア・メモリ・デバイス202Bを有することになる。いくつかの実施形態では、メモリ・コントローラ110は、ECCメモリ・デバイス202Bがスペアとして利用可能であるように、(メモリ・デバイス102Bの)ECCメモリ・デバイス202Bをオフにするか、またはECCメモリ・デバイス202Bが誤り訂正符号メモリとして機能することができないようするか、あるいはその両方を行うように構成される。シングル・チャネル・モードにおいて、メモリ・チャネル110は、以前であればECCメモリ・デバイス202Bに対しアドレス指定されていた任意のコマンドをECCメモリ・デバイス202Aに発行するように構成される。また、メモリ・デバイス102Aおよび102Bのいずれか1つの故障時には、メモリ・コントローラ110は、データをスペア(ECC)メモリ・デバイス202B上に保存するために、スペア(ECC)メモリ・デバイス202Bに向けてコマンドをアドレス指定するようにも構成される。メモリ・コントローラ110は、本明細書において論考されるように機能するハードウェアとして回路214を用いて構成される。回路214は、本明細書において論考したように動作するためのロジック212、バッファ等を含むことができる。メモリ・コントローラ110は、当業者に理解されるように、メモリ・モジュールおよび中央処理ユニット(すなわち、図示されていないプロセッサ)に作動的に接続するための標準的なハードウェアを含む。1つの場合、ロジック212は、回路214が本明細書において論考されるように動作するためのロジック212を実行するように、ファームウェアまたはミニコードあるいはその両方を含むことができる。ロジック212は、実行可能命令、特定用途向け集積回路(ASSIC)等の形態をとることができる。

#### 【0024】

メモリ・コントローラ110は、メモリ・モジュール100をデュアル・チャネル・モードで動作させることと、シングル・チャネル・モードで動作させることとの間で往復して切り替えることができる。例えば、ユーザは、メモリ・コントローラ110上でシング

ル・チャネル・モードまたはデュアル・チャネル・モードあるいはその両方の設定を選択することができる。例えば、メモリ・コントローラ 110 がメモリ・デバイス 102A および 102B において故障したメモリ・デバイスを検出すると、メモリ・コントローラ 110 は、故障したメモリ・デバイスの代わりにスペア・メモリ・デバイス 202B を利用することができるよう、デュアル・チャネル・モード（すなわち、チャネル 0 およびチャネル 1 を別個に動作させる）からシングル・チャネル・モードに切り替えるように構成することができる。説明の目的であり、限定ではないが、以下は、メモリ・コントローラ 110 をどのようにデュアル・チャネル・モードからシングル・チャネル・モードに切り替えることができるかの例示的なシナリオである。通常、デュアル・チャネル・モードで実行しているとき、各 32b 幅チャネル 102A および 102B はその ECC メモリ・デバイス（それぞれ、ECC メモリ・デバイス 202A および 202B）を用いてそれぞれのチャネル 0 および 1 における故障を検出し、訂正するため、スペア・デバイスは存在しない。しかしながら、1 つの実施形態において、任意のデータ・メモリ・デバイスにおける 1 ビット誤り率が増大し始める（例えば、ビット誤り率が所定の閾値に到達する）場合、メモリ・コントローラ 110 は、所定の閾値に到達したことを、メモリ・コントローラ 110 が故障デバイスを外すようにスペア処理を行う必要があるトリガとして認識する。メモリ・コントローラ 110 は、故障デバイスを外すようにスペア処理を行うよう構成される。しかし、デュアル・チャネル構成ではスペア・デバイスが存在せず、メモリ・コントローラ 110 は、デュアル・チャネル・モードからシングル・チャネル・モードに切り替える（それによって、故障メモリ・デバイスの代わりに使用するためにスペア・メモリ・デバイスが利用可能となるようになる）ように構成される。デュアル・チャネル・システムにおいて、この切替えは、メモリ・コントローラ 110 が、双方のチャネルから DIMM からの全てのデータを読み出し（すなわち、メモリ・デバイス 102A および 102B の双方から全てのデータを読み出し）、データをストレージ 285（例えば、メイン・メモリ）内に配置し、メモリ・モジュール 100 をシングル・チャネル・モードに切り替えることを要する場合がある。シングル・チャネル・モードでは、1 つの ECC デバイス（例えば、ECC メモリ・デバイス 202A）を要する 1 つの 64b 幅チャネルが存在し、1 つの ECC デバイスをスペア（例えば、スペア ECC メモリ・デバイス 202B）として使用されないままにする。メモリ制御部 110 は、故障デバイス（例えば、1 つのデータ・メモリ・デバイス 102A（または 1 つのデータ・メモリ・デバイス 102B））を、スペアとしての、使用されていない ECC デバイス（例えば、スペア ECC メモリ・デバイス 202B）にマッピングし、次に、全てのメモリを DIMM に（それぞれのメモリ・デバイス 102A および 102B 内に）戻して書き込むように構成される。

#### 【0025】

メモリ・コントローラ 110 は、標準的な DDR5 DIMM（メモリ・モジュール 100）を用いているとき、7 ビット ECC 符号を用いた 2 つの 32 ビット・データ・チャネルのいずれか（すなわち、デュアル・チャネル・モード）で実行され、8 ビット ECC 符号および 8 ビット・スペア・メモリ・デバイスを用いた 単一 64b チャネル（すなわち、シングル・チャネル・モード）に切り替えるように構成されることが理解されるべきである。一般的な SECDED（1 ビット誤り訂正・2 ビット誤り検出）ECC 符号化では、フェイルを検出し訂正するのに要するビット数が減少し、チェックされているビット数が増大する。SECDED ECC で 32b のデータをカバーするには、7 ビットの ECC 符号を要し、SECDED ECC で 64b のデータをカバーするには、更なる 1 ビットのみの ECC 符号を要し、合計 8 ビットとなる。デュアル・チャネル・モードは、CH0 バス 210A および CH1 バス 210B において別個にかつ独立してコマンドおよびアドレス情報を発行する。シングル・チャネル・モードは、CH0 バス 210A および CH1 バス 210B の双方において同じコマンドおよびアドレス情報を発行する。

#### 【0026】

図 3 は、実施形態による、変更されたメモリ・コントローラ 110 に接続された、変更されたメモリ・モジュール 100 の概略図である。図 3 は、メモリ・モジュール 100 が

10

20

30

40

50

2つ以上のRCDを有する場合を示している。この場合、メモリ・モジュール100は、RCD212AおよびRCD212Bとして指定される2つのRCDを有して示される。RCD212Aはチャネル1のためのロジック150Aを有するのに対し、RCD212Bはチャネル2のためのロジック150B

を有する。本明細書に論考したように、メモリ・コントローラ110は、デュアル・チャネル・モードでメモリ・モジュール100を動作させるように構成される。デュアル・チャネル・モードでは、バス210Aにおいて（RCD212Aのロジック150Aを介して）メモリ・デバイス102Aに発行されたコマンドおよびアドレス情報は、バス210Bにおいて（RCD212Bのロジック150Bを介して）メモリ・デバイス102Bに発行されたコマンドおよび情報と独立している。独立とは、書き込みコマンド等の1つのタイプのコマンドをCH0バス210Aに対し発行することができる一方で、読み出しコマンド等の別のタイプのコマンドがCH1バス210Bに対し同時に発行されることを意味する。メモリ・コントローラ110は、シングル・チャネル・モードでメモリ・モジュール100を動作させるように構成される。シングル・チャネル・モードでは、バス210Aおよび210Bの双方においてRCD212Aおよび212Bのロジック150Aおよび150Bを介してメモリ・デバイス102Aおよび102Bに同じコマンドおよびアドレス情報が発行される。

#### 【0027】

コマンド・アドレスおよびデータ・バス210Aおよび210Bは、シングル・エンド型であっても差動型であってもよい。

#### 【0028】

図4は、実施形態による、メモリ・コントローラ110を動作させるための方法のフロー・チャート400である。ブロック402において、メモリ・コントローラ110は、第1のメモリ・デバイス102Aおよび第2のメモリ・デバイス102Bをデュアル・チャネル・モードで駆動するように構成される。ここで、第1の誤り訂正符号（ECC）メモリ・デバイス202Aおよび第2のECCメモリ・デバイス202Bは、第1のメモリ・デバイス102Aおよび第2のメモリ・デバイス102Bを保護する。

#### 【0029】

ブロック404において、メモリ・コントローラ110は、第2のECCメモリ・デバイス202Bがスペア・メモリ・デバイスとなるようにシングル・チャネル・モードで第1のメモリ・デバイス102Aおよび第2のメモリ・デバイス102Bを駆動するように構成される。ここで、第1のECCメモリ・デバイス202Aは第1のメモリ・デバイス102Aおよび第2のメモリ・デバイス102Bを保護し、ここでメモリ・コントローラ110は、デュアル・チャネル・モードとシングル・チャネル・モードとの間で切り替えるように構成される。

#### 【0030】

メモリ・モジュール100は、ダイナミック・ランダム・アクセス・メモリ（DRAM）である。メモリ・モジュールは、DRAMデュアル・イン・ライン・メモリ・モジュール（DIMM）である。

#### 【0031】

第1のメモリ・デバイス102Aは、データ記憶のために構成された第1のデータ・メモリ・デバイス102Aと、誤り訂正のために構成された第1のECCメモリ・デバイス202Aとを備える。第2のメモリ・デバイス102Bは、データ記憶のために構成された第2のデータ・メモリ・デバイス102Bと、誤り訂正のために構成された第1のECCメモリ・デバイス202Bとを備える。メモリ・コントローラ110は、第2のECCメモリ・デバイス202Bがスペア・メモリ・デバイスとなるように、シングル・チャネル・モード中に第2のECCメモリ・デバイス202Bを使用不可能にするように構成される。

#### 【0032】

メモリ・コントローラ110は、第1のメモリ・デバイス102Aおよび第2のメモリ

10

20

30

40

50

・デバイス 102B から故障したメモリ・デバイスを検出するように構成される。メモリ・コントローラ 110 は、スペア・メモリ・デバイスが、メモリ・モジュール 100 内の故障したメモリ・デバイスの代わりに動作するように、故障したメモリ・デバイスをスペア・メモリ・デバイスと置き換えるように構成される。故障したメモリ・デバイスの検出に応答して、メモリ・コントローラ 110 は、スペア・メモリ・デバイスに、第 1 のデータ・メモリ・デバイス 102A、第 1 の ECC メモリ・デバイス 202A、および第 2 のメモリ・デバイス 102B のうちの任意の 1 つの代わりに動作させるように構成される。

#### 【0033】

第 1 のデータ・メモリ・デバイス 102A は、32 ビット幅データ・インターフェースを有し、第 2 のデータ・メモリ・デバイス 102B は、別の 32 ビット幅データ・インターフェースを有する。シングル・チャネル・モード中、メモリ・コントローラ 110 は、第 1 の ECC メモリ・デバイス 202A に、第 1 のデータ・メモリ・デバイス 102A および第 2 のデータ・メモリ・デバイス 102B の双方について 64 ビット幅データ・インターフェースを保護するように構成され、64 ビット幅データ・インターフェースは、32 ビット幅データ・インターフェースと、別の 32 ビット幅データ・インターフェースとの組合せである。第 1 の ECC メモリ・デバイス 202A は 8 ビットであり、第 2 の ECC メモリ・デバイス 202B は 8 ビットである。

#### 【0034】

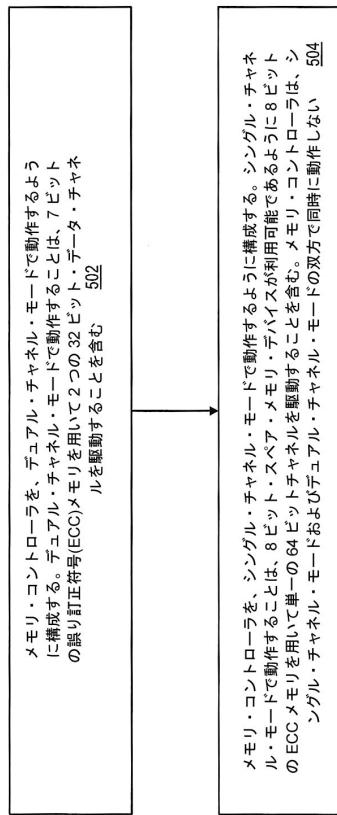

図 5 は、実施形態による、メモリ・コントローラ 110 を構成する方法のフロー・チャート 500 である。ブロック 502 において、メモリ・コントローラ 110 は、デュアル・チャネル・モードで動作するように構成される。ここで、デュアル・チャネル・モードで動作することは、7 ビットの誤り訂正符号 (ECC) メモリ (ECC メモリ・デバイス 202A および 202B) を用いて 2 つの 32 ビット・データ・チャネルを駆動することを含む。ECC メモリ・デバイス 202A および 202B はそれぞれ 8 ビットを有するが、ECC メモリ・デバイス 202A および 202B の各々において、8 ビットのうち 7 ビットしか必要とされない。

#### 【0035】

ブロック 504 において、メモリ・コントローラ 110 は、シングル・チャネル・モードで動作するように構成され、ここで、シングル・チャネル・モードで動作することは、8 ビット・スペア・メモリ・デバイス (例えば、ECC メモリ・デバイス 202B) が利用可能であるように 8 ビットの ECC メモリ (例えば、ECC メモリ・デバイス 202A) を用いて単一の 64 ビットチャネルを駆動することを含む。ここで、メモリ・コントローラ 110 は、シングル・チャネル・モードおよびデュアル・チャネル・モードの双方で同時に動作しない。

#### 【0036】

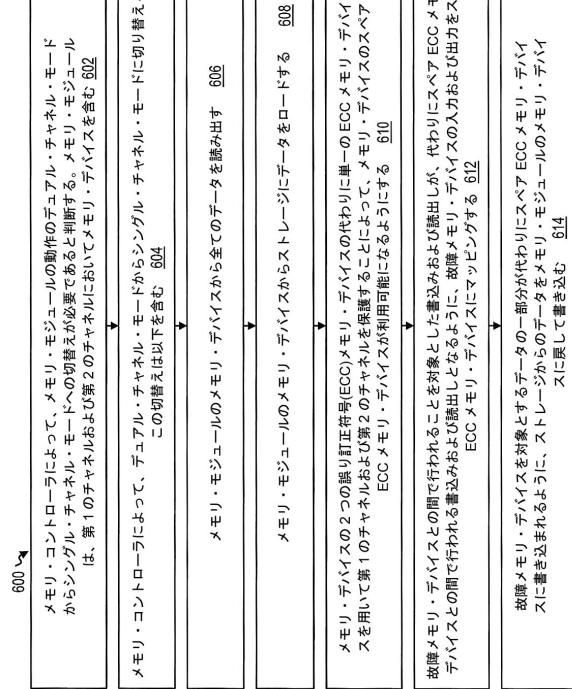

図 6 は、実施形態による、デュアル・チャネル・モードからシングル・チャネル・モードに切り替える方法のフロー・チャート 600 である。ブロック 602 において、メモリ・コントローラ 110 は、メモリ・モジュールの動作のデュアル・チャネル・モード (例えば、チャネル 0 およびチャネル 1 の双方を別個に動作させる) からシングル・チャネル・モードへの切替えが必要であると (例えば、回路 214 およびロジック 212 を介して) 判断するように構成される。メモリ・モジュール 100 は、第 1 のチャネル (例えば、チャネル 0) および第 2 のチャネル (例えば、チャネル 1) においてメモリ・デバイス 102A および 102B を含む。

#### 【0037】

ブロック 604 において、メモリ・コントローラ 110 は、デュアル・チャネル・モードからシングル・チャネル・モード (例えば、チャネル 0 および 1 の双方をシングル・チャネル 0 として動作させる) に切り替えるように構成される。この切替えは、(ブロック 606 において) メモリ・モジュール 100 のメモリ・デバイス 102A および 102B から全てのデータを読み出すことと、(ブロック 608 において) メモリ・モジュール 100 のメモリ・デバイス 102A および 102B からストレージ / メイン・メモリ 285

10

20

30

40

50

にデータをロードすることと、(ブロック 610において)メモリ・デバイス 102A、102B の 2 つの誤り訂正符号 (ECC) メモリ・デバイスの代わりに (ECC メモリ・デバイス 202A および 202B の双方の代わりに) 単一の ECC メモリ・デバイス 202A を用いて第 1 のチャネル 0 および第 2 のチャネル 1 を保護することによって、メモリ・デバイスのスペア ECC メモリ・デバイス 202B が利用可能になるようにすることと、(ブロック 612において) 故障メモリ・デバイスとの間で行われることを対象とした書込みおよび読出しが、代わりにスペア ECC メモリ・デバイス 202B との間で行われる書込みおよび読出しどのように、故障メモリ・デバイス (例えば、102A または 102B からのメモリ・デバイスのうちの 1 つ) の入力および出力を (例えば、マルチプレクサ・ネットワーク 280 を介して) スペア ECC メモリ・デバイス 202B にマッピングすることと、(ブロック 614において) 故障メモリ・デバイスを対象とするデータの一部 / 部分が代わりにスペア ECC メモリ・デバイス 202B に書き込まれるよう、ストレージ 285 からのデータをメモリ・モジュール 100 のメモリ・デバイス 102A および 102B に戻して書き込むこととを含む。

#### 【0038】

メモリ・コントローラ 110 は、メモリ・モジュール上でスペア・メモリ・デバイスが利用可能でないデュアル・チャネル・モードでの動作中に所定のトリガが生じることを認識することによって、メモリ・モジュールの動作をデュアル・チャネル・モードからシングル・チャネル・モードに切り替えることが必要であると判断するように構成される。所定のトリガは、メモリ・デバイスの任意の 1 つにおける 1 ビット誤り率が所定の閾値に達するときに生じる。故障メモリ・デバイスは、所定のトリガを発生させる。

#### 【0039】

技術的効果および利点は、標準メモリ・モジュールからスペア・メモリ・デバイスを提供するための構造および方法を含む。技術的効果および利点は、メモリ・コントローラが、標準的な DDR5 DIMM を用いているとき、7 ビット ECC 符号を用いた 2 つの 32 ビット・データ・チャネルのいずれかで実行され、8 ビット ECC 符号および 8 ビット・スペア・メモリ・デバイスを用いた単一の 64 ビット・チャネルに切り替えるように構成されることを含む。更に、技術的利点により、元々ロード・エンド・コンピュータ用に設計された RAS を有しない (すなわち、スペア・メモリ・デバイスがない) メモリ・モジュールが、ハイ・エンド・コンピュータのための RAS を有する (すなわち、スペア・メモリ・デバイスを有する) メモリ・モジュールとして利用されることを可能にする。

#### 【0040】

本発明は、任意の可能な技術的詳細レベルの統合における、システム、方法、またはコンピュータ・プログラム製品、あるいはその組合せであってよい。コンピュータ・プログラム製品は、プロセッサに本発明の態様を実行させるためのコンピュータ可読プログラム命令を有するコンピュータ可読記憶媒体を含むことができる。

#### 【0041】

コンピュータ可読記憶媒体は、命令実行デバイスによる使用のために命令を保持し記憶することができる有形のデバイスとすることができる。コンピュータ可読記憶媒体は、例えば、限定ではないが、電子記憶デバイス、磁気記憶デバイス、光記憶デバイス、電磁記憶デバイス、半導体記憶デバイス、またはこれらの任意の適切な組合せであり得る。コンピュータ可読記憶媒体のより具体的な例の非網羅的なリストは、ポータブル・コンピュータ・ディスクケット、ハード・ディスク、ランダム・アクセス・メモリ (RAM)、読み専用メモリ (ROM)、消去可能プログラマブル読み専用メモリ (EPROM またはフラッシュ・メモリ)、スタティック・ランダム・アクセス・メモリ (SRAM)、ポータブル・コンパクト・ディスク読み専用メモリ (CD-ROM)、デジタル多用途ディスク (DVD)、メモリ・スティック、フロッピー (R)・ディスク、パンチ・カード等の機械的に符号化されたデバイス、または命令が記録された溝の隆起構造、および上記の任意の適切な組合せを含む。本明細書で使用されるコンピュータ可読記憶媒体は、電波もしくは他の自由に伝播する電磁波、導波管もしくは他の伝送媒体を伝播する電磁波 (例えば、光

アイバ・ケーブルを通過する光パルス)、または、ワイヤを介して送信される電気信号等の一時的な信号自体であると解釈されるべきではない。

#### 【0042】

本明細書に記載のコンピュータ可読プログラム命令は、コンピュータ可読記憶媒体から、それぞれのコンピューティング/処理デバイスへ、または、例えばインターネット、ローカル・エリア・ネットワーク、広域ネットワーク、もしくはワイヤレスネットワーク、あるいはその組合せのようなネットワークを介して、外部コンピュータまたは外部記憶デバイスへダウンロードされ得る。ネットワークは、銅伝送ケーブル、光伝送ファイバ、ワイヤレス伝送、ルータ、ファイアウォール、スイッチ、ゲートウェイ・コンピュータ、またはエッジ・サーバ、あるいはその組合せを備え得る。各コンピューティング/処理デバイス内のネットワーク・アダプタ・カードまたはネットワーク・インターフェースは、ネットワークからコンピュータ可読プログラム命令を受信し、コンピュータ可読プログラム命令を、それぞれのコンピューティング/処理デバイス内のコンピュータ可読記憶媒体に記憶するために転送する。

10

#### 【0043】

本発明の動作を実行するためのコンピュータ可読プログラム命令は、アセンブラー命令、命令セット・アーキテクチャ (ISA) 命令、機械命令、機械依存命令、マイクロコード、ファームウェア命令、状態設定データ、集積回路用の構成データ、または、Smalltalk (R)、C++ 等のようなオブジェクト指向プログラミング言語、および「C」プログラミング言語もしくは類似のプログラミング言語等の手続型プログラミング言語を含む、1つまたは複数のプログラミング言語の任意の組合せで記述されたソース・コードまたはオブジェクト・コードのいずれかであり得る。コンピュータ可読プログラム命令は、完全にユーザのコンピュータ上、部分的にユーザのコンピュータ上、独立型ソフトウェア・パッケージとして、部分的にユーザのコンピュータ上および部分的にリモート・コンピュータ上で、または全体的にリモート・コンピュータもしくはサーバ上で実行することができる。後者のシナリオでは、リモート・コンピュータは、ローカル・エリア・ネットワーク (LAN) もしくは広域ネットワーク (WAN) を含む任意のタイプのネットワークを介してユーザのコンピュータに接続することができるか、または(例えば、インターネット・サービス・プロバイダを使用してインターネットを通じて)外部コンピュータに接続することができる。いくつかの実施形態では、例えばプログラマブル・ロジック回路、フィールド・プログラマブル・ゲート・アレイ (FPGA)、またはプログラマブル・ロジック・アレイ (PLA) を含む電子回路は、本発明の態様を実行するために、電子回路を個人化するためにコンピュータ可読プログラム命令の状態情報を利用することによってコンピュータ可読プログラム命令を実行し得る。

20

#### 【0044】

本発明の態様は、本明細書において、本発明の実施形態に従って、方法、装置(システム)、およびコンピュータ・プログラム製品のフロー・チャート図またはブロック図あるいはその両方を参照して説明される。フロー・チャート図またはブロック図あるいはその両方の各ブロック、ならびにフロー・チャート図またはブロック図あるいはその両方におけるブロックの組合せが、コンピュータ可読プログラム命令によって実装され得ることが理解されるであろう。

30

#### 【0045】

これらのコンピュータ可読プログラム命令は、コンピュータまたは他のプログラマブル・データ処理装置のプロセッサを介して実行される命令が、フロー・チャートまたはブロック図あるいはその両方の1つまたは複数のブロックに指定される機能/動作を実施する手段を作り出すように、汎用コンピュータ、専用コンピュータ、または他のプログラマブル・データ処理装置のプロセッサに提供されてマシンを作り出すものであってよい。これらのコンピュータ可読プログラム命令は、命令が記憶されたコンピュータ可読記憶媒体がフロー・チャートまたはブロック図あるいはその両方の1つまたは複数のブロックに指定される機能/動作の態様を実施する命令を含んでいる製造品を備えるように、コンピュ

40

50

タ可読記憶媒体に記憶され、コンピュータ、プログラマブル・データ処理装置、または他のデバイス、あるいはその組合せに特定の方式で機能するように指示することができるものであってもよい。

【0046】

コンピュータ可読プログラム命令は、コンピュータ、他のプログラム可能な装置、または他のデバイス上で実行される命令がフロー・チャートまたはブロック図あるいはその両方の1つまたは複数のブロックに指定される機能／動作を実装するように、コンピュータ実施プロセスをもたらすために、コンピュータ、他のプログラム可能なデータ処理装置、または他のデバイス上にロードされ、コンピュータ、他のプログラム可能な装置または他のデバイス上で一連の動作ステップを行わせるものであってもよい。

10

【0047】

図中のフロー・チャートおよびブロック図は、本発明の様々な実施形態によるシステム、方法、およびコンピュータ・プログラム製品の可能な実施のアーキテクチャ、機能、および動作を例示している。これに関して、フロー・チャートまたはブロック図における各ブロックは、指定された論理機能を実施するための1つまたは複数の実行可能命令を含むモジュール、セグメント、または命令の一部を表し得る。いくつかの代替的な実装形態では、ブロックに示されている機能は、図に示されている順序とは異なる順序で生じ得る。例えば、連続して図示されている2つのブロックは、実際には、実質的に同時に実行されてもよく、または関連する機能に応じて、場合によっては逆の順序で実行されてもよい。ブロック図、またはフロー・チャート図、あるいはその両方の各ブロック、およびブロック図、またはフロー・チャート図、あるいはその両方におけるブロックの組合せは、指定された機能または動作を実行する専用ハードウェア・ベースのシステムによって実施され得るか、または、専用ハードウェアとコンピュータ命令との組合せを実行し得ることにも留意されたい。

20

30

40

50

【図1】

【図2】

【図3】

【図4】

【図 5】

500 ↘

【図 6】

---

フロントページの続き

(72)発明者 マッキルベイン、ケヴィン

アメリカ合衆国 1 2 6 0 1 - 5 4 0 0 ニューヨーク州ポキプシー サウス・ロード 2 4 5 5

(72)発明者 マウレ、ウォーレン

アメリカ合衆国 7 8 7 5 8 - 3 4 9 3 テキサス州オースティン バーネット・ロード 1 1 4 0 0

(72)発明者 キム、キュ-ヒョン

アメリカ合衆国 1 0 5 9 8 ニューヨーク州ヨークタウン・ハイツ キッチャワン・ロード 1 1 0 1

(72)発明者 セツラマン、サラヴァナン

インド 5 6 0 0 4 5 バンガロール ラチェナハリ&ナガワラ・ビレッジ マニヤータ・エンバシー

アウター・リング・ロード

審査官 北村 学

(56)参考文献

特開 2 0 0 1 - 1 4 2 7 8 9 (JP, A)

特開 2 0 0 1 - 1 6 7 0 0 1 (JP, A)

特開 2 0 0 9 - 2 1 7 4 0 8 (JP, A)

特表 2 0 1 0 - 5 3 7 3 1 1 (JP, A)

特表 2 0 1 3 - 5 0 3 3 9 7 (JP, A)

米国特許出願公開第 2 0 1 7 / 0 1 9 9 8 3 0 (US, A1)

米国特許出願公開第 2 0 1 7 / 0 2 8 7 5 3 8 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

IPC G 0 6 F 3 / 0 6

G 0 6 F 1 1 / 0 8 - 1 1 / 1 0

G 0 6 F 1 1 / 1 6 - 1 1 / 2 0

G 0 6 F 1 2 / 0 0 - 1 2 / 0 6

G 0 6 F 1 3 / 1 6

G 1 1 C 7 / 0 0 - 8 / 2 0

G 1 1 C 1 1 / 4 0 1 - 1 1 / 4 0 9 9

G 1 1 C 1 4 / 0 0