(12) 发明专利

(10) 授权公告号 CN 109407190 B

(45) 授权公告日 2022.02.01

(21) 申请号 201810926942.0

(51) Int.CI.

(22) 申请日 2018.08.15

G02B 5/18 (2006.01)

(65) 同一申请的已公布的文献号

G02B 1/115 (2015.01)

申请公布号 CN 109407190 A

(56) 对比文件

(43) 申请公布日 2019.03.01

CN 106654858 A, 2017.05.10

(30) 优先权数据

CN 101140400 A, 2008.03.12

62/546,174 2017.08.16 US

15/837,990 2017.12.11 US

US 2008074748 A1, 2008.03.27

US 2004020892 A1, 2004.02.05

DE 102005020944 A1, 2005.12.01

(73) 专利权人 朗美通运营有限责任公司

审查员 张玥

地址 美国加利福尼亚州

(72) 发明人 约翰·迈克尔·米勒

斯蒂芬·拜格纳德

(74) 专利代理机构 北京安信方达知识产权代理

有限公司 11262

代理人 张瑞 杨明钊

权利要求书3页 说明书11页 附图14页

(54) 发明名称

衍射光学元件的多层薄膜堆叠

(57) 摘要

本申请涉及衍射光学元件的多层薄膜堆叠。光学元件可以包括衬底。光学元件可以包括形成在衬底上的用于特定波长范围的第一抗反射结构。光学元件可包括设置在第一抗反射结构的一部分上的至少一个层。光学元件可包括形成在该至少一个层上的用于该特定波长范围的第二抗反射结构。可以选择在第一抗反射结构的第一表面和第二抗反射结构的第二表面之间的深度、第一抗反射结构的第一折射率、第二抗反射结构的第二折射率和至少一层的第三折射率，以形成与特定波长的特定相位延迟相关联的衍射光学元件。

1. 一种光学元件，包括：

衬底；

第一抗反射结构，所述第一抗反射结构形成在所述衬底上，用于特定波长范围；

至少一个层，所述至少一个层设置在所述第一抗反射结构的一部分上；和

第二抗反射结构，所述第二抗反射结构形成在所述至少一个层上，用于所述特定波长范围，

其中，选择在所述第一抗反射结构的第一表面和所述第二抗反射结构的第二表面之间的深度、所述第一抗反射结构的第一折射率、所述第二抗反射结构的第二折射率和所述至少一个层的第三折射率，以形成与所述特定波长范围中包括的特定波长的特定相位延迟相关联的衍射光学元件，

其中，所述第二折射率不同于所述第三折射率，以及

其中，所述第一抗反射结构包括两个层，所述两个层具有彼此不同的相应折射率。

2. 根据权利要求1所述的光学元件，其中，所述第一抗反射结构形成在所述衬底的第一侧上；并且

所述光学元件还包括：

抗反射涂层，所述抗反射涂层形成在所述衬底的第二侧上。

3. 根据权利要求1所述的光学元件，其中，所述第一抗反射结构是用于蚀刻所述第二抗反射结构的蚀刻停止部。

4. 根据权利要求1所述的光学元件，其中，所述第一抗反射结构、所述第二抗反射结构或所述至少一个层中的至少一者使用薄膜沉积形成。

5. 根据权利要求1所述的光学元件，其中，所述第一抗反射结构包括第一硅层和第一二氧化硅层；

其中，所述至少一个层包括第二硅层；

其中，所述第二抗反射结构包括第二二氧化硅层；和

其中，所述特定波长范围在大约840纳米和860纳米之间。

6. 根据权利要求1所述的光学元件，其中，所述第一抗反射结构、所述第二抗反射结构和所述至少一个层由硅和二氧化硅的交替层形成。

7. 根据权利要求1所述的光学元件，其中，所述第一抗反射结构、所述第二抗反射结构和所述至少一个层由氢化硅和二氧化硅的交替层形成。

8. 根据权利要求1所述的光学元件，其中，所述第一抗反射结构由第一材料的第一层和第二材料的第二层形成；

其中，所述至少一个层由所述第一材料的第三层形成；和

其中，所述第二抗反射结构由所述第一层、所述第二层、所述第三层、所述第二材料的第四层和所述第一材料的第五层形成。

9. 根据权利要求1所述的光学元件，其中，所述第一抗反射结构形成在所述衬底的第一侧上；并且

所述光学元件还包括：

第三抗反射结构，所述第三抗反射结构形成在所述衬底的第二侧上，用于另一特定波长范围；

另外的至少一个层，所述另外的至少一个层设置在所述第三抗反射结构的一部分上；和

第四抗反射结构，所述第四抗反射结构形成在所述另外的至少一个层上，用于所述另一特定波长范围。

10. 根据权利要求1所述的光学元件，其中，所述第一抗反射结构和所述第二抗反射结构形成两级浮雕轮廓。

11. 根据权利要求1所述的光学元件，其中，所述第一抗反射结构包括第一硅层和第一二氧化硅层；

其中，所述至少一个层包括第二硅层；

其中，所述第二抗反射结构包括第二二氧化硅层；和

其中，所述特定波长范围在大约930纳米和950纳米之间。

12. 根据权利要求1所述的光学元件，其中，所述第一抗反射结构包括第一硅层和第一二氧化硅层；

其中，所述至少一个层包括第二硅层和第二二氧化硅层；

其中，所述第二抗反射结构包括第三硅层；和

其中，所述特定波长在大约1540纳米和1560纳米之间。

13. 根据权利要求1所述的光学元件，其中，所述特定波长在大约840纳米和940纳米之间。

14. 根据权利要求1所述的光学元件，其中，所述深度在 $\lambda/4$ 和 $\lambda/2$ 之间，

其中 $\lambda$ 表示所述特定波长。

15. 根据权利要求1所述的光学元件，其中，所述光学元件的有效折射率在2.0和3.0之间。

16. 根据权利要求1所述的光学元件，其中，所述特定相位延迟是 $\pi$ 相位延迟。

17. 根据权利要求1所述的光学元件，其中，所述特定相位延迟是非 $\pi$ 相位延迟。

18. 一种制造光学元件的方法，包括：

在晶片上沉积多个层，

其中，所述沉积在至少一个层和用于特定波长的第二抗反射结构之下形成用于所述特定波长的第一抗反射结构，所述至少一个层在所述第一抗反射结构的一部分上形成，

其中，所述第二抗反射结构的折射率不同于所述至少一个层的折射率，以及

其中，所述第一抗反射结构包括两个层，所述两个层具有彼此不同的相应折射率；和

蚀刻所述多个层中的层的子集以形成两级浮雕轮廓，

其中，所述蚀刻在所述第一抗反射结构和所述第二抗反射结构之间形成与所述特定波长的特定相位延迟相关联的衍射光学元件，以及

其中，所述第二抗反射结构形成在所述至少一个层的顶部上。

19. 根据权利要求18所述的方法，还包括：

将所述晶片切割成多个衍射光学元件。

20. 根据权利要求18所述的方法，其中，在所述第一抗反射结构和所述第二抗反射结构之间形成所述至少一个层。

21. 一种制造光学元件的方法，包括：

使用薄膜沉积技术将多个薄膜沉积到晶片上，沉积所述多个薄膜包括沉积用于特定波长的第一抗反射结构和在沉积所述第一抗反射结构之后沉积用于所述特定波长的第二抗反射结构；在所述多个薄膜的表面上沉积掩模；基于限定所述晶片的多个区域的一组确定的转变点来图案化所述掩模；基于所述掩模蚀刻所述多个薄膜中的薄膜的子集以形成两级浮雕轮廓，其中，所述蚀刻在所述第一抗反射结构和所述第二抗反射结构之间形成与所述特定波长的 $\pi$ 相位延迟相关联的衍射光学元件，以及其中，所述第一抗反射结构包括两个层，所述两个层具有彼此不同的相应折射率；和去除所述掩模，以及其中，在所述第一抗反射结构的一部分上以及在所述第一抗反射结构和所述第二抗反射结构之间形成至少一个层，以及其中，所述第二抗反射结构的折射率不同于所述至少一个层的折射率。

22. 根据权利要求21所述的方法，还包括：

将所述晶片切割成多个衍射光学元件。

23. 根据权利要求21所述的方法，还包括：

在所述晶片的另一侧上形成另外的衍射光学元件，所述另外的衍射光学元件在所述另外的衍射光学元件的第三抗反射结构和第四抗反射结构之间与所述特定波长的 $\pi$ 相位延迟有关。

## 衍射光学元件的多层薄膜堆叠

### 技术领域

[0001] 本公开涉及薄膜堆叠。更具体地，本公开的一些方面涉及一种用于衍射光学元件(DOE)的多层薄膜堆叠，该衍射光学元件在多层薄膜堆叠的蚀刻区域和未蚀刻区域之间提供特定相位延迟，并且为特定波长范围提供抗反射(anti-reflectance)涂层。

### [0002] 背景

[0003] 衍射光学元件(DOE)可用于引导光束。例如，诸如衍射透镜、点阵(spot array)照明器、点阵发生器、傅立叶阵列发生器等的DOE可用于分割光束、成形光束、聚焦光束等。DOE可以集成到多播开关、波长选择开关、手势识别系统、运动感测系统等中。

[0004] 可以为表面浮雕DOE选择多级表面浮雕轮廓(profile)。例如，可以为表面浮雕DOE选择两级(有时称为“二元”)表面浮雕轮廓。可以选择多级表面浮雕轮廓来近似连续表面浮雕轮廓，并使得能够使用光刻程序和/或蚀刻程序来制造DOE。两级薄膜堆叠可用于产生单阶(order)二元DOE，例如衍射透镜。用于DOE的一些材料可能需要大于阈值的蚀刻深度，从而导致制造DOE的阈值蚀刻时间。

### [0005] 概述

[0006] 本申请的实现方式主要包括以下方面：

[0007] (1) 一种光学元件可以包括衬底。光学元件可以包括形成在衬底上的用于特定波长范围的第一抗反射结构。光学元件可包括设置在第一抗反射结构的一部分上的至少一个层。光学元件可包括形成在该至少一个层上的用于特定波长范围的第二抗反射结构。可以选择第一抗反射结构的第一表面和第二抗反射结构的第二表面之间的深度、第一抗反射结构的第一折射率、第二抗反射结构的第二折射率和该至少一个层的第三折射率，以形成与特定波长的特定相位延迟相关联的衍射光学元件。

[0008] (2) 根据(1)所述的光学元件，其中，所述第一抗反射结构形成在所述衬底的第一侧上；并且所述光学元件还包括：抗反射涂层，所述抗反射涂层形成在所述衬底的第二侧上。

[0009] (3) 根据(1)所述的光学元件，其中，所述第一抗反射结构是用于蚀刻所述第二抗反射结构的蚀刻停止部。

[0010] (4) 根据(1)所述的光学元件，其中，所述第一抗反射结构、所述第二抗反射结构或所述至少一个层中的至少一者使用薄膜沉积形成。

[0011] (5) 根据(1)所述的光学元件，其中，所述第一抗反射结构包括第一硅层和第一二氧化硅层；其中，所述至少一个层包括第二硅层；其中，所述第二抗反射结构包括第二二氧化硅层；和其中，所述特定波长范围在大约840纳米和860纳米之间。

[0012] (6) 根据(1)所述的光学元件，其中，所述第一抗反射结构、所述第二抗反射结构和所述至少一个层由硅和二氧化硅的交替层形成。

[0013] (7) 根据(1)所述的光学元件，其中，所述第一抗反射结构、所述第二抗反射结构和所述至少一个层由氢化硅和二氧化硅的交替层形成。

[0014] (8) 根据(1)所述的光学元件，其中，所述第一抗反射结构由第一材料的第一层和

第二材料的第二层形成；其中，所述至少一层由所述第一材料的第三层形成；和其中，所述第二抗反射结构由所述第一层、所述第二层、所述第三层、所述第二材料的第四层和所述第一材料的第五层形成。

[0015] (9) 根据(1)所述的光学元件，其中，所述第一抗反射结构形成在所述衬底的第一侧上；并且所述光学元件还包括：第三抗反射结构，所述第三抗反射结构形成在所述衬底的第二侧上，用于另一特定波长；另外的至少一个层，所述另外的至少一个层设置在所述第三抗反射结构的一部分上；和第四抗反射结构，所述第四抗反射结构形成在所述其他的至少一个层上，用于所述其他的特定波长。

[0016] (10) 根据(1)所述的光学元件，其中，所述第一抗反射结构和所述第二抗反射结构形成两级浮雕轮廓。

[0017] (11) 根据(1)所述的光学元件，其中，所述第一抗反射结构包括第一硅层和第一二氧化硅层；其中，所述至少一个层包括第二硅层；其中，所述第二抗反射结构包括第二二氧化硅层；和其中，所述特定波长范围在大约930纳米和950纳米之间。

[0018] (12) 根据(1)所述的光学元件，其中，所述第一抗反射结构包括第一硅层和第一二氧化硅层；其中，所述至少一个层包括第二硅层和第二二氧化硅层；其中，所述第二抗反射结构包括第三硅层；和其中，所述特定波长在大约1540纳米和1560纳米之间。

[0019] (13) 根据(1)所述的光学元件，其中，所述特定波长在大约840纳米和940纳米之间。

[0020] (14) 根据(1)所述的光学元件，其中，所述深度在 $\lambda/4$ 和 $\lambda/2$ 之间，其中 $\lambda$ 表示所述特定波长。

[0021] (15) 根据(1)所述的光学元件，其中，所述光学元件的有效折射率在2.0和3.0之间。

[0022] (16) 根据(1)所述的光学元件，其中，所述特定相位延迟是 $\pi$ 相位延迟。

[0023] (17) 根据(1)所述的光学元件，其中，所述特定相位延迟是非 $\pi$ 相位延迟。

[0024] (18) 一种方法，可以包括在晶片上沉积多个层。沉积可以在关于特定波长的第二抗反射结构之下形成关于该特定波长的第一抗反射结构。该方法可以包括蚀刻多个层中的层的子集以形成两级浮雕轮廓。蚀刻可以在第一抗反射结构和第二抗反射结构之间形成与特定波长的特定相位延迟相关联的衍射光学元件。

[0025] (19) 根据(18)所述的方法，还包括：将所述晶片切割成多个衍射光学元件。

[0026] (20) 根据(18)所述的方法，其中，所述第二抗反射结构形成在所述第一抗反射结构的顶部上。

[0027] (21) 根据(18)所述的方法，其中，在所述第一抗反射结构和所述第二抗反射结构之间形成至少一个层。

[0028] (22) 一种方法，可以包括使用薄膜沉积技术将多个薄膜沉积到晶片上。沉积多个薄膜可以包括沉积关于特定波长的第一抗反射结构，以及在沉积第一抗反射结构之后沉积关于特定波长的第二抗反射结构。该方法可包括基于限定晶片的多个区域的一组确定的转变点来图案化掩模。该方法可包括基于掩模来蚀刻多个薄膜中的薄膜子集以形成两级浮雕轮廓。蚀刻可以在第一抗反射结构和第二抗反射结构之间形成与特定波长的 $\pi$ 相位延迟相关联的衍射光学元件。该方法可以包括去除掩模。

- [0029] (23) 根据(22)所述的方法,还包括:将所述晶片切割成多个衍射光学元件。

- [0030] (24) 根据(22)所述的方法,还包括:在所述晶片的另一侧上形成另外的衍射光学元件,所述另外的衍射光学元件在所述其他的衍射光学元件的第三抗反射结构和第四抗反射结构之间与所述特定波长的π相位延迟有关。

- [0031] (25) 根据(22)所述的方法,其中,在所述第一抗反射结构和所述第二抗反射结构之间形成至少一个层。

## 附图说明

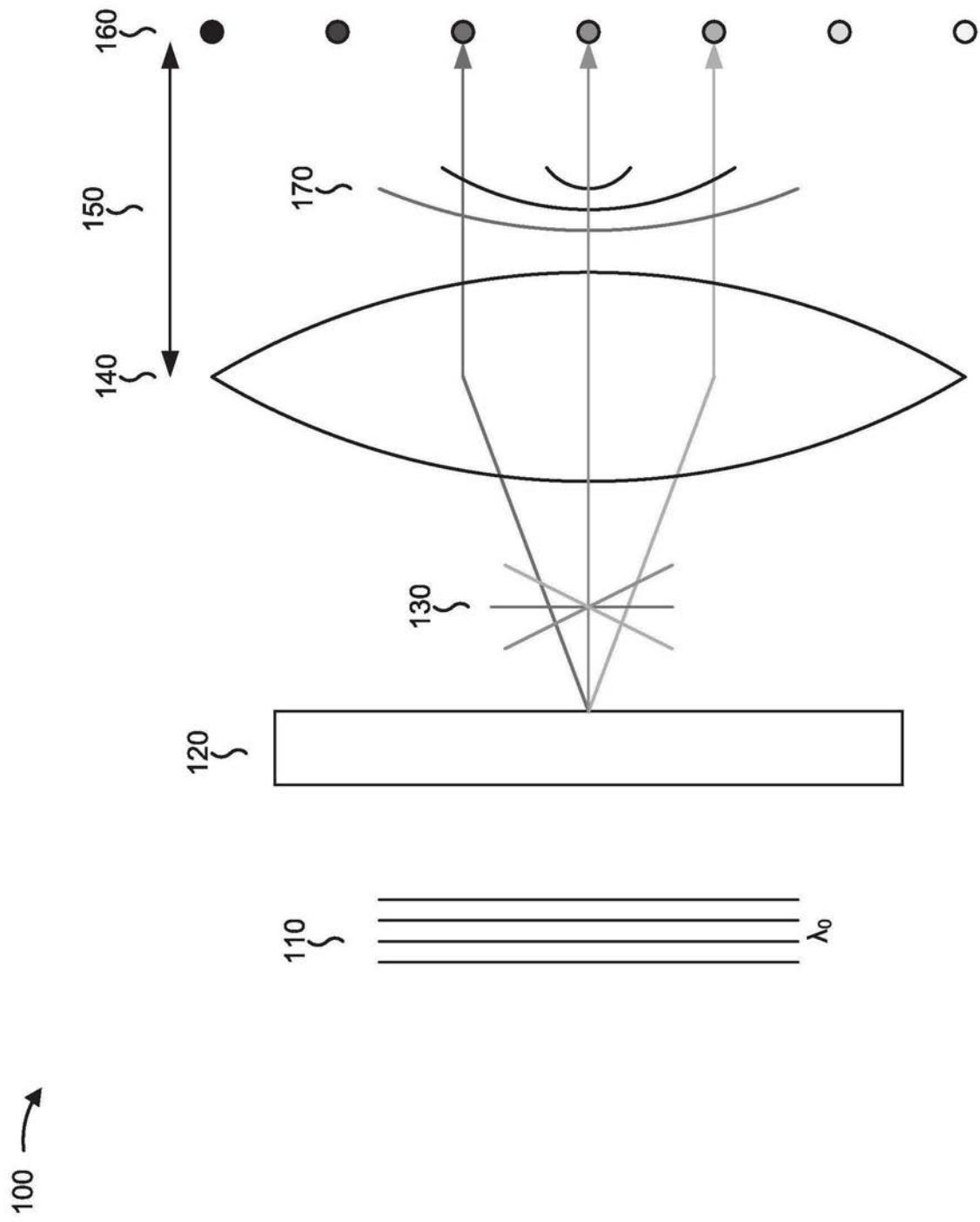

- [0032] 图1是本文描述的示例实现方式的概略图;

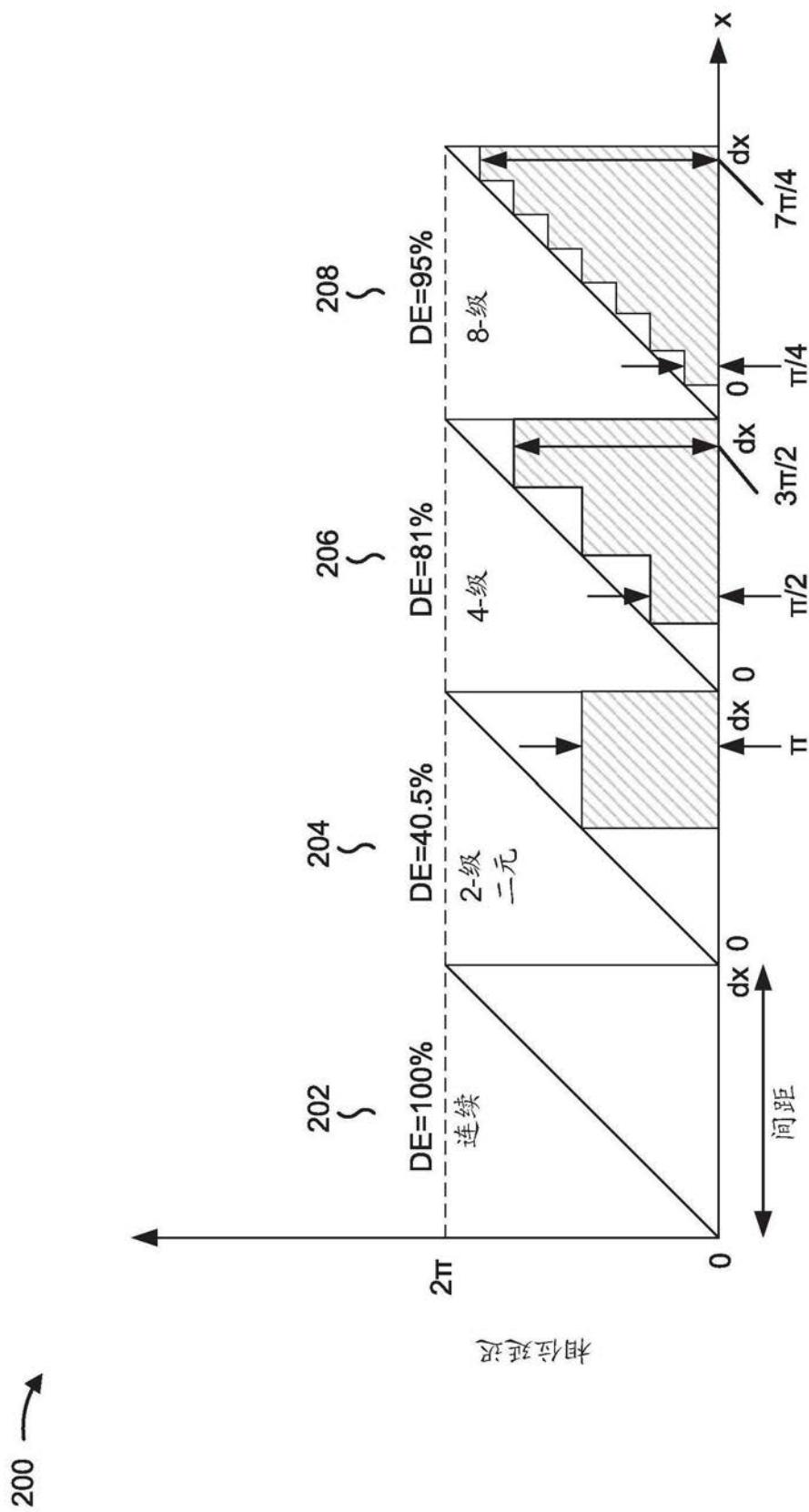

- [0033] 图2A和2B是与本文描述的示例实现方式相关的特性的简图;

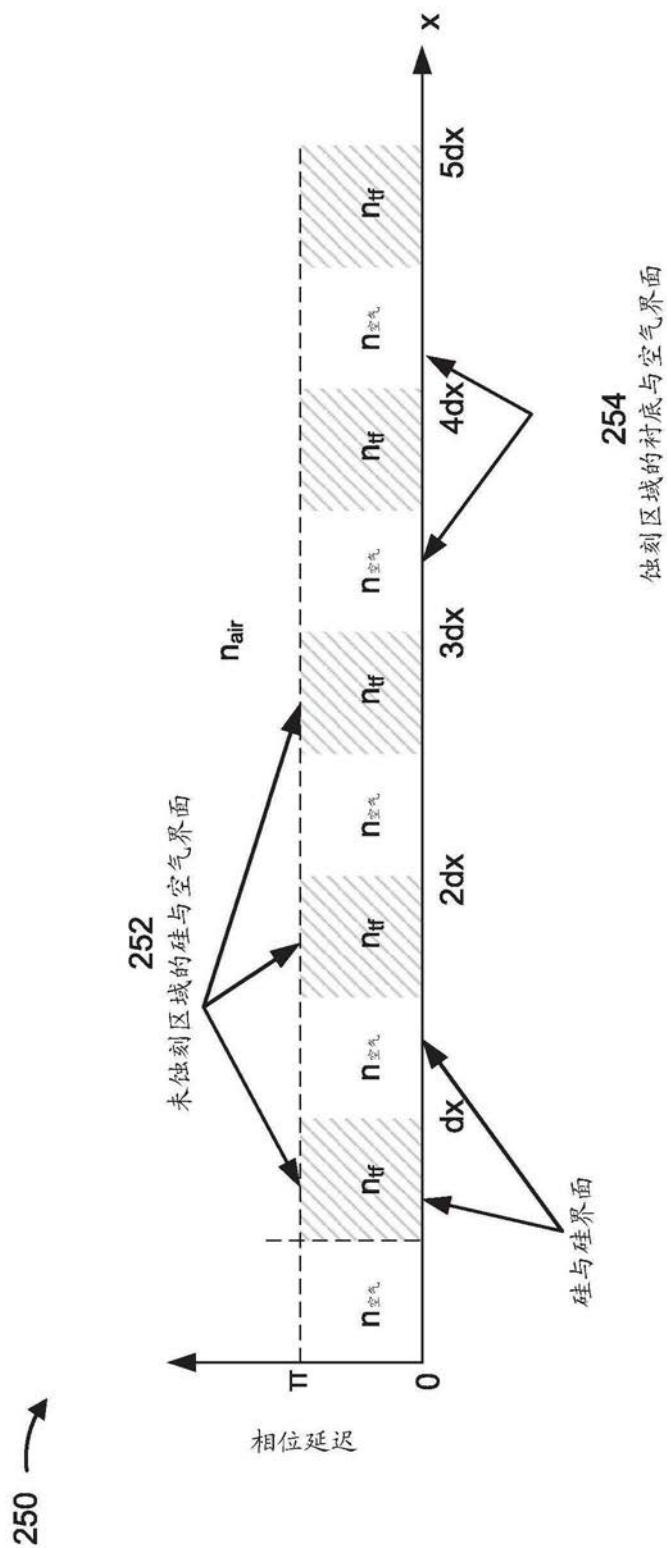

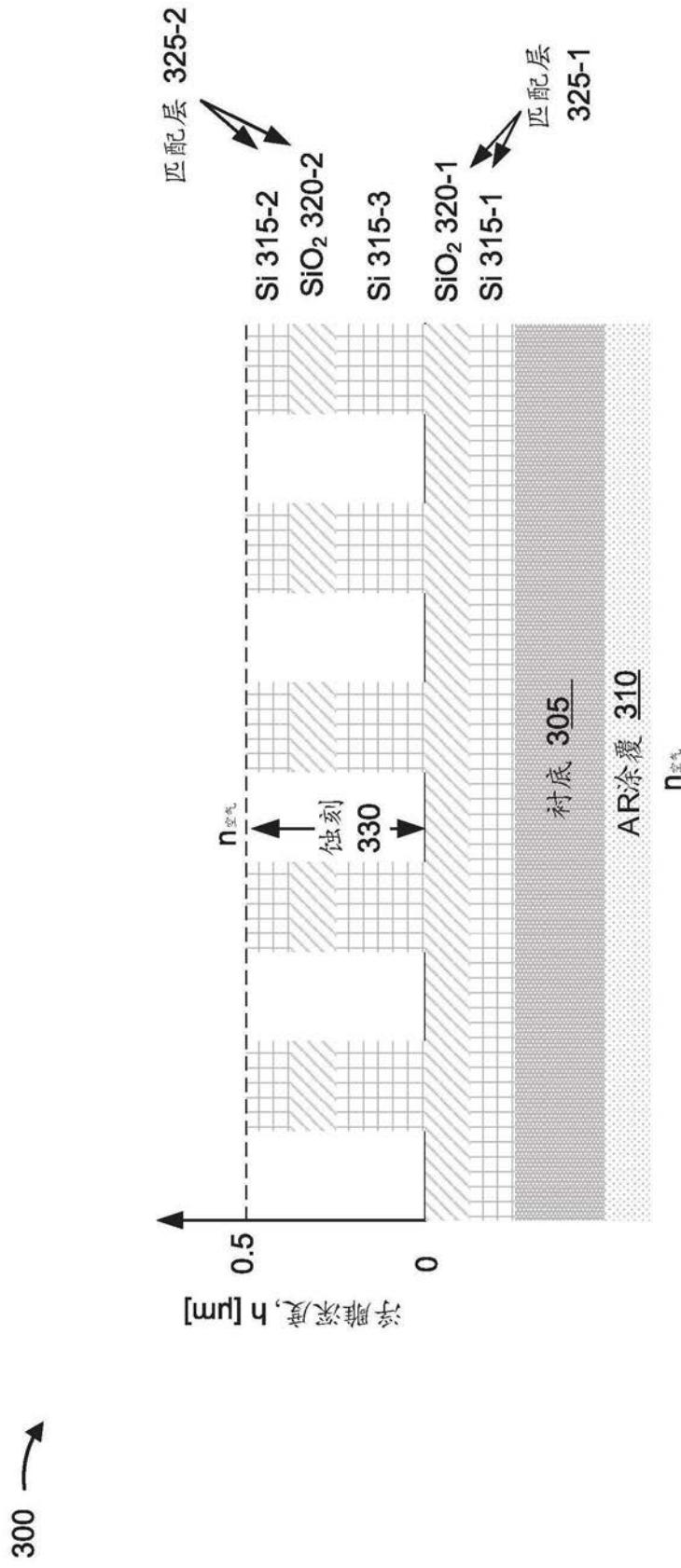

- [0034] 图3A和3B是与本文描述的示例实现方式相关的特性的简图;

- [0035] 图4A-4C是本文描述的示例实现方式的简图;

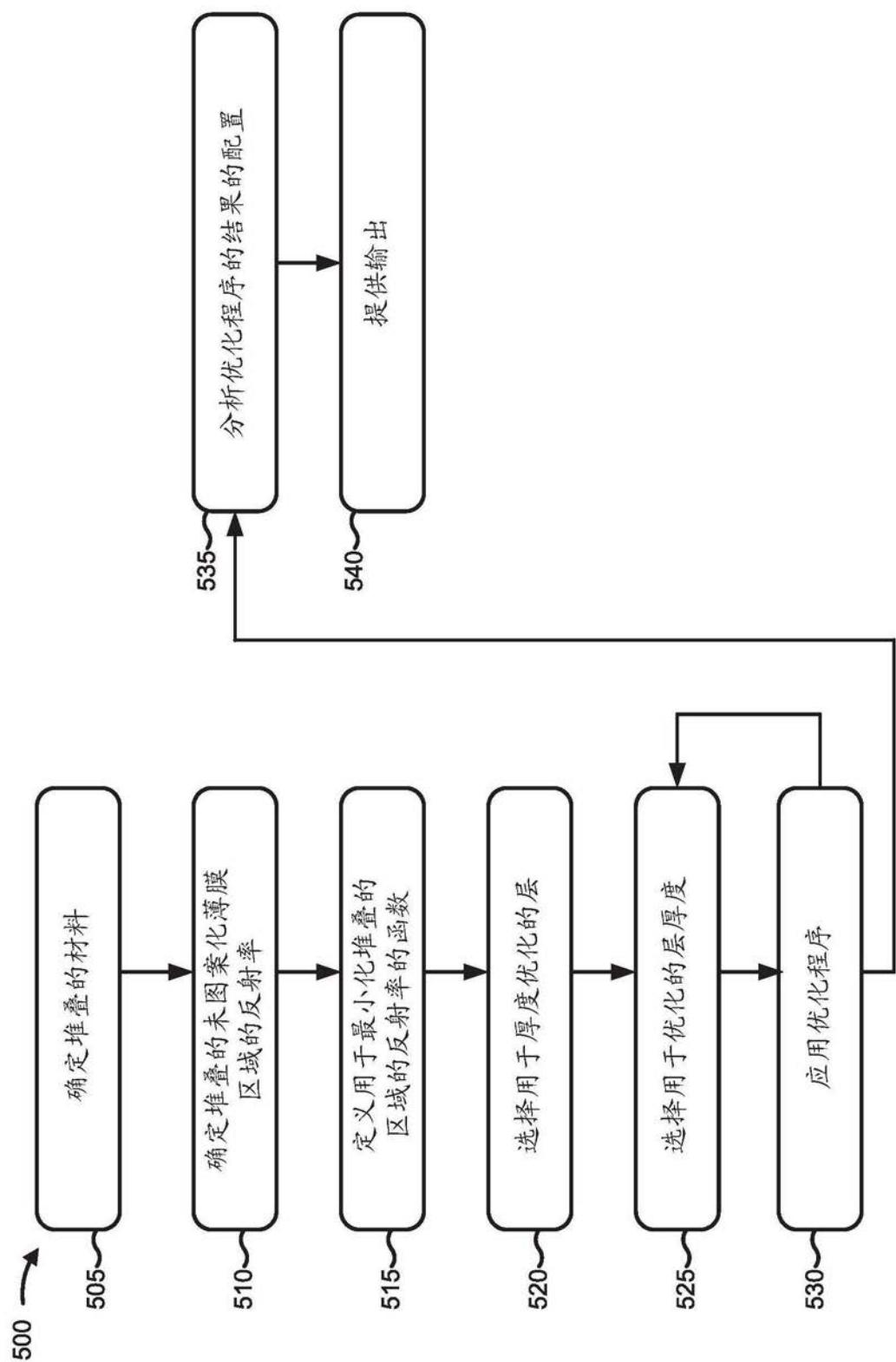

- [0036] 图5是用于配置本文描述的示例实现方式的示例过程的流程图;

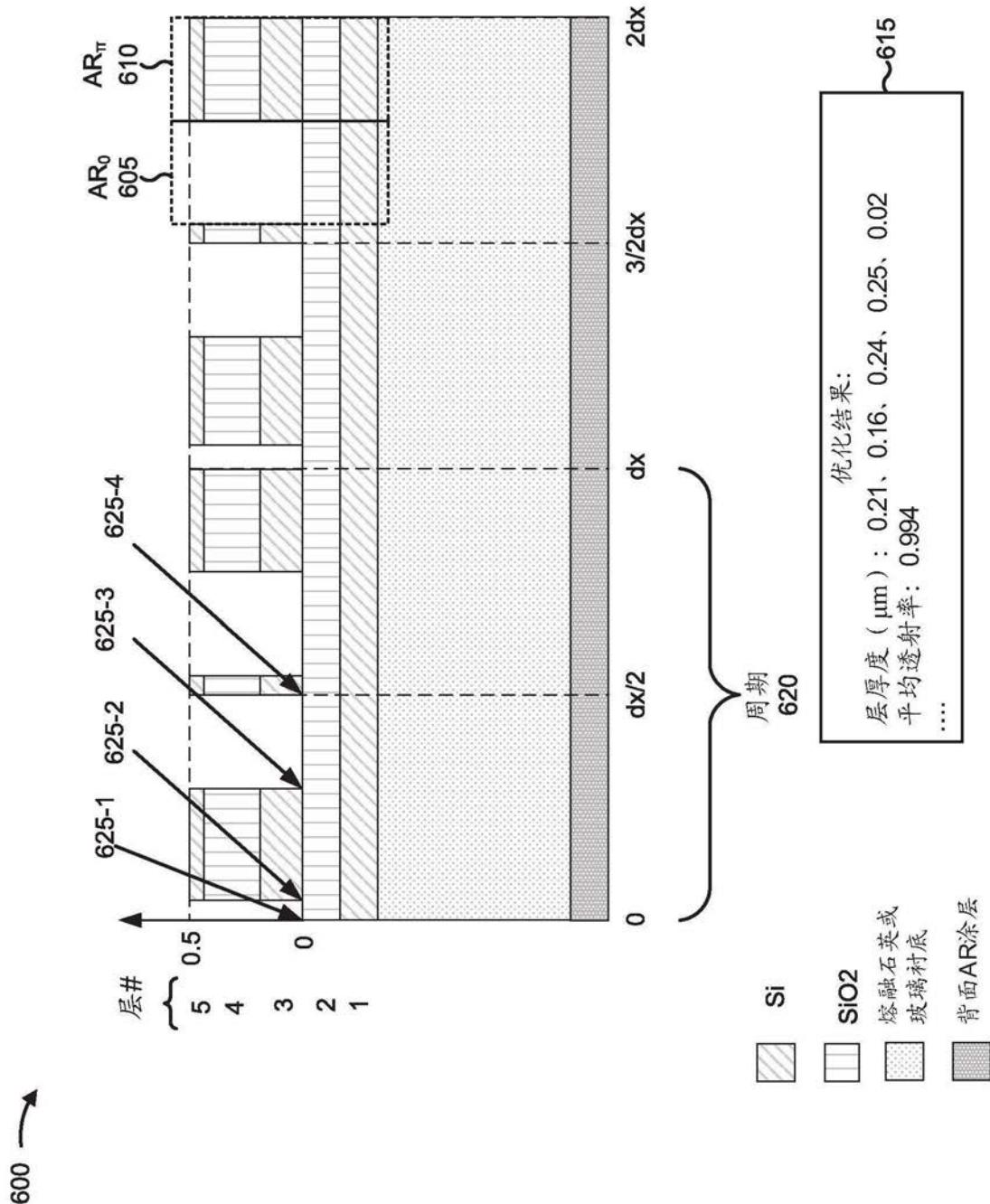

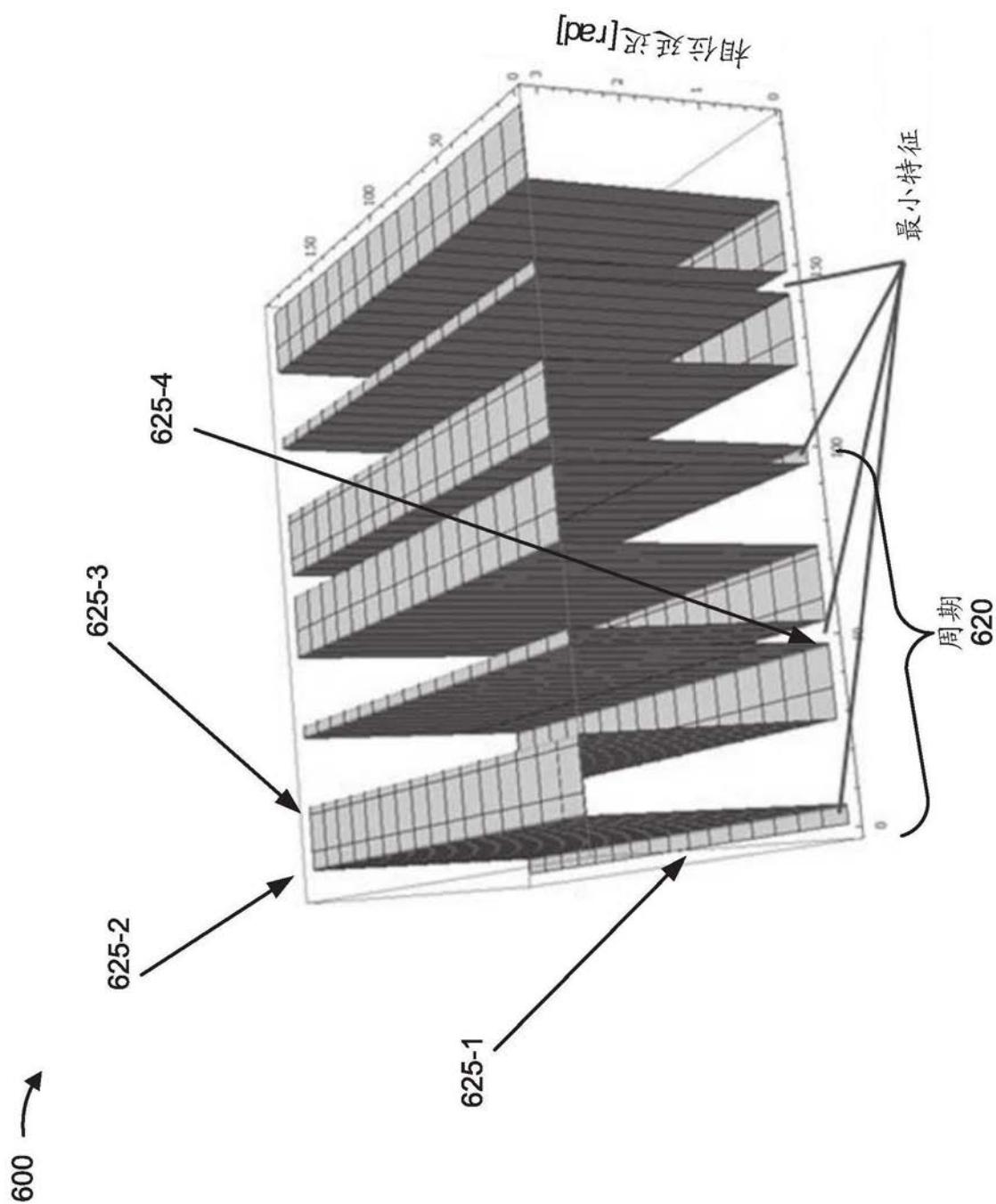

- [0037] 图6A和6B是与图5所示的示例过程相关的示例实现方式的简图;

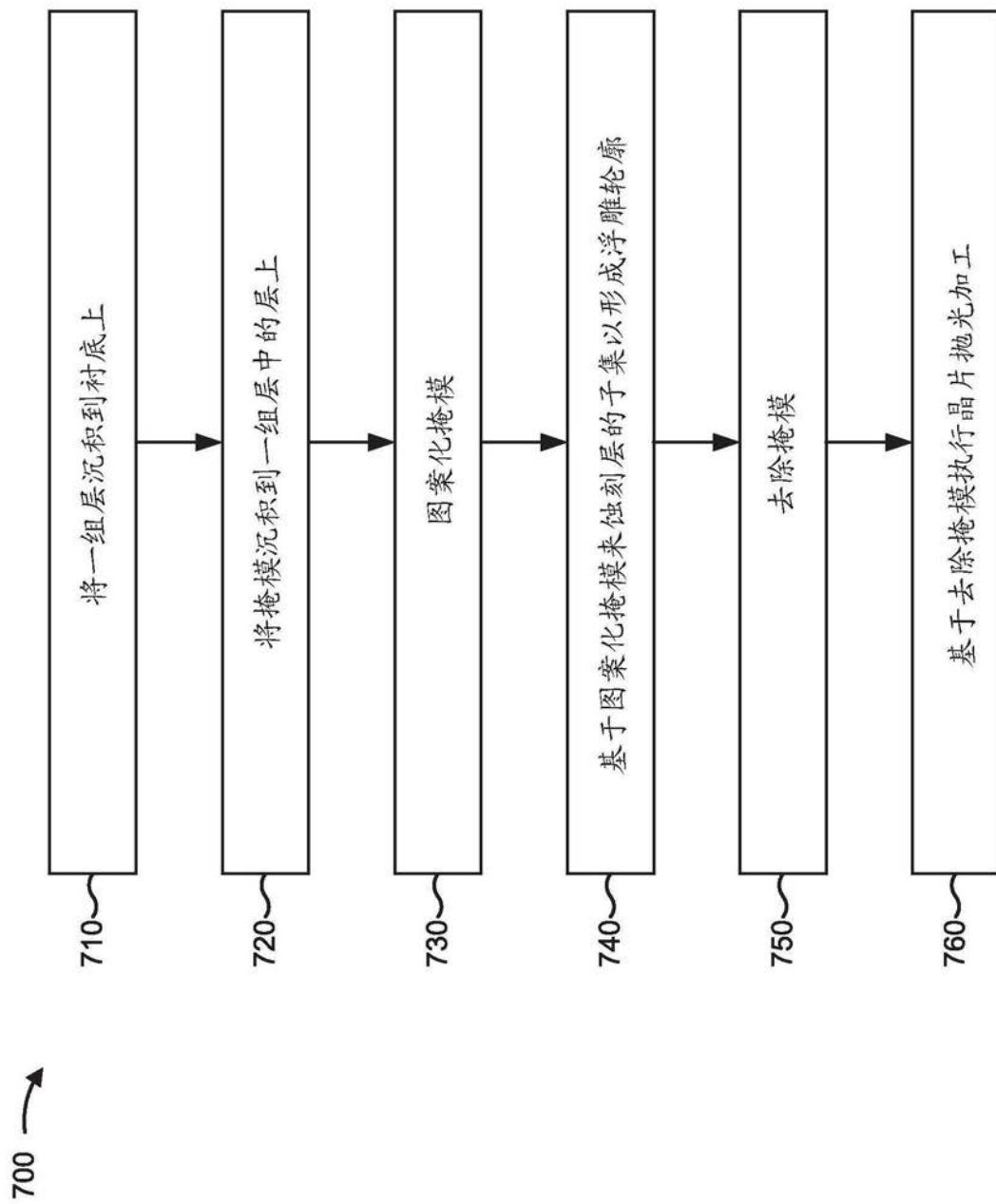

- [0038] 图7是用于制造本文描述的示例实现方式的示例过程的流程图;和

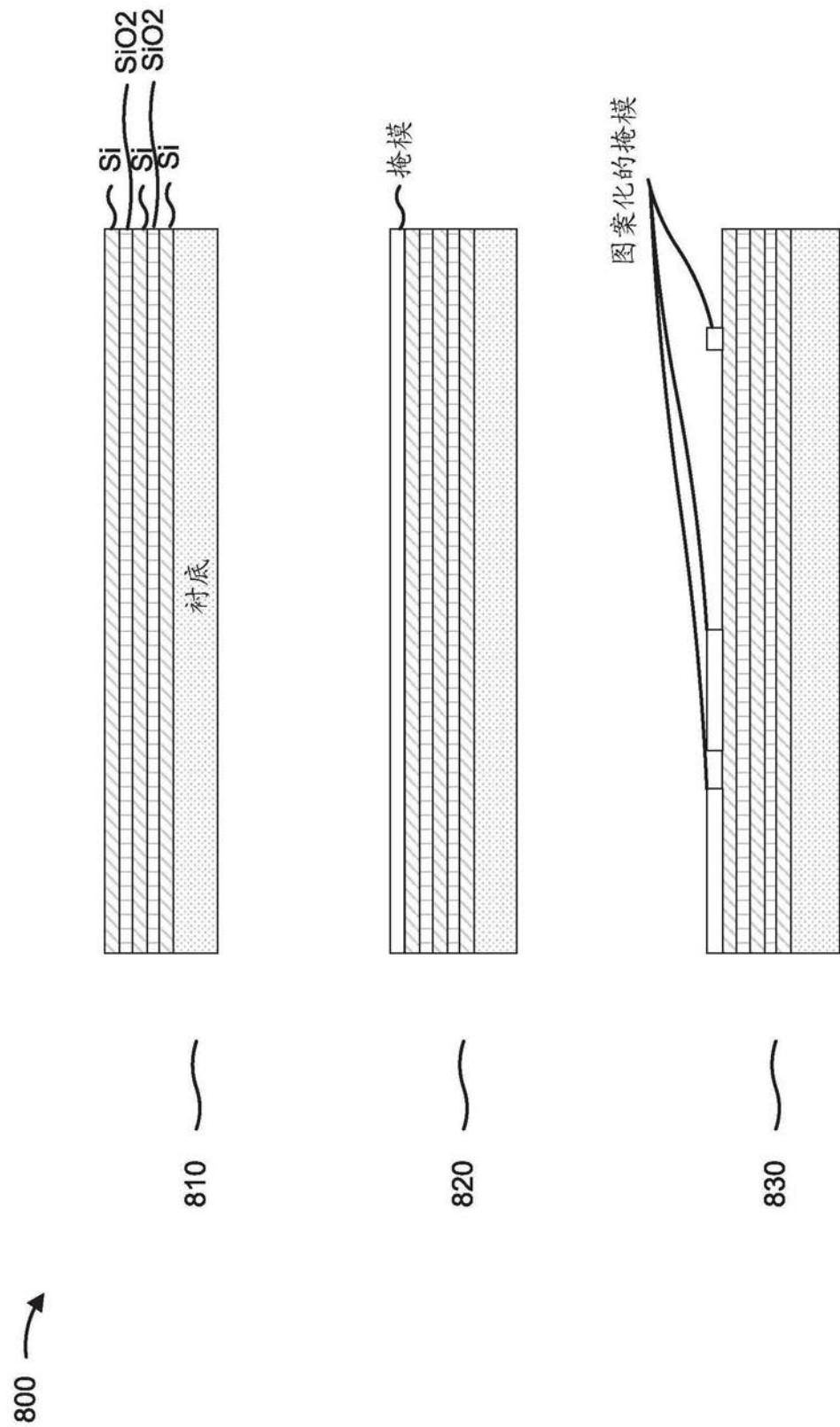

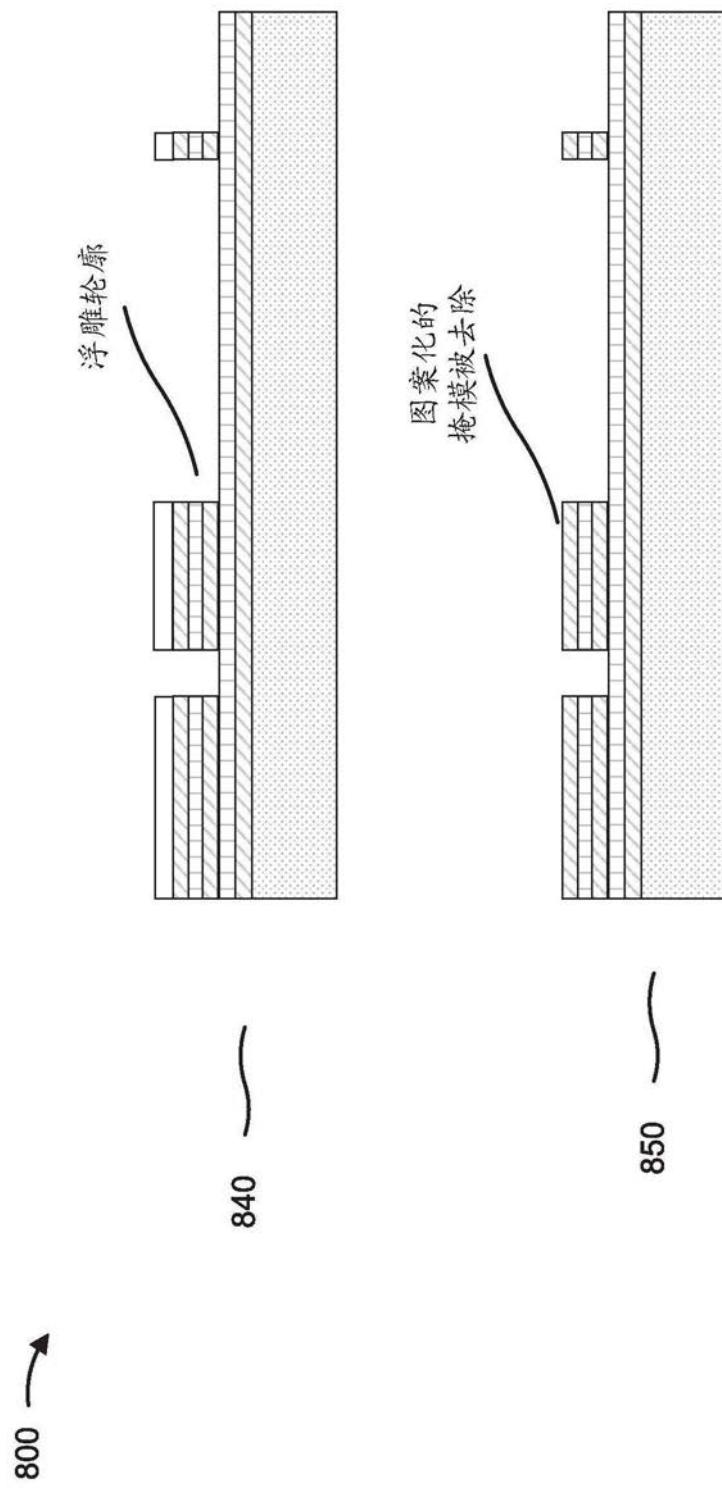

- [0039] 图8A和8B是与图7所示的示例过程相关的示例实现方式的简图。

- [0040] 详细描述

- [0041] 下面的示例实现方式的详细描述参考附图。在不同的附图中的相同的参考标记可指代相同或相似的元素。

[0042] 衍射光学元件(DOE)可以使用光刻程序和/或蚀刻程序制造。例如,为了近似连续表面浮雕轮廓,可以为DOE选择多级表面浮雕轮廓,并且可以蚀刻或图案化DOE的表面以形成多级表面浮雕轮廓。多级表面浮雕轮廓可用于为通过DOE的光束产生相位延迟。对于单阶二元DOE,例如衍射透镜,使用二元级表面浮雕轮廓可以获得大约40%的衍射效率。然而,该衍射效率可以小于阈值,这对于在光学系统中使用DOE是必需的,所述光学系统例如是光学通信系统、手势识别系统、运动检测系统等。此外,在一些系统中,降低光学系统的0阶以避免例如在手势识别系统中引起眼睛损伤可能是有利的。

[0043] 本文描述的一些实现方式可以提供具有阈值衍射效率的两级DOE。例如,本文描述的一些实现方式可以提供具有阈值特征尺寸(例如,波长的阈值量)的两级(也称为“二元”)DOE,以在DOE的各部分之间提供π相位延迟。此外,DOE可与蚀刻深度相关联以制造小于阈值的选定的表面浮雕轮廓,从而导致(相对于制造DOE的其它技术)DOE的减小的长宽比、减小的蚀刻时间和/或减小的制造成本。此外,DOE的层可以为DOE提供抗反射功能、可以为DOE提供集成蚀刻停止、可以包括为DOE的特定操作波长范围选择的材料等。本文描述的一些实现方式可以提供用于配置和/或制造DOE的方法。基于使用薄膜沉积技术,可以以更高的精度控制相位延迟,这可以减少光学系统的0阶。例如,薄膜沉积技术可以与小于1%、小于0.5%、小于0.2%、小于0.1%等的公差相关联。具有类似受控公差的其它制造技术也可用于构造本文所述的DOE。

[0044] 图1是本文描述的示例实现方式的概略图100。图1示出了使用表面浮雕DOE光栅和会聚透镜作为点阵照明器(有时称为点阵发生器)的点阵产生的示例。

[0045] 如图1所示,波长 $\lambda_0$ 的入射平面波110指向表面浮雕DOE光栅120。在一些实现方式

中,表面浮雕DOE光栅120可以是具有多级表面浮雕轮廓的DOE,例如两级DOE(有时称为二元DOE)。在一些实现方式中,表面浮雕DOE光栅120可以包括例如硅(Si)和二氧化硅(SiO<sub>2</sub>)的交替层、氢化硅(Si:H)和二氧化硅的交替层等。在一些实现方式中,表面浮雕DOE光栅120的层可以被配置成在表面浮雕DOE光栅120的蚀刻区域和表面浮雕DOE光栅120的未蚀刻区域中提供抗反射功能。在一些实现方式中,表面浮雕DOE光栅120的层(例如,二氧化硅层)可以在表面浮雕DOE光栅120的制造期间提供蚀刻停止功能。在一些实现方式中,入射平面波110可以具有从大约800纳米(nm)到大约1100纳米、大约800纳米到大约1000纳米、大约830纳米到大约1000纳米、大约850纳米到大约1000纳米、大约915纳米到大约1000纳米、大约940纳米到大约1000纳米等的波长范围。本文描述了关于表面浮雕DOE光栅120的附加细节。

[0046] 如图1进一步所示,表面浮雕DOE光栅120衍射入射平面波110,并将波前130(例如,入射平面波110的衍射阶)导向会聚透镜140。会聚透镜140与焦平面160隔开焦距150。在一些实现方式中,示例实现方式100可以用于手势识别系统,并且焦平面160可以是手势识别的目标。另外或替代地,焦平面160可以是对象(例如,用于运动感测系统)、通信目标(例如,用于光通信系统)等。

[0047] 如图1进一步所示,基于会聚透镜140改变波前130的定向以形成波前170,波前170被导向焦平面160,从而在焦平面160处形成多点阵图案。在一些实现方式中,表面浮雕DOE光栅120可用于创建一维点阵。在一些实现方式中,表面浮雕DOE光栅120可用于创建二维点阵。这样,表面浮雕DOE光栅可用作点阵照明器,以在焦平面160处根据入射平面波110创建点阵,从而实现手势识别系统、运动感测系统、光学通信系统等。

[0048] 如上所述,图1仅作为示例提供。其它示例是可能的,并且可以不同于关于图1描述的示例。

[0049] 图2A和2B分别是与DOE相关的特性相关联的简图200和250。如图2A所示,且通过简图200,可以将连续浮雕轮廓量化为一系列离散级,以使得光刻和/或蚀刻程序能够用于制造DOE。

[0050] 如图2A并且通过附图标记202进一步示出的,连续浮雕轮廓可以与大约100%的衍射效率相关联(对于单阶配置),并且可以提供相对于第一间距位置0从第二间距位置dx的2π的连续增加的相位延迟。如附图标记204所示,连续浮雕轮廓可以由两级浮雕轮廓(有时称为二元浮雕轮廓)近似。两级二元浮雕轮廓可以与大约40.5%的衍射效率相关联(对于单阶配置),并且可以提供相对于DOE从间距位置0到间距位置0.5dx的第一区域,在DOE从间距位置0.5dx到间距位置dx的第二区域处的π相位延迟。

[0051] 如图2A并且通过附图标记206进一步所示,连续浮雕轮廓可以由4级浮雕轮廓近似。4级浮雕轮廓可以与大约81%的衍射效率相关联(对于单阶配置),并且可以提供相对于DOE从0到0.25dx的第一区域,在DOE从间距位置0.25dx到间距位置0.5dx的第二区域处的π/2相位延迟;相对于DOE的第一区域,在DOE从0.5dx到0.75dx的第三区域处的π相位延迟;以及相对于DOE的第一区域,在DOE从0.75dx到dx的第四区域处的3π/2相位延迟。

[0052] 如图2A并且通过附图标记208进一步所示,连续浮雕轮廓可以由8级浮雕轮廓近似。8级浮雕轮廓可以与大约95%的衍射效率相关联(对于单阶配置),并且可以在DOE的区域提供π/4增量的相位延迟(例如,相对于DOE从0到0.125dx的第一区域,在从0.125dx到0.25dx的第二区域处的π/4;在从0.25dx到0.375dx的第三区域的π/2;在从0.375dx到0.5dx

的第四区域的 $3\pi/4$ ;等等)。在一些实现方式中,可以使用具有另一衍射效率的另一配置。例如,相对于单阶配置,使用2阶、4阶、10阶、100阶、数千阶等的配置可以用于增加衍射效率。在这种情况下,例如对于 $+/-100$ 阶,对于两级浮雕轮廓,可以获得大约65%至80%的衍射效率。

[0053] 如图2B并且通过简图250所示,两级浮雕轮廓可用于具有多个未蚀刻区域252和蚀刻区域254的DOE。在一些实现方式中,未蚀刻区域252可与相对于蚀刻区域254的 $\pi$ 相位延迟相关联。在一些实现方式中,未蚀刻区域252可与用于硅(Si)与空气界面的薄膜折射率 $n_{tf}$ 相关联。在一些实现方式中,蚀刻区域254可以与无相位延迟相关联。换句话说,未蚀刻区域252与相对于蚀刻区域254的 $\pi$ 相位延迟相关联。在一些实现方式中,蚀刻区域254与衬底(例如硅)到空气界面的折射率 $n_{air}$ 相关联。在一些实现方式中,蚀刻区域254和未蚀刻区域252的每一组可以共同与宽度 $dx$ 相关联,并且DOE可以与 $N*dx$ 的总宽度相关联,其中N是表示蚀刻区域254和未蚀刻区域252的组的数量的整数值(例如,1、2、3、4、5等)。

[0054] 如上所述,图2A和2B仅作为示例提供。其它示例是可能的,并且可以不同于关于图2A和2B描述的示例。

[0055] 图3A和3B是与关于DOE的特性相关联的简图。示出DOE 300的图3A对应于图2B中的DOE的两级浮雕轮廓,其可以被配置为提供 $\pi$ 相位延迟。

[0056] 如图3A所示,DOE 300可以包括衬底305。在一些实现方式中,衬底305可以是玻璃衬底、熔融石英衬底等。例如,衬底305可以是厚度约为200毫米、且折射率 $n_{衬底}$ 为1.45的熔融石英衬底。在一些实现方式中,抗反射涂层310可以设置在衬底305的表面上。例如,如图3A所示,一组交替的硅和二氧化硅层可设置在衬底305的顶表面上,并被图案化以形成浮雕轮廓,如本文所述,以及抗反射涂层310可覆盖衬底305的底表面。

[0057] 如图3A进一步所示,一组硅层315和一组二氧化硅层320可以设置在衬底305的顶表面上。例如,硅层315-1可以设置在衬底305上,以及二氧化硅层320-1可以设置在硅层315-1上。硅层315-1和二氧化硅层320-1可以形成一对匹配层325-1。类似地,硅层315-2可以设置在二氧化硅层320-2上,并且可以形成一对匹配层325-2。如图所示,硅层315-3可以设置在匹配层325-1和匹配层325-2之间。

[0058] 在一些实现方式中,匹配层325-1和匹配层325-2可形成抗反射涂层以增加DOE 300的透射率。在一些实现方式中,DOE 300可以暴露于空中界面。例如,DOE 300的第一表面(例如,匹配层325-1的表面和匹配层325-2的表面)和DOE 300的第二表面(例如,抗反射涂层310的表面)可以暴露于折射率为1.0的空气界面。浮雕深度h可基于以下等式计算:

$$[0059] h = \frac{\lambda_0}{2(n_{tf} - n_{air})},$$

[0060] 其中 $\lambda_0$ 是DOE(例如DOE 300)标称照明波长。为了减小浮雕深度,可以选择具有相对大折射率的材料,例如硅,在一些实现方式中,这可以导致蚀刻(例如,蚀刻330)的浮雕深度h大约为0.5微米( $\mu m$ )。在一些实现方式中,浮雕深度可以在大约 $\lambda/4$ 和 $\lambda/2$ 之间,其中 $\lambda$ 表示获得特定相位延迟的特定波长,例如大约940nm的波长、在840nm和940nm之间的波长等,在这些波长处,例如对于2.0和3.0之间的有效折射率、2.2的有效折射率等获得 $\pi$ 相位延迟。在一些实现方式中,层可以匹配折射率(index)以增加DOE 300的透射率。例如,硅层315和二氧化硅层320可以基于分别在3.1至3.9之间和在1.4至1.5之间的阈值量内的3.5和1.45

的相应折射率来选择。以这种方式，基于相对于其他DOE减小浮雕深度，本文所述的一些实现方式能够提高制造公差。

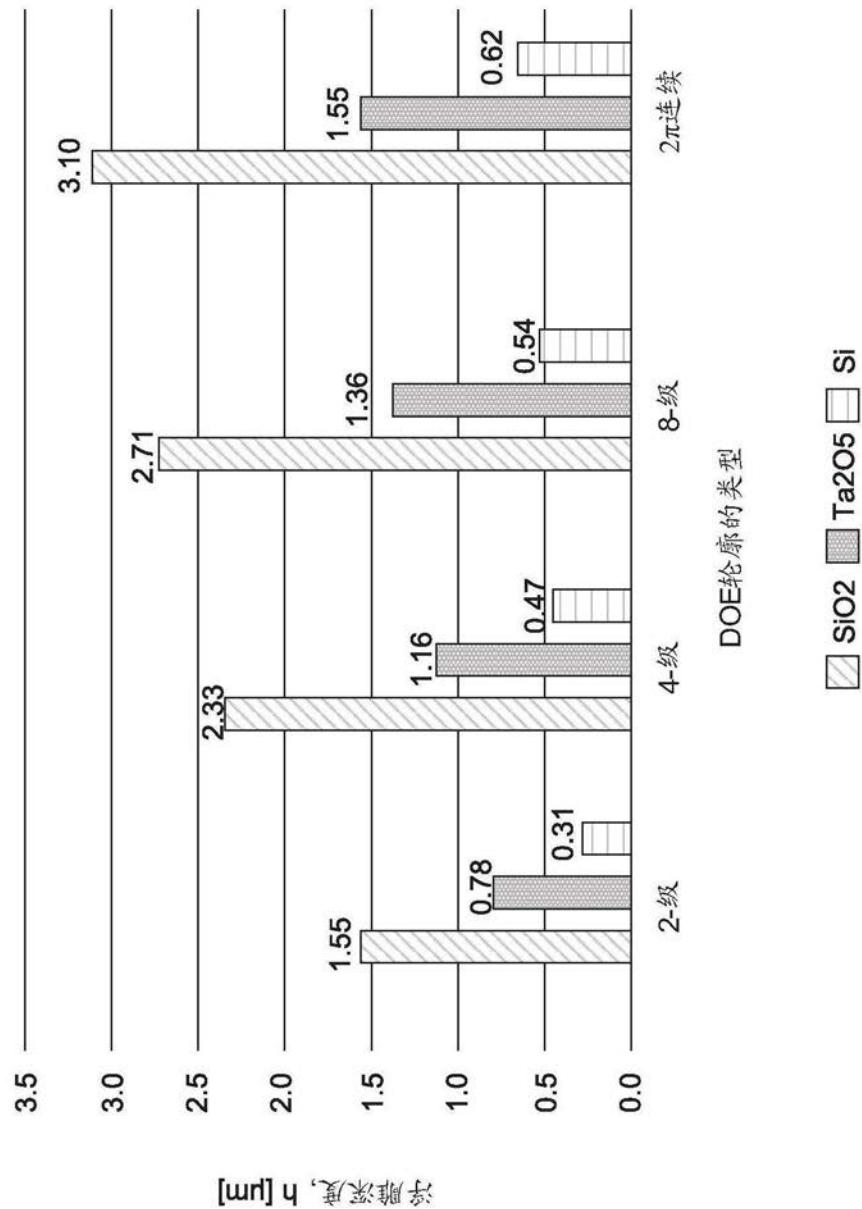

[0061] 如图3B并且通过简图350所示，可以为薄膜涂层材料选择其它材料，例如五氧化二钽( $Ta_2O_5$ )和氮化硅( $Si_3N_4$ )，其可以具有大约2.0的折射率。如简图350进一步所示，基于对DOE 300的层使用硅薄膜，相对于其它材料选择，两级、4级、8级或连续浮雕轮廓中的每一个的浮雕深度减小。例如，对于标称照明波长为1550nm的两级浮雕轮廓中的 $\pi$ 相位延迟，二氧化硅可与约1.55 $\mu m$ 的浮雕深度相关联，五氧化二钽和氮化硅可与约0.78 $\mu m$ 的浮雕深度相关联，并且硅可与约0.31 $\mu m$ 的浮雕深度相关联。

[0062] 如上所述，图3A和3B仅作为示例提供。其它示例是可能的，并且可以不同于关于图3A和3B描述的示例。

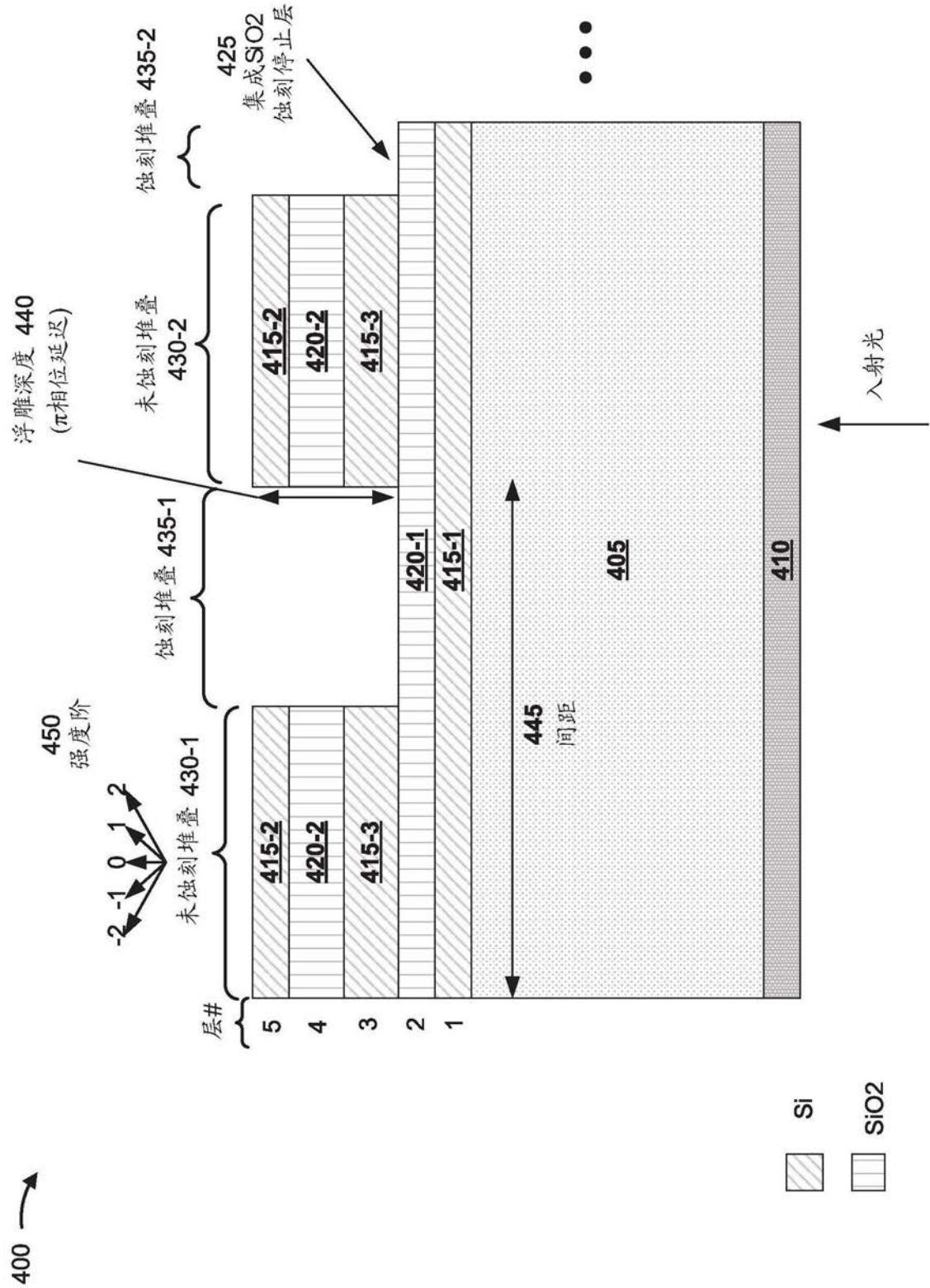

[0063] 图4A-4C是DOE 400/400' /400''的示例实现方式的简图。如图4A所示，DOE 400包括衬底405、抗反射涂层410、一组硅层415-1至415-3和一组二氧化硅层420-1至420-2。

[0064] 如图4A以及通过参考标号425进一步所示，二氧化硅层420-1可以是蚀刻停止层，以使蚀刻能够形成 $\pi$ 相位延迟。例如，可以执行蚀刻程序，使得未蚀刻的堆叠430-1和430-2保持未蚀刻，并且蚀刻的堆叠435-1和435-2被蚀刻到阈值浮雕深度440，在以蚀刻的堆叠435-1和435-2与未蚀刻的堆叠430-1和430-2之间提供 $\pi$ 相位延迟。在一些实现方式中，可以执行使用多个工具的多个蚀刻程序来蚀刻DOE 400。例如，DOE 400可以以二氧化硅层作为蚀刻停止部使用第一硅蚀刻、以硅层作为蚀刻停止部使用第一二氧化硅蚀刻和以另一二氧化硅层作为蚀刻停止部使用第二硅蚀刻(例如，使用深反应离子(DRIE)蚀刻工具)等来制造。

[0065] 在一些实现方式中，DOE 400的层可以形成一组抗反射结构。例如，层420-1和415-1可形成用于特定波长范围的第一抗反射结构，层415-2和420-2可形成用于特定波长范围的第二抗反射结构，从而形成两级浮雕轮廓。附加地或替代地，层415-2可形成第二抗反射结构。第二抗反射结构可以形成在第一抗反射结构上(例如，在未蚀刻的堆叠430中)，并且第一抗反射结构(例如，层420-1)可以是用于蚀刻的蚀刻停止部以形成第二抗反射结构。在一些实现方式中，至少一个层，例如层415-3、层415-3和420-2两者等，可以在第一抗反射结构和第二抗反射结构之间。这样，可以对蚀刻区域进行改变，以改变DOE 400的特性，而不改变DOE 400的透射率。在一些实现方式中，第一抗反射结构和第二抗反射结构可以不被层分开。在一些实现方式中，层415-3可以为DOE 400提供另一功能，例如除了特定相位延迟(例如 $\pi$ 相位延迟)和抗反射功能之外的另一功能。在一些实现方式中，DOE 400的抗反射结构共同形成DOE。

[0066] 在一些实现方式中，每个层可以与特定厚度相关联。例如，层1(例如硅层415-1)可以与大约209纳米(nm)的厚度相关联；层2(例如，二氧化硅层420-1)可以与162nm的厚度相关联；层3(例如，硅层415-3)(如果存在)可以与238nm的厚度相关联；层4(例如，二氧化硅层420-2)(如果存在)可以与254nm的厚度相关联；而层5(例如，硅层415-2)(如果存在)可以与20nm的厚度相关联。在一些实现方式中，DOE 400可以与特定间距445(有时称为周期)dx相关联。例如，间距445可以是大约1微米至1000微米。在一些实现方式中，可以在第五层(例如，另一个二氧化硅层)上形成覆盖层，这可以在切割包括衬底405的晶片期间提高鲁棒性。

[0067] 在一些实现方式中，可以选择DOE 400的层的厚度、间距445的尺寸、抗反射结构

和/或其层的折射率等,以在抗反射结构提供抗反射功能的特定波长处引起特定相位延迟(例如 $\pi$ 相位延迟)。例如,第一抗反射结构可以与1.5的第一(有效)折射率相关联,第二抗反射结构可以与3.5的第二(有效)折射率相关联,并且第一抗反射结构和第二抗反射结构之间的一组层(例如,层415-3)可以与3.5的第三(有效)折射率相关联。附加地或替代地,特定波长可以包括大约1540nm和1560nm之间的波长范围。如附图标记450所示,基于被引导到衬底405的第一侧的入射光,一组强度阶(例如,强度阶-2、-1、0、1、2等)由DOE 400提供。

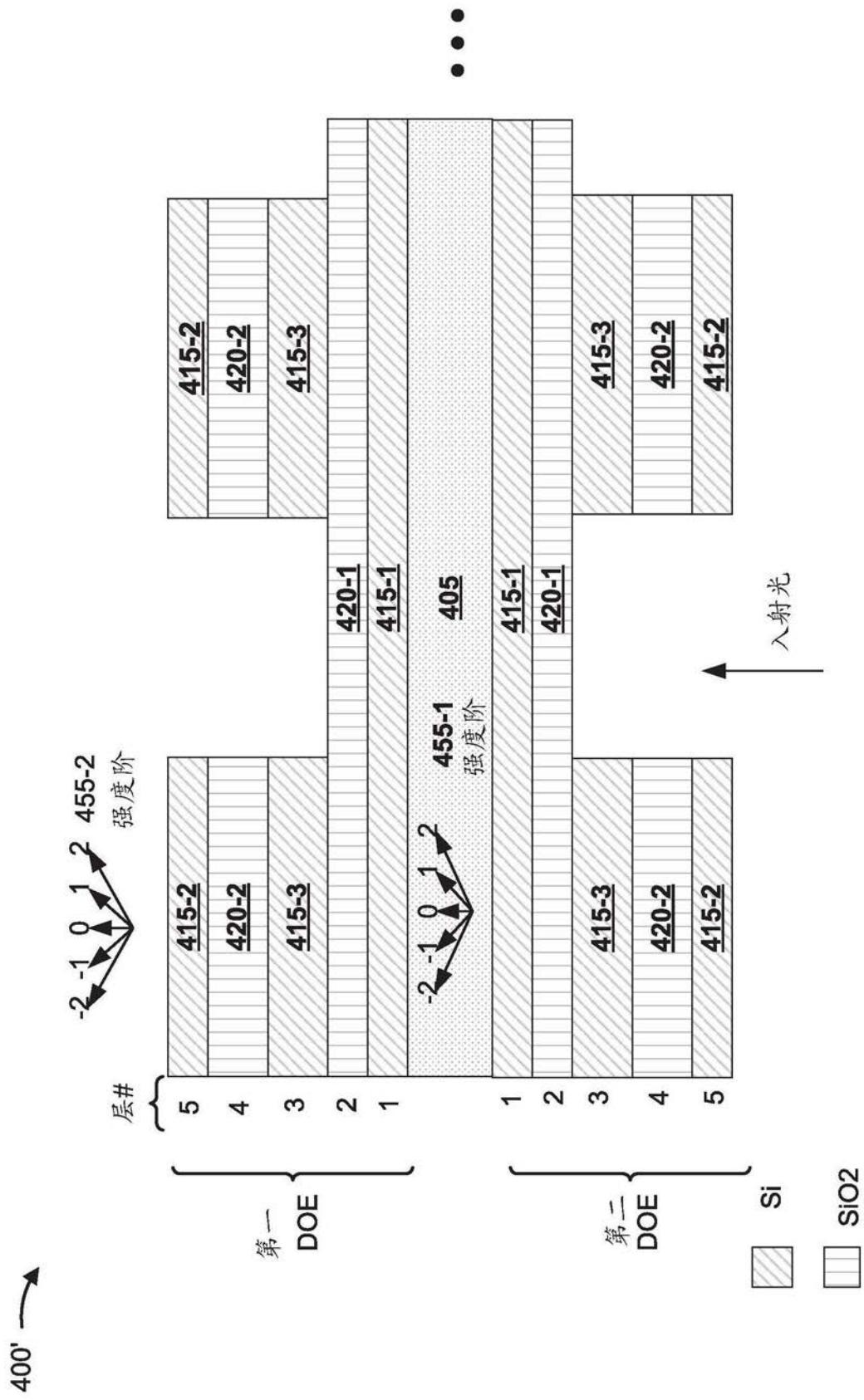

[0068] 如图4B所示,DOE 400'包括形成在衬底405的第一侧上的第一衍射光学元件和形成在衬底405的第二侧上的第二衍射光学元件。每个衍射光学元件包括一组硅层415-1至415-3和一组二氧化硅层420-1至420-2。如附图标记455-1和455-2所示,基于朝向DOE 400'的入射光,第二衍射光学元件使得第一组强度阶被引导通过衬底405到达第一衍射光学元件,这使得从DOE 400'提供第二组强度阶。这样,衬底405保持第一衍射光学元件和第二衍射光学元件的对准,从而相对于另一种技术(例如自由空间光学或使用拾取和放置机器)降低了保持对准的困难。

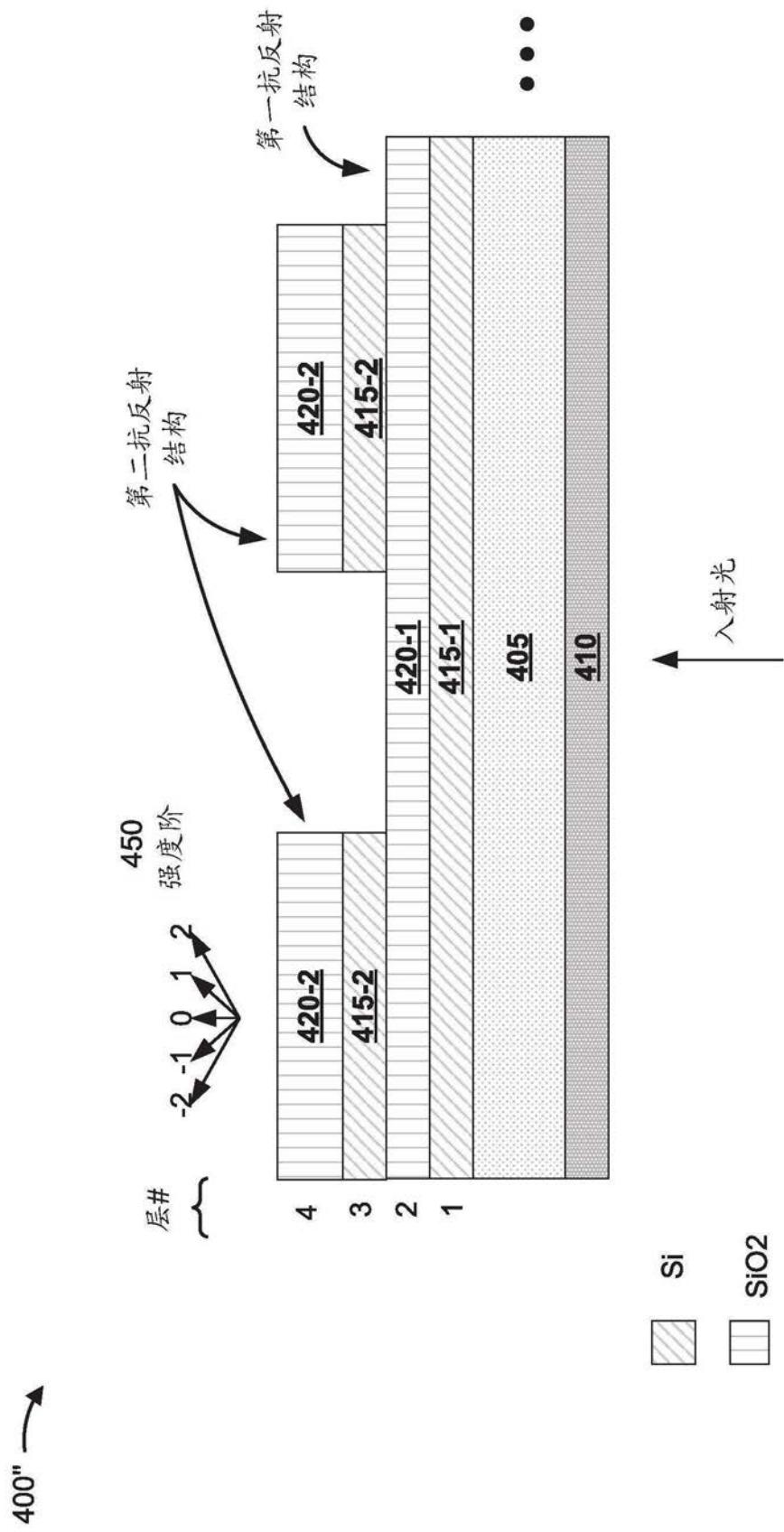

[0069] 如图4C所示,DOE 400"包括形成在衬底405的表面上的第一抗反射结构和形成在第一抗反射结构的一部分的表面上的第二抗反射结构(例如,在第一抗反射结构和第二抗反射结构之间没有形成一个或更多个层)。例如,第一抗反射结构和第二抗反射结构可以为特定波长(例如930nm至950nm之间的波长范围)提供抗反射功能,并且可以在特定波长提供特定相位延迟(例如 $\pi$ 相位延迟)。在一些实现方式中,DOE 400"的层可以与特定厚度相关联。例如,层1可以与大约121nm的厚度相关联,层2可以与大约107nm的厚度相关联,层3可以与大约130nm的厚度相关联,层4可以与大约258nm的厚度相关联,等等。

[0070] 尽管本文描述的一些实现方式是根据特定数量的层来描述的,例如4层或5层,但是其他数量的层也是可能的,例如6层(例如6个交替的硅/二氧化硅层)、7层、10层、20层等。

[0071] 如上所述,图4A-4C仅作为示例提供。其它示例是可能的,并且可以不同于关于图4A-4C描述的示例。

[0072] 图5是用于配置DOE的示例过程500的流程图。在一些实现方式中,图5的一个或更多个处理块可以由客户端设备执行。在一些实现方式中,图5的一个或更多个处理块可以由与客户端设备(例如服务器设备)分离或包括客户端设备的另一设备或一组设备来执行。图6A和6B是与图5所示的示例过程500相关的示例实现方式600的简图。

[0073] 如图5所示,过程500可包括确定堆叠的材料(块505)。例如,客户端设备可以确定堆叠的材料。在一些实现方式中,客户端设备可以接收标识用于堆叠的材料的输入。例如,在DOE的设计期间,设计者可以基于一组设计标准选择一组涂层材料。在一些实现方式中,该组涂层材料可包括硅、氢化硅、二氧化硅、五氧化二钽、氮化硅、其组合等。在一些实现方式中,该组设计标准可以包括DOE的波长范围、材料的折射率、材料的透射率等。在一些实现方式中,堆叠可以是多层堆叠。例如,如图6A所示,堆叠可以是设置在熔融石英衬底、玻璃衬底等上的交替的硅和二氧化硅薄膜的5层堆叠。

[0074] 如图5进一步所示,过程500可包括确定堆叠的未图案化薄膜区域的反射率(块510)。例如,客户端设备可以确定堆叠的未图案化薄膜区域的反射率。在一些实现方式中,客户端设备可以接收标识第一区域和第二区域的反射率的输入。例如,设计者可以确定包括衬底和第一对交替的硅和二氧化硅薄膜层的堆叠的第一区域的反射率,如图6A中的附图

标记605所示。该第一区域可以被称为 $AR_0$ 。在这种情况下,设计者可以确定堆叠的第二区域的反射率,该第二区域包括衬底、第一对交替的硅和二氧化硅薄膜层、硅薄膜层以及第二对交替的硅和二氧化硅薄膜层,如图6A中的附图标记610所示。这个第二区域可以称为 $AR_\pi$ 。基于 $AR_0$ 和 $AR_\pi$ 作为单独的未图案化堆叠,可以使用薄膜理论来确定 $AR_0$ 和 $AR_\pi$ 的反射率、透射率和相位延迟,从而使得能够以相对于使用衍射理论进行的优化计算而言提高的效率来使用全局优化。这样,相对于其他技术,可以减少客户端设备对用于DOE的配置的优化的计算资源的利用率。

[0075] 如图5进一步所示,过程500可包括定义用于最小化堆叠的区域的反射率的函数(块515)。例如,客户端设备可以定义用于最小化堆叠的区域的反射率的函数。在一些实现方式中,该函数可以是价值函数、成本函数等。例如,客户端设备可以接收标识函数的输入,使得函数的优化(例如,最小化)导致堆叠的区域的反射率降低, $\pi$ 的相位延迟保持在 $AR_0$ 和 $AR_\pi$ 之间。这样,客户端设备可以将特定波长范围的透射率提高到阈值水平,例如至少大约80%、大约90%、大约95%、大约99%等的透射率。

[0076] 如图5进一步所示,过程500可包括选择用于厚度优化的层(块520)。例如,客户端设备可以选择至少一个层用于厚度优化。在一些实现方式中,客户端设备可以接收标识至少一个层的输入。例如,设计者可以选择优化图6A中所示的层3的厚度(例如,夹在匹配层1和2与匹配层4和5之间的硅层),并且可以指定层1、2、4、5的厚度,以便能够相对于层3的厚度优化DOE的反射率。在一些实现方式中,层的厚度可以基于一组等式来确定:

$$[0077] \Delta\phi = k \sum_{i=1}^N h_i (n_i - 1)$$

$$[0078] k = 2\pi/\lambda_0,$$

[0079] 其中,  $\Delta\phi$  表示所选择的相位延迟(例如 $\pi$ ),  $k$  表示(例如层3的)常数值,  $h_i$  表示层*i*的浮雕深度,  $n_i$  表示层*i*的折射率, 以及  $\lambda_0$  表示DOE的标称照明波长。这样,客户端设备可以计算例如层3的厚度,以基于DOE的其他层的厚度获得所选择的相位延迟。

[0080] 如图5进一步所示,过程500可包括选择用于优化的层厚度(块525)。例如,客户端设备可以选择用于优化的层厚度。在一些实现方式中,客户端设备可以随机选择厚度。例如,客户端设备可以利用随机选择程序来选择层1、2、4和5的层厚度,以便能够确定层3的层厚度。在一些实现方式中,客户端设备可以利用非随机选择程序,例如优化程序来选择厚度。

[0081] 如图5进一步所示,过程500可以包括应用优化程序(块530)。例如,客户端设备可以应用优化程序。在一些实现方式中,客户端设备可以使用模拟退火来优化DOE的反射率。例如,客户端设备可以执行模拟退火程序和最陡下降算法程序,以优化用于配置层厚度以优化(例如最小化)反射率的成本函数。在一些实现方式中,客户端设备可以执行优化程序,直到满足阈值标准(例如,计算透射率的阈值水平,诸如大于50%的透射率、大于80%的透射率、大于90%的透射率、大于95%的透射率、大于99%的透射率、大于99.5%的透射率等)。

[0082] 如图5进一步所示,过程500可以包括分析优化程序的结果的配置(块535)。例如,客户端设备可以确定DOE的转变点以确定表面浮雕轮廓。如图6A并且通过附图标记615所示,优化的结果可以识别DOE的优化特性。在一些实现方式中,客户端设备可以分析偶数阶

和零阶被抑制的配置(其可以被称为偶数阶缺失(EOM)配置)。例如,如图6A和6B所示,客户端设备可以确定衍射理论分析,以确定1x4点阵发生器的DOE的浮雕轮廓。在这种情况下,DOE包括具有一组过渡点625的周期620的浮雕轮廓。例如,转变点625-1可以位于0dx,625-2位于0.054dx,625-3位于0.277dx,以及625-4位于0.5dx,其中dx表示周期620的宽度。在一些实现方式中,客户端设备可以基于包括DOE的点阵照明器的配置来接收标识转变点的信息。在一些实现方式中,客户端设备可以基于点阵照明器的配置自动确定转变点。如进一步参照图6A和6B所示,每个转变点对应于浮雕深度最小值和浮雕深度最大值之间的转变,以及对应于相位延迟最小值(0)和相位延迟最大值( $\pi$ )之间的转变。

[0083] 在一些实现方式中,客户端设备可以执行电磁衍射理论分析。例如,客户端设备可以确定光束的横向电(TE)偏振部分和光束的横向磁(TM)偏振部分的衍射效率。基于TE偏振的衍射效率和满足第一阈值的TM偏振的衍射效率(即大于第一阈值或在连续浮雕轮廓衍射效率的阈值内,例如在10%内、在5%内、在2%内等),并且基于满足第二阈值的零阶衍射效率(即小于第二阈值,例如小于10%、小于5%、小于2%等),客户端设备可以确定DOE的配置满足一组设计标准。

[0084] 如图5进一步所示,过程500可以包括提供输出(块540)。例如,客户端设备可以提供标识DOE的配置(例如,浮雕轮廓)的输出,以使得能够制造DOE。在一些实现方式中,客户端设备可以存储标识配置的输出、向服务器设备提供标识配置的输出以触发DOE的制造等。

[0085] 尽管图5示出了过程500的示例块,但是在一些实现方式中,与图5中描述的块相比,过程500可以包括附加的块、更少的块、不同的块或不同排列的块。附加地或替代地,过程500的两个或更多个块可以并行执行。如上所述,图6A和6B仅作为示例提供。其它示例是可能的,并且可以不同于关于图6A和6B描述的示例。

[0086] 图7是用于制造DOE的示例过程700的流程图。图8A和8B是与图7所示的示例过程700相关的示例实现方式800的简图。

[0087] 如图7所示,过程700可包括在衬底上沉积一组层(块710)。例如,如图8A并且由附图标记810所示,多个薄膜,例如一组硅层和二氧化硅层,可以沉积在衬底上,例如玻璃衬底或熔融石英衬底上,以沉积用于特定波长的第一抗反射结构和用于特定波长的第二抗反射结构。在一些实现方式中,该组层可以包括沉积在衬底上的第一对硅和二氧化硅层、硅层以及第二对硅和二氧化硅层。在一些实现方式中,抗反射涂层可以沉积在衬底的另一表面上,使得衬底设置在抗反射涂层和交替的硅和二氧化硅层之间。在一些实现方式中,抗反射结构可以沉积在衬底的第一侧和衬底的第二侧上。在一些实现方式中,另一组材料可用于至少一层,例如五氧化二钽基材料、氮化硅基材料等。

[0088] 如图7进一步所示,过程700可包括将掩模沉积到该组层中的一层上(块720)。例如,如图8A所示,并且如附图标记820所示,掩模层可以沉积在第二对硅和二氧化硅层的硅层上,使得掩模层覆盖硅层。在一些实现方式中,可以选择用于掩模的材料,使得掩模选择性地与阈值相关或者与硅蚀刻和二氧化硅蚀刻的阈值电阻率相关联。

[0089] 如图7进一步所示,过程700可包括图案化掩模(块730)。例如,如图8A所示,并且通过附图标记830所述,可以基于DOE的配置来图案化掩模层。在这种情况下,掩模层可以被图案化,使得掩模覆盖DOE的相对于图4将对应于未蚀刻堆叠430的部分,并且掩模层被去除,使得DOE的相对于图4将对应于蚀刻堆叠435的部分。在这种情况下,可以基于配置DOE来确

定掩模的图案,如本文关于图5所描述的。例如,基于DOE的确定的转变点来图案化掩模。

[0090] 如图7进一步所示,过程700可包括基于图案化掩模来蚀刻层的子集以形成浮雕轮廓(块740)。例如,如图8B所示,并通过附图标记840所示,可以使用硅蚀刻、二氧化硅蚀刻等去除未被图案化的掩模覆盖的一组层的一部分。在这种情况下,在该一组层的子集中形成浮雕轮廓。在一些实现方式中,执行蚀刻以去除少于该整个一组层(remove less than the entire set of layers)。例如,参照图4,执行蚀刻以去除层3-5的部分。在这种情况下,(例如,层2的)二氧化硅可以对DOE执行蚀刻停止功能。

[0091] 如图7进一步所示,过程700可包括去除掩模(块750)。例如,如图8B所示,并通过附图标记850所示,可以去除掩模。在这种情况下,该一组层保留在被图案化的衬底上,以在层的子集被去除的DOE部分和层的子集未被去除的DOE部分之间提供π相位延迟。

[0092] 如图7进一步所示,过程700可包括基于去除掩模来执行晶片抛光加工(块760)。例如,DOE可以被测试,DOE可以被切割成多个离散DOE(例如,其上图案化了多个DOE的晶片可以被切割成多个离散DOE),并且DOE可以被封装以包含在光学设备中。在一些实现方式中,晶片可以是200毫米(mm) x 0.725mm的晶片。

[0093] 这样,相对于包括蚀刻二氧化硅晶片以产生表面浮雕轮廓、用抗反射涂层涂覆表面浮雕轮廓等的另外的技术,通过提供涂覆有抗反射薄膜层的晶片,减少了制造步骤的数量。此外,相对于其他技术,基于减少步骤的数量,可以降低成本、供应链难度等。

[0094] 尽管图7示出了过程700的示例块,但是在一些实现方式中,与图7中描述的块相比,过程700可以包括附加的块、更少的块、不同的块或不同排列的块。附加地或替代地,过程700的两个或更多个块可以并行执行。如上所述,图8A和8B仅作为示例提供。其它示例是可能的,并且可以不同于关于图8A和8B描述的示例。

[0095] 这样,设计和/或制造具有包括蚀刻成两级浮雕轮廓的交替的硅层(例如氢化硅层)和二氧化硅层的薄膜堆叠的DOE。此外,DOE的层可设计成提供抗反射特性、集成蚀刻停止特性等。此外,可以使用薄膜工艺沉积来执行设计,这可以控制零阶功率。在一些实现方式中,可以使用基于非衍射理论的计算技术来设计DOE,从而减少处理资源以确定DOE的设计。此外,基于使用薄膜沉积技术和蚀刻技术,可以减少制造DOE的制造步骤的数量,从而相对于用于制造DOE的其他技术减少时间和成本。

[0096] 前述公开内容提供的是说明和描述,但并不意欲穷举或将实现方式限制在所公开的精确形式。根据上面的公开内容,修改和变化是可能的,或可从实现方式的实践中获得。

[0097] 本文描述的一些实现方式结合了阈值。如本文所使用的,满足阈值可指值大于阈值、多于阈值、高于阈值、大于或等于阈值、小于阈值、少于阈值、低于阈值、小于或等于阈值、等于阈值等。

[0098] 将明显的是,本文描述的系统和/或方法可以以硬件、固件或硬件和软件的结合的不同形式来实现。用于实现这些系统和/或方法的实际的专用控制硬件或软件代码不是对该实现方式的限制。因此,系统和/或方法的操作和行为在本文被描述而未参考专用软件代码--应理解的是,软件和硬件可被设计为基于本文的描述来实现系统和/或方法。

[0099] 尽管特征的特定结合在权利要求中被阐述和/或在说明书中被公开,这些结合不旨在限制可能的实现方式的公开。事实上,这些特征中的许多特征可以不具体地在权利要求中阐述和/或在说明书中被公开的方式结合。尽管下面列出的每个从属权利要求可直接

仅从属于一个权利要求,但是可能的实现方式的公开可包括:每个从属权利要求与权利要求组中的每个其它权利要求相结合。

[0100] 本文使用的元件、动作或指令不应被解释为关键或必要的,除非明确地描述为这样。此外,如本文所使用的,冠词“一(a)”和“一(an)”旨在包括一个或更多个项,并可与“一个或更多个”交换使用。另外,如本文所使用的,术语“组(set)”旨在包括一个或多个项(如,有关的项、无关的项、有关的项和无关的项的结合等),并可与“一个或更多个”交换使用。当意欲仅有一个项时,术语“一个(one)”或类似语言被使用。此外,如本文所使用的,术语“具有(has)”,“具有(have)”,“具有(having)”等意欲为开放术语。另外,短语“基于”旨在意味着“至少部分地基于”,除非以其它方式明确声明。

图1

图2A

图2B

图3A

350 →

在SiO<sub>2</sub>、Ta<sub>2</sub>O<sub>5</sub>/Si<sub>3</sub>N<sub>4</sub>或Si中实现的2、4、8级和

连续DOE的表面浮雕高度[μm]

图3B

图4A

图4B

图4C

图5

图6B

图7

图8A

图8B