# (19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

*H01L 31/042* (2006.01) *H01L 31/0236* (2006.01)

**H01L 31/18** (2006.01) **H01L 29/04** (2006.01)

(21) 출원번호 10-2012-7005010

(22) 출원일자(국제) **2010년09월20일**

심사청구일자 **없음**

(85) 번역문제출일자 2012년02월27일

(86) 국제출원번호 PCT/US2010/049542

(87) 국제공개번호 **WO 2011/035272** 국제공개일자 **2011년03월24일**

(30) 우선권주장

61/244,052 2009년09월20일 미국(US)

(11) 공개번호 10-2012-0068845

(43) 공개일자 2012년06월27일

(71) 출원인

인터몰레큘러 인코퍼레이티드

미국, 캘리포니아 95134, 샌 호세, 엔. 제1스트 리트 3011

(72) 발명자

리, 지안

미국, 캘리포니아 95134, 산 호세, 쟁커 로드 2865

느규엔, 민, 안

미국, 캘리포니아 95134, 산 호세, 쟁커 로드 2865

(뒷면에 계속)

(74) 대리인

강명구

전체 청구항 수 : 총 13 항

#### (54) 발명의 명칭 조합 스크리닝에서의 사용을 위한 결정 실리콘 태양 전지 제조 방법

#### (57) 요 약

본 발명의 구체 예는 조합적으로 변화될 수 있고 평가될 수 있는 서로 다른 유형의 결정 실리콘계 태양 전지를 형성하는 방법을 기술한다. 이러한 서로 다른 유형의 태양 전지의 예는 전면 및 후면 전극 실리콘계 태양 전지, 후면전극 태양 전지, 및 선택적 에미터 태양 전지를 포함한다.

#### 대 표 도 - 도2b

## (72) 발명자

## 칼얀카, 닉힐

미국, 캘리포니아 95134, 산 호세, 쟁커 로드 2865

# 쿠마르, 니틴

미국, 캘리포니아 95134, 산 호세, 쟁커 로드 2865

# 헌터, 제임스, 크레이그

미국, 캘리포니아 95134, 산 호세, 쟁커 로드 2865

#### 특허청구의 범위

#### 청구항 1

확산 장벽 재료를 결정 실리콘 기판의 전면 및 후면에 증착하는 단계;

상기 결정 실리콘 기판을 조합 습식 공정 기구 내에 위치시켜 다음 단계를 사용하여 복수의 사이트-분리된 영역을 가공하는 단계:

상기 확산 장벽을 상기 복수의 사이트-분리된 영역 내 기판의 전면으로부터 에칭시켜 결정 실리콘의 영역을 노출시키는 단계; 및

상기 결정 실리콘의 영역을 텍스처링하여 복수의 텍스처링된 영역을 형성하는 단계;

를 포함하는, 결정 실리콘 태양전지 시험 기판 형성 방법.

#### 청구항 2

제 1 항에 있어서, 상기 복수의 텍스처링된 영역을 세정하는 단계를 더욱 포함하는, 결정 실리콘 태양전지 시험 기판 형성 방법.

#### 청구항 3

제 2 항에 있어서, 상기 복수의 텍스처링된 영역을 세정하는 단계는 상기 조합 습식 공정 기구 내에서 수행되며 세정 용액은 적어도 두 개의 사이트-분리된 영역에서 변화되는, 결정 실리콘 태양전지 시험 기판 형성 방법.

#### 청구항 4

제 2 항에 있어서, 상기 복수의 텍스처링된 영역을 세정하는 단계는 기판의 전면 상부 전반에서 수행되는, 결정 실리콘 태양전지 시험 기판 형성 방법.

#### 청구항 5

제 1 항에 있어서, 상기 복수의 텍스처링된 영역에 도판트를 가하는 단계를 더욱 포함하는, 결정 실리콘 태양전지 시험 기판 형성 방법.

#### 청구항 6

제 5 항에 있어서, 상기 도판트를 가하는 단계는 액체 도판트 용액을 사용하여 조합 습식 공정 기구 내에서 수행되는, 결정 실리콘 태양전지 시험 기판 형성 방법.

#### 청구항 7

제 6 항에 있어서, 상기 액체 도판트 용액은 적어도 두 개의 사이트-분리된 영역에서 변화되는, 결정 실리콘 태양전지 시험 기판 형성 방법.

#### 청구항 8

제 5 항에 있어서, 상기 도판트를 가하는 단계는 사이트-분리된 영역들 내에서 고농도 도핑된 영역 및 저농도 도핑된 영역을 형성하여 선택적 에미터 결정 실리콘 태양전지를 형성하는 단계를 포함하는, 결정 실리콘 태양 전지 시험 기판 형성 방법.

#### 청구항 9

제 5 항에 있어서, 상기 도판트를 상기 복수의 텍스처링된 영역 내에 확산시키는 단계를 더욱 포함하는, 결정 실리콘 태양전지 시험 기판 형성 방법.

#### 청구항 10

제 9 항에 있어서, 상기 사이트-분리된 영역 상부에 패시베이션 층을 형성하는 단계를 더욱 포함하는, 결정 실리콘 태양전지 시험 기판 형성 방법.

#### 청구항 11

제 10 항에 있어서, 상기 사이트-분리된 영역에 전기적 접촉부를 형성하는 단계를 더욱 포함하는, 결정 실리 콘 태양전지 시험 기판 형성 방법.

#### 청구항 12

제 11 항에 있어서, 상기 사이트-분리된 영역에 전기적 접촉부를 형성하는 단계는 전면 및 후면 접촉부를 형성하는 단계를 포함하는, 결정 실리콘 태양전지 시험 기판 형성 방법.

#### 청구항 13

제 1 항에 있어서,

상기 복수의 테스처링된 영역 상부에 패시베이션 층을 형성하는 단계;

상기 사이트-분리된 영역에 대응하는 영역에서 기판의 후면에 n-도핑된 영역 및 p-도핑된 영역을 형성하는 단계; 및

상기 사이트-분리된 영역 각각에서 복수의 후면 접촉부를 형성하여 후면전극 태양 전지를 형성하는 단계; 를 더욱 포함하는, 결정 실리콘 태양전지 시험 기판 형성 방법.

#### 명 세 서

#### 기술분야

#### [0001] 발명의 분야

[0002] 본 발명은 일반적으로 결정 실리콘 태양전지 공정에 관한 것이다. 더욱 상세하게는, 조합 방법에서 사용되기 위한 결정 실리콘 태양전지 시험 기판의 제조 방법을 기재한다.

#### 배경기술

#### [0003] 발명의 배경

[0004] 조합 공정법(combinatorial processing)은 반도체 공정뿐만 아니라 또 다른 산업 예컨대 배터리, 촉매, 약품 및 바이오공학에서 형성된 재료, 공정 및 장치를 평가하기 위하여 사용되어 왔다. 태양 응용분야에 조합 공정 법을 적용시키려는 상당한 노력은 이루어지지 않았다. 특히, 실리콘계 태양 전지의 조합 평가를 위한 태양 전지 시험 기판의 개발은 수행되지 않았다.

[0005] 실리콘계 태양 전지의 형성을 위한 일부 예시적인 태양 공정 작업(solar processing operation)은 층 추가(증착) 및 제거(에칭 또는 텍스처링), 피처(feature) 정의, 층 준비(예컨대, 세정 또는 표면 처리), 도핑 등을 위한 작업을 포함한다. 태양 공정에 대한 재료, 유닛 공정, 또는 공정 순서에서의 개선이 추구되고 있다. 그렇지만, 태양 회사는 전체 기판 공정에 대한 연구 및 개발(R&D)을 수행한다. 이러한 접근법은 R&D 비용을 증가시켰고 시간 및 비용 효과적인 방식으로 광범위한 실험을 수행할 수 없게 만들었다.

#### 발명의 내용

[0006] 내용 없음

#### 도면의 간단한 설명

### [0007] 도면의 간단한 설명

본 발명의 다양한 구체 예를 이하의 상세한 설명 및 첨부하는 도면에서 기술한다.

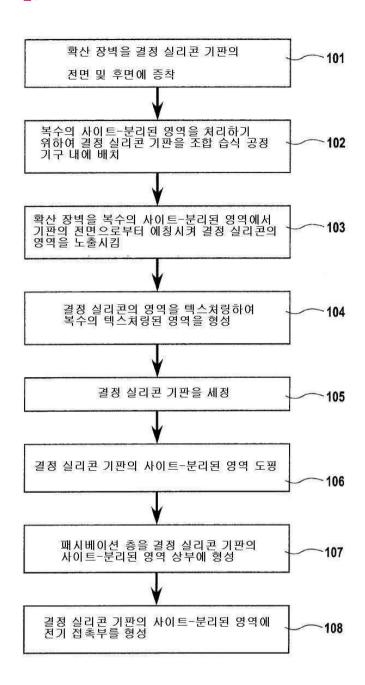

도 1은 다양한 구체 예에 따르는 결정 실리콘 태양전지 기판을 형성하기 위한 공정을 설명하는 흐름도이다.

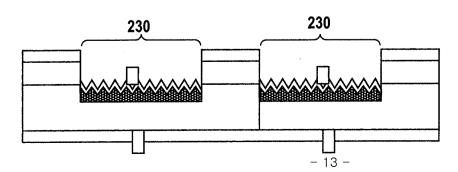

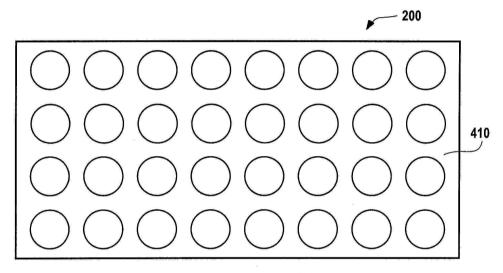

도 2A-2P는 한 구체 예에 따라 "종래" 결정 실리콘 태양전지 시험 기판을 형성하기 위한 공정을 나타낸다.

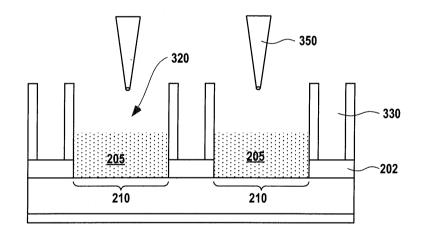

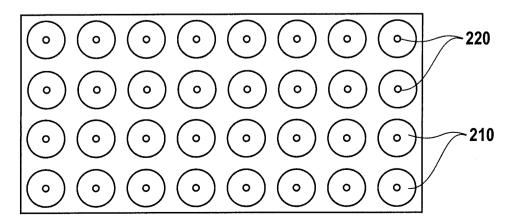

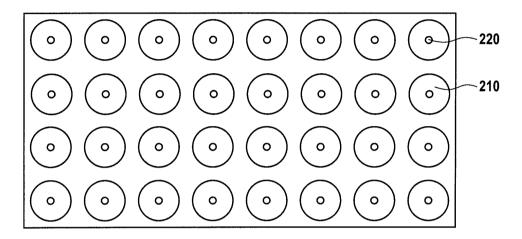

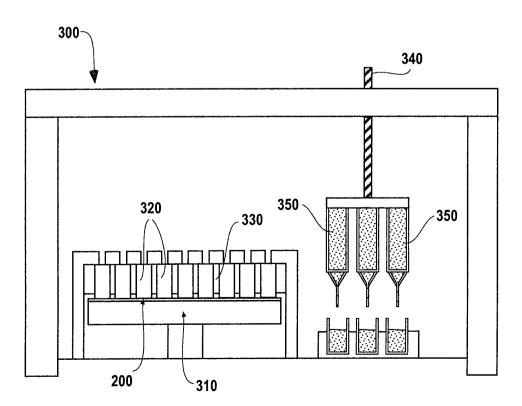

도 3A는 조합 습식 공정 기구(combinatorial wet processing tool)의 한 예를 나타낸다.

도 3B는 조합 습식 공정 기구에 의해 형성된 사이트-분리된 영역(site-isolated region)을 갖는 기판의 한 예를 나타내는데, 사이트-분리된 영역 내 면적이 태양 전지의 면적을 정의한다.

도 4A-4G는 후면전극(all-back contact) 결정 실리콘 태양전지를 형성하기 위한 공정을 나타낸다.

도 5A-5C는 선택적 에미터(selective emitter) 태양 전지를 포함하는 결정 실리콘 태양전지 기판을 형성하기 위한 대안적인 공정을 나타낸다.

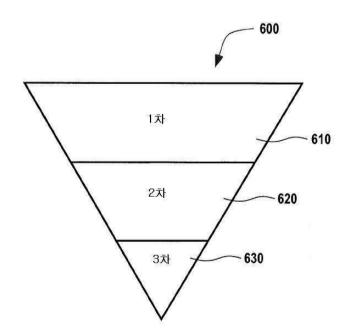

도 6은 본 발명의 한 구체 예에 따르는 조합 스크리닝 흐름(combinatorial screening flow)의 다이어그램을 나타낸다.

#### 발명을 실시하기 위한 구체적인 내용

#### [0008] 상세한 설명

- [0009] 하나 이상의 구체 예의 상세한 설명을 이하에서 첨부하는 도면과 함께 기재한다. 상세한 설명은 이러한 구체 예와 조합되어 제시되지만, 어떠한 특정 실시예에 제한되지 않는다. 범위는 청구범위에 의해서 제한되며, 다양한 변형, 변경, 및 균등범위가 포함된다. 여러 구체적인 상세사항이 완전한 이해를 제공하기 위하여 이하의 설명에 제시된다. 이러한 상세사항은 실시예의 목적으로 제공되며 기재된 기술은 이러한 구체적인 상세사항의 일부 또는 전부가 없이 청구범위에 따라 실시될 수 있다. 명확성을 위하여, 구체 예와 관련된 기술 분야에서 공지된 기술적 사항은 설명을 불필요하게 모호하게 하는 것을 회피하기 위하여 상세하게 기술하지 않았다.

- [0010] 재료, 공정, 및 장치를 조합적으로 시험하기 위해 태양 전지 시험 기판을 형성하는 공정이 본 명세서에 기재한다. 조합 공정법은 복수의 실험이 단일 기판상에서 수행되도록 하며 태양 전지 가공 작업 및 태양 전지 재료의 신속한 평가를 가능하게 한다. 서로 다른 조합 공정을 병렬로, 직렬로, 또는 이들 둘의 조합으로 운영하도록 태양 전지 시험 기판을 설계한다. 본 발명의 구체 예는 조합적으로 변화하고 평가될 수 있는 서로 다른 유형의 결정 실리콘계 태양 전지를 형성하는 방법을 기재한다. 이러한 서로 다른 유형의 태양 전지의 예에는 전면 및 후면 전극(front and back contact) 실리콘계 태양 전지, 후면전극 태양 전지, 및 선택적 에미터 태양 전지가 있다. 이러한 방법론들은 모두 최소 하나의 조합 공정법 기구를 사용하는 사이트-분리된 영역의 형성 및 태양 전지 영역을 형성하기 위한 이러한 사이트-분리된 영역의 사용을 포함한다. 따라서, 복수의 태양전지가 조합 방법론에서의 사용되기 위해 단일 결정 실리콘 기판상에 신속하게 형성될 수 있다. 기재된 방법의 개별적인 공정, 공정 조건, 또는 재료 중 어떤 것도 태양 전지에 미치는 변수의 영향을 시험하기 위하여조합적으로 변화할 수 있다.

- [0011] 도 1은 단일 결정 실리콘 기판상에 복수의 태양 전지를 형성하기 위한 작업 방법을 나타내는 흐름도이다. 이러한 흐름도는 다양한 서로 다른 유형의 결정 실리콘계 태양 전지를 형성하기 위하여 사용될 수 있는 공정을 개략적으로 나타낸다. 본 흐름도에 제시된 공정들은 전면전극(front contact) 결정 실리콘계 태양 전지, 후면 전극 태양 전지, 및 선택적 에미터 태양 전지를 형성하기 위하여 사용될 수 있다.

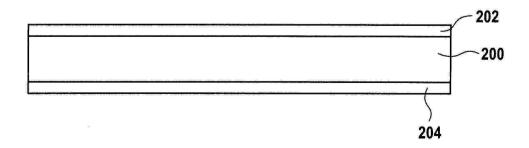

- [0012] 도 2A-2P에서, 단일 결정 실리콘 기판(200)상에 복수의 종래 결정 실리콘계 태양 전지를 형성하기 위한 방법을 도 1의 흐름도를 참조하여 기재한다. 결정 실리콘 기판은 156mm x 156mm 또는 125mm x 125mm의 치수를 갖는 단결정 또는 다결정 기판일 수 있다. 이러한 치수를 갖는 기판은 태양 산업계에서 흔하며 많은 표준 태양기판 공정 기구와의 사용에 적합할 수 있다. 태양 전지의 조합 개발(combinatorial development)을 위한 이러한 치수를 갖는 기판의 사용은 제조 규모의 기구와 기판의 상용성을 허용할 수 있다. 이에 따라, 기판이 조합공정법을 위하여 태양 전지 제조 라인의 내부 또는 외부에서 취해질 수 있다.

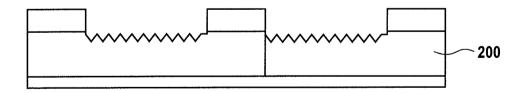

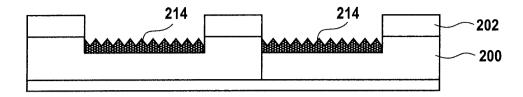

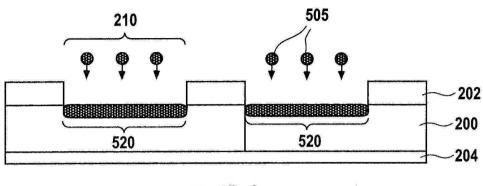

- [0013] 도 1의 블록(101)에서, 확산 장벽(202)을 결정 실리콘 기판(200)의 전면에 증착하고 확산 장벽(204)을 결정 실리콘 기판(200)의 후면에 증착한다. 확산 장벽(202 및 204)을 위하여 사용되는 재료는 도판트가 결정 실리콘 기판(200) 내로 확산되는 것을 방지하고, 예컨대 최대 950℃의 온도인 태양 전지 공정 조건을 견딜 수 있는 모든 재료일 수 있다. 예를 들면, 확산 장벽은 예컨대 실리콘 질화물(SiN<sub>x</sub>) 또는 이산화실리콘(SiO<sub>2</sub>)과 같은 물질일 수 있다. 확산 장벽 재료는 PECVD, LPCVD, 또는 PVD에 의해 증착될 수 있다. 이산화실리콘 확산 장벽은 열적 성장을 할 수 있다. 또한, 확산 장벽 재료는 졸-겔 방법에 의해 증착될 수 있다. 전면 확산 장벽(202) 및 후면 확산 장벽(204)은 서로 다른 시간 또는 동일 시간에 증착될 수 있다. 확산 장벽은 후속하여 확

산된 도판트의 확산이 결정 실리콘 기판에 도달하는 것을 방지할 수 있는 충분한 두께로 증착된다. 한 구체예에서, 확산 장벽(202 및 204)의 두께는 PVD 또는 CVD에 의해 기판(200)의 각 면에 증착된 실리콘 질화물의약 200 nm이다.

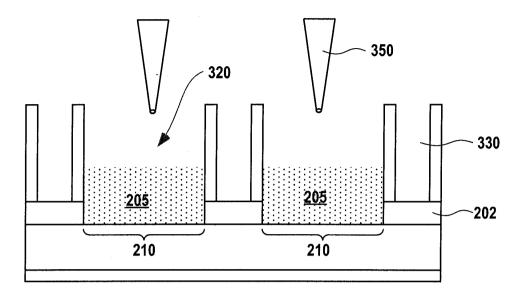

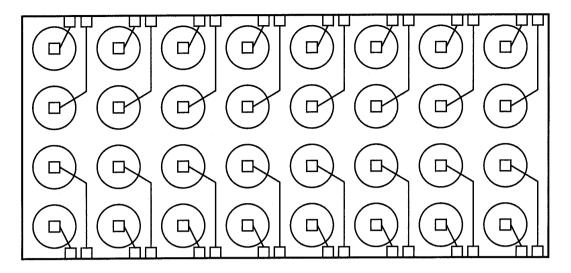

- [0014] 도 1의 흐름도의 블록(102)에서, 결정 실리콘 기판(200)의 복수의 사이트-분리된 영역을 처리하기 위하여 상기 기판(200)을 조합 습식 공정 기구에 배치한다. 도 3A는 조합 습식 공정 기구(300)의 한 예를 나타낸다. 본예에서, 기판(200)이 받침대(310) 위에 배치되고 상기 받침대(310)는 측벽(330)에 의해 서로 분리된 사이트-분리된 반응기(site-isolated reactor)(320) 아래에서 상기 기판(200)을 붙잡는다. 도 3B는 사이트-분리된 반응기(320)의 측벽(330)에 의해 생성된 사이트-분리된 영역(210)을 갖는 기판의 평면도(top-down view)의 예를 나타낸다. 사이트-분리된 영역(210)은 최종적으로 조합적으로 평가될 수 있는 개별 태양 전지가 되는 것의 영역을 정의한다. 도 3A의 조합 습식 공정 기구(300)는 액체를 각각의 반응기(320) 내로 분배하기 위하여 사용되는 다중 분배기(350)를 붙잡는 분배 팔(dispense arm)(340)을 포함한다. 다중 분배기(350)는 변화된 공정액체 또는 동일한 액체를 붙잡을 수 있다. 도 3A는 습식 공정 기구의 한 예를 나타내지만, 대안적인 것도 사용될 수 있다. 예를 들면, 분배 라인뿐만 아니라 퇴거 라인 및 기체 라인이 각각의 반응기(320) 내에 일체화될 수 있다.

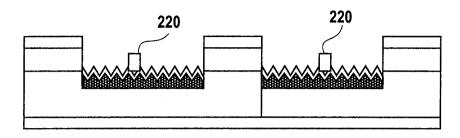

- [0015] 도 1의 흐름도의 블록(103)에서, 확산 장벽을 복수의 사이트-분리된 영역에서 기판의 전면으로부터 에칭시켜 결정 실리콘의 영역을 노출시킨다. 도 2B는 측벽(330) 및 분배기(350)를 포함하는 두 개의 반응기(320)의 간략화된 측면도를 나타낸다. 분배기는 전면 확산 장벽(202)을 에칭하기 위하여 사이트-분리된 영역(210) 내의 기판(300) 표면에 에칭제(205)를 분배할 수 있다. 선택된 에칭제(205)는 HF 또는 H<sub>2</sub>PO<sub>3</sub>, 또는 전면 확산 장벽(202) 재료를 에칭하지만 결정 실리콘 기판(200)은 에칭하지 않는 임의 에칭제일 수 있다. 에칭제(205)는 효율적인 시간 동안 사이트-분리된 영역(210) 내의 영역을 에칭하기에 충분하고, 그리고 단지 확산 장벽 재료(202)만을 에칭하며 실리콘 기판(200)은 에칭하지 않는 충분한 농도와 온도이다. 에칭제(205)는 조합적으로 (combinatorially) 변화될 수 있다. 사이트-분리된 영역(210) 내에서 에칭된 영역은 최종적으로 기판(200)상에 개별 태양 전지를 형성하는 영역을 정의한다.

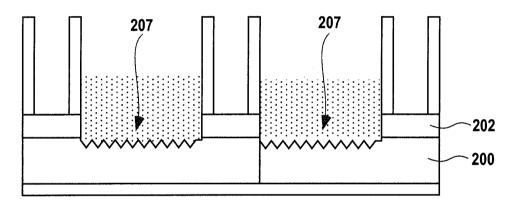

- [0016] 도 1의 흐름도의 블록(104)에서, 노출된 결정 실리콘 기판(200)의 사이트-분리된 영역(210)을 택스처링하여 택스처링된 표면(207)을 갖는 복수의 사이트-분리된 택스처링된 실리콘 영역을 형성한다. 전면 확산 장벽은 에칭되면서 블록(104)의 택스처링 공정을 위한 에칭 마스크로서 역할을 한다. 택스처링 용액, 예를 들면 수산화포타슘(KOH) 및 이소프로필 알코올(IPA) 또는 KOH 및 예컨대 부탄올과 같은 단사슬 알코올을 사용하여 실온에서, 태양 전지의 효율을 최대화하기 위하여 태양 전지 내에서 빛을 포획할 수 있는 택스처링된 실리콘 표면을 생성하기에 충분한 시간 동안, 영역(210)을 택스처링한다. 택스처링 용액은 서로 다른 택스처링 용액을 조합적으로 시험하기 위하여 변화될 수 있다. 화학 성분, 이들 성분의 농도를 변화시키거나, 또는 시간 및 온도와 같은 임의의 공정 조건을 변화시킴으로써 택스처링 용액을 변화시킬 수 있다. 택스처링 공정은 전면 확산장벽(202)을 에칭한 이후에 결정 실리콘 기판(200)을 습식 공정 기구(300)로부터 제거하지 않고 수행될 수 있다. 동일한 기구에서 확산 장벽 에칭 공정(103)과 실리콘 에칭 공정(104) 둘 모두를 수행하는 것은 결정 실리콘 기판의 높은 처리율의 조합 공정법을 가능하게 할 수 있다. 조합적 목적뿐만 아니라 개별 태양 전지 각각의 영역을 형성하기 위한 사이트-분리의 형성을 위하여 습식 공정 기구(300)를 사용하는 것은 또한 조합 방법론의 효율을 증가시킨다.

- [0017] 도 1의 흐름도의 블록(105)에서, 결정 기판을 세정할 수 있다. 세정 공정은 조합 습식 공정 기구(300)를 사용하여 수행될 수 있는데, 즉 이는 블록(104)에서의 텍스처링 이후에 결정 실리콘 기판(200)이 기구 내에 잔류할 수 있음을 의미한다.한 구체 예에서, 세정이 습식 공정 기구(300) 내에서 수행된다면 세정 용액은 조합적으로 변화될 수 있다. 그 대신에, 세정은 도 2D에 도시된 바와 같이 결정 실리콘 기판(200)을 조합 습식 공정 기구(300)로부터 제거한 이후에 기판의 전체 표면에 걸쳐 수행될 수 있다. 전체 기판을 세정하는 것은 욕조 내에서 세정 용액의 침적, 스프레이, 또는 분배에 의해 수행될 수 있다. 세정 공정은 모든 잔류물 또는 금속 오염물을 기판(200)으로부터 제거하기 위하여 수행될 수 있다. 사용되는 세정 용액은 예컨대 묽은 플루오르화수소산 용액, RCA 클린, 또는 피란하(piranha) 클린(황산 및 과산화수소)일 수 있다. 세정은 선택사항이지만본 방법에 의해 형성된 태양 전지의 성능을 향상시킬 수 있다.

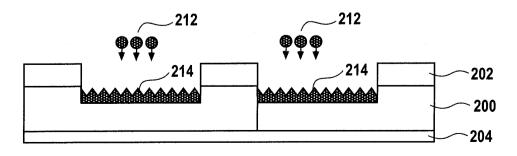

- [0018] 블록(106)에서, 결정 실리콘 기판의 사이트-분리된 영역은 n-도핑된다. 도 2E에 도시된 바와 같이, 도핑은 전 면 확산 장벽(202) 내에 형성된 에칭 패턴에 의하여 자체-정렬된다. 도 2E 및 2F에 제시된 공정에서, 인 n-도 판트(phosphor n-dopant)가 노(furnace) 내에서 기체로부터 상기 노출된 결정 실리콘 기판 내로 확산된다. 본 공정에서, 질소(N2) 기체가 석영 노 내에서 액체 도판트(POCl3)를 통하여 발포(bubble)된다. 본 구체 예에서,

도판트 기체가 노 내부로 흐르는 동안, 결정 실리콘 기판(200)이 다른 기판에 대하여 보트에서 수직으로 배치되고 노 내부에서 약 900℃ 내지 950℃ 범위의 온도까지 약 5 내지 10분 동안 가열될 수 있다. 확산 장벽(202및 204)은 텍스처링된 결정 실리콘 기판의 사이트-분리된 노출 영역 이외의 영역으로 도판트가 확산되는 것을 방지한다. 텍스처링된 결정 실리콘의 도핑된 층(214)이 도 2F에 도시된 바와 같이 형성된다.

- [0019] 대안적인 구체 예에서, 결정 실리콘 기판은 도판트가 액체 용액으로부터 확산되는 조합 습식 공정 기구(300) 내에서 도핑될 수 있다. 본 구체 예에서, 다음과 같은 결정 실리콘 기판(200)의 다중 공정이 조합 습식 공정 기구에서 수행될 수 있다: 블록(103)의 확산 장벽(202)의 에칭, 블록(104)의 결정 실리콘 기판(200)의 텍스처 링, 선택사항인 블록(105)의 세정 공정, 및 블록(106)의 결정 실리콘 기판(200)의 n-도핑. 액체 도판트 용액 은 조합 습식 공정 기구(300)에서 적용되는 경우 조합적으로 변화될 수 있다. 액체 도판트 용액은 도핑을 위 한 인(phosphor)을 함유하며 한 구체 예에서 용매와 POCl<sub>3</sub>의 용액일 수 있다. 그 대신에, 인 n-도판트 (phosphor n-dopant)는 POCl<sub>3</sub> 페이스트로서 적용될 수 있는데 상기 POCl<sub>3</sub> 페이스트는 결정 실리콘 기판(200)의 전면에 스크린 프린트되거나 또는 스핀(spin)되고 그 후 건조될 수 있다. 액체 또는 페이스트를 건조한 이후 에, 기판(200)을 노 내부에 위치시켜 도판트를 결정 실리콘 기판에 확산시킨다. 패터닝된 전면 확산 장벽 (202) 및 후면 확산 장벽(204)은 도판트가 단지 사이트-분리된 텍스처링된 영역(210) 내의 결정 실리콘 기판 (200)의 노출된 표면으로 확산되어 도핑된 영역(214)을 형성하는 것을 보장한다. 기판(200)을 그 후 노 내부 에 위치시키고 텍스처링된 노출된 영역(210)으로 인을 확산시켜 도 2F에 도시된 바와 같이 도핑된 영역(214) 을 형성한다. 한 구체 예에서, 노는 벨트 노일 수 있는데 여기서 상기 기판(200)은 컨베이어 벨트상에 위치하 여 노로 이동되어 기판(200)의 표면상에서 상기 건조된 액체 또는 페이스트로부터의 n-도판트 확산을 수행한 다. 한 실시예에서, 실제 도핑을 위하여 질소 분위기에서 약 15분 동안 약 950℃로 램핑 업(ramping up)하기 전에, 기판(200)이 컨베이어 벨트 상에서 노로 들어가서 모든 유기 오염물을 연소시키기 때문에, 벨트 노는 약 600℃의 온도 및 세정 공기를 가질 수 있다.

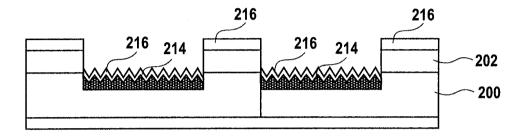

- [0020] 블록(107)에서, 도 2G에 도시된 바와 같이 패시베이션 층(216)이 도핑된 사이트-분리된 영역(214) 상부에 그리고 패터닝된 전면 확산 장벽 층(202) 상부에 형성된다. 패시베이션 층은 모든 절연 물질 예컨대 이산화실리 콘(SiO<sub>2</sub>) 또는 수첨(hydrogenated) 실리콘 질화물(SiN<sub>2</sub>)일 수 있다. 한 구체 예에서, 패시베이션 층은 태양 전지를 위한 반사-방지 코팅(ARC) 또는 투과 보호층일 수 있다. 패시베이션 층(216)은 PECVD, PVD, 또는 ALD로 증착될 수 있다. 패시베이션 층은 조합 CVD, PVD, 또는 ALD 기구에서 조합적으로 변화될 수 있다.

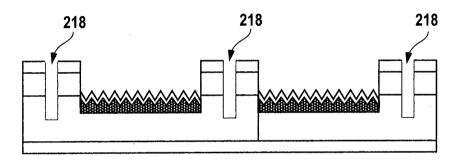

- [0021] 도 2H에서, 스크라이빙(scribing)에 의한 사이트-분리된 태양 전지의 추가적인 분리가 레이저 또는 다이서 (dicer)에 의해 달성될 수 있다. 추가적인 분리는 선택사항이며 태양 전지를 제조하기 위하여 사용되는 공정에 따라 선택될 수 있다. 예컨대, 도판트의 확산이 결정 실리콘 기판의 개별적인 사이트-분리된 텍스처링된 영역들 사이에서 확산 장벽 영역 아래로 연장되는 경우 스크라이빙이 사용될 수 있다.

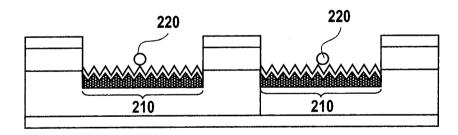

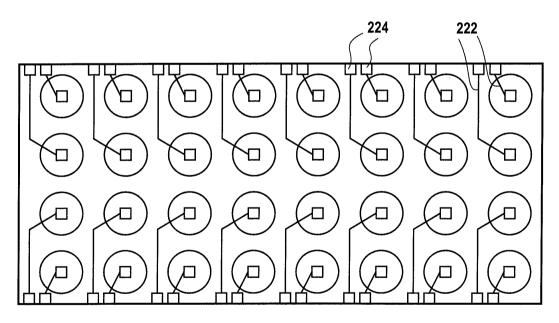

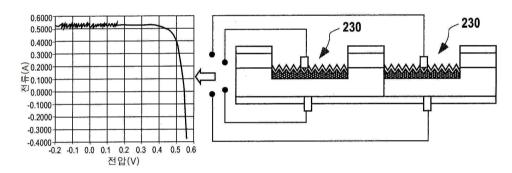

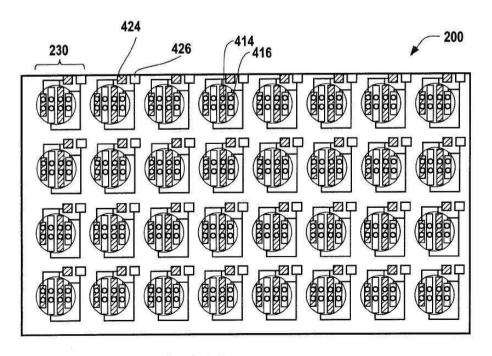

- [0022] 도 1의 흐름도의 블록(108)에서, 전기적 접촉부를 형성하여 결정 실리콘 기판(200)의 사이트-분리된 영역 (210) 각각에서 개별 태양 전지의 형성을 완결한다.결정 실리콘 기판(200)의 전면 및 후면에서의 금속배선 (metallization)에 의한 전기적 접촉부의 형성이 도 2I 내지 도 2P에 도시된다. 도 2I에서, 에칭 페이스트 (220)의 점들이 사이트-분리된 영역(210) 각각의 대략적인 중앙에 분배된다. 에칭 페이스트(220)는, 가열될 때 패시베이션 층(16)을 에칭할 수 있고 결정 실리콘(200)과의 전기적 접촉을 형성하기 위한 전도성 부품을 포함하는 물질이다. 도 2I는 에칭 페이스트(220)의 점이 어떻게 패시베이션 층(216)의 상부에 안착하는가를 보여주는 측면도이다. 도 2J는 에칭 페이스트(220)의 점들 각각이 어떻게 사이트-분리된 영역(210)의 각각의 대략적인 중앙에 위치하는가를 나타낸다. 도 2K에서, 에칭 페이스트(220)와 함께 기판(200)이 가열되어, 사이 트-분리된 영역(210) 각각의 상부의 에칭 페이스트(220)의 점들이 절연 재료로 형성될 수 있는 패시베이션 층 (216)을 통하여 에칭하도록 하여, 결정 실리콘과의 전기적 접촉을 형성하도록 한다. 도 2L은 이러한 공정의 측면도를 나타낸다. 에칭 페이스트(220)는 예컨대 사용되는 페이스트의 종류를 변화시킴으로써 또는 소성 단 계(firing step)의 온도를 변화시킴으로써 조합적으로 평가될 수 있다. 도 2M에서, 전도성 재료가 증착되어 결정 실리콘 기판(200)의 가장자리에 대한 전기 라인(222)을 형성하여 편리한 접촉 포인트(224)를 형성한다. 한 구체 예에서, 전도성 재료는 은(Ag)일 수 있다. 전기 라인(222) 및 접촉 포인트(224)는 스크린 프린팅, 잉 크 젯 프린팅에 의하거나, 또는 그 대신에 섀도우마스크를 통한 PVD에 의해 프린트될 수 있다. 후면 접촉부는 전면 접촉부의 형성을 위하여 사용된 방법과 동일한 방법을 사용하여 형성될 수 있다. 도 2N 및 도 20는 후면 접촉부의 측면도 및 저면도를 각각 나타낸다. 도 2P에서, 결정 실리콘 기판(200)상에 형성된 태양 전지(230) 각각이, 조합적인 스크리닝 목적을 위하여 그 성능을 비교하기 위해, 전기적으로 시험되고 평가된다.

- [0023] 전술한 것과 유사한 방법이 예컨대 선택적 에미터 태양 전지 또는 후면전극 태양 전지와 같은 대안적인 태양 전지를 제조하기 위하여 사용될 수 있다. 후면전극 태양 전지는 결정 실리콘 태양전지를 투과하는 태양빛의 양을 최대화하기 위하여 단지 기판의 후면에 금속배선이 형성되는데 왜냐하면 전면 금속배선에 의해 생성되는 전면의 그림자가 없기 때문이다. 도 1의 흐름도를 참고하면, 블록(101) 내지 블록(107) 및 도 2A 2G에서 앞서 설명한 것과 동일한 공정이 조합 시험 기판상에서 후면전극 태양 전지를 형성하기 위하여 사용될 수 있다. 주된 차이점은 도 1의 흐름도의 블록(108)에서 결정 실리콘 기판의 사이트-분리된 영역 상에서 전기적 접촉부가 형성되는 방법이다.

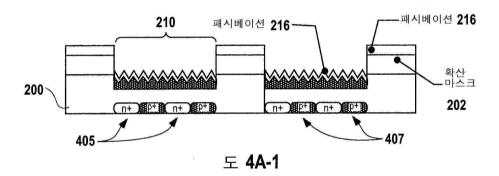

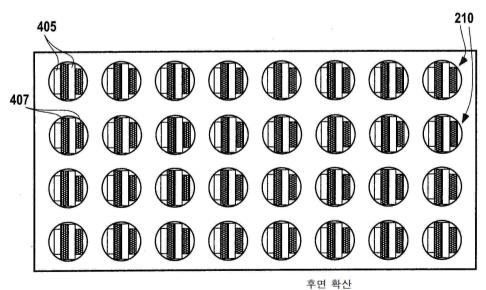

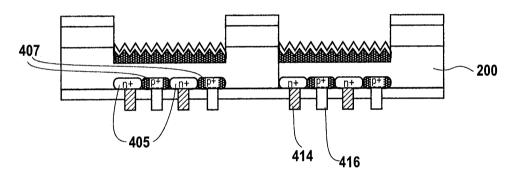

- [0024] 도 4A-1은 도 1의 흐름도의 블록(107)의 전면 페시베이션 공정 이후 그리고 사이트-분리된 태양 전지 영역 (210) 각각의 후면에서 교대하는 n-도핑된 영역(405)과 p-도핑된 영역(407)의 형성 이후의 조합적 결정 실리 콘 시험 기판(200)을 도시한다. 후면 도핑된 영역을 형성하기 위하여, 도 1의 흐름도의 공정(101)에서 형성된 확산 마스크(204)가 후면 도핑 이전에 후면으로부터 제거되거나 또는 단순히 형성되지 않을 수 있다. 이러한 교대하는 n-도핑된 영역(405)과 p-도핑된 영역(407)은 각각의 도핑 공정 동안 기판의 마스크 영역에 대한 포토리소그래피(photolithography)의 사용을 통하여 형성될 수 있다. n-도핑된 영역(405) 각각에 대한 도핑은 도 1의 공정(106)과 관련하여 전술한 바와 같이, 액체, 페이스트, 또는 기체 도판트를 사용하고 그리고 후속하여 열 확산 단계에 의해 수행될 수 있다. p-도판트를 사용하는 것을 제외한 유사한 공정이 p-도핑된 영역(407)을 형성하기 위하여 수행될 수 있다. 도 4A-1은 교대하는 도핑된 영역(405 및 407)을 갖는 두 개의 대표적인 태양 전지 영역(210)의 측면도를 나타내며, 도 4A-2는 사이트-분리된 태양 전지 영역 각각의 상부에서 교대하는 도핑된 영역(405 및 407)을 갖는 기판(200)의 후면의 평면도를 나타낸다. 도핑이 완료된 이후, 도핑공정 동안 형성된 모든 잔류물 또는 포스포실리케이트 유리(phosphosilicate glass)를 제거하기 위하여 기관이 세정될 수 있다.

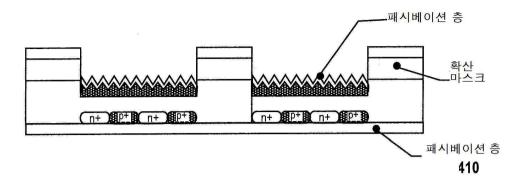

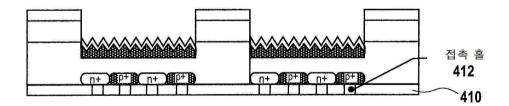

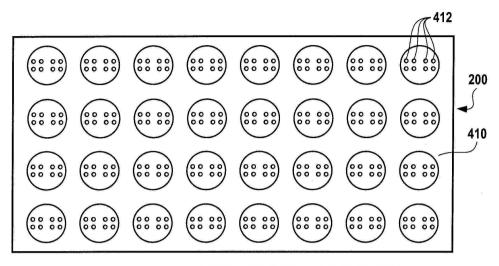

- [0025] 도 4B에서, 패시베이션 층(410)이 결정 실리콘 기판(200)의 후면에 증착될 수 있다. 패시베이션 층(410)은 실리콘 질화물 또는 이산화실리콘과 같은 임의의 절연 재료일 수 있다. 한 구체 예에서 패시베이션 층(410)은 PECVD 증착된 실리콘 질화물일 수 있다. 도 4C는 교대하는 도핑된 영역 상부의 패시베이션 층(410)의 증착 이후 기판(200) 후면의 평면도를 나타낸다.

- [0026] 도 4D에서, 접촉 홀(412)이 결정 실리콘 기판(200)의 후면의 패시베이션 충(410)을 통하여 에칭된다. 접촉 홀(412)이 에칭되어 n-도핑된 영역(405) 및 p-도핑된 영역(407) 각각과의 접촉을 형성한다. 에칭되지 않는 후면 영역을 덮는 마스크를 형성하기 위하여 포토리소그래피 기술이 사용될 수 있다. 에칭제는 패시베이션 충은 에칭할 수 있으나 결정 실리콘 기판(200)의 하부 도핑된 영역은 에칭할 수 없는 액체 용액일 수 있다. 그 대신에, 플라즈마 에칭이 사용될 수 있다. 포토레지스트를 제거한 이후에, 기판(200)의 후면은 도 4E와 같이 보일수 있는데 상기 도 4E는 그 평면도를 나타낸다. 도 4E에서, 예컨대, n-도핑된 영역(405) 및 p-도핑된 영역(407) 각각은 2개의 접촉 홀을 가지지만, 도핑된 영역에 대한 임의 수의 접촉 홀이 생성될 수 있다.

- [0027] 도 4F 및 4G는 금속배선을 통한 접촉을 형성한 이후의 기판(200)을 나타낸다. 제1 금속 라인(414)은 n-도핑된 영역(405) 상부에 형성되며 제2 금속 라인(416)은 태양 전지(230) 각각에 대한 2개의 시험 패드(424 및 426)를 생성하는 p-도핑된 영역(407)의 상부에 형성된다. 시험 패드 각각에 전기 리드(electrical lead)를 연결시 킴으로써, 태양 전지(230) 각각의 전기적 성능이 시험되고 조합적으로 평가될 수 있다.

- [0028] 선택적 에미터 결정 실리콘 태양전지를 또한 도 1의 흐름도에 제시된 방법을 사용하여 형성하고 조합적으로 평가할 수 있다. 선택적 에미터는, 접촉이 태양 전지의 전면에서 형성되는 영역의 하부에서 결정 실리콘 기판이 더욱 고도로 도핑되는 결정 실리콘 태양전지의 유형을 의미한다. 이는 결정 실리콘 태양전지 내의 전자의 재조합을 감소시키고 그에 따라 태양 전지의 효율을 전위적으로 향상시키기 위한 것이다. 일반적으로, 선택적에미터 태양 전지는 2-단계 도핑 공정에 의해 형성되는데, 즉 먼저 광 도핑 영역이 형성되고 후속하여 더욱고농도 도핑된 영역이 형성된다.

- [0029] 한 구체 예에서, 도 2A 2D와 관련하여 앞서 설명한 바와 같이 도 1의 흐름도의 공정(101) 내지 공정(105)은 종래 유형의 결정 실리콘 태양전지의 형성을 위한 공정과 동일할 수 있다. 도 1의 흐름도의 블록(106)에서, 결정 실리콘 기판(200)의 사이트-분리된 영역(210)은 n-도핑된다. 선택적 에미터 태양 전지에 대하여, 이러한 블록(106)에서의 n-도핑은 대안적인 방법을 통하여 수행된다.

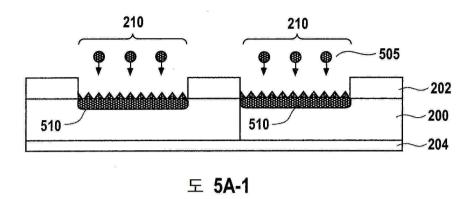

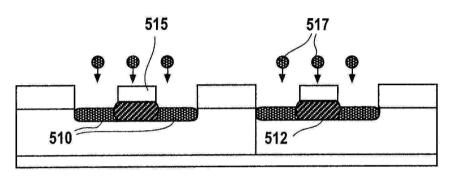

- [0030] 한 특정 구체예에서, 도 5A-1 내지 5A-3은 선택적 에미터 태양 전지의 저농도(lightly) 도핑된 영역 및 고농도(heavily) 도핑된 영역 둘 모두의 형성을 위한 한 가지 방법을 나타낸다. 도 5A-1에서, 결정 실리콘 기판(200)의 사이트-분리된 영역(210)은 인(phosphor)과 같은 n-도판트(505)로 조금 도핑되어 저농도 도핑된 영역

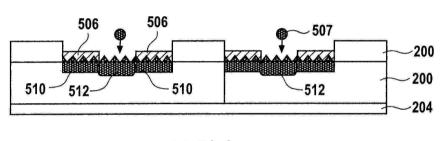

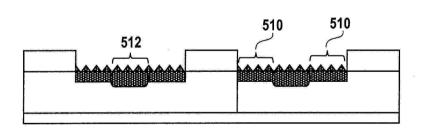

(510)을 형성한다. 전술한 바와 같이, n-도판트를 액체, 페이스트, 또는 기체로서 가하고 그 후 노 내부에서 연소시켜 도판트를 확산 장벽(202)(전면) 및 (204)(후면)에 의해 보호되지 않는 영역에서 기판(200)으로 확산시킬 수 있다. 저농도 도핑된 영역(510)은 약 70-100 옵/스퀘어의 시트 저항(sheet resistance)을 갖도록 도핑될 수 있다. 도 5A-2에서, 결정 실리콘 기판은 더욱 많이 도핑되어 고농도 도핑된 영역(512)을 형성할 수 있다. 고농도 도핑(heavy doping)을 수행하기 위하여, 금속배선이 최종적으로 형성되는 영역에서 사이트-분리된 영역(210)의 상부에 또 다른 도핑 공정이 수행될 수 있다. 먼저 사이트-분리된 영역(210)의 일부분(506)에서 기판 상부에 포토레지스트 마스크를 형성하여 도판트(507)가 저농도 도핑된 영역(510)으로 확산되지 못하도록 함으로써, 더욱 고농도 도핑된 영역(512)을 형성할 수 있다. 도판트(507)는 그 후 기판에 노출되어서 사이트-분리된 영역(210) 내 마스크안된 일부분으로 확산하여 고농도 도핑된 영역(512)을 형성한다. 고농도 도핑된 영역(512)은 약 20-30 옵/스퀘어의 시트 저항을 갖기에 충분한 정도로 도핑된다. 포토레지스트 마스크 (506)를 그 후 도 5A-3에 제시된 바와 같이 완전히 제거하고 기판을 노 내부에 위치시켜 도판트(507)를 고농도 도핑된 영역(512)으로 확산시킨다. 선택적 에미터 태양 전지는 그 후 완결되어 블록(107 및 108)에 대하여 앞서 설명한 방법 중 임의의 것에 의해 조합적으로 가공된 시험 기판을 형성한다.

- [0031] 대안적인 구체 예에서, 도 5B-1 내지 도 5B-3은 추가적인 에칭 단계를 사용하여 선택적 에미터 태양 전지의 저농도 도핑된 영역 및 고농도 도핑된 영역 둘 모두를 형성하는 또 다른 방법을 도시한다. 본 구체 예에서, 블록(104)에서 결정 실리콘 영역의 텍스처링은 도핑 단계 이후에 수행된다. 도 5B-1의 사이트-분리된 영역 (210)은 액체 또는 기체 도판트(505)에 노출되어 저농도 도핑된 영역(510)을 형성한다. 도 5B-2에서 포토레지 스트와 같은 패터닝된 마스크(515)가 해당 기술분야의 통상의 기술자에게 공지된 종래 방법에 의해, 사이트-분리된 영역(210)의 중앙 영역(512) 상부에 형성되었다. 그 후 에칭제(517)를 기판에 도포하여 저농도 도핑된 영역(510)을 에칭시킨다. 영역은 저농도 도핑된 영역(510)에서의 시트 저항을 약 70-100 옴/스퀘어로 조정하 기에 충분한 정도로 에칭된다. 그 후 도판트 페이스트(525)를 도 5C-1에 도시된 바와 같이 사이트-분리된 영 역(210)에서 기판(200)상에 패턴화시키고 후속하여 노 안에서 열에 노출시켜 더욱 많은 도판트를 고농도 도핑 된 영역(512)으로 확산시킨다. 그 후 도판트 페이스트(525)를 제거하고 사이트-분리된 영역(210) 내 노출된 실리콘 기판(200)의 표면을 도 5C-2에서 앞서 설명한 방법에 따라 텍스처링 한다. 텍스처링은 전술한 바와 같 이 습식 조합 공정법 기구를 사용하여 조합적으로 변화될 수 있다. 그 후 전술한 임의 방법을 사용하여 블록 (107)에서 결정 실리콘 기판의 사이트-분리된 영역의 상부에서 패시베이션 층을 형성시킴으로써 태양 전지 시 험 기판을 완성한다. 그 후 전술한 임의 방법을 사용하거나 또는 해당 기술분야의 통상의 기술자에게 공지된 방법을 사용하여 매립된 접촉을 형성함으로써 블록(108)에서 전기적 접촉을 형성한다.

- [0032] 설명된 방법 중 임의의 것에 따라 결정 실리콘 태양전지 시험 기판을 형성한 이후에, 조합적으로 변화된 태양전지를 평가한다. 평가는 시험 기판상의 변화된 태양 전지 각각의 전기적 성능을 측정함으로써 수행된다. 예를 들면, 전지 각각의 전류 대 전압을 측정할 수 있거나 또는 전지의 양자 효율(quantum efficiency)을 결정할 수도 있다. 최선의 성능을 갖는 변화된 태양 전지를 그 후 또 다른 시험 기판상에서 식별하고 시험하거나 또는 제조규모로 규모를 확장시킬 수 있다.

- [0033] 조합 공정법은 기판의 둘 또는 그 이상의 영역에서의 공정을 변화시키는 임의 공정을 포함할 수 있다. 본 발명의 구체 예에서, 조합 방법은 추가적인 변화 및 최적화를 위한, 예를 들면 재료, 공정 조건, 공정 순서, 또는 공정 통합을 식별하기 위한 다중 스크리닝 수준을 포함할 수 있다. 도 6은 조합 방법을 사용하여 결정 실리콘 태양전지의 개선을 위한 3가지의 스크리닝 수준을 나타내는 다이어그램(600)을 도시한다. 다이어그램(600)은 깔때기를 나타내는데, 여기서 1차 스크리닝(610)은 2차 스크리닝(620) 및 3차 스크리닝(630)으로 통과되는 가장 많은 수의 텍스처링 용액 샘플을 포함하며, 상기 3차 스크리닝(630)에서 가장 적은 수의 텍스처링 용액 샘플이 시험된다. 임의의 스크리닝 수준에서 사용되는 샘플의 수는 샘플을 처리하기 위하여 사용되는 기판 또는 기구에 의존한다.

- [0034] 비록 전술한 실시예들이 이해의 명확성 목적을 위하여 다소 상세하게 기재되었지만, 본 발명은 제시된 상세사항에 제한되지 않는다. 본 발명을 실시하게 위한 많은 대체적인 방법이 존재한다. 기술된 실시예들은 예시적인 것이며 제한적인 것이 아니다.

도면

#### 도면1

#### 도면2a

# 도면2b

# 도면2c

# 도면2d

# 도면2e

## 도면2f

# 도면2g

도면2h

도면2i

도면2j

도면2k

도면21

도면2m

도면2n

# 도면20

# 도면2p

# 도면3a

도면3b

도면4a

-1--

도 4A-2

## 도면4b

# 도면4c

후면 패시베이션

# 도면4d

## 도면4e

접촉을 위한 패시베이션 층을 관통하는 에칭 홀

#### 도면4f

### 도면4g

후면 금속배선

# 도면5a

도 5A-2

도 **5A-3**

# 도면5b

도 5B-1

도 **5B-2**

# 도면6