(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5027365号

(P5027365)

(45) 発行日 平成24年9月19日(2012.9.19)

(24) 登録日 平成24年6月29日(2012.6.29)

(51) Int.Cl.

F 1

HO1L 27/115 (2006.01)

HO1L 21/8247 (2006.01)

HO1L 29/792 (2006.01)

HO1L 29/788 (2006.01)

HO1L 21/336 (2006.01)

HO1L 27/10 434

HO1L 29/78 371

請求項の数 19 外国語出願 (全 26 頁)

(21) 出願番号 特願2001-284734 (P2001-284734)

(22) 出願日 平成13年9月19日 (2001.9.19)

(65) 公開番号 特開2002-158302 (P2002-158302A)

(43) 公開日 平成14年5月31日 (2002.5.31)

審査請求日 平成20年7月17日 (2008.7.17)

(31) 優先権主張番号 60/234314

(32) 優先日 平成12年9月20日 (2000.9.20)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 60/242096

(32) 優先日 平成12年10月19日 (2000.10.19)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 60/260167

(32) 優先日 平成13年1月5日 (2001.1.5)

(33) 優先権主張国 米国(US)

(73) 特許権者 593229642

シリコン・ストーリッジ・テクノロジー・

インク

アメリカ合衆国、カリフォルニア州 94

086、サンベール、ソノラ・コート

1171

(74) 代理人 100071010

弁理士 山崎 行造

(74) 代理人 100107799

弁理士 岡田 希子

(74) 代理人 100113402

弁理士 前 直美

(74) 代理人 100114742

弁理士 林 秀男

最終頁に続く

(54) 【発明の名称】低抵抗ソース領域と高ソース結合を持つフローティングゲートメモリセルの半導体メモリアレイ

を形成する自己整合方法、及びそれにより作られたメモリアレイ

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板のフローティングゲートメモリセルの半導体メモリアレイを形成する自己整合方法であって、各メモリセルは、フローティングゲートと、第1の端子と、その間にチャネル領域を持つ第2の端子と、コントロールゲートとを有し、該方法は、

a) 互いに概ね平行であり、第1の方向に延びる基板上に、隣接する各絶縁領域間に活性領域を持つ、複数の離隔した絶縁領域を形成するステップであって、該活性領域は、半導体基板上に絶縁材料の第1の層と、絶縁材料の第1の層上に導電性材料の第1の層を備える、形成ステップと、

b) 互いに概ね平行であり、前記第1の方向と概ね垂直な第2の方向に延びる、前記活性領域及び絶縁領域を横切る複数の離隔した第1のトレンチを形成するステップであって、該第1のトレンチのそれぞれがその中に形成されるくぼみを持つ側壁を有する、形成ステップと、

c) 導電性材料の第1のブロックを形成するために、前記第1のトレンチのそれぞれを導電性材料で満たすステップであって、各活性領域の該第1のブロックについて、

前記第1のブロックは、前記第1の端子の鉛直上に配置され、導電性材料の前記第1の層に隣接し、該第1の層から側面方向に絶縁される、前記第1のトレンチ側壁のくぼみの下に形成される下部と、前記導電性材料の第1の層上に配置され、該第1の層から絶縁され、前記導電性材料の第1の層上に垂直に配置され該第1の層から絶縁された一対の第1端部に終端を有する、該くぼみの上部に形成される上部とを含む、充填ステップと、

10

20

d ) 前記基板に複数の第 1 の端子を形成するステップであって、各前記活性領域では、該第 1 の端子のそれぞれは、導電性材料の前記第 1 のブロックの一つに隣接し、電気的に接続される、形成ステップと、

e ) 前記基板に複数の第 2 の端子を形成するステップであって、各前記活性領域では、該第 2 の端子のそれぞれは、前記第 1 の端子から離隔される、形成ステップと、

f ) 互いに概ね平行であり、前記第 1 のトレンチに概ね平行な複数の離隔した第 2 のトレンチを形成するステップと、

g ) 第 2 のトレンチに導電性材料の第 2 のブロックを形成するステップであって、導電性材料の各第 2 のブロックについて、該第 2 のブロックは、

前記導電性材料の第 1 の層に隣接して配置され、それから絶縁される下部と、

10

前記導電性材料の第 1 の層上に配置され、該第 1 の層から絶縁され、該第 1 の層上に鉛直に配置され該第 1 の層から絶縁される第 2 端部に終端を有する上部とを含み、

各前記第 1 端部は、前記第 2 端部の 1 つに隣接して側面方向に配置され、該第 2 端部から絶縁され、前記導電性材料の第 2 のブロックには前記導電性材料の第 1 の層と前記導電性材料の第 1 のブロックの一部との間に直接配置される部分はない、第 2 のブロックを形成するステップと、

h ) 前記第 1 端部と前記導電性材料の第 1 の層との間に直接、それらの間に電圧結合できる厚さで絶縁材料を形成するステップと、

を有することを特徴とする自己整合方法。

#### 【請求項 2】

20

導電性材料の前記第 1 のブロックは、概ね T 型であることを特徴とする請求項 1 記載の方法。

#### 【請求項 3】

導電性材料の前記第 1 のブロックのそれぞれ上に金属化シリコンの層を形成するステップを更に有することを特徴とする請求項 1 記載の方法。

#### 【請求項 4】

導電性材料の第 1 のブロックを形成する前に、第 1 のトレンチに導電性材料の第 2 の層を形成するステップを更に有することを特徴とする請求項 1 記載の方法。

#### 【請求項 5】

第 1 のトレンチのそれぞれの側壁に沿って絶縁材料の第 2 の層を形成するステップであって、各第 1 のブロックの下部及び上部が絶縁材料の第 2 の層によって導電性材料の第 1 の層から絶縁される、形成ステップを更に有することを特徴とする請求項 1 記載の方法。

#### 【請求項 6】

導電性材料の第 2 のブロックのそれぞれ上に金属化シリコンの層を形成するステップを更に有することを特徴とする請求項 1 記載の方法。

#### 【請求項 7】

第 1 のトレンチの形成ステップは、

導電性材料の第 1 の層上に第 1 の材料の少なくとも一つの層を形成するステップと、

第 1 のトレンチの上部を形成するために、前記第 1 の材料の少なくとも一つの層を通して、選択的にエッチングするステップと、

30

第 1 のトレンチの底表面に沿って第 2 の材料の少なくとも一つの層を形成するステップと、

第 1 のトレンチのそれぞれの側壁上に側壁スペーサを形成するステップと、

導電性材料の第 1 の層の部分を曝すために、第 1 のトレンチのそれぞれの側壁スペーサ間に、前記第 2 の材料の少なくとも一つの層を通してエッチングするステップと、

第 1 のトレンチの底部分を形成するために、導電性材料の第 1 の層の曝された部分をエッチングするステップと、

を有し、側壁くぼみは、第 1 のトレンチの上部と底部の間に形成されることを特徴とする請求項 1 記載の方法。

#### 【請求項 8】

40

50

導電性材料の各第2のブロックの側壁に沿って絶縁材料の側壁スペーサを形成するステップと、

第2の端子のそれぞれ上に金属化シリコンの層を形成するステップであって、金属化シリコンの層のそれぞれは、側壁スペーサの一つに自己整合される、形成ステップと、

を更に有することを特徴とする請求項1記載の方法。

【請求項9】

金属化シリコンの層のそれぞれ上で、その上に自己整合された側壁スペーサに対して導電性材料を形成するステップを更に有することを特徴とする請求項8記載の方法。

【請求項10】

前記側壁スペーサのそれぞれの形成ステップは、側壁スペーサと導電性材料の第2のブロックの側壁との間に、絶縁材料の層を形成するステップを含むことを特徴とする請求項8記載の方法。 10

【請求項11】

第2のトレンチ内に、導電性材料の第2のブロックに隣接して材料の第3のブロックを形成するステップと、

導電性材料の第2のブロックのそれぞれ上に金属化シリコンの層を形成するステップであって、各第2のトレンチのために、材料の第3のブロックの一つの側壁は、導電性材料の第2のブロックの端部に金属化シリコン層の端部を整合する、形成ステップと、

金属化シリコンの層上に絶縁材料の第2の層を形成するステップであって、各第2のトレンチのために、材料の第3のブロックの一つの側壁は、金属化シリコンの端部と導電性材料の第2のブロックの端部のそれぞれとに、絶縁材料の第2の層の端部を整合する、形成ステップと、

を更に有することを特徴とする請求項1記載の方法。 20

【請求項12】

側壁スペーサの対が概ねその間の第2の端子の一つに隣接するが、それとは互いに離隔するように、導電性材料の各第2のブロックの側壁に沿って、絶縁材料の側壁スペーサを形成するステップと、

金属化シリコンの層が側壁スペーサの対応する対によって第2の端子の一つに自己整合されるように、該第2の端子の一つに対応する側壁スペーサ対間の第2の端子の各一つ上に金属化シリコンの層を形成するステップと、 30

導電性材料の第2のブロック上に保護絶縁材料の層を形成するステップと、

活性領域上にパッシベーション材料の層を形成するステップと、

パッシベーション材料を通してコンタクト孔を形成するステップであって、該コンタクト孔は、金属化シリコン層の一つに向かって下方に延伸し、その部分を曝し、側壁スペーサの対応する対によって境界をなす下部を有し、側壁スペーサの対応する対間の間隔より広い上部を有する、形成ステップと、

導電性材料で各コンタクト孔を満たすステップと、

を更に有することを特徴とする請求項1記載の方法。

【請求項13】

前記第1のトレンチのそれぞれは、上部及び下部を有し、上部は下部より大きい幅を有し、 40

各第1のブロック下部は、第1のトレンチの一つの下部の一つに形成され、

各第1のブロック上部は、第1のトレンチの一つの上部の一つに形成されることを特徴とする請求項1記載の方法。

【請求項14】

第1の伝導型の半導体材料の基板と、

それぞれの隣接する絶縁領域対間に活性領域を持つ、概ね互いに平行であり、第1の方向に延びる前記基板上に形成される離隔された絶縁領域と、

前記第1の方向に延びるメモリセル対の縦列を含む前記活性領域のそれであって、該メモリセル対のそれぞれは、 50

第1及び第2の領域の間の基板に形成されるチャネル領域を持つ第2の伝導型を有する該基板で離隔される第1の領域及び第2の領域対と、

前記チャネル領域の一つの一部及び前記第1の領域の一部の鉛直上に配置され、前記チャネル領域の一つの一部及び前記第1の領域から絶縁された電気的に導電性のフローティングゲート対と、

前記基板の前記第1の領域に電気的に接続される電気的に導電性のソース領域であって、前記第1の領域の上に鉛直に配置され、前記フローティングゲート対に側面方向に隣接しかつ該フローティングゲート対から絶縁される下部と、それぞれが前記フローティングゲートの上に延伸し、前記フローティングゲートの一つの上に鉛直に配置されかつ該フローティングゲートの一つから絶縁される第1端部の対を終端とする上部とを有する、ソース領域と、

第1の部分と第2の部分とをそれぞれが有する電気的に導電性のコントロールゲート対であって、第1のコントロールゲート部分はフローティングゲートの一つの側面方向に隣接して配置されかつ該フローティングゲートから絶縁され、第2のコントロールゲート部分は前記フローティングゲートの一つの上に延伸し、該フローティングゲートの一つの上部に鉛直に配置され該フローティングゲートの一つから絶縁される第2端部に終端を有し、前記第1端部のぞれぞれは、前記コントロールゲートが前記フローティングゲートと前記ソース領域の間に直接配置される部分がないように、前記第2端部の一つに側面方向に隣接しかつ該第2端部の一つから絶縁される、電気的に導電性のコントロールゲート対と、前記第1端部と前記フローティングゲートとの間に直接的に配置される絶縁材料であって、前記第1端部と前記フローティングゲートとの間に電圧結合できる厚さを有する絶縁材料とを含む、前記活性領域のそれぞれと、

を備えることを特徴とする電気的にプログラム及び消去可能なメモリ装置のアレイ。

【請求項15】

前記ソース領域上部は、ソース領域下部よりも大きい幅を有することを特徴とする請求項14記載の装置。

【請求項16】

前記ソース領域は、概ねT型の断面を有することを特徴とする請求項15記載の装置。

【請求項17】

第1の伝導型の半導体材料の基板と、

その間にチャネル領域を持つ、基板に形成された第2の伝導型の第1及び第2の離隔領域と、

前記チャネル領域の一部と前記第1の領域の一部の鉛直上に配置され、前記チャネル領域の一部と前記第1の領域から絶縁される電気的に導電性のフローティングゲートと、

前記基板の第1の領域に電気的に接続される電気的に導電性のソース領域であって、前記第1の領域の鉛直上に配置され前記フローティングゲートに側面方向に隣接して配置されかつ該フローティングゲートから絶縁される下部と、前記フローティングゲートの上に延伸し前記フローティングゲートの上に鉛直に配置されかつ該フローティングゲートから絶縁される第1端部に終端を有する上部とを有する、ソース領域と、

第1の部分と第2の部分とを有する電気的に導電性のコントロールゲートであって、第1のコントロールゲート部分は前記フローティングゲートに側面方向に隣接して配置されかつ該フローティングゲートから絶縁され、第2コントロールゲート部分は前記フローティングゲートの上に延伸し、該フローティングゲートの上に鉛直に配置され該フローティングゲートから絶縁される第2端部に終端を有し、前記第1端部と第2端部は前記コントロールゲートが前記フローティングゲートと前記ソース領域の間に直接的に配置される部分がないように互いに側面方向に隣接し絶縁される、電気的に導電性のコントロールゲートと、

前記第1端部と前記フローティングゲートの間に直接配置され、前記第1端部と前記フローティングゲートの間に電気結合を生ずる厚さを有する絶縁材料と

を備えることを特徴とする電気的にプログラム及び消去可能なメモリ装置。

10

20

30

40

50

**【請求項 1 8】**

前記ソース領域上部は、前記ソース領域下部よりも大きい幅を有することを特徴とする請求項 1 7 記載の装置。

**【請求項 1 9】**

前記ソース領域は、概ね T 型の断面を有することを特徴とする請求項 1 8 記載の装置。

**【発明の詳細な説明】****【0 0 0 1】****【発明の属する技術分野】**

本発明は、スプリットゲートタイプのフローティングゲートメモリセルの半導体メモリアレイを形成する自己整合方法に関する。また、本発明は、前述のタイプのフローティングゲートメモリセルの半導体メモリアレイに関する。

10

**【0 0 0 2】****【従来の技術】**

そこに電荷を蓄電するためのフローティングゲートを用いる不揮発性半導体メモリセル、及び半導体基板に形成されるそのような不揮発性メモリセルのメモリアレイは、この技術では周知である。典型的に、そのようなフローティングゲートメモリセルは、スプリットゲートタイプ若しくはスタックゲートタイプ、又はそれらの組み合わせであった。

**【0 0 0 3】**

半導体フローティングゲートメモリセルアレイの製造性に直面する問題の一つは、特にメモリセルの大きさがスケールダウンされるときにおける、そのようなソース、ドレン、コントロールゲート、及びフローティングゲートのような種々の構成要素の整合であった。半導体処理の統一の設計ルールが減少するにつれて、最も小さいリソグラフィックの特徴を縮小し、正確な整合の必要性が一層重大になる。種々のパーツの整合もまた、半導体製品の製造の歩留まりを決定する。

20

**【0 0 0 4】**

自己整合（セルフアライメント）は周知技術である。自己整合は、その特徴がそのステップ処理で互いに關して自動的に整合されるように、1 以上の材料を含む 1 以上のステップを処理する技術に關連する。したがって、本発明は、フローティングゲートメモリセルタイプの半導体メモリアレイの製造を達成する自己整合の技術を使用する。

**【0 0 0 5】**

30

**【発明が解決しようとする課題】**

メモリセル寸法がスケールダウンされるとき、2 つの主要な問題がしばしば関与する。第一に、ソース線の抵抗が、メモリセルの寸法が小さくなるにつれて増加し、より高い抵抗は、読み取りイベント中望ましいセル電流を抑制する。第二に、より小さいメモリセルの寸法は、ソースとビット線結合間のより低い突抜け電圧  $V_{PT}$  を結果として生じる。その電圧は、プログラムイベント中の達成可能な最大フローティングゲート電圧  $V_{fg}$  を制限する。フローティングゲート電圧  $V_{fg}$  は、ソースとフローティングゲート間にある結合酸化膜層を通して、ソース領域からの電圧結合を通じて達成される。ソース側注入機構では、より高い  $V_{fg}$  (及び、従って、より高い突抜け電圧  $V_{PT}$ ) は、十分なホットキャリア注入率に欠くことができない。

40

**【0 0 0 6】****【課題を解決するための手段】**

本発明は、(T 型) ソース領域を提供することによって、上記課題を解決する。そこでは、より広い伝導性上部が、ソース線抵抗を減ずるが、ソース線のより狭い下部は、より小さいメモリセル結合構造を容易にする。また、メモリセル構造は、底部結合酸化物を通しての結合の他、フローティングゲートの上部上の酸化物を通してフローティングゲートへのソース電圧の結合を容易にする。それは、ソース電極とフローティングゲートの間の結合係数を高める。

**【0 0 0 7】**

本発明は、半導体基板のフローティングゲートメモリセルの半導体メモリアレイを形成す

50

る自己整合方法である。そして、各メモリセルは、フローティングゲートと、第1の端子と、その間にチャネル領域を持つ第2の端子と、コントロールゲートとを有する。その方法は、以下のステップを含む：

a) 互いに概ね平行であり、第1の方向に延びる基板上に、隣接する各絶縁領域間に活性領域を持つ、複数の離隔された絶縁領域を形成するステップであって、該活性領域は、半導体基板上に絶縁材料の第1の層と、絶縁材料の第1の層上に導電性材料の第1の層を備える、形成ステップ、

b) 互いに概ね平行であり、前記第1の方向と概ね垂直な第2の方向に延びる、前記活性領域及び絶縁領域を横切る複数の離隔された第1のトレンチを形成するステップであって、該第1のトレンチのそれぞれがその中に形成されるくぼみを持つ側壁を有する、形成ステップ、

c) 導電性材料の第1のブロックを形成するために、前記第1のトレンチのそれぞれを導電性材料で満たすステップであって、各活性領域の該第1のブロックのために、前記第1のブロックは、導電性材料の前記第1の層に隣接し、それから絶縁される前記第1のトレンチ側壁のくぼみの下に形成される下部と、該くぼみの上部に形成される上部とを含む、充填ステップ、

d) 前記基板に複数の第1の端子を形成するステップであって、各前記活性領域では、該第1の端子のそれぞれは、導電性材料の前記第1のブロックの一つに隣接し、電気的に接続される、形成ステップ、

e) 前記基板に複数の第2の端子を形成するステップであって、各前記活性領域では、該第2の端子のそれぞれは、前記第1の端子から離隔される、形成ステップ。

#### 【0008】

本発明のもう一つの面では、電気的にプログラム及び消去可能なメモリ装置は、第1の伝導型の半導体材料の基板と、その間にチャネル領域を持つ、第1及び第2の離隔領域と、前記基板の一面に配置される第1の絶縁層と、前記第1の絶縁層の一面に配置され、前記チャネル領域の一部と前記第1の領域の一部を越えて延伸する電気的に導電性のフローティングゲートと、前記基板の第1の領域の一面に配置され、それと電気的に接続される電気的に導電性のソース領域とを含む。そのソース領域は、前記フローティングゲートに隣接して配置され、それから絶縁される下部と、前記フローティングゲートの一面に配置され、それから絶縁される上部とを有する。

#### 【0009】

本発明のまだ1以上の面では、電気的にプログラム及び消去可能なメモリ装置のアレイは、第1の伝導型の半導体材料の基板と、それぞれの隣接する絶縁領域対間に活性領域を持つ、概ね互いに平行であり、第1の方向に延びる前記基板上に形成される離隔された絶縁領域と、前記第1の方向に延びるメモリセル対の縦列を含む前記活性領域のそれぞれとを含む。前記メモリセル対のそれぞれは、前記第1及び第2の領域の間の基板に形成されるチャネル領域を持つ第2の伝導型を有する該基板で離隔される第1の領域及び第2の領域対と、前記チャネル領域上に含む前記基板の一面に配置される第1の絶縁層と、それそれが前記第1の絶縁層の一面に配置され、前記チャネル領域の一つの一部及び前記第1の領域の一部を超えて延伸する電気的に導電性のフローティングゲート対と、前記基板の前記第1の領域の一面に配置され、それに電気的に接続される電気的に導電性のソース領域とを含む。そのソース領域は、前記フローティングゲート対に隣接して配置され、それから絶縁される下部と、前記フローティングゲート対の一面に配置され、それから絶縁される上部とを有する。

#### 【0010】

本発明の他の目的及びその特徴は、明細書の概観、特許請求の範囲及び添付図面によって明らかになるであろう。

#### 【0011】

##### 【発明の実施の形態】

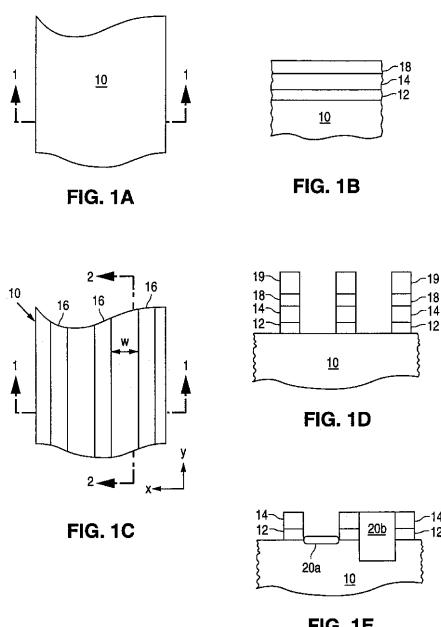

図1Aには、好ましくはP型であり、周知技術である半導体基板の平面図が示される。二

10

20

30

40

50

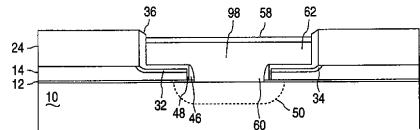

酸化ケイ素(酸化物)のような絶縁材料の第1層12は、図1Bに示されるようにその上に配置される。第1の絶縁層12は、二酸化ケイ素(以下、「酸化物」という)の層を形成して、酸化又は蒸着(例えば、化学蒸着法又はCVD)のような周知技術によって基板10上に形成される。ポリシリコン(FGポリ)の第1層14は、絶縁材料の第1層12の上に蒸着される。第1の絶縁層12上への第1のポリシリコン層14の蒸着及び形成は、低圧CVD又はLPCVDのような周知の処理によってなされ得る。窒化ケイ素層18(以下、「窒化物」という)は、好ましくはCVDによって、ポリシリコン層14上に蒸着される。この窒化物層18は、分離形成中、活性領域を画定するために用いられる。勿論、前述のパラメータ及び以下に記述されるパラメータのすべては、設計ルール及びプロセス技術生成に依存する。ここに記述されるのは0.18ミクロン処理のものである。しかしながら、本発明が特定のプロセス技術生成にも以下に記述される処理パラメータの特定の値にも制限されることは、当業者に理解されるだろう。

#### 【0012】

第1の絶縁層12、第1のポリシリコン層14、及び窒化ケイ素18が一度形成されると、適当なフォトレジスト材料19は、窒化ケイ素18上に適用され、マスキングステップは、ある領域(ストライプ16)からフォトレジスト材料を選択的に取り除くために実行される。フォトレジスト材料19が取り除かれると、窒化ケイ素18、ポリシリコン14及び基礎をなす絶縁材料12は、図1Cに示されるように、一般的エッティング技術(すなわち、異方性エッティング処理)を用いて、Y方向又は縦列方向に形成されるストライプ16にエッティングされる。隣接するストライプ16間の距離Wは、用いられる処理の最小のリソグラフィック特徴と同じくらい小さくできる。フォトレジスト19が取り除かれないと、窒化ケイ素18、第1のポリシリコン領域14及び基礎をなす絶縁材料12が維持される。結果として生じる構造は、図1Dに示される。記述されるように、絶縁領域の形成における2つの実施例、すなわち、LOCOS及びSTIがある。STI実施例では、エッティングは、予め決められた深さまで基板10中へ続く。

#### 【0013】

その構造は、更に、残存するフォトレジスト19を取り除くために、処理される。それから、二酸化ケイ素のような絶縁材料20a又は20bは、その領域又は「溝」16に形成される。窒化物層18は、図1Eに示される構造を形成するために、選択的に取り除かれる。絶縁体は、狭い領域酸化物20aを結果として生じる周知のLOCOS処理(例えば、露出基板を酸化することによって)を介して形成され得る。あるいは、それは、領域20bに形成される二酸化ケイ素を結果として生じる浅トレンチ処理(STI)(例えば、酸化物層を蒸着し、その後、化学機械研磨又はCMPエッティングによって)を介して形成され得る。LOCOS形成の間、スペーサが狭い領域の酸化物の形成中ポリ層14の側壁を保護するために必要であり得ることに注意されたい。

#### 【0014】

残存する第1のポリシリコン層14及び基礎をなす第1の絶縁材料12は、活性領域を形成する。したがって、この点において、基板10は、LOCOS絶縁材料20a又は浅トレンチ絶縁材料20bのいずれかを形成する絶縁領域を持つ活性領域及び絶縁領域の代わりのストライプを有する。図1EがLOCOS領域20a及び浅トレンチ領域20bの両方の形成を示すけれども、LOCOS処理(20a)又は浅トレンチ処理(20b)のただ一つのみが使用される。好ましい実施の形態では、浅トレンチ20bが形成される。より小さい設計ルールでより正確に形成され得るので、浅トレンチ20bが望ましい。

#### 【0015】

図1Eの構造は、非自己整合方法によって形成される構造よりもコンパクトである自己整合構造を表す。周知及び従来のものである図1Eに示される構造を形成する非自己整合方法は、以下のとおりである。絶縁体の領域20は、最初に基板10に形成される。これは、基板10上に窒化ケイ素の一層を蒸着し、フォトレジストを蒸着し、基板10の選択的部分を曝すために第1のマスキングステップを用いて窒化ケイ素をかたどり、シリコントレンチ形成及びトレンチ充填が含まれるLOCOS処理又はSTI処理のいずれかを用い

10

20

30

40

50

て曝された基板 10 を酸化することによってなされ得る。その後、窒化ケイ素は取り除かれ、二酸化ケイ素の第 1 層 12 は、(ゲート酸化物を形成するために) 基板 10 の一面に蒸着される。ポリシリコンの第 1 層 14 は、ゲート酸化物 12 の一面に配置される。ポリシリコンの第 1 層 14 は、第 2 のマスキングステップを用いてかたどられ、選択的部分が取り除かれ。従って、ポリシリコン 14 は、絶縁の領域 20 で自己整合されず、第 2 のマスキングステップが要求される。さらに、追加のマスキングステップは、ポリシリコン 14 の寸法が絶縁の領域 20 に関して整合耐性を有することを要求する。非自己整合方法が窒化物層 18 を利用しないことに注意されたい。

【0016】

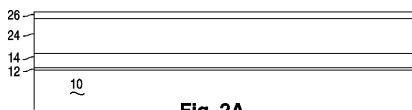

自己整合方法か非自己整合方法のいずれかを用いて作られる図 1 E に示される構造で、その構造は、更に以下のように処理される。図 1 B 及び 1 E の構造に直交する図からその構造を示す図 2 A において、本発明の次のステップが示される。窒化ケイ素(以下、「窒化物」という)のような厚い絶縁層 24 がその構造上に形成され、その後、ポリシリコン(以下、「ポリ」という)のような薄い保護層 26 の形成が続く。結果として生じる構造は図 2 A に示される。

【0017】

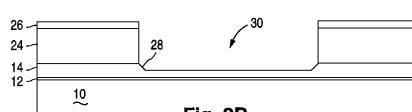

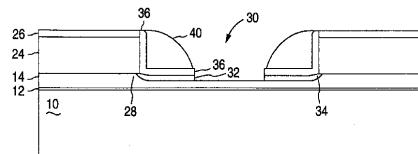

従来のフォトリソグラフィマスキング操作は、ポリ層 26 の上部に適用されるフォトレジストで実行される。ストライプ(すなわち、マスキング領域)が X 又は横列方向に画定されるマスキングステップが適用される。隣接するストライプ間の距離は、製作される装置のニーズによって決定されるサイズであり得る。フォトレジストは、画定されたマスク領域、すなわち、横列方向のストライプで取り除かれ。その後、取り除かれたフォトレジストの基礎となるポリ層 26 は、基礎をなす窒化物層 24 の部分を曝すために、従来の異方性ポリエッチング処理を用いてストライプにエッチングされる。それから、ポリ層 14 の部分を曝すための窒化物層 24 の曝された部分を取り除くために、異方性窒化物エッチング処理が実行される。曝されたポリ層 14 のちょうど上部を取り除き、残存する窒化物層 24 に比較してポリ層 14 にわずかに凹所を設け、窒化物層 24 に接するポリ層 14 の傾斜部分 28 を形成するために、任意のポリエッチング処理が続き得る。そのようなミラーメモリセル対のそれぞののために、これらのエッチング処理は、ポリシリコン層 14 へ下方に(好ましくは、わずかにその中に)延伸する一つの第 1 のトレンチ 30 の形成をもたらす。残存するフォトレジストが取り除かれ、図 2 B に示される構造をもたらす。

【0018】

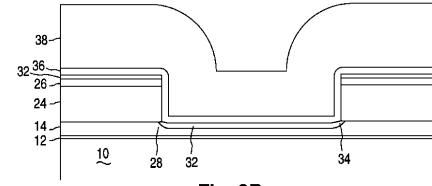

二酸化ケイ素(以下、「酸化物」という)のような絶縁材料の層 32 は、例えば、熱酸素処理を用いてその構造の上に形成される。トレンチ 30 におけるポリ層 14 上に形成される酸化物層 32 の部分は、トレンチ 30 内部の酸化物層 32 にレンズ形状を供給して、ポリ層 14 の傾斜部分 28 によりもたらされる部分 34 を出現させた。結果として生じる構造は図 2 C に示される。

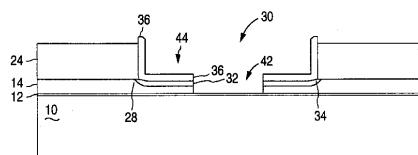

【0019】

絶縁スペーサ 40 は、トレンチ 30 内に形成される(図 2 E)。構造の外形上に材料を蒸着し、その後、異方性エッチング処理(例えば、RIE)によるスペーサの形成は、当該技術では周知である。それによって、材料は、構造の水平表面上から取り除かれるが、材料は、構造の垂直方向表面上に十分にそのまま残っている。スペーサ 40 は、あらゆる誘電材料から形成され得る。好ましい実施の形態では、スペーサ 40 は、次の方法で窒化物から形成される。絶縁材料(例えば、酸化物)の薄い層 36 は、好ましくは化学蒸着法(CVD)処理を用いて図 2 C の構造上に形成される。絶縁材料(例えば、窒化物)の厚い層 38 は、図 2 D に示されるように、好ましくは従来の窒化物蒸着処理によって構造上に形成される。これは、エッチングステップをして酸化物層 36 を用いる厚い窒化物エッチング処理によって続けられる。このエッチング処理は、トレンチ 30 の側壁に沿って側壁スペーサ 40 を除いて、すべての窒化物層 38 を取り除く。それから、エッチングステップとしてポリ層 26 を用いる異方性酸化物エッチング処理が実行される。この酸化物エッチングは、窒化物層 24 上にある酸化物層 36 及び 32 の曝された部分を取り除く。また、酸化物工

10

20

30

40

50

ツチングは、トレンチ 3 0 の中心でポリ層 1 4 の部分を曝すために、スペーサ 4 0 間のトレンチ 3 0 で曝される酸化物層 3 6 及び 3 2 の部分を取り除く。結果として生じる構造は、図 2 E に示される。

【 0 0 2 0 】

厚い窒化物エッチング処理は、トレンチ 3 0 からスペーサ 4 0 を取り除くために実行される。ポリエッチング処理は、窒化物層 2 4 を曝すポリ層 2 6 を取り除き、酸化物層 1 2 を曝すトレンチ 3 0 の下心においてポリ層の曝された部分を取り除くために、実行される。図 2 F に示されるように、トレンチ 3 0 はそれぞれ、ポリ層 1 4 並びに酸化物層 3 2 及び 3 6 によって境界をなす狭い下部 4 2 と、酸化物層 3 6 によって境界をなすより広い上部 4 4 とを有する。スペーサ 4 0 がポリ層 1 4 の部分を取り除くポリエッチング処理後に取り除かれ得ることに注意されたい。10

【 0 0 2 1 】

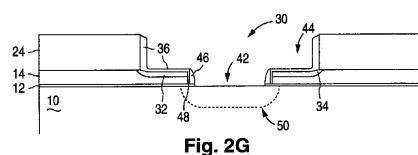

適当なイオン注入が、構造の全表面にわたってなされる。イオンがトレンチ 3 0 内の第 1 の二酸化ケイ素層 1 2 に浸透するのに十分なエネルギーを有すると、それらは、基板 1 0 内の第 1 の領域（端子）5 0 を形成する。すべての他の領域では、イオンは、効力を有しない既存の構造によって吸収される。絶縁スペーサ 4 6（例えば、酸化物）は、トレンチ 3 0 の下部 4 2 の側壁上に形成される。好ましくは、酸化物スペーサ 4 6 形成は、トレンチ 3 0 内で曝されるポリシリコン層 1 4 の側面上に絶縁側壁層 4 8（酸化物）を最初に形成することによって（すなわち、構造を酸化することあるいは CVD によって）、先行される。それから、酸化物は、構造上に形成され（すなわち、CVD 処理）、その後、より低いトレンチ部分 4 2 の側壁上に形成される酸化物スペーサ 4 6 を除いて、構造上に形成される酸化物を取り除く酸化物異方性エッチングが続く。また、この酸化物形成及びエッチング処理は、トレンチ上部 4 4 における酸化物層 3 6 の垂直部分の厚さに加える。異方性エッチングはまた、基板 1 0 を曝すために、スペーサ 4 6 間におけるトレンチ 3 0 の底部において酸化物層 1 2 の部分を取り除くのと同様に、酸化物層 3 6 の上部を取り除き、酸化物層 3 2 上の酸化物層 3 6 の部分を薄くする。結果として生じる構造は図 2 G に示される。20

【 0 0 2 2 】

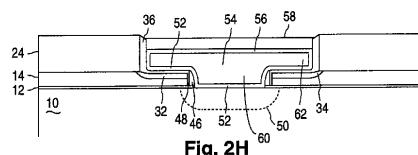

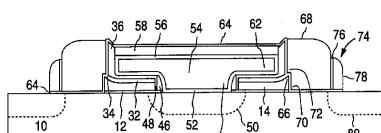

曝された基板 1 0 によく付着する窒化チタンのような導電層 5 2 は、全体構造上に形成される。それは、その中にトレンチ 3 0 の側壁と曝された基板 1 0 を一列に並べる。これは、トレンチ 3 0 内の導電性ブロック 5 4 の形成によって続けられる。それは、構造上にタンゲステンのような導電材料を蒸着することによって形成され、導電性ブロック 5 4 でトレンチ 3 0 を満たすために、タンゲステンプラナリゼーション処理（好ましくは CMP）が続く。タンゲステンエッチバックステップは、トレンチ 3 0 の外部のあらゆるタンゲステンを取り除き、好ましくは、酸化物層 3 6 の上部以下に導電性ブロック 5 4 の上面を画定するために続く。導電層 5 6（窒化チタン）は、トレンチ 3 0 の導電性ブロック 5 4 上の導電層 5 6 を除いて、蒸着された窒化チタンを取り除く平坦化処理（CMP）によって続けられ、好ましくは、構造上に窒化チタンを蒸着することによって、導電性ブロック 5 4 上に形成される。窒化チタンエッチングは、導電層 5 6 が酸化物層 3 6 の上部以下に凹所を設けるように実行される。絶縁材料（酸化物）の層 5 8 は、その構造上に形成され、導電層 5 6 上のその部分を除き、蒸着された酸化物を取り除くために、プラナリゼーション処理（CMP）及び酸化物エッチング処理が続く。結果として生じる構造は図 2 H に示される。そこでは、狭い／広いトレンチ部分 4 2 / 4 4 は、狭い下部ブロック部分 6 0 及びより広い上部ブロック部分 6 2 を持つ概ね T 型のタンゲステン導電性ブロック 5 4 を結果として生じる。3040

【 0 0 2 3 】

第 2 のトレンチ 6 3 は、メモリセルのセット対間で、次の方法で第 1 のトレンチ 3 0 に隣接して形成される。窒化物層 2 4 は、図 2 I に示されるように、ポリ層 1 4 及び酸化物層 3 2 の部分を曝すために、好ましくは、等方性エッチング処理を用いて取り除かれる。ポリエッチング処理（すなわち、ドライエッチング）は、ポリ層 1 4 の曝された部分を取り50

除き、酸化物層 12 を曝すために、続けられる。それから、酸化物層 12 の曝された部分は、基板 10 を曝して制御された酸化物エッチングを介して取り除かれる。絶縁層 64 、好みしくは、酸化物は、全体構造上に形成され、図 2 J に示される構造を結果として生じる。酸化物層 32 の上げ部分 34 は、層 14 が酸化物層 64 と接するポリ層 14 の上部に延伸する鋭い端部の形成を結果として生じる。

【 0024 】

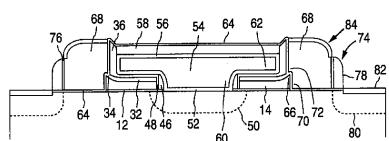

コントロールゲートポリblockは、以下の方法で第 2 のトレンチ 63 に形成される。ポリシリコンの厚い層は、構造上に蒸着され、その後、異方性ポリエッチング処理が続く。その処理は、酸化物層 64 の垂直方向部分に対して形成されるポリスペーサ (block) 68 を除き、すべての蒸着されたポリシリコンを取り除く。ポリblock 68 は、ポリ層 14 に直接隣接して蒸着される下部 70 と、鋭い端部 66 を含むポリ層 14 の部分上に延びる上部 72 とを有する。ポリblock 68 は、酸化物層 64 及び 32 によってポリ層 14 から絶縁される。結果として生じる構造は、図 2 K に示される。

10

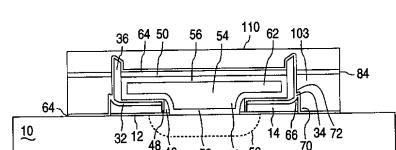

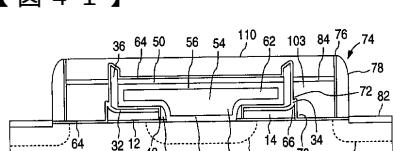

【 0025 】

絶縁スペーサ 74 は、ポリblock 68 に隣接して形成され、材料の 1 以上の層からなる。好みしい実施の形態では、絶縁スペーサ 74 は、酸化物の薄い層 76 を最初に蒸着することによって、材料の 2 つの層から作られ、その後、構造上への窒化物の蒸着が続く。異方性窒化物エッチングは、窒化物スペーサ 78 を残して、蒸着された窒化物を取り除くために実行される。イオン注入 ( 例えは、N+ ) は、第 1 の領域 50 が形成されるのと同じ方法で、基板に第 2 の領域 ( 端子 ) 80 を形成するために用いられる。基板 10 及び第 2 の領域 80 を曝すための酸化物層 64 の曝された部分と同様に、酸化物層 76 の曝された部分を取り除く、制御された酸化物エッチングが続く。結果として生じる構造は図 2 L に示される。

20

【 0026 】

金属化シリコン (シリサイド) の層 82 は、基板上にタンゲステン、コバルト、チタン、ニッケル、白金、又はモリブデンのような金属を蒸着することによって、ポリblock 68 上に金属化シリコン 84 の層とともに、側壁スペーサ 74 の次に基板 10 の上部に形成される。構造はアニールされ、シリサイド 82 を形成するために、基板の曝された上部へ、及び、金属化シリコンを形成するために、ポリblock の曝された上部へ、熱い金属が流れで浸透するのを可能にする。残りの構造上に蒸着される金属は、金属エッチング処理によって取り除かれる。基板 10 上の金属化シリコン領域 82 は、自己整合シリサイド ( すなわち、salicide ) と呼ばれ得る。なぜならば、それは、スペーサ 78 によって第 2 の領域 80 に自己整合されるからである。結果として生じる構造は図 2 M に示される。

30

【 0027 】

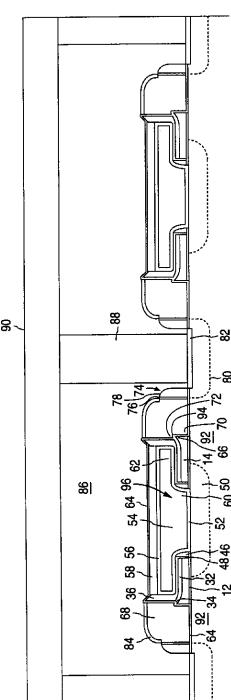

BPSG 86 のようなマスキングステップが、全体構造をカバーするために用いられる。マスキングステップは、シリサイド領域 82 上のエッチング領域を画定するために実行される。BPSG 86 は、対をなすメモリセルの隣接するセット間に形成されるシリサイド領域 82 上に理想的に真中に置かれ、それに向けて下方に延伸するコンタクト孔を生成するために、マスク領域に選択的にエッチングされる。コンタクト孔は、コンタクト導体 88 を形成するために、金属蒸着及びプラナリゼーションエッチバッくによって導体金属で満たされる。シリサイド層 82 は、導体 88 と第 2 の領域 80 の間の伝導を容易にする。ビット線 90 は、メモリセルの縦列にすべての導体 88 とともに接続するために、BPSG 86 上への金属マスキングによって加えられる。最終的なメモリセル構造は図 2 N に示される。

40

【 0028 】

図 2 N に示されるように、第 1 及び第 2 の領域 50 / 80 は、( 当業者は、ソース及びドレインが動作中切り替えられ得ることを知っている ) 各セルのソース及びドレインを形成する。各セルのチャネル領域 92 は、ソース及びドレイン 50 / 80 間にある基板の部分である。ポリblock 68 は、コントロールゲートを構成し、ポリ層 14 は、フローティングゲートを構成する。酸化物層 32 、 36 、 46 及び 48 は、ソース 96 からそれを絶

50

縁するために、フローティングゲート 14 に隣接してその上に配置される絶縁層を共に形成する。酸化物層 36 及び 64 は、コントロールゲート 68 からソース線 96 を絶縁する絶縁層を共に形成する。コントロールゲート 68 は、第 2 の領域 80 の端部に整合される一側面を有し、チャネル領域 92 の部分上に配置される。コントロールゲート 68 は、(酸化物層 64 によってそれから絶縁される) フローティングゲート 14 に隣接して配置される下部 70 と、(酸化物層 64 によってそれから絶縁されるポリ層 14 に隣接する部分上に配置される(延伸する) 突き出た上部とを有する。切欠き(ノッチ) 94 は、突き出た部分 72 によって形成される。そこでは、フローティングゲートの鋭い端部 66 が、ノッチ 94 に延伸する。各フローティングゲート 14 は、チャネル領域 92 の一部上に配置され、コントロールゲート 68 によって一端で部分的に重ねられ、他端で第 1 の領域 50 を部分的に重ねる。導電性ブロック 54 及び導電層 52/56 はともに、メモリセルの縦列の向こう側に延伸するソース線 96 を形成する。ソース線 96 の上部 62 は、フローティングゲート 14 上に延びるが、それから絶縁される。一方、ソース線 96 の下部 60 は、フローティングゲート 14 に隣接するが、それから絶縁される。図 2N に示されるように、本発明の処理は、互いに反映するメモリセルの対を形成する。反映されるメモリセルの対は、酸化物層 76、窒化物スペーサ 78 及び BPSG 86 によって他のセル対から絶縁される。

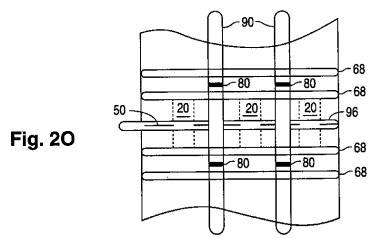

#### 【0029】

図 2Oにおいて、結果として生じる構造及び第 2 の領域 80 へのビット線 90 の配線が示される。第 2 の領域 80 の制御線 68 は、X 又は横列方向に走り、そのソース線 96 は、基板 10 内の第 1 の領域 50 に接続される。ソース線 96 (当業者によって理解されるべきであるように、用語「ソース」は、用語「ドレイン」と交換可能である) が全体の横列方向に基板 10 と接触する、すなわち、絶縁領域と同様に活性領域と接触するけれども、ソース線 96 は、基板 10 の第 1 の領域 50 のみに電気的に接続する。加えて、「ソース」線 96 が接続される各第 1 の領域 50 は、2 つの隣接するメモリセル間で共有される。同様に、ビット線 90 が接続される各第 2 の領域 80 は、メモリセルの異なるミラーセットから隣接するメモリセル間で共有される。

#### 【0030】

その結果は、フローティングゲート 14 と、フローティングゲート 14 にすぐ隣接するがそれから離隔され、同列の他のメモリセルのコントロールゲートに接続する横列方向の長さに沿って走るコントロールゲート 68 と、同列方向のメモリセルの第 1 の領域 50 の対に接続する横列方向に沿って同じく走るソース線 96 と、縦列又は Y 方向に沿って走り、同列方向のメモリセルの第 2 の領域 80 の対に接続するビット線 90 とを有するスプリットゲートタイプの複数の不揮発性メモリセルである。コントロールゲート、フローティングゲート、ソース線、及びビット線の形成は、すべて自己整合される。不揮発性メモリセルは、米国特許第 5,572,054 号に開示されるように、すべてのゲートトンネルを制御するために、フローティングゲートを有するスプリットゲートタイプのものである。その開示は、不揮発性メモリセルの操作及びそれによって形成されるアレイに関して、参考によりここに組み込まれる。

#### 【0031】

本発明は、T 型導電性ブロック 52 のより広い上部 62 のために、ソース線抵抗の減少を示すが、T 型導電性ブロック 52 のより狭い底部 60 (すなわち、ソース線の T 型を形成する上部及び下部 62/60 間の第 1 のレンチ 30 の側壁のくぼみ) のために、メモリセル寸法のより小さいスケーリングをまだ提供する。上部 62 は、また、(酸化物層 46/48 を通して下部 60 を介し、酸化物層 12 を通して第 1 の領域 50 を介する結合に加えて、) 酸化物層 32/36 を通してソース線 96 からフローティングゲート 14 までのソース電圧の結合を可能にする、フローティングゲート 14 上に延びるが、それから絶縁される。したがって、電源電極とフローティングゲートの間の結合係数が向上される。

#### 【0032】

第 1 の代わりの実施の形態

10

20

30

40

50

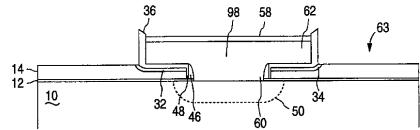

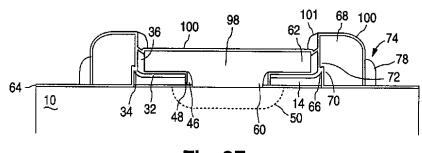

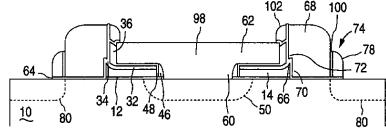

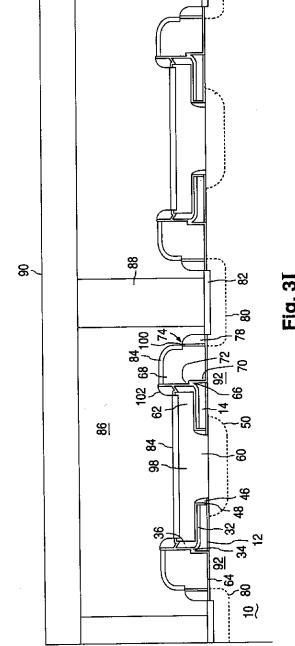

図3A～3Iは、図2Nに示されるのと類似であるが、ポリシリコンソース線を持つメモリセルアレイを形成する第1の代わりの処理を示す。この第1の代わりの処理は、図2Gに示されるのと同じ構造で始まり、以下のように続く。

【0033】

導電性ブロック98は、好ましくは構造上にポリシリコンのような導電性材料を蒸着することによって、トレンチ30内に形成され、その後、トレンチ30上のポリシリコンを取り除くためのポリプラナリゼーション処理（好ましくはCMP）が続く。ポリエッチバックステップは、トレンチ30の外部のあらゆるポリシリコンを取り除き、酸化物層36の上部以下に導電性ブロック98の上部表面に凹所を設けることが続く。ポリブロック98は、もとの場所に不純物を添加され得、あるいは注入を用いてそうされ得る。絶縁材料（酸化物）の層58は、酸化物層58が酸化物層36の上部以下に凹所を設けるように、例えば、熱酸化によって、あるいは、CMPプラナリゼーション処理及び酸化物エッチング処理によって続けられる酸化物蒸着によって、ポリブロック98上に形成される。結果として生じる構造は図3Aに示される。そこでは、狭い／広いトレンチ部分42／44は、より狭い下部ブロック60とより広い上部ブロック62を持つ概ねT型の導電性ポリブロック98を結果として生じる。

【0034】

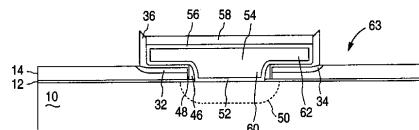

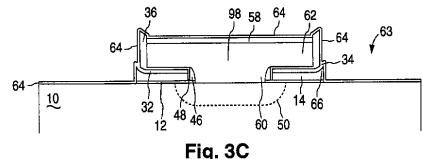

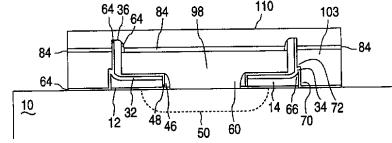

第2のトレンチ63は、メモリセルのセット対間に形成され、次の方法で第1のトレンチ30に隣接する。窒化物層24は、図3Bに示されるように、好ましくは、ポリ層14及び酸化物層32の部分を曝すために、等方性エッチング処理を用いて取り除かれる。ポリエッチング処理（すなわち、ドライエッチング）は、ポリ層14の曝された部分を取り除き、酸化物層12の部分を曝すことに続く。酸化物層12の曝された部分は、基板10を曝して、制御された酸化物エッチングを介して取り除かれる。好ましくは酸化物の絶縁層64は、全体構造上に形成され、図3Cに示される構造を結果として生じる。酸化物層32の上げ部分34は、層14が酸化物層64と接するポリ層14の上部に延びる鋭い端部の形成を結果として生じる。

【0035】

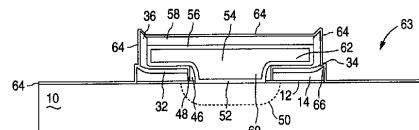

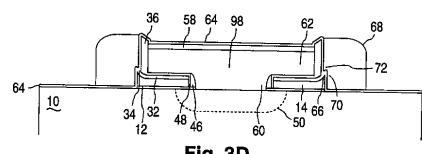

コントロールゲートポリブロックは、次の方法で第2のトレンチ63に形成される。ポリシリコンの厚い層が構造上に蒸着され、その後、酸化物層64の垂直に向かう部分に対して形成されるポリスペーサ（ブロック）68を除き、すべての蒸着されたポリシリコンを取り除く、異方性ポリエッチング処理が続く。ポリブロック68は、ポリ層14にすぐ隣接して配置される下部70と、鋭い端部66を含むポリ層14の部分上に延伸する上部72とを有する。ポリブロック68は、酸化物層64及び32によってポリ層14から絶縁される。結果として生じる構造は図3Dに示される。

【0036】

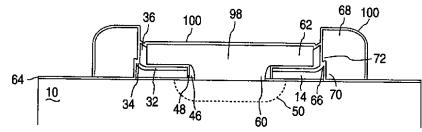

酸化物エッチングは、酸化物層64の曝された部分及び基礎をなす酸化物層58を取り除き、ポリブロック98及び基板10を曝すために、実行される。好ましくは、ポリブロック98の上部表面と概ね同じであるように、酸化物層36の上部を同じく取り除く、端点検出を持つドライエッチング処理が用いられる。酸化物蒸着処理は、構造上に酸化物層100を形成し、基板10上に酸化物層64を置き換えることに続く。結果として生じる構造は図3Eに示される。

【0037】

絶縁スペーサ74は、ポリブロック68に隣接して形成され、材料の1以上の層から作られる。好ましい実施の形態では、絶縁スペーサ74は、酸化物層100の下部と、酸化物層64上でポリスペーサ68に隣接する窒化物スペーサ78を残して、蒸着された窒化物を取り除くために（エッチストップとして酸化物層100を用いる）、構造上への窒化物の蒸着、その後、異方性窒化物エッチングによって形成される窒化物スペーサ78とを含む合成スペーサである。窒化スペーサ101は、また、図3Fに示されるように、導電性ブロック98の端部上に形成される。

【0038】

10

20

30

40

50

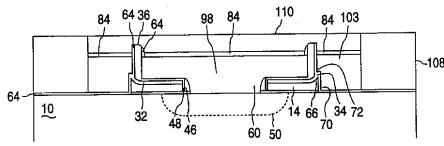

イオン注入（例えば、N+）は、第1の領域50が形成されたのと同じ方法で、基板に第2の領域（端子）80を形成するために用いられる。制御された酸化物エッチングは、ポリブロック98を曝すために酸化物層100の曝された部分を取り除き、基板10を曝すために酸化物層64の曝された部分を取り除くことに続く。結果として生じる構造は図3Gに示される。

【0039】

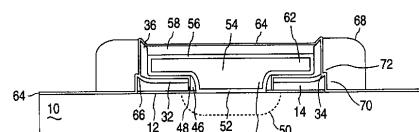

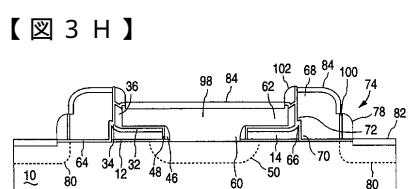

金属化シリコン（シリサイド）の層82は、タングステン、コバルト、チタン、ニッケル、白金、またはモリブデンのような金属を構造上に蒸着することによって、ポリブロック68とポリブロック98上の金属化シリコン84の層とともに、側壁スペーサ74の次に基板10の上部に形成される。その構造はアニールされ、シリサイド82を形成するために熱い金属が基板の曝された上部に流れて浸透し、金属化シリコン84を形成するためにポリブロック68及び98の曝された上部に浸透するのを可能にする。残存する構造上に蒸着された金属は、金属エッチング処理によって取り除かれる。基板10上の金属化シリコン領域82は、自己整合シリサイド（すなわち、salicide）と呼ばれ得る。なぜならば、それは、スペーサ78によって第2の領域80に自己整合されるからである。結果として生じる構造は図3Hに示される。

10

【0040】

BPSG86のようなマスキングステップは、全体構造をカバーするために用いられる。マスキングステップは、シリサイド領域82上にエッチング領域を画定するために実行される。BPSG86は、対をなすメモリセルの隣接するセット間に形成されるシリサイド領域82上に理想的に真中に置かれ、それに向けて下方に延伸するコンタクト孔を作り出すために、マスク領域に選択的にエッチングされる。コンタクト孔は、接触導体88を形成するために、金属蒸着及びプラナリゼーションエッチバッくによって、導体金属で満たされる。シリサイド層82は、導体88と第2の領域80の間の伝導を容易にする。ビット線90は、メモリセルの縦列にすべての導体88とともに接続するために、BPSG86上への金属マスキングによって加えられる。最終的なメモリセル構造は図3Iに示される。

20

【0041】

第1の代わりの実施の形態は、T型ポリブロック98のより広い上部62及びその上に形成されるより高い導電性金属化シリコン層84のために、ソース線抵抗の減少を示すが、T型導電性ブロック98のより狭い底部60のために、メモリセル寸法のより小さいスケーリングをまだ提供する。上部62は、また、（酸化物層46/48を通して下部60を介し、酸化物層12を通して第1の領域50を介する結合に加えて、）酸化物層32/36を通してポリブロック98からフローティングゲート14までのソース電圧の結合を可能にする、フローティングゲート14上に延びる。したがって、電源電極とフローティングゲートの間の結合係数が向上される。

30

【0042】

第2の代わりの実施の形態

図4A～4Iは、図2Nに示されるものと類似であるが、自己整合接触機構を利用するメモリセルアレイを形成する第2の代わりの処理を示す。この第2の代わりの処理は、図2Jに示されるような同一の構造で始まるが、以下のように続く。

40

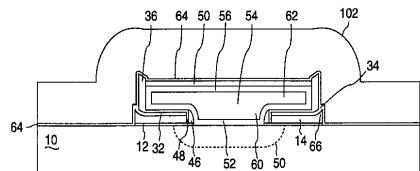

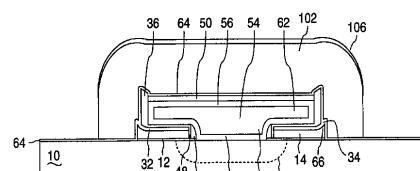

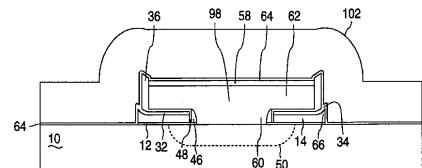

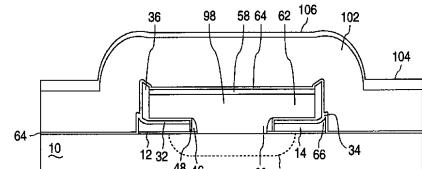

【0043】

ポリシリコンのような導電性材料の厚い層102は、図4Aに示されるように、構造上に蒸着される。窒化物の層104は、構造上に蒸着され、その後、窒化物プラナリゼーション処理（例えば、CMP）が続く。窒化物エッチバックスステップは、ポリ層102の上げ部分上に窒化物層104の部分を取り除くことが続くが、ポリ層102の平坦な側面部分上に窒化物層104の部分を残す。その上に酸化物の層106を形成するために、ポリ層102の曝された中心部分を酸化する酸化処理ステップが続く。結果として生じる構造は図4Bに示される。

【0044】

50

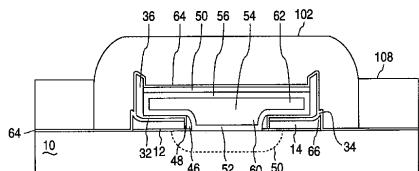

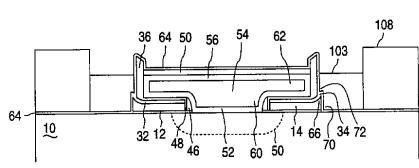

窒化物層 104 は、窒化物エッチング処理によって取り除かれる。それは、図 4 C に示されるように、酸化物層 106 下に直接的にではなくポリ層 102 の部分を取り除くための異方性ポリエッチング処理によって続けられる。

【0045】

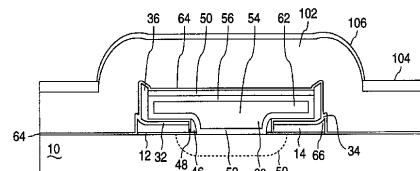

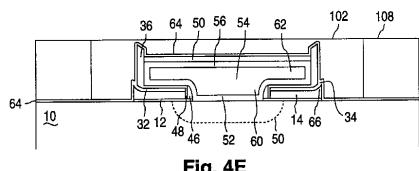

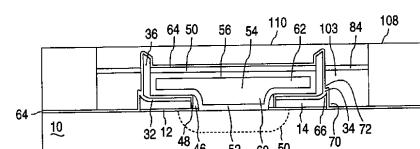

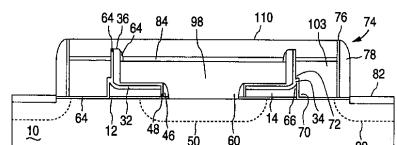

酸化物蒸着ステップは、構造上に厚い酸化物層を適用するために実行される。これは、エッチングストップとしてポリ層 102 を用いて構造を平坦化するために、CMP のような平坦化酸化物エッチングによって続けられる。酸化物エッチバックステップが実行され、ポリ層 102 のいずれかの側面上に酸化物のブロック 108 を残す。酸化物層 106 は、また、酸化物平坦化及びエッチバックステップによって取り除かれ、図 4 D に示される構造を結果として生じる。CMP のような平坦化ポリエッチングは、図 4 E に示されるように、エッチングストップとして酸化物ブロック 108 を用いて実行される。これは、酸化物ブロック 108 に隣接するポリブロック 103 を残して、酸化物層 64 を曝す、ポリ層 102 の上部を取り除くために、RIE のようなポリエッチバック処理によって続けられる。ポリブロック 103 は、ポリ層 14 にすぐ隣接して配置される下部 70 と、鋭い端部 66 を含むポリ層 14 の部分上に延びる上部 72 とを有する。ポリブロック 103 は、酸化物層 64 及び 32 によってポリ層 14 から絶縁される。酸化物ブロック 108 及び酸化物層 36 は、図 4 F に示されるように、ポリブロック 103 の上部表面上にうまく延びるように置かれる。

【0046】

任意の注入ステップは、曝されたポリブロック 103 に不純物を添加するために実行され得る。金属蒸着ステップは、タンゲステン、コバルト、チタン、ニッケル、白金、またはモリブデンのような金属を構造上に蒸着するために、実行される。その構造はアニールされ、熱い金属が、その上に金属化シリコン 84 の導電層を形成するために、ポリブロック 103 の曝された上部に流れて浸透するのを可能にする。残存する構造上に蒸着された金属は、金属エッチング処理によって取り除かれる。金属化シリコン層 84 は、自己整合と呼ばれ得る。なぜならば、それは、酸化物層 64 及び酸化物ブロック 108 によってポリブロック 103 に自己整合されるからである。保護する窒化物層 110 は、次の方法で、ポリブロック 103 上で酸化物ブロック 108 間に形成される。窒化物が構造上に蒸着され、窒化物層 110 が酸化物ブロック 108 と同じ高さであるように、エッチングストップ層として用いられる酸化物ブロック 108 で、CMP のような平坦化窒化物エッチングが続く。窒化物層 110 は、酸化物ブロック 108 によってポリブロック 103 に自己整合される。結果として生じる構造は図 4 G に示される。

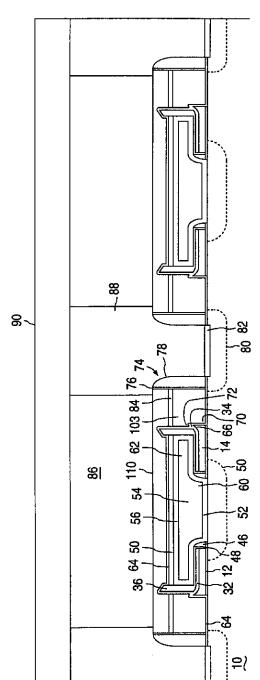

【0047】

酸化物エッチングは、図 4 H に示されるように、酸化物ブロック 108 と酸化物層 64 の曝された部分を取り除くために続く。絶縁スペーサ 74 は、ポリブロック 103 に隣接して形成され、材料の 1 以上の層から作られる。好ましい実施の形態では、絶縁スペーサ 74 は、酸化物の薄い層 76 を最初に蒸着することによって材料の 2 つの層から作られ、構造上への窒化物の蒸着が続く。異方性窒化物エッチングは、窒化物スペーサ 78 を残して、蒸着された窒化物を取り除くために実行される。イオン注入（例えば、N+）は、第 1 の領域 50 が形成されたのと同じ方法で、基板に第 2 の領域（端子）80 を形成するために用いられる。酸化物層 76 の曝された部分を取り除く酸化物エッチングが続く。金属化シリコン（シリサイド）の層 82 は、タンゲステン、コバルト、チタン、ニッケル、白金、又はモリブデンのような金属を構造上に蒸着することによって、側壁スペーサ 74 の次に基板 10 の上部に形成される。その構造はアニールされ、シリサイド領域 82 を形成するために、熱い金属が基板 10 の曝された上部に流れて浸透するのを可能にする。構造上に蒸着された残存する金属は、金属エッチング処理によって取り除かれる。基板 10 上の金属化シリコン領域 82 は、自己整合シリサイド（すなわち、salicide）と呼ばれ得る。なぜならば、それは、スペーサ 78 によって第 2 の領域 80 に自己整合されるからである。結果として生じる構造は図 4 I に示される。

【0048】

10

20

30

40

50

B P S G 8 6 のようなパッジベーションは、全体構造をカバーするために用いられる。マスキングステップは、salicide領域 8 2 上にエッチング領域を画定するために実行される。B P S G 8 6 は、対をなすメモリセルの隣接するセット間に形成されるsalicide領域 8 2 上に理想的に真中に置かれ、それより広いコンタクト孔を作り出すために、マスク領域に選択的にエッチングされる。窒化物層 1 1 0 は、ポリブロック 1 0 3 及び金属化シリコン 8 4 をこのエッチング処理から保護するのに役立つ。コンタクト孔は、金属蒸着及びプラナリゼーションエッチバックによって、導体金属で満たされる。それによって、対をなすメモリセルの隣接するセットの窒化物スペーサ 7 8 間の全体領域は、窒化物スペーサ 7 8 (すなわち、自己整合接触機構、又はS A C ) によってsalicide領域 8 2 に自己整合される接触導体 8 8 を形成するために、蒸着金属で満たされる。salicide層 8 2 は、導体 8 8 と第 2 の領域 8 0 の間の伝導を容易にする。ビット線 9 0 は、メモリセルの縦列にすべての導体 8 8 をともに接続するために、B P S G 8 6 上への金属マスキングによって加えられる。最終的なメモリセル構造は図 4 J に示される。

#### 【 0 0 4 9 】

自己整合接触機構 (S A C ) は、対をなすメモリセルの隣接するセット間の最小の間隔要求において、重要な制限を取り除く。特に、図 4 J が、salicide領域 8 2 上に完全に真中に置かれる接触領域 (及び、従って導体 8 8 ) を示すが、実際には、salicide領域 8 2 に関して幾らかの望ましくない水平シフトなしに、コンタクト孔を形成することは非常に困難である。B P S G 形成の前に構造上に窒化物の保護層がない非自己整合接触機構では、接觸 8 8 が金属化シリコン 8 4 及びポリブロック 1 0 3 上でシフトされ、形成されるならば、電気ショートが起こり得る。非自己整合接触機構での電気ショートを防ぐために、コンタクト孔は、接觸領域の最大可能シフトと同じように、窒化物スペーサ 7 8 から十分に離れて形成されなければならない。それらは、窒化物スペーサ 7 8 又はその向こうに延伸しない。勿論、これは、対をなすミラーセルの隣接するセット間の十分な許容距離を提供するために、スペーサ 7 8 間の最小距離での制約を示す。

#### 【 0 0 5 0 】

本発明のS A C 方法は、B P S G の下で材料の保護層 (窒化物層 1 1 0 ) を用いることによって、この制約を排除する。この保護層では、コンタクト孔は、形成中コンタクト孔の十分な水平シフトがあるとしても、salicide領域 8 2 でコンタクト孔の部分的重複があるのを保証するために、十分な幅でB P S G に形成される。窒化物層 1 1 0 は、接觸の部分 8 8 が、それらの間にあらゆるショートなく、ポリブロック 1 0 3 又は金属化シリコン層 8 4 上に形成されることを可能にする。広いコンタクト孔は、接觸 8 8 がスペーサ 7 8 間の非常に狭いスペースを完全に満たし、salicide領域 8 2 で良く電気接觸することを保証する。したがって、スペーサ 7 8 間の接觸領域の幅は最小にされ得、スペーサ 7 8 間のスペースを満たすことによって、接觸不良を防ぐが、全体的セル寸法のスケーリングダウンを可能にする。

#### 【 0 0 5 1 】

第 2 の代わりの実施の形態は、コントロールゲート 1 0 3 がフローティングゲート 1 4 上に突き出た部分 7 2 と、スペーサ 7 4 の形成及び自己整合導体 8 8 の形成を容易にし、同様に、salicide領域 8 2 の自己整合形成を容易にする平坦な対向表面とで十分に直角に形成されるというさらなる利点を有する。

#### 【 0 0 5 2 】

#### 第 3 の代わりの実施の形態

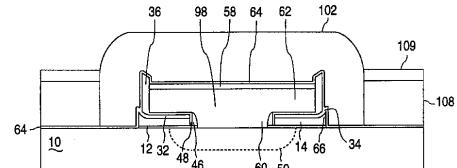

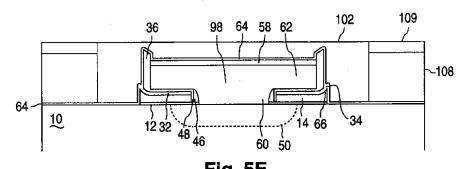

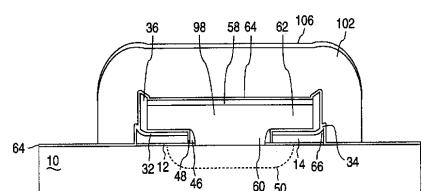

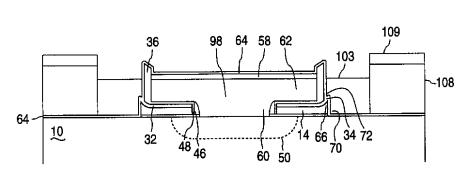

図 5 A ~ 5 K は、図 3 I に示されるものと類似であるが、自己整合接触機構を利用するメモリセルアレイを形成する第 3 の代わりの処理を示す。この第 3 の代わりの処理は、図 3 C に示されるような同一の構造で始まるが、以下のように続く。

#### 【 0 0 5 3 】

ポリシリコンのような導電性材料の厚い層 1 0 2 は、図 5 A に示されるように、構造上に蒸着される。窒化物の層 1 0 4 が構造上に蒸着され、その後、窒化物プラナリゼーション処理 (例えば、C M P ) が続く。窒化物エッチバックステップは、ポリ層 1 0 2 の上げ部

分上に窒化物層 104 の部分を取り除くことが続くが、ポリ層 102 の平坦な側面部分上に窒化物層 104 の部分を残す。その上に酸化物の層 106 を形成するために、ポリ層 102 の曝された中心部分を酸化する酸化処理ステップが続く。結果として生じる構造は図 5 B に示される。

【0054】

窒化物層 104 は、窒化物エッチング処理によって取り除かれ、その後、図 5 C に示されるように、酸化物層 106 下に直接的にではなくポリ層 102 のこれらの部分を取り除くための異方性ポリエッチング処理が続く。

【0055】

酸化物蒸着ステップは、構造上に厚い酸化物層を適用するために実行される。これは、エッチングステップとしてポリ層 102 を用いて構造を平坦化するために、CMP のような平坦化酸化物エッチングによって続けられる。酸化物エッチバックステップが実行され、ポリ層 102 のいずれかの側面上に酸化物のブロック 108 を残す。酸化物層 106 は、また、酸化物平坦化及びエッチバックステップによって取り除かれ。窒化物蒸着ステップは、構造上の窒化物層に適用するために実行される。これは、エッチングステップとしてポリ層 102 を用いて構造を平坦化するために、CMP のような平坦化窒化物エッチングによって続けられる。窒化物エッチバックステップが実行され、酸化物ブロック 108 上に窒化物層 109 を残す。結果として生じる構造は図 5 D に示される。

【0056】

CMP のような平坦化ポリエッチングは、図 5 E に示されるように、エッチングステップとして窒化物層 109 を用いて実行される。これは、酸化物ブロック 108 に隣接するポリブロック 103 をちょうど残して、酸化物層 64 を曝す、ポリ層 102 の上部を取り除くために、RIE のようなポリエッチバック処理によって続けられる。ポリブロック 103 は、ポリ層 14 にすぐ隣接して配置される下部 70 と、鋭い端部 66 を含むポリ層 14 の部分上に延びる上部 72 とを有する。ポリブロック 103 は、酸化物層 64 及び 32 によってポリ層 14 から絶縁される。酸化物ブロック 108 及び酸化物層 36 は、図 5 F に示されるように、ポリブロック 103 の上部表面上にうまく延びるように置かれる。

【0057】

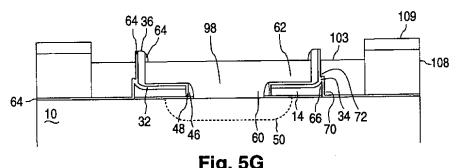

制御された酸化物エッチングは、酸化物層 64 の曝された水平部分及び基礎をなす酸化物層 58 を取り除き、ポリブロック 98 を曝すために実行される。好ましくは、図 5 G に示されるように、酸化物層 36 の上部を同じく取り除く、端点検出を持つドライエッチング処理が用いられる。

【0058】

任意の注入ステップは、曝されたポリブロック 103 に不純物を添加するために実行され得る。金属蒸着ステップは、タンゲステン、コバルト、チタン、ニッケル、白金、又はモリブデンのような金属を構造上に蒸着するために、実行される。その構造はアニールされ、熱い金属が、その上に金属化シリコン 84 の導電層を形成するために、ポリブロック 103 及び 98 の曝された上部に流れて浸透するのを可能にする。残存する構造上に蒸着された金属は、金属エッチング処理によって取り除かれ。金属化シリコン層 84 は、自己整合と呼ばれ得る。なぜならば、それは、酸化物層 64 及び酸化物ブロック 108 によってポリブロック 103 に自己整合されるからである。保護する窒化物層 110 は、次の方法で、ポリブロック 103 上で酸化物ブロック 108 間に形成される。窒化物が構造上に蒸着され、窒化物層 110 が酸化物ブロック 108 と同じ高さであるように、エッチングステップ層として用いられる酸化物ブロック 108 で、CMP のような平坦化窒化物エッチングが続く。窒化物層 109 は、この処理によって同様に取り除かれ。窒化物層 110 は、酸化物ブロック 108 によってポリブロック 103 に自己整合される。結果として生じる構造は図 5 H に示される。

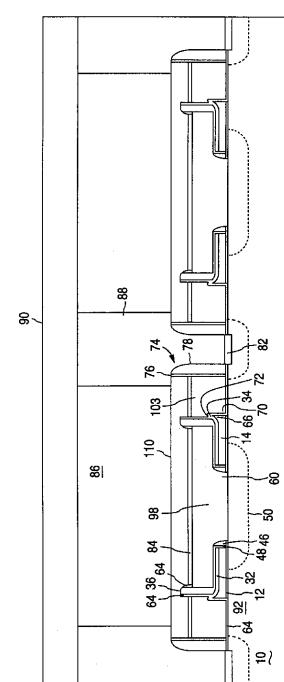

【0059】

酸化物エッチングは、図 5 I に示されるように、酸化物ブロック 108 と酸化物層 64 の曝された部分とを取り除くために続く。絶縁スペーサ 74 は、ポリブロック 103 に隣接

10

20

30

40

50

して形成され、材料の 1 以上の層から作られる。好ましい実施の形態では、絶縁スペーサ 74 は、酸化物の薄い層 76 を最初に蒸着することによって材料の 2 つの層から作られ、その後、構造上への窒化物の蒸着が続く。異方性窒化物エッチングは、窒化物スペーサ 78 を除いて、蒸着された窒化物を取り除くためのエッチングステップとして酸化物層 76 を用いて実行される。イオン注入（例えば、N<sup>+</sup>）は、第 1 の領域 50 が形成されたのと同じ方法で、基板に第 2 の領域（端子）80 を形成するために用いられる。酸化物層 76 の曝された部分を取り除く酸化物エッチングが続く。金属化シリコン（シリサイド）の層 82 は、タンゲステン、コバルト、チタン、ニッケル、白金、又はモリブデンのような金属を構造上に蒸着することによって、側壁スペーサ 74 の次に基板 10 の上部に形成される。その構造はアニールされ、シリサイド領域 82 を形成するために、熱い金属が基板 10 の曝された上部に流れて浸透するのを可能にする。構造上に蒸着された残存する金属は、金属エッチング処理によって取り除かれる。基板 10 上の金属化シリコン領域 82 は、自己整合シリサイド（すなわち、salicide）と呼ばれ得る。なぜならば、それは、スペーサ 78 によって第 2 の領域 80 に自己整合されるからである。結果として生じる構造は図 5 J に示される。

#### 【0060】

BPSG 86 のようなパッシベーションは、全体構造をカバーするために用いられる。マスキングステップは、salicide 領域 82 上にエッチング領域を画定するために実行される。BPSG 86 は、対をなすメモリセルの隣接するセット間に形成される salicide 領域 82 上に理想的に真中に置かれ、それより広いコンタクト孔を作り出すために、マスク領域に選択的にエッチングされる。窒化物層 110 は、ポリブロック 103 及び金属化シリコン層 84 をこのエッチング処理から保護するのに役立つ。コンタクト孔は、金属蒸着及びプラナリゼーションエッチバックによって、導体金属で満たされる。それによって、対をなすメモリセルの隣接するセットの窒化物スペーサ 78 間の全体領域は、窒化物スペーサ 78（すなわち、自己整合接触機構、又は SAC）によって salicide 領域 82 に自己整合される接触導体 88 を形成するために、蒸着金属で満たされる。salicide 層 82 は、導体 88 と第 2 の領域 80 の間の伝導を容易にする。ピット線 90 は、メモリセルの縦列にすべての導体 88 をともに接続するために、BPSG 86 上への金属マスキングによって加えられる。最終的なメモリセル構造は図 5 K に示される。

#### 【0061】

第 3 の代わりの実施の形態は、第 1 の代わりの実施の形態の利点と SAC の利点を兼ね備える利点を有する。

#### 【0062】

本発明は、上述のここで示された実施の形態に制限されず、添付された特許請求の範囲に属するあらゆるすべてのバリエーションを含むものと理解されたい。例えば、前述の方法がメモリセルを形成するために用いられる導電性材料として適当に不純物を添加されたポリシリコンの使用を記述するけれども、あらゆる適当な導電性材料が使用され得ることは、当業者にとって明白である。それに加えて、あらゆる適当な絶縁体が、二酸化ケイ素あるいは窒化ケイ素の代わりに用いられ得る。さらに、エッチング特性が二酸化ケイ素（あるいはあらゆる絶縁体）及びポリシリコン（あるいはあらゆる導体）と異なる適当な材料が、窒化ケイ素の代わりに用いられ得る。さらに、特許請求の範囲から明白なように、すべての方法ステップが示されあるいは要求される正確な順序で実行される必要はなく、むしろ、本発明のメモリセルの適切な形成を可能にするあらゆる順序で実行される。最後に、第 1 のトレンチ上部及び下部は、対称である必要はないが、むしろ、第 1 のトレンチは、その中に形成されるソース線がフローティングゲートに隣接して蒸着される第 1 の部分と、フローティングゲート上に蒸着される第 2 の部分とを有するように、その側壁にくぼみを有することのみが必要である。

#### 【図面の簡単な説明】

【図 1】図 1 A は、絶縁領域を形成するために、本発明の方法の第 1 のステップで用いられる半導体基板の平面図である。

10

20

30

40

50

図1Bは、ライン1-1に沿って取られる断面図である。

図1Cは、その中に絶縁領域を形成される、図1Bの構造の処理における次のステップの平面図である。

図1Dは、その構造に形成される絶縁ストライプを示す、ライン1-1に沿って取られる図1Cの構造の断面図である。

図1Eは、半導体基板に形成される2つのタイプの絶縁領域、LOCOS又は浅いトレンチを示す、ライン1-1に沿って取られる図1Cの構造の断面図である。

【図2A】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

10

【図2B】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図2C】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図2D】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

20

【図2E】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図2F】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

20

【図2G】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図2H】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

30

【図2I】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図2J】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図2K】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

40

【図2L】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図2M】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図2N】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の処理における次のステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図2O】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイ

50

の形成において、活性領域の端子への横列線とビット線の配線を示す平面図である。

【図3A】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第1の代わりの処理におけるステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図3B】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第1の代わりの処理におけるステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図3C】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第1の代わりの処理におけるステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図3D】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第1の代わりの処理におけるステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図3E】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第1の代わりの処理におけるステップを連続的に示す。図1Cのライン2-2に沿って取られる断面図である。

【図3F】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第1の代わりの処理におけるステップを連続的に示す。図1Cのライン2-2に沿って取られる断面図である。

【図3G】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第1の代わりの処理におけるステップを連続的に示す。図1Cのライン2-2に沿って取られる断面図である。

【図3H】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第1の代わりの処理におけるステップを連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図31】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第1の代わりの処理におけるステップを連続的に示す。図1Cのライン2-2に沿って取られる断面図である。

【図4A】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第2の代わりの処理を連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図4B】スプリットゲートタイプのフローイングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第2の代わりの処理を連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図4C】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第2の代わりの処理を連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図 4 D】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 2 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2' に沿って取られる断面図である。

【図4E】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第2の代わりの処理を連続的に示す、図1Cのライン2-2に沿って取られる断面図である。

【図4F】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第2の代わりの処理を連続的に示す、図1Cのライン2-2'に沿って取られる断面図である。

【図4G】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図1Cに示される構造の第2の代わりの処理を連続的に示す、図1Cの二段の露光工程に沿って示す断面図である。

【図1-1-1】スズランの根、花、花序の構造。二重管状花の不規整性が特徴的である。

の形成において、図 1 C に示される構造の第 2 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。

【図 4 I】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 2 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。

【図 4 J】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 2 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。

【図 5 A】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 3 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。 10

【図 5 B】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 3 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。

【図 5 C】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 3 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。 20

【図 5 D】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 3 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。

【図 5 E】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 3 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。

【図 5 F】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 3 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。

【図 5 G】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 3 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。 30

【図 5 H】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 3 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。

【図 5 I】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 3 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。

【図 5 J】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 3 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。

【図 5 K】スプリットゲートタイプのフローティングメモリセルの不揮発性メモリアレイの形成において、図 1 C に示される構造の第 3 の代わりの処理を連続的に示す、図 1 C のライン 2 - 2 に沿って取られる断面図である。 40

#### 【符号の説明】

1 0 基板

1 2 二酸化ケイ素層

1 4 フローティングゲート

1 8 窒化ケイ素層

1 9 フォトレジスト材料

2 0 a 絶縁材料

2 0 b 浅トレンチ絶縁材料

2 4 、 3 8 、 1 0 4 、 1 0 9 窒化物層

|                                 |               |    |

|---------------------------------|---------------|----|

| 2 6                             | 保護層           |    |

| 3 0、6 3                         | トレンチ          |    |

| 3 2、3 6、5 8、6 4、7 6、1 0 0、1 0 6 | 酸化物層          |    |

| 4 0、7 4                         | 側壁スペーサ        |    |

| 4 6                             | 酸化物スペーサ       |    |

| 4 8                             | 絶縁側壁層         |    |

| 5 0、8 0                         | ドレイン          |    |

| 5 4                             | タングステン導電性ブロック |    |

| 5 6                             | 導電層           | 10 |

| 6 8                             | 制御線           |    |

| 7 8、1 0 1                       | 窒化物スペーサ       |    |

| 8 2                             | 金属化シリコン領域     |    |

| 8 4                             | 導電性金属化シリコン層   |    |

| 8 8                             | 自己整合導体        |    |

| 9 0                             | ビット線          |    |

| 9 2                             | チャネル領域        |    |

| 9 4                             | ノッチ           |    |

| 9 6                             | ソース線          |    |

| 9 8                             | 導電性ポリブロック     | 20 |

| 1 0 3                           | コントロールゲート     |    |

| 1 0 8                           | 酸化物ブロック       |    |

| 1 1 0                           | 窒化物層 C V D 低圧 |    |

【図 1】

【図 2 A】

Fig. 2A

【図 2 B】

Fig. 2B

【図 2 C】

Fig. 2C

【図 2 D】

Fig. 2D

【図2E】

Fig. 2E

【図2F】

Fig. 2F

【図2G】

Fig. 2G

【図2H】

Fig. 2H

【図2M】

Fig. 2M

【図2I】

Fig. 2I

【図2J】

Fig. 2J

【図2K】

Fig. 2K

【図2L】

Fig. 2L

【図2N】

Fig. 2N

【図2O】

Fig. 2O

【図3A】

Fig. 3A

【図3B】

Fig. 3B

【図3C】

Fig. 3C

【図3D】

Fig. 3D

【図3E】

Fig. 3E

【図3F】

Fig. 3F

【図3G】

Fig. 3G

【図3H】

Fig. 3H

【図3I】

【図 4 A】

Fig. 4A

【図 4 D】

Fig. 4D

【図 4 B】

Fig. 4B

【図 4 E】

Fig. 4E

【図 4 C】

Fig. 4C

【図 4 F】

Fig. 4F

【図 4 G】

Fig. 4G

【図 4 J】

Fig. 4J

【図 4 H】

Fig. 4H

【図 4 I】

Fig. 4I

【図 5 A】

Fig. 5A

【図 5 D】

Fig. 5D

【図 5 B】

Fig. 5B

【図 5 E】

Fig. 5E

【図 5 C】

Fig. 5C

【図 5 F】

Fig. 5F

【図 5 G】

Fig. 5G

【図 5 H】

Fig. 5H

【図 5 K】

Fig. 5K

【図 5 I】

Fig. 5I

【図 5 J】

Fig. 5J

---

フロントページの続き

(31)優先権主張番号 60/275517

(32)優先日 平成13年3月12日(2001.3.12)

(33)優先権主張国 米国(US)

(31)優先権主張番号 60/287047

(32)優先日 平成13年4月26日(2001.4.26)

(33)優先権主張国 米国(US)

(31)優先権主張番号 09/916555

(32)優先日 平成13年7月26日(2001.7.26)

(33)優先権主張国 米国(US)

(74)代理人 100119253

弁理士 金山 賢教

(72)発明者 チー・シン・ワン

アメリカ合衆国、カリフォルニア州 95120、サン・ホセ、ギリス・ドライブ 6585

審査官 加藤 俊哉

(56)参考文献 特開平10-092960(JP,A)

特開平09-321156(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8247

H01L 21/336

H01L 27/115

H01L 29/788

H01L 29/792