(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6230797号

(P6230797)

(45) 発行日 平成29年11月15日(2017.11.15)

(24) 登録日 平成29年10月27日(2017.10.27)

(51) Int.Cl.

F 1

|             |               |                  |             |               |             |

|-------------|---------------|------------------|-------------|---------------|-------------|

| <b>G09G</b> | <b>3/3233</b> | <b>(2016.01)</b> | <b>G09G</b> | <b>3/3233</b> |             |

| <b>G09G</b> | <b>3/20</b>   | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>   | <b>624B</b> |

| <b>H01L</b> | <b>51/50</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>   | <b>611H</b> |

| <b>H01L</b> | <b>29/786</b> | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>   | <b>670D</b> |

|             |               |                  | <b>HO5B</b> | <b>33/14</b>  | <b>A</b>    |

請求項の数 1 (全 22 頁) 最終頁に続く

(21) 出願番号 特願2013-46513 (P2013-46513)

(22) 出願日 平成25年3月8日 (2013.3.8)

(65) 公開番号 特開2013-218311 (P2013-218311A)

(43) 公開日 平成25年10月24日 (2013.10.24)

審査請求日 平成27年12月10日 (2015.12.10)

(31) 優先権主張番号 特願2012-56909 (P2012-56909)

(32) 優先日 平成24年3月14日 (2012.3.14)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 斎藤 厚志

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1乃至第6のトランジスタと、第1乃至第8の配線と、容量素子と、発光素子と、を有し、

前記第2のトランジスタは、酸化物半導体層にチャネル形成領域を有し、

前記第3のトランジスタは、酸化物半導体層にチャネル形成領域を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第1の配線と電気的に接続され、

前記容量素子の一対の電極のうちの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記容量素子の一対の電極のうちの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記第3の配線と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第4の配線と電気的に接

10

20

続され、

前記第3のトランジスタのゲートは、前記第2の配線と電気的に接続され、

前記第4のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第4のトランジスタのゲートは、前記第5の配線と電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記容量素子の一対の電極のうちの一方と電気的に接続され、

前記第5のトランジスタのソース又はドレインの他方は、前記容量素子の一対の電極のうちの他方と電気的に接続され、

前記第5のトランジスタのゲートは、前記第6の配線と電気的に接続され、

前記第6のトランジスタのソース又はドレインの他方は、前記発光素子のアノード又はカソードの一方と電気的に接続され、

前記第6のトランジスタのゲートは、前記第7の配線と電気的に接続され、

前記発光素子のアノード又はカソードの他方は、前記第8の配線と電気的に接続され、

第1の期間において、前記第2の配線、前記第5の配線、及び前記第6の配線にローレベルの電位が与えられ、前記第7の配線にハイレベルの電位が与えられ、

前記第1の期間の後の第2の期間において、前記第7の配線に与えられる電位はハイレベルからローレベルに切り替えられ、

前記第2の期間の後の第3の期間において、前記第5の配線及び前記第7の配線に与えられる各々の電位はローレベルからハイレベルに切り替えられ、

前記第3の期間の後のリセット期間において、前記第6の配線に与えられる電位はローレベルからハイレベルに切り替えられ、

前記第1の期間と前記第2の期間との間の期間において、前記第2の配線に与えられる電位は、ローレベルからハイレベルに切り替えられ、

前記第2の期間と前記第3の期間との間の期間において、前記第2の配線に与えられる電位は、ハイレベルからローレベルに切り替えられることを特徴とする表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

30

##### 【0001】

本発明は、表示装置に関する。特に、各画素にチャネルが酸化物半導体層に形成されるトランジスタが設けられているアクティブマトリクス型の表示装置に関する。

##### 【背景技術】

##### 【0002】

発光素子を用いた表示装置は視認性が高く、薄型化に最適であると共に、視野角にも制限が無いため、CRT (cathode ray tube) や液晶表示装置に替わる表示装置として注目されている。発光素子を用いたアクティブマトリクス型の表示装置は、具体的に提案されている構成がメーカーによって異なるが、通常、少なくとも発光素子と、画素へのビデオ信号の入力を制御するトランジスタと、該発光素子に供給される電流を制御するトランジスタ(駆動トランジスタ)とが、各画素に設けられている。

##### 【0003】

画素に設けられるトランジスタのすべてを同じ極性とすることで、トランジスタの作製工程の低減を図ることができる。特許文献1では、nチャネル型のトランジスタのみで画素が構成された表示装置が開示されている。

##### 【先行技術文献】

##### 【特許文献】

##### 【0004】

##### 【特許文献1】特開2003-195810号公報

##### 【発明の概要】

40

50

## 【発明が解決しようとする課題】

## 【0005】

ところで、画素を構成するnチャネル型トランジスタとして、チャネルが酸化物半導体層に形成されるトランジスタが期待されている。当該トランジスタは、非晶質シリコン層にチャネルが形成されるトランジスタと比較して、電界効果移動度が高く、また、各画素に当該トランジスタが設けられる表示装置の大型化を図ることが可能であるからである。

## 【0006】

また、酸化物半導体層にチャネルが形成されるトランジスタは、オフ電流が著しく低いという特徴を備える。これは、当該トランジスタがスイッチとして好ましいことを意味する。ただし、当該トランジスタを有する表示装置に対する電源電圧の供給を停止した場合に不具合を生じることがある。具体的には、電源電圧の供給を停止した場合であっても、画素の特定のノードに電荷が保持され続けうる。そのため、再度、表示装置に対して電源電圧の供給を再開した場合などに表示に不具合が生じることがある。

## 【0007】

上述した課題に鑑み、本発明の一態様において、表示装置の表示不良を抑制することを目的の一とする。

## 【課題を解決するための手段】

## 【0008】

本発明の一態様は、複数の画素がマトリクス状に配設されている表示装置であって、画素は、発光素子と、ゲートとソース間の電圧に応じた電流を発光素子に供給する駆動トランジスタと、駆動トランジスタのゲートに所望の電位を供給するか否かを選択する第1のトランジスタと、駆動トランジスタのゲートとソースを電気的に接続させるか否かを選択する第2のトランジスタと、を有し、第1のトランジスタ及び第2のトランジスタは、チャネルが酸化物半導体層に形成されるトランジスタである表示装置である。

## 【0009】

なお、駆動トランジスタのソースから出力される電流が発光素子に対して供給される場合には、さらに、当該駆動トランジスタのしきい値電圧に依存せずに発光素子に供給される電流を制御する手段を画素に設けることが好ましい。例えば、ドレンが高電源電位を供給する配線に電気的に接続されるnチャネル型のトランジスタを駆動トランジスタとして適用する場合には、当該手段を画素に設けることが好ましい。

## 【発明の効果】

## 【0010】

本発明の一態様の表示装置においては、各画素に設けられている駆動トランジスタのゲートとソースを電気的に接続させるか否かを選択することが可能である。また、駆動トランジスタのゲートと他のノードとの電気的な接続をチャネルが酸化物半導体層に形成されるトランジスタによって制御する。これにより、駆動トランジスタのゲートと電気的に接続するノードに蓄積されている電荷の保持と放出を任意に行うことが可能となる。例えば、当該表示装置に対する電源電圧の供給を停止する前、又は電源電圧の供給再開後であって発光素子に電流が供給される前に駆動トランジスタのゲートとソースを電気的に接続させることで駆動トランジスタをオフ状態とすることが可能である。これにより、当該表示装置に対する電源電圧の供給を再開した際の表示不良を抑制することが可能である。

## 【図面の簡単な説明】

## 【0011】

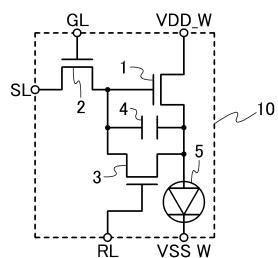

【図1】画素の構成例を示す回路図。

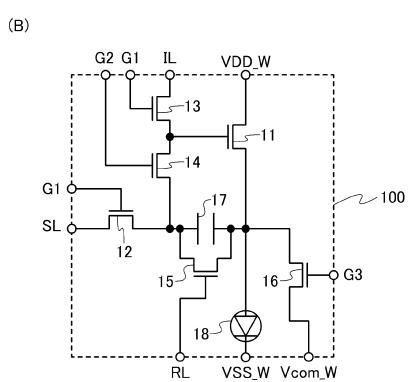

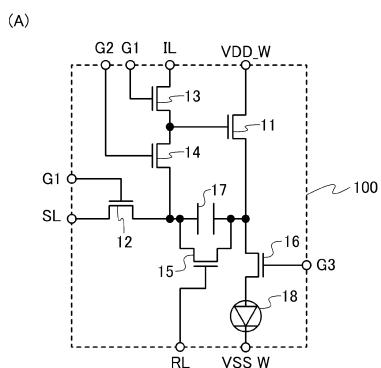

【図2】(A)、(B)画素の構成例を示す回路図。

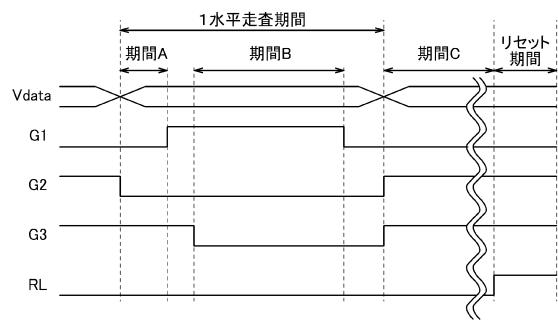

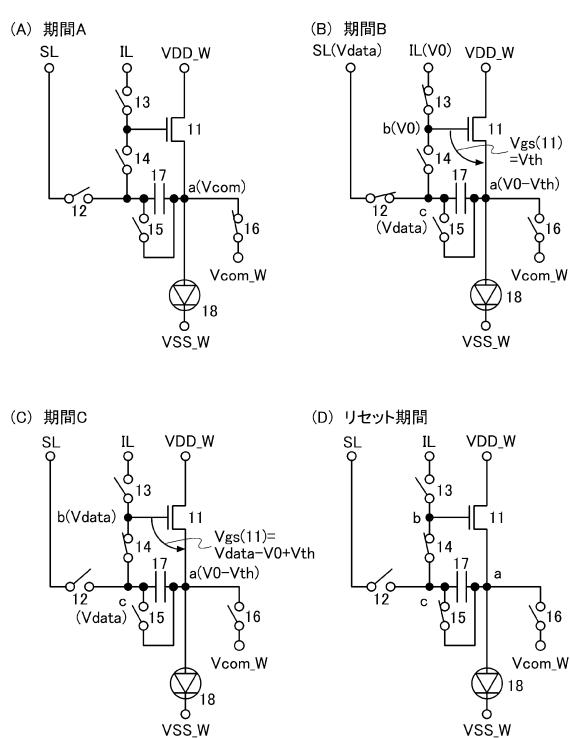

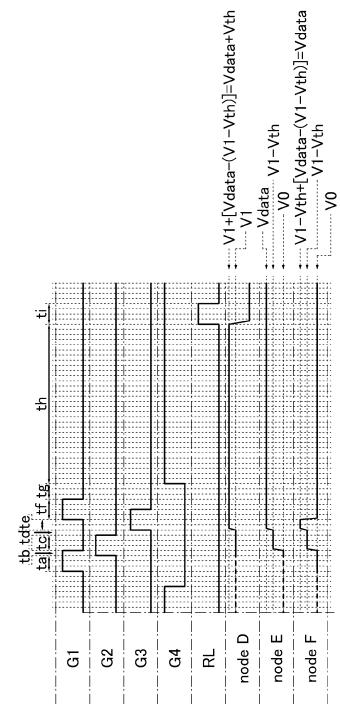

【図3】タイミングチャートの一例を示す図。

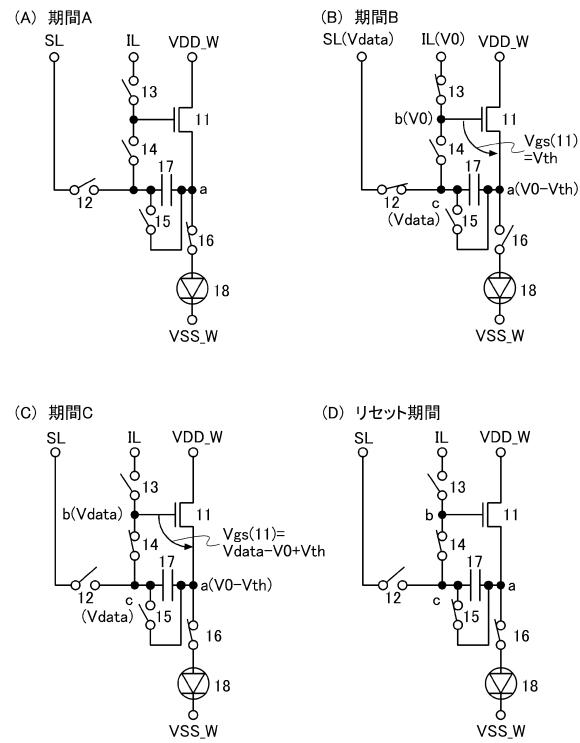

【図4】(A)～(D)画素の動作を説明するための図。

【図5】タイミングチャートの一例を示す図。

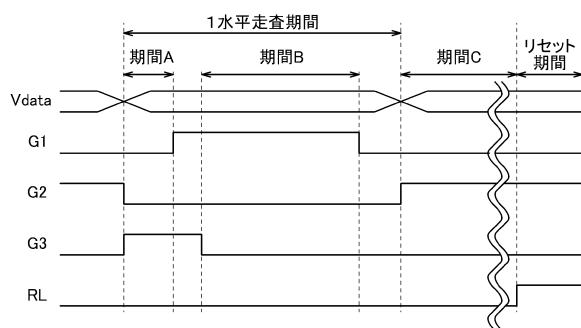

【図6】(A)～(D)画素の動作を説明するための図。

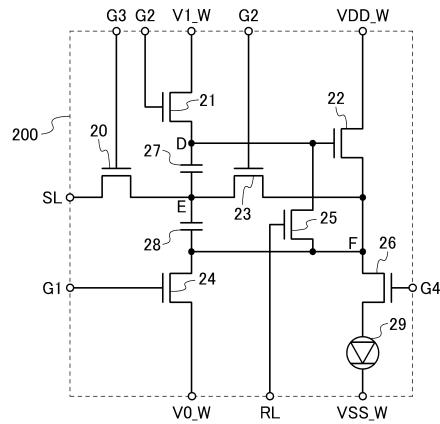

【図7】画素の構造例を示す回路図。

10

20

30

40

50

【図8】タイミングチャートの一例を示す図。

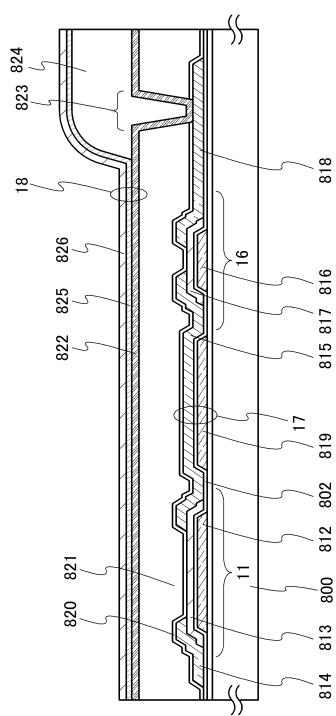

【図9】表示装置の構造例を示す断面図。

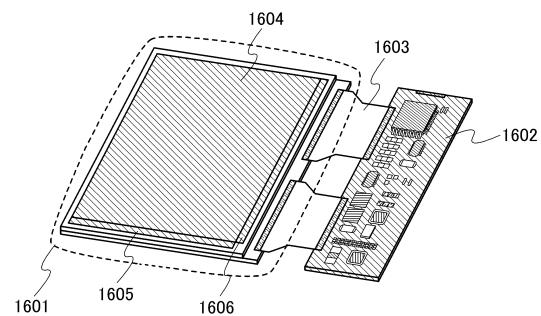

【図10】表示装置の一例を示す斜視図。

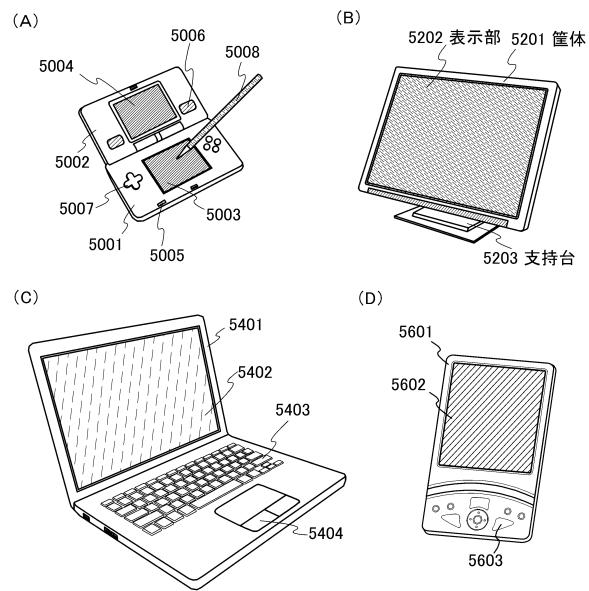

【図11】(A)～(D)電子機器の具体例を示す図。

【発明を実施するための形態】

【0012】

以下では、本発明の一態様について詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態を々々に変更し得る。したがって、本発明は以下に示す記載内容に限定して解釈されるものではない。

【0013】

なお、以下において「電気的に接続」とは、電流、電圧又は電位が、供給可能、又は伝送可能な状態に相当する。従って、電気的に接続している状態とは、直接接続している状態を必ずしも指すわけではなく、電流、電圧又は電位が、供給可能、又は伝送可能であるよう、配線、導電膜、抵抗、ダイオード、トランジスタなどの素子を介して間接的に接続している状態も、その範疇に含む。

【0014】

また、回路図上では独立している構成要素どうしが接続されている場合であっても、実際には、配線の一部が電極として機能する場合など、一の導電膜が、複数の構成要素の機能を併せ持っている場合がある。本明細書において接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

【0015】

(実施の形態1)

図1は、本実施の形態に係る表示装置が有する画素10の構成例を示す回路図である。図1に示す画素10は、トランジスタ1～3と、キャパシタ4と、発光素子5とを有する。なお、トランジスタ1～3は、チャネルが酸化物半導体層に形成されるnチャネル型のトランジスタである。

【0016】

トランジスタ1は、ゲートとソース間の電圧に応じた電流を発光素子5に供給する機能を有する。トランジスタ2は、配線SLとトランジスタ1のゲートを電気的に接続させるか否かを選択する機能を有する。トランジスタ3は、トランジスタ1のゲートとソースを電気的に接続させるか否かを選択する機能を有する。キャパシタ4は、トランジスタ1のゲートとソース間の電圧を保持する機能を有する。発光素子5は、トランジスタ1から供給される電流に応じた輝度で発光する機能を有する。

【0017】

さらに、トランジスタ1のドレインは、高電源電位(VDD)を供給する配線VDD\_Wに電気的に接続されている。また、トランジスタ2のゲートは、選択信号又は非選択信号を供給する配線GLに電気的に接続されている。また、トランジスタ3のゲートは、リセット信号を供給する配線RLに電気的に接続されている。また、発光素子5のカソードは、低電源電位(VSS)を供給する配線VSS\_Wに電気的に接続されている。

【0018】

次いで、図1に示す画素10の動作について説明する。

【0019】

画素10では、トランジスタ2のスイッチングによって、配線SLの電位をトランジスタ1のゲートに供給するか否かが選択される。具体的には、トランジスタ2のゲートに選択信号が供給される場合に配線SLの電位がトランジスタ1のゲートに供給され、トランジスタ2のゲートに非選択信号が供給される場合に配線SLの電位がトランジスタ1のゲートに供給されない。そして、トランジスタ1のゲートの電位に応じてトランジスタ1のゲートとソース間の電圧が変動する。これにより、トランジスタ1のゲートに供給される電位に応じた電流が発光素子5に供給されることになる。すなわち、当該電位に応じて発光素子5の発光輝度が制御されることになる。本実施の形態の表示装置においては、複数

10

20

30

40

50

の画素に設けられている発光素子のそれぞれの発光輝度を当該電位に応じて制御することで所望の表示を行う。

【0020】

また、画素10では、トランジスタ3のスイッチングによって、トランジスタ1のゲートとソースが電気的に接続されるか否かが選択される。例えば、表示装置に対する電源電圧の供給を停止する直前の一定期間に渡ってトランジスタ3をオン状態とし、その他の期間に渡ってトランジスタ3をオフ状態とする。これにより、表示装置に対する電源電圧の供給が停止される直前にトランジスタ1のゲートが電気的に接続するノードに蓄積されている電荷を放出させることが可能となる。すなわち、トランジスタ1を確実にオフ状態とすることが可能である。よって、本実施の形態の表示装置においては、電源電圧の供給を再開した際に発光素子5に電流が供給されることがなく、表示不良を抑制することが可能である。

10

【0021】

なお、電源電圧の供給を再開した後であって発光素子5に対して電流が供給されうる前(配線VDD\_Wに高電源電位(VDD)が供給され、且つ配線VSS\_Wに低電源電位(VSS)が供給される前)の一定期間に渡ってトランジスタ3をオン状態とすることによっても上記同様の効果を得ることが可能である。

【0022】

(実施の形態2)

図2(A)、(B)は、実施の形態1に示す画素10と異なる画素100の構成例を示す回路図である。

20

【0023】

<画素の構成例1>

図2(A)に示す画素100は、トランジスタ11~16と、キャパシタ17と、発光素子18とを有する。なお、トランジスタ11~16は、チャネルが酸化物半導体層に形成されるnチャネル型のトランジスタである。

【0024】

トランジスタ12は、配線SLとキャパシタ17の一方の電極を電気的に接続させるか否かを選択する機能を有する。トランジスタ13は、配線ILとトランジスタ11のゲートを電気的に接続させるか否かを選択する機能を有する。トランジスタ14は、キャパシタ17の一方の電極とトランジスタ11のゲートを電気的に接続させるか否かを選択する機能を有する。トランジスタ15は、キャパシタ17の一方の電極と他方の電極を電気的に接続させるか否かを選択する機能を有する。トランジスタ16は、トランジスタ11のソースと発光素子18のアノードを電気的に接続させるか否かを選択する機能を有する。

30

【0025】

さらに、トランジスタ11のドレインは、配線VDD\_Wに電気的に接続されている。また、トランジスタ12のゲート及びトランジスタ13のゲートは、選択信号又は非選択信号を供給する配線G1に電気的に接続されている。また、トランジスタ14のゲートは、選択信号又は非選択信号を供給する配線G2に電気的に接続されている。また、トランジスタ15のゲートは、リセット信号を供給する配線RLに電気的に接続されている。また、トランジスタ16のゲートは、選択信号又は非選択信号を供給する配線G3に電気的に接続されている。また、発光素子18のカソードは、配線VSS\_Wに電気的に接続されている。

40

【0026】

<画素の構成例2>

図2(B)に示す画素100は、トランジスタ11~15、19と、キャパシタ17と、発光素子18とを有する。なお、トランジスタ11~15、19は、チャネルが酸化物半導体層に形成されるnチャネル型のトランジスタである。

【0027】

図2(B)に示す画素100におけるトランジスタ12~15は、図2(A)に示す画

50

素 100 におけるトランジスタ 12～15 と同様の機能を有する。図 2 (B) に示す画素 100 におけるトランジスタ 19 は、トランジスタ 11 のソースと共に通電位 (Vcom) を供給する配線 Vcom\_W を電気的に接続させるか否かを選択する機能を有する。なお、共通電位 (Vcom) は、低電源電位 (VSS) と、発光素子 18 の順方向電圧降下との和よりも低い電位であることとする。例えば、共通電位 (Vcom) として低電源電位 (VSS) を適用することが可能である。

#### 【0028】

<画素の動作例 1>

次いで、図 2 (A) に示す画素 100 の動作について説明する。

#### 【0029】

図 3 は、図 2 (A) に示す画素 100 に接続される配線 G1～配線 G3 の電位と、配線 RL に供給される電位と、配線 SL に供給される信号 (Vdata) とのタイミングチャートを示す図である。図 3 に示すように、図 2 (A) に示す画素 100 の動作は、主に 1 水平走査期間に含まれる期間 A における動作、及び期間 B における動作、表示を行う期間 C における動作、並びにリセット期間における動作に分けることができる。

#### 【0030】

まず、期間 A において行われる動作について説明する。期間 A では、配線 G1 にローレベルの電位が与えられ、配線 G2 にローレベルの電位が与えられ、配線 G3 にハイレベルの電位が与えられ、配線 RL にローレベルの電位が与えられる。よって、トランジスタ 16 がオン状態となり、トランジスタ 12～15 がオフ状態となる。

#### 【0031】

図 4 (A) に、期間 A における画素 100 の動作を示す。なお、図 4 (A) では、トランジスタ 12～16 をスイッチとして表記している（以下、図 4 (B)～(D) においても同様）。期間 A では、上記動作により、トランジスタ 11 のソースと電気的に接続するノード（図 4 において、a を付記したノード）の電位が、低電源電位 (VSS) と発光素子 18 の順方向電圧降下を加算した電位となる。

#### 【0032】

次いで、期間 B において行われる動作について説明する。期間 B では、配線 G1 にハイレベルの電位が与えられ、配線 G2 にローレベルの電位が与えられ、配線 G3 にローレベルの電位が与えられ、配線 RL にローレベルの電位が与えられる。よって、トランジスタ 12、13 がオン状態となり、トランジスタ 14～16 がオフ状態となる。

#### 【0033】

なお、期間 A から期間 B に移行する際、配線 G1 に与える電位をローレベルからハイレベルに切り替えてから、配線 G3 に与える電位をハイレベルからローレベルに切り替えることが望ましい。これにより、ノード a の電位の変動を抑制することができる。

#### 【0034】

また、配線 IL には電位 (V0) が与えられ、配線 SL には画像信号の電位 (Vdata) が与えられる。なお、電位 (V0) は、低電源電位 (VSS) と、トランジスタ 11 のしきい値電圧 (Vth) と、発光素子 18 の順方向電圧降下とを加算した電位よりも高いことが望ましい。

#### 【0035】

図 4 (B) に、期間 B における画素 100 の動作を示す。期間 B では、上記動作により、トランジスタ 11 のゲートと電気的に接続するノード（図 4 において、b を付記したノード）に電位 (V0) が与えられるため、トランジスタ 11 がオン状態になる。よって、ノード a の電位が電位 (V0 - Vth) となるまで上昇する。換言すると、トランジスタ 11 のゲートとソース間の電圧 (Vgs(11)) がしきい値電圧 (Vth) になった段階で、トランジスタ 11 がオフ状態となる。また、キャパシタ 17 の一方の電極と電気的に接続するノード（図 4 において、c を付記したノード）には、電位 (Vdata) が与えられる。

#### 【0036】

10

20

30

40

50

次いで、期間 C において行われる動作について説明する。期間 C では、配線 G 1 にローレベルの電位が与えられ、配線 G 2 にハイレベルの電位が与えられ、配線 G 3 にハイレベルの電位が与えられ、配線 R L にローレベルの電位が与えられる。よって、トランジスタ 14、16 がオン状態となり、トランジスタ 12、13、15 がオフ状態となる。

#### 【0037】

なお、期間 B から期間 C に移行する際、配線 G 1 に与える電位をハイレベルからローレベルに切り替えてから、配線 G 2 及び配線 G 3 に与える電位をローレベルからハイレベルに切り替えることが望ましい。これにより、ノード a の電位の変動を抑制することができる。

#### 【0038】

図 4 (C) に、期間 C における画素 100 の動作を示す。期間 C では、上記動作により、ノード b に電位 (V data) が与えられるため、トランジスタ 11 のゲートの電位が (V data) まで上昇する。よって、トランジスタ 11 のゲートとソース間の電圧 (V gs(11)) が、電位 (V data) とノード a の電位 (V0 - Vth) の差 (V data - V0 + Vth) となる。このように、トランジスタ 11 のゲートとソース間の電圧がトランジスタ 11 のしきい値電圧を含む値となっている場合には、トランジスタ 11 のしきい値電圧 (Vth) のばらつきに依存せずに発光素子 18 に供給される電流を制御することが可能となる。また、トランジスタ 11 が劣化して、しきい値電圧 (Vth) が変化する場合であっても、当該変化に依存せずに発光素子 18 に供給される電流を制御することが可能となる。よって、表示ムラを低減でき、高い画質の表示を行うことが可能となる。

10

#### 【0039】

次いで、リセット期間において行われる動作について説明する。リセット期間では、配線 G 1 にローレベルの電位が与えられ、配線 G 2 にハイレベルの電位が与えられ、配線 G 3 にハイレベルの電位が与えられ、配線 R L にハイレベルの電位が与えられる。よって、トランジスタ 14 ~ 16 がオン状態となり、トランジスタ 12、13 がオフ状態となる。

#### 【0040】

図 4 (D) に、リセット期間における画素 100 の動作を示す。リセット期間では、上記動作により、トランジスタ 11 のゲートとソースが電気的に接続される。これにより、トランジスタ 11 のゲート及びキャパシタ 17 の一方の電極に蓄積されていた電荷が、トランジスタ 14 ~ 16 及び発光素子 18 を介して放出される。その結果、トランジスタ 11 がオフ状態となる。このように、トランジスタ 11 を確実にオフ状態とした後に電源電圧の供給を停止することで、電源電圧の供給を再開した際に発光素子 18 に電流が供給されることはなく、表示不良を抑制することが可能である。

20

#### 【0041】

なお、電源電圧の供給を再開した後であって、発光素子 18 に対して電流が供給される前に当該リセット期間を設ける場合であっても上記同様の効果を得ることが可能である。

30

#### 【0042】

##### <画素の動作例 2 >

40

次いで、図 2 (B) に示す画素 100 の動作について説明する。

#### 【0043】

図 5 は、図 2 (B) に示す画素 100 に接続される配線 G 1 ~ 配線 G 3 の電位と、配線 R L に供給される電位と、配線 S L に供給される信号 (V data) とのタイミングチャートを示す図である。図 5 に示すように、図 2 (B) に示す画素 100 の動作は、主に 1 水平走査期間に含まれる期間 A における動作、及び期間 B における動作、表示を行う期間 C における動作、並びにリセット期間における動作に分けることができる。

#### 【0044】

まず、期間 A において行われる動作について説明する。期間 A では、配線 G 1 にローレベルの電位が与えられ、配線 G 2 にローレベルの電位が与えられ、配線 G 3 にハイレベル

50

の電位が与えられ、配線 R L にローレベルの電位が与えられる。よって、トランジスタ 1 9 がオン状態となり、トランジスタ 1 2 ~ 1 5 がオフ状態となる。

#### 【 0 0 4 5 】

図 6 ( A ) に、期間 A における画素 1 0 0 の動作を示す。なお、図 6 ( A ) では、トランジスタ 1 2 ~ 1 5 、 1 9 をスイッチとして表記している ( 以下、図 6 ( B ) ~ ( D ) においても同様 )。期間 A では、上記動作により、トランジスタ 1 1 のソースと電気的に接続するノード ( 図 6 において、 a を付記したノード ) の電位が、共通電位 ( V c o m ) となる。

#### 【 0 0 4 6 】

次いで、期間 B において行われる動作について説明する。期間 B では、配線 G 1 にハイレベルの電位が与えられ、配線 G 2 にローレベルの電位が与えられ、配線 G 3 にローレベルの電位が与えられ、配線 R L にローレベルの電位が与えられる。よって、トランジスタ 1 2 、 1 3 がオン状態となり、トランジスタ 1 4 、 1 5 、 1 9 がオフ状態となる。

#### 【 0 0 4 7 】

なお、期間 A から期間 B に移行する際、配線 G 1 に与える電位をローレベルからハイレベルに切り替えてから、配線 G 3 に与える電位をハイレベルからローレベルに切り替えることが望ましい。これにより、ノード a の電位の変動を抑制することができる。

#### 【 0 0 4 8 】

また、配線 I L には電位 ( V 0 ) が与えられ、配線 S L には画像信号の電位 ( V d a t a ) が与えられる。

#### 【 0 0 4 9 】

図 6 ( B ) に、期間 B における画素 1 0 0 の動作を示す。なお、期間 B では、図 2 ( B ) に示す画素 1 0 0 は、図 2 ( A ) に示す画素 1 0 0 と同様の動作を行うため、ここでは上述の説明を援用することとする。

#### 【 0 0 5 0 】

次いで、期間 C において行われる動作について説明する。期間 C では、配線 G 1 にローレベルの電位が与えられ、配線 G 2 にハイレベルの電位が与えられ、配線 G 3 にローレベルの電位が与えられ、配線 R L にローレベルの電位が与えられる。よって、トランジスタ 1 4 がオン状態となり、トランジスタ 1 2 、 1 3 、 1 5 、 1 9 がオフ状態となる。

#### 【 0 0 5 1 】

なお、期間 B から期間 C に移行する際、配線 G 1 に与える電位をハイレベルからローレベルに切り替えてから、配線 G 2 に与える電位をローレベルからハイレベルに切り替えることが望ましい。これにより、ノード a の電位の変動を抑制することができる。

#### 【 0 0 5 2 】

図 6 ( C ) に、期間 C における画素 1 0 0 の動作を示す。なお、期間 C では、図 2 ( B ) に示す画素 1 0 0 は、図 2 ( A ) に示す画素 1 0 0 と同様の動作を行うため、ここでは上述の説明を援用することとする。

#### 【 0 0 5 3 】

次いで、リセット期間において行われる動作について説明する。リセット期間では、配線 G 1 にローレベルの電位が与えられ、配線 G 2 にハイレベルの電位が与えられ、配線 G 3 にローレベルの電位が与えられ、配線 R L にハイレベルの電位が与えられる。よって、トランジスタ 1 4 、 1 5 がオン状態となり、トランジスタ 1 2 、 1 3 、 1 9 がオフ状態となる。

#### 【 0 0 5 4 】

図 6 ( D ) に、リセット期間における画素 1 0 0 の動作を示す。リセット期間では、上記動作により、トランジスタ 1 1 のゲートとソースが電気的に接続される。これにより、トランジスタ 1 1 のゲート及びキャパシタ 1 7 の一方の電極に蓄積されていた電荷が、トランジスタ 1 4 、 1 5 及び発光素子 1 8 を介して放出される。その結果、トランジスタ 1 1 がオフ状態となる。このように、トランジスタ 1 1 を確実にオフ状態とした後に電源電圧の供給を停止することで、電源電圧の供給を再開した際に発光素子 1 8 に電流が供給さ

10

20

30

40

50

れることがなく、表示不良を抑制することが可能である。

【0055】

なお、電源電圧の供給を再開した後であって発光素子18に対して電流が供給されうる前に当該リセット期間を設ける場合であっても上記同様の効果を得ることが可能である。

【0056】

(実施の形態3)

図7は、上記実施の形態に示す画素と異なる画素200の構成例を示す回路図である。図7に示す画素200は、トランジスタ20～26と、キャパシタ27、28と、発光素子29とを有する。なお、トランジスタ20～26は、チャネルが酸化物半導体層に形成されるnチャネル型のトランジスタである。

10

【0057】

トランジスタ20では、ソース及びドレインの一方が配線SLに電気的に接続され、ゲートが配線G3に電気的に接続されている。

【0058】

トランジスタ21では、ソース及びドレインの一方が電位(V1)を供給する配線V1\_Wに電気的に接続され、ゲートが配線G2に電気的に接続されている。なお、ここでは、電位V1は、高電源電位(VDD)よりも低電位であり且つ低電源電位(VSS)よりも高電位であることとする。

20

【0059】

トランジスタ22では、ドレインが高電源電位(VDD)を供給する配線VDD\_Wに電気的に接続され、ゲートがトランジスタ21のソース及びドレインの他方に電気的に接続されている。

【0060】

トランジスタ23では、ソース及びドレインの一方がトランジスタ20のソース及びドレインの他方に電気的に接続され、ソース及びドレインの他方がトランジスタ22のソースに電気的に接続され、ゲートが配線G2に電気的に接続されている。

30

【0061】

トランジスタ24では、ソース及びドレインの一方が電位(V0)を供給する配線V0\_Wに電気的に接続され、ソース及びドレインの他方がトランジスタ22のソース、及びトランジスタ23のソース及びドレインの他方に電気的に接続され、ゲートが配線G1に電気的に接続されている。なお、ここでは、電位(V0)は、電位(V1)よりも低電位であり且つ低電源電位(VSS)よりも高電位であることとする。

【0062】

トランジスタ25では、ソース及びドレインの一方がトランジスタ21のソース及びドレインの他方、及びトランジスタ22のゲートに電気的に接続され、ソース及びドレインの他方がトランジスタ22のソース、トランジスタ23のソース及びドレインの他方、及びトランジスタ24のソース及びドレインの他方に電気的に接続され、ゲートが配線RLに電気的に接続されている。

30

【0063】

トランジスタ26では、ソース及びドレインの一方がトランジスタ22のソース、トランジスタ23のソース及びドレインの他方、トランジスタ24のソース及びドレインの他方、及びトランジスタ25のソース及びドレインの他方に電気的に接続され、ゲートが配線G4に電気的に接続されている。

40

【0064】

キャパシタ27では、一方の電極がトランジスタ21のソース及びドレインの他方、トランジスタ22のゲート、及びトランジスタ25のソース及びドレインの一方に電気的に接続され、他方の電極がトランジスタ20のソース及びドレインの他方、及びトランジスタ23のソース及びドレインの一方に電気的に接続されている。

【0065】

キャパシタ28では、一方の電極がトランジスタ20のソース及びドレインの他方、ト

50

ランジスタ 2 3 のソース及びドレインの一方、及びキャパシタ 2 7 の他方の電極に電気的に接続され、他方の電極がトランジスタ 2 2 のソース、トランジスタ 2 3 のソース及びドレインの他方、トランジスタ 2 4 のソース及びドレインの他方、トランジスタ 2 5 のソース及びドレインの他方、及びトランジスタ 2 6 のソース及びドレインの一方電気的に接続されている。

【 0 0 6 6 】

発光素子 2 9 では、アノードがトランジスタ 2 6 のソース及びドレインの他方に電気的に接続され、カソードが低電源電位 ( V S S ) を供給する配線 ( V S S \_ W ) に電気的に接続されている。

【 0 0 6 7 】

また、以下においては、トランジスタ 2 1 のソース及びドレインの他方、トランジスタ 2 2 のゲート、トランジスタ 2 5 のソース及びドレインの一方、及びキャパシタ 2 7 の一方の電極が電気的に接続するノードをノード D と呼び、トランジスタ 2 0 のソース及びドレインの他方、トランジスタ 2 3 のソース及びドレインの一方、キャパシタ 2 7 の他方の電極、及びキャパシタ 2 8 の一方の電極が電気的に接続するノードをノード E と呼び、トランジスタ 2 2 のソース、トランジスタ 2 3 のソース及びドレインの他方、トランジスタ 2 4 のソース及びドレインの他方、トランジスタ 2 5 のソース及びドレインの他方、トランジスタ 2 6 のソース及びドレインの一方、及びキャパシタ 2 8 の他方の電極が電気的に接続するノードをノード F と呼ぶこととする。

【 0 0 6 8 】

< 画素の動作例 >

上述した画素の動作例について図 8 を参照して説明する。具体的には、図 8 では、配線 G 1 ~ G 4 の電位、配線 R L の電位、ノード D、E、F の電位の変化を示している。

【 0 0 6 9 】

期間 t a において、配線 G 1 にハイレベルの電位が与えられ、配線 G 2 ~ G 4 にローレベルの電位が与えられ、配線 R L にローレベルの電位が与えられる。よって、トランジスタ 2 4 がオン状態となり、トランジスタ 2 0、2 1、2 3、2 5、2 6 がオフ状態となる。

【 0 0 7 0 】

期間 t b において、配線 G 2 にハイレベルの電位が与えられるようになる。これにより、トランジスタ 2 1、2 3 がオン状態となる。その結果、ノード D の電位が、電位 ( V 1 ) となり、ノード E の電位が、電位 ( V 0 ) となる。さらに、ノード D の電位が電位 ( V 1 ) になったことに付随して、トランジスタ 2 2 がオン状態となる。

【 0 0 7 1 】

期間 t c において、配線 G 1 にローレベルの電位が与えられるようになる。これにより、トランジスタ 2 4 がオフ状態となる。ここで、トランジスタ 2 2 は、ゲートとソース間の電圧がしきい値電圧以下となるまでオン状態を維持する。すなわち、トランジスタ 2 2 は、ノード F ( トランジスタ 2 2 のソース ) の電位が、ノード D の電位 ( 電位 ( V 1 ) ) からトランジスタ 2 2 のしきい値電圧 ( V t h ) 分低い値となるまでオン状態を維持する。その結果、ノード F の電位が、電位 ( V 1 - V t h ) となる。なお、期間 t c においては、ノード E の電位も電位 ( V 1 - V t h ) まで上昇することになる。

【 0 0 7 2 】

期間 t d において、配線 G 2 にローレベルの電位が与えられるようになる。これにより、トランジスタ 2 1、2 3 がオフ状態となる。

【 0 0 7 3 】

期間 t e において、配線 G 3 にハイレベルの電位が与えられるようになる。これにより、トランジスタ 2 0 がオン状態となる。なお、期間 t e において、配線 S L には、画像信号の電位 ( V d a t a ) が供給されている。その結果、ノード E の電位が電位 ( V d a t a ) となる。さらに、ノード D とノード F の電位もノード E の電位によって変動する。具体的には、浮遊状態にあるノード D の電位が、キャパシタ 2 7 を介したノード E との容量

10

20

30

40

50

結合によりノード E の電位の変動分（画像信号に応じた電位（V data）と、電位（V 1）からトランジスタ 2 2 のしきい値電圧（V th）分低い値との差分）上昇又は下降し（ノード D の電位が、 $V 1 + [V data - (V 1 - V th)] = V data + V th$  となる）、且つ浮遊状態にあるノード F の電位が、キャパシタ 2 8 を介したノード E との容量結合により当該ノード E の電位の変動分上昇又は下降する（ノード F の電位が、 $V 1 - V th + [V data - (V 1 - V th)] = V data$  となる）。

#### 【0074】

期間 t f において、配線 G 1 にハイレベルの電位が与えられるようになる。これにより、トランジスタ 2 4 がオン状態となる。その結果、ノード F の電位が、電位（V 0）となる。

10

#### 【0075】

期間 t g において、配線 G 1 にローレベルの電位が与えられるようになる。これにより、トランジスタ 2 4 がオフ状態となる。

#### 【0076】

期間 t h において、配線 G 4 にハイレベルの電位が与えられるようになる。これにより、トランジスタ 2 6 がオン状態となる。その結果、トランジスタ 2 2 のゲートとソース間の電圧に応じた電流が発光素子 2 9 に供給される。ここで、当該電圧は、ノード D の電位（V data + V th）とノード F の電位の差である。この場合、発光素子 2 9 に供給される電流（トランジスタ 2 2 の飽和領域におけるドレイン電流）は、トランジスタ 2 2 のしきい値電圧に依存することがない。

20

#### 【0077】

期間 t i において、配線 R L にハイレベルの電位が与えられるようになる。これにより、トランジスタ 2 5 がオン状態になる。その結果、トランジスタ 2 2 がオフ状態となる。

#### 【0078】

そして、期間 t i 後に表示装置に対する電源電圧の供給を停止する。このように、トランジスタ 2 2 を確実にオフ状態とした後に電源電圧の供給を停止することで、電源電圧の供給を再開した際に発光素子 2 9 に電流が供給されることがなく、表示不良を抑制することが可能である。

#### 【0079】

なお、電源電圧の供給を再開した後であって発光素子 2 9 に対して電流が供給されうる前に当該期間 t i を設ける場合であっても上記同様の効果を得ることが可能である。

30

#### 【0080】

##### （実施の形態 4）

本実施の形態では、表示装置の構造例について説明する。具体的には、本実施の形態では、トップエミッション構造の表示装置について例示する。ただし、本明細書で開示される表示装置は、トップエミッション構造に限定されず、ボトムエミッション構造、デュアルエミッション構造とすることが可能であることは言うまでもない。なお、デュアルエミッション構造とは、発光素子の光が表示装置の 2 面から射出される構造を意味する。

#### 【0081】

##### <断面構造例>

40

図 9 は、本明細書で開示される表示装置の一例を示す断面図である。具体的には、図 9 に示す表示装置は、図 2 (A) に示すトランジスタ 1 1、1 6、キャパシタ 1 7、及び発光素子 1 8 の一例を示す断面図である。

#### 【0082】

トランジスタ 1 1 は、絶縁表面を有する基板 8 0 0 上に、ゲートとして機能する導電膜 8 1 2 と、導電膜 8 1 2 上のゲート絶縁膜 8 0 2 と、導電膜 8 1 2 と重なる位置においてゲート絶縁膜 8 0 2 上に位置する酸化物半導体層 8 1 3 と、ソースまたはドレインとして機能し、酸化物半導体層 8 1 3 上に位置する導電膜 8 1 4 及び導電膜 8 1 5 とを有する。なお、導電膜 8 1 4 は、図 2 (A) に示す配線 V D D \_ W である。

#### 【0083】

50

トランジスタ 16 は、絶縁表面を有する基板 800 上に、ゲートとして機能する導電膜 816 と、導電膜 816 上のゲート絶縁膜 802 と、導電膜 816 と重なる位置においてゲート絶縁膜 802 上に位置する酸化物半導体層 817 と、ソースまたはドレインとして機能し、酸化物半導体層 817 上に位置する導電膜 815 及び導電膜 818 とを有する。なお、導電膜 816 は、図 2 (A) に示す配線 G3 である。

#### 【0084】

キャパシタ 17 は、絶縁表面を有する基板 800 上に、導電膜 819 と、導電膜 819 上のゲート絶縁膜 802 と、導電膜 819 と重なる位置においてゲート絶縁膜 802 上に位置する導電膜 815 とを有する。

#### 【0085】

また、導電膜 814、815、818 上には、絶縁膜 820、821 が形成されている。そして、絶縁膜 821 上には、発光素子 18 のアノードとして機能する導電膜 822 が設けられている。なお、導電膜 822 は、絶縁膜 820 及び絶縁膜 821 に形成されたコントクトホール 823 において導電膜 818 に電気的に接続されている。

#### 【0086】

また、導電膜 822 の一部を露出させる開口部を有した絶縁膜 824 が、絶縁膜 821 上に設けられている。導電膜 822 の一部及び絶縁膜 824 上には、EL 層 825 と、発光素子 18 のカソードとして機能する導電膜 826 とが、順に積層するように設けられている。導電膜 822 と、EL 層 825 と、導電膜 826 とが重なっている領域が、発光素子 18 に相当する。

#### 【0087】

<酸化物半導体層 813、817 の具体例>

<(1) 材料について>

酸化物半導体層 813、817 として、少なくともインジウムを含む膜を適用することができる。特に、インジウムと亜鉛を含む膜を適用することが好ましい。また、トランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウムを有する膜を適用することが好ましい。

#### 【0088】

また、酸化物半導体層 813、817 として、スズ、ハフニウム、アルミニウム、若しくはジルコニウム、又はランタノイドである、ランタン、セリウム、プラセオジム、ネオジム、サマリウム、ユウロピウム、ガドリニウム、テルビウム、ジスプロシウム、ホルミウム、エルビウム、ツリウム、イッテルビウム、若しくはルテチウムのいずれか一種又は複数種をスタビライザーとして含む膜を適用することもできる。

#### 【0089】

例えば、酸化物半導体層 813、817 として、酸化インジウム膜、二元系金属の酸化物である In-Zn 系酸化物膜、In-Mg 系酸化物膜、In-Ga 系酸化物膜、三元系金属の酸化物である In-Ga-Zn 系酸化物膜、In-Al-Zn 系酸化物膜、In-Sn-Zn 系酸化物膜、In-Hf-Zn 系酸化物膜、In-La-Zn 系酸化物膜、In-Ce-Zn 系酸化物膜、In-Pr-Zn 系酸化物膜、In-Nd-Zn 系酸化物膜、In-Sm-Zn 系酸化物膜、In-Eu-Zn 系酸化物膜、In-Gd-Zn 系酸化物膜、In-Tb-Zn 系酸化物膜、In-Dy-Zn 系酸化物膜、In-Ho-Zn 系酸化物膜、In-Er-Zn 系酸化物膜、In-Tm-Zn 系酸化物膜、In-Yb-Zn 系酸化物膜、In-Lu-Zn 系酸化物膜、四元系金属の酸化物である In-Sn-Ga-Zn 系酸化物膜、In-Hf-Ga-Zn 系酸化物膜、In-Al-Ga-Zn 系酸化物膜、In-Sn-Al-Zn 系酸化物膜、In-Sn-Hf-Zn 系酸化物膜、In-Hf-Al-Zn 系酸化物膜を適用することができる。

#### 【0090】

ここで、例えば、In-Ga-Zn 系酸化物とは、In と Ga と Zn を主成分として有する酸化物という意味であり、In と Ga と Zn の比率は問わない。また、In と Ga と Zn 以外の金属元素が入っていてもよい。

10

20

30

40

50

## 【0091】

なお、酸化物半導体層813、817を構成する酸素の一部は窒素で置換されてもよい。

## 【0092】

<(2)結晶構造について>

酸化物半導体層813、817として、単結晶、多結晶(ポリクリスタルともいう)又は非晶質などの結晶構造を有する膜を適用することができる。また、酸化物半導体層813、817として、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)膜を適用することができる。以下、CAAC-OS膜について詳述する。

10

## 【0093】

CAAC-OS膜は、例えば、透過型電子顕微鏡(TEM: Transmission Electron Microscope)による観察像で、結晶領域を観察することができる場合がある。例えば、当該結晶領域は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、CAAC-OS膜に含まれる結晶領域の境界を明確に確認できない場合がある。また、TEMによってCAAC-OS膜には粒界は確認できない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が抑制される。

## 【0094】

CAAC-OS膜に含まれる結晶領域は、c軸がCAAC-OS膜の被形成面の法線ベクトル又は表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状又は六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状又は金属原子と酸素原子とが層状に配列している。なお、異なる結晶領域間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°以上5°以下の範囲も含まれることとする。

20

## 【0095】

なお、CAAC-OS膜において、膜厚方向における結晶領域の分布が一様でないことがある。例えば、CAAC-OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶領域の占める割合が高くなることがある。

30

## 【0096】

CAAC-OS膜に含まれる結晶領域のc軸は、CAAC-OS膜の被形成面の法線ベクトル又は表面の法線ベクトルに平行な方向に揃うため、CAAC-OS膜の形状(被形成面の断面形状又は表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶領域のc軸の方向は、CAAC-OS膜が形成されたときの被形成面の法線ベクトル又は表面の法線ベクトルに平行な方向となる。結晶領域は、成膜することにより、又は成膜後に熱処理などの結晶化処理を行うことにより形成される。

## 【0097】

CAAC-OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

40

## 【0098】

<(3)層構造について>

酸化物半導体層813、817として、単一層からなる酸化物半導体膜のみならず複数種の酸化物半導体膜の積層を適用することができる。例えば、非晶質酸化物半導体膜、多結晶酸化物半導体膜、及びCAAC-OS膜の少なくとも2種を含む層を酸化物半導体層813、817として適用することができる。

## 【0099】

また、組成の異なる酸化物半導体膜の積層からなる層を酸化物半導体層813、817として適用することもできる。具体的には、ゲート絶縁膜802と接する面を含む第1の酸化物半導体膜(以下、下層ともいう)と、絶縁膜820と接し、且つ第1の酸化物半導

50

体膜と組成が異なる第2の酸化物半導体膜（以下、上層ともいう）とを含む層を酸化物半導体層813、817として適用することもできる。なお、この場合、下層にチャネルが形成される領域の多くが含まれることになる。下層は、上層よりもゲートとして機能する導電膜812、816に近接するからである。

【0100】

ここで、下層及び上層が共にインジウム、ガリウム、及び亜鉛を含んで構成される場合には、下層におけるインジウム濃度を上層におけるインジウム濃度よりも高くし、且つ上層におけるガリウム濃度を下層におけるガリウム濃度よりも高くすること、又は／及び、下層におけるインジウム濃度を下層におけるガリウム濃度よりも高くし、且つ上層におけるガリウム濃度を上層におけるインジウム濃度よりも高くすることが好ましい。

10

【0101】

これにより、酸化物半導体層813、817を有するトランジスタの移動度の向上及び寄生チャネルの形成の抑制を図ることが可能となる。具体的には、下層のインジウム濃度を高くすることによって当該トランジスタの移動度の向上を図ることが可能である。これは、酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、Inの含有率を高くすることでs軌道のオーバーラップが多くなることに起因する。また、上層のガリウム濃度を高くすることによって酸素の脱離を抑制し、上層における寄生チャネルの形成を抑制することが可能である。これは、GaがInと比較して酸素欠損の形成エネルギーが大きく、酸素欠損が生じにくいことに起因する。

【0102】

20

＜ゲート絶縁膜802の具体例＞

ゲート絶縁膜802として、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、又は酸化ガリウム膜などの無機絶縁材料膜を適用することができる。また、これらの材料の積層を適用することもできる。なお、酸化アルミニウム膜は、水素などの不純物、及び酸素の両方に対して膜を透過させない遮断（ブロッキング）効果が高い。よって、ゲート絶縁膜802として酸化アルミニウム膜を含む層を適用することで、酸化物半導体層813、817からの酸素の脱離を防止するとともに、酸化物半導体層813、817への水素などの不純物の混入を防止することができる。

【0103】

30

また、ゲート絶縁膜802として、酸化ハフニウム膜、酸化イットリウム膜、ハフニウムシリケート（ $HfSi_xO_y$  ( $x > 0$ 、 $y > 0$ )）膜、窒素が添加されたハフニウムシリケート膜、ハフニウムアルミネート（ $HfAl_xO_y$  ( $x > 0$ 、 $y > 0$ )）膜、又は酸化ランタン膜など（いわゆるhigh-k材料からなる膜）を含む膜を適用することもできる。このような膜を用いることでゲートリーク電流の低減が可能である。

【0104】

＜導電膜812、816、819の具体例＞

導電膜812、816、819として、アルミニウム、銅、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素又はこれらの元素を成分とする合金からなる膜を適用することができる。また、導電膜812、816、819として、窒素を含む金属酸化物、具体的には、窒素を含むIn-Ga-Zn-O膜、窒素を含むIn-Sn-O膜、窒素を含むIn-Ga-O膜、窒素を含むIn-Zn-O膜、窒素を含むSn-O膜、窒素を含むIn-O膜、又は金属窒化膜（InN、SnNなど）を適用することもできる。これらの窒化膜は5eV（電子ボルト）以上、好ましくは5.5eV（電子ボルト）以上の仕事関数を有し、ゲートとして用いた場合、トランジスタのしきい値電圧をプラスにすることができる、所謂ノーマリーオフのスイッチング素子を実現できる。また、これらの膜の積層を適用することもできる。

40

【0105】

＜導電膜814、815、818の具体例＞

導電膜814、815、818として、アルミニウム、銅、チタン、タンタル、タンゲ

50

ステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素、これらの元素を成分とする合金、又はこれらの元素を含む窒化物からなる膜を適用することができる。また、これらの膜の積層を適用することもできる。

【0106】

<絶縁膜820の具体例>

絶縁膜820として、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、又は酸化ガリウム膜などの無機絶縁材料膜を適用することができる。また、これらの膜の積層を適用することもできる。なお、酸化アルミニウム膜は、水素などの不純物、及び酸素の両方に対して膜を透過させない遮断（ブロッキング）効果が高い。よって、絶縁膜820として酸化アルミニウム膜を含む層を適用することで、酸化物半導体層813、817からの酸素の脱離を防止するとともに、酸化物半導体層813、817への水素などの不純物の混入を防止することができる。

【0107】

<絶縁膜821の具体例>

絶縁膜821として、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、又は酸化ガリウム膜などの無機絶縁材料膜を適用することができる。また、ポリイミド、アクリル等の有機絶縁材料膜を適用することもできる。また、これらの膜の積層を適用することもできる。

【0108】

<導電膜822の具体例>

導電膜822として、アルミニウム、銅、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素、これらの元素を成分とする合金、又はこれらの元素を含む窒化物からなる膜を適用することができる。また、これらの膜の積層を適用することもできる。特に、導電膜822として、反射率の高い金属（アルミニウム、銀など）又は当該金属を含む合金を適用することが好ましい。

【0109】

<EL層825の具体例>

EL層825として、発光性の有機物を含む発光層を含む単層又は積層を適用することができる。

【0110】

<導電膜826の具体例>

導電膜826として、酸化インジウム-酸化スズ、シリコン若しくは酸化シリコンを含有した酸化インジウム-酸化スズ、酸化インジウム-酸化亜鉛、酸化タンゲステン及び酸化亜鉛を含有した酸化インジウムなどの透光性を有する導電膜を適用することができる。

【0111】

<絶縁膜824の具体例>

絶縁膜824として、ポリイミド、アクリル等の有機絶縁材料膜を適用することができる。

【実施例1】

【0112】

図10は、表示装置の一例を示す斜視図である。

【0113】

図10に示す表示装置は、パネル1601と、回路基板1602と、接続部1603とを有している。パネル1601は、画素が複数設けられた画素部1604と、複数の画素を行ごとに選択する走査線駆動回路1605と、選択された行内の画素への画像信号の入力を制御する信号線駆動回路1606とを有する。具体的には、走査線駆動回路1605では、図1に示す配線GL、図2(A)、(B)に示す配線G1～G3、図7に示す配線G1～G4に入力する信号を生成する。

【0114】

10

20

30

40

50

回路基板 1602 から、接続部 1603 を介して、各種信号と、電源の電位とが、パネル 1601 に入力される。接続部 1603 には、FPC (Flexible Printed Circuit)などを用いることができる。また、接続部 1603 に COF テープを用いる場合、回路基板 1602 内の一部の回路、又はパネル 1601 が有する走査線駆動回路 1605 や信号線駆動回路 1606 の一部などを別途用意したチップに形成しておき、COF (Chip On Film) 法を用いて当該チップを COF テープに接続しておいても良い。

【実施例 2】

【0115】

本発明の一態様に係る表示装置は、テレビジョン受像機、電子計算機用ディスプレイ、記録媒体を備えた画像再生装置（代表的には DVD : Digital Versatile Disc 等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る表示装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図 11 に示す。

【0116】

図 11 (A) は携帯型ゲーム機であり、筐体 5001、筐体 5002、表示部 5003、表示部 5004、マイクロホン 5005、スピーカー 5006、操作キー 5007、スタイルス 5008 等を有する。本発明の一態様に係る表示装置は、表示部 5003、表示部 5004 に用いることができる。なお、図 11 (A) に示した携帯型ゲーム機は、2 つの表示部 5003 と表示部 5004 とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

【0117】

図 11 (B) はテレビジョン受像機であり、筐体 5201、表示部 5202、支持台 5203 等を有する。本発明の一態様に係る表示装置は、表示部 5202 に用いることができる。

【0118】

図 11 (C) はノート型パーソナルコンピュータであり、筐体 5401、表示部 5402、キーボード 5403、ポインティングデバイス 5404 等を有する。本発明の一態様に係る表示装置は、表示部 5402 に用いることができる。

【0119】

図 11 (D) は携帯情報端末であり、筐体 5601、表示部 5602、操作キー 5603 等を有する。図 11 (D) に示す携帯情報端末は、モジュールが筐体 5601 に内蔵されていても良い。本発明の一態様に係る表示装置は、表示部 5602 に用いることができる。

【符号の説明】

【0120】

- |    |        |

|----|--------|

| 1  | トランジスタ |

| 2  | トランジスタ |

| 3  | トランジスタ |

| 4  | キャパシタ  |

| 5  | 発光素子   |

| 10 | 画素     |

| 11 | トランジスタ |

| 12 | トランジスタ |

| 13 | トランジスタ |

| 14 | トランジスタ |

10

20

30

40

50

|         |           |    |

|---------|-----------|----|

| 1 5     | トランジスタ    |    |

| 1 6     | トランジスタ    |    |

| 1 7     | キャパシタ     |    |

| 1 8     | 発光素子      |    |

| 1 9     | トランジスタ    | 10 |

| 2 0     | トランジスタ    |    |

| 2 1     | トランジスタ    |    |

| 2 2     | トランジスタ    |    |

| 2 3     | トランジスタ    |    |

| 2 4     | トランジスタ    |    |

| 2 5     | トランジスタ    |    |

| 2 6     | トランジスタ    |    |

| 2 7     | キャパシタ     |    |

| 2 8     | キャパシタ     |    |

| 2 9     | 発光素子      |    |

| 1 0 0   | 画素        |    |

| 2 0 0   | 画素        |    |

| 8 0 0   | 基板        |    |

| 8 0 2   | ゲート絶縁膜    |    |

| 8 1 2   | 導電膜       | 20 |

| 8 1 3   | 酸化物半導体層   |    |

| 8 1 4   | 導電膜       |    |

| 8 1 5   | 導電膜       |    |

| 8 1 6   | 導電膜       |    |

| 8 1 7   | 酸化物半導体層   |    |

| 8 1 8   | 導電膜       |    |

| 8 1 9   | 導電膜       |    |

| 8 2 0   | 絶縁膜       |    |

| 8 2 1   | 絶縁膜       |    |

| 8 2 2   | 導電膜       | 30 |

| 8 2 3   | コントラクトホール |    |

| 8 2 4   | 絶縁膜       |    |

| 8 2 5   | EL層       |    |

| 8 2 6   | 導電膜       |    |

| 1 6 0 1 | パネル       |    |

| 1 6 0 2 | 回路基板      |    |

| 1 6 0 3 | 接続部       |    |

| 1 6 0 4 | 画素部       |    |

| 1 6 0 5 | 走査線駆動回路   |    |

| 1 6 0 6 | 信号線駆動回路   | 40 |

| 5 0 0 1 | 筐体        |    |

| 5 0 0 2 | 筐体        |    |

| 5 0 0 3 | 表示部       |    |

| 5 0 0 4 | 表示部       |    |

| 5 0 0 5 | マイクロホン    |    |

| 5 0 0 6 | スピーカー     |    |

| 5 0 0 7 | 操作キー      |    |

| 5 0 0 8 | スタイルス     |    |

| 5 2 0 1 | 筐体        |    |

| 5 2 0 2 | 表示部       | 50 |

|         |             |

|---------|-------------|

| 5 2 0 3 | 支持台         |

| 5 4 0 1 | 筐体          |

| 5 4 0 2 | 表示部         |

| 5 4 0 3 | キー ボード      |

| 5 4 0 4 | ポインティングデバイス |

| 5 6 0 1 | 筐体          |

| 5 6 0 2 | 表示部         |

| 5 6 0 3 | 操作キー        |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 四 8 】

【 図 9 】

【 10 】

## 【図 1 1】

---

フロントページの続き

(51)Int.Cl.

F I

H 01L 29/78 613Z

H 01L 29/78 618B

(56)参考文献 特開2008-176287 (JP, A)

特開2007-179041 (JP, A)

特開2000-221942 (JP, A)

米国特許出願公開第2011/0193768 (US, A1)

特表2011-520138 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 3233

G 09 G 3 / 20

H 01 L 29 / 786

H 01 L 51 / 50