(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 10 2004 038 552 B4 2006.05.11

(12)

## Patentschrift

(21) Aktenzeichen: 10 2004 038 552.1

(51) Int Cl.<sup>8</sup>: H03K 5/24 (2006.01)

(22) Anmelddatum: 06.08.2004

H03M 1/12 (2006.01)

(43) Offenlegungstag: 23.02.2006

(45) Veröffentlichungstag

der Patenterteilung: 11.05.2006

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

(73) Patentinhaber:

ATMEL Germany GmbH, 74072 Heilbronn, DE

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

US 60 08 673 A

EP 14 92 232 A1

(72) Erfinder:

Hehn, Lars, 74080 Heilbronn, DE; Gruber, Berthold, 74906 Bad Rappenau, DE

(54) Bezeichnung: Spannungskomparator

(57) Hauptanspruch: Spannungskomparator zum Vergleich einer Vergleichsspannung ( $U_{diff}$ ) mit einer Schwelle, mit

– einem ersten Spannungs-Strom-Wandler (1) zur Wandlung einer die Schwelle bestimmenden Referenzspannung ( $U_{ref}$ ) in einen von der Referenzspannung ( $U_{ref}$ ) abhängigen Referenzstrom ( $I_{ref}$ )

– einem zweiten Spannungs-Strom-Wandler (2) zur Wandlung der Vergleichsspannung ( $U_{diff}$ ) in einen von der Vergleichsspannung ( $U_{diff}$ ) abhängigen Vergleichsstrom ( $I_v$ ),

– zwei Eingängen ( $IN_{-n}$ ,  $IN_{-p}$ ), an denen die Vergleichsspannung als Differenzspannung ( $U_{diff}$ ) anliegt, und

– einer Ausgangsstufe (3) zur Ausgabe eines digitalen Ausgangspegels, wobei der Ausgangspegel von dem Referenzstrom ( $I_{ref}$ ) und dem Vergleichsstrom ( $I_v$ ) abhängig ist.

**Beschreibung**

**[0001]** Die vorliegende Erfindung betrifft einen Spannungskomparator.

**[0002]** Spannungskomparatoren haben die Aufgabe, eine Vergleichsspannung mit einer Referenzspannung zu vergleichen und das Ergebnis dieses Vergleiches am Ausgang möglichst trägeheitslos zu signalisieren. Analogkomparatoren wirken als Schnittstelle zwischen analogen und digitalen Funktionseinheiten. Das amplitudenanaloge Eingangssignal (Spannung) wird in ein binäres Ausgangssignal (Spannung) umgewandelt. Am Ausgang tritt entweder H-Pegel (High-Pegel, hohes Potential) oder L-Pegel (Low-Pegel, niedriges Potential) auf. Komparatorschaltkreise sind beispielsweise spezielle Verstärker, die entsprechend den Operationsverstärkern einen <sup>Diff</sup>erenzeingang und einen unsymmetrischen Ausgang aufweisen können. Die Ausgangsstufe des Komparators ist meist so ausgelegt, dass sie mit den Logikpegeln mehrerer digitaler Schaltkreisfamilien kompatibel ist. Das bedeutet, dass digitale Schaltkreise ohne Zwischenschalten weiterer Elemente vom Komparatorausgang ansteuerbar sind. Komparatoren können dabei ohne und mit Rückkopplung (Hysterese) betrieben werden.

**[0003]** Typische Komparatoranwendungen sind Schwellwertschalter (Pegeldetektoren), Fensterdiskriminatoren, Gleichrichterschaltungen für kleine Signale, Schmitt-Trigger und andere Kippschaltungen, die u.a. zur Flankenversteilung und zur Umwandlung zeitveränderlicher, beispielsweise sinusförmiger Spannungen in eine Rechteckfolge angewendet werden.

**Stand der Technik**

**[0004]** Aus der US 6,008,673 ist ein Niederspannungs-Komparator bekannt, der zwei Ströme miteinander vergleicht und in Abhängigkeit des Vergleichs ein Ausgangssignal abgibt. Der mittels eines Stromspiegels gespiegelte Strom ist dabei abhängig von der Eingangsspannung.

**Aufgabenstellung**

**[0005]** Aufgabe der vorliegenden Erfindung ist es, einen Spannungskomparator anzugeben, der möglichst im Automobilbereich einsetzbar ist. Diese Aufgabe wird durch den Spannungskomparator mit den Merkmalen des Anspruchs 1 gelöst. Günstige Weiterbildungen und Ausgestaltungsformen sind jeweils Gegenstand von Unteransprüchen.

**[0006]** Gemäß der Erfindung wird anstelle eines Differenzverstärkers eine Komparatorfunktion durch zu vergleichende Ströme bereitgestellt. Demzufolge ist ein Spannungskomparator zum Vergleich einer Ver-

gleichsspannung mit einer Schwelle vorgesehen. Der Spannungskomparator weist dabei vorzugsweise einen ersten Spannungs-Strom-Wandler zur Wandlung einer die Schwelle bestimmenden Referenzspannung in einen von der Referenzspannung abhängigen Referenzstrom auf. Im einfachsten Fall ist die Referenzspannung eine konstante Spannung, beispielsweise eine Zehnerspannung oder Versorgungsspannung. Bevorzugt ist die Referenzspannung jedoch eine einstellbare Spannung, beispielsweise eine analoge Ausgangsspannung eines Mikrocontrollers. Um den Referenzstrom zu generieren, wirkt der erste Spannungs-Strom-Wandler an seinem Ausgang vorteilhafterweise wie eine referenzspannungsabhängige Stromquelle mit einem Innenwiderstand.

**[0007]** Für den Spannungskomparator ist ein zweiter Spannungs-Strom-Wandler zur Wandlung der Vergleichsspannung in einen von der Vergleichsspannung abhängigen Vergleichsstrom erforderlich. Hinsichtlich des Vergleichsstromes wirkt der zweite Spannungs-Strom-Wandler an seinem Ausgang vorteilhafterweise wie eine vergleichsspannungsabhängige Stromquelle mit Innenwiderstand.

**[0008]** An zwei Eingängen ist die Vergleichsspannung als Differenzspannung angelegt. Die Differenzspannung kann dabei von einer an beiden Eingängen anliegenden Gleichtakteingangsspannung signifikant abweichen.

**[0009]** Weiterhin weist der Spannungskomparator eine Ausgangsstufe zur Ausgabe eines digitalen Ausgangspegels auf, wobei der Ausgangspegel von dem Referenzstrom und dem Vergleichsstrom abhängig ist. Die Abhängigkeit des Ausgangspegels bildet dabei die Komparatorfunktion ab, indem beispielsweise ein erster Ausgangspegel (high) einer Vergleichsspannung oberhalb einer ersten Schwelle zugeordnet ist und ein zweiter Ausgangspegel (low) einer Vergleichsspannung unterhalb einer zweiten Schwelle zugeordnet ist, wobei die erste und die zweite Schwelle gleich oder unterschiedlich sein können und beispielsweise eine Funktion eines Fensterkomparators abbilden.

**[0010]** Eine vorteilhafte Ausgestaltung der Erfindung sieht vor, dass die Ausgangsstufe mit einem Stromsummationsknoten verbunden ist, in dem sich der Vergleichsstrom und ein von dem Referenzstrom abhängiger Schwellenstrom summieren, wobei einer der beiden Ströme als negativer Wert in die Summation eingeht. Die Summe der in den Stromsummationsknoten hinein und heraus fließenden Ströme ist dabei stets null. Die Beziehung der Abhängigkeit zwischen dem Schwellenstrom und dem Referenzstrom ist dabei durch eine mathematische Funktion gegeben.

**[0011]** In einer Weiterbildung der Erfindung sind Mittel zur Multiplikation des Referenzstromes mit einem Multiplikationsfaktor vorgesehen, so dass der mittels des Multiplikationsfaktors generierte Schwellenstrom in die Summation im Stromsummationsknoten ein geht. Beispielsweise kann zum Vervielfachen des Stromes ein Mehrfaches des Referenzstromes zum Schwellenstrom mittels NMOS- oder PMOS-Transistoren geschalten werden. Zur Weiterbildung der Erfindung ist hierzu ein Referenzstromspiegel vorgesehen, dessen Stromspiegelverhältnis als Mittel zur Multiplikation einstellbar, insbesondere schaltbar ist. Beispielsweise können mehrere Transistoren, die den gespiegelten Strom des Referenzstromspiegels steuern parallel geschalten sein. Zur Einstellung des Multiplikationsfaktors werden einer oder mehrere dieser steuernden Transistoren aktiviert beziehungsweise deaktiviert, indem beispielsweise deren Gate-Potential verändert wird.

**[0012]** Eine bevorzugte Ausgestaltung der Erfindung sieht vor, dass der Ausgangspegel durch ein Potential im Stromsummationsknoten bestimmt ist, das von dem Vergleichstrom und dem Schwellenstrom abhängig ist. Bevorzugt ist der Spannungs-komparator dabei derart dimensioniert, dass sich das Potential im Stromsummationsknoten in dem Bereich signifikant ändert, in dem Werte des Vergleichsstroms und des Schwellenstroms nahe beieinander liegen. Bevorzugt ist das Potential im Stromsummationsknoten dabei unabhängig von elektrischen Eigen-schaften der Ausgangsstufe, diese weist hierzu vor teilhafterweise einen hochohmigen Eingang auf.

**[0013]** Vorzugsweise werden die Ausgangsstufe und nachfolgende digitale Auswerteschaltkreise und vorzugsweise auch der die Spannungsreferenz generierende Schaltkreis mit Transistoreigenschaften für geringe Durchbruchsspannungen von 10V hergestellt. Geringe Durchbruchsspannungen ermöglichen eine kleine Strukturbreite, die eine hohe Integrationsdichte insbesondere für digitale Auswerteschaltungen oder Kommunikationsschaltungen ermöglicht. In einer besonders bevorzugten Weiterbildung der Erfindung ist daher ein Spannungsbegrenzungsmittel zur Begrenzung der zwischen dem Stromsummationsknoten und dem Masseanschluss liegenden Spannung vorgesehen.

**[0014]** Ein Beispiel für ein derartiges Spannungsbegrenzungsmittel ist eine entsprechend mit dem Stromsummationsknoten und dem Masseanschluss verbundene Zehnerdiode. Oberhalb der Zehnerspannung fließt durch die Zehnerdiode ein zusätzlicher Zehnerstrom aus dem Stromsummationsknoten. Ohne einen Zehnerstrom ist in einer vorteilhaften, weiterbildenden Ausgestaltung der Erfindung vorgesehen, dass der Stromsummationsknoten über zumindest einen (zweiten) Transistor mit einem, mit dem zweiten Spannungs-Strom-Wandler verbunde-

nen Stromspiegel verbunden ist. Dabei weist dieser, als Spannungsbegrenzungsmittel wirkende Transistor gegenüber der Ausgangsstufe eine höhere Durchbruchsspannungsfestigkeit auf. Insbesondere die hohe Durchbruchsspannungsfestigkeit dieses Transistors ermöglicht die Verwendung des Spannungskomparators als integrierter Bestandteil in einer Schaltung in einer so genannten Smart-Power-Technologie für den Einsatz in einem Kraftfahrzeug mit einer 42V Bordnetzspannung. Vorzugsweise weist dieser Transistor hierzu eine Durchbruchsspannungsfestigkeit von 80V auf.

**[0015]** Der als Spannungsbegrenzungsmittel wirkende Transistor ist hierbei vorzugsweise als Emitterfolger geschaltet. So ist vorteilhafterweise das Gate beziehungsweise die Basis dieses Transistors mit der Versorgungsspannung der Ausgangsstufe verbunden oder verbindbar.

**[0016]** Werden auch Referenzspannungen größer als die maximal zulässige Spannung in der Ausgangsstufe benötigt, ist in einer vorteilhaften Ausgestaltung der Erfindung vorgesehen, dass der Stromsummationsknoten über einen anderen Transistor mit dem ersten Spannungs-Strom-Wandler verbunden ist, wobei dieser, als Spannungsbegrenzungsmittel wirkende Transistor ebenfalls gegenüber der Ausgangsstufe eine höhere Durchbruchsspannungsfestigkeit aufweist. Vorzugsweise ist ebenfalls das Gate beziehungsweise die Basis dieses Transistors mit der Versorgungsspannung der Ausgangsstufe verbunden oder verbindbar.

**[0017]** Eine vorteilhafte Ausgestaltung der Erfindung sieht vor, dass der erste Spannungs-Strom-Wandler und der zweite Spannungs-Strom-Wandler auf einem Halbleiterchip zu einander benachbart oder ineinander gesetzt angeordnet sind. Dies bewirkt, dass beide Wandler im Wesentlichen derselben Betriebstemperatur in diesem Bereich des Halbleiterchips ausgesetzt sind. Zudem sind die Auswirkungen von Fertigungstoleranzen, die über die Gesamtfläche eines Halbleiterchips auftreten in diesem Bereich der benachbarten oder ineinander verschachtelten Wandler nur gering. Dieses so genannte „matching“ der beiden Wandlerstrukturen auf dem Halbleiterchip wird besonders vorteilhaft angewendet, indem der erste Spannungs-Strom-Wandler und der zweite Spannungs-Strom-Wandler gleiche Bauelemente aufweisen. Dies ermöglicht ein sehr ähnliches Verhalten der beiden Wandler auf physikalische Effekte, wie Temperaturänderungen oder mechanische Spannungen.

**[0018]** Eine bevorzugte und besonders einfache Ausgestaltung der Erfindung wird realisiert, indem zumindest einer der beiden Spannungs-Strom-Wandler einen Stromspiegel mit zumindest einem in Reihe geschalteten Widerstand auf-

## Ausführungsbeispiel

weist. Mit der Annahme im Wesentlichen linearer Widerstände kann demzufolge oberhalb einer oder mehrerer Thresholdspannungen des Stromspiegels ein im Wesentlichen lineares Verhalten des Spannungs-Strom-Wandler angenommen werden. Für Spannungen unterhalb der Thresholdspannung verbleibt der Spannungs-Strom-Wandler inaktiv, so dass nur ein sehr geringer Ruhestrom im inaktiven Zustand benötigt wird.

**[0019]** Bevorzugt ist in einer Ausgestaltungsvariante der Erfindung vorgesehen, dass zusätzlich zum Referenzstrom und zum Vergleichstrom Mittel zur Generierung eines, vorzugsweise vom Referenzstrom abhängigen Querstroms vorgesehen sind, wobei der Querstrom einmal negativ und einmal positiv in die Summation im Stromsummationsknoten eingeht.

**[0020]** Ändert sich die Vergleichsspannung im Bereich der Schwelle in einem Zeitbereich nur sehr langsam, ändert sich das Potential unter Umständen ebenfalls nur langsam zwischen dem binären Wert 0 und dem binären Wert 1. Vorzugsweise weist daher die Ausgangsstufe einen Schmitt-Trigger auf, dessen Eingang mit dem Stromsummationsknoten verbunden ist.

**[0021]** Die Erfindung weiterbildend ist vorteilhafterweise vorgesehen, dass der zweite Spannungs-Strom-Wandler zur Wandlung einer positiven und einer negativen Differenzspannung ausgebildet ist, wobei der zweite Spannungs-Strom-Wandler hierzu vorzugsweise einen ersten, der positiven Differenzspannung zugeordneten Stromspiegel und einen zweiten, der negativen Differenzspannung zugeordneten Stromspiegel aufweist.

**[0022]** Um in ein Strommanagement eines Kraftfahrzeugs auch den Komparator einzubeziehen, ist vorteilhafterweise ein Mittel zur Abschaltung der Versorgungsspannung der Ausgangsstufe vorgesehen, so dass der Spannungskomparator zwischen einem Schlafmodus und einem Betriebsmodus schaltbar ist.

**[0023]** Ein besonderer Aspekt der Erfindung ist eine Verwendung eines zuvor beschriebenen Spannungskomparators innerhalb einer Schaltung zur Auswertung und/oder Überwachung einer, mittels einer Ladeungspumpe generierten Spannung.

**[0024]** Ein weiterer Aspekt der Erfindung ist ein Analog-Digital-Umsetzer insbesondere nach dem Wägeverfahren oder nach dem Zählverfahren zur Umsetzung von einem zeitlichen Vergleichsspannungsverlauf in digitale Ausgangssignale mit einem zuvor beschriebenen Spannungskomparator.

**[0025]** Die Erfindung soll nachfolgend durch Ausführungsbeispiele im Zusammenhang mit zwei schematisierten Zeichnungen erläutert werden.

**[0026]** Im Einzelnen zeigt

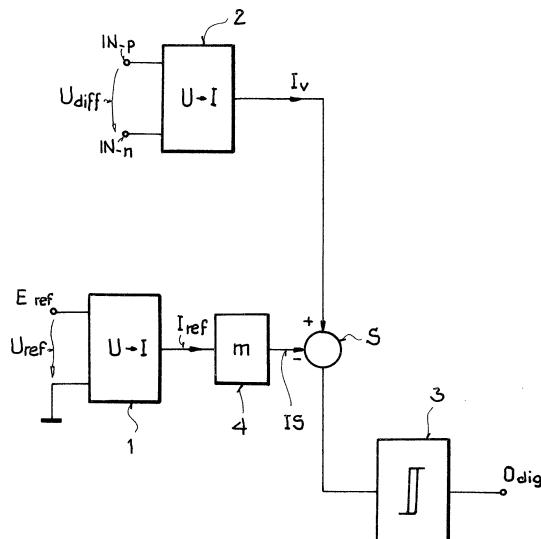

**[0027]** [Fig. 1](#) ein schematisches Blockschaltplan des Spannungskomparators; und

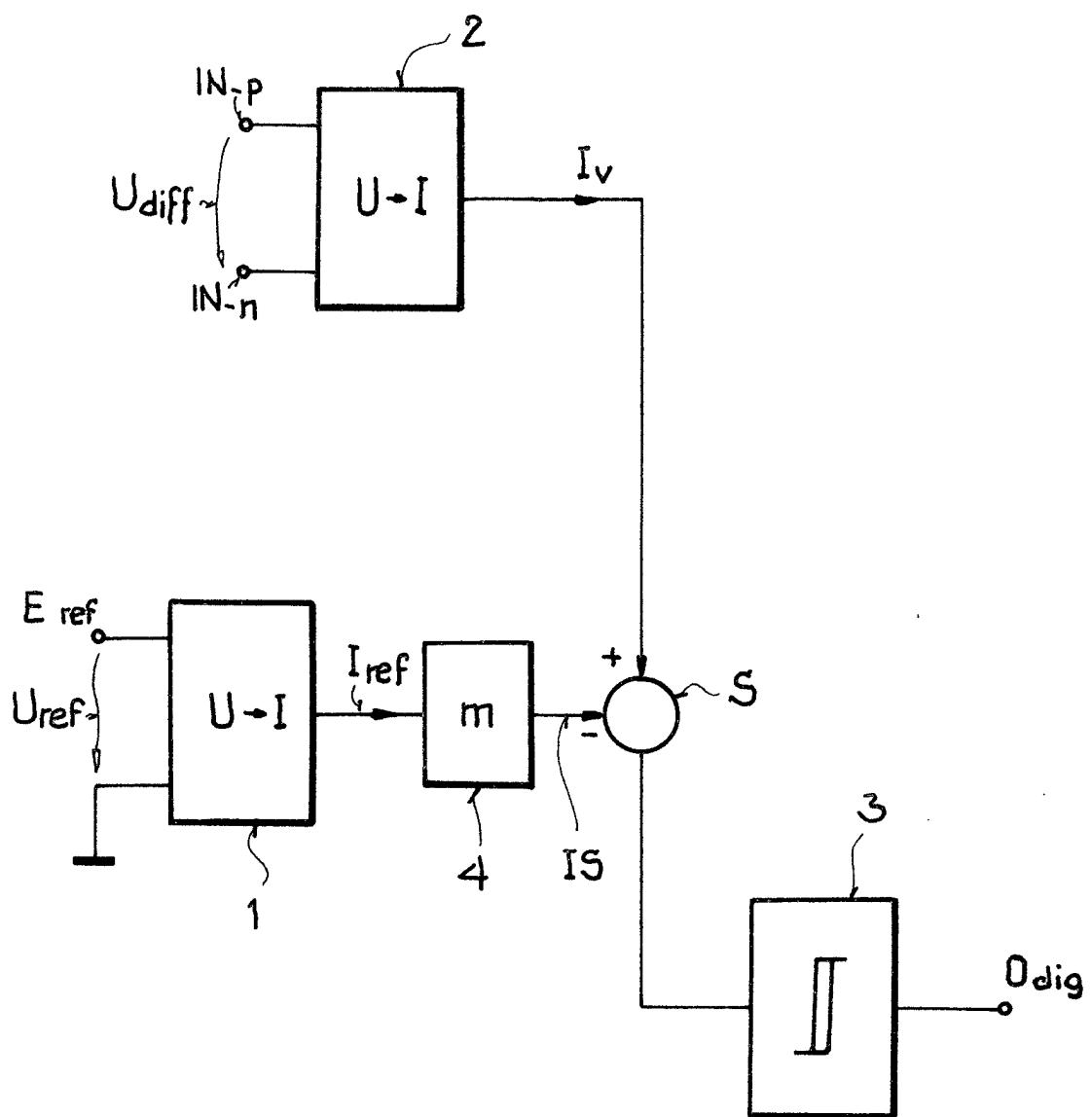

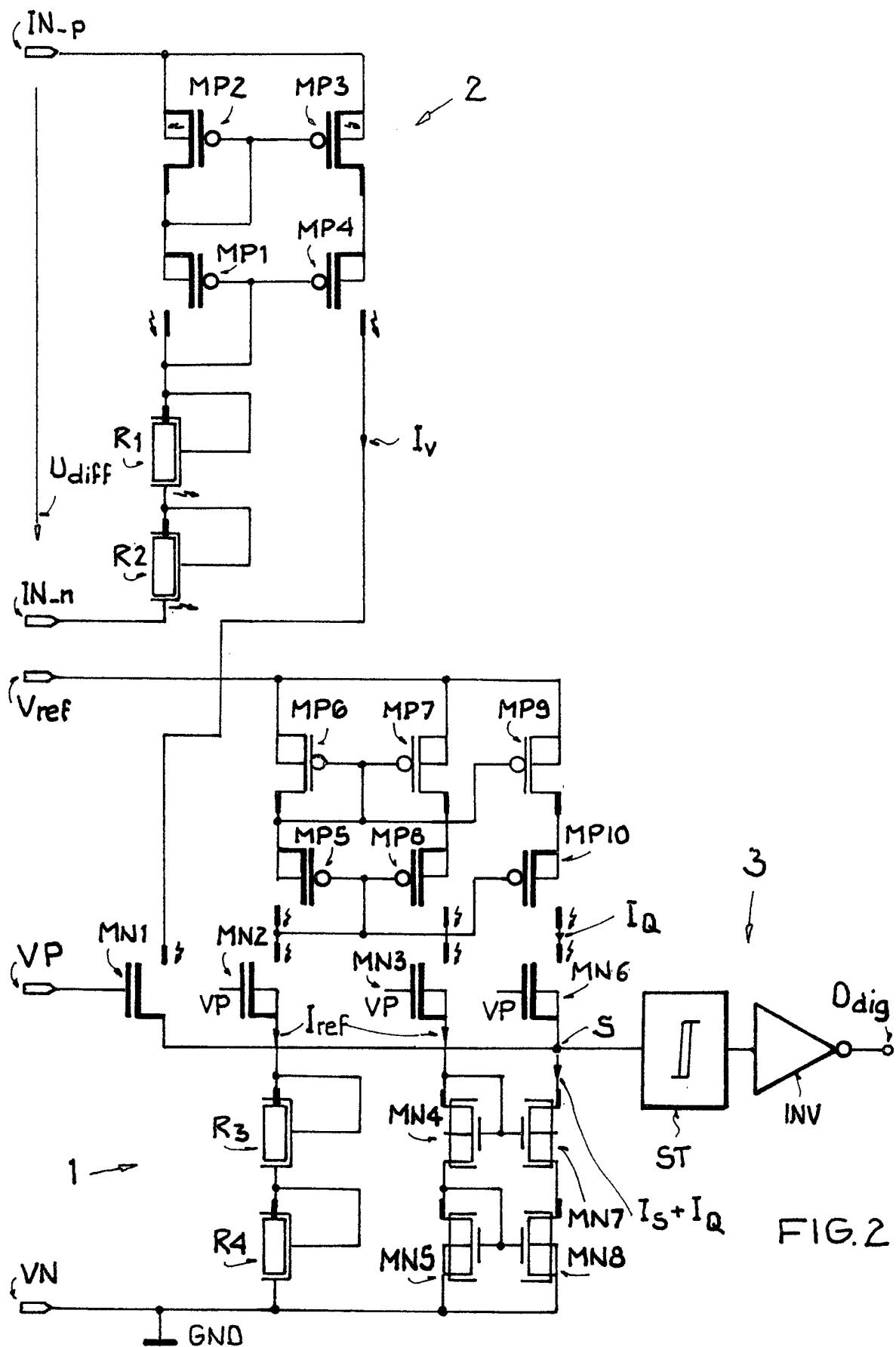

**[0028]** [Fig. 2](#) einen Schaltplan des Spannungskomparators auf Transistorlevel.

**[0029]** In [Fig. 1](#) ist ein Blockschaltplan eines Spannungskomparators dargestellt. Der Spannungskomparator weist einen ersten Spannungs-Strom-Wandler **1** auf, der eine Referenzspannung  $U_{ref}$  am Eingang  $E_{ref}$  in den Strom  $I_{ref}$  wandelt. In dem dargestellten Ausführungsbeispiel zeigt die Stromrichtung des Referenzstromes  $I_{ref}$  aus dem Spannungs-Strom-Wandler **1** heraus. Die Referenzspannung  $U_{ref}$  ist dabei auf den Masseanschluss bezogen.

**[0030]** Dem ersten Spannungs-Strom-Wandler **1** ist ein Multiplikator **4** nachgeschalten, der den Referenzstrom  $I_{ref}$  mit dem Multiplikationsfaktor  $m$  multipliziert. Der Multiplikationsfaktor  $m$  ist vorzugsweise von 0,5 bis 10 in Stufen einstellbar. Wiederum vom Referenzstrom  $I_{ref}$  abhängig ist der Schwellenstrom  $I_s$ . Die Abhängigkeit ist im dargestellten Ausführungsbeispiel der [Fig. 1](#) durch den Multiplikationsfaktor  $m$  gegeben, so dass unter Vernachlässigung des Einflusses durch einen Vergleichsstrom  $I_v$  gilt

$$I_s = m \cdot I_{ref}$$

**[0031]** Weiterhin ist ein zweiter Spannungs-Strom-Wandler **2** vorgesehen, der eine an den Eingängen  $IN_{-p}$  und  $IN_{-n}$  anliegende Differenzspannung  $U_{diff}$  in den Vergleichsstrom  $I_v$  wandelt. Der zweite Spannungs-Strom-Wandler **2** ist mit seinem Ausgang mit einem Stromsummationsknoten  $S$  verbunden. Ebenfalls ist der Multiplikator **4** mit dem Stromsummationsknoten  $S$  verbunden, wobei in diesem Ausführungsbeispiel der Vergleichsstrom  $I_v$  mit positiven Vorzeichen in den Stromsummationsknoten  $S$  hineinfließt, während der der Schwellenstrom  $I_s$  negativ in die Summation im Stromsummationsknoten  $S$  eingeht.

**[0032]** Weiterhin ist der Stromsummationsknoten  $S$  mit einer Ausgangsstufe **3** verbunden, deren Schmitt-Trigger-Eingang hochohmig ist, so dass der in die Ausgangsstufe **3** fließende Strom vernachlässigt werden kann. Da die Summe aller Ströme, die in den Stromsummationsknoten  $S$  hineinbeziehungsweise herausfließen gleich Null sein muss, ist in dem schematisch dargestellten Ausführungsbeispiel der Schwellenstrom  $I_s$  gleich dem Vergleichsstrom  $I_v$ .

**[0033]** Für einen niedrigen Vergleichsstrom  $I_v$  wird der Stromfluss durch den Stromsummationsknoten S durch den Vergleichstrom  $I_v$  bestimmt. Der erste Multiplikator **4** wirkt daher als Stromsenke, die jedoch einen größeren Strom aufnehmen kann als durch den Vergleichsstrom  $I_v$  zufließt. Demzufolge ist in diesem Zustand die Spannung vom Stromsummationsknoten S gegenüber Masse gering und unterhalb der Schwellen des Schmitt-Triggers der Ausgangsstufe **3**. Steigt der Vergleichsstrom  $I_v$  weiter an, gelang dieser in jene Größenordnung, die durch den als Stromsenke wirkenden Multiplikator **4** aufgenommen werden kann. Mit Erreichen dieser Schwelle ist der Strom auf einen von der Referenzspannung  $U_{ref}$  abhängigen Wert des Schwellenstromes  $I_s$  begrenzt.

**[0034]** Wird die Differenzspannung  $U_{diff}$  weiter erhöht, verbleibt der durch den Stromsummationsknoten S fließende Strom im wesentlichen konstant. Dadurch, dass der zweite Spannungs-Strom-Wandler **2** als Stromquelle mit einem Innenwiderstand wirkt, steigt die Spannung im Stromsummationsknoten S signifikant an und überschreitet die Schwellen des Schmitt-Triggers der Ausgangsstufe **3**. Um den Spannungskomparator für hohe Bordnetzspannungen eines Kraftfahrzeugs zu nutzen, weist der zweite Spannungs-Strom-Wandler **2** eine hohe Durchbruchsspannungsfestigkeit auf, die vorzugsweise bei 80 V oder höher liegt.

**[0035]** Dieser zweite Spannungs-Strom-Wandler **2** ist demzufolge vorteilhafterweise derart hochspannungsfest ausgebildet, dass dieser eine Durchbruchsspannungsfestigkeit aufweist, die signifikant über den Spannungswerten der Versorgungsspannung VP der Ausgangsstufe **3** oder der maximalen Referenzspannung  $U_{ref}$  liegt und an eine, an den zwei Eingängen  $IN_{-p}$  und  $IN_{-n}$  anlegbare maximale Gleichtakteingangsspannung angepasst ist.

**[0036]** Die Ausgangssignale der Ausgangsstufe **3** sind binäre, digitale Rechtecksignale mit den Zuständen "high" und "low", wobei in dem Ausführungsbeispiel der [Fig. 1](#) eine Differenzspannung  $U_{diff}$  oberhalb der von der Referenzspannung  $U_{ref}$  abhängigen Schwelle des Spannungskomparators ein "high"-Signal und einer Differenzspannung  $U_{diff}$  unterhalb der von der Referenzspannung  $U_{ref}$  abhängigen Schwelle des Komparators ein "low"-Signal zugeordnet ist.

**[0037]** Die Ausgangsstufe **3** des Komparators ist so ausgelegt, dass sie mit den Logikpegeln vorzugsweise mehrerer Schaltkreisfamilien kompatibel ist. Das bedeutet, dass digitale Schaltkreise ohne Zwischen-schalten weiterer Elemente vom Komparatorausgang ansteuerbar sind. Abweichend von der Darstellung der [Fig. 1](#) ist der Komparatorausgang vorteilhaftweise mittels eines Strobe-Anschlusses abschaltbar. Bei abgeschaltetem Ausgang ist der Ausgang hochohmig. Das hat insbesondere den Vorteil, dass

mehrere Komparatoren sich auf eine gemeinsame Bus-Leitung schalten lassen. Hierbei wird stets nur ein Ausgang aktiviert, die übrigen sind hochohmig und beeinflussen den Ausgang des angeschlossenen aktiven Komparators nicht.

**[0038]** Die [Fig. 2](#) zeigt ein Ausführungsbeispiel der Erfindung auf Transistor-Level. Der erste Strom-Spannungs-Wandler **1** und der zweite Strom-Spannungs-Wandler **2** weisen jeweils zwei Widerstände R3, R4 und R1, R2 auf, die mit einem Stromspiegel, bestehend aus den PMOS-Transistoren MP5 bis MP8 beziehungsweise MP1 bis MP4, in Reihe geschalten sind. Übersteigt die Differenzspannung  $U_{diff}$  beziehungsweise die Referenzspannung  $U_{ref}$  die zweifache Threshold-Spannung, beginnt ein Strom durch die PMOS-Transistoren MP5 bis MP8 beziehungsweise MP1 bis MP4 und durch die Widerstände R3, R4 beziehungsweise R1, R2 zu fließen. Dieser Strom wird mittels der jeweiligen Stromspiegel gespiegelt. Zudem weist die Schaltung der [Fig. 2](#) einen schaltbaren Stromspiegel aus NMOS-Transistoren MN4, MN5, MN7, MN8 auf. Mittels in [Fig. 2](#) nicht dargestellter Schalttransistoren kann das Spiegelverhältnis des schaltbaren Stromspiegels verändert werden.

**[0039]** Die PMOS-Transistoren MP5 bis MP8 und die Widerstände R3, R4 des ersten Spannungs-Strom-Wandlers **1** und die PMOS-Transistoren MP1 bis MP4 und die Widerstände R1, R2 des zweiten Spannungs-Strom-Wandlers **2** stimmen dabei im wesentlichen überein. Die entsprechenden PMOS-Transistoren MP1 zu MP5 usw. weisen hierzu dasselbe Aspektverhältnis auf. Ebenfalls sind die Widerstände R1 bis R4 durch denselben Technologie-schritt entstanden. Weiterhin ist es besonders vorteilhaft ein gutes, so genanntes "matching" zu erreichen, indem diese PMOS-Transistoren MP1 bis MP8 und Widerstände R1 bis R4 zueinander benachbart angeordnet oder in einander verschachtelt angeordnet sind. Dies bewirkt, dass diese Schaltungsteile im wesentlichen dasselbe Verhalten für unterschiedliche Betriebstemperaturen aufweisen.

**[0040]** Um eine Einsatzmöglichkeit für ein 42V Bordnetz eines Kraftfahrzeugs zu erhalten sind zumindest die PMOS-Transistoren MP1 bis MP4 als Hochvolt-PMOS-Transistoren mit einer Durchbruchsspannungsfestigkeit von 80V ausgelegt. Die Ausgangsstufe **3** weist einen Schmitt-Trigger ST und einen, mit dem Ausgang  $O_{dig}$  des Spannungskomparators verbundenen Inverter INV auf. Der eine Versorgungsspannungsanschluss VN liegt auf Masse GND, während der andere Versorgungsspannungsanschluss VP auf einem Versorgungsspannungspotential von 5 V liegt, mit dem auch nachfolgende, in [Fig. 2](#) nicht dargestellte digitale Schaltkreise versorgt werden. Die maximale Durchbruchsspannungsfestigkeit des Schmitt-Triggers ST ist in Bezug auf die Ver-

sorgungsspannung VP von 5V ausgelegt, und erreicht beispielsweise Werte zwischen 8V und 10V.

**[0041]** Versucht der zweite Spannungs-Strom-Wandler **2** einen großen Strom  $I_v$  zu treiben, würden die über 10V hinausgehenden Spannungen die Eingangstransistoren des Schmitt-Triggers ST zerstören. Um die im Stromsummationsknoten S auftretende Spannung zu begrenzen ist der NMOS-Transistor MN1 vorgesehen, der eine Durchbruchsspannungsfestigkeit aufweist, die zumindest der eines der Transistoren MP1 bis MP4 entspricht. Da dieser NMOS Transistor MN1 als Source-Folger geschalten ist, beträgt das maximale Potential am Source-Anschluss das Versorgungsspannungspotential VP weniger der Thresholdspannung des Transistors MN1, sofern ein Strom von der Drain zur Source fließt. Übersteigt die Referenzspannung  $U_{ref}$  ebenfalls die Versorgungsspannung VP signifikant, können, wie in [Fig. 2](#) dargestellt, weitere NMOS-Transistoren MN2, MN3 oder MN6 als Begrenzungsmittel vorgesehen sein. Weiterhin können die Transistoren MN1, MN2, MN3 oder MN6 auch dazu dienen die Ströme  $I_v$ ,  $I_{ref}$ ,  $I_Q$  zuzuschalten oder abzuschalten.

**[0042]** Die Referenzspannung  $U_{ref}$  wird in diesem Ausführungsbeispiel von Außen an den Spannungskomparator angelegt. Vorzugsweise sind die Bauelemente des Spannungskomparators auf einem Halbleiterchip integriert, wobei die Referenzspannung  $U_{ref}$  an einen Anschluss des Halbleiterchips anschließbar ist. Alternativ ist es natürlich auch möglich die Referenzspannung  $U_{ref}$  innerhalb des Spannungskomparators zu generieren.

**[0043]** Neben dem Vergleichsstrom  $I_v$  und dem Schwellenstrom  $I_s$  geht ein weiterer Strom  $I_Q$  in die Summation im Stromsummationsknoten S ein. Dieser Strom kann als Querstrom  $I_Q$  bezeichnet werden, der sowohl positiv als auch negativ in die Stromsummation im Stromsummationsknoten S eingeht und damit durch den Stromsummationsknoten S lediglich hindurch fließt. In dem Ausführungsbeispiel der [Fig. 2](#) ist der Querstrom  $I_Q$  vom Referenzstrom  $I_{ref}$  gespiegelt.

#### Bezugszeichenliste

|                    |                              |

|--------------------|------------------------------|

| <b>1, 2</b>        | Spannungs-Strom-Wandler      |

| <b>3</b>           | Ausgangsstufe                |

| <b>4</b>           | Multiplikator                |

| $U_{dif}$          | Differenzspannung            |

| $IN_{-p}, IN_{-n}$ | Komparatoreingänge           |

| $U_{ref}$          | Referenzspannung             |

| $E_{ref}$          | Eingang der Referenzspannung |

| $I_v$              | Vergleichsstrom              |

| $I_{ref}$          | Referenzstrom                |

| $I_s$              | Schwellenstrom               |

| <b>S</b>           | Stromsummationsknoten        |

|                     |                                  |

|---------------------|----------------------------------|

| $O_{dig}$           | Komparatorausgang                |

| <b>VP</b>           | Versorgungsspannungsanschluss 5V |

| <b>VN, GND</b>      | Masse                            |

| <b>MP1 bis MP10</b> | PMOS-Transistor                  |

| <b>MN1 bis MN8</b>  | NMOS-Transistor                  |

| <b>R1 bis R4</b>    | Widerstand                       |

| $I_Q$               | Querstrom                        |

| <b>ST</b>           | Schmitt-Trigger                  |

| <b>INV</b>          | Inverter                         |

#### Patentansprüche

1. Spannungskomparator zum Vergleich einer Vergleichsspannung ( $U_{diff}$ ) mit einer Schwelle, mit – einem ersten Spannungs-Strom-Wandler **(1)** zur Wandlung einer die Schwelle bestimmenden Referenzspannung ( $U_{ref}$ ) in einen von der Referenzspannung ( $U_{ref}$ ) abhängigen Referenzstrom ( $I_{ref}$ ) – einem zweiten Spannungs-Strom-Wandler **(2)** zur Wandlung der Vergleichsspannung ( $U_{diff}$ ) in einen von der Vergleichsspannung ( $U_{diff}$ ) abhängigen Vergleichsstrom ( $I_v$ ), – zwei Eingängen ( $IN_{-p}, IN_{-n}$ ), an denen die Vergleichsspannung als Differenzspannung ( $U_{diff}$ ) anliegt, und – einer Ausgangsstufe **(3)** zur Ausgabe eines digitalen Ausgangspegels, wobei der Ausgangspegel von dem Referenzstrom ( $I_{ref}$ ) und dem Vergleichsstrom ( $I_v$ ) abhängig ist.

2. Spannungskomparator nach Anspruch 1, dadurch gekennzeichnet, dass die Ausgangsstufe **(3)** mit einem Stromsummationsknoten (S) verbunden ist, in dem sich der Vergleichsstrom ( $I_v$ ) und ein von dem Referenzstrom ( $I_{ref}$ ) abhängiger Schwellenstrom ( $I_s$ ) summieren, wobei einer der beiden Ströme ( $I_s, I_v$ ) als negativer Wert in die Summation eingeht.

3. Spannungskomparator nach Anspruch 2, gekennzeichnet durch Mittel zur Multiplikation des Referenzstromes ( $I_{ref}$ ) mit einem Multiplikationsfaktor (m), so dass der in die Summation im Stromsummationsknoten (S) eingehende Schwellenstrom ( $I_s$ ) von dem Multiplikationsfaktor (m) und von dem Referenzstrom ( $I_{ref}$ ) abhängig ist.

4. Spannungskomparator nach Anspruch 3, gekennzeichnet durch einen Referenzstromspiegel (MN4, MN5, MN7, MN8), dessen Stromspiegelverhältnis als Mittel zur Multiplikation einstellbar, insbesondere schaltbar ist.

5. Spannungskomparator nach einem der Ansprüche 2 bis 4, dadurch gekennzeichnet, dass der Ausgangspegel durch ein Potential im Stromsummationsknoten (S) bestimmt ist, das von dem Vergleichsstrom ( $I_v$ ) und dem Schwellenstrom ( $I_s$ ) abhängig ist.

6. Spannungskomparator nach einem der vorhergehenden Ansprüche, gekennzeichnet durch ein Spannungsbegrenzungsmittel (MN1, MN6) zur Begrenzung der zwischen dem Stromsummationsknoten (S) und dem Masseanschluss (GND, VN) der Ausgangsstufe (3) liegenden Spannung.

7. Spannungskomparator nach Anspruch 6, dadurch gekennzeichnet, dass der Stromsummationsknoten (S) über zumindest einen ersten Transistor (MN6) mit einem mit dem ersten Spannungs-Strom-Wandler (1) verbundenen Stromspiegel verbunden ist, wobei der erste, als Spannungsbegrenzungsmittel wirkende Transistor (MN6) gegenüber der Ausgangsstufe (3) eine höhere Durchbruchsspannungsfestigkeit aufweist.

8. Spannungskomparator nach Anspruch 7, dadurch gekennzeichnet, dass das Gate beziehungsweise die Basis des ersten Transistors (MN6) mit der Versorgungsspannung (VP) der Ausgangsstufe (3) verbunden oder verbindbar ist.

9. Spannungskomparator nach einem der Ansprüche 6 bis 8, dadurch gekennzeichnet, dass der Stromsummationsknoten (S) über einen zweiten Transistor (MN1) mit dem zweiten Spannungs-Strom-Wandler (2) verbunden ist, wobei der zweite, als Spannungsbegrenzungsmittel wirkende Transistor (MN1) gegenüber der Ausgangsstufe (3) eine höhere Durchbruchsspannungsfestigkeit aufweist.

10. Spannungskomparator nach Anspruch 9, dadurch gekennzeichnet, dass das Gate beziehungsweise die Basis des zweiten Transistors (MN1) mit der Versorgungsspannung (VP) der Ausgangsstufe (3) verbunden oder verbindbar ist.

11. Spannungskomparator nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass der erste Spannungs-Strom-Wandler (1) und der zweite Spannungs-Strom-Wandler (2) auf einem Halbleiterchip zueinander benachbart oder ineinander gesetzt angeordnet sind.

12. Spannungskomparator nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass der erste Spannungs-Strom-Wandler (1) und der zweite Spannungs-Strom-Wandler (2) gleiche Bauelemente aufweisen.

13. Spannungskomparator nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass der erste Spannungs-Strom-Wandler (1) einen Stromspiegel mit zumindest einem in Reihe geschalteten Widerstand (R3, R4) aufweist, und/oder der zweite Spannungs-Strom-Wandler (2) einen Stromspiegel mit zumindest einem in Reihe geschalteten Widerstand (R1, R2) aufweist.

14. Spannungskomparator nach einem der vorhergehenden Ansprüche, gekennzeichnet durch Mittel zur Generierung eines, vorzugsweise vom Referenzstrom ( $I_{ref}$ ) abhängigen Querstroms ( $I_Q$ ), wobei der Querstrom ( $I_Q$ ) einmal negativ und einmal positiv in die Summation im Stromsummationsknoten (S) (zusätzlich zum Referenzstrom und zum Vergleichstrom) eingeht.

15. Spannungskomparator nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass die Ausgangsstufe (3) einen Schmitt-Trigger (ST) aufweist, dessen Eingang mit dem Stromsummationsknoten (S) verbunden ist.

16. Spannungskomparator nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass die Bauelemente des Spannungskomparators auf einem Halbleiterchip integriert sind, wobei die Referenzspannung ( $U_{ref}$ ) an einen Anschluss des Halbleiterchips anschließbar ist.

17. Spannungskomparator nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass der zweite Spannungs-Strom-Wandler zur Wandlung einer positiven und einer negativen Differenzspannung ausgebildet ist, wobei der zweite Spannungs-Strom-Wandler hierzu vorzugsweise einen ersten, der positiven Differenzspannung zugeordneten Stromspiegel und einen zweiten, der negativen Differenzspannung zugeordneten Stromspiegel aufweist.

18. Spannungskomparator nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass der zweite Spannungs-Strom-Wandler (2) hochspannungsfest ausgebildet ist, indem dieser eine Durchbruchsspannungsfestigkeit aufweist, die signifikant über den Spannungswerten der Versorgungsspannung (VP) der Ausgangsstufe (3) oder der maximalen Referenzspannung ( $U_{ref}$ ) liegt und an eine, an den zwei Eingängen ( $IN_{-n}$ ,  $IN_{-p}$ ) anlegbare maximale Gleichtakteingangsspannung angepasst ist.

19. Spannungskomparator nach einem der vorhergehenden Ansprüche, gekennzeichnet durch Mittel zur Abschaltung der Versorgungsspannung (VP) der Ausgangsstufe (3), so dass der Spannungskomparator zwischen einem Schlafmodus und einem Betriebsmodus schaltbar ist.

20. Verwendung eines Spannungskomparators nach einem der vorhergehenden Ansprüche innerhalb einer Schaltung zur Auswertung und/oder Überwachung einer mittels einer Ladungspumpe generierten Spannung.

21. Analog-Digital-Umsetzer insbesondere nach dem Wägeverfahren oder nach dem Zählverfahren zur Umsetzung von einem zeitlichen Vergleichsspan-

nungsverlauf in digitale Ausgangssignale mit einem

Spannungskomparator nach einem der Ansprüche 1

bis 19.

Es folgen 2 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG.1

FIG.2