(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2022-74445

(P2022-74445A)

(43)公開日 令和4年5月18日(2022.5.18)

## (51)国際特許分類

|        |                 |        |        |

|--------|-----------------|--------|--------|

| H 03 M | 1/56 (2006.01)  | H 03 M | 1/56   |

| H 04 N | 5/378(2011.01)  | H 04 N | 5/378  |

| H 04 N | 5/374(2011.01)  | H 04 N | 5/374  |

| H 04 N | 5/3745(2011.01) | H 04 N | 5/3745 |

## テーマコード(参考)

|           |

|-----------|

| 5 C 0 2 4 |

| 5 J 0 2 2 |

審査請求 未請求 請求項の数 20 O L (全22頁)

|          |                             |         |                                            |

|----------|-----------------------------|---------|--------------------------------------------|

| (21)出願番号 | 特願2020-184492(P2020-184492) | (71)出願人 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22)出願日  | 令和2年11月4日(2020.11.4)        | (74)代理人 | 100126240<br>弁理士 阿部 琢磨                     |

|          |                             | (74)代理人 | 100124442<br>弁理士 黒岩 創吾                     |

|          |                             | (72)発明者 | 中村 恒一<br>東京都大田区下丸子3丁目30番2号                 |

|          |                             | (72)発明者 | キヤノン株式会社内<br>亀山 弘明                         |

|          |                             | (72)発明者 | 東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内             |

|          |                             | (72)発明者 | 岩田 公一郎<br>東京都大田区下丸子3丁目30番2号                |

|          |                             |         | 最終頁に続く                                     |

(54)【発明の名称】 アナログデジタル変換回路、光電変換装置、光電変換システム

## (57)【要約】 (修正有)

【課題】画素列毎にアナログデジタル変換部を持つ光電変換装置で、カウンタ回路の消費電力を低減する。

【解決手段】光電変換装置において、アナログデジタル変換回路は、アナログ信号とランプ信号とを比較処理する比較回路3と、比較回路での比較処理に並行してカウント処理を行うカウンタ部7、とを有する。アナログデジタル変換期間は、1つのアナログ信号のアナログデジタル変換の開始から終了までの期間に第1の期間および第1の期間の後の第2の期間が含まれ、第1の期間ではカウント処理が高速に実行され、第2の期間ではカウント処理が低速に実行される。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

アナログ信号とランプ信号とを比較処理する比較回路と、

前記比較回路での前記比較処理に並行してカウント処理を行うカウンタ部と、を有し、

前記比較処理に応じたカウント値であるデジタルデータを取得することによって前記アナログ信号のアナログデジタル変換を行うアナログデジタル変換回路であって、

1つの前記アナログ信号のアナログデジタル変換の開始から終了までの期間に第1の期間および前記第1の期間の後の第2の期間が含まれ、前記第1の期間では前記カウント処理が高速に実行され、前記第2の期間では前記カウント処理が低速に実行されることを特徴とするアナログデジタル変換回路。

10

**【請求項 2】**

アナログ信号とランプ信号とを比較処理する比較回路と、

前記比較回路での前記比較処理に並行してカウント処理を行うカウンタ部と、を有し、

前記比較処理に応じたカウント値であるデジタルデータを取得することによって前記アナログ信号のアナログデジタル変換を行うアナログデジタル変換回路であって、

1つの前記アナログ信号のアナログデジタル変換の開始から終了までの期間に第1の期間および前記第1の期間の後の第2の期間が含まれ、

前記第1の期間では、第一の分解能で前記アナログデジタル変換回路が前記アナログデジタル変換を行い、

前記第2の期間では、前記第一の分解能よりも低い第二の分解能で前記アナログデジタル変換回路が前記アナログデジタル変換を行うことを特徴とするアナログデジタル変換回路。

20

**【請求項 3】**

アナログ信号と、ランプ信号とを比較処理する比較回路と、複数ビットを有するカウント値を出力するカウンタ部を含み、

前記カウンタ部は前記比較回路での前記比較処理に並行してカウント処理を行うことによって前記カウント値を出力し、

前記比較処理に応じたカウント値であるデジタルデータを取得してアナログデジタル変換を行うアナログデジタル変換回路であって、

1つの前記アナログ信号のアナログデジタル変換の開始から終了までの期間に第1の期間および前記第1の期間の後の第2の期間が含まれ、

前記第1の期間において信号が変化する、前記複数ビットの最下位ビット側から少なくとも1ビットが、前記第2の期間においては所定の電位に固定されることを特徴とするアナログデジタル変換回路。

30

**【請求項 4】**

アナログ信号と、ランプ信号とを比較処理する比較回路と、カウンタ部を有し、

前記カウンタ部は前記比較回路での前記比較処理に並行してカウント処理を行い、

前記比較処理に応じたカウント値であるデジタルデータを取得してアナログデジタル変換を行うアナログデジタル変換回路であって、

1つの前記アナログ信号のアナログデジタル変換の開始から終了までの期間に第1の期間および前記第1の期間の後の第2の期間が含まれ、

前記第2の期間における前記カウンタ部の動作周波数が前記第1の期間における前記カウンタ部の動作周波数よりも小さいことを特徴とするアナログデジタル変換回路。

40

**【請求項 5】**

前記カウンタ部には周波数の異なる複数のクロックが入力されることを特徴とする請求項1乃至請求項4のいずれか1項に記載のアナログデジタル変換回路。

**【請求項 6】**

前記カウンタ部の最上位ビットの出力を反転させるインバータ回路と、

前記カウンタ部の最下位ビットの出力と、前記インバータ回路を介した前記最上位ビットの出力とが入力される論理回路とを含むゲーティング部を有することを特徴とする、請求

50

項 1 乃至 請求項 5 のいずれか一項に記載のアナログデジタル変換回路。

【請求項 7】

周波数の異なる複数のクロックが入力され、前記カウンタ部の出力によって制御されるマルチプレクサであって、

前記カウンタ部の最上位ビットの出力が H i g h のときに出力されるクロックの周波数と、

前記カウンタ部の最上位ビットの出力が L o w のときに出力されるクロックの周波数と、が異なるマルチプレクサを含むゲーティング部を有することを特徴とする、請求項 1 乃至 請求項 5 のいずれか一項に記載のアナログデジタル変換回路。

【請求項 8】

前記第 1 の期間は、前記カウンタ部によって計測されることを特徴とする請求項 1 乃至 請求項 7 のいずれか一項に記載のアナログデジタル変換回路。

【請求項 9】

複数の画素と、請求項 1 乃至 請求項 8 のいずれか一項に記載のアナログデジタル変換回路と、を有し、

前記アナログ信号は前記画素で生じる電荷に基づく信号であることを特徴とする光電変換装置。

【請求項 10】

前記複数の画素はアレイ状に配置され、該アレイの列はそれぞれ列メモリに接続され、

前記カウンタ部は複数の前記列メモリにカウント値を供給する共通カウンタを含むことを特徴とする請求項 9 記載の光電変換装置。

【請求項 11】

前記カウンタ部は前記アレイが列ごとに接続される列カウンタを含むことを特徴とする請求項 10 記載の光電変換装置。

【請求項 12】

前記カウント値は複数ビットを有し、

前記共通カウンタは前記カウント値のうち下位ビットの値を生成し、

前記列カウンタは前記カウント値のうち上位ビットの値を生成することを特徴とする請求項 11 記載の光電変換装置。

【請求項 13】

前記光電変換装置は第一の画素群と第二の画素群とを有し、

前記第一の画素群は前記複数の画素を含み、

前記第二の画素群は前記複数の画素とは異なる画素を含み、

前記第二の画素群に含まれる前記画素で生じる電荷に基づくアナログ信号は、第三の分解能でデジタルデータに変換されることを特徴とする、請求項 9 乃至 請求項 12 のいずれか 1 項に記載の光電変換装置。

【請求項 14】

前記第二の画素群に含まれる画素は焦点距離検出用の画素であることを特徴とする請求項 13 記載の光電変換装置。

【請求項 15】

前記光電変換装置は複数の撮影モードで動作し、

請求項 9 乃至 請求項 14 のいずれか一項に記載の光電変換装置として動作する撮影モードを有することを特徴とする光電変換装置。

【請求項 16】

前記複数の画素は半導体基板に形成され、

前記半導体基板を含む複数の半導体基板を積層して構成されることを特徴とする請求項 9 乃至 請求項 15 のいずれか一項に記載の光電変換装置。

【請求項 17】

請求項 9 乃至 請求項 16 のいずれか 1 項に記載の光電変換装置と、

前記光電変換装置が出力する信号を用いて画像を生成する信号処理部とを有することを特

10

20

30

40

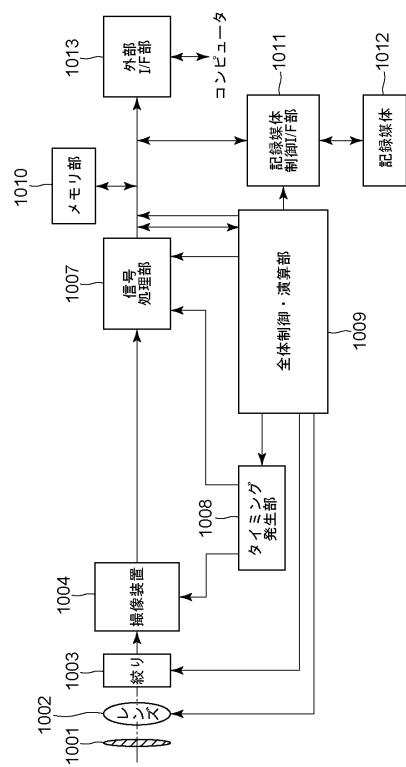

50

徴とする光電変換システム。

【請求項 18】

請求項 9 乃至請求項 16 のいずれか 1 項に記載の光電変換装置を備える移動体であって、前記光電変換装置が出力する信号を用いて前記移動体の移動を制御する制御部を有することを特徴とする移動体。

【請求項 19】

他の半導体基板に積層するための半導体基板であって、

アナログ信号と、ランプ信号とを比較処理する比較回路と、

前記比較回路での前記比較処理に並行してカウント処理を行うカウンタ部と、を有し、

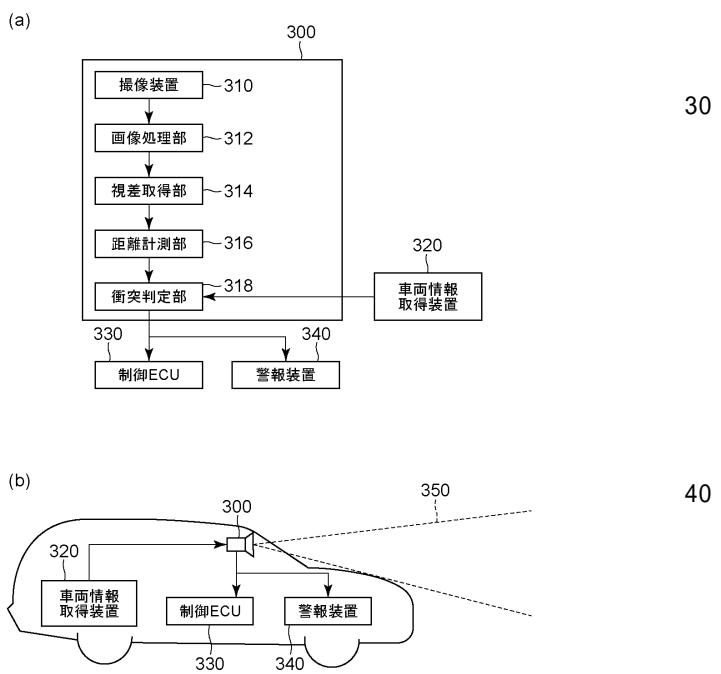

前記比較処理に応じたカウント値を保持することでデジタルデータを取得することによって前記アナログ信号のアナログデジタル変換を行うアナログデジタル変換回路を有し、

前記アナログ信号のアナログデジタル変換の開始から終了までの期間に第 1 の期間および前記第 1 の期間の後の第 2 の期間が含まれ、前記第 1 の期間では前記カウント処理が高速に実行され、前記第 2 の期間では前記カウント処理が低速に実行されることを特徴とする半導体基板。

10

【請求項 20】

他の半導体基板に積層するための半導体基板であって、

アナログ信号と、ランプ信号とを比較処理する比較回路と、

前記比較回路での前記比較処理に並行してカウント処理を行うカウンタ部と、を有し、

前記比較処理に応じたカウント値を保持することでデジタルデータを取得することによって前記アナログ信号のアナログデジタル変換を行うアナログデジタル変換回路を有し、

1 つの前記アナログ信号のアナログデジタル変換の開始から終了までの期間に第 1 の期間および前記第 1 の期間の後の第 2 の期間が含まれ、

前記第 1 の期間では、前記アナログデジタル変換回路が第一の分解能で前記アナログデジタル変換を行い、

前記第 2 の期間では、前記第一の分解能よりも低い第二の分解能として前記アナログデジタル変換回路が前記アナログデジタル変換を行うことを特徴とする半導体基板。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、アナログデジタル変換回路、この回路を備えた光電変換装置、この光電変換装置を備えた撮像システムに関する。

30

【背景技術】

【0002】

光電変換装置において、アレイ状に配置された画素の列ごとにアナログデジタル変換（以下、A D 変換）部を配置して、各画素で生じた電荷に基づく画素信号をデジタルデータに変換する技術がある。特許文献 1 の A D 変換部は、時間の経過とともに電位が変化する参照信号の電位と、画素信号の電位との大小関係を比較し、A D 変換開始から参照信号と画素信号の電位の大小関係が反転するまでの時間を計測することで A D 変換を実現している。特許文献 1 では、時間を計測する手段として、列ごとに列メモリを設け、複数列の列メモリに共通に接続される共通カウンタを用いて、参照信号と画素信号の電位の大小関係の反転に応じたカウント値を各列で列メモリに記憶する。

40

【先行技術文献】

【特許文献】

【0003】

【特許文献 1】特開 2013-093837 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献 1 に記載の光電変換装置では、カウンタ回路の動作が入射光の輝度によらず一定

50

であるため、カウンタ回路の消費電力が大きくなるという課題があった。

【0005】

本発明は上記課題を鑑みてなされたものであり、カウンタ回路の消費電力低減を実現することを目的とする。

【課題を解決するための手段】

【0006】

本発明の一つの側面は、アナログ信号とランプ信号とを比較処理する比較回路と、前記比較回路での前記比較処理に並行してカウント処理を行うカウンタ部と、を有し、前記比較処理に応じたカウント値であるデジタルデータを取得することによって前記アナログ信号のアナログデジタル変換を行うアナログデジタル変換回路であって、1つの前記アナログ信号のアナログデジタル変換の開始から終了までの期間に第1の期間および前記第1の期間の後の第2の期間が含まれ、前記第1の期間では前記カウント処理が高速に実行され、前記第2の期間では前記カウント処理が低速に実行されることを特徴とする。

10

【0007】

本発明の別の側面は、アナログ信号とランプ信号とを比較処理する比較回路と、前記比較回路での前記比較処理に並行してカウント処理を行うカウンタ部と、を有し、前記比較処理に応じたカウント値であるデジタルデータを取得することによって前記アナログ信号のアナログデジタル変換を行うアナログデジタル変換回路であって、1つの前記アナログ信号のアナログデジタル変換の開始から終了までの期間に第1の期間および前記第1の期間の後の第2の期間が含まれ、前記第1の期間では、第一の分解能で前記アナログデジタル変換回路が前記アナログデジタル変換を行い、前記第2の期間では、前記第一の分解能よりも低い第二の分解能で前記アナログデジタル変換回路が前記アナログデジタル変換を行うことを特徴とする。

20

【0008】

本発明の更に別の側面は、アナログ信号と、ランプ信号とを比較処理する比較回路と、複数ビットを有するカウント値を出力するカウンタ部を含み、前記カウンタ部は前記比較回路での前記比較処理に並行してカウント処理を行うことによって前記カウント値を出力し、前記比較処理に応じたカウント値であるデジタルデータを取得してアナログデジタル変換を行うアナログデジタル変換回路であって、1つの前記アナログ信号のアナログデジタル変換の開始から終了までの期間に第1の期間および前記第1の期間の後の第2の期間が含まれ、前記第1の期間において信号が変化する、前記複数ビットの最下位ビット側から少なくとも1ビットが、前記第2の期間においては所定の電位に固定されることを特徴とする。

30

【0009】

本発明の更に別の側面は、アナログ信号と、ランプ信号とを比較処理する比較回路と、カウンタ部を有し、前記カウンタ部は前記比較回路での前記比較処理に並行してカウント処理を行い、前記比較処理に応じたカウント値であるデジタルデータを取得してアナログデジタル変換を行うアナログデジタル変換回路であって、1つの前記アナログ信号のアナログデジタル変換の開始から終了までの期間に第1の期間および前記第1の期間の後の第2の期間が含まれ、前記第2の期間における前記カウンタ部の動作周波数が前記第1の期間における前記カウンタ部の動作周波数よりも小さいことを特徴とする。

40

【発明の効果】

【0010】

本発明によれば、入射する光の輝度に応じてA/D変換の分解能を最適化することで、カウンタ回路の消費電力の低減が実現できる。

【図面の簡単な説明】

【0011】

【図1】実施形態にかかる光電変換装置の構成を示した概略図である。

【図2】光電変換装置のA/D変換動作を説明するタイミングチャートである。

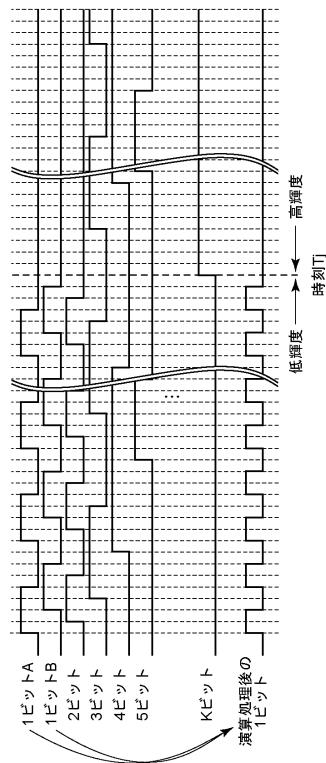

【図3】カウント値の各ビット動作を説明するタイミングチャートである。

50

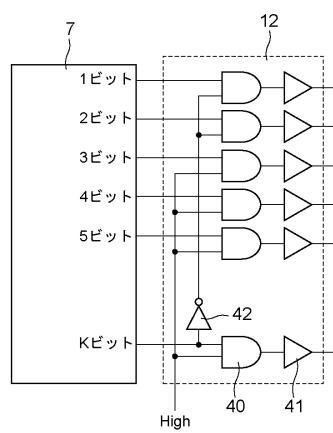

- 【図4】実施形態にかかるカウンタ回路とゲーティング回路の構成例である。

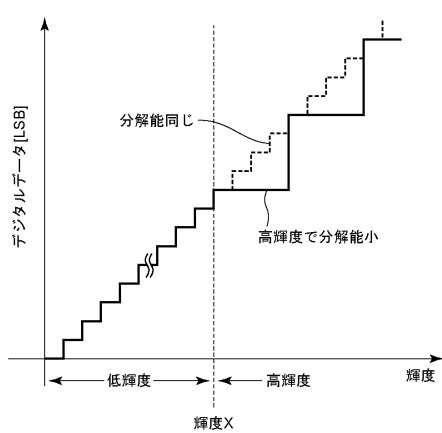

- 【図5】実施形態の、輝度とA/D変換の分解能の関係を説明する図面である。

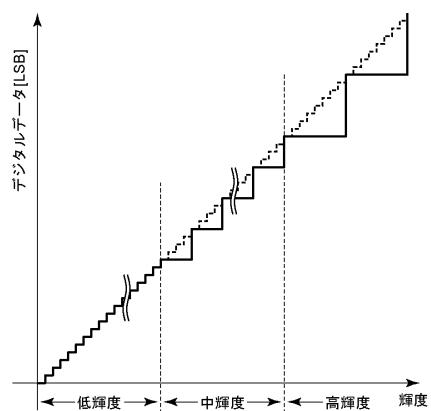

- 【図6】実施形態の、輝度とA/D変換の分解能の関係を説明する図面である。

- 【図7】実施形態のカウント値の各ビット動作の一例を説明するタイミングチャートである。

- 【図8】実施形態のカウント値の各ビット動作の一例を説明するタイミングチャートである。

- 【図9】実施形態にかかる光電変換装置の構成を示した概略図である。

- 【図10】光電変換装置のA/D変換動作を説明するタイミングチャートである。

- 【図11】実施形態にかかる列カウンタ部の動作を示すタイミングチャートである。 10

- 【図12】実施形態にかかる列カウンタ部の回路構成例である。

- 【図13】実施形態にかかる光電変換装置の構成を示した概略図である。

- 【図14】実施形態のカウント値の各ビット動作を説明するタイミングチャートである。

- 【図15】実施形態のタイミングチャートを実現する共通カウンタ部の構成例である。

- 【図16】積層構造の光電変換装置の概略図である。

- 【図17】光電変換システムの構成を示す図である。

- 【図18】移動体の構成及び動作を示す図である。

【発明を実施するための形態】

【0012】

以下、図面を参照しながら各実施形態を説明する。 20

【0013】

以下に述べる各実施形態では、本発明を適用可能な装置の一例として、光電変換装置の一例である撮像装置を中心に説明する。ただし、各実施形態は、光電変換装置に限られるものではなく、他の装置にも適用可能である。また、光電変換装置への適用についても撮像装置に限られるものではない。例えば、測距装置（焦点検出やTOF（Time Of Flight）を用いた距離測定等の装置）、測光装置（入射光量の測定等の装置）などに適用可能である。

【0014】

[第1の実施形態]

本発明の第一の実施形態について図1から図8を用いて説明する。 30

【0015】

（光電変換装置の全体構成）

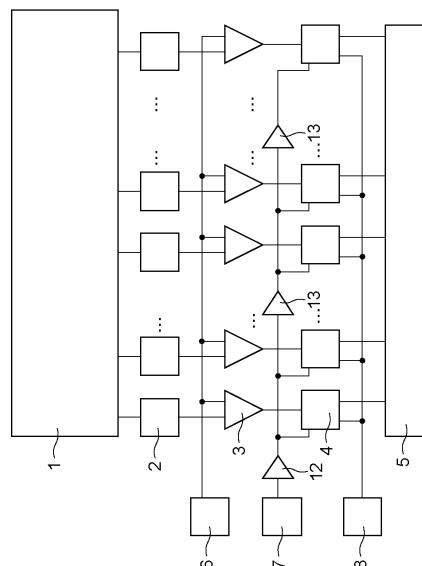

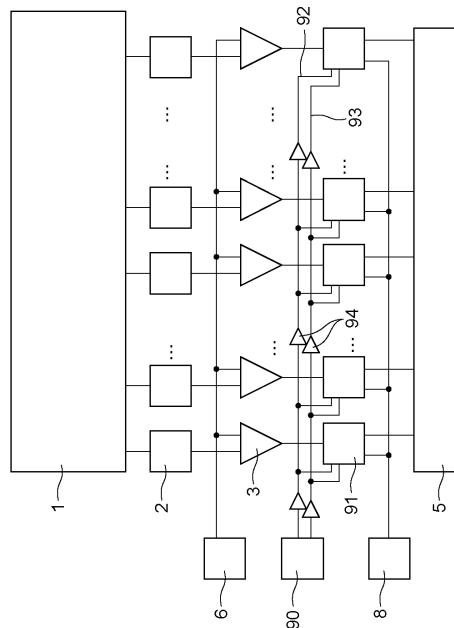

図1は本実施形態にかかる光電変換装置の構成を示した概略図である。本実施形態の光電変換装置は、画素部1と、読み出し回路2と、比較回路3と、列メモリ4と、水平走査回路5と、ランプ源6と、カウンタ回路7と、演算処理回路8と、ゲーティング部12と、バッファ部13とを含む。

【0016】

画素部1には、複数行及び複数列に渡ってアレイ状に配された複数の画素が設けられている。画素部1の画素アレイの各行には、列方向（図1において縦方向）に延在して、読み出し回路2が配されている。読み出し回路2は、列方向に並ぶ画素のそれぞれに列ごとに接続され、これらの画素で生じる電荷をアナログ信号である画素信号として出力する共通の信号線をなしている。 40

【0017】

画素部1を構成する画素の数は、特に限定されるものではない。例えば、一般的なデジタルカメラのように数千行×数千列の画素で画素部1を構成してもよく、1行又は1列に並べた複数の画素で画素部1を構成してもよい。

【0018】

カウンタ回路7より出力されるカウント値はゲーティング部12やバッファ部13を介して列メモリ4に入力される。ゲーティング部12とバッファ部13は、図に示したように複数列ごとに配置される。 50

## 【 0 0 1 9 】

比較回路 3 は、画素アレイの列ごとに読み出し回路 2 に接続されている。比較回路 3 には読み出し回路 2 の出力信号と、ランプ源 6 で生成されるランプ信号とが入力され、入力される信号同士の電位の大きさを比較する。読み出し回路 2 より出力される信号とランプ信号との電位の大小関係の反転によって時、比較回路 3 の出力電位も反転する。比較回路 3 の出力電位の反転によってカウンタ回路 7 から出力されるカウント値が列メモリ 4 にデジタルデータとして記憶される。この出力信号とランプ信号との比較処理を画素のリセット信号である出力信号と画素信号である出力信号とで 1 回ずつを行い、それぞれのデジタルデータを取得する。

## 【 0 0 2 0 】

列メモリ 4 に記憶されたデジタルデータは、水平走査回路 5 から出力される信号によって、列ごとに演算処理回路 8 に順次転送される。演算処理回路 8 では、リセット信号に対応するデジタルデータと画素信号に対応するデジタルデータを減算する演算処理を行うことで、デジタル CDS ( デジタル相関二重サンプリング ) を実現する。なお、図 1 において各回路に必要なパルスとそのタイミングを制御する回路は省略している。

## 【 0 0 2 1 】

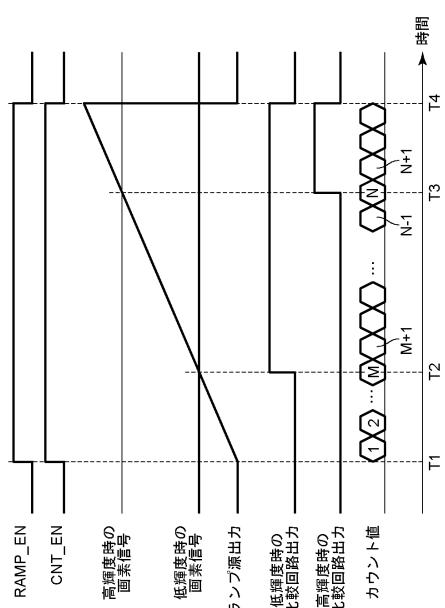

## ( 光電変換装置の A D 変換 )

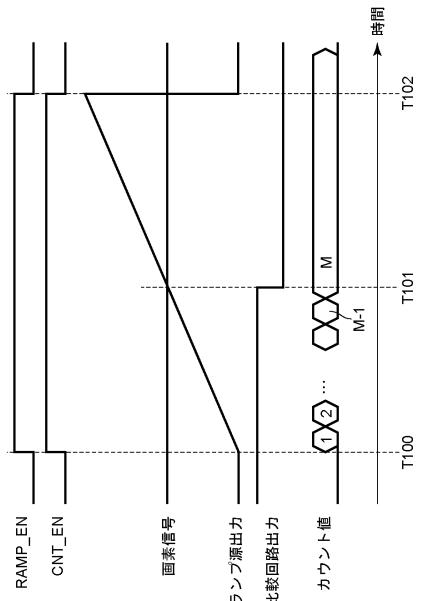

光電変換装置の A D 変換動作について図 2 のタイミングチャートを用いて詳細に説明する。

## 【 0 0 2 2 】

図 2 は、輝度によらず A D 変換の分解能が一定な場合のタイミングチャートである。以下の説明では、入射される光の輝度が高くなると、読み出し回路 2 の処理により画素信号のレベルは高くなるものとする。読み出し回路 2 は例えば反転増幅アンプを含む。

## 【 0 0 2 3 】

時刻 T 1 でランプ源 6 の制御信号 RAMP\_EN およびカウンタ回路 7 の制御信号 CNT\_EN が High になると、RAMP\_EN が High になると、ランプ源 6 は、時間の経過とともに電位が上昇するランプ信号を出力する。また、CNT\_EN が High になるとカウンタ回路 7 がカウント動作を開始し、ランプ信号の変化に並行してカウント動作が行われる。

## 【 0 0 2 4 】

ここで、ランプ信号は時間経過に応じて連続的に電位が上昇するような信号でもよいし、ノコギリ状に電位が変化する信号でも構わない。前者の場合、電位の立ち上がりで電位変化が鈍る場合も許容される。

## 【 0 0 2 5 】

入射光が低輝度の時の画素信号は、入射光が高輝度の時の画素信号よりもレベルが低いので、時間の経過とともに電位が上昇するランプ信号では画素信号の電位とランプ信号の電位の大小関係が反転するタイミングは高輝度の時よりも低輝度の時の方が早い。

## 【 0 0 2 6 】

低輝度の光が入射した時、画素信号とランプ信号の両電位の大小関係が反転する時刻を T 2 とする。同時刻で比較回路出力は Low から High に遷移する。比較回路出力が Low から High に遷移すると、列メモリ 4 はこのときのカウント値 M ( M は整数 ) を記憶する。

## 【 0 0 2 7 】

高輝度の光が入射した時の画素信号は低輝度の光が入射したときの画素信号よりもレベルが高いので、画素信号の電位とランプ信号の電位の大小関係が反転するタイミングは時刻 T 2 よりも遅くなる。高輝度の光が入射した時の両電位の大小関係が反転する時刻を T 3 とすると、時刻 T 3 で比較回路出力が Low から High に遷移し、列メモリはその時のカウント値 N ( N は整数、 N > M ) を記憶する。

## 【 0 0 2 8 】

時刻 T 4 になると RAMP\_EN および CNT\_EN が Low になり、ランプ源出力も電

10

20

30

40

50

位の上昇を停止して基準電位に戻る。ここで基準電位とはランプ信号が電位の上昇を開始する時点の電位を指すものとする。カウンタ回路7はカウント動作を終了する。以上の動作を行うことでA/D変換を実現する。上記A/D変換に用いる回路を以降アナログデジタル変換回路(A/D変換回路)と称する。

【0029】

上記のA/D変換手法では、入射光の輝度が高くなるにつれて、比較回路がLowからHighに遷移するタイミングが遅くなる。つまり、入射光の輝度が高くなるにつれて、列メモリが記憶するカウント値は大きくなる。

【0030】

なお、図2に示したタイミングチャートは一例であり、本実施形態を限定するものではない。 10

【0031】

(本実施形態の駆動)

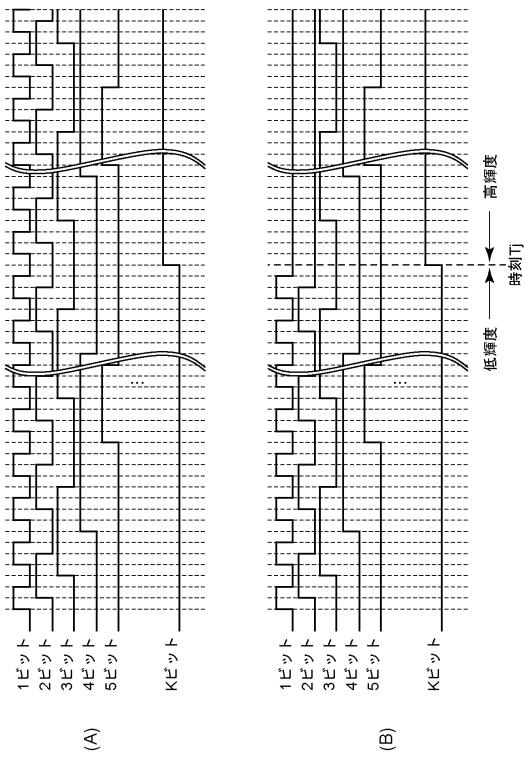

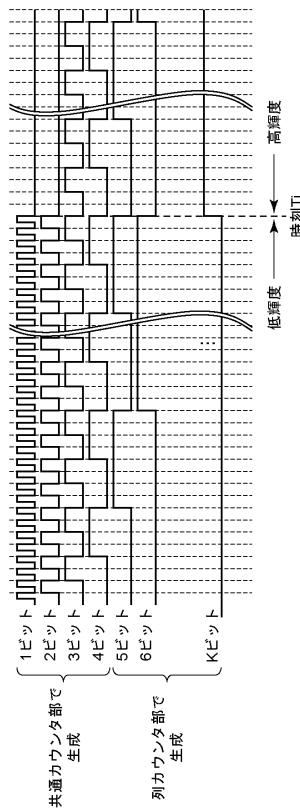

図3、図4を用いて本実施形態の駆動について説明する。

【0032】

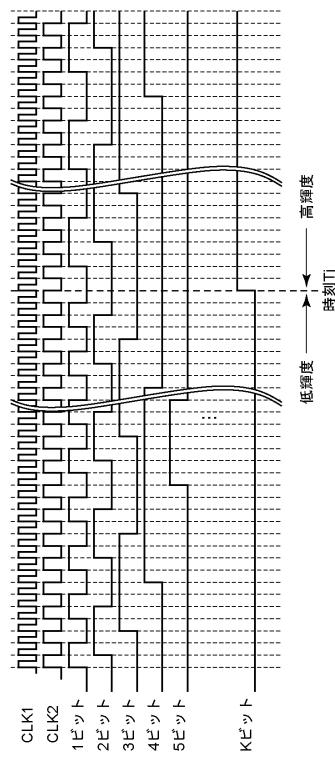

図3(A)および(B)はカウンタ回路7をKビット(Kは整数)のグレイコードカウンタとした場合の、各列メモリに入力される各ビットの動作を示したタイミングチャートである。図3(A)は、輝度によらず、A/D変換の分解能を一定とした場合のタイミングチャートである。図3(B)は本実施形態を適用し、高輝度領域で下位ビットの動作を止めた場合のタイミングチャートである。図3(B)では、カウンタ回路7のKビット目がLowからHighに遷移する時刻Tjより前の第1の期間に比較回路3出力が反転する場合の輝度を低輝度とし、時刻Tjより後の第2の期間に比較回路出力が反転する場合の輝度を高輝度としている。 20

【0033】

図4は図3(B)に示したタイミングチャートの動作を実現するカウンタ回路7とゲーティング部12の一例である。

【0034】

ゲーティング部12は、カウンタ回路7の各ビット出力に接続されるAND回路40と、AND回路40のそれぞれに接続されるバッファ回路41と、インバータ回路42とで構成される。図示した通り、バッファ回路41の出力が、ゲーティング部12の出力となる。3ビット目からKビット目までのAND回路40のもう一方の入力端子には、Highレベルの信号が入力され、1、2ビット目のAND回路40の入力端子にはカウンタ回路7のKビット目の出力がインバータ回路42によって反転された信号が入力される。よって、1、2ビット目のAND回路40出力は、カウンタ回路7のKビット目がHighになるとLowに固定され、1、2ビット目のAND回路40に接続されたバッファ回路41の出力もLowに固定される。AND回路40にHigh信号が入力されている他のビットは、輝度によらず、カウンタ回路7の出力をバッファ回路を介して出力する。ここで、High信号には例えばゲーティング部12内で使用する電源電圧を接続すればよい。

【0035】

以上のようにゲーティング部12を構成することによって、図3(B)のタイミングチャートに示した動作が実現可能である。図4に示したゲーティング部12により、高輝度側で1、2ビット目がゲーティングされるので、次段以降のバッファ部も1、2ビット目は動作しない。よって、ゲーティング部12およびバッファ部13が輝度によらず全ビット動作する図3(A)に示したタイミングチャートの動作より、本実施形態の図3(B)に示したタイミングチャートの動作の方が消費電力を低減できる。言い換えると、カウント処理を高速に実行する第1の期間に対し、第2の期間ではカウント処理を低速に実行することで消費電力を低減することが可能である。 40

【0036】

ここで、下位ビット側は上位ビット側と比較してゲーティング部12、バッファ部13内 50

の動作回数が多いので、動作を停止した際の電力削減の効果が大きい。

【0037】

なお、ゲーティングを行うのは最下位ビット側の2ビットとしたが、遅延量をそろえるために全ビットにAND回路40を配置している。AND回路はその他の論理回路の組み合わせとしても構成可能である。

【0038】

図5は、光電変換装置に入射される光の輝度とそれに対応するデジタルデータを説明する図面である。

【0039】

図5において、輝度X以上の輝度を高輝度、輝度X以下の輝度を低輝度とする。高輝度の光が入射するときに本実施形態を適用した場合のデジタルデータの変化を実線で示し、従来技術の場合のデジタルデータの変化は点線で示している。本実施形態を適用した場合も従来技術の場合も、低輝度領域におけるAD変換の分解能は等しい。

10

【0040】

図5では図3(B)、図4と同様、高輝度領域でカウンタ回路の下位2ビットをゲーティングするものとする。カウンタ回路の下位2ビットをゲーティングするので、高輝度領域において、点線での4階調分の輝度の変化が実線の1階調分の輝度の変化になる。

20

【0041】

一般的に、撮影された画像において、高輝度よりも低輝度の方が輝度の変化に対する視認性が高い。したがって、分解能の変化を視認されにくい高輝度領域であれば分解能を小さくしても画質への影響は小さい。よって、本実施形態を適用すれば、画質に与える影響を抑えて消費電力低減を実現できる。

20

【0042】

本実施形態は、輝度領域を2以上の任意の領域に細分化し、それぞれの輝度領域で異なる分解能を設定することも可能である。輝度領域の分け方や分解能は求められる画質によって設定することができる。

30

【0043】

図5では輝度の領域を低輝度と高輝度の2種類に分けて分解能を切り替えたが、図6では輝度の領域を低輝度、中輝度、高輝度の3つにわけ、それぞれの領域で異なる分解能を設定している。

30

【0044】

図6では、中輝度以上の輝度領域で、入射光が低輝度のときから分解能を変更しない場合のデジタルデータの変化を点線で示し、分解能を変更する場合のデジタルデータの変化を実線で記載している。この例では中輝度領域ではカウンタ回路の下位2ビット、高輝度の領域ではカウンタ回路の下位3ビットをゲーティングし、ゲーティングしたビットが動作しないようにしている。よって中輝度領域での1階調の変化は、低輝度領域での4階調分の変化に相当し、高輝度領域での1階調分の変化は低輝度領域での8階調分の変化に相当する。

30

【0045】

これまで、カウンタ回路7に一般的なグレイコードカウンタを用いる場合について説明してきたが、図7に示すタイミングチャートのような動作をするカウンタにも本実施形態は適用可能である。

40

【0046】

図7に示したタイミングチャートでは、1ビット目にあたる信号を位相の異なる2つの信号1ビットAと1ビットBとにおきかえている。2ビット目以降は一般的なグレイコードカウンタと同じ動作である。位相の異なる信号1ビットAと1ビットBとは、比較回路3の出力の反転に応じたレベルを列メモリにそのまま格納する。演算処理回路8の演算処理で、列メモリ4に記憶された1ビットAと1ビットBの排他的論理和( XOR )を得る処理を行うことで、1ビット目の信号を生成することができる。図7に示したタイミングチャートのような動作は、例えばカウンタ回路の動作周波数が早く、回路動作が困難な場

50

合などで好適に使用できる。

【0047】

図7では最下位ビットである1ビット目のみを位相の異なる信号で代用する構成を説明したが、本実施形態はそれに限定されない。複数ビットを複数の位相の異なる信号でおきかえて、演算処理で該複数ビットを生成してもよい。

【0048】

また、これまで、カウンタ回路7の出力にゲーティング部12を接続し、ゲーティング部12で複数ビットの動作を停止していたが、本実施形態はそれに限定されない。例えば、カウンタ回路7内で、下位複数ビットのカウント動作を停止する構成であってもよい。その場合は、ゲーティング部12を配置する必要はない。

10

【0049】

図8に示すタイミングチャートは、カウンタ回路7に周波数の高いクロックCLK1と周波数の低いクロックCLK2とを供給する例である。

【0050】

図8のタイミングチャートでは、図3同様にカウンタ回路7のKビット目がLowからHighに遷移する時刻Tjを境に低輝度領域と高輝度領域とを分けている。カウンタ回路7は、低輝度領域ではCLK1に同期してカウント動作を行い、高輝度領域ではCLK2に同期してカウント動作を行っている。なお、図8の例ではCLK2の周波数はCLK1の周波数の1/2であり、カウンタ回路7はグレイコードカウンタである。

20

【0051】

この構成では、時刻Tj以前にAD変換が終了した場合はそのまま演算処理を行い、得られたカウント値に対応するデジタルデータを得ることができる。

【0052】

一方時刻Tj以後にAD変換が終了する場合は、1ビット目からK-1ビット目のカウント値に対応するデジタルデータを2倍にした値と、Kビット目の値 $2^{(K-1)}$ とを足すことで、分解能が小さくなつたKビットのデジタルデータを得ることができる。

30

【0053】

図8に示した例では、高輝度領域でカウンタ回路7の動作周波数が低くなり、カウンタ回路7の後段に接続されるバッファ部13の動作周波数も低くなるので、これまでと同様に消費電力の低減が可能である。

30

【0054】

なお、図8のタイミングチャートの場合、カウンタ回路7の内部で分解能を小さくするので、ゲーティング部12を配する必要はない。

【0055】

ここまでカウンタ回路7をグレイコードカウンタとして説明してきたが、カウンタ回路7はグレイコードカウンタに限定されず、例えば、適用できるならばバイナリカウンタであつてもよい。全列の列メモリに対して、カウンタ回路7を一つとしたが、複数の列メモリごとにカウンタ回路7を配置してもよい。

40

【0056】

また、高輝度側になると、下位ビットがLowに固定されるものとして説明したが、本実施形態はそれに限定されない。例えばHighに固定してもよいし、可能ならば中間電位に固定してもよい。

【0057】

カウンタ回路7の出力のうち、ある1ビットの信号でゲーティングしたが、本実施形態はそれに限定されない。複数ビットの信号を用いて、ゲート信号を生成してもよい。

【0058】

本実施形態では、時刻Tj以前を第1の期間、時刻Tj以後を第2の期間とし、第1の期間と第2の期間とを連続した期間として説明したが、例えば第1の期間の経過後第2の期間の開始までの間にカウンタを休止させる第3の期間が存在してもかまわない。

50

【0059】

## [ 第二の実施形態 ]

本実施形態について図9から図12を用いて説明する。

## 【 0 0 6 0 】

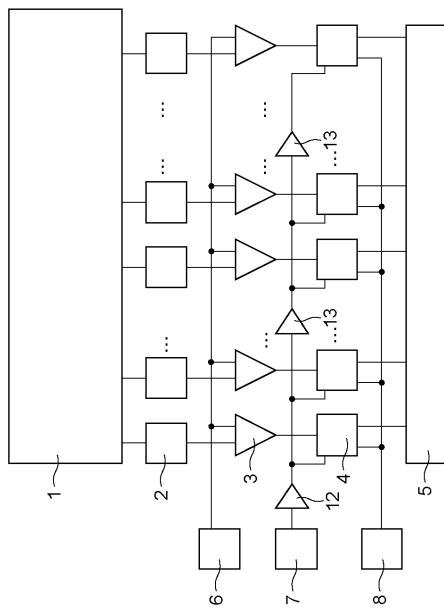

図9は本実施形態における光電変換装置を説明する図面である。図9における各番号のうち図2と同一のものには同一符号を付してあるため説明を省略し、主として第一の実施形態と異なる部分を説明する。

## 【 0 0 6 1 】

図9の光電変換装置では、図1のカウンタ回路7と列メモリ4が、CLK生成回路90と列カウンタ部91に変更されている。

## 【 0 0 6 2 】

列カウンタ部91には高周波数のクロックが伝搬するCLK配線92と低周波数のクロックが伝搬するCLK配線93とが接続される。CLK配線92、93には複数列ごとにクロックバッファ回路94が配置されている。

## 【 0 0 6 3 】

図10に、本実施形態におけるAD変換動作のタイミングチャートを示す。

## 【 0 0 6 4 】

図2で説明した箇所については、詳細な説明を省略する。図2と同様に、入射光の輝度が高くなれば、読み出し回路2の処理により画素信号の電位も大きくなるものとする。また、比較回路3の出力はランプ信号の電位が画素信号より大きいとき、Lowになるものとする。

## 【 0 0 6 5 】

時刻T100で制御信号RAMPE\_Nおよび制御信号CNT\_ENがLowからHighに遷移し、電位が時間によって変化するランプ信号の出力が開始されるとともに、列カウンタ部91はカウント動作を開始する。

## 【 0 0 6 6 】

時刻T101になると、比較回路3に入力されるランプ信号と画素信号との電位の大小関係が反転し、比較回路3の出力がHighからLowに遷移する。このタイミングで列カウンタ部91のカウント動作を終了し、その時のカウント値M(Mは整数)を保持することで、AD変換を実現する。その後、演算処理回路にデータを転送し、演算処理を行う。

## 【 0 0 6 7 】

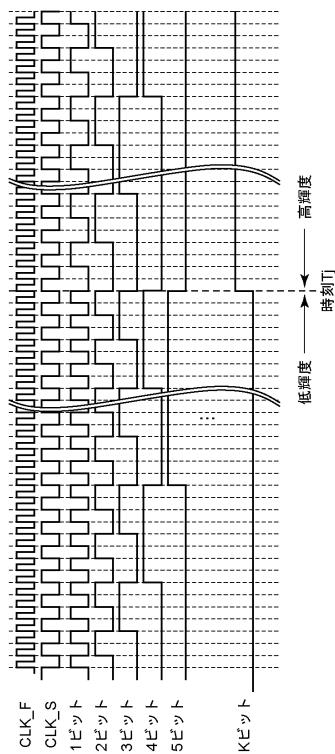

図11は本実施形態における列カウンタ部91の動作を説明するタイミングチャートである。

## 【 0 0 6 8 】

高周波数のクロックをCLK\_F、低周波数のクロックをCLK\_Sとし、列カウンタ部91をバイナリカウンタとしている。図11ではCLK\_Sの周波数をCLK\_Fの周波数の1/2としている。カウンタのKビット目がLowからHighに遷移する時刻Tjより前に比較回路3の出力が反転する場合の輝度低輝度、時刻Tjより後に比較回路3の出力が反転する場合の輝度は高輝度としている。

## 【 0 0 6 9 】

列カウンタ部に入力される2つのクロックのうち、入射光が低輝度領域に属する輝度の場合はカウンタ部91をCLK\_Fに同期してカウント動作がされる。高輝度領域に属する輝度の光が入射する場合はカウンタ部91をCLK\_Sに同期してカウント動作がなされる。

## 【 0 0 7 0 】

時刻Tjより前にAD変換が終了した場合は、保持されたカウント値がそのままデジタルデータとなる。時刻Tj後にAD変換が終了する場合は、1ビット目からK-1ビット目に対応するデジタルデータを2倍にした値と、Kビット目の値 $2^{K-1}$ とを足せば、分解能が小さくなったKビットのデジタルデータを得ることができる。

## 【 0 0 7 1 】

図12は図11に示したタイミングチャートの動作を実現する列カウンタ部91の一例で

10

20

30

40

50

ある。

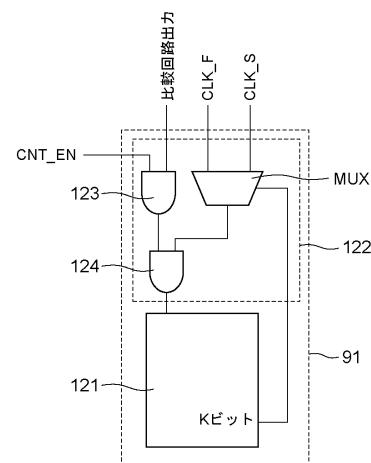

【0072】

列カウンタ部91は列カウンタ回路121と、クロックゲート回路122とで構成される。

【0073】

クロックゲート回路122はマルチプレクサMUXと2入力のAND回路123、124とで構成される。

【0074】

AND回路123には信号CNT\_ENと比較回路出力が入力される。

【0075】

マルチプレクサMUXには高周波クロックCLK\_Fと低周波クロックCLK\_Sとが入力され、さらに制御入力として列カウンタ回路121のKビット目の出力が入力される。マルチプレクサMUXは列カウンタ回路121のKビット目がLowの時はCLK\_Fを出力し、Highの時はCLK\_Sを出力する。

【0076】

AND回路124の入力には、マルチプレクサMUXの出力とAND回路123の出力とが入力され、AND回路124を介して列カウンタ回路121に動作用クロックが供給される。

【0077】

図12の回路より、比較回路出力がHighかつ、信号CNT\_ENがHighで、列カウンタ回路121のKビット目がLowの時にCLK\_Fが列カウンタ部91に供給される。

【0078】

一方、比較回路出力がHighかつ、信号CNT\_ENがHighで、列カウンタ回路121のKビット目がHighの時にはCLK\_Sが列カウンタ部91に供給される。

【0079】

なお、図12に示した回路は列カウンタ部91の一例であり、構成を限定するものではない。

【0080】

以上の説明より、列カウンタ部を有する光電変換装置においても、ある輝度以上の光について分解能を小さくすることで光電変換装置の消費電力低減が可能である。また、前述の通り、輝度の変化が視認されにくい高輝度領域で分解能を小さくするので、画質への影響は小さい。

【0081】

これまで、列カウンタ部に2種類のクロックが入力されるものとして説明したが、本実施形態はそれに限定されない。例えば、1種類のクロックのみを列カウンタ部に入力し、もう1種類のクロックを列カウンタ部内で生成してもよい。また、3種類以上のクロックを列カウンタ部に入力してもよい。例えば3種類のクロックを用いれば、図6に示したように輝度領域を低輝度領域、中輝度領域、高輝度領域にわけ、それぞれの領域で分解能を設定することが可能である。

【0082】

本実施例では列カウンタ回路121の出力のうちある1ビットの信号でゲーティングしたが、複数ビットの信号を用いて、ゲート信号を生成してもよい。

【0083】

[第三の実施形態]

本実施形態について図13～図15を用いて説明する。

【0084】

図13は本実施形態における光電変換装置を示した図面である。これまでに説明した箇所について詳しい説明を省略し、主として第一及び第二の実施形態と異なる部分を説明する。

10

20

30

40

50

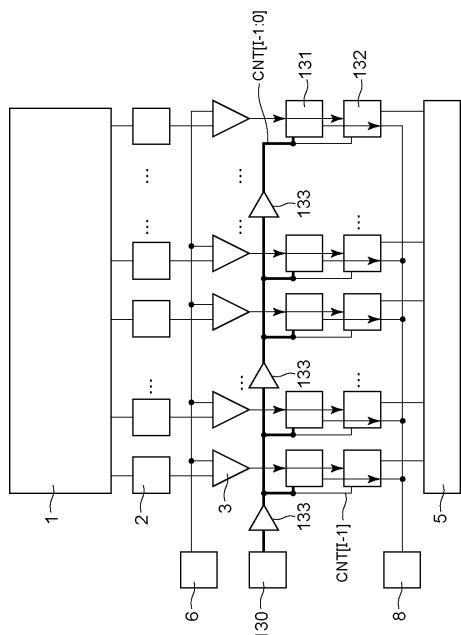

## 【0085】

図13に示す光電変換装置は、画素アレイの列ごとに列メモリ131と列カウンタ部132を備える。列メモリ131には、バッファ回路133を介して、共通カウンタ部130で生成されるIビット(Iは整数)のカウント値CNT[I-1:0]を入力する。列カウンタ部132にはIビットのカウント値のうち最上位ビットの信号CNT[I-1]が入力される。

## 【0086】

AD変換が開始されるとともに共通カウンタ部130が動作を開始する。列カウンタ部132は、共通カウンタ部130で生成される信号CNT[I-1]の入力されるパルス数をカウントする。ランプ信号と画素信号の電位の大小関係が反転し、比較回路3の出力が反転すると、列メモリ131はカウント値CNT[I-1:0]を記憶する。また、列カウンタ部132はカウント動作を停止し、自身でカウントしている値を保持する。

## 【0087】

図13の例では、AD変換されたデジタルデータのうち、下位ビットは共通カウンタ部130のカウント値から生成され、上位ビットは列カウンタ部132のカウント値から生成される。AD変換が終了すると、列メモリ131に記憶された下位ビットのデータと、列カウンタ部132で保持されている上位ビットのデータとが演算処理回路8に伝搬され、演算処理がなされてデジタルデータが生成される。

## 【0088】

図14は図13の光電変換装置に本実施形態を適用した場合の、共通カウンタ部130および列カウンタ部132の動作を説明するタイミングチャートである。説明を簡単にするために、共通カウンタ部130はバイナリカウンタによってカウント値を生成するものとする。

## 【0089】

本実施形態では、デジタルデータの下位4ビットを共通カウンタ部130でカウントし、残りの上位ビットを列カウンタ部132でカウントする。列カウンタ部132に入力されるクロックは、共通カウンタ部130から出力される4ビット目の信号の反転信号である。よって、列カウンタ部132は共通カウンタ部130から出力される4ビット目の立下りエッジに同期して動作する。時刻TjでKビット目がHighになり、その信号で下位2ビットを固定する。時刻Tj以降ではAD変換終了まで下位2ビットはLowに固定されている。

## 【0090】

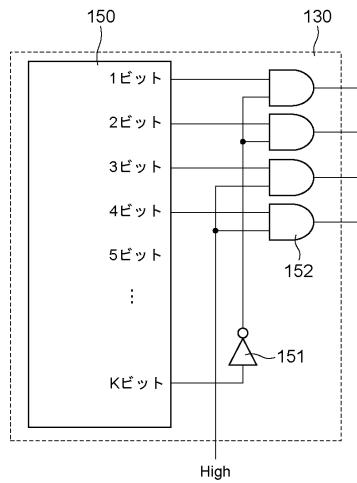

図15は図14に示したタイミングチャートの動作を実現する共通カウンタ部130の一例である。

## 【0091】

図15の例では、共通カウンタ部130はKビットのカウンタ回路150、インバータ回路151、4つのAND回路152で構成される。カウンタ回路150はKビットカウンタであるが、共通カウンタ部130からは下位4ビットのみが出力される。

## 【0092】

カウンタ回路150のKビット目がHighになると、インバータ回路151によりLowに反転された信号が、1、2ビット目のAND回路に入力される。よって、Kビット目がHighになった時刻Tj以降では1、2ビット目の出力はLowに固定される。3、4ビット目のAND回路152にはHighが入力されているため、3、4ビット目は時刻Tj以降もそのまま共通カウンタ部130から出力される。共通カウンタ部130からは下位4ビットのみが出力されるが、Kビット目の信号を下位2ビットのゲート信号として使用するため、カウンタ回路150をKビットカウンタとしている。なお、3、4ビット目をゲートする必要はないが、出力する4ビットすべてで遅延量をそろえるために、3、4ビット目にもAND回路152を配置している。

## 【0093】

以上説明してきた通り、本実施形態では高輝度領域で共通カウンタ部130の下位ビット

10

20

30

40

50

を L o w に固定することで、ゲートされた下位ビットのバッファ回路 133 が動作しなくなり、その分の消費電力の低減が実現できる。前述の通り、分解能が小さくなるのは輝度の変化が視認されにくい高輝度領域なので、画質への影響は小さい。よって本実施形態を適用すれば、画質低下を抑制しつつ、消費電力の低減が可能となる。

#### 【 0 0 9 4 】

本実施形態では共通カウンタ部 130 ではバイナリカウンタでカウント値を生成されるとしたが、本実施形態はそれに限定されない。例えば、グレイコードカウンタであってもよい。

#### 【 0 0 9 5 】

カウンタ回路 150 を K ビットとしたが、例えば、4 ビットのカウンタとし、K ビット目の信号を列カウンタ部 132 から共通カウンタ部 130 に供給し、その信号をゲート信号として使用してもよい。

#### 【 0 0 9 6 】

図 15 のタイミングチャートでは下位 2 ビットをゲートするものとして説明したが、下位 1 ビットでもよいし、3 ビット以上であってもよい。また、図 7 のタイミングチャートで説明したように、複数の信号の位相をずらすことで、下位ビットの信号を生成してもよい。

#### 【 0 0 9 7 】

本実施形態では、下位ビットをゲートする構成で説明したが、これまでにも説明したように、低輝度領域と高輝度領域でカウンタの動作周波数が異なる構成であってもよい。

#### 【 0 0 9 8 】

カウンタ回路 150 のある 1 ビットの信号でカウンタをゲーティングしたが、本実施形態はそれに限定されない。複数ビットの信号を用いて、ゲート信号を生成してもよい。また、列カウンタ部 132 の出力の複数ビットを用いてゲート信号を生成してもよい。

#### 【 0 0 9 9 】

以上第一の実施形態から第三の実施形態までの説明では、読み出し回路から出力される画素信号は入射される光の輝度に応じて、電位が大きくなるものとして説明したが、本実施形態はそれに限定されない。輝度に応じて、電位が小さくなる構成であってもよい。読み出し回路に、入力信号にゲインをかけられるアンプを配置してもよい。その際アンプは反転アンプでも、非反転アンプでもよい。

#### 【 0 1 0 0 】

第一の実施形態から第三の実施形態までの説明では、下位ビットのゲートや、A D 変換に用いるカウンタの動作周波数の変更に、該カウンタの出力信号を用いていたが、本実施形態はそれに限定されない。例えば、前記カウンタ以外に時間計測手段を持ち、該時間計測手段で生成される信号で、あるビットをゲートする、もしくは前記カウンタの動作周波数を変更する構成であってもよい。

#### 【 0 1 0 1 】

なお、前述したデジタル C D S を行うために、画素のリセット信号と画素信号のそれぞれで A D 変換を行うが、本実施形態は画素信号の A D 変換時により好適に使用できる。

#### 【 0 1 0 2 】

また、焦点距離検出機能を有する光電変換装置において、画素から焦点距離検出用の第 1 の信号と、画像情報用の第 2 の信号とをそれぞれ読み出す技術が知られている。本実施形態はそのような技術にも好適に適用できる。焦点距離検出用の第 1 の信号を読み出す第一の画素群と、画像情報用の第 2 の信号を読み出す第二の画素群を有する光電変換装置を例に挙げる。このような光電変換装置において、例えば画像情報である第 2 の信号の低輝度領域において分解能を大きく、高輝度領域において分解能を小さくすることが可能である。焦点距離検出用である第 1 の信号は、画像情報として使用しないことから第 2 の信号ほどの分解能は必要がない場合も考えられる。その場合は第 1 の信号の分解能を第 2 の信号の分解能よりも小さくすることが可能となる。

#### 【 0 1 0 3 】

10

20

30

40

50

以上のように、入射される光の輝度に応じて第1の信号、第2の信号のそれぞれの分解能を設定することで、焦点距離検出機能を有する光電変換装置においても消費電力の低減が可能である。

#### 【0104】

本実施形態は撮影モードごとに適用可否を設定できる。例えば高い画質が必要な静止画撮影モードにおいては輝度によらず分解能を一定とし、動画撮影モードにおいては、輝度によって分解能を設定することが可能である。また、各撮影モードにおいて、輝度領域とその領域における分解能をそれぞれで設定することも可能である。

#### 【0105】

なお、各実施例における光電変換装置は図16に示すような積層型の構成をとっても構わない。

#### 【0106】

図16に示した積層構造の光電変換装置は画素基板300と、回路基板310を有する。画素基板300には少なくとも画素部1が配される。回路基板には比較回路3、列メモリ4、ランプ源6、カウンタ回路7といった回路部が配されるが、回路の配置は回路基板上に限られず、例えば画素基板300にランプ源6やその他の回路を配してもよい。各回路はその一部を画素基板300に配し、他の一部を回路基板301に配してもよい。図16では2枚の基板からなる積層構造を示したが、例えばさらに回路を分割するか、回路や機能を追加するなどして3枚以上の基板からなる積層構造にしてもよい。

#### 【0107】

#### [第四の実施形態]

本実施形態による光電変換システムについて、図17を用いて説明する。図17は、本実施形態による光電変換システムの概略構成を示すブロック図である。

#### 【0108】

上記第1～第3実施形態で述べた光電変換装置（撮像装置）は、種々の光電変換システムに適用可能である。適用可能な光電変換システムの例としては、デジタルスチルカメラ、デジタルカムコーダ、監視カメラ、複写機、ファックス、携帯電話、車載カメラ、観測衛星などが挙げられる。また、レンズなどの光学系と撮像装置とを備えるカメラモジュールも、光電変換システムに含まれる。図17には、これらのうちの一例として、デジタルスチルカメラのブロック図を例示している。

#### 【0109】

図17に例示した光電変換システムは、光電変換装置の一例である撮像装置1004、被写体の光学像を撮像装置1004に結像させるレンズ1002を有する。さらに、レンズ1002を通過する光量を可変にするための絞り1003、レンズ1002の保護のためのバリア1001を有する。レンズ1002及び絞り1003は、撮像装置1004に光を集光する光学系である。撮像装置1004は、上記のいずれかの実施形態の光電変換装置（撮像装置）であって、レンズ1002により結像された光学像を電気信号に変換する。

#### 【0110】

光電変換システムは、また、撮像装置1004より出力される出力信号の処理を行うことで画像を生成する画像生成部である信号処理部1007を有する。信号処理部1007は、必要に応じて各種の補正、圧縮を行って画像データを出力する動作を行う。信号処理部1007は、撮像装置1004が設けられた半導体基板に形成されていてもよいし、撮像装置1004とは別の半導体基板に形成されていてもよい。

#### 【0111】

光電変換システムは、更に、画像データを一時的に記憶するためのメモリ部1010、外部コンピュータ等と通信するための外部インターフェース部（外部I/F部）1013を有する。更に光電変換システムは、撮像データの記録又は読み出しを行うための半導体メモリ等の記録媒体1012、記録媒体1012に記録又は読み出しを行ったための記録媒体制御インターフェース部（記録媒体制御I/F部）1011を有する。なお、記録媒体1

10

20

30

40

50

012は、光電変換システムに内蔵されていてもよく、着脱可能であってもよい。

【0112】

更に光電変換システムは、各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部1009、撮像装置1004と信号処理部1007に各種タイミング信号を出力するタイミング発生部1008を有する。ここで、タイミング信号などは外部から入力されてもよく、光電変換システムは少なくとも撮像装置1004と、撮像装置1004から出力された出力信号を処理する信号処理部1007とを有すればよい。

【0113】

撮像装置1004は、撮像信号を信号処理部1007に出力する。信号処理部1007は、撮像装置1004から出力される撮像信号に対して所定の信号処理を実施し、画像データを出力する。光電変換システムは、この画像データを用いて、画像を生成する。10

【0114】

このように、本実施形態によれば、上記のいずれかの実施形態の光電変換装置（撮像装置）を適用した光電変換システムを実現することができる。

【0115】

[第五の実施形態]

本実施形態の光電変換システム及び移動体について、図18を用いて説明する。図18は、本実施形態の光電変換システム及び移動体の構成を示す図である。

【0116】

図18（a）は、車載カメラに関する光電変換システムの一例を示したものである。光電変換システム300は、撮像装置310を有する。撮像装置310は、上記のいずれかの実施形態に記載の光電変換装置（撮像装置）である。光電変換システム300は、撮像装置310により取得された複数の画像データに対し、画像処理を行う画像処理部312と、光電変換システム300により取得された複数の画像データから視差（視差画像の位相差）の算出を行う視差取得部314を有する。また、光電変換システム300は、算出された視差に基づいて対象物までの距離を算出する距離取得部316と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部318と、を有する。ここで、視差取得部314や距離取得部316は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部318はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA（Field Programmable Gate Array）やASIC（Application Specific Integrated Circuit）等によって実現されてもよいし、これらの組合せによって実現されてもよい。2030

【0117】

光電変換システム300は車両情報取得装置320と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、光電変換システム300は、衝突判定部318での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御部ECU330が接続されている。また、光電変換システム300は、衝突判定部318での判定結果に基づいて、ドライバーへ警報を発する警報装置340とも接続されている。例えば、衝突判定部318の判定結果として衝突可能性が高い場合、制御部ECU330はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置340は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。40

【0118】

本実施形態では、車両の周囲、例えば前方又は後方を光電変換システム300で撮像する。図18（b）に、車両前方（撮像範囲350）を撮像する場合の光電変換システムを示した。車両情報取得装置320が、光電変換システム300ないしは撮像装置310に指

示を送る。このような構成により、測距の精度をより向上させることができる。

【0119】

上記では、他の車両と衝突しないように制御する例を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。更に、光電変換システムは、自車両等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体（移動装置）に適用することができる。加えて、移動体に限らず、高度道路交通システム（ITS）等、広く物体認識を利用する機器に適用することができる。

【符号の説明】

【0120】

1 画素部

3 比較回路

6 ランプ源

7 カウンタ回路

12 ゲーティング部

【図面】

【図1】

【図2】

10

20

30

40

50

【図3】

【図4】

10

20

30

40

【図5】

【図6】

50

【図7】

【図8】

10

20

30

40

【図9】

【図10】

50

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

【図14】

【図15】

【図16】

10

20

30

40

【図17】

【図18】

50

---

フロントページの続き

キヤノン株式会社内

(72)発明者 有嶋 優

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

F ターム(参考) 5C024 CY17 CY42 GY31 HX23 HX29 HX32

5J022 AA09 BA06 CB08 CD04 CE05 CE08 CF01 CF02 CF10 CG04